# Dual 14-Bit 250Msps ADC with JESD204B Serial Outputs

## **FEATURES**

- 5Gbps JESD204B Interface

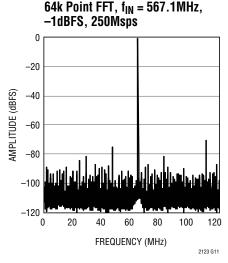

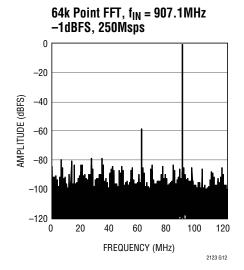

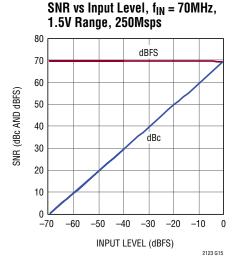

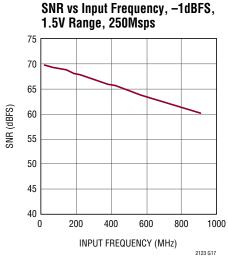

- 70dBFS SNR

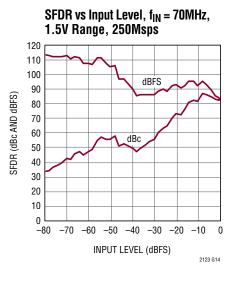

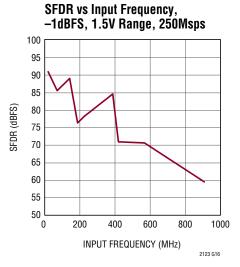

- 90dBFS SFDR

- Low Power: 864mW Total

- Single 1.8V Supply

- Easy to Drive 1.5V<sub>P-P</sub> Input Range

- 1.25GHz Full Power Bandwidth S/H

- Optional Clock Divide by Two

- Optional Clock Duty Cycle Stabilizer

- Low Power Sleep and Nap Modes

- Serial SPI Port for Configuration

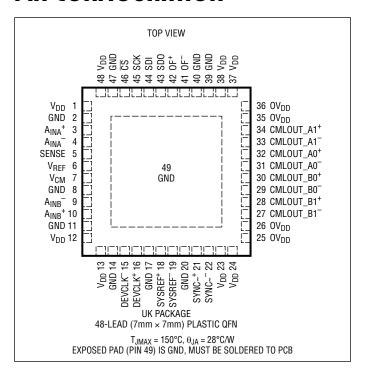

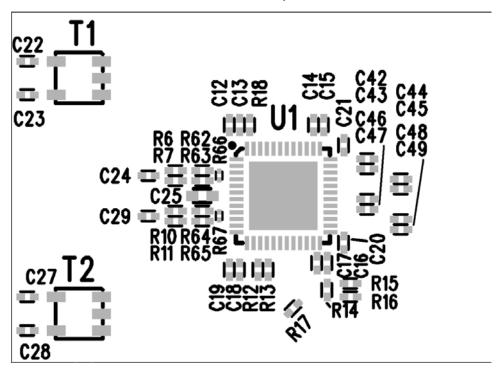

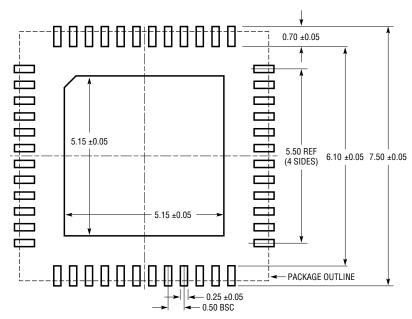

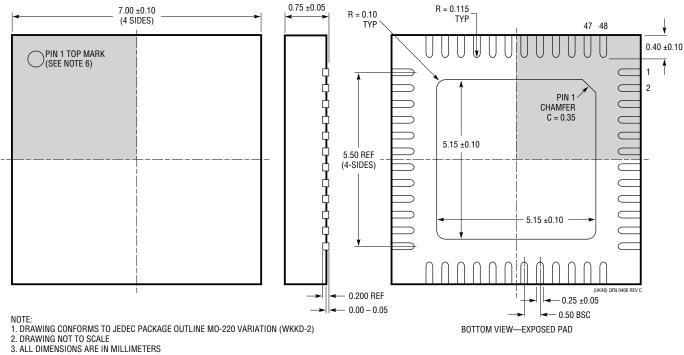

- 48-Lead (7mm × 7mm) QFN Package

### **APPLICATIONS**

- Communications

- Cellular Base Stations

- Software Defined Radios

- Medical Imaging

- **High Definition Video**

- Test and Measurement Instrumentation

## DESCRIPTION

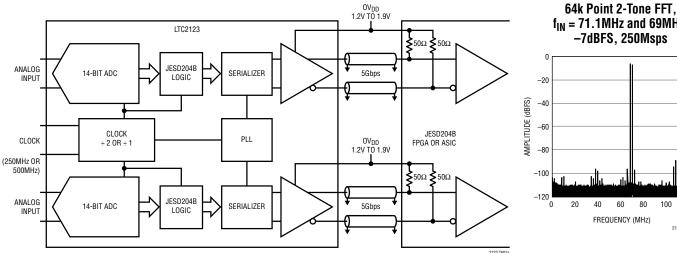

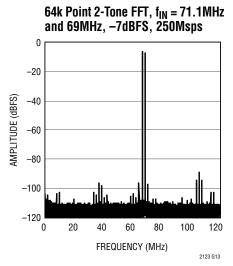

The LTC<sup>®</sup>2123 is a 2-channel simultaneous sampling 250Msps 14-bit A/D converter with serial JESD204B outputs. It is designed for digitizing high frequency, wide dynamic range signals. It is perfect for demanding communications applications with AC performance that includes 70dBFS SNR and 90dBFS spurious free dynamic range (SFDR). The 1.25GHz input bandwidth allows the ADC to under-sample high frequencies.

The 5Gbps JESD204B serial interface simplifies the PCB design by minimizing the number of data lines required.

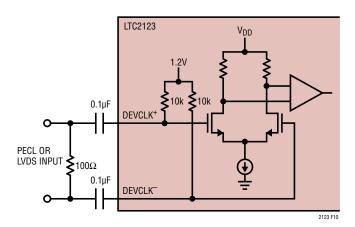

The DEVCLK+ and DEVCLK- inputs can be driven differentially with sine wave, PECL, or LVDS signals. An optional clock divide-by-two circuit or clock duty cycle stabilizer maintains high performance at full speed for a wide range of clock duty cycles.

Technology Corporation. All other trademarks are the property of their respective owners.

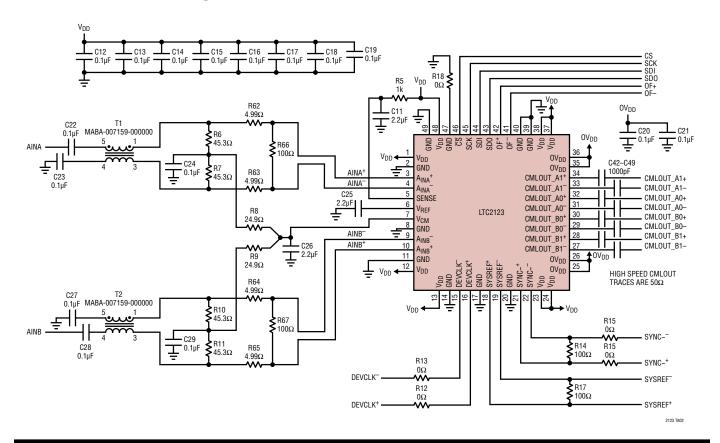

## TYPICAL APPLICATION

$f_{IN} = 71.1MHz$  and 69MHz, -7dBFS, 250Msps 60 80 100 120 FREQUENCY (MHz) 2123 TA01b

## **ABSOLUTE MAXIMUM RATINGS**

## (Notes 1, 2) Supply Voltages V<sub>DD</sub>, OV<sub>DD</sub>...... 0.3V to 2V Analog Input Voltage $A_{INA/B}^+$ , $A_{INA/B}^-$ .....-0.3V to $(V_{DD} + 0.2V)$ Digital Input Voltage DEVCLK+, DEVCLK-, SYSREF+, SYSREF-, $SYNC^{+}$ , $SYNC^{-}$ (Note 3)...... -0.3V to $(V_{DD} + 0.3V)$ <del>CS</del>, SDI, SCK (Note 4) ......–0.3V to 3.9V Digital Output Voltage ..... -0.3V to $(V_{DD} + 0.3V)$ **Operating Ambient Temperature Range** LTC2123C ......0°C to 70°C LTC2123I .....-40°C to 85°C Storage Temperature Range ......-65°C to 150°C

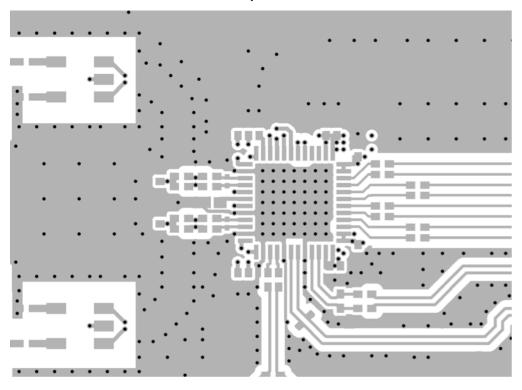

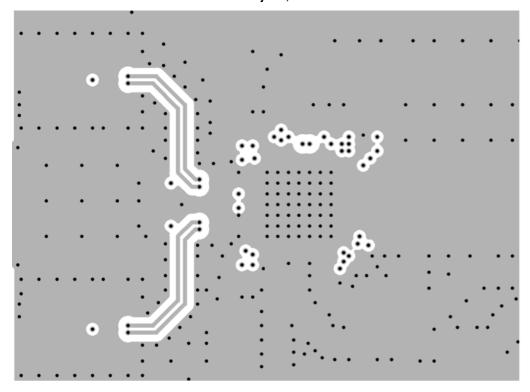

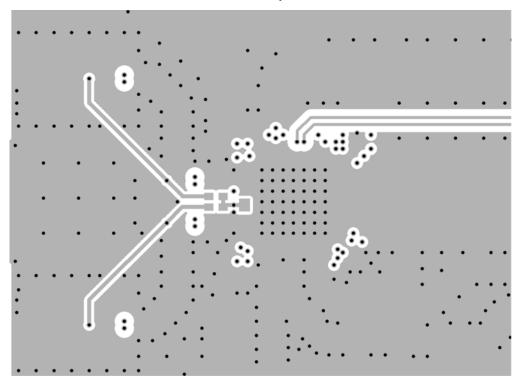

## PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL    | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |  |

|------------------|------------------|---------------|---------------------------------|-------------------|--|

| LTC2123CUK#PBF   | LTC2123CUK#TRPBF | LTC2123UK     | 48-Lead (7mm × 7mm) Plastic QFN | 0°C to 70°C       |  |

| LTC2123IUK#PBF   | LTC2123IUK#TRPBF | LTC2123UK     | 48-Lead (7mm × 7mm) Plastic QFN | -40°C to 85°C     |  |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on nonstandard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

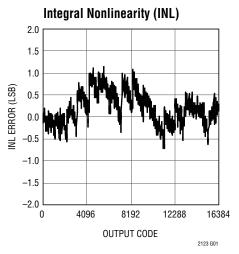

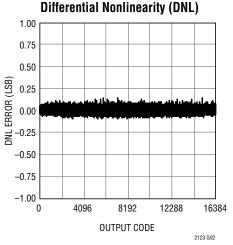

# **CONVERTER CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}$ C. (Note 5)

| PARAMETER                     | CONDITIONS                               |   | MIN  | TYP        | MAX | UNITS              |

|-------------------------------|------------------------------------------|---|------|------------|-----|--------------------|

| Resolution (No Missing Codes) |                                          | • | 14   |            |     | Bits               |

| Integral Linearity Error      | Differential Analog Input (Note 6)       | • | -5.5 | ±0.85      | 5.5 | LSB                |

| Differential Linearity Error  | Differential Analog Input                | • | -0.9 | ±0.25      | 0.9 | LSB                |

| Offset Error                  | (Note 7)                                 | • | -13  | ±5         | 13  | mV                 |

| Gain Error                    | Internal Reference<br>External Reference | • | -4.0 | ±1.5<br>±1 | 2.2 | %FS<br>%FS         |

| Offset Drift                  |                                          |   |      | ±20        |     | μV/°C              |

| Full-Scale Drift              | Internal Reference<br>External Reference |   |      | ±30<br>±10 |     | ppm/°C<br>ppm/°C   |

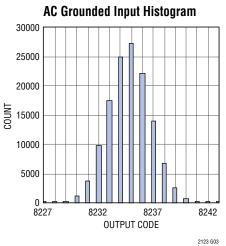

| Transition Noise              |                                          |   |      | 1.82       |     | LSB <sub>RMS</sub> |

# **RNALOG INPUT** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 5)

| SYMBOL              | PARAMETER                                                                         | CONDITIONS                                   |   | MIN                    | TYP      | MAX                    | UNITS             |

|---------------------|-----------------------------------------------------------------------------------|----------------------------------------------|---|------------------------|----------|------------------------|-------------------|

| V <sub>IN</sub>     | Analog Input Range (A <sub>IN</sub> <sup>+</sup> – A <sub>IN</sub> <sup>-</sup> ) | 1.7V < V <sub>DD</sub> < 1.9V                | • |                        | 1.5      |                        | V <sub>P-P</sub>  |

| V <sub>IN(CM)</sub> | Analog Input Common Mode $(A_{IN}^+ + A_{IN}^-)/2$                                | Differential Analog Input (Note 8)           | • | V <sub>CM</sub> – 20mV | $V_{CM}$ | V <sub>CM</sub> + 20mV | V                 |

| $V_{SENSE}$         | External Voltage Reference Applied to SENSE                                       | External Reference Mode                      | • | 1.2                    | 1.250    | 1.3                    | V                 |

| I <sub>IN1</sub>    | Analog Input Leakage Current                                                      | $0 < A_{IN}^+, A_{IN}^- < V_{DD}$ , No Clock | • | -1                     |          | 1                      | μA                |

| I <sub>IN2</sub>    | SENSE Input Leakage Current                                                       | 1.23V < SENSE < 1.27V                        | • | -1                     |          | 1                      | μA                |

| t <sub>AP</sub>     | Sample-and-Hold Acquisition Delay Time                                            |                                              |   |                        | 1        |                        | ns                |

| t <sub>JITTER</sub> | Sample-and-Hold Acquisition Delay Jitter                                          |                                              |   |                        | 0.15     |                        | ps <sub>RMS</sub> |

| CMRR                | Analog Input Common Mode Rejection Ratio                                          |                                              |   |                        | 75       |                        | dB                |

| BW-3dB              | Full-Power Bandwidth                                                              |                                              |   |                        | 1250     |                        | MHz               |

# **DYNAMIC ACCURACY** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 5)

| SYMBOL    | PARAMETER                                          | CONDITIONS                                 |   | MIN  | TYP                  | MAX | UNITS                |

|-----------|----------------------------------------------------|--------------------------------------------|---|------|----------------------|-----|----------------------|

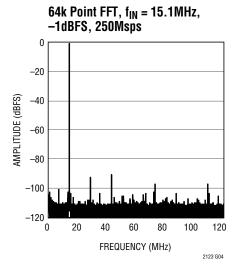

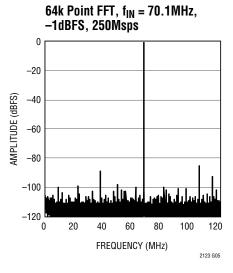

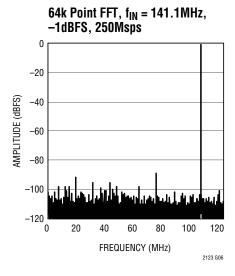

| SNR       | Signal-to-Noise Ratio                              | 15MHz Input<br>70MHz Input<br>140MHz Input | • | 67.1 | 70<br>69.7<br>69     |     | dBFS<br>dBFS<br>dBFS |

| SFDR      | Spurious Free Dynamic Range 2nd or 3rd<br>Harmonic | 15MHz Input<br>70MHz Input<br>140MHz Input | • | 71   | 90<br>85<br>80       |     | dBFS<br>dBFS<br>dBFS |

|           | Spurious Free Dynamic Range 4th Harmonic or Higher | 15MHz Input<br>70MHz Input<br>140MHz Input | • | 81   | 98<br>95<br>85       |     | dBFS<br>dBFS<br>dBFS |

| S/(N+D)   | Signal-to-Noise Plus Distortion Ratio              | 15MHz Input<br>70MHz Input<br>140MHz Input | • | 66.3 | 69.9<br>69.4<br>68.8 |     | dBFS<br>dBFS<br>dBFS |

| Crosstalk | Crosstalk Between Channels                         | Up to 250MHz Input                         |   |      | -90                  |     | dB                   |

# **INTERNAL REFERENCE CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 5)

| PARAMETER                                 | CONDITIONS                      | MIN                               | TYP                        | MAX                               | UNITS  |

|-------------------------------------------|---------------------------------|-----------------------------------|----------------------------|-----------------------------------|--------|

| V <sub>CM</sub> Output Voltage            | I <sub>OUT</sub> = 0            | 0.435 •<br>V <sub>DD</sub> – 18mV | 0.435 •<br>V <sub>DD</sub> | 0.435 •<br>V <sub>DD</sub> + 18mV | V      |

| V <sub>CM</sub> Output Temperature Drift  |                                 |                                   | ±37                        |                                   | ppm/°C |

| V <sub>CM</sub> Output Resistance         | −1mA < I <sub>OUT</sub> < 1mA   |                                   | 4                          |                                   | Ω      |

| V <sub>REF</sub> Output Voltage           | I <sub>OUT</sub> = 0            | 1.225                             | 1.250                      | 1.275                             | V      |

| V <sub>REF</sub> Output Temperature Drift |                                 |                                   | ±30                        |                                   | ppm/°C |

| V <sub>REF</sub> Output Resistance        | -400μA < I <sub>OUT</sub> < 1mA |                                   | 7                          |                                   | Ω      |

| V <sub>REF</sub> Line Regulation          | 1.7V < V <sub>DD</sub> < 1.9V   |                                   | 0.6                        |                                   | mV/V   |

# **POWER REQUIREMENTS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 5)

| SYMBOL             | PARAMETER                      | CONDITIONS                                                                            |   | MIN        | TYP | MAX        | UNITS |

|--------------------|--------------------------------|---------------------------------------------------------------------------------------|---|------------|-----|------------|-------|

| $V_{DD}$           | Analog Supply Voltage          | (Note 9)                                                                              | • | 1.7        | 1.8 | 1.9        | V     |

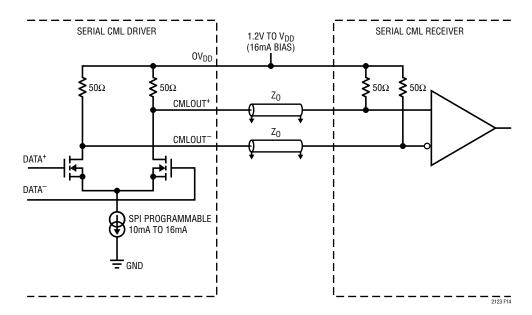

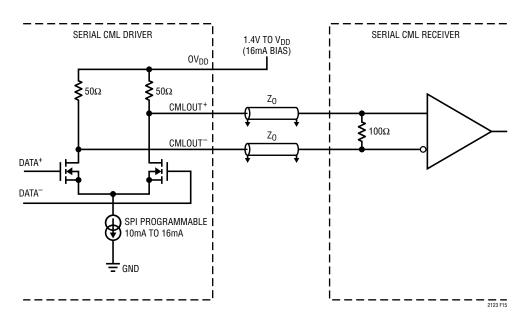

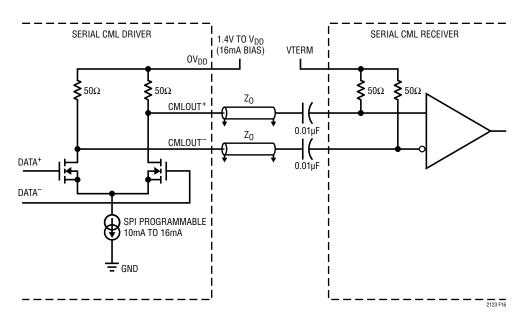

| OV <sub>DD</sub>   | Output Supply Voltage          | CML Current = 16mA, Directly Terminated (Note 8)<br>CML Current = 16mA, AC Terminated | • | 1.2<br>1.4 |     | 1.9<br>1.9 | V     |

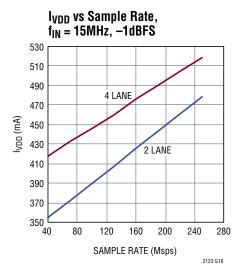

| I <sub>VDD</sub>   | Analog Supply Current          |                                                                                       | • |            | 480 | 520        | mA    |

| I <sub>OVDD</sub>  | Output Supply Current Per Lane | CML Current = 12mA                                                                    | • | 11         | 12  | 13.8       | mA    |

| P <sub>DISS</sub>  | Power Dissipation              | $V_{DD} = 1.8V$ , Excluding $OV_{DD}$ Power                                           | • |            | 864 | 936        | mW    |

| P <sub>SLEEP</sub> | Sleep Mode Power               |                                                                                       |   |            | 2   |            | mW    |

| P <sub>NAP</sub>   | Nap Mode Power                 |                                                                                       |   |            | 468 |            | mW    |

# **DIGITAL INPUTS AND OUTPUTS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25 \,^{\circ}\text{C}$ . (Note 5)

| SYMBOL           | PARAMETER                                 | CONDITIONS                                |   | MIN   | TYP  | MAX   | UNITS |

|------------------|-------------------------------------------|-------------------------------------------|---|-------|------|-------|-------|

| CLOCK INF        | PUTS (DEVCLK+, DEVCLK-)                   | ·                                         |   |       |      |       |       |

| $V_{ID}$         | Differential Input Voltage                | (Note 8)                                  | • | 0.2   |      |       | V     |

| V <sub>ICM</sub> | Common Mode Input Voltage                 | Internally Set<br>Externally Set (Note 8) | • | 1.1   | 1.2  | 1.5   | V     |

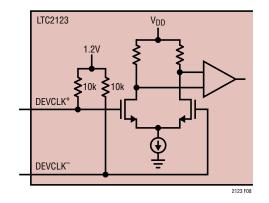

| R <sub>IN</sub>  | Input Resistance                          | (See Figure 2)                            |   |       | 10   |       | kΩ    |

| C <sub>IN</sub>  | Input Capacitance                         |                                           |   |       | 2    |       | pF    |

| DIFFEREN         | TIAL DIGITAL INPUTS (SYNC~+, SYNC~-, SY   | /SREF+, SYSREF <sup>-</sup> )             |   |       |      |       |       |

| $V_{ID}$         | Differential Input Voltage                | (Note 8)                                  | • | 0.2   |      |       | V     |

| V <sub>ICM</sub> | Common Mode Input Voltage                 | Internally Set<br>Externally Set (Note 8) | • | 1.1   | 1.2  | 1.5   | V     |

| R <sub>IN</sub>  | Input Resistance                          |                                           |   |       | 6.7  |       | kΩ    |

| C <sub>IN</sub>  | Input Capacitance                         |                                           |   |       | 2    |       | pF    |

| DIGITAL IN       | IPUTS ( <del>cs</del> , sdi, sck)         |                                           |   |       |      |       |       |

| $V_{IH}$         | High Level Input Voltage                  | V <sub>DD</sub> = 1.8V                    | • | 1.3   |      |       | V     |

| V <sub>IL</sub>  | Low Level Input Voltage                   | V <sub>DD</sub> = 1.8V                    | • |       |      | 0.6   | V     |

| I <sub>IN</sub>  | Input Current                             | V <sub>IN</sub> = 0V to 3.6V              | • | -10   |      | 10    | μА    |

| C <sub>IN</sub>  | Input Capacitance                         | (Note 8)                                  |   |       | 3    |       | pF    |

| SDO OUTP         | UT (Open-Drain Output. Requires 2k Pull-U | p Resistor if SDO Is Used)                |   |       |      |       |       |

| R <sub>OL</sub>  | Logic Low Output Resistance to GND        | V <sub>DD</sub> = 1.8V, SDO = 0V          |   |       | 200  |       | Ω     |

| I <sub>OH</sub>  | Logic High Output Leakage Current         | SD0 = 0V to 3.6V                          | • | -10   |      | 10    | μА    |

| C <sub>OUT</sub> | Output Capacitance                        | (Note 8)                                  |   |       | 4    |       | pF    |

| LVDS OUT         | PUTS (0F+, 0F <sup>-</sup> )              |                                           |   |       |      |       | ·     |

| $V_{OD}$         | Differential Output Voltage               | 100Ω Differential Load                    | • | 247   | 350  | 454   | mV    |

| V <sub>OS</sub>  | Common Mode Output Voltage                |                                           | • | 1.125 | 1.25 | 1.375 | V     |

# **DIGITAL INPUTS AND OUTPUTS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 5)

| SYMBOL            | PARAMETER                       | CONDITIONS                                                                                                  |   | MIN | TYP                                                                                                               | MAX    | UNITS                            |

|-------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------|---|-----|-------------------------------------------------------------------------------------------------------------------|--------|----------------------------------|

| CML Outputs       |                                 |                                                                                                             |   |     |                                                                                                                   |        |                                  |

| V <sub>DIFF</sub> | CML Differential Output Voltage | Output Current Set to 10mA Output Current Set to 12mA Output Current Set to 14mA Output Current Set to 16mA |   |     | 500<br>600<br>700<br>800                                                                                          |        | mVppd<br>mVppd<br>mVppd<br>mVppd |

| V <sub>OH</sub>   | Output High Level               | Directly-Coupled $50\Omega$ to $0V_{DD}$ Directly-Coupled $100\Omega$ Differential AC-Coupled               |   |     | OV <sub>DD</sub><br>OV <sub>DD</sub> -¼V <sub>DIF</sub><br>OV <sub>DD</sub> -¼V <sub>DIF</sub>                    |        | V<br>V<br>V                      |

| V <sub>OL</sub>   | Output Low Level                | Directly-Coupled $50\Omega$ to $0V_{DD}$ Directly-Coupled $100\Omega$ Differential AC-Coupled               |   | (   | OV <sub>DD</sub> -½V <sub>DIF</sub><br>OV <sub>DD</sub> -¾V <sub>DIF</sub><br>OV <sub>DD</sub> -¾V <sub>DIF</sub> | ·<br>F | V<br>V<br>V                      |

| V <sub>OCM</sub>  | Output Common Mode Level        | Directly-Coupled $50\Omega$ to $0V_{DD}$ Directly-Coupled $100\Omega$ Differential AC-Coupled               |   | (   | OV <sub>DD</sub> -¼V <sub>DIF</sub><br>OV <sub>DD</sub> -½V <sub>DIF</sub><br>OV <sub>DD</sub> -½V <sub>DIF</sub> | ·<br>F | V<br>V<br>V                      |

| R <sub>OUT</sub>  | Output Resistance               | Single-Ended<br>Differential                                                                                | • | 80  | 50<br>100                                                                                                         | 120    | Ω<br>Ω                           |

# **TIMING CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25 \, ^{\circ}\text{C}$ . (Note 5)

| SYMBOL                            | PARAMETER                         | CONDITIONS                                                                                 |   | MIN        | TYP    | MAX          | UNITS    |

|-----------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------|---|------------|--------|--------------|----------|

| f <sub>S</sub> , 1/t <sub>S</sub> | Sampling Frequency                | (Note 9)                                                                                   | • | 50         |        | 250          | MHz      |

| t <sub>L</sub>                    | 1× CLK Low Time (Note 8)          | Duty Cycle Stabilizer Off<br>Duty Cycle Stabilizer On                                      | • | 1.9<br>1.5 | 2 2    | 10<br>10     | ns<br>ns |

| t <sub>H</sub>                    | 1× CLK High Time (Note 8)         | Duty Cycle Stabilizer Off<br>Duty Cycle Stabilizer On                                      | • | 1.9<br>1.5 | 2<br>2 | 10<br>10     | ns<br>ns |

| t <sub>DCK</sub>                  | DEVCLK Period                     | 2X_CLK SPI Register = 0<br>2X_CLK SPI Register = 1                                         | • | 4<br>2     |        | 20<br>10     | ns<br>ns |

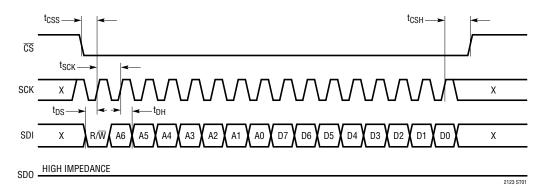

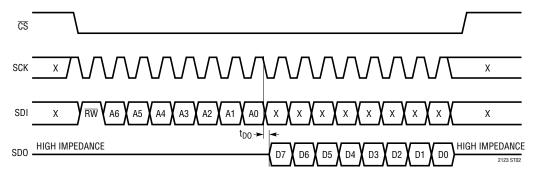

| SPI Port                          | Timing (Note 8)                   |                                                                                            |   |            |        |              |          |

| t <sub>SCK</sub>                  | SCK Period                        | Write Mode<br>Readback Mode C <sub>SDO</sub> = 20pF, R <sub>PULLUP</sub> = 2k              | • | 40<br>250  |        |              | ns<br>ns |

| t <sub>CSS</sub>                  | CS to SCK Set-Up Time             |                                                                                            | • | 5          |        |              | ns       |

| t <sub>CSH</sub>                  | SCK to CS Hold Time               |                                                                                            | • | 5          |        |              | ns       |

| $t_{DS}$                          | SDI Set-Up Time                   |                                                                                            | • | 5          |        |              | ns       |

| t <sub>DH</sub>                   | SDI Hold Time                     |                                                                                            | • | 5          |        |              | ns       |

| t <sub>DO</sub>                   | SCK Falling to SDO Valid          | Readback Mode C <sub>SDO</sub> = 20pF, R <sub>PULLUP</sub> = 2K                            | • |            |        | 125          | ns       |

| JESD204                           | B Timing (Note 8)                 |                                                                                            |   |            |        |              |          |

| t <sub>BIT, UI</sub>              | High Speed Serial Bit Period      | 2 Lane Mode (1 Lane Per ADC)<br>4 Lane Mode (2 Lanes Per ADC)                              | • | 200<br>400 |        | 1000<br>1000 | ps<br>ps |

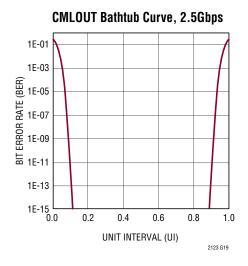

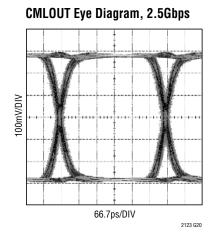

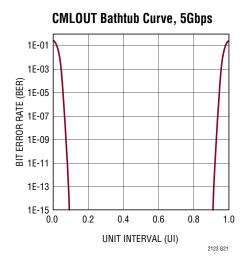

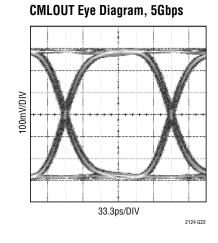

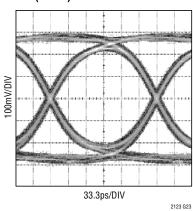

| t <sub>JIT</sub>                  | Total Jitter of CML Outputs (P-P) | > 3.125Gbps Per Lane (BER = 1E-15, Note 8)<br>< = 3.125Gbps Per Lane (BER = 1E-12, Note 8) | • |            |        | 0.3<br>0.35  | UI<br>UI |

# **TIMING CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 5)

| SYMBOL              | PARAMETER                                               | CONDITIONS     |   | MIN  | TYP MAX            | UNITS          |

|---------------------|---------------------------------------------------------|----------------|---|------|--------------------|----------------|

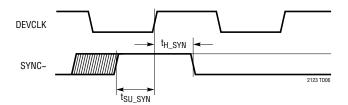

| t <sub>SU_SYN</sub> | SYNC~ to DEVCLK Set-Up Time                             | (Note 8)       | • | 0.6  |                    | ns             |

| t <sub>H_SYN</sub>  | DEVCLK to SYNC~ Hold Time                               | (Note 8)       | • | 0.6  |                    | ns             |

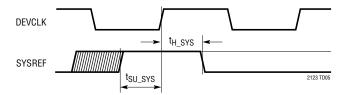

| $t_{SU\_SYS}$       | SYSREF to DEVCLK Set-Up Time                            | (Note 8)       | • | 0.2  | $(t_{DCK} - 0.32)$ | ns             |

| t <sub>H_SYS</sub>  | DEVCLK to SYSREF Hold Time                              | (Note 8)       | • | 0.32 |                    | ns             |

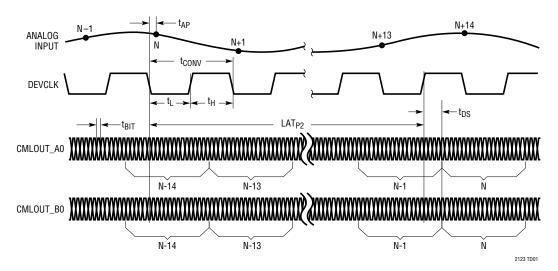

| LAT <sub>P2</sub>   | Pipeline Latency, 2-Lane Mode                           | (Note 10)      | • | 13.5 | 13.5               | ts             |

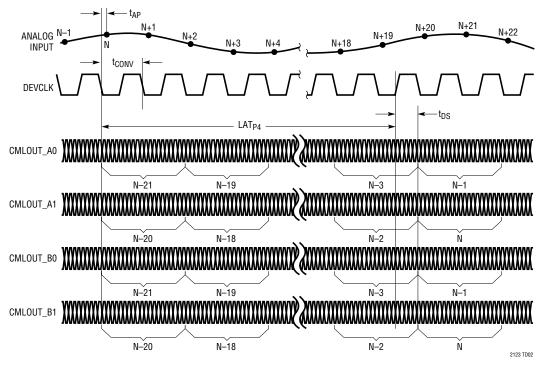

| LAT <sub>P4</sub>   | Pipeline Latency, 4-Lane Mode                           | (Note 10)      | • | 19.5 | 19.5               | ts             |

| t <sub>DS</sub>     | Delay from DEVCLK to Serial Data Out                    | (Note 8)       | • |      | 0.6                | ts             |

| LAT <sub>SC2</sub>  | Latency from SYNC~ Assertion to COMMA Out, 2-Lane Mode  | (Note 10)      | • | 10   | 10                 | t <sub>S</sub> |

| LAT <sub>SC4</sub>  | Latency from SYNC~ Assertion to COMMA Out, 4-Lane Mode  | (Note 10)      | • | 20   | 20                 | t <sub>S</sub> |

| LAT <sub>SL2</sub>  | Latency from SYNC~ De-assertion to LAS Out, 2-Lane Mode | (Notes 10, 11) | • | 6    | 6                  | t <sub>S</sub> |

| LAT <sub>SL4</sub>  | Latency from SYNC~ De-assertion to LAS Out, 4-Lane Mode | (Notes 10, 11) | • | 12   | 12                 | t <sub>S</sub> |

| LAT <sub>OF</sub>   | Overflow Latency                                        | (Note 10)      | • | 6    | 6                  | ts             |

| t <sub>D_OF1X</sub> | Analog Delay of OF with 1X_CLK                          | (Note 8)       | • | 1.4  | 1.7 2.0            | ns             |

| t <sub>D_OF2X</sub> | Analog Delay of OF with 2X_CLK                          | (Note 8)       | • | 1.6  | 1.9 2.2            | ns             |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** All voltage values are with respect to GND (unless otherwise noted). **Note 3:** When these pin voltages are taken below GND or above  $V_{DD}$ , they will be clamped by internal diodes. This product can handle input currents of greater than 100mA below GND or above  $V_{DD}$  without latchup.

**Note 4:** When these pin voltages are taken below GND they will be clamped by internal diodes. When these pin voltages are taken above  $V_{DD}$  they will not be clamped by internal diodes. This product can handle input currents of greater than 100mA below GND without latch-up.

**Note 5:**  $V_{DD} = 1.8V$ ,  $f_{SAMPLE} = 250MHz$ , differential DEVCLK+/DEVCLK- =  $2V_{P-P}$  sine wave, input range =  $1.5V_{P-P}$  with differential drive, unless otherwise noted.

**Note 6:** Integral nonlinearity is defined as the deviation of a code from a best fit straight line to the transfer curve. The deviation is measured from the center of the quantization band.

**Note 7:** Offset error is the offset voltage measured from -0.5LSB when the output code flickers between 01 1111 1111 1111 and 10 0000 0000 0000.

Note 8: Guaranteed by design, not subject to test.

Note 9: Recommended operating conditions.

**Note 10:** When the "2X\_CLK" SPI register bit is set, the DEVCLK frequency is 2X the sampling frequency. When the "2X\_CLK" bit is not set, the DEVCLK frequency is equal to the sampling frequency. Latency is measured in units of sampling periods  $(t_S)$ , where  $t_S$  is the inverse of the sampling frequency.

**Note 11:** When in subclass 0, the Lane Alignment Sequence (LAS) latency measurement begins at the start of the frame following the detection of SYNC~ de-assertion. When in subclasses 1 or 2 this LAS latency measurement begins at the start of the first multiframe following the detection of SYNC~ de-assertion.

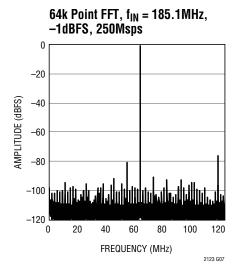

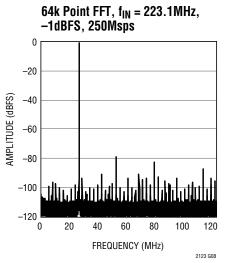

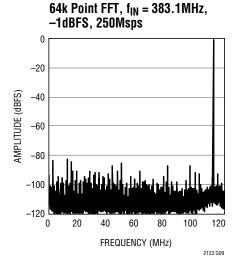

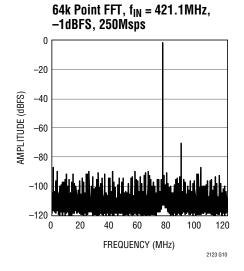

## TYPICAL PERFORMANCE CHARACTERISTICS

## TYPICAL PERFORMANCE CHARACTERISTICS

# TYPICAL PERFORMANCE CHARACTERISTICS

## PIN FUNCTIONS

**V<sub>DD</sub>** (**Pins 1, 12, 13, 23, 24, 37, 38, 48):** 1.8V Power Supply. Bypass to ground with 0.1μF ceramic capacitors. Adjacent pins can share bypass capacitor.

**GND (Pins 2, 8, 11, 14, 17, 20, 39, 40, 47, Exposed Pad Pin 49):** Device Power Ground. The exposed pad must be soldered to the PCB ground.

A<sub>INA</sub>+/A<sub>INA</sub>- (Pins 3, 4): Analog Input Pair for Channel A.

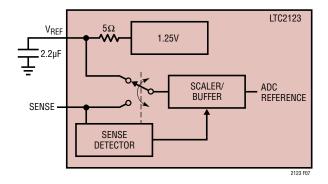

**SENSE (Pin 5):** Reference Programming Pin. Connecting SENSE to  $V_{DD}$  selects the internal reference and a  $\pm 0.75V$  input range. An external reference between 1.2V and 1.3V applied to SENSE selects an input range of  $\pm 0.6 \cdot V_{SENSE}$ .

**V**<sub>REF</sub> (**Pin 6**): Reference Voltage Output. Bypass to ground with a 2.2µF ceramic capacitor. Nominally 1.25V.

$V_{CM}$  (Pin 7): Common Mode Bias Output. Nominally equal to 0.435 •  $V_{DD}$ .  $V_{CM}$  should be used to bias the common mode of the analog inputs. Bypass to ground with a 0.1 $\mu$ F ceramic capacitor.

A<sub>INB</sub><sup>-</sup>/A<sub>INB</sub><sup>+</sup> (Pins 9, 10): Analog Input Pair for Channel B.

**DEVCLK**<sup>-</sup>/**DEVCLK**<sup>+</sup> (**Pins 15, 16**): Device Clock Input Pair. The sample clock is derived from this clock signal. In divide-by-one mode, the analog signal is sampled on the falling edge of DEVCLK (DEVCLK = DEVCLK<sup>+</sup> – DEVCLK<sup>-</sup>).

DEVCLK may optionally be divided by two. In subclass 1 a low to high transition of the SYSREF signal will initialize the divide-by-two circuit on the rising edge of DEVCLK. In Subclass 2 a low to high transition of the SYNC~ signal will initialize the divide-by-two circuit on the rising edge of DEVCLK.

**SYSREF**<sup>+</sup>/**SYSREF**<sup>-</sup> (**Pins 18, 19**): A JESD204B Subclass 1 Input Signal Pair. A low to high transition of SYSREF is sampled on the rising edge of DEVCLK to reset the internal dividers and set up deterministic latency (SYSREF = SYSREF<sup>+</sup> – SYSREF<sup>-</sup>).

**SYNC~**+/**SYNC~** (**Pins 21, 22**): A JESD204B Synchronization Input Signal Pair. Used to establish initial Code Group synchronization for all three subclasses. A low level of the SYNC~ signal causes the LTC2123 to output K28.5 commas (SYNC~ = SYNC~<sup>+</sup> – SYNC~<sup>-</sup>).

In subclass 2 a low to high transition of SYNC~ is sampled on the rising edge of DEVCLK to reset the internal dividers and set up deterministic latency.

$OV_{DD}$  (Pins 25, 26, 35, 36): 1.2V to 1.9V Output Driver Supply. Bypass each pair to ground with  $0.1\mu F$  ceramic capacitors.

**CMLOUT\_B1**<sup>-</sup>/**CMLOUT\_B1**<sup>+</sup> (**Pins 27, 28**): Current Mode Logic Output Pair for Channel B Lane 2. Must be terminated with a  $50\Omega$  resistor to  $0V_{DD}$ , a differential  $100\Omega$  resistor to the complementary output, or AC coupled to another termination voltage.

**CMLOUT\_B0<sup>-</sup>/CMLOUT\_B0<sup>+</sup> (Pins 29, 30):** Current Mode Logic Output Pair for Channel B Lane 1. Must be terminated with a  $50\Omega$  resistor to  $OV_{DD}$ , a differential  $100\Omega$  resistor to the complementary output, or AC coupled to another termination voltage.

**CMLOUT\_A0<sup>-</sup>/CMLOUT\_A0<sup>+</sup> (Pins 31, 32):** Current Mode Logic Output Pair for Channel A Lane 1. Must be terminated with a  $50\Omega$  resistor to  $0V_{DD}$ , a differential  $100\Omega$  resistor to the complementary output, or AC coupled to another termination voltage.

**CMLOUT\_A1**<sup>-</sup>/**CMLOUT\_A1**<sup>+</sup> (**Pins 33, 34**): Current Mode Logic Output Pair for Channel A Lane 2. Must be terminated with a  $50\Omega$  resistor to  $0V_{DD}$ , a differential  $100\Omega$  resistor to the complementary output, or AC coupled to another termination voltage.

**OF**<sup>-</sup>/**OF**<sup>+</sup> **(Pins 41, 42):** Over/Underflow LVDS Digital Output. OF is high when an overflow or underflow has occurred. The overflows for channel A and channel B are multiplexed together and transmitted at twice the sample frequency (OF = OF<sup>+</sup> – OF<sup>-</sup>).

**SDO (Pin 43):** Serial Interface Data Output. SDO is the optional serial interface data output. Data on SDO is read back from the mode control registers and can be latched on the falling edge of SCK. SDO is an open-drain N-channel MOSFET output that requires an external 2k pull-up resistor from 1.8V to 3.3V. If readback from the mode control registers is not needed, the pull-up resistor is not necessary and SDO can be left unconnected.

LINEAR TECHNOLOGY

## PIN FUNCTIONS

**SDI (Pin 44):** Serial Interface Data Input. SDI is the serial interface data input. Data on SDI is clocked into the mode control registers on the rising edge of SCK. SDI can be driven with 1.8V to 3.3V logic.

**SCK (Pin 45):** Serial Interface Clock Input. SCK is the serial interface clock input. SCK can be driven with 1.8V to 3.3V logic.

$\overline{\text{CS}}$  (Pin 46): Serial Interface Chip Select Input. When  $\overline{\text{CS}}$  is low, SCK is enabled for shifting data on SDI into the mode control registers.  $\overline{\text{CS}}$  can be driven with 1.8V to 3.3V logic.

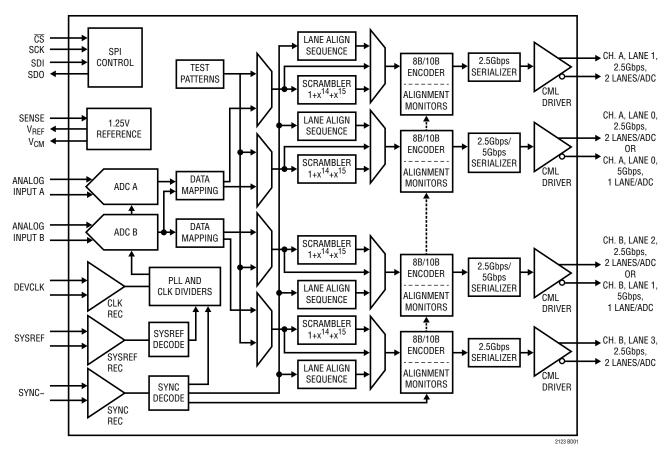

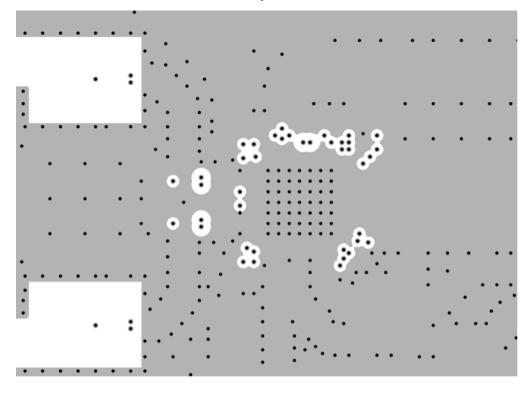

## **BLOCK DIAGRAM**

Figure 1. Functional Block Diagram

## TIMING DIAGRAM

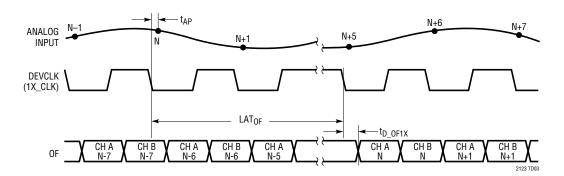

Two-Lane Timing (One Lane Per ADC),  $f_{DEVCLK} = f_{S}$

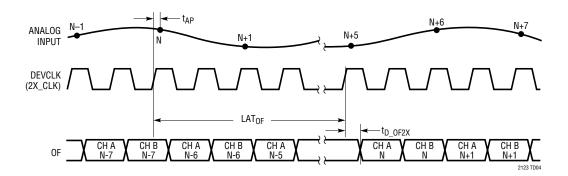

Four-Lane Timing (Two Lane Per ADC),  $f_{DEVCLK} = f_{S}$

NOTE: DEVCLK = DEVCLK+ - DEVCLK-

# **TIMING DIAGRAM**

Over Flow (OF) Timing, 1X\_CLK Mode

Over-Flow (OF) Timing 2X\_CLK Mode

# **TIMING DIAGRAM**

## **SYSREF Timing (Subclass 1)**

SYNC~ Rising Edge Clock Reset Timing (Subclass 2)

$NOTE: DEVCLK = DEVCLK^+ - DEVCLK^-, OF = OF^+ - OF^-, SYSREF = SYSREF^+ - SYSREF^-, SYNC^- = SYNC^+ - SYNC^- = SYNC^- + SYNC^- = SYNC^- + SYNC^- + SYNC^- = SYNC^- + SYNC^- + SYNC^- + SYNC^- = SYNC^- + SYNC^-$

# **SPI TIMING**

### **SPI Timing, Write Mode**

**SPI Timing, Read Mode**

### **DEFINITIONS**

#### ADC PERFORMANCE TERMS

#### **Aperture Delay Time**

The time it takes for the input signal to be held by the sample-and-hold circuit after the rising edge of DEVCLK<sup>+</sup> is equal to the falling edge of DEVCLK<sup>-</sup> on the sampling edge of DEVCLK.

#### **Aperture Delay Jitter**

The variation in the aperture delay time from conversion to conversion. This random variation will result in noise when sampling an AC input. The signal to noise ratio due to the jitter alone will be:

$SNR_{JITTER} = -20log (2\pi \bullet f_{IN} \bullet t_{JITTER})$

#### Crosstalk

Crosstalk is the coupling from one channel (being driven by a full-scale signal) onto the other channel (being driven by a -1dBFS signal).

#### Intermodulation Distortion

If the ADC input signal consists of more than one spectral component, the ADC transfer function nonlinearity can produce intermodulation distortion (IMD) in addition to THD. IMD is the change in one sinusoidal input caused by the presence of another sinusoidal input at a different frequency.

If two pure sine waves of frequencies fa and fb are applied to the ADC input, nonlinearities in the ADC transfer function can create distortion products at the sum and difference frequencies of mfa  $\pm$  nfb, where m and n = 0, 1, 2, 3, etc. For example, the 3rd order IMD terms include (2fa + fb), (fa + 2fb), (2fa – fb) and (fa – 2fb). The 3rd order IMD is defined as the ratio of the RMS value of either input tone to the RMS value of the largest 3rd order IMD product.

## Signal-to-Noise Plus Distortion Ratio

The signal-to-noise plus distortion ratio [S/(N+D)] is the ratio between the RMS amplitude of the fundamental input frequency and the RMS amplitude of all other frequency components at the ADC output. The output is band limited to frequencies above DC to below half the sampling frequency.

#### Signal-to-Noise Ratio

The signal-to-noise (SNR) is the ratio between the RMS amplitude of the fundamental input frequency and the RMS amplitude of all other frequency components, except the first five harmonics.

## Spurious Free Dynamic Range (SFDR)

The ratio of the RMS input signal amplitude to the RMS value of the peak spurious spectral component expressed in dBc. SFDR may also be calculated relative to full scale and expressed in dBFS.

## **DEFINITIONS**

#### SERIAL INTERFACE TERMS

#### 8B/10B Encoding

A data encoding standard that encodes an 8-bit octet into a 10-bit code-group (IEEE Std 802.3-2002 part 3, clause 36.2). The resulting code-group is ideal for serial transmission for two fundamental reasons: 1) The receiver does not require a high speed clock to capture the data because the code-groups are run-length limited to ensure a sufficient number of transitions for PLL-based clock recovery 2) AC coupling is permitted because the code-groups are DC balanced (see Running Disparity).

A table of the 256 possible input octets with the resulting 10-bit code-groups is documented in IEEE Std 802.3-2002 part 3 Table 36-1. A name associated with each of the 256 data code-groups is formatted "Dx.y", with x ranging from 0 to 31 and y ranging from 0 to 7. Additionally, Table 36-2 of the standard defines a set of 12 special code-groups used as non-data characters (such as commas) with the naming format of "Kx.y".

### **Current Mode Logic (CML)**

A circuit technique used to implement differential high speed logic. CML employs differential pairs (usually n-type) to steer current into resistive loads. It is possible to implement any logic function using CML. The output swing and offset is dependent on the bias current, the load resistance, and termination resistance.

This product family uses CML drivers to transmit high speed serial data to the outside world. The output driver bias current is programmable from 10mA to 16mA, generating a signal swing of approximately 250mV<sub>P-P</sub> (500mVppd) to  $400mV_{P-P}$  (800mVppd) across the combined internal and external termination resistance of  $25\Omega$  (50 $\Omega$  source//50 $\Omega$  termination) on each output (mVppd stands for  $mV_{P-P}$  differential).

#### Code-Group

The 10-bit output from an 8B/10B encoder or the 10-bit input to the 8B/10B decoder.

#### Comma

A special 8B/10B code-group containing the binary sequence "0011111" or "1100000". Commas are used for frame alignment and synchronization because a comma sequence cannot be generated by any combination of normal code-groups (unless a bit error occurs). There are three special code-groups that contain a comma, K28.1, K28.5, and K28.7.

For brevity, each of these three special code-groups are often called a comma, but in the strictest sense it is the first 7 bits of these code-groups that are designated a comma.

#### **DC Balanced Signal**

A specially conditioned signal that may be AC coupled with minimal degradation to the signal. DC balance is achieved when the average number of 1's and 0's are equal, eliminating the undesirable effects of DC wander on the receive side of the coupling capacitor. When 8B/10B coding is used, DC balance is achieved by following disparity rules (see Running Disparity).

#### De-Scrambler

A logic block that restores scrambled data to its prescrambled state. A self aligning de-scrambler is based on the same pseudo random bit sequence as the scrambler, so it requires no alignment signals. In this product family the scrambler is based on the 1+x<sup>14</sup>+x<sup>15</sup> polynomial, and the self aligning process results in an initial loss of 15 bits, or one ADC sample.

#### **Deterministic Latency**

A predictable and repeatable delay from the input to the output of the system. JESD204B subclasses 1 and 2 employ technologies that support a predictable and repeatable pipeline delay through the system.

#### Frame

The LTC2123 frame consists of two complete code-groups per lane, and constitutes one complete ADC sample per lane.

### **DEFINITIONS**

### Frame Alignment Monitoring (FAM)

After initial frame synchronization has been established, frame alignment monitoring enables the receiver to verify that code-group alignment is maintained without the loss of data. This is done by substituting a K28.7 comma for the last code-group of the frame when certain conditions are met. The receiver uses this comma as a position marker within the frame for alignment verification. After decoding the data, the receiver replaces the K28.7 comma with the original data.

#### **Initial Frame Synchronization**

The process of communicating frame boundary information to the receiver for alignment purposes. The receiver asserts the SYNC~ signal, causing the ADC to transmit K28.5 commas to the receiver. The receiver de-asserts the SYNC~ signal, and the ADC ceases transmission of commas according to the rules of the particular sub-class and mode of operation. The point of termination of commas in the data stream marks the frame boundary.

### Lane Alignment Monitoring (LAM)

In JESD204B, lane alignment is attained and monitored through the use of the 8B/10B K28.3 special characters. These characters are conditionally embedded in the data stream at the end of the multiframe. The receiver uses this character as a position marker within the multiframe for lane alignment verification. After decoding the data, the receiver replaces the K28.3 character with the original data.

## **Local Multiframe Clock (LMFC)**

An internal clock within each device of a JESD204B system that marks the multiframe boundary.

#### Multiframe

A group of frames intended to be of long duration compared to lane mismatches in multiple lane systems. In JESD204B the maximum multiframe length is 32 frames.

There is no external multiframe clock in a JESD204B system, so the signal marking the multiframe boundaries is referred to as the local multiframe clock (LMFC).

#### Octet

The 8-bit input to an 8B/10B encoder, or the 8-bit output from an 8B/10B decoder.

#### **Run-Length Limited (RLL)**

Data that has been encoded for the purpose of limiting the number of consecutive 1's or 0's in a data stream.

This process guarantees that there will be an adequate number of transitions in the serial data for the receiver to lock onto with a phase-locked loop and recover the high speed clock.

#### **Running Disparity**

In order to maintain DC balance most 8B/10B code-groups have two output possibilities for each input octet. The running disparity is calculated to determine which of the two code-groups should be transmitted to maintain DC balance.

The disparity of a code-group is analyzed in two segments called sub-blocks. Sub-block1 consists of the first six bits of a code-group and sub-block2 consists of the last four bits of a code-group. When a sub-block is more heavily weighted with 1's the running disparity is positive, and when it is more heavily weighted with 0's the running disparity is negative. When the number of 1's and 0's are equal in a sub-block, the running disparity remains unchanged.

The polarity of the current running disparity determines which code-group should be transmitted to maintain DC balance. For a complete description of disparity rules, refer to IEEE Std 802.3-2002 part 3, Clause 36.2.4.4.

#### **Pseudo Random Bit Sequence (PRBS)**

A data sequence having a random nature over a finite interval. The most commonly used PRBS test patterns may be described by a polynomial in the form of  $1+x^m+x^n$  and have a random nature for the length of up to 2n-1 bits, where n indicates the order of the PRBS polynomial and m plays a role in maximizing the length of the random sequence.

#### Scrambler

A logic block that applies a pseudo random bit sequence to the input octets to minimize the tonal content of the high speed serial bit stream.

#### **CONVERTER OPERATION**

The LTC2123 is a two-channel, 14-bit 250Msps A/D converter with JESD204B high speed serial outputs. The analog inputs must be driven differentially. The DEVCLK inputs should be driven differentially for optimal performance. The high speed serial interface is capable of data rates of up to 5Gbps per lane. The overflow/underflow indicators are available as part of the high speed serial data, and optionally as low-latency double data rate LVDS outputs. A SPI port provides programmability of multiple user options.

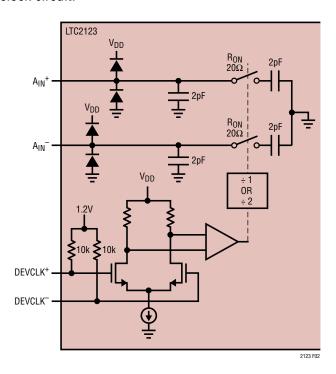

#### ANALOG INPUT

The analog inputs are differential CMOS sample-and hold circuits (Figure 2). The inputs must be driven differentially around a common mode voltage set by the  $V_{CM}$  output pin, which is nominally 0.8V. For the 1.5V input range, the inputs should swing from  $V_{CM}-0.375V$  to  $V_{CM}+0.375V$ . There should be 180° phase difference between the inputs. The two channels are simultaneously sampled by a shared clock circuit.

Figure 2. Equivalent Input Circuit for a Single Channel

#### **INPUT DRIVE CIRCUITS**

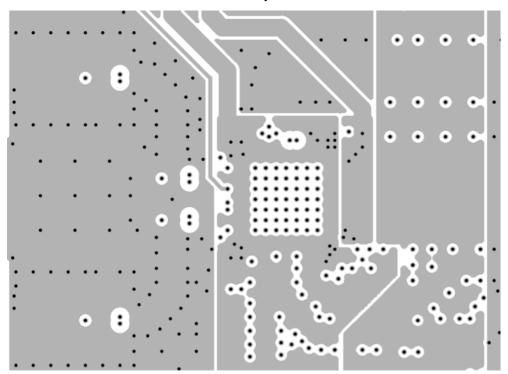

#### **Input Filtering**

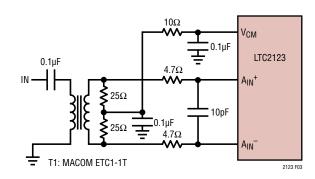

If possible, there should be an RC lowpass filter right at the analog inputs. This lowpass filter isolates the drive circuitry from the A/D sample-and-hold switching, and also limits wide band noise from the drive circuitry. Figure 3 shows an example of an input RC filter. The RC component values should be chosen based on the application's specific input frequency.

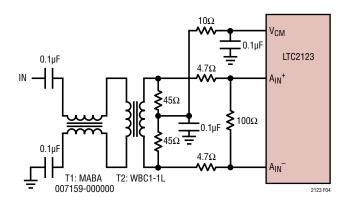

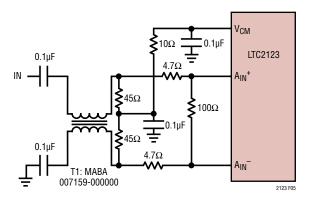

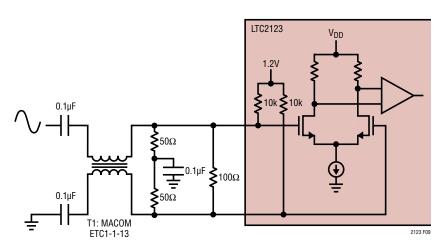

#### **Transformer-Coupled Circuits**

Figure 3 shows the analog input being driven by an RF transformer with the common mode supplied through a pair of resistors via the  $V_{CM}$  pin. At higher input frequencies a transmission line balun transformer (Figures 4 and 5) has better balance, resulting in lower A/D distortion.

Figure 3. Analog Input Circuit Using a Transformer.

Recommended for Input Frequencies from 5MHz to 70MHz

Figure 4. Recommended Front-End Circuit for Input Frequencies from 15MHz to 150MHz

Figure 5. Recommended Front-End Circuit for Input Frequencies from 150MHz to 900MHz

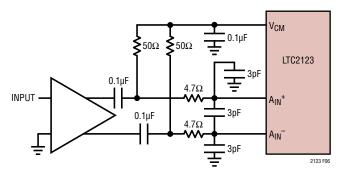

Figure 6. Front-End Circuit Using a High Speed Differential Amplifier

Figure 7. Reference Circuit

#### **Amplifier Circuits**

Figure 6 shows the analog input being driven by a high speed differential amplifier. The output of the amplifier is AC coupled to the A/D so the amplifier's output common mode voltage can be optimally set to minimize distortion. At very high frequencies an RF gain block will often have lower distortion than a differential amplifier. If the gain block is single-ended, then a transformer circuit (Figures 3 through 5) should convert the signal to differential before driving the A/D. The A/D cannot be driven single-ended.

#### Reference

The LTC2123 has an internal 1.25V voltage reference. For a 1.5V input range with internal reference, connect SENSE to  $V_{DD}$ . For a 1.5V input range with an external reference, apply a 1.25V reference voltage to SENSE (Figure 7).

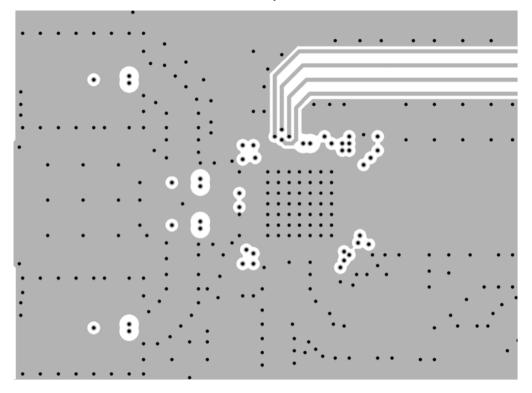

#### **Device Clock (DEVCLK) Input**

The DEVCLK is used to derive the ADC sample clock, so the signal quality of the DEVCLK inputs strongly affects the A/D noise performance. The DEVCLK inputs should be treated as analog signals. Do not route them next to digital traces on the circuit board. The DEVCLK inputs are internally biased to 1.2V through 10k equivalent resistance (Figure 8).

Figure 8. Equivalent DEVCLK Input Circuit

LINEAR TECHNOLOGY

If the common mode of the driver is within 1.1V to 1.5V, it is possible to drive the DEVCLK inputs directly. Otherwise a transformer or coupling capacitors are needed (Figures 9 and 10). The maximum (peak) voltage of the input signal should never exceed  $V_{DD}$  +0.1V or go below -0.1V.

The ADC sample clock is derived from DEVCLK. For good performance the sample clock should have a 50% (±5%) duty cycle. There are two programmable options provided in the LTC2123 that will ensure a 50% duty cycle sample clock:

- An optional DEVCLK divide-by-two circuit is provided in the clock path to convert a 2X harmonic DEVCLK to a 50% duty cycle sample clock. The 2X\_CLK option is enabled via SPI register 2, bit 2.

- 2) If a 2X clock is not available, the clock Duty Cycle Stabilizer (DCS) circuit may be enabled. When enabled, the DEVCLK duty cycle can vary from 30% to 70% and the duty cycle stabilizer will maintain a constant 50% internal duty cycle. The duty cycle stabilizer is enabled via SPI register 2, bit 0. If the 2X\_CLK option is selected in the SPI register the Duty Cycle Stabilizer is disabled regardless of the state of the DCS\_en bit.

For applications where the sample rate needs to be changed quickly and a 2X clock is not available, both the 2X\_CLK and the clock duty cycle stabilizer may be disabled. In this case, care should be taken to make the DEVCLK a 50% (±5%) duty cycle.

#### **Overflow Detection**

An overflow (OF) is detected when the analog inputs are either over-ranged or under-ranged. There are two mechanisms for reporting an OF event:

- 1) The OF bit is transmitted as part of the serial bit stream following the LSB of the ADC data.

- 2) There is a separate LVDS output pair dedicated to early indication of an OF event. The LVDS OF indicator has a latency of 6 sample clock cycles. Both ADC OF signals are multiplexed to one output pair at double data rate. The Channel A OF signal is active on the first half of the internal sample clock and the Channel B OF signal is active on the second half of the cycle.

The LVDS OF indicator is output at standard LVDS levels: 3.5mA output current and a 1.25V output common mode voltage. An external  $100\Omega$  differential termination resistor is required to function properly. The termination resistor should be located as close as possible to the LVDS receiver. If used, this LVDS output pair is enabled via SPI register 2, bit 1.

#### **DATA FORMAT**

Table 1 shows the relationship between the analog input voltage, the digital data output bits and the overflow bit. The output data format is offset binary.

Figure 9. Sinusoidal DEVCLK Drive

Figure 10. AC Coupled DEVCLK Drive

Table 1. Output Codes vs Input Voltage

| A <sub>IN</sub> <sup>+</sup> – A <sub>IN</sub> <sup>-</sup> (1.5V RANGE) | 0F | D13-D0<br>(OFFSET BINARY) |

|--------------------------------------------------------------------------|----|---------------------------|

| >0.75V                                                                   | 1  | 11 1111 1111 1111         |

| +0.75V                                                                   | 0  | 11 1111 1111 1111         |

| +0.749908V                                                               | 0  | 11 1111 1111 1110         |

| +0.0000915V                                                              | 0  | 10 0000 0000 0001         |

| +0.00000V                                                                | 0  | 10 0000 0000 0000         |

| -0.0000915V                                                              | 0  | 01 1111 1111 1111         |

| -0.0001831V                                                              | 0  | 01 1111 1111 1110         |

| -0.7499084V                                                              | 0  | 00 0000 0000 0001         |

| -0.75V                                                                   | 0  | 00 0000 0000 0000         |

| <-0.75V                                                                  | 1  | 00 0000 0000 0000         |

#### **Power Down Modes**

The power down modes are controlled through register 1 of the SPI interface. The two ADC channels may be powered down separately, simultaneously, or the entire device may be placed in sleep mode to conserve power. The "PDA" and "PDB" SPI register bits are used to power down each ADC channel individually while keeping the internal clock and reference circuits active. "SLEEP" powers down the entire device, resulting in < 5mW power consumption. The amount of time required to recover from sleep mode depends on the size of the bypass capacitor on  $V_{REF}$ . For the suggested value of 2.2µF, the A/D will stabilize after 0.1ms + 2500 • tp where tp is the period of the sampling clock.

#### Nap Mode

In "NAP" mode both ADC cores are powered down while the internal clock circuits, reference circuits, and serial

interface stay active, allowing faster wake-up. While in nap mode the data at the output of the each ADC is forced to zero. The SPI and the serial test patterns are fully functional in nap mode, so any test pattern may be selected through the SPI. Recovering from nap mode requires at least 100 clock cycles.

#### **JESD204B Overview**

JESD204B is a JEDEC standard that defines a high speed serial interface for data converters. The advantages of serialization include the simplification of printed circuit board (PCB) layout through the reduction of traces on the PCB. JESD204B solves several problems associated with serial data transmission, such as the identification of the start of a sample and the proper alignment of data arriving on multiple lanes.

JESD204B devices encode the parallel data using industry standard 8B/10B code-groups (IEEE 802.3-2002, section 3). There is an overhead requirement of 2 bits for every 8 encoded bits (8 bits are encoded to 10 bits), but encoding the ADC data prior to serialization provides certain benefits which make the transmitted data more suitable for serial transmission: These benefits include DC balance (for AC coupling), and Run-Length Limiting (providing a sufficient number of transitions for the receiver to extract the clock from the data with a Phase-Locked Loop).

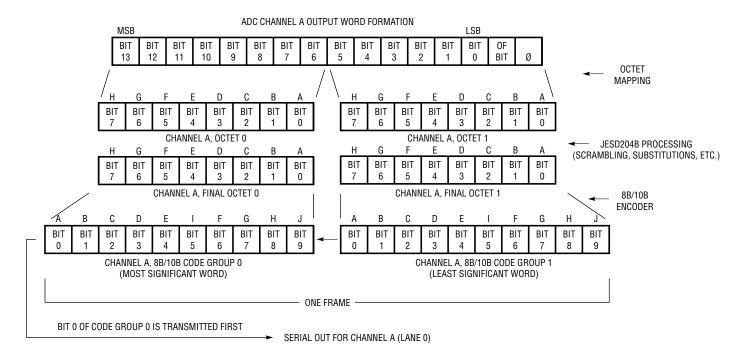

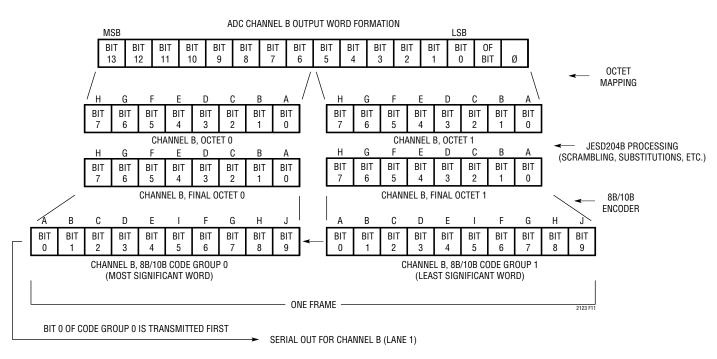

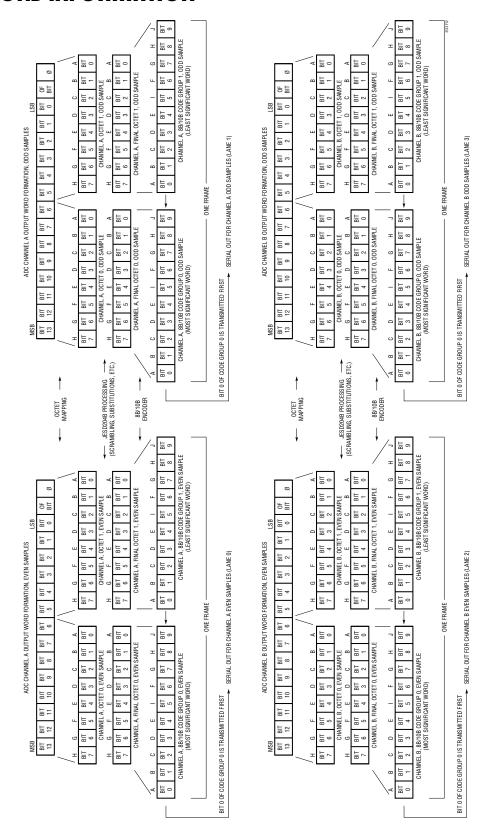

Figures 11 and 12 illustrate the transformation of ADC sampled data into 10-bit code groups prior to transmission. The code-groups are formed into frames and multiframes. For the LTC2123, there are two possible lane configurations:

- 1) Two lane mode (one lane per ADC) operating at up to 5Gbps per lane.

- 2) Four lane mode (two lanes per ADC) operating up to 2.5Gbps per lane.

### SYNC~ Signal

In addition to the high speed serial lanes, JESD204B requires the use of a SYNC~ (active low) signal. The SYNC~ signal originates from the receiver and serves as a request to the LTC2123 that synchronization is required (JESD204B 4.9).

LINEAR TECHNOLOGY

Figure 11. Word Formation of Each Lane in Two-Lane Mode

Figure 12. Word Formation of Each Lane in Four-Lane Mode

Table 2. JESD204B Link Configuration Parameters

| IGDIO E. GEODEO ID EI                       | iik ooiiiigaratioii i araiiioto                      | 10                                                   |                      |

|---------------------------------------------|------------------------------------------------------|------------------------------------------------------|----------------------|

| JESD204B LINK<br>CONFIGURATION<br>PARAMETER | LTC2123 DEVICE<br>VALUE FOR ONE LANE<br>PER ADC MODE | LTC2123 DEVICE<br>VALUE FOR TWO LANE<br>PER ADC MODE | ENCODING             |

| DID<7:0>                                    | SPI Programmable                                     | SPI Programmable                                     | Binary Value         |

| ADJCNT<3:0>                                 | NA, 0000                                             | NA, 0000                                             | Binary Value         |

| BID<3:0>                                    | SPI Programmable                                     | SPI Programmable                                     | Binary Value         |

| ADJDIR                                      | NA, 0                                                | NA, 0                                                | Binary Value         |

| PHADJ                                       | NA, 0                                                | NA, 0                                                | Binary Value         |

| CMLOUT_A0 CMLOUT_A1 CMLOUT_B0 CMLOUT_B1     | 0_0000<br>NA<br>0_0001<br>NA                         | 0_0000<br>0_0001<br>0_0010<br>0_0011                 | Binary Value Minus 1 |

| SCR<0>                                      | SPI Programmable                                     |                                                      | Binary Value         |

| L <sub>-1</sub> <4:0>                       | 0_0001                                               | 0_0011                                               | Binary Value Minus 1 |

| F <sub>-1</sub> <7:0>                       | 0000_0001                                            | 0000_0001                                            | Binary Value Minus 1 |

| K <sub>-1</sub> <4:0>                       | SPI Programmable                                     | SPI Programmable                                     | Binary Value Minus 1 |

| M <sub>-1</sub> <7:0>                       | 0000_0001                                            | 0000_0001                                            | Binary Value Minus 1 |

| <del></del>                                 | 01                                                   | 01                                                   | Binary Value         |

| N <sub>-1</sub> <4:0>                       | 0_1101                                               | 0_1101                                               | Binary Value Minus 1 |

| SUBCLASSV<2:0>                              | SPI Programmable                                     | SPI Programmable                                     | Binary Value         |

| N' <sub>-1</sub> <4:0>                      | 0_1111                                               | 0_1111                                               | Binary Value Minus 1 |

| JESDV<2:0>                                  | 001                                                  | 001                                                  | Binary Value         |

| S <sub>-1</sub> <4:0>                       | 0_0000                                               | 0_0001                                               | Binary Value Minus 1 |

| HD                                          | 0                                                    | 0                                                    | Binary Value         |

| CF<4:0>                                     | 0_0000                                               | 0_0000                                               | Binary Value         |

| FCHK<7:0>                                   | Sum of all fields mod 256                            | Sum of all fields mod 256                            | Binary Value         |

|                                             |                                                      |                                                      |                      |

#### **JESD204B Link Configuration Parameters**

There are 20 link configuration parameters used by JESD204B to describe the operation of the link (JESD204B 8.3, Table 20). The receiver must match the parameters of the LTC2123 in order for error free communication to take place. Table 2 summarizes the link parameters of the LTC2123.

#### **JESD204B Subclasses**

There are 3 subclasses of operation for JESD204B. These subclasses provide different levels of deterministic latency through the communication link. Below is a simple overview of the three subclasses:

Subclass 0: No deterministic latency support is provided. There is no support for resetting and aligning critical clocks between the LTC2123 and the receiver. The LTC2123 is compliant with this subclass.

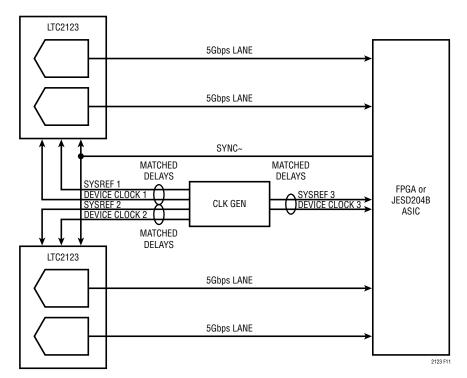

Subclass 1: Deterministic latency is obtained through the addition of a SYSREF signal. The SYSREF signal provides precise timing information for aligning critical clocks in the LTC2123 and in the receiver. The low to high transition of SYSREF is sampled by the rising edge of DEVCLK, so the DEVCLK and SYSREF signals should originate from close proximity to each other and delays between these signals should closely match (Figure 13). The LTC2123 is compliant with this subclass.

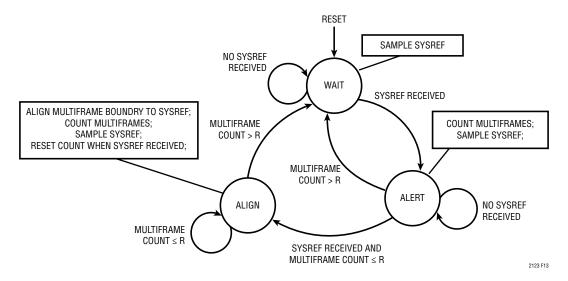

As an added subclass 1 protection, the LTC2123 provides an optional Alert mode. Depending on the SYSREF generation circuit, there could be an erroneous or short pulse generated as the first SYSREF pulse. To avoid the possibility of alignment errors due to a compromised first pulse, an optional Alert mode may be enabled in the SPI. While in Alert mode, the LTC2123 will ignore the first SYSREF pulse, and reset critical clocks with the second pulse. The first pulse, therefore, serves to arm the system, and the second pulse resets the clocks. After a programmable number of multiframes without a second SYSREF

pulse, the system is disarmed until the next SYSREF pulse is received. Figure 14 illustrates the state machine of the Subclass 1 Alert mode.

Subclass 2: Deterministic latency support is obtained by sampling the low to high transition of the SYNC~ signal with the rising edge of DEVCLK. Upon detection of the SYNC~ low to high transition, the critical clocks are realigned. The LTC2123 is compatible with this subclass, but the detection resolution is always determined by the ADC DEVCLK frequency.

NOTE: INTERNAL CLOCKS ARE RESET BY SYSREF ON THE RISING EDGE OF THE DEVICE CLOCK. FOR DETERMINISTIC LATENCY, EACH SYSREF/DEVICE CLOCK PAIR SHOULD HAVE MATCHED DELAYS, AND SHOULD SATISFY SETUP AND HOLD REQUIREMENTS,  $t_{SU\_SYN}$  AND  $t_{L\_SYS}$ .

Figure 13. JESD204B Subclass 1 Configuration

Figure 14. Alert Mode of Subclass 1

## **Code-Group Synchronization**

(JESD204B 5.3.3.1)

In order for each receiver to properly align to the received serial data, each ADC transmitter must communicate the location of the start of a code-group and the start of a frame to its receiver. When multiple ADC devices are transmitting on multiple lanes, this alignment must take place on all lanes simultaneously in order for the receivers to determine the relationship between lanes. A receiver initiates synchronization by asserting its SYNC~ signal. When multiple receivers are present, the SYNC~ signals of all receivers may be logically ORed to provide synchronization requests to all ADC devices simultaneously. The following synchronization process may be initiated by the receivers at any time:

- The receiver issues a request for synchronization by asserting the SYNC~ signal (active low).

- The ADC device will detect the SYNC~ assertion on the fifth rising edge of its Local Frame Clock (LFC). At the beginning of the frame following detection, each ADC transmitter will broadcast a continuous stream of K28.5 symbols in place of data.

- After the receiver has successfully received at least four consecutive K28.5 symbols, it will de-assert the SYNC~ signal.

#### Subclass 0:

- The ADC device will detect the de-assertion of the SYNC~ signal on the rising edge of its device clock, and continue to transmit K28.5 symbols on each lane until the beginning of the frame following detection.

- If the Initial Lane Alignment Sequence (ILAS) is not disabled, the ADC device will reset its multiframe start marker and transmit an ILAS followed by encoded ADC data. The ILAS will be four multiframes in length.

- If the ILAS is disabled, the ADC device will begin transmitting encoded ADC data on each lane.

#### Subclass 1:

- The ADC device will detect the de-assertion of the SYNC~ signal on the rising edge of its device clock, and continue to transmit K28.5 symbols on each lane until the beginning of the next multiframe.

- If the ILAS is not disabled, the ADC device will transmit an ILAS at the beginning of the multiframe. The ILAS is immediately followed by encoded ADC data.

- If the ILAS is disabled the ADC device will begin transmitting encoded ADC data on each lane at the beginning of the multiframe boundary.

#### Subclass 2:

- Unique to this subclass, the SYNC~ signal must be de-asserted by the receiver on its multiframe boundary. The ADC device will detect the de-assertion of the SYNC~ signal on the rising edge of its device clock (for minimum latency error the ADC device clock frequency must be greater than or equal to the receiver device clock frequency).

- The ADC's Local Frame Clock (LFC) and Local Multiframe Clock (LMFC) are reset on the detected edge.

- After resetting the internal clocks, the ADC device will continue to transmit K28.5 symbols on each lane for one multiframe (at least 5 frames + 9 octets) to enable the receiver to re-sync to the new clock positions. The ADC device will then cease K28.5 transmission at the next multiframe start.

- If the ILAS is enabled, the ADC device will transmit an ILAS followed by encoded ADC data.

- If the ILAS is not enabled the ADC device will transmit encoded ADC data on each lane.

The start of a code-group will coincide with the start of each K28.5 symbol.

The start of a frame will coincide with the first non-K28.5 symbol after the SYNC~ signal has been de-asserted.

# **Initial Lane Alignment Sequence Transmission** (JESD204B 5.3.3.5)

When the lane alignment sequence is not disabled via the SPI, the sequence illustrated in the Lane Alignment Sequence Tables will be transmitted immediately after code-group synchronization is complete. The lane alignment sequence consists of four complete multiframes. The minimum number of octets in a multiframe is ultimately controlled by the configuration contents of the 2nd multiframe in the lane alignment sequence.

The lane alignment sequence is constructed as follows:

- Each multiframe in the sequence will begin with a K28.0 control character, and will end with a K28.3 symbol.

- An 8-bit lane alignment counter is used to generate the octet data for the lane alignment sequence. The counter is reset by the code group synchronization process. The counter is clocked by an octet clock (character clock).

- The octet of the lane alignment counter is always transmitted during the lane alignment sequence unless a control character or configuration octet is being transmitted.

- The second multiframe contains the configuration data.

The configuration data begins on the 3rd octet of the multiframe, and is preceded by a K28.4 symbol.

- The lane alignment sequence may not be scrambled (the Scramble option in the SPI register is ignored).

Note that the K28.3 symbol is the lane alignment symbol, and may be used by the receivers to align the multiframe boundary pointers in all the lanes in the link.

Lane Alignment Sequence Tables for Two Lane Mode (One Lane per ADC), 1st Multiframe

Table 3a. Minimum Multiframe Length (K=9), 1st Multiframe

| FRAME | DESCRIPTION           | DATA<br>OCTET<br>(HEX) | 8B/10B<br>SYMBOL |

|-------|-----------------------|------------------------|------------------|

| 0     | Start of Subsequence  |                        | K28.0            |

|       | Octet Counter         | 01                     | D1.0             |

| 1     | Octet Counter         | 02                     | D2.0             |

|       | Octet Counter         | 03                     | D3.0             |

| 2     | Octet Counter         | 04                     | D4.0             |

|       | Octet Counter         | 05                     | D5.0             |

| 3     | Octet Counter         | 06                     | D6.0             |

|       | Octet Counter         | 07                     | D7.0             |

| 4     | Octet Counter         | 08                     | D8.0             |

|       | Octet Counter         | 09                     | D9.0             |

| 5     | Octet Counter         | 0A                     | D10.0            |

|       | Octet Counter         | OB                     | D11.0            |

| 6     | Octet Counter         | 0C                     | D12.0            |

|       | Octet Counter         | 0D                     | D13.0            |

| 7     | Octet Counter         | 0E                     | D14.0            |

|       | Octet Counter         | 0F                     | D15.0            |

| 8     | Octet Counter         | 10                     | D16.0            |

|       | Lane Alignment Symbol |                        | K28.3            |

Table 3b. Maximum Multiframe Length (K=32), 1st Multiframe

| FRAME | DESCRIPTION           | DATA<br>OCTET<br>(HEX) | 8B/10B<br>SYMBOL |  |

|-------|-----------------------|------------------------|------------------|--|

| 0     | Start of Subsequence  |                        | K28.0            |  |

|       | Octet Counter         | 01                     | D1.0             |  |

| 1     | Octet Counter         | 02                     | D2.0             |  |

|       | Octet Counter         | 03                     | D3.0             |  |

| 2     | Octet Counter         | 04                     | D4.0             |  |

|       | Octet Counter         | 05                     | D5.0             |  |

| 3     | Octet Counter         | 06                     | D6.0             |  |

|       | Octet Counter         | 07                     | D7.0             |  |

| 4     | Octet Counter         | 08                     | D8.0             |  |

|       | Octet Counter         | 09                     | D9.0             |  |

| 5     | Octet Counter         | 0A                     | D10.0            |  |

|       | Octet Counter         | 0B                     | D11.0            |  |

| 6     | Octet Counter         | 0C                     | D12.0            |  |

|       | Octet Counter         | 0D                     | D13.0            |  |

| 7     | Octet Counter         | 0E                     | D14.0            |  |

|       | Octet Counter         | 0F                     | D15.0            |  |

| 8     | Octet Counter         | 10                     | D16.0            |  |

|       | Octet Counter         | 11                     | D17.0            |  |

| :     | :                     | :                      | ÷                |  |

| 25    | Octet Counter         | 32                     | D18.1            |  |

|       | Octet Counter         | 33                     | D19.1            |  |

| 26    | Octet Counter         | 34                     | D20.1            |  |

|       | Octet Counter         | 35                     | D21.1            |  |

| 27    | Octet Counter         | 36                     | D22.1            |  |

|       | Octet Counter         | 37                     | D23.1            |  |

| 28    | Octet Counter         | 38                     | D24.1            |  |

|       | Octet Counter         | 39                     | D25.1            |  |

| 29    | Octet Counter         | 3A                     | D26.1            |  |

|       | Octet Counter         | 3B                     | D27.1            |  |

| 30    | Octet Counter         | 3C                     | D28.1            |  |

|       | Octet Counter         | 3D                     | D29.1            |  |

| 31    | Octet Counter         | 3E                     | D30.1            |  |

|       | Lane Alignment Symbol |                        | K28.3            |  |

Lane Alignment Sequence Tables for Two Lane Mode (One Lane per ADC), 2nd Multiframe

Table 3c. Minimum Multiframe Length (K=9), 2nd Multiframe

| FRAME | DESCRIPTION                                                    | DATA<br>OCTET<br>(HEX) | 8B/10B<br>SYMBOL |

|-------|----------------------------------------------------------------|------------------------|------------------|

| 0     | Start of Subsequence                                           |                        | K28.0            |

|       | Start of Link Configuration                                    |                        | K28.4            |

| 1     | <i>DID</i> [7:0]                                               | *00                    | D0.0             |

|       | { <i>ADJCNT</i> [3:0], <i>BID</i> [3:0]}                       | *00                    | D0.0             |

| 2     | {O, ADJDIR, PHADJ, LID[4:0]}                                   | 00                     | D0.0             |

|       | {SCR, 00, L_1[4:0]}                                            | *01                    | D1.0             |

| 3     | F <sub>-1</sub> [7:0]                                          | 01                     | D1.0             |

|       | {000, K_1[4:0]}                                                | *08                    | D8.0             |

| 4     | <i>M</i> <sub>-1</sub> [7:0]                                   | 01                     | D1.0             |

|       | { <i>CS</i> [1:0]], <i>0</i> , [ <i>N</i> <sub>-1</sub> [4:0]} | 4D                     | D13.2            |

| 5     | {SUBCLASSV[2:0], N'_1[4:0]}                                    | 0F                     | D15.0            |

|       | { <i>JESDV</i> [2:0], <i>S</i> <sub>-1</sub> [4:0]}            | 20                     | D0.1             |

| 6     | { <i>HD</i> [0], <i>00</i> , <i>CF</i> [4:0]}                  | 00                     | D0.0             |

|       | Reserved                                                       | 00                     | D0.0             |

| 7     | Reserved                                                       | 00                     | D0.0             |

|       | FCHK[7:0]                                                      | 29                     | D9.1             |

| 8     | Octet Counter                                                  | 22                     | D2.1             |

|       | Lane Alignment Symbol                                          |                        | K28.3            |

X\_1 Indicates that field X is affected by -1 encoding

**Configuration Field Defaults:** *DID*=0, *BID*=0, *LID*=0, *SCR*=0, *L*=2, *F*=2, *K*=9 or 32, *M*=2, *CS*=1, *N*=14, SUB-CLASSV=0, *N*'=16, *S*=1, *HD*=0, *CF*=0

**Field Descriptions:** *DID*=Device ID, *BID*=Bank ID, *LID*=Lane ID, *SCR*=Scrambling enabled, *L*=Lanes per device, *F*=Octets per frame, *K*=Frames per multiframe, *M*=Converters per device, *CS*=Control bits per sample, *N*=Converter Resolution, *N*'=Total bits per sample, *S*=Samples per converter per frame, *HD*=High density format, *CF*=Control words per frame per link, *FCHK*=Checksum of all fields (mod 256)

Table 3d. Maximum Multiframe Length (K=32), 2nd Multiframe

| FRAME | DESCRIPTION                                            | DATA<br>OCTET<br>(HEX) | 8B/10B<br>Symbol |

|-------|--------------------------------------------------------|------------------------|------------------|

| 0     | Start of Subsequence                                   |                        | K28.0            |

|       | Start of Link Configuration                            |                        | K28.4            |

| 1     | <i>DID</i> [7:0]                                       | *00                    | D0.0             |

|       | { <i>ADJCNT</i> [3:0], <i>BID</i> [3:0]}               | *00                    | D0.0             |

| 2     | {0, <i>ADJDIR</i> , <i>PHADJ</i> , <i>LID</i> [4:0]}   | *00                    | D0.0             |

|       | { <i>SCR</i> [0], 00, <i>L</i> <sub>-1</sub> [4:0]}    | *01                    | D1.0             |

| 3     | F <sub>-1</sub> [7:0]                                  | 01                     | D1.0             |

|       | {000, <i>K</i> <sub>-1</sub> [4:0]}                    | *1F                    | D8.0             |

| 4     | M <sub>-1</sub> [7:0]                                  | 01                     | D1.0             |

|       | { <i>CS</i> [1:0]], 0, [ <i>N</i> <sub>-1</sub> [4:0]} | 4D                     | D13.2            |

| 5     | {SUBCLASSV[2:0], N'_1[4:0]}                            | 0F                     | D15.0            |

|       | { <i>JESDV</i> [2:0], <i>S</i> <sub>-1</sub> [4:0]}    | 20                     | D0.1             |

| 6     | { <i>HD</i> [0], 00, <i>CF</i> [4:0]}                  | 00                     | D0.0             |

|       | Reserved                                               | 00                     | D0.0             |

| 7     | Reserved                                               | 00                     | D0.0             |

|       | FCHK[7:0]                                              | 40                     | D0.2             |

| 8     | Octet Counter                                          | 50                     | D16.2            |

|       | Octet Counter                                          | 51                     | D17.2            |

| ÷     | :                                                      | ÷                      | ÷                |

| 25    | Octet Counter                                          | 72                     | D18.3            |

|       | Octet Counter                                          | 73                     | D19.3            |

| 26    | Octet Counter                                          | 74                     | D20.3            |

|       | Octet Counter                                          | 75                     | D21.3            |

| 27    | Octet Counter                                          | 76                     | D22.3            |

|       | Octet Counter                                          | 77                     | D23.3            |

| 28    | Octet Counter                                          | 78                     | D24.3            |

|       | Octet Counter                                          | 79                     | D25.3            |

| 29    | Octet Counter                                          | 7A D26.3               |                  |

|       | Octet Counter                                          | counter 7B D27         |                  |

| 30    | Octet Counter                                          | 7C                     | D28.3            |

|       | Octet Counter                                          | 7D                     | D29.3            |