### **Features and Benefits**

- Supply voltage, V<sub>BB</sub>, 36 V maximum

- Maximum DC current 3 A continuous, 6 A pulsed (1 kHz, duty cycle < 1%, pulse width < 10 μs)</li>

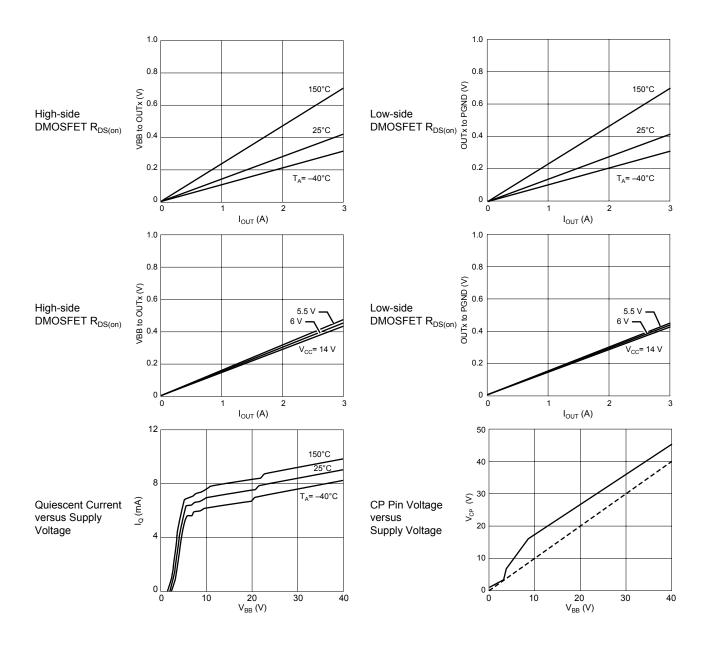

- $R_{DS(on)} = 300 \text{ m}\Omega$  maximum, at  $T_J = 125$ °C

- Operation modes: forward, reverse, brake (high- or lowside freewheeling current circulation)

- Output disable pin (DI pin)

- Protections:

- Overvoltage protection (OVP), 36 V minimum

- Overcurrent protection (OCP), 3 A typical

- Overcurrent limitation (OCL), 6 A typical

- Externally adjustable delay timer to halt OCL

- <sup>o</sup> Thermal shutdown protection (TSD), 151°C minimum

- Undervoltage lockout on V<sub>BB</sub> (UVLO), 4.2 V minimum

- Open load detection at startup

- Diagnosis output linked to OVP, OCP, TSD, UVLO, and open load detection, at startup and in operation

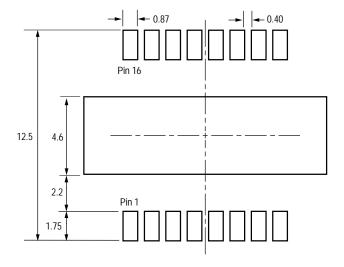

Package: 16 pin HSOP with exposed thermal pad and tabs

The SPF7302 is a fully protected, single chip full-bridge driver IC for DC brush motor applications. The various protection circuits integrated are: overvoltage protection (OVP); overcurrent protection (OCP) with latch, which is adapted to the DMOSFETs in each full bridge; undervoltage lockout (UVLO); open load detection; and overcurrent limitation.

**Description**

The package is a thermally enhanced 16-pin HSOP power package with an exposed thermal pad on the bottom side of the package.

Not to scale

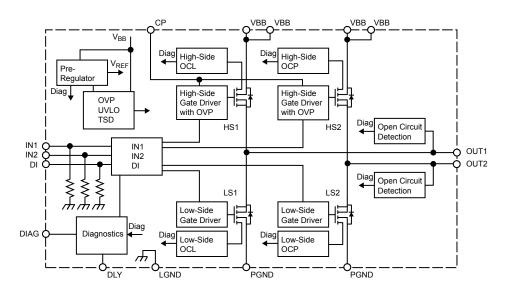

# **Functional Block Diagram**

### **Selection Guide**

| Part Number | Package                                         | Packing                      |

|-------------|-------------------------------------------------|------------------------------|

| SPE / 302   | Thermally enhanced surface mount (HSOP), 16-pin | Minimum quantity 1400 pieces |

## **Absolute Maximum Ratings** at $T_A = 25$ °C

| Characteristic                          | Symbol             | Notes                                                                                           | Rating     | Unit |  |

|-----------------------------------------|--------------------|-------------------------------------------------------------------------------------------------|------------|------|--|

| Supply Voltage                          | V <sub>BB</sub>    |                                                                                                 | -0.3 to 36 | V    |  |

| IN1, IN2, DI, and DLY Pin Input Voltage | V <sub>x</sub>     |                                                                                                 | -0.3 to 6  | V    |  |

| Output Current                          | Io                 |                                                                                                 | ±3         | Α    |  |

| Output Gurrent                          | I <sub>Opeak</sub> | Continuous: 1 kHz, duty cycle <1%; pulse: < 10 µs                                               | ±6         | Α    |  |

| DIAG Pin Output Voltage                 | $V_{DIAG}$         |                                                                                                 | -0.3 to 6  | V    |  |

| DIAG Pin Input Current                  | I <sub>DIAG</sub>  | DIAG pin sink current                                                                           | -2         | mA   |  |

| CP Pin Voltage                          | V <sub>CP</sub>    |                                                                                                 | -0.3 to 36 | V    |  |

|                                         | P <sub>D1</sub>    | With infinite heatsink                                                                          | 39         |      |  |

| Power Dissipation                       | P <sub>D2</sub>    | Mounted on glass epoxy PCB, 50 mm×74 mm×1.6 mm; 0.5 oz copper (18 µm thick) exposed copper area | 4          | W    |  |

| Junction Temperature                    | TJ                 |                                                                                                 | -40 to 150 | °C   |  |

| Operating Ambient Temperature           | T <sub>A</sub>     |                                                                                                 | -40 to 105 | °C   |  |

| Storage Temperature                     | T <sub>stg</sub>   |                                                                                                 | 40 to 150  | °C   |  |

| Thermal Resistance, Junction to Case    | R <sub>θJC</sub>   | Mounted on glass epoxy PCB, 50 mm×74 mm×1.6 mm;                                                 | 3.2        | °C/W |  |

| Thermal Resistance, Junction to Ambient | $R_{\theta JA}$    | 0.5 oz copper (18 µm thick) exposed copper area                                                 | 31         | °C/W |  |

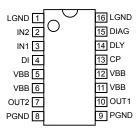

## **Pin-out Diagram**

## **Terminal List Table**

| Number | Name | Description                                    |

|--------|------|------------------------------------------------|

| 1      | LGND | Logic GND                                      |

| 2      | IN2  | Input pin 2                                    |

| 3      | IN1  | Input pin 1                                    |

| 4      | DI   | Disable pin                                    |

| 5      | VBB  | Supply input voltage                           |

| 6      | VBB  | Supply input voltage                           |

| 7      | OUT2 | Output 2                                       |

| 8      | PGND | Power GND                                      |

| 9      | PGND | Power GND                                      |

| 10     | OUT1 | Output 1                                       |

| 11     | VBB  | Supply input voltage                           |

| 12     | VBB  | Supply input voltage                           |

| 13     | СР   | Charge pump capacitor pin                      |

| 14     | DLY  | Overcurrent limitation delay setting input pin |

| 15     | DIAG | Diagnostics output pin                         |

| 16     | LGND | Logic GND                                      |

All performance characteristics given are typical values for circuit or system baseline design only and are at the nominal operating voltage and an ambient temperature, T<sub>A</sub>, of 25°C, unless otherwise stated.

# **SPF7302**

**ELECTRICAL CHARACTERISTICS**¹ valid at  $T_J$  =  $-30^{\circ}$ C to 125°C,  $V_{BB}$  = 14 V,  $V_{DI}$  = 5 V,  $C_{CP}$  = 47 nF,  $R_{DIAG}$  = 5.1 k $\Omega$ , unless otherwise specified

| Characteristic                             | Symbol                 | Test Conditions                                                          | Min.       | Тур. | Max. | Unit |

|--------------------------------------------|------------------------|--------------------------------------------------------------------------|------------|------|------|------|

| Supply Voltage                             | V <sub>BB</sub>        |                                                                          | 6          | _    | 18   | V    |

| OUTx Pin Leakage Current                   | I <sub>leakHS</sub>    |                                                                          | -1         | _    | _    | mA   |

| OUTX Fill Leakage Current                  | I <sub>leakLS</sub>    |                                                                          | _          | _    | 1    | mA   |

|                                            | R <sub>DS(ON_1H</sub>  | I <sub>OUT</sub> = 1 A                                                   | _          | _    | 300  | mΩ   |

| DMOSFET On Resistance                      | R <sub>DS(ON)_2H</sub> | I <sub>OUT</sub> = 3 A                                                   | _          | _    | 300  | mΩ   |

| DIVIOSI ET OTTRESISTANCE                   | R <sub>DS(ON)_1L</sub> | I <sub>OUT</sub> = 1 A                                                   | _          | _    | 300  | mΩ   |

|                                            | R <sub>DS(ON)_2L</sub> | I <sub>OUT</sub> = 3 A                                                   | _          | _    | 300  | mΩ   |

|                                            | V <sub>F_H1</sub>      | I <sub>OUT1</sub> = 1 A                                                  | _          | 1.0  | 2.0  | V    |

| DMOSFET Body Diode Forward Voltage         | V <sub>F_H2</sub>      | I <sub>OUT2</sub> = 1 A                                                  | _          | 1.0  | 2.0  | V    |

| Diviosi E1 Body Blode i diward voltage     | V <sub>F_L1</sub>      | I <sub>OUT1</sub> = -1 A                                                 | _          | 1.0  | 2.0  | V    |

|                                            | V <sub>F_L2</sub>      | I <sub>OUT2</sub> = -1 A                                                 | _          | 1.0  | 2.0  | V    |

| Quiescent Current                          | I <sub>BB</sub>        |                                                                          | _          | 7    | _    | mA   |

|                                            | I <sub>OCL_H1</sub>    |                                                                          | 2.0        | 3.0  | 4.5  | А    |

| Overcurrent Limit (OCL)                    | I <sub>OCL_H2</sub>    | $T_J = -40^{\circ}$ C to 150°C, $I_{OCL} < I_{OCP}$ ; guaranteed by      | 2.0        | 3.0  | 4.5  | Α    |

| Overcurrent Limit (OCL)                    | I <sub>OCL_L1</sub>    | design                                                                   | 2.0        | 3.0  | 4.5  | Α    |

|                                            | I <sub>OCL_L2</sub>    |                                                                          | 2.0        | 3.0  | 4.5  | Α    |

|                                            | I <sub>OCP_H1</sub>    |                                                                          | 4.5        | 6.0  | 8.0  | А    |

| Overcurrent Protection (OCP)               | I <sub>OCP_H2</sub>    | $T_J = -40$ °C to 150°C, $I_{OCL} < I_{OCP}$ ; guaranteed by             | 4.5        | 6.0  | 8.0  | А    |

| Overcurrent Protection (OCP)               | I <sub>OCP_L1</sub>    | design                                                                   | 4.5        | 6.0  | 8.0  | А    |

|                                            | I <sub>OCP_L2</sub>    |                                                                          | 4.5        | 6.0  | 8.0  | Α    |

| IN1, IN2, DI, and DLY Pin Input Voltage    | $V_{x\_H}$             |                                                                          | 3.0        | _    | 5.3  | V    |

| in 1, in 2, bi, and bet rill input voltage | V <sub>x_L</sub>       |                                                                          | -0.3       | _    | 1.5  | V    |

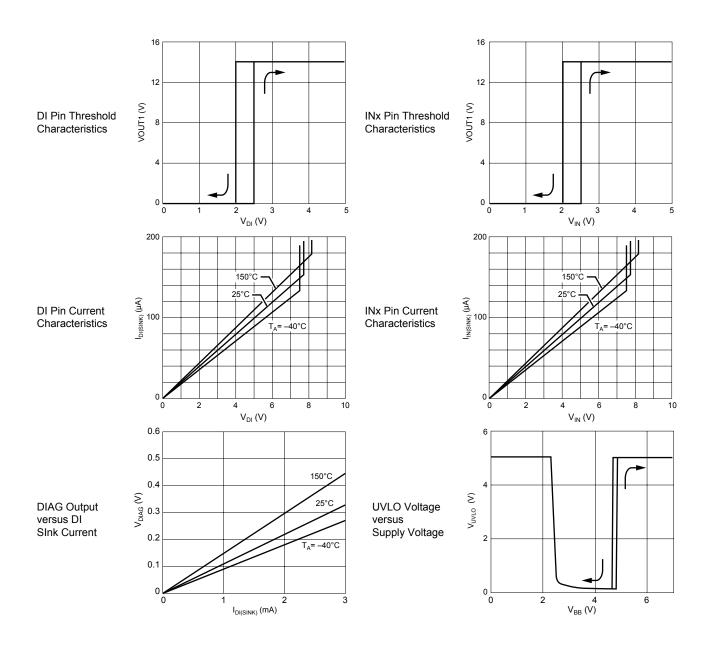

| IN1, IN2, DI, and DLY Pin Input Current    | I <sub>x_H</sub>       | V <sub>DLY</sub> = 5 V                                                   | _          | 100  | 200  | μΑ   |

| in 1, in 2, bi, and but Fill input current | I <sub>x_L</sub>       | V <sub>DLY</sub> = 0 V                                                   | <b>–</b> 1 | _    | 1    | μΑ   |

| DIAG Pin Output Voltage                    | V <sub>DIAG_H</sub>    | V <sub>CC</sub> = 5 V                                                    | 4.0        | _    | _    | V    |

| DIAG 1 III Gutput Voltage                  | V <sub>DIAG_L</sub>    | I <sub>sink</sub> = 2 mA                                                 | _          | _    | 0.4  | V    |

| DIAG Pin Output Current                    | I <sub>DIAG_H</sub>    | V <sub>CC</sub> = 5 V, DIAG pin source current                           | -250       | _    | _    | μΑ   |

| DIAG FIII Output Current                   | I <sub>DIAG_L</sub>    | V <sub>CC</sub> = 5 V, DIAG pin sink current, V <sub>DIAG</sub> = 2 V    | _          | _    | 3    | mA   |

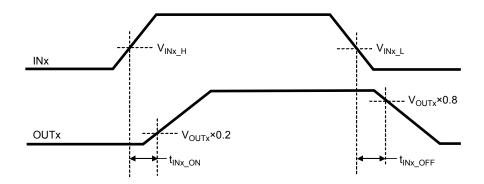

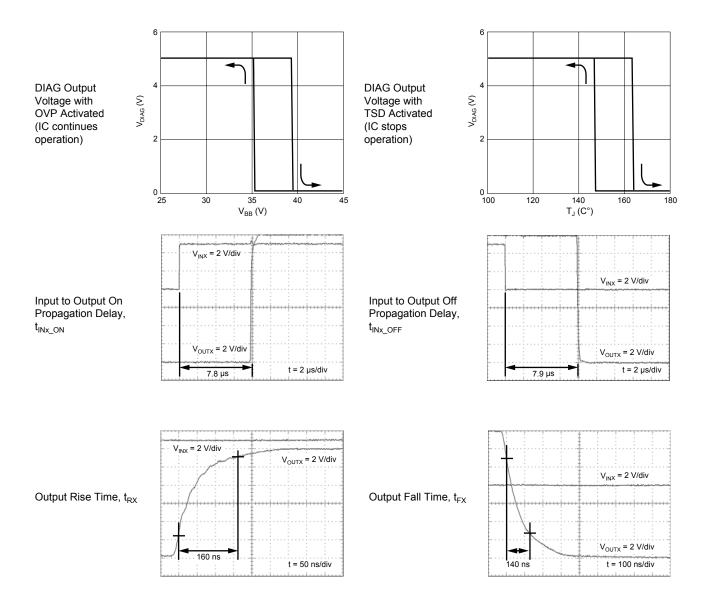

| IN1 and IN2 Pin Input Propagation Time     | t <sub>INx_ON</sub>    | Delay from V <sub>INx</sub> = 2 V→V <sub>OUTx</sub> × 0.2                | _          | 7    | 15   | μs   |

| in and in z i in input Fropagation fille   | t <sub>INx_OFF</sub>   | Delay from V <sub>INx</sub> = 1.5 V→V <sub>OUTx</sub> × 0.8              | _          | 7    | 15   | μs   |

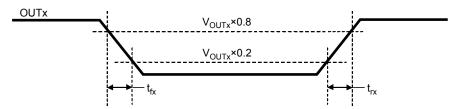

| Output Rise Time                           | t <sub>rx</sub>        | Delay from V <sub>OUTx</sub> = 20%→80% points, at I <sub>OUTx</sub> =1 A | _          | 0.5  | 2    | μs   |

| Output Fall Time                           | t <sub>fx</sub>        | Delay from V <sub>OUTx</sub> = 20%→80% points, at I <sub>OUTx</sub> =1 A | _          | 0.5  | 2    | μs   |

Continued on the next page...

# **ELECTRICAL CHARACTERISTICS**¹ (continued) valid at $T_J = -30$ °C to 125°C, $V_{BB} = 14$ V, $V_{DI} = 5$ V, $C_{CP} = 47$ nF,

$R_{DIAG} = 5.1 \text{ k}\Omega$ . unless otherwise specified

| Characteristic                                       | Symbol                | Test Conditions                                 | Min. | Тур. | Max. | Unit |

|------------------------------------------------------|-----------------------|-------------------------------------------------|------|------|------|------|

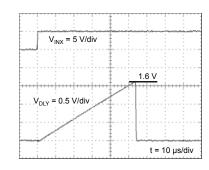

| DLY Pin Threshold Voltage                            | V <sub>DLY(th)</sub>  | Overcurrent limitation (OCL) activating voltage | 1.4  | 1.6  | 1.8  | V    |

| DLY Pin Sourcing Current <sup>2</sup>                | I <sub>DLY</sub>      |                                                 | 15   | 30   | 60   | μΑ   |

| UVLO Releasing Voltage                               | V <sub>UVLO_OFF</sub> |                                                 | _    | -    | 5.2  | V    |

| UVLO Activating Voltage                              | V <sub>UVLO_ON</sub>  |                                                 | 4.2  | -    | _    | V    |

| UVLO Hysteresis                                      | V <sub>UVLOhys</sub>  |                                                 | _    | 0.2  | _    | V    |

| OVP Protection Activating Voltage                    | V <sub>OVP_ON</sub>   |                                                 | 36   | -    | 42   | V    |

| OVP Protection Releasing Voltage                     | V <sub>OVP_OFF</sub>  |                                                 | 32   | -    | 38   | V    |

| OVP Hysteresis                                       | V <sub>OVPhys</sub>   |                                                 | _    | 5    | _    | V    |

| Thermal Shutdown Activating Temperature <sup>3</sup> | T <sub>TSD_ON</sub>   | Starts at 165°C typical; guaranteed by design   | 151  | 165  | _    | °C   |

| Thermal Shutdown Releasing Temperature <sup>3</sup>  | T <sub>TSD_OFF</sub>  | Guaranteed by design                            | 136  | 150  | _    | °C   |

| Thermal Shutdown Hysteresis <sup>3</sup>             | T <sub>TSDhys</sub>   | Guaranteed by design                            | _    | 15   | _    | °C   |

$<sup>^{1}</sup>$ The parameters at  $T_J$  =  $-40^{\circ}$ C to  $150^{\circ}$ C are specified by design. The actual production tests are done at  $25^{\circ}$ C and  $125^{\circ}$ C.

### Motor Control Truth Table<sup>1</sup>

| Reference | ce Status                                            |    | Input |     |      | Output |      |     | DMOSFET status |     |     |  |

|-----------|------------------------------------------------------|----|-------|-----|------|--------|------|-----|----------------|-----|-----|--|

| Number    | Status                                               | DI | IN1   | IN2 | OUT1 | OUT2   | DIAG | HS1 | LS1            | HS2 | LS2 |  |

| 1         | Forward rotation <sup>2</sup>                        | Н  | Н     | L   | Н    | L      | Н    | ON  | OFF            | OFF | ON  |  |

| 2         | Reverse rotation <sup>2</sup>                        | Н  | L     | Н   | L    | Н      | Н    | OFF | ON             | ON  | OFF |  |

| 3         | Low-side freewheeling                                | Н  | L     | L   | L    | L      | Н    | OFF | ON             | OFF | ON  |  |

| 4         | High-side freewheeling                               | Н  | Н     | Н   | H    | Н      | Н    | ON  | OFF            | ON  | OFF |  |

| 5         | Output disabled                                      | L  | Χ     | X   | Z    | Z      | Н    | OFF | OFF            | OFF | OFF |  |

| 6         | Overcurrent limitation (OCL) active (HS1)            | Н  | Н     | Χ   | Н    | Χ      | Н    | ON  | OFF            | Χ   | Χ   |  |

| 7         | Overcurrent limitation (OCL) active (HS2)            | Н  | X     | Н   | X    | Н      | Н    | X   | Χ              | ON  | OFF |  |

| 8         | Overcurrent limitation (OCL) active (LS1)            | Н  | L     | X   | L    | X      | Н    | OFF | ON             | Χ   | X   |  |

| 9         | Overcurrent limitation (OCL) active (LS2)            | Н  | X     | L   | X    | L      | Н    | X   | Χ              | OFF | ON  |  |

| 10        | Overcurrent protection with latch (OCP) active (HS1) | Н  | Н     | Х   | Z    | Z      | L    | OFF | OFF            | OFF | OFF |  |

| 11        | Overcurrent protection with latch (OCP) active (HS2) | Н  | X     | Н   | Z    | Z      | L    | OFF | OFF            | OFF | OFF |  |

| 12        | Overcurrent protection with latch (OCP) active (LS1) | Н  | L     | X   | Z    | Z      | L    | OFF | OFF            | OFF | OFF |  |

| 13        | Overcurrent protection with latch (OCP) active (LS2) | Н  | X     | L   | Z    | Z      | L    | OFF | OFF            | OFF | OFF |  |

| 14        | Undervoltage lockout (UVLO) protection active        | Х  | Х     | Х   | Z    | Z      | L    | OFF | OFF            | OFF | OFF |  |

| 15        | Overvoltage protection (OVP) active                  | X  | X     | X   | X    | X      | L    | Х   | Χ              | Χ   | X   |  |

| 16        | Open load detected at startup                        | L  | X     | X   | X    | Χ      | L    | OFF | OFF            | OFF | OFF |  |

| 17        | Open load detected in operation                      | Н  | X     | X   | X    | X      | L    | Х   | Χ              | X   | X   |  |

| 18        | Thermal shutdown protection (TSD) active             | X  | Χ     | X   | Z    | Z      | L    | OFF | OFF            | OFF | OFF |  |

<sup>&</sup>lt;sup>1</sup>X is "don't care," Z is high impedance.

<sup>&</sup>lt;sup>2</sup>The individual overcurrent limitation of each DMOSFET is masked during the delay period. Therefore, ensure proper thermal design for dissipating transient temperature increase caused by current during this period.

<sup>&</sup>lt;sup>3</sup>TSD (thermal shutdown protection starts at 165°C typical, and it is specified by design.

<sup>&</sup>lt;sup>2</sup>"Forward" and "reverse" only indicate opposite relative direction.

# **Switching Operation Timing Charts**

Figure 1. Output Delay Time

Figure 2. Output Switching Time

### **Characteristic Performance**

$T_A = 25$ °C unless otherwise specified

DLY Voltage versus INx Pin Voltage

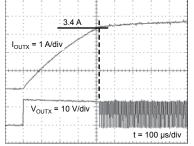

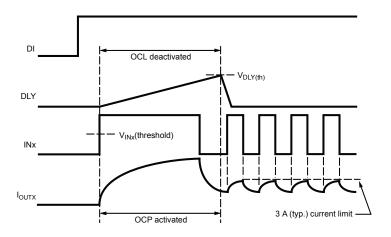

High-side DMOSFET OCL Operation Example

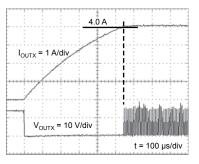

Low-side DMOSFET OCL Operation Example

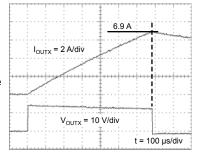

High-side DMOSFET OCP Operation Example

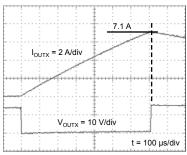

Low-side DMOSFET OCP Operation Example

## **Protection Function Operation**

#### **Current Limitation and Overcurrent Protection**

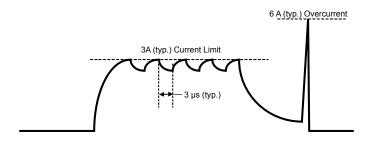

The overcurrent limit is adapted to each DMOSFET, and is activated when the drain current reaches 3 A typical. After that, it is followed by a 3  $\mu$ s typical off-time, and then it restarts automatically.

Overcurrent protection is activated when the drain current reaches 6 A typical within 3  $\mu$ s, as shown in figure 3. It shuts down the IC in a latch mode. Setting the DI pin to logic low level resets the internal logic circuit and releases the latch.

#### **DIAG Pin and Open Load Detection Behavior**

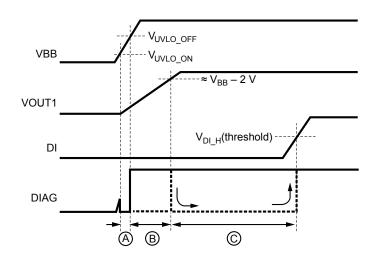

Open load detection does not operate until after the output voltage of OUT1 ( $V_{OUT1}$ ) reaches about  $V_{BB}-2$  V. If an open load is detected, the DIAG signal goes high. The process of open load detection is shown in figure 4:

- A. During this period, UVLO is activated and DIAG stays low.

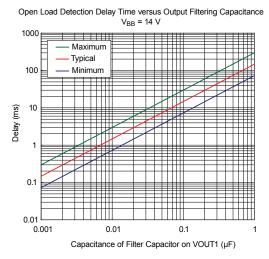

- B. If a filtering capacitor is used at the outputs, it causes a delay of open load detection. (Refer to figure 5 for the relationship of the delay versus the filtering capacitor value.)

- C. The open load detection period starts functioning. Raising DI input above  $V_{DI\_H}$  (threshold), that is, by activating the IC, clears the DIAG signal. Therefore, the open load condition must be checked before the time of that event.

Figure 3. Behavior of Current Limitation and Overcurrent Protection function

Figure 4. Open Load Detection

Figure 5. Delay to Open Load protection activation versus value of external capacitor on the output pins

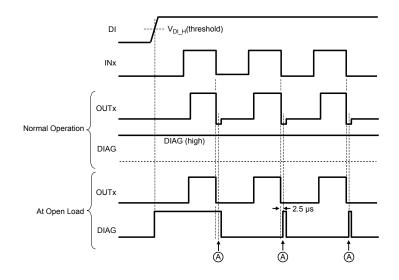

Open load detection during normal operation of the IC is done by checking the negative potential of the output.

Referring to figure 6, during normal operation, recirculation current causes the output to be below GND. The IC checks the output voltage during 2.5  $\mu$ s typical, just after the falling edge of the corresponding IN signal, and if it does not detect the negative potential, DIAG is asserted after the 2.5  $\mu$ s detection period. During the 2.5  $\mu$ s period, the DIAG pin is set to high because the internal circuit is reset during that period (see the arrows marked *A* in figure 6).

Open load detection operates differently during startup of the IC. The overcurrent limitation deactivated period occurs immediately after DI is asserted. Therefore, in order to repeat OCL deactivation, recycle DI.

During this period, overcurrent protection (OCP) is still active. (With regard to OCL delay, see also note 2 to the Electrical Characteristics table.)

Figure 6. Open load detection in normal operation

Figure 7. DLY pin effect at startup

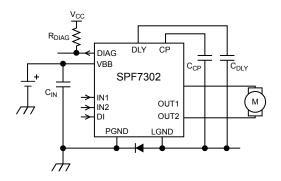

# **Application Information**

Figure 8. Typical application circuit. Recommended components are:

$\begin{array}{cc} C_{CP} & 48 \text{ nF} \\ \\ C_{DLY} & 0.1 \text{ } \mu\text{F} \\ \\ R_{DIAG} & 3.3 \text{ } k\Omega \end{array}$

Figure 9. Recommended Solder Pad Layout, dimensions in mm

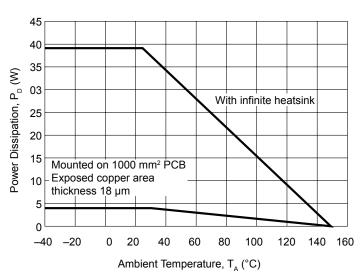

## **Thermal Design**

Figure 10. Power Dissipation Derating Curve

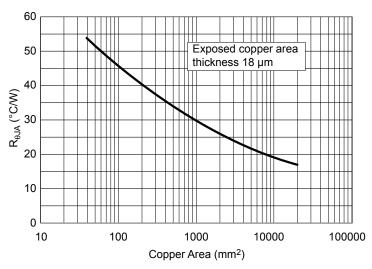

Figure 11. Thermal Resistance versus PCB Copper Area

Figure 12. Test PCB Land Pattern

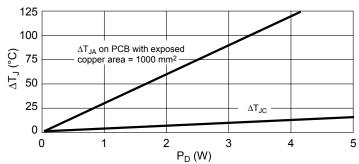

Figure 13. Thermal Performance

Approximate power dissipation,  $P_D$ , in normal operation is calculated by equation 1, and the junction temperature,  $T_J$ , is estimated by equation 2 or 3. Figure 13 shows example data of  $\Delta T_J$  versus  $P_D$ . Note: a final thermal evaluation should be done under actual application conditions, taking into account actual PCB and load conditions.

$$\begin{split} P_D &\approx V_{BB} \times I_{BB1} + \ (V_{satH} + V_{satL}) \times I_{OM} \times D_{ON} \\ &+ (V_{satL(H)} + V_F) \times I_{OM} \times D_{OFF} \end{split} \tag{1}$$

where

V<sub>BB</sub> is the supply voltage (battery voltage),

I<sub>BB1</sub> is the circuit current during operation,

V<sub>satH</sub> is the high-side saturation voltage,

V<sub>satL</sub> is the low-side saturation voltage,

V<sub>F</sub> is the freewheeling diode forward voltage,

I<sub>OM</sub> is the motor current,

D<sub>ON</sub> is the IN1 and IN2 duty cycle (proportion on), and

$D_{OFF}$  is the IN1 and IN2 proportion off ( $D_{ON} + D_{OFF} = 100\%$ ).

To calculate T<sub>I</sub>:

$$T_{J} = R_{\theta JA} \times P_{D} + T_{A} \tag{2}$$

or

$$T_{\rm J} = T_{\rm P} + R_{\rm \theta JC} (3.2^{\circ} \text{C/W}) \times P_{\rm D}$$

(3)

where:

$R_{\theta JA}$  can be obtained from figure 11, and

T<sub>P</sub> is the temperature at the exposed thermal pad of the device.

## Package Outline Drawing, 16 Pin HSOP

Package: HSOP-16

Dimensions in millimeters

Branding codes (exact appearance at manufacturer discretion):

1st line, type: SPF7302 2nd line, lot: YMDD

Where: Y is the last digit of the year of manufacture M is the month (1 to 9, O, N, D)

DD is the date

Because reliability can be affected adversely by improper storage environments and handling methods, please observe the following cautions.

#### **Cautions for Storage**

- Ensure that storage conditions comply with the standard temperature (5°C to 35°C) and the standard relative humidity (around 40% to 75%); avoid storage locations that experience extreme changes in temperature or humidity.

- Avoid locations where dust or harmful gases are present and avoid direct sunlight.

- Reinspect for rust on leads and solderability of the products that have been stored for a long time.

#### **Cautions for Testing and Handling**

When tests are carried out during inspection testing and other standard test periods, protect the products from power surges from the testing device, shorts between the product pins, and wrong connections. Ensure all test parameters are within the ratings specified by Sanken for the products.

#### Soldering

- When soldering the products, please be sure to minimize the working time, and any soldering iron should be kept at a distance from the body of the product.

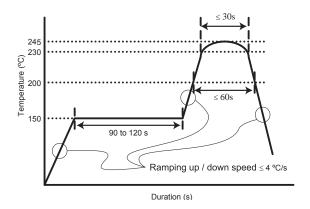

- The number of reflow procedures is restricted to two only. Device reliability and appearance are guaranteed within the temperature profile below, after storage conditions of up to 168 hours at T<sub>A</sub> = 85°C and RH = 85%.

Solder Reflow Profile

### **Electrostatic Discharge**

- When handling the products, the operator must be grounded. Grounded wrist straps worn should have at least 1 M $\Omega$  of resistance from the operator to ground to prevent shock hazard, and it should be placed near the operator.

- Workbenches where the products are handled should be grounded and be provided with conductive table and floor mats

- When using measuring equipment such as a curve tracer, the equipment should be grounded.

- When soldering the products, the head of soldering irons or the solder bath must be grounded in order to prevent leak voltages generated by them from being applied to the products.

- The products should always be stored and transported in Sanken shipping containers or conductive containers, or be wrapped in aluminum foil.

- The contents in this document are subject to changes, for improvement and other purposes, without notice. Make sure that this is the latest revision of the document before use.

- Application and operation examples described in this document are quoted for the sole purpose of reference for the use of the products herein and Sanken can assume no responsibility for any infringement of industrial property rights, intellectual property rights or any other rights of Sanken or any third party which may result from its use.

- Although Sanken undertakes to enhance the quality and reliability of its products, the occurrence of failure and defect of semiconductor products at a certain rate is inevitable. Users of Sanken products are requested to take, at their own risk, preventative measures including safety design of the equipment or systems against any possible injury, death, fires or damages to the society due to device failure or malfunction.

- Sanken products listed in this document are designed and intended for the use as components in general purpose electronic equipment or apparatus (home appliances, office equipment, telecommunication equipment, measuring equipment, etc.).

- When considering the use of Sanken products in the applications where higher reliability is required (transportation equipment and its control systems, traffic signal control systems or equipment, fire/crime alarm systems, various safety devices, etc.), and whenever long life expectancy is required even in general purpose electronic equipment or apparatus, please contact your nearest Sanken sales representative to discuss, prior to the use of the products herein.

- The use of Sanken products without the written consent of Sanken in the applications where extremely high reliability is required (aerospace equipment, nuclear power control systems, life support systems, etc.) is strictly prohibited.

- In the case that you use Sanken products or design your products by using Sanken products, the reliability largely depends on the degree of derating to be made to the rated values. Derating may be interpreted as a case that an operation range is set by derating the load from each rated value or surge voltage or noise is considered for derating in order to assure or improve the reliability. In general, derating factors include electric stresses such as electric voltage, electric current, electric power etc., environmental stresses such as ambient temperature, humidity etc. and thermal stress caused due to self-heating of semiconductor products. For these stresses, instantaneous values, maximum values and minimum values must be taken into consideration.

- In addition, it should be noted that since power devices or IC's including power devices have large self-heating value, the degree of derating of junction temperature affects the reliability significantly.

- When using the products specified herein by either (i) combining other products or materials therewith or (ii) physically, chemically or otherwise processing or treating the products, please duly consider all possible risks that may result from all such uses in advance and proceed therewith at your own responsibility.

- Anti radioactive ray design is not considered for the products listed herein.

- Sanken assumes no responsibility for any troubles, such as dropping products caused during transportation out of Sanken's distribution network.

- The contents in this document must not be transcribed or copied without Sanken's written consent.