### Multi-Output Power Supply with VCOM Amplifier for EPD

### Features

- Single Chip Power Management Solution for Epaper Displays

- Input Supply Voltage Range: 3.0~5.5V

- · I<sup>2</sup>C Series Interface

- Boost Converter for Positive Rail Base (HVINP)

- Inverting Buck-Boost Converter for Negative Rail Base (HVINN)

- Accurate Voltage Tracking between HVINP and HVINN: <u>+</u>50mV

- Integrated Two Power Switches with Soft-start Control for Source Driver Supply

-POS: +15V/120mA

-NEG: -15V/120mA

- Two Charge Pump for Gate Driver Supply

-DGVDD: +22V/20mA

-DGVEE:-22V/20mA

- Accurate and Adjustable VCOM Voltage for Panel Backplane Biasing

-0.3 to -2.85V/100mA, 10mV per step

- -8-bit Control

- Programmable Turn-on/Turn-off Timing in every Output Voltage

- · Remote Temperature Sensing

- POK Output

- · FAULT Output

- Enable Input

- Current Limit Protection

- Over Temperature Protection

- Fault Events Report in Every Output for Easy Debugging

- 1MHz Fixed PWM Frequency

- Up to 85% efficiency for the Boost

- Internal Soft Start Control

- Available in TQFN5x5-32 Package

- Halogen and Lead Free Available (RoHS Compliant)

### **General Description**

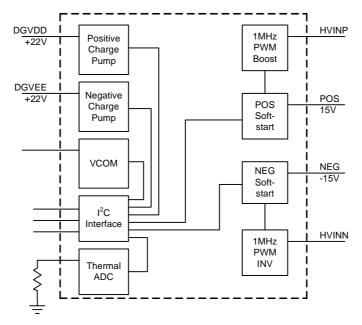

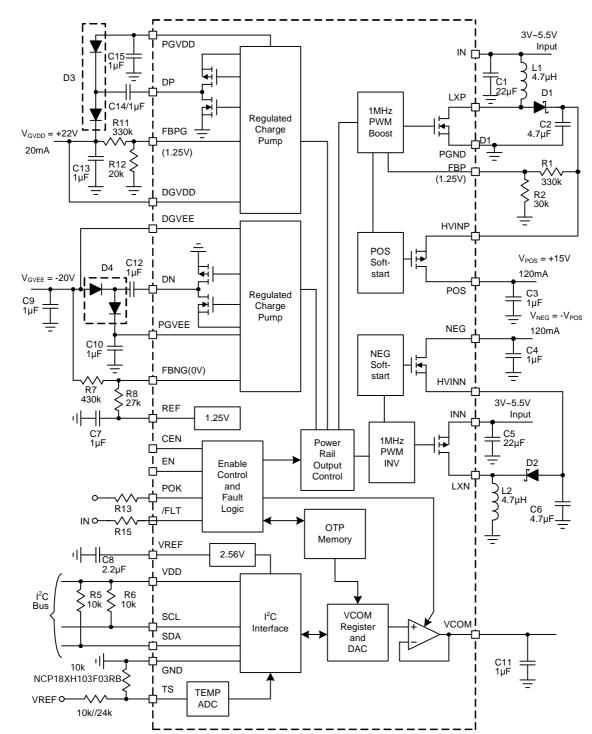

The APW7223 is a single chip, multi outputs PMIC for Epaper displays. Two PWM converters respectively generate positive and negative voltages which are boosted to higher voltage by two charge pumps for both source and gate drivers. Two integrated power switches are used to disconnect these PWM outputs from load in shutdown mode. All PWM and charge pump output voltages are adjustable by external resistors and their power on/off timings can be individually programmable via I<sup>2</sup>C interface. One accurate VCOM voltage, for backplane biasing, is adjustable via I<sup>2</sup>C interface from -0.3V to -2.85V with 10mV per step. The VCOM is capable of sourcing and sinking current, depending on panel condition, at lease 100mA. An external negative temperature coefficient(NTC) resistor is incorporated to sense remote temperature. This remote temperature sensing can be used to monitor the battery's surface temperature to avoid over heating. The temperature data is mapped from the voltage on TS pin according to a preset conversion table. Approximately every 250us the APW7223 executes the voltage/temperature conversion and stores the temperature date in register in two's complement format.

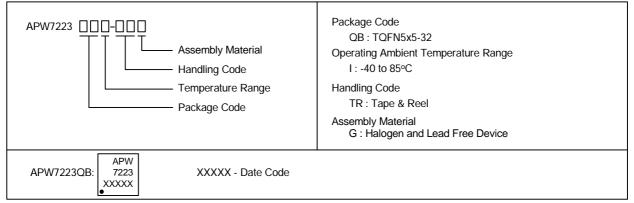

The APW7223 is available in a space saving TQFN5x5 32-pin package and is specified over the -40°C to +85°C extended temperature range.

## Applications

E-paper Displays

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and advise customers to obtain the latest version of relevant information to verify before placing orders.

## **Simplified Application Circuit**

## Ordering and Marking Information

Note: ANPEC lead-free products contain molding compounds/die attach materials and 100% matte tin plate termination finish; which are fully compliant with RoHS. ANPEC lead-free products meet or exceed the lead-free requirements of IPC/JEDEC J-STD-020D for MSL classification at lead-free peak reflow temperature. ANPEC defines "Green" to mean lead-free (RoHS compliant) and halogen free (Br or CI does not exceed 900ppm by weight in homogeneous material and total of Br and CI does not exceed 1500ppm by weight).

# APW7223

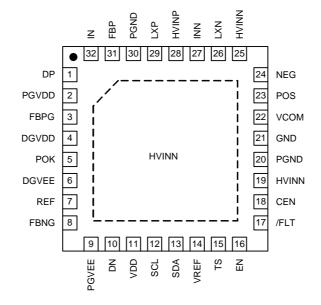

## **Pin Configuration**

### Absolute Maximum Ratings (Note 1)

| Symbol           | Parameter                                                                           | Rating             | Unit |  |

|------------------|-------------------------------------------------------------------------------------|--------------------|------|--|

|                  | IN, INN, CEN, EN, POK, /FLT, FBP, FBPG, FBNG, REF, VDD, SCL, SDA, TS to GND Voltage | -0.3 ~ 6.5         | V    |  |

|                  | VREF to GND Voltage                                                                 | -0.3 ~ 4           | V    |  |

|                  | LXP, HVINP, POS, PGVDD, DP to PGND                                                  | -0.3 ~ 24          | V    |  |

|                  | LXN, HVINN, NEG, PGVEE, DN, PBKG, VCOM to PGND                                      | -24 ~ 0.3          | V    |  |

|                  | DGVDD to PGND                                                                       | -0.3 ~ 40          | V    |  |

|                  | DGVEE to PGND                                                                       | -40 ~ 0.3          | V    |  |

|                  | PGND to GND Voltage                                                                 | -0.3 ~ 0.3         | V    |  |

| PD               | Power Dissipation                                                                   | Internally Limited | W    |  |

|                  | Maximum Junction Temperature                                                        | 150                | °C   |  |

| T <sub>STG</sub> | Storage Temperature                                                                 | -65 ~ 150          | °C   |  |

| T <sub>SDR</sub> | Maximum Lead Soldering Temperature (10 Seconds) 260                                 |                    |      |  |

Note1: Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability

### **Thermal Characteristics**

| Symbol        | Parameter                                           | Typical Value | Unit |

|---------------|-----------------------------------------------------|---------------|------|

| $\theta_{JA}$ | Junction-to-Ambient Resistance in free air (Note 2) | 20            | °C/W |

Note 2:  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air.

### Recommended Operating Conditions (Note 3)

| Symbol         | Parameter                                               | Range                          | Unit |

|----------------|---------------------------------------------------------|--------------------------------|------|

|                | IN, INN, VDD, SCL, SDA, TS to GND Voltage               | -0.3 ~ 5.5                     | V    |

|                | CEN, EN, POK, /FLT, FBP, FBPG, FBNG, REF to GND Voltage | -0.3 ~ V <sub>IN</sub> +0.3    | V    |

|                | LXP, HVINP to PGND Voltage                              | 12 ~ 18                        | V    |

|                | POS, PGVDD, DP to PGND Voltage                          | -0.3 ~ V <sub>HVINP</sub> +0.3 | V    |

|                | LXN, HVINN to PGND Voltage                              | -20 ~ V <sub>IN</sub> +0.3     | V    |

|                | NEG, PGVEE, DN, VCOM, PBKG to PGND Voltage              | -V <sub>HVINN</sub> -0.3 ~ 0.3 | V    |

|                | DGVDD to PGND                                           | -0.3 ~ 30                      | V    |

|                | DGVEE to PGND                                           | -30 ~ 0.3                      | V    |

|                | PGND to GND Voltage                                     | -0.3 ~ 0.3                     | V    |

|                | LXP, LXN, INN, PGND RMS Current                         | -0.3 ~1.6                      | А    |

| T <sub>A</sub> | Ambient Temperature                                     | -40 ~ 85                       | °C   |

| TJ             | Junction Temperature                                    | -40 ~ 125                      | °C   |

Note 3: Refer to the typical application circuit

## **Electrical Characteristics**

Unless otherwise specified, these specifications apply over V\_{\_{\rm IN}}=3.6V and T\_\_ = 25°C.

| Cum h al          | Parameter                  | Test Conditions                     |     | APW7223 |      |        |  |

|-------------------|----------------------------|-------------------------------------|-----|---------|------|--------|--|

| Symbol            | Parameter                  | Test Conditions                     | Min | Тур     | Max  | – Unit |  |

| INPUT S           | SUPPLY and REFERENCE VOLTA | GE                                  |     |         |      | 1      |  |

| VIN               | Input Voltage Range        |                                     | 3   | -       | 5.5  | V      |  |

|                   | IN UVLO Threshold          |                                     | 2.5 | 2.8     | 2.95 | V      |  |

|                   | IN UVLO Hysteresis         |                                     | -   | 0.15    | -    | V      |  |

| I <sub>DD1</sub>  | IN Quiescent Current       | EN=GND and the Shutdown bit=0       | -   | 40      | 60   | μA     |  |

| I <sub>D D2</sub> |                            | V <sub>EN</sub> =3.6V, No Switching | -   | 2       | 3.5  | mA     |  |

|                   | VDD Input Voltage          |                                     | 1.6 | -       | 5.5  | V      |  |

|                   | VDD UVLO Threshold         | V <sub>VDD</sub> rising             | 1.0 | 1.2     | 1.5  | V      |  |

|                   | VDD UVLO Hysteresis        |                                     | -   | 50      | -    | mV     |  |

|                   | VDD Quiescent Current      | Normal Mode                         | -   | 20      | 50   | μA     |  |

|                   | REF Output Voltage         | No Load                             | -   | 1.250   | -    | V      |  |

|                   | REFUVLO Threshold          | REF Rising                          | -   | 1.0     | 1.2  | V      |  |

|                   | REFUVLO Threshold          |                                     | -   | 50      | -    | mV     |  |

Unless otherwise specified, these specifications apply over V<sub>IN</sub>=3.6V and T<sub>A</sub>= 25°C.

| 0                  | Bananatan                                             | Test Oser litteres                  |                 | APW7223 |       |      |

|--------------------|-------------------------------------------------------|-------------------------------------|-----------------|---------|-------|------|

| Symbol             |                                                       |                                     | Min             | Тур     | Мах   | Unit |

| INPUT              | SUPPLY and REFERENCE VOLT                             | AGE                                 |                 |         |       |      |

|                    | VDD Quiescent Current                                 | Normal Mode                         | -               | 20      | 50    | μΑ   |

|                    | REF Output Voltage                                    | No Load                             | -               | 1.250   | -     | V    |

|                    | REF UVLO Threshold                                    | REF Rising                          | -               | 1.0     | 1.2   | V    |

|                    | REF UVLO Threshold                                    |                                     | -               | 50      | -     | mV   |

|                    | REFOK High Threshold                                  | REF rising                          | -               | 1.5     | -     | V    |

|                    | REFOK Low Threshold                                   | REF falling                         | -               | 1.1     | -     | V    |

|                    | REF Load Regulation                                   | 0 < I <sub>REF</sub> < 100μA        | -               | 10      | 20    | mV   |

|                    | REF Line Regulation                                   | 3V < V <sub>IN</sub> < 5.5V         | -               | 2       | 5     | mV   |

|                    | VREF Output Voltage                                   | No Load (10mV/step)                 | 2.51            | 2.56    | 2.61  | V    |

|                    | VREF Output Current                                   |                                     | 5               | -       | -     | mA   |

| STEP-U             | IP REGULATOR                                          | •                                   |                 |         |       |      |

| $V_{\text{HVINP}}$ | Output Voltage Range                                  |                                     | V <sub>IN</sub> | -       | 18    | V    |

|                    | Operating Frequency                                   |                                     | 850             | 1000    | 1150  | kHz  |

|                    | Oscillator Maximum Duty Cycle                         |                                     | 91              | 95      | 98    | %    |

|                    | FBP Regulation Voltage                                |                                     | 1.238           | 1.250   | 1.262 | V    |

|                    | FBP Load Regulation                                   | 1mA < I <sub>POS</sub> < 200mA      | -               | -1      | -     | %    |

|                    | FBP Line Regulation                                   | $V_{IN} = 3V$ to 5.5V               | -0.3            | -0.08   | 0.3   | %/V  |

|                    | FBP Input Bias Current                                | V <sub>FBP</sub> =1.25V             | -               | -       | 100   | nA   |

|                    | LXP On Resistance                                     | I <sub>LXP</sub> = 0.2A             | -               | 250     | 500   | mΩ   |

|                    | LXP Leakage Current                                   | EN=GND, V <sub>LXP</sub> = 18V      | -               | -       | 20    | μA   |

|                    | LXP Current Limit                                     | Duty Cycle = 80%                    | 1.5             | 1.8     | -     | А    |

|                    | Soft-Start Period                                     |                                     | -               | 680     | -     | μs   |

| INVERT             | ING REGULATOR                                         | ·                                   |                 |         |       |      |

|                    | INN Input Voltage Range                               |                                     | 3               | -       | 5.5   | V    |

|                    | INN Outcocont Current                                 | No Switching                        | -               | 80      | -     | μA   |

|                    | INN Quiescent Current                                 | Switching                           | -               | 0.5     | -     | mA   |

| $V_{\text{HVINN}}$ | Output Voltage Range                                  |                                     | -18             | -       | -     | V    |

|                    | Operating Frequency                                   |                                     | 850             | 1000    | 1150  | kHz  |

|                    | Oscillator Maximum Duty Cycle                         |                                     | 91              | 95      | 98    | %    |

|                    | LXN On-Resistance                                     | INN to LXN, I <sub>LXN</sub> = 0.2A | -               | 250     | -     | mΩ   |

|                    | LXN Leakage Current                                   | IN=3.6V, LXN= -18V                  | -               | -       | 20    | μA   |

|                    | LXN Current Limit                                     | Duty Cycle = 80%                    | 1.8             | 2.1     | -     | Α    |

|                    | Soft-Start Current Limit                              |                                     | -               | 500     | -     | mA   |

|                    | V <sub>POS</sub> -V <sub>NEG</sub> Regulation Voltage |                                     | -50             | -       | 50    | mV   |

Unless otherwise specified, these specifications apply over V<sub>IN</sub>=3.6V and T<sub>A</sub>= 25°C.

| Sumbol           | Deremeter                  | Test Conditions                          |                    | APW7223 |       |      |

|------------------|----------------------------|------------------------------------------|--------------------|---------|-------|------|

| Symbol           | Parameter                  | Test Conditions                          | Min                | Тур     | Max   | Unit |

| POSITI           | VE CHARGE PUMP REGULATO    | R                                        |                    |         |       |      |

|                  | HVINP-DP Current Limit     |                                          | 200                | 300     | -     | mA   |

|                  | Oscillator Frequency       |                                          | 400                | 500     | 600   | kHz  |

|                  | FBPG Regulation Voltage    |                                          | 1.238              | 1.250   | 1.262 | V    |

|                  | FBPG Line Regulation       | V <sub>HVINP</sub> =12V to 18V           | -                  | 0.05    | 0.2   | %/V  |

|                  | FBPG Input Bias Current    | V <sub>FBPG</sub> = 1.25V                | -50                | -       | 50    | nA   |

|                  | DP On-Resistance High      | I <sub>DP</sub> = 100mA                  | -                  | 20      | -     | Ω    |

|                  | DP On-Resistance Low       | I <sub>DP</sub> = -100mA                 | -                  | 24      | -     | Ω    |

|                  | Soft-Start Period          |                                          | -                  | 2.5     | -     | ms   |

| NEGAT            | VE CHARGE PUMP REGULATO    | DR                                       |                    |         |       |      |

|                  | HVINN-DN Current Limit     |                                          | 200                | 300     | -     | mA   |

|                  | Oscillator Frequency       |                                          | 400                | 500     | 600   | kHz  |

|                  | FBNG Regulation Voltage    |                                          | -12                | 0       | 12    | mV   |

|                  | FBNG Line Regulation       | V <sub>NEG</sub> = -12V to -18V          | -                  | 0.05    | 0.2   | %/V  |

|                  | FBNG Input Bias Current    | V <sub>FBNG</sub> = 0V                   | -50                | -       | 50    | nA   |

|                  | DN On-Resistance High      | I <sub>DN</sub> = 100mA                  | -                  | 20      | -     | Ω    |

|                  | DN On-Resistance Low       | I <sub>DP</sub> = -100mA                 | -                  | 12      | -     | Ω    |

|                  | Soft-Start Period          |                                          | -                  | 2       | -     | ms   |

| VCOM             |                            |                                          |                    |         |       |      |

|                  | Input Supply Range         |                                          | V <sub>HVINN</sub> | -       | -5    | V    |

|                  | HVINN Quiescent Current    |                                          | -                  | 0.6     | 5     | mA   |

|                  | VCOMP Voltage High         | I <sub>VCOM</sub> = 5mA                  | -                  | -       | -0.3  | V    |

|                  | VCOMP Voltage Low          | I <sub>VCOM</sub> = -5mA                 | -2.85              | -       | -     | V    |

|                  |                            | Sourcing                                 | 100                | -       | -     | mA   |

|                  | VCOM Output Current        | Sinking                                  | 100                | -       | -     | mA   |

|                  | VCOM Tri-State Leakage     | CEN=GND                                  | -                  | -       | 1     | μA   |

| SEQUE            | NCE SWITCHES               |                                          |                    |         |       |      |

| VPOS             | POS Output Range           | Tracks HVINP                             | V <sub>IN</sub>    | -       | 18    | V    |

|                  | POS On-Resistance          | (HVINP-POS), I <sub>POS</sub> = 100mA    | -                  | 0.5     | 1     | Ω    |

|                  | POS Discharge Resistance   |                                          | -                  | 200     | -     | Ω    |

|                  | POS Soft-Start Charge Time |                                          | -                  | 2       | -     | ms   |

| V <sub>NEG</sub> | NEG Output Range           | Tracks HVINN                             | -18                | -       | -     | V    |

|                  | NEG On-Resistance          | (HVINN-NEG), I <sub>NEG</sub> = 100mA    | -                  | 0.5     | 1     | Ω    |

|                  | NEG Discharge Resistance   |                                          | -                  | 150     | -     | Ω    |

|                  | NEG Soft-Start Charge Time |                                          | -                  | 2       | -     | ms   |

|                  | PGVDD On-Resistance        | (HVINP-PGVDD), I <sub>PGVDD</sub> = 30mA | -                  | 20      | -     | Ω    |

|                  | PGVEE On-Resistance        | (HVINN-PGVEE), I <sub>PGVEE</sub> = 30mA |                    | 10      | -     | Ω    |

Unless otherwise specified, these specifications apply over V<sub>IN</sub>=3.6V and T<sub>A</sub>= 25°C.

| Symbol | Parameter                               | Test Conditions            |                               | APW7223                      |                              |             |

|--------|-----------------------------------------|----------------------------|-------------------------------|------------------------------|------------------------------|-------------|

| Symbol | Parameter                               | Test Conditions            | Min                           | Тур                          | Max                          | Unit        |

| SEQUE  | NCE SWITCHES                            |                            |                               |                              |                              |             |

|        | DGVDD Input Voltage Range               |                            | -                             | -                            | 30                           | V           |

|        | DGVDD Discharge Resistance              |                            | -                             | 100                          | -                            | Ω           |

|        | DGVEE Input Voltage Range               |                            | -30                           | -                            | 0                            | V           |

|        | DGVEE Discharge Resistance              |                            | -                             | 150                          | -                            | Ω           |

|        | VCOM Discharge Resistance               |                            | -                             | 1000                         | -                            | Ω           |

| FAULT  | PROTECTION                              |                            |                               |                              |                              |             |

|        | FBP Fault Threshold                     | V <sub>FBP</sub> Falling   | 0.94                          | 1.00                         | 1.05                         | V           |

|        | FBPG Fault Threshold                    | V <sub>FBPG</sub> Falling  | 0.94                          | 1.00                         | 1.05                         | V           |

|        | HVINN Fault Threshold                   | V <sub>HVINN</sub> Rising  | - V <sub>HVINP</sub><br>*0.85 | -V <sub>HVINP</sub><br>*0.80 | -V <sub>HVINP</sub><br>*0.75 | mV          |

|        | FBNG Fault Threshold                    | V <sub>FBNG</sub> Falling  | 200                           | 250                          | 330                          | mV          |

|        | Fault Debounce                          |                            | -                             | 250                          | -                            | μs          |

|        | Thermal Shutdown                        | Hysteresis = 30°C          | -                             | 160                          | -                            | °C          |

| TEMPE  | RATURE SENSOR                           |                            |                               |                              | •                            |             |

|        | Tama antur Das shufa s                  | Monotonicity guaranteed    | 10                            | -                            | -                            | Bits        |

|        | Temperature Resolution                  | LSB                        | -                             | 0.5                          | -                            | °C          |

|        | Conversion Time                         |                            | -                             | 19                           | -                            | μs          |

|        | Conversion Rate                         | CONF: D7=D6=0              | -                             | 250                          | -                            | Conv<br>/μs |

| PROGR  | AMMABLE VCOM CALIBRATOR                 |                            |                               |                              |                              |             |

|        | VCOM-DAC Voltage Resolution             |                            | 8                             | -                            | -                            | Bits        |

|        | VCOM-DAC Differential<br>Non linea rity | Monotonic over temperature | -1                            | -                            | +1                           | LSB         |

|        | VCOM-DAC Zero-Scale Error               |                            | 0                             | +1                           | +2                           | LSB         |

|        | VCOM-DAC Full-Scale Error               |                            | -4                            | -                            | +4                           | LSB         |

|        | Memory Factory Setting                  |                            | -                             | 80                           | -                            | Hex         |

|        | Memory Program Voltage                  | Supply to /FLT pin         | 7.00                          | 7.15                         | 7.3                          | V           |

|        | Memory Write Cycles                     |                            | 8                             | -                            | -                            | times       |

|        | Memory Write Time                       | Need to confirm            | TBD                           | -                            | -                            | ms          |

| CONTR  | OL LOGIC                                |                            | _                             |                              |                              |             |

|        | Input Low Voltage (IN)                  | EN, CEN                    | -                             | -                            | 0.4                          | V           |

|        | Input High Voltage (IN)                 | EN, CEN                    | 1.2                           | -                            | -                            | V           |

|        | POK Logic-Low Output Voltage            | I <sub>POK</sub> = -6mA    | -                             | -                            | 0.4                          | V           |

|        | /FLT Leakage Current                    | V <sub>FLT</sub> = 5.5V    | -                             | -                            | 1                            | μA          |

|        | /FLT Output Low Voltage                 | I <sub>FLT</sub> = 6mA     | -                             | -                            | 0.4                          | V           |

7

Unless otherwise specified, these specifications apply over V\_{IN}=3.6V and T\_A= 25^{\circ}C.

| Symbol                | Devenueter                  | Test Conditions                                                                                  | APW7223                    |     |                  |      |

|-----------------------|-----------------------------|--------------------------------------------------------------------------------------------------|----------------------------|-----|------------------|------|

| Symbol                | Parameter                   | Test Conditions                                                                                  | Min                        | Тур | Max              | Unit |

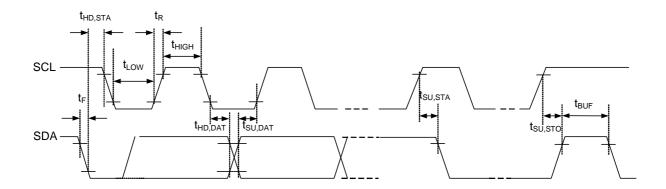

| I <sup>2</sup> C INTE | ERFACE                      | •                                                                                                |                            |     |                  |      |

|                       | Input Capacitance           | SDA, SCL                                                                                         | -                          | 5   | -                | pF   |

| VIL                   | Input Low Voltage           | SDA, SCL                                                                                         | -                          | -   | $0.3^{*}V_{VDD}$ | V    |

| VIH                   | Input High Voltage          | SDA, SCL                                                                                         | $0.7^*V_{VDD}$             | -   | -                | V    |

|                       | SDA Sink Current            | $V_{SDA} = 0.4V$                                                                                 | 6                          | -   | -                | mA   |

| $F_{SCL}$             | SCL Frequency               |                                                                                                  | DC                         | -   | 400              | kHz  |

| t <sub>HIGH</sub>     | SCL High Time               |                                                                                                  | 600                        | -   | -                | ns   |

| $\mathbf{t}_{LOW}$    | SCL Low Time                | SCL Low Time                                                                                     |                            | -   | -                | ns   |

| t <sub>R</sub>        | SDA, SCL Rise Time          | Time $C_{BUS} = Total Bus Line Capacitance (pF)$ $\begin{array}{c} 20+\\ 10xC_{BUS} \end{array}$ |                            | -   | 300              | ns   |

| t <sub>F</sub>        | SDA, SCL Fall Time          | C <sub>BUS</sub> = Total Bus Line Capacitance (pF)                                               | 20+<br>10xC <sub>BUS</sub> | -   | 300              | Ns   |

| $t_{\text{HD:STA}}$   | START Hold Time             | 10% of SDA to 90% of SCL                                                                         | 600                        | -   | -                | ns   |

| t <sub>su:sta</sub>   | START Setup Time            |                                                                                                  | 600                        | -   | -                | ns   |

| t <sub>HD:DAT</sub>   | Data Input Hold Time        |                                                                                                  | 0                          | -   | -                | ns   |

| t <sub>SU:DAT</sub>   | Data Input Setup Time       |                                                                                                  | 100                        | -   | -                | ns   |

| t <sub>su:sto</sub>   | STOP Setup Time             |                                                                                                  | 600                        | -   | -                | ns   |

| t <sub>BUF</sub>      | Bus Free Time               |                                                                                                  | 1300                       | -   | -                | ns   |

|                       | Input Spike Suppression     | SDA, SCL                                                                                         | -                          | -   | 50               | ns   |

| t <sub>TIMEOUT</sub>  | SDA Reset Low Time (note 5) |                                                                                                  | -                          | -   | 50               | ms   |

Note 4: Guaranteed by design, not production tested.

Note 5: Holding the SDA line low for a time greater than t<sub>TIMEOUT</sub> causes the device to reset SDA to the IDLE state of the serial bus communication (SDA set high).

# APW7223

# **Pin Description**

| PI             | N     |                                                                                                                      |  |  |  |

|----------------|-------|----------------------------------------------------------------------------------------------------------------------|--|--|--|

| NO.            | NAME  | Function                                                                                                             |  |  |  |

| 1              | DP    | Regulated charge pump driver for GVDD. Connect to flying cap.                                                        |  |  |  |

| 2              | PGVDD | Supplies the HVINP voltage for the positive charge pump. Connect as shown in Figure 1.                               |  |  |  |

| 3              | FBPG  | Feedback input for GVDD. Threshold = 1.25V.                                                                          |  |  |  |

| 4              | DGVDD | Connect the output of the positive charge pump to DGVDD as shown in Figure 1.                                        |  |  |  |

| 5              | POK   | Power OK. Open drain output that goes low when all outputs have reached regulation.                                  |  |  |  |

| 6              | DGVEE | Connect the output of the negative charge pump to DGVEE as shown in Figure 1.                                        |  |  |  |

| 7              | REF   | IC voltage reference. 1.25V. Connect an 1µF cap to this pin.                                                         |  |  |  |

| 8              | FBNG  | Feedback input for GVEE. Threshold = 0V.                                                                             |  |  |  |

| 9              | PGVEE | Supplies the HVINN voltage to the negative charge pump for the GVEE output. Connect as shown in Figure 1.            |  |  |  |

| 10             | DN    | Regulated charge pump driver for GVEE. Connect to flying cap.                                                        |  |  |  |

| 11             | VDD   | Logic supply input for the $I^2C$ . Bypass to GND through a minimum 0.1µF capacitor.                                 |  |  |  |

| 12             | SCL   | I <sup>2</sup> C Serial clock input.                                                                                 |  |  |  |

| 13             | SDA   | I <sup>2</sup> C Serial data input/output.                                                                           |  |  |  |

| 14             | VREF  | Filter pin for 2.5V Internal reference to ADC.                                                                       |  |  |  |

| 15             | TS    | Thermistor input pin. Connect a 10k NTC thermistor and a $7k\Omega$ linearization resistor between this pin and GND. |  |  |  |

| 16             | EN    | Enable pin. Logic high initiates power-up sequencing. Logic low initiates power down sequencing.                     |  |  |  |

| 17             | /FLT  | Fault Indicator. Open drain output goes low during a fault condition.                                                |  |  |  |

| 18             | CEN   | VCOM Enable. Logic high enables VCOM output. Logic low causes the load on the VCOM output to be discharged           |  |  |  |

| 19             | HVINN | Input power for the NEG voltage rail. Connect the output of the inverting converter to this pin.                     |  |  |  |

| 20             | PGND  | Power Ground.                                                                                                        |  |  |  |

| 21             | GND   | Analog Ground. Connected this pin PGND.                                                                              |  |  |  |

| 22             | VCOM  | VCOM output.                                                                                                         |  |  |  |

| 23             | POS   | Positive Source Driver Output Voltage.                                                                               |  |  |  |

| 24             | NEG   | Negative Source Driver Output Voltage.                                                                               |  |  |  |

| 25             | HVINN | Input power for the NEG voltage rail. Connect the output of the inverting converter to this pin.                     |  |  |  |

| 26             | LXN   | DC-DC inverting converter inductor/diode connection.                                                                 |  |  |  |

| 27             | INN   | Inverting converter power input. 3V to 5.5V.                                                                         |  |  |  |

| 28             | HVINP | Input power for the POS voltage rail. Connect the output of the Step-up converter to this pin.                       |  |  |  |

| 29             | LXP   | Step-up converter inductor/diode connection.                                                                         |  |  |  |

| 30             | PGND  | Power Ground.                                                                                                        |  |  |  |

| 31             | FBP   | Feedback pin for HVINP output. Threshold = 1.25V                                                                     |  |  |  |

| 32             | IN    | IC power input.                                                                                                      |  |  |  |

| Exposed<br>Pad |       | Die substrate/thermal pad. Connected this pad to HVINN.                                                              |  |  |  |

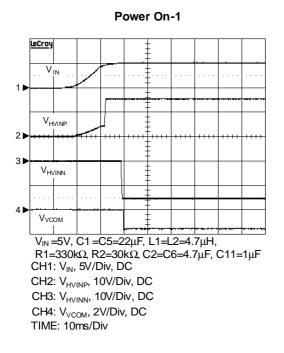

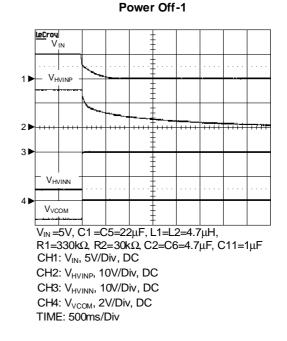

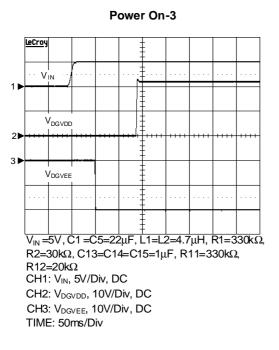

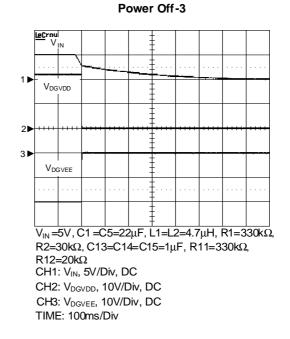

### **Operating Waveforms**

The test condition is  $V_{IN}$ =5V,  $T_A$ = 25°C unless otherwise specified.

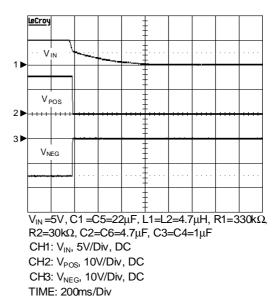

#### Power Off-2

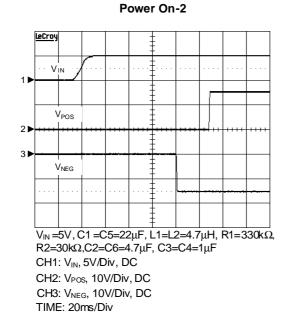

### **Operating Waveforms**

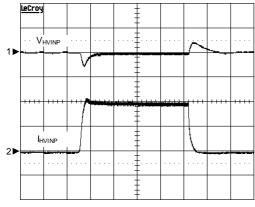

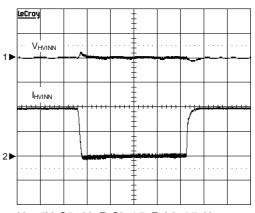

The test condition is  $V_{IN}$ =5V,  $T_A$ = 25°C unless otherwise specified.

#### Load Transient-2

Load Transient-1

$\begin{array}{l} {\sf V}_{\sf IN} \!=\! \! 5{\sf V}, \, C1 \!=\! 22\mu{\sf F}, \, C2 \!=\! 4.7\mu{\sf F}, \, L1 \!=\! 4.7\mu{\sf H}, \\ {\sf R1} \!=\! 330 k\Omega, \, {\sf R2} \!=\! 30 k\Omega, \, {\sf I}_{\sf H \! \lor \! INP} \!\!=\! 0mA \!\!-\! 200 mA \!\!-\! 0mA \!\!-$

$\label{eq:VIN} \begin{array}{l} V_{\text{IN}} \!=\!\! 5V, \, C5 \!=\! 22 \mu F, \, C6 \!=\!\! 4.7 \mu F, \, L2 \!=\!\! 4.7 \mu H, \\ I_{\text{HVINN}} \!\!=\!\! 0mA \!\!-\! 200mA \!\!-\! 0mA \end{array}$

CH1: V<sub>HVINN</sub>, 1V/Div, offset=-15V CH2: I<sub>HVINP</sub>, 100mA/Div, DC TIME: 200µs/Div

### **Block Diagram and Typical Application Circuit**

Note : Forced 3.3V to VREF pin for  $\rm V_{\rm COM}$  : -0.3V to -3.59V

Copyright © ANPEC Electronics Corp. Rev. A.2 - May., 2016

# APW7223

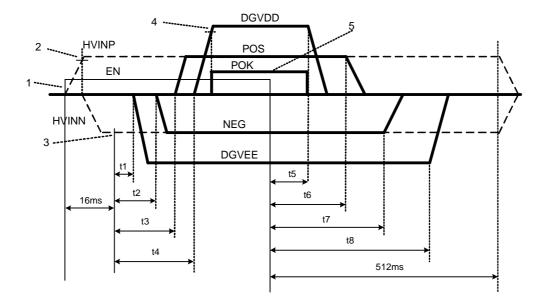

### **Power Sequence**

Pulling the EN pin high initiates an adjustable pre-set power-up sequence while pulling the EN pin low initiates an adjustable pre-set power-down sequence. The power-up/power-down sequence and timing between rails are determined by the user's values programmed into the Timing Registers via l<sup>2</sup>C before the EN pin is pulled high/low. The desired sequence and timing between rails contained in the Timing Registers can also be stored in the MTP, such that desired timing information is loaded into the Timing Registers at power-up.

Figure 2 shows a sample power-up and power-down sequence. The sequence and timing between the power rails for both power-up and power-down are accomplished by programming the desired t1-t8 times into the Timing Registers and/or storing the desired t1-t8 times into the MTP.

1. The HVINP power rail begins its soft-start sequence once EN is driven high.

2. The HVINN power rails begin its soft-start sequence once HVINP soft-start period has expired.

3. Each power rail will begin to power-up at a time depending on the values stored in the timing registers(t1-t4).

4. POK is asserted high after FBNG, NEG, POS and FBPG have all exceeded 80% of their regulation voltages and all the corresponding power rails' soft-start periods have expired.

5. Once EN goes low, each power rail is actively discharged at a time depending on the values stored in the timing registers (t5-t8). Approximately 512 ms after EN is driven low, HVINP and HVINN are powered down but not actively discharged.

### **Function Description**

#### Main Control Loop

The APW7223 is a single chip power supplies designed to for portable e-paper displays applications. Two high efficiency DC/DC boost converters generate +/-15V rails which are boosted to +/- 22V by two change pumps to provide the gate driver supply panel. Two tracking LDOs create the +/-15V source driver supplies which support up to 120mA of output current. All rails are adjustable through the I<sup>2</sup>C interface to accommodate specific panel requirements.

#### **Under-Voltage Lockout**

An under-voltage lockout function prevents the device from operating if the input voltage on  $V_{\rm IN}$  is lower than approximately 2.8V. The device automatically enters the shutdown mode if the voltage on  $V_{\rm IN}$  drops below approximately 2.65V. This under-voltage lockout function is implemented in order to prevent the malfunctioning of the converter.

#### VCOM

Accurate back-plane biasing is provided by a linear amplifier and can be adjusted either by the I<sup>2</sup>C interface. The VCOM driver can source or sink current depending on panel condition.

For automatic VCOM adjustment in production line, VCOM can be set from -0.3V to -2.85V with 8 bits control through the serial interface. The power switch is integrated to isolate VCOM driver.

#### Soft-start

The APW7223 has a built-in soft-start to control the output voltage rise during start-up. During soft-start, an internal ramp voltage, connected to the one of the positive inputs of the error amplifier, raises up to replace the reference voltage (1.25V typical) until the ramp voltage reaches the reference voltage. Then the voltage on FBx regulated at reference voltage.

#### Pulse Skipping Modulation Mode (PSM)

The APW7223 is a fixed frequency PWM peak current mode control step-down converter. At light loads, the APW7223 will automatically enter in pulse skipping mode operation to reduce the dominant switching losses. These controls get low quiescent current, help to maintain high efficiency over the complete load range.

#### **Over-Temperature Protection (OTP)**

The over-temperature circuit limits the junction temperature of the APW7223. When the junction temperature exceeds 160°C, a thermal sensor turns off the both power MOSFETs, allowing the devices to cool. The thermal sensor allows the converters to start a soft-start process and regulate the output voltage again after the junction temperature cools by 30°C. The OTP designed with a 30°C hysteresis lowers the average Junction Temperature (T<sub>\_</sub>) during continuous thermal overload conditions, increasing the life time of the device.

#### **Temperature Sensor**

The APW7223 allows the user to take full control of the temperature sensing circuit at the expense of additional I<sup>2</sup>C read/writes and associated software over-head in the main processor. It is designed for use with host processors that can read and write to multiple registers using standard I<sup>2</sup>C protocol.

#### **Fault Protection**

The under-voltage protection circuit monitors the voltage on FBx ( $V_{FBx}$ ) by Under-Voltage (UV) comparator to protect the PWM converter against short-circuit conditions. When the  $V_{FBx}$  falls below the falling UVP threshold (20% of REF), a fault signal is generated and the device turns off all MOSFETs. The converter shuts down and the output is latched to be floating. The APW7223 will initials a soft-start process until re-cycle EN or  $V_{IN}$ .

# Function Description (Cont.)

#### Load Disconnected

The APW7223 completely disconnects the loads from the input when in shutdown mode. In most boost converters the external rectifying diode and inductor form a DC current path from the battery to the output. This can drain the battery even in shutdown if a load were connected at the boost converter output. The APW7223 integrated 4 isolated switch at POS/NEG/PGVDD/PGVEE. When these switches turn off during shutdown there is no DC path from the input to POS/NEG/PGVDD/PGVEE.

### **Application Information**

#### Input Capacitor Selection

Because buck converters have a pulsating input current, a low ESR input capacitor is required. This results in the best input voltage filtering, minimizing the interference with other circuits caused by high input voltage spikes. Also, the input capacitor must be sufficiently large to stabilize the input voltage during heavy load transients. For good input voltage filtering, usually a  $4.7\mu$ F input capacitor is sufficient. It can be increased without any limit for better input-voltage filtering. Ceramic capacitors show better performance because of the low ESR value, and they are less sensitive against voltage transients and spikes compared to tantalum capacitors. Place the input capacitor as close as possible to the input and GND pin of the device for better performance.

#### **Inductor Selection**

For high efficiencies, the inductor should have a low dc resistance to minimize conduction losses. Especially at high-switching frequencies the core material has a higher impact on efficiency. When using small chip inductors, the efficiency is reduced mainly due to higher inductor core losses. This needs to be considered when selecting the appropriate inductor. The inductor value determines the inductor ripple current. The larger the inductor value, the smaller the inductor ripple current and the lower the conduction losses of the converter. Conversely, larger inductor values cause a slower load transient response. A reasonable starting point for setting ripple current,  $\Delta IL$ , is 40% of maximum output current. The recommended inductor value can be calculated as below:

$$L \geq \frac{V_{OUT} \left(1 - \frac{V_{OUT}}{V_{IN}}\right)}{F_{SW} \cdot \Delta I_{L}}$$

$I_{L(MAX)} = I_{OUT(MAX)} + 1/2 \times \Delta IL$

To avoid saturation of the inductor, the inductor should be rated at least for the maximum output current of the converter plus the inductor ripple current.

#### **Output Voltage Setting**

In the adjustable version, the output voltage is set by a resistive divider. The external resistive divider is connected to the output, allowing remote voltage sensing as shown in "Typical Application Circuits". A suggestion of maximum value of R2 is  $400k\Omega$  to keep the minimum current that provides enough noise rejection ability through the resistor divider. The output voltage can be calculated as below:

$$V_{OUT} = V_{REF} \cdot \left(1 + \frac{R1}{R2}\right) = 1.25 \cdot \left(1 + \frac{R1}{R2}\right)$$

#### **Output Capacitor Selection**

The current-mode control scheme of the APW7223 allows the use of tiny ceramic capacitors. The higher capacitor value provides the good load transients response. Ceramic capacitors with low ESR values have the lowest output voltage ripple and are recommended. When choosing the input and output ceramic capacitors, choose the X5R or X7R dielectric formulations. These dielectrics have the best temperature and voltage characteristics of all the ceramics for a given value and size.

Copyright © ANPEC Electronics Corp. Rev. A.2 - May., 2016

# APW7223

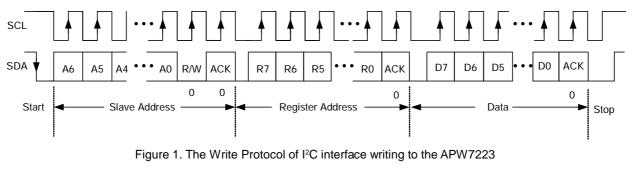

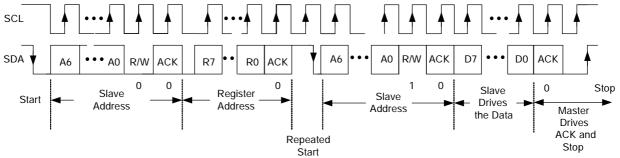

## I<sup>2</sup>C Programming

The APW7223's I<sup>2</sup>C Slave Address is a hard-coded 7 bit address 90h(1001000). The APW7223 supports the following write and read protocol and contains 17 registers.

Figure 2. The Read Protocol of I<sup>2</sup>C interface reading from the APW7223

# **Register Address Map**

| Register | Register (Hex) R/W |           | Name                                 | Power On Default |

|----------|--------------------|-----------|--------------------------------------|------------------|

| 1        | 00                 | Read only | External Temperature Register        | N/A              |

| 2        | 01                 | R/W       | Temperature Offset (for calibration) | 00h              |

| 3        | 02                 | R/W       | Configuration Register               | N/A              |

| 4        | 03                 | R/W       | Enable Register                      | 00               |

| 5        | 04                 | R/W       | VCOM_ADJUST                          | 80h              |

| 6        | 05                 | Read only | Fault Register                       | N/A              |

| 7        | 06                 | R/W       | Programming Control Register         | 00h              |

| 8        | 07                 | R/W       | t1 Timing Register                   | 1Eh              |

| 9        | 08                 | R/W       | t2 Timing Register                   | 3Ch              |

| 10       | 09                 | R/W       | t3 Timing Register                   | 5Ah              |

| 11       | 0A                 | R/W       | t4 Timing Register                   | 78h              |

| 12       | 0B                 | R/W       | t5 Timing Register                   | 1Eh              |

| 13       | 0C                 | R/W       | t6 Timing Register                   | 3Ch              |

| 14       | 0D                 | R/W       | t7 Timing Register                   | 5Ah              |

| 15       | 0E                 | R/W       | t8 Timing Register                   | 78h              |

| 16       | 0F                 | Read only | Product Revision ID                  | 00h              |

| 17       | 10                 | Read only | Product ID                           | 4Dh              |

# **Register Definition**

#### Register Address: 00h

| Field Name       |      | External Temperature[7 |     |     |     | [7:0] |     |     |

|------------------|------|------------------------|-----|-----|-----|-------|-----|-----|

| Data Bit D7      |      | D6                     | D5  | D4  | D3  | D2    | D1  | D0  |

| Bit Name         | Sign | Temperature Data       |     |     |     |       |     |     |

| Read/Write R/W   |      | R/W                    | R/W | R/W | R/W | R/W   | R/W | R/W |

| Power On Default |      |                        |     |     |     |       |     |     |

| Field Name               | Bit Definition                                                                                                                                                                                                  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | Temperature readout:<br>1000 0001: -127°C                                                                                                                                                                       |

| ExternalTemperature[7:0] | <br>1111 1110: -2°C<br>1111 1111: -1°C<br>0000 0000: 0°C<br>0000 0001: +1°C<br>0000 0010: +2°C                                                                                                                  |

|                          | <br>0111 1111: +127°C<br>When the Configuration register (02h) has been written "01h", meaning the temperature<br>conversion is shutdown, reading from this ExternalTemperature register will return a<br>NACK. |

### Register Address: 01h

| Field Name       |      | TempOffset[7:0] |                         |     |     |     |     |     |

|------------------|------|-----------------|-------------------------|-----|-----|-----|-----|-----|

| Data Bit         | D7   | D6              | D5                      | D4  | D3  | D2  | D1  | D0  |

| Bit Name         | Sign |                 | Temperature Offset Code |     |     |     |     |     |

| Read/Write       | R/W  | R/W             | R/W                     | R/W | R/W | R/W | R/W | R/W |

| Power On Default | 0    | 0               | 0                       | 0   | 0   | 0   | 0   | 0   |

| Field Name      | Bit Definition                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| TempOffset[7:0] | For some reason the user may want to set a temperature offset from the temperature readout.<br>Temperature Offset Selection<br>1111 0110: -10°C<br><br>1111 1110: -2°C<br>1111 1111: -1°C<br>0000 0000: 0°C<br>0000 0001: +1°C<br>0000 0010: +2°C<br><br>0000 1010: +10°C |  |  |  |  |  |  |

### Register Address: 02h

| Field Name       | Configuration[7:0] |                         |  |  |  |  |  |          |  |  |

|------------------|--------------------|-------------------------|--|--|--|--|--|----------|--|--|

| Data Bit         | D7                 | D7 D6 D5 D4 D3 D2 D1 D0 |  |  |  |  |  | D0       |  |  |

| Bit Name         |                    |                         |  |  |  |  |  | ShutDown |  |  |

| Read/Write       |                    | Reserved R/W            |  |  |  |  |  |          |  |  |

| Power On Default |                    | 0                       |  |  |  |  |  |          |  |  |

| Field Name         | Bit Definition                                                                                                                                                                                                                                                                |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuration[0:0] | "0h":<br>The APW7223 temperature immediately begins a temperature conversion and performs<br>subsequent temperature conversion approximately every 250us.<br>"01h":<br>The APW7223 temperature conversion is shut down. The internal NTC circuit and ADC<br>bias is disabled. |

### **Register Address: 03h**

| Field Name       | Enable[7:0]          |     |   |  |     |     |         |    |  |

|------------------|----------------------|-----|---|--|-----|-----|---------|----|--|

| Data Bit         | D7 D6 D5 D4 D3 D2 D1 |     |   |  |     | D1  | D0      |    |  |

| Bit Name         |                      |     |   |  |     |     | VCOM_EN | EN |  |

| Read/Write       |                      |     | R |  | R/W | R/W |         |    |  |

| Power On Default |                      | 0 0 |   |  |     |     |         |    |  |

| Field Name  | Bit Definition                                                                                                                                                                                                                                                                                                                                                     |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Enable[1:0] | 00: $V_{COM}$ and all outputs are disabled.<br>01: $V_{COM}$ is disabled, the other outputs is enabled.<br>10: $V_{COM}$ is enabled, the other outputs is disabled <sup>(Note)</sup><br>11: $V_{COM}$ and all outputs are enabled.<br>Note: Because HVINN is disabled, there is no voltage to supply the $V_{COM}$ , resulting $V_{COM}$<br>no output voltage too. |

Copyright © ANPEC Electronics Corp. Rev. A.2 - May., 2016

## Register Address: 04h

| Field Name       |     | VCOM_ADJUST[7:0]  |     |     |     |     |     |     |

|------------------|-----|-------------------|-----|-----|-----|-----|-----|-----|

| Data Bit         | D7  | D6                | D5  | D4  | D3  | D2  | D1  | D0  |

| Bit Name         |     | VCOM Voltage Code |     |     |     |     |     |     |

| Read/Write       | R/W | R/W               | R/W | R/W | R/W | R/W | R/W | R/W |

| Power On Default | 1   | 0                 | 0   | 0   | 0   | 0   | 0   | 0   |

|                  | Bit Definition                                                        |                                                                   |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------|--|--|--|--|--|--|

| Field Name       | Vcom voltage adjustment                                               |                                                                   |  |  |  |  |  |  |

|                  | VREF=open(VVREF=internal 2.56V)                                       | VREF=forced 3.3V                                                  |  |  |  |  |  |  |

| VCOM_ADJUST[7:0] | 0000 0000: -0.30 0V<br>0000 0001: -0.31 0V<br>0000 0010: -0.32 0V<br> | 0000 0000: -0.3000V<br>0000 0001: -0.3129V<br>0000 0010: -0.3258V |  |  |  |  |  |  |

|                  | 1000 0000: -1.58V<br>                                                 | 1000 0000: -1.9514V<br>                                           |  |  |  |  |  |  |

|                  | 1111 1111: -2.850 V                                                   | 1111 1111: -3.5900V                                               |  |  |  |  |  |  |

### **Register Address: 05h**

| Field Name       |            | FAULT[7:0] |                 |                 |               |               |                |                |  |

|------------------|------------|------------|-----------------|-----------------|---------------|---------------|----------------|----------------|--|

| Data Bit         | D7         | D6         | D5              | D4              | D3            | D2            | D1             | D0             |  |

| Bit Name         | POK        | ОТ         | HVINN_<br>FAULT | HVINP_<br>FAULT | POS_<br>FAULT | NEG_<br>FAULT | GVDD_<br>FAULT | GVEE_<br>FAULT |  |

| Read/Write       | R/W        | R          | R               | R               | R             | R             | R              | R              |  |

| Power On Default | $\searrow$ |            |                 |                 |               |               |                |                |  |

| Field Name | Bit Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FAULT[7:0] | The POK bit="1" indicates all outputs voltages have risen above their POK thresholds; otherwise,<br>there is at least one fault occurrence.<br>The OT bit="1" indicates over temperature has occurred.<br>The HVINN_FAULT bit="1" indicates the HVINN voltage is not good, and UV or SC is likely<br>happening on it.<br>The HVINP_FAULT bit="1" indicates the HVINP voltage is not good and UV or SC is likely<br>happening on it.<br>The POS_FAULT bit="1" indicates the POS voltage is not good and UV or SC is likely happening<br>on it.<br>The NEG_FAULT bit="1" indicates the NEG voltage is not good and UV or SC is likely happening<br>on it.<br>The NEG_FAULT bit="1" indicates the NEG voltage is not good and UV or SC is likely happening<br>on it.<br>The GVDD_FAULT bit="1" indicates the GVDD voltage is not good and UV or SC is likely<br>happening on it.<br>The GVEE_FAULT bit="1" indicates the GVEE voltage is not good and UV or SC is likely<br>happening on it. |

### Register Address: 06h

| Field Name       |    | ProgrammingControl[7:0] |        |     |    |    |    |    |

|------------------|----|-------------------------|--------|-----|----|----|----|----|

| Data Bit         | D7 | D6                      | D5     | D4  | D3 | D2 | D1 | D0 |

| Bit Name         |    |                         | TIMING | DVR |    |    |    |    |

| Read/Write       |    |                         | R/W    | R/W |    |    |    |    |

| Power On Default |    |                         |        |     |    |    | 0  | 0  |

| Field Name          | Bit Definition                                                                                                                                                                                                                                                                                                       |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | This register is used to control a multiplexer which determines the timing t1~t8 and VCOM voltage are programmed by either the registers(eq. timing registers and/or VCOM_ADJUST) or by the OTP(one-time programmable memory) values.                                                                                |

|                     | The Bit "TIMING" and "DVR" can be separately written and read.                                                                                                                                                                                                                                                       |

|                     | When writing "1" to the TIMING and/or DVR bit, the t1~t8 timing and/or VCOM voltage are<br>programmed according to the current values stored in those timing registers(08h~0Fh<br>registers) and/or VCOM_ADJUST register.                                                                                            |

| ProgramControl[1:0] | When writing "0" to the TIMING and/or DVR bit, the t1~t8 timing and/or VCOM voltage are programmed according to the current values stored in the OTP memory. Furthermore, in the meantime writing <sup>(Note 1)</sup> to the t1~t8 timing registers and/or VCOM_ADJUT register will rewrite the OTP memory's values. |

|                     | The OTP memory can be rewritten for several times:<br>8 times rewriting for VCOM voltage .<br>2 times rewriting for each t1~t8 timing.                                                                                                                                                                               |

|                     | When TIMING or DVR bit is "0" and you are writing 08h~0Fh or 04h registers, you will alter the timgings' or VCOM voltage's default values. When the OTP memory is run out, those default values will not be altered.                                                                                                 |

|                     | Note 1: In the OTP memory rewriting process, The APW7223 needs a 7.15V voltage to be supplied to the /FLT pin, otherwise OTP values will not be altered.                                                                                                                                                             |

### Register Address: 07h~0Eh

| Field Name       |     | Timing[7:0]                                                     |    |    |    |    |     |    |

|------------------|-----|-----------------------------------------------------------------|----|----|----|----|-----|----|

| Data Bit         | D7  | D6                                                              | D5 | D4 | D3 | D2 | D1  | D0 |

| Bit Name         |     | Timing code                                                     |    |    |    |    |     |    |

| Read/Write       | R/W | R/W R/W R/W R/W R/W R/W R/W                                     |    |    |    |    | R/W |    |

| Power On Default |     | Various values among 08h~0Fh register, see Bit Definition below |    |    |    |    |     |    |

| Field Name  | Bit Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Timing[7:0] | The t1~t8 timing is programmable by writing following value into corresponding register to meet<br>your application.<br>0000 0000=0ms<br>0000 0001=1ms<br>0000 0010=2ms<br>0000 0010=2ms<br>0000 011=3ms<br>0000 0100=4ms<br><br>1111 1111=255ms<br>The power on default value of t1 (07h register) and t5 (0Bh register) is "1Eh"<br>The power on default value of t1 (07h register) and t5 (0Bh register) is "1Eh"<br>The power on default value of t2 (08h register) and t5 (0Ch register) is "3Ch"<br>The power on default value of t3 (09h register) and t7 (0Dh register) is "5Ah"<br>The power on default value of t4 (0Ah register) and t8 (0Eh register) is "78h" |

### Register Address: 0Fh

| Field Name       |                  | Product Revision ID[7:0] |    |    |    |    |    |    |

|------------------|------------------|--------------------------|----|----|----|----|----|----|

| Data Bit         | D7               | D6                       | D5 | D4 | D3 | D2 | D1 | D0 |

| Bit Name         | Bit Name ID code |                          |    |    |    |    |    |    |

| Read/Write       |                  | Reserved                 |    |    | R  | R  | R  | R  |

| Power On Default |                  |                          |    |    | 0  | 0  | 0  | 0  |

| Field Name               | Bit Definition                                                                                                                                  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Product Revision ID[3:0] | This register stores the version code:<br>First version: "00h"<br>Second version: "01h"<br>Third version: "02h"<br><br>The eighth version:"07h" |

### Register Address: 10h

| Field Name       |    | Product ID[7:0] |    |    |    |    |    |    |

|------------------|----|-----------------|----|----|----|----|----|----|

| Data Bit         | D7 | D6              | D5 | D4 | D3 | D2 | D1 | D0 |

| Bit Name         |    | Product ID code |    |    |    |    |    |    |

| Read/Write       | R  | R               | R  | R  | R  | R  | R  | R  |

| Power On Default | 0  | 1               | 0  | 0  | 1  | 1  | 0  | 1  |

| Field Name      | Bit Definition              |

|-----------------|-----------------------------|

| Product ID[7:0] | Read only, Product ID="4Dh" |

### Layout Considerations

For all switching power supplies, the layout is an important step in the design; especially at high peak currents and switching frequencies. If the layout is not carefully done, the regulator might show noise problems and duty cycle jitter.

1. The input capacitor C1 and C2 should be placed close to the IN/INN and GND. Connecting the capacitor and IN/ INN-GND with short and wide trace without any via holes for good input voltage filtering. The distance between IN/ GND to capacitor less than 2mm respectively is recommended.

2. To minimize copper trace connections that can inject noise into the system, the inductor should be placed as close as possible to the SW pin to minimize the noise coupling into other circuits.

3. The output capacitor should be place closed to VOUT and GND.

4. Since the feedback pin and network is a high impedance circuit the feedback network should be routed away from the inductor. The feedback pin and feedback network should be shielded with a ground plane or trace to minimize noise coupling into this circuit.

5. A star ground connection or ground plane minimizes ground shifts and noise is recommended.

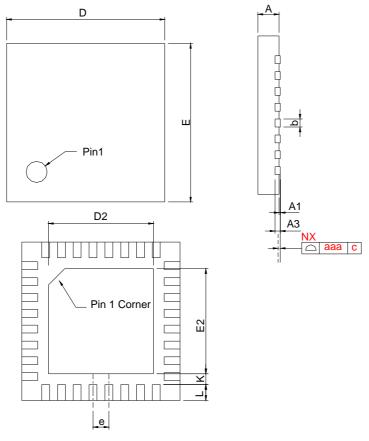

# Package Information

TQFN5x5-32

| Ş      |          | TQFI   | N5x5-32   |       |  |

|--------|----------|--------|-----------|-------|--|

| SY MBO | MILLI    | METERS | INC       | HES   |  |

| L C    | MIN.     | MAX.   | MIN.      | MAX.  |  |

| А      | 0.70     | 0.80   | 0.028     | 0.031 |  |

| A1     | 0.00     | 0.05   | 0.000     | 0.002 |  |

| A3     | 0.2      | 0 REF  | 0.008 REF |       |  |

| b      | 0.18     | 0.30   | 0.007     | 0.012 |  |

| D      | 4.90     | 5.10   | 0.193     | 0.201 |  |

| D2     | 3.50     | 3.80   | 0.138     | 0.150 |  |

| E      | 4.90     | 5.10   | 0.193     | 0.201 |  |

| E2     | 3.50     | 3.80   | 0.138     | 0.150 |  |

| е      | 0.50 BSC |        | 0.02      | 0 BSC |  |

| L      | 0.35     | 0.45   | 0.014     | 0.018 |  |

| к      | 0.20     |        | 0.008     |       |  |

| aaa    | 0        | .08    | 0.0       | 003   |  |

Note : 1. Followed from JEDEC MO-220 WHHD-4.

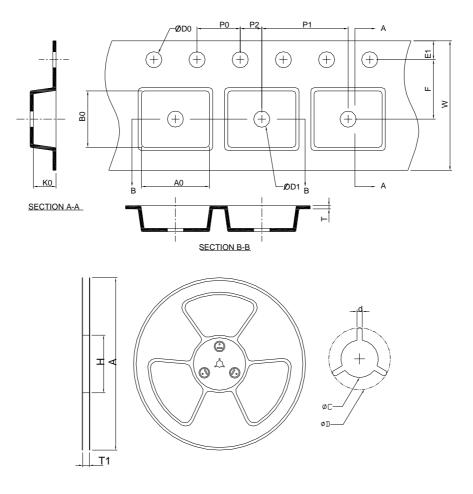

# **Carrier Tape & Reel Dimensions**

| Application | Α          | Н        | T1                 | С                  | d        | D                 | W         | E1        | F         |

|-------------|------------|----------|--------------------|--------------------|----------|-------------------|-----------|-----------|-----------|

|             | 330.0±2.00 | 50 MIN.  | 12.4+2.00<br>-0.00 | 13.0+0.50<br>-0.20 | 1.5 MIN. | 20.2 MIN.         | 12.0±0.30 | 1.75±0.10 | 5.5±0.10  |

| TQFN 5x5    | P0         | P1       | P2                 | D0                 | D1       | Т                 | A0        | B0        | K0        |

|             | 4.0±0.10   | 8.0±0.10 | 2.0±0.10           | 1.5+0.10<br>-0.00  | 1.5 MIN. | 0.6+0.00<br>-0.40 | 5.35±0.20 | 5.35±0.20 | 1.00±0.20 |

(mm)

### **Devices Per Unit**

| Package Type | Unit        | Quantity |

|--------------|-------------|----------|

| TQFN5x5-32   | Tape & Reel | 2500     |

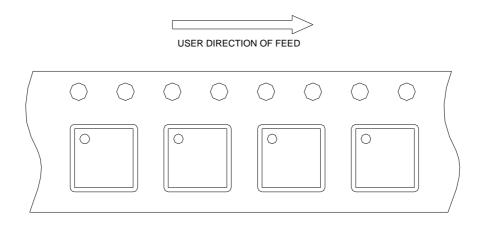

## **Taping Direction Information**

### TQFN5x5-32

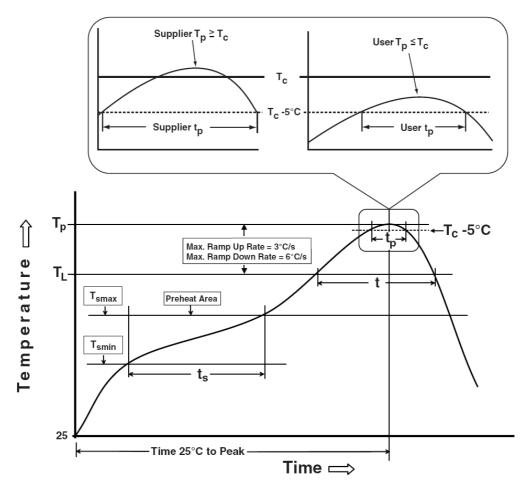

### **Classification Profile**

Copyright © ANPEC Electronics Corp. Rev. A.2 - May., 2016

### **Classification Reflow Profiles**

| Sn-Pb Eutectic Assembly            | Pb-Free Assembly                                                                                                                                             |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 100 °C<br>150 °C<br>60-120 seconds | 150 °C<br>200 °C<br>60-120 seconds                                                                                                                           |

| 3 °C/second max.                   | 3°C/second max.                                                                                                                                              |

| 183 °C<br>60-150 seconds           | 217 °C<br>60-150 seconds                                                                                                                                     |

| See Classification Temp in table 1 | See Classification Temp in table 2                                                                                                                           |

| 20** seconds                       | 30** seconds                                                                                                                                                 |

| 6 °C/second max.                   | 6 °C/second max.                                                                                                                                             |

| 6 minutes max.                     | 8 minutes max.                                                                                                                                               |

|                                    | 100 °C<br>150 °C<br>60-120 seconds<br>3 °C/second max.<br>183 °C<br>60-150 seconds<br>See Classification Temp in table 1<br>20** seconds<br>6 °C/second max. |

\*\* Tolerance for time at peak profile temperature (t<sub>p</sub>) is defined as a supplier minimum and a user maximum.

Table 1. SnPb Eutectic Process – Classification Temperatures (Tc)

| Package<br>Thickness | Volume mm <sup>3</sup><br><350 | Volume mm <sup>3</sup><br><sup>3</sup> 350 |