# **ARM28XXT SERIES**

# HYBRID-HIGH RELIABILITY 1MEGA-RAD HARDENED DC-DC CONVERTER

### Description

The ARM Series of three output DC-DC converters are designed specifically for use in the high-dose radiation environments encountered during deep space planetary missions. The extremely high level of radiation tolerance inherent in the ARM design is assured as a result of extensive research, thorough analysis and testing, careful selection of components and lot verification testing of finished hybrids. Many of the best circuit design features characterizing earlier IR HiRel products have been incorporated into the ARM topology. Capable of uniformly high performance through long term exposures in radiation intense environments, this series sets the standard for distributed power systems demanding high performance and reliability.

The ARM converters are hermetically sealed in a rugged, low profile package utilizing copper core pins to minimize resistive DC losses. Long-term hermetically is assured through use of parallel seam welded lid attachment along with IR HiRel rugged ceramic pin-to-package seal. Axial lead orientation facilitates preferred bulkhead mounting to the principal heat-dissipating surface.

Manufactured in a facility fully qualified to MIL-PRF-38534, these converters are fabricated utilizing DLA Land and Maritime qualified processes. For available screening options, refer to device screening table in the data sheet.

Variations in electrical, mechanical and screening specifications can be accommodated. Contact IR HiRel San Jose for special requirements.

# 28V Input, Triple Output

#### Features

- Total Dose > 1 MRads(Si)

- SEE Hardened to LET up to 83 MeV.cm<sup>2</sup>/mg

- De-rated per MIL-STD-975 & MIL-STD-1547

- Output Power Range 3 to 30 Watts

- 19 to 50 Volt Input Range

- Input Under voltage Lockout

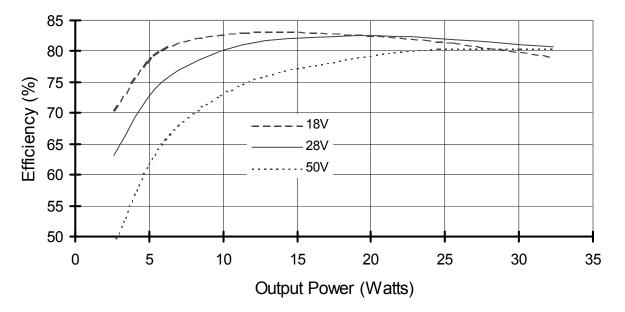

- High Electrical Efficiency > 80%

- Full Performance from -55°C to +125°C

- Continuous Short Circuit Protection

- 12.8 W/in<sup>3</sup> Output Power Density

- True Hermetic Package

- External Inhibit Port

- Externally Synchronization

- Fault Tolerant Design

- 5V, ±12V or 5V, ±15V Outputs Available

| Specifications                                                                                                                                |                                      |                                  |                                                                                               |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------|--|--|--|

| Absolute Maximum Ratings                                                                                                                      |                                      | Recommended Operating Conditions |                                                                                               |  |  |  |

| Input voltage range -0.5V <sub>DC</sub> to +80V <sub>DC</sub>                                                                                 |                                      | Input voltage range              | +19V <sub>DC</sub> to +60V <sub>DC</sub><br>+19V to +50V for full de-rating to<br>MIL-STD-975 |  |  |  |

| Minimum Output Current                                                                                                                        | 5% Maximum rated current, any Output | Output power                     | 3.0W to 30W                                                                                   |  |  |  |

| Soldering temperature                                                                                                                         | 300°C for 10 seconds                 |                                  | -55°C to +125°C                                                                               |  |  |  |

| Storage case temperature                                                                                                                      | -65°C to +135°C                      | Operating case temperature       | -55°C to +85°C for full de-rating to MIL-STD-975                                              |  |  |  |

| <b>Static Characteristics</b> $-55^{\circ}C \le T_{CASE} \le +125^{\circ}C$ , $V_{IN} = 28V_{DC}$ , $C_{L} = 0$ , unless otherwise specified. |                                      |                                  |                                                                                               |  |  |  |

| Parameter Symbol                                             |           | Symbol              | I Test Conditions                                                                                      |                                                                                           |                       | Limits                |                   |  |

|--------------------------------------------------------------|-----------|---------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------|-----------------------|-------------------|--|

|                                                              |           | Symbol              |                                                                                                        | Min.                                                                                      | Max.                  | Unit                  |                   |  |

| Output voltage accuracy                                      |           | N                   | I <sub>OUT</sub> = 1.5Adc, T <sub>C</sub> = +25°C                                                      | (main)                                                                                    | 4.95                  | 5.05                  | V <sub>DC</sub>   |  |

|                                                              |           | V <sub>OUT</sub>    | $I_{OUT}$ = ±250mAdc, $T_C$ = +25°C<br>$I_{OUT}$ = ±250mAdc, $T_C$ = +25°C                             | ARM2812 (dual)<br>ARM2815 (dual)                                                          | ±11.50<br>±14.50      | ±12.50<br>±15.15      | -                 |  |

| Output power                                                 | Note 5    | P <sub>OUT</sub>    | $19 V_{DC} < V_{IN} < 50 V_{DC}$                                                                       |                                                                                           | 3.0                   | 30                    | W                 |  |

| Output current                                               | Note 5    | I <sub>OUT</sub>    | 19 V <sub>DC</sub> < V <sub>IN</sub> < 50V <sub>DC</sub>                                               | (main)                                                                                    | 150                   | 3000                  | mAdc              |  |

|                                                              |           |                     |                                                                                                        | (dual)                                                                                    | 75                    | 750                   |                   |  |

| Line regulation                                              | Note 3    | VR <sub>LINE</sub>  | 150 mAdc < $I_{OUT}$ < 3000 mAdc<br>19 Vdc< $V_{IN}$ < 50Vdc                                           | (main)                                                                                    | -15                   | +15                   | mV                |  |

| Line regulation                                              | 1000 0    | VILINE              | $\pm 75 \text{ mAdc} < I_{OUT} < \pm 750 \text{ mAdc}$                                                 | (dual)                                                                                    | -60                   | +60                   |                   |  |

| Load regulation                                              | Note 4    |                     | 150 mAdc < $I_{OUT}$ < 3000 mAdc 19 $V_{DC}$ < $V_{IN}$ < 50 $V_{DC}$                                  | (main)                                                                                    | -180                  | +180                  | mV                |  |

|                                                              |           | VICLOAD             | $\pm$ 75 mAdc < I <sub>OUT</sub> < $\pm$ 750 mAdc (du                                                  |                                                                                           | -300                  | +300                  |                   |  |

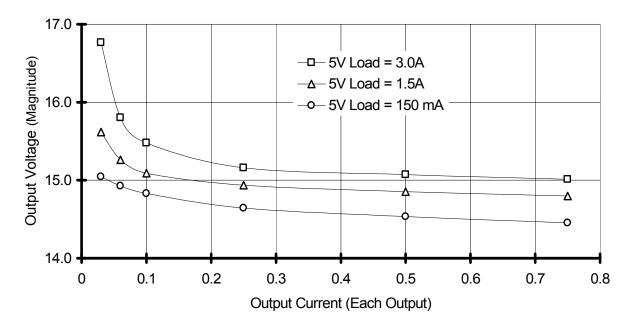

| Cross regulation                                             | Note 8    | VR <sub>CROSS</sub> | $19 V_{DC} < V_{IN} < 50 V_{DC}$                                                                       | (main)                                                                                    | -10                   | +10                   | mV                |  |

|                                                              |           | VICROSS             |                                                                                                        | (dual)                                                                                    | -500                  | +500                  |                   |  |

| Total regulation                                             |           | V <sub>R</sub>      | All conditions of Line, Load,<br>Cross Regulation, Aging,<br>Temperature and Radiation                 | (main)<br>ARM2812 (dual)<br>ARM2815 (dual)                                                | 4.8<br>±11.1<br>±13.9 | 5.2<br>±12.9<br>±16.0 | v                 |  |

|                                                              |           |                     | I <sub>OUT</sub> = minimum rated, Pin 3 op                                                             | en                                                                                        |                       | 250                   |                   |  |

| Input current                                                |           | I <sub>IN</sub>     | Pin 3 shorted to pin 2 (disabled                                                                       | )                                                                                         |                       | 8.0                   | mA                |  |

| Output ripple voltage                                        | e Note 6  | V <sub>RIP</sub>    | 19 V <sub>DC</sub> < V <sub>IN</sub> < 50V <sub>DC</sub><br>I <sub>OUT</sub> = 3000 mAdc (main), ±500  | $19 V_{DC} < V_{IN} < 50 V_{DC}$<br>I <sub>OUT</sub> = 3000 mAdc (main), ±500 mAdc (dual) |                       | 100                   | $mV_{p.p}$        |  |

| Input ripple current                                         | Note 6    | I <sub>RIP</sub>    | $19 V_{DC} < V_{IN} < 50 V_{DC}$<br>$I_{OUT} = 3000 \text{ mAdc (main), } \pm 500 \text{ mAdc}$ (dual) |                                                                                           |                       | 150                   | mA <sub>p.p</sub> |  |

| Switching frequency                                          | /         | Fs                  | Synchronization input open. (pi                                                                        | n 6)                                                                                      | 225                   | 275                   | kHz               |  |

| Efficiency                                                   |           | E <sub>FF</sub>     | I <sub>OUT</sub> = 3000 mAdc (main), ±500                                                              | mAdc (dual)                                                                               | 80                    |                       | %                 |  |

| Enable Input<br>open circuit<br>drive curren<br>voltage rang | nt (sink) |                     | 19V <sub>DC</sub> < V <sub>IN</sub> < 50V <sub>DC</sub>                                                |                                                                                           | 3.0<br>0.1<br>-0.5    | 5.0<br>50.0           | V<br>mA<br>V      |  |

For Notes to Electrical Performance Characteristics, refer to page 3

#### **Static Characteristics** (Continued) $-55^{\circ}C \le T_{CASE} \le +125^{\circ}C, V_{IN} = 28V_{DC}, C_{L} = 0$ , unless otherwise specified.

|                                                                                                                        |                    | <b>T</b> ( <b>0</b> )                                                                 | Test Conditions  |                                | nits                      | Unit                       |

|------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------|------------------|--------------------------------|---------------------------|----------------------------|

| Parameter                                                                                                              | Symbol             | Test Conditions                                                                       |                  |                                | Max.                      |                            |

| Synchronization Input<br>frequency range<br>pulse high level<br>pulse low level<br>pulse rise time<br>pulse duty cycle |                    | External clock signal on Sync. inp                                                    | ut (pin 4)       | 225<br>4.5<br>-0.5<br>40<br>20 | 310<br>10.0<br>0.25<br>80 | kHz<br>V<br>V<br>V/μs<br>% |

| Power dissipation, load fault                                                                                          | PD                 | Short circuit, any output                                                             |                  |                                | 7.5                       | W                          |

| Output response to step load changes<br>Notes 7, 11                                                                    | S V <sub>TLD</sub> | 10% Load to/from 50% load<br>50% Load to/from 100% load                               |                  | -200<br>-200                   | 200<br>200                | тV <sub>РК</sub>           |

| Recovery time from step load change<br>Notes 11, 12                                                                    |                    | 10% Load to/from 50% load<br>50% Load to/from 100% load                               |                  |                                | 200<br>200                | μs                         |

| Output response to step line changes<br>Notes 10, 1                                                                    | 1 V <sub>TLN</sub> | $I_{OUT}$ = 3000 mAdc<br>V <sub>IN</sub> = 19 V to/from 50 V<br>$I_{OUT}$ = ±500 mAdc | (main)<br>(dual) | -350<br>-1050                  | 350<br>1050               | тV <sub>РК</sub>           |

| Recovery time from step line changes<br>Notes 10, 11,13                                                                |                    | $I_{OUT}$ = 3000 mAdc<br>V <sub>IN</sub> = 19 V to/from 50 V<br>$I_{OUT}$ = ±500 mAdc | (main)<br>(dual) |                                | 500<br>500                | μs                         |

| Turn on overshoot                                                                                                      | V <sub>os</sub>    | I <sub>OUT</sub> = minimum and full rated                                             | (main)<br>(dual) |                                | 500<br>1500               | mV                         |

| Turn on delay Note 14                                                                                                  | T <sub>DLY</sub>   | I <sub>OUT</sub> = minimum and full rated                                             |                  | 5.0                            | 20                        | ms                         |

| Capacitive load Notes 9, 10                                                                                            | CL                 | No effect on DC performance                                                           | (main)<br>(dual) |                                | 500<br>100                | μF                         |

| Isolation                                                                                                              | I <sub>SO</sub>    | 500V <sub>DC</sub> Input to Output or any pin to case (except pin 12)                 |                  | 100                            |                           | MΩ                         |

#### **Notes to Specifications**

- 1. Operation outside absolute maximum/minimum limits may cause permanent damage to the device. Extended operation at the limits may permanently degrade performance and affect reliability.

- 2. Device performance specified in Electrical Performance table is guaranteed when operated within recommended limits. Operation outside recommended limits is not specified.

- 3. Parameter measured from 28V to 19 V or to 50V while loads remain fixed.

- 4. Parameter measured from nominal to minimum or maximum load conditions while line remains fixed.

- 5. Up to 750 mA is available from each of the dual outputs provided the total output power does not exceed 30W.

- 6. Guaranteed for a bandwidth of DC to 20 MHz.Tested using a 20 kHz to 2 MHz bandwidth.

- 7. Load current is stepped for output under test while other outputs are fixed at half rated load.

- 8. Load current is fixed for output under test while other output loads are varied for any combination of minimum to maximum.

- A capacitive load of any value from 0 to the specified maximum is permitted without compromise to DC performance. A capacitive load in excess of the maximum limit may interfere with the proper operation of the converter's short circuit protection, causing erratic behavior during turn on.

- Parameter is tested as part of design characterization or after design or process changes. Thereafter, parameters shall be guaranteed to the limits specified in the table.

- 11. Load transient rate of change, di/dt  $\leq$  2 A/µs.

- 12. Recovery time is measured from the initiation of the transient to where  $V_{OUT}$  has returned to within ±1% of its steady state value.

- 13. Line transient rate of change,  $dv/dt \le 50 V/\mu s$ .

- 14. Turn on delay time is for either a step application of input power or a logical low to high transition on the enable pin (pin 3) while power is present at the input.

# **Group A Tests** $V_{IN}$ = 28V, $C_L$ = 0 unless otherwise specified.

| Demonster                               |                  | Dense had been to be a difference                                                                                                      |                      | Limits           |                  | 1114              |

|-----------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------|------------------|-------------------|

| Parameter                               | Symbol           | Test Conditions                                                                                                                        | Group A<br>Subgroups | Min.             | Max.             | Unit              |

|                                         |                  | $I_{OUT} = 1.5 A_{DC}$ (main)                                                                                                          | 1, 2, 3              | 4.95             | 5.05             |                   |

| Output voltage accuracy                 | V <sub>OUT</sub> | $I_{OUT} = \pm 250$ mAdc ARM2812(dual)<br>$I_{OUT} = \pm 250$ mAdc ARM2815(dual)                                                       | 1, 2, 3<br>1, 2, 3   | ±11.70<br>±14.50 | ±12.30<br>±15.15 | V                 |

| Output power Note 1                     | P <sub>OUT</sub> | V <sub>IN</sub> = 19 V, 28V, 50 V                                                                                                      | 1, 2, 3              | 3.0              | 30               | W                 |

| Output current<br>Note 1                |                  | (main)<br>V <sub>IN</sub> 19 V, 28V, 50 V                                                                                              | 1, 2, 3              | 150              | 3000             |                   |

|                                         | I <sub>OUT</sub> | (dual)                                                                                                                                 | 1, 2, 3              | 75               | 500              | mA                |

| Output regulation Note 4                |                  | $I_{OUT}$ = 150, 1500, 3000mA <sub>DC</sub> (main)<br>V <sub>IN</sub> = 19 V, 28V, 50 V<br>$I_{OUT}$ = ±75, ±310, ±625mA <sub>DC</sub> | 1, 2, 3              | 4.8              | 5.2              |                   |

|                                         | V <sub>R</sub>   | 2812 (dual)<br>I <sub>OUT</sub> = ±75, ±250, ±500mA <sub>DC</sub>                                                                      | 1, 2, 3              | ±11.1            | ±12.9            | V                 |

|                                         |                  | 2815 (dual)                                                                                                                            | 1, 2, 3              | ±14.0            | ±15.8            |                   |

| Input current                           |                  | I <sub>OUT</sub> = minimum rated, Pin 3 open                                                                                           | 1, 2, 3              |                  | 250              |                   |

|                                         | I <sub>IN</sub>  | Pin 3 shorted to pin 2 (disabled)                                                                                                      | 1, 2, 3              |                  | 8.0              | mA                |

| V <sub>RIP</sub> I <sub>OUT</sub> = 300 |                  | V <sub>IN</sub> = 19 V, 28V, 50 V<br>I <sub>OUT</sub> = 3000mA main, ±500mA<br>(dual)                                                  | 1, 2, 3              |                  | 100              | $mV_{P-P}$        |

| Input ripple Note 2                     | I <sub>RIP</sub> | V <sub>IN</sub> = 19 V, 28V, 50 V<br>I <sub>OUT</sub> = 3000mA main, ±500mA<br>(dual)                                                  | 1, 2, 3              |                  | 150              | mA <sub>P-P</sub> |

| Switching frequency                     | Fs               | Synchronization pin (pin 6) open                                                                                                       | 4, 5, 6              | 225              | 275              | kHz               |

| Efficiency                              | E <sub>FF</sub>  | I <sub>OUT</sub> = 800mA main, ±500mA (dual)                                                                                           | 1<br>2, 3            | 80<br>78         |                  | %                 |

| Power dissipation,<br>load fault        | P <sub>D</sub>   | Short circuit, any output                                                                                                              | 1, 2, 3              |                  | 7.5              | W                 |

| Output response to step load            |                  | 10% Load to/from 50% load                                                                                                              | 4, 5, 6              | -200             | 200              |                   |

| changes Notes 3, 5                      | V <sub>TL</sub>  | 50% Load to/from 100% load                                                                                                             | 4, 5, 6              | -200             | 200              | тV <sub>РК</sub>  |

| Recovery time from step load            |                  | 10% Load to/from 50% load                                                                                                              | 4, 5, 6              |                  | 200              |                   |

| changes Notes 5, 6                      | T <sub>TL</sub>  | 50% Load to/from 100% load                                                                                                             | 4, 5, 6              |                  | 200              | μs                |

| <b>-</b>                                |                  | (main)                                                                                                                                 | 4, 5, 6              |                  | 500              |                   |

| Turn on overshoot                       | Vos              | I <sub>OUT</sub> = minimum and full rated<br>(dual)                                                                                    | 4, 5, 6              |                  | 1500             | mV                |

| Turn on delay Note 7                    | T <sub>DLY</sub> | I <sub>OUT</sub> = minimum and full rated                                                                                              | 4, 5, 6              | 5.0              | 20               | ms                |

| Isolation                               | I <sub>SO</sub>  | $500V_{DC}$ Input to output or any pin to case (except pin 12)                                                                         | 1                    | 100              |                  | MΩ                |

For Notes to Group A Tests, refer to page 5.

#### Notes to Group A Test Table

- 1. Parameter verified during dynamic load regulation tests.

- 2. Guaranteed for DC to 20 MHz bandwidth. Test conducted using a 20 kHz to 2 MHz bandwidth.

- 3. Load current is stepped for output under test while other outputs are fixed at half rated load.

- 4. Each output is measured for all combinations of line and load. Only the minimum and maximum readings for each output are recorded.

- 5. Load step transition time  $\geq 10 \mu S.$

- 6. Recovery time is measured from the initiation of the transient to where  $V_{OUT}$  has returned to within ±1% of its steady state value.

- 7. Turn on delay time is tested by application of a logical low to high transition on the enable pin (pin 3) with power present at the input.

- 8. Subgroups 1 and 4 are performed at +25°C, subgroups 2 and 5 at -55°C and subgroups 3 and 6 at +125°C.

#### **Radiation Performance**

The radiation tolerance characteristics inherent in the ARM28XXT converter are based on the results of the ground-up design effort on the ART2800T program and started with specific radiation design goals. By imposing sufficiently large margins on those electrical parameters subject to the degrading effects of radiation, appropriate elements were selected for incorporation into the ART2800T circuit. Known radiation data was utilized for input to PSPICE and Rad SPICE in the generation of circuit performance verification analyses. Thus, electrical performance capability under all environmental conditions including radiation was well understood before first application of power to the inputs.

The principal ART2800T design goal was a converter topology, which because of large design margins, had radiation performance essentially independent of wafer-lot radiation performance variations. Radiation tests on random ART2800T manufacturing lots provide continued confirmation of the soundness of the design goals as well as justification for the element selection criteria.

To achieve the radiation levels specified for the ARM28XXT, the ART2800T topology is utilized as the basis but lot assurance testing is utilized as part of the screening process to assure the specified level. Each ARM28XXT converter is delivered with lot test data at the hybrid level supporting the minimum TID specification. Other radiation specifications are assured by design and generic data are available on request.

The following table specifies guaranteed minimum radiation exposure levels tolerated while maintaining specification limits.

### Radiation Specification Tcase = 25°C

| Parameter                           | Condition                                                            | Min  | Тур | Max | Unit                    |

|-------------------------------------|----------------------------------------------------------------------|------|-----|-----|-------------------------|

| Total Ionizing Dose (2 :1 Margin)   | MIL-STD-883, Method 1019.4<br>Operating bias applied during exposure |      |     |     | kRads (Si)              |

| Dose Rate                           |                                                                      |      |     |     |                         |

| Temporary Saturation                | MIL-STD-883, Method 1021                                             | 1E8  |     |     | Rads(Si)/sec            |

| Survival                            |                                                                      | 1E11 |     |     |                         |

| Neutron Fluence                     | MIL-STD-883, Method 1017.2                                           | 3E12 |     |     | Neutron/cm <sup>2</sup> |

| Heavy Ion<br>(Single event effects) | BNL Dual Van de Graf Generator                                       | 83   |     |     | MeV∙cm²/mg              |

IR HiRel currently does not have a DLA certified Radiation Hardness Assurance Program.

#### Standard Quality Conformance Inspections on ARH28XXXXS Series (Flight Screened)

| Inspection | Application                                      | Samples   |

|------------|--------------------------------------------------|-----------|

| Group A    | Part of screening on each unit                   | 100%      |

| Group B    | Each inspection lot                              | * 5 units |

| Group C    | First inspection lot or following class 1 change | 10 units  |

| Group D    | In line (Part of element evaluation)             | 3 units   |

\* Group B quantity for option 2 End of Line QCI. No Group B samples required for Option 1, In-line.

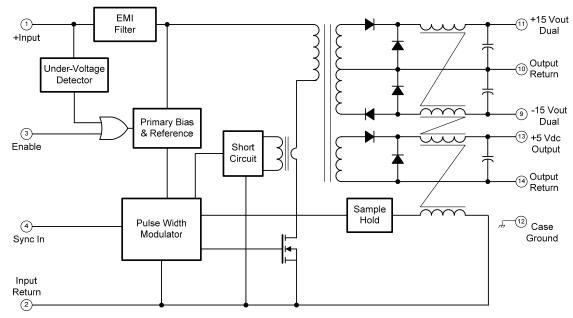

### Fig I. Block Diagram

#### **Circuit Operation and Application Information**

The ARM28XXT Series of converters have been designed using a single ended forward switched mode converter topology. (refer to Figure I.) Single ended topologies enjoy some advantage in radiation hardened designs in that they eliminate the possibility of simultaneous turn on of both switching elements during a radiation induced upset; in addition, single ended topologies are not subject to transformer saturation problems often associated with double ended implementations.

The design incorporates an LC input filter to attenuate input ripple current. A low overhead linear bias regulator is used to provide bias voltage for the converter primary control logic and a stable, well regulated reference for the error amplifier. Output control is realized using a wide band discrete pulse width modulator control circuit incorporating a unique non-linear ramp generator circuit. This circuit helps stabilize loop gain over variations in line voltage for superior output transient response. Nominal conversion frequency has been selected as 250 kHz to maximize efficiency and minimize magnetic element size.

Output voltages are sensed using a coupled inductor and a patented magnetic feedback circuit. This circuit is relatively insensitive to variations in temperature, aging, radiation and manufacturing tolerances making it particularly well suited to radiation hardened designs. The control logic has been designed to use only radiation tolerant components, and all current paths are limited with series resistance to limit photo currents.

Other key circuit design features include short circuit protection, under voltage lockout and an external synchronization port permitting operation at an externally set clock rate.

#### **Operating Guidelines**

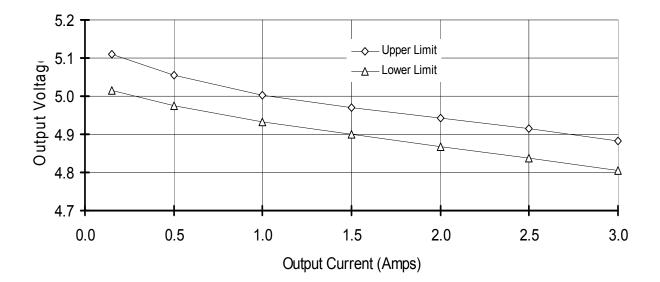

The circuit topology used for regulating output voltages in the ARM28XXT Series of converters was selected for a number of reasons. Significant among these is the ability to simultaneously provide adequate regulation to three output voltages while maintaining modest circuit complexity. These attributes were fundamental in retaining the high reliability and insensitivity to radiation that characterizes device performance. Use of this topology dictates that the user maintain the minimum load specified in the electrical tables on each output. Attempts to operate the converter without a load on any output will result in peak charging to an output voltage well above the specified voltage regulation limits, potentially in excess of ratings, and should be avoided. Output loads that are less than specification minimums will result in regulation performance outside the limits presented in the tables. In most practical applications, this lower bound on the load range does not present a serious constraint; however the user should be mindful of the results. Characteristic curves illustrating typical regulation performance are shown in Figures VII, VIII and IX.

#### **Thermal Considerations**

The ARM Series of converters is capable of providing relatively high output power from a package of modest volume. The power density exhibited by these devices is obtained by combining high circuit efficiency with effective methods of heat removal from the die junctions. Good design practices have effectively addressed this requirement inside the device. However when operating at maximum loads, significant heat generated at the die junctions must be carried away by conduction from the base. To maintain case temperature at or below the specified maximum of 125°C, this heat can be transferred by attachment to an appropriate heat dissipater held in intimate contact with the converter base-plate.

Effectiveness of this heat transfer is dependent on the intimacy of the baseplate-heatsink interface. It is therefore suggested that a heat transferring medium possessing good themal conductivity is inserted between the baseplate and heat sink. A material utilized at the factory during testing and burn-in processes is sold under the trade name of Sil-Pad<sup>®</sup>400<sup>1</sup>. This particular product is an insulator but electrically conductive versions are also available. Use of these materials assures optimum surface contact with the heat dissipater by compensating for minor surface variations. While other available types of heat conducting materials and thermal compounds provide similar effectiveness, these alternatives are often less convenient and are frequently messy to use.

A conservative aid to estimating the total heat sink surface area ( $A_{HEAT}$  SINK) required to set the maximum case temperature rise ( $\Delta T$ ) above ambient temperature is given by the following expression:

A heat sink

$$\approx \left\{ \frac{\Delta T}{80P^{0.85}} \right\}^{-1.43} - 5.94$$

Where

$\Delta T = \text{Case temperature rise above ambient}$  $P = \text{Device dissipation in Watts} = P_{out} \left\{ \frac{1}{E_{ff}} - \frac{1}{E_{ff}} \right\}$

As an example, assume that it is desired to maintain the case temperature of an ARM2815T at +65°C or less while operating in an open area whose ambient temperature does not exceed +35°C; then

$$\Delta T = 65 - 35 = 35^{\circ}C$$

From the Specification Table, the worst case full load efficiency for this device is 80%; therefore the maximum power dissipation at full load is given by

$$P = 30 \bullet \left\{ \frac{1}{.80} - 1 \right\} = 30 \bullet (0.25) = 7.5 W$$

and the required heat sink area is

A heat sink =

$$\left\{\frac{35}{80 \bullet 7.5^{0.85}}\right\}^{-1.43} - 5.94 = 31.8 \text{ in}^2$$

<sup>1</sup>Sil-Pad is a registered Trade Mark of Bergquist, Minneapolis, MN

Thus, a total heat sink surface area (including fins, if any) of approximately 32 in<sup>2</sup> in this example, would limit case rise to  $35^{\circ}$ C above ambient. A flat aluminum plate, 0.25" thick and of approximate dimension 4" by 4" (16 in<sup>2</sup> per side) would suffice for this application in a still air environment. Note that to meet the criteria, both sides of the plate require unrestricted exposure to the ambient air.

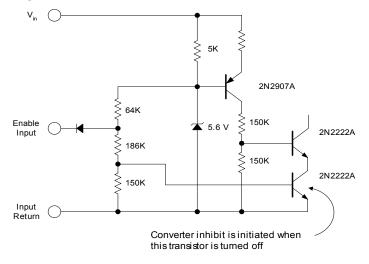

#### Inhibiting Converter Output

As an alternative to application and removal of the DC voltage to the input, the user can control the converter output by providing an input referenced, TTL compatible, logic signal to the enable pin 3. This port is internally pulled "high" so that when not used, an open connection on the pin permits normal converter operation. When inhibited outputs are desired, a logical "low" on this port will shut the converter down. An open collector device capable of sinking at least 100  $\mu$ A connected to enable pin 3 will work well in this application.

A benefit of utilization of the enable input is that following initial charge of the input capacitor, subsequent turn-on commands will induce no uncontrolled current inrush.

#### Fig. II. Enable Input Equivalent Circuit

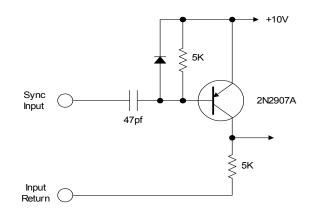

#### Synchronization

When using multiple converters, system requirements may dictate operating several converters at a common system frequency. To accommodate this requirement, the ARM28XXT type converter provides a synchronization input port (pin 4). Circuit topology is as illustrated in Fig. III.

The sync input port permits synchronization of an ARM converter to any compatible external frequency source operating in the band of 225 to 310 kHz. The synchronization input is edge triggered with synchronization initiated on the negative transition. This input signal should be a negative going pulse referenced to the input return and have a 20% to 80% duty cycle. Compatibility requires the negative transition time to be less than 100 ns with a minimum pulse amplitude of +4.25 volts referred to the input return. In the event of failure of an external synchronization source, the converter will revert to its own internally set frequency. When external synchronization is not desired, the sync in port may be left open (unconnected) permitting the converter to operate at its' own internally set frequency.

#### Fig. III. Synchronization Input Equivalent Circuit

#### **Output Short Circuit Protection**

Protection against accidental short circuits on any output is provided in the ARM28XXT converters. This protection is implemented by sensing primary switching current and, when an over-current condition is detected, switching action is terminated and a restart cycle is initiated. If the short circuit condition has not been cleared by the time the restart cycle has completed, another restart cycle is initiated. The sequence will repeat until the short circuit condition is cleared at which time the converter will resume normal operation. The effect is that during a shorted condition, a series of narrow pulses are generated at approximately 5% duty cycle which periodically sample the state of the load. Thus device power dissipation is greatly reduced during this mode of operation.

### **Parallel Operation**

Although no special provision for forced current sharing has been incorporated in the ARM28XXT Series, multiple units may be operated in parallel for increased output power applications. The 5 volt outputs will typically share to within approximately 10% of their full load capability and the dual (±15 volt) outputs will typically share to within 50% of their full load. Load sharing is a function of the individual impedance of each output and the converter with the highest nominal set voltage will furnish the predominant load current.

#### Input Under voltage Protection

A minimum voltage is required at the input of the converter to initiate operation. This voltage is set to a nominal value of 16.8 volts. To preclude the possibility of noise or other variations at the input falsely initiating and halting converter operation, a hysteresis of approximately 1.0 volts is incorporated in this circuit. The converter is guaranteed to operate at 19 Volts input under all specified conditions.

#### **Input Filter**

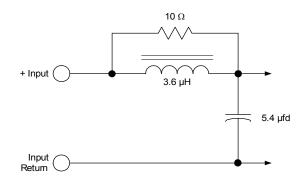

To attenuate input ripple current, the ARM28XXT Series converters incorporate a single stage LC input filter. The elements of this filter comprise the dominant input load impedance characteristic, and therefore determine the nature of the current inrush at tum-on. The input filter circuit elements are as shown in Fig. IV.

#### Fig. IV. Input Filter Circuit

#### Additional Filtering

Although internal filtering is provided at both the input and output terminals of the ARM2800 series, additional filtering may be desirable in some applications to accommodate more stringent system requirements.

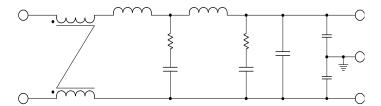

While the internal input filter of Fig. IV keeps input ripple current below 100 mAp-p, an external filter is available that will further attenuate this ripple content to a level below the CE03 limits imposed by MIL-STD-461B. Fig. V is a general diagram of the Advanced Analog ARF461 filter module designed to operate in conjunction with the ARM2800 Series converters to provide that attenuation.

### Fig. V. ARF461 Input EMI Filter

This circuit as shown in Fig. V is constructed using the same quality materials and processes as those employed in the ARM2800 Series converters and is intended for use in the same environments. This filter is fabricated in a complementary package style whose output pin configuration allows pin to pin connection between the filter and the converter. More complete information on this filter can be obtained from the ARF461 data sheet.

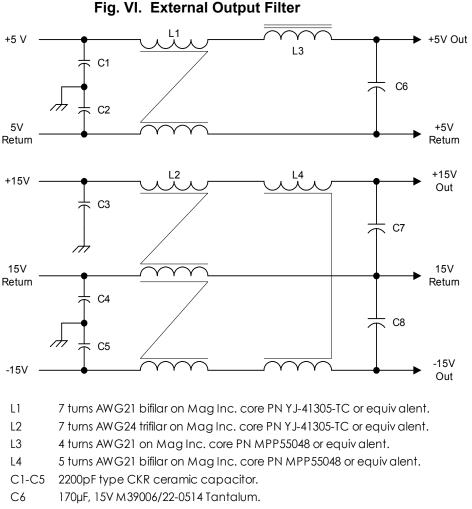

An external filter may also be added to the output where circuit requirements dictate extremely low output ripple noise. The output filter described by Fig.VI has been characterized with the ARM2815T using the values shown in the associated material list.

It is important to be aware that when filtering high frequency noise, parasitic circuit elements can easily dominate filter performance. Therefore, it is incumbent on the designer to exercise care when preparing a circuit layout for such devices. Wire runs and lengths should be minimized, high frequency loops should be avoided and careful attention paid to the construction details of magnetic circuit elements. Tight magnetic coupling will improve overall magnetic performance and reduce stray magnetic fields.

C7,C8 25µF, 50V M39006/22-0568 Tantalum.

Measurement techniques can impose a significant influence on results. All noise measurements should be measured with test leads as close to the device output pins and as short as physically possible. Probe ground leads should be kept to a minimum length.

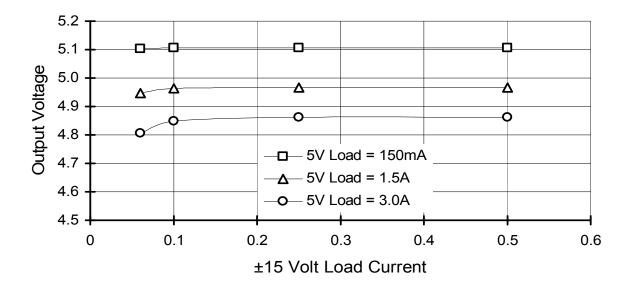

# Performance Characteristics (Typical @ 25°C)

for Three Line Voltages.

Fig. VIII. 5 V Output Regulation Limits

Including all conditions of Line, Load and Cross Regulation.

## Performance Characteristics (Typical @ 25°C) (Continued)

### Fig. IX. ±15 V Regulation Curves

For Three conditions of Load on the 5 Volt Output.

5 Volt Output as a function of 15 Volt Load Current for Three 5 Volt Loads.

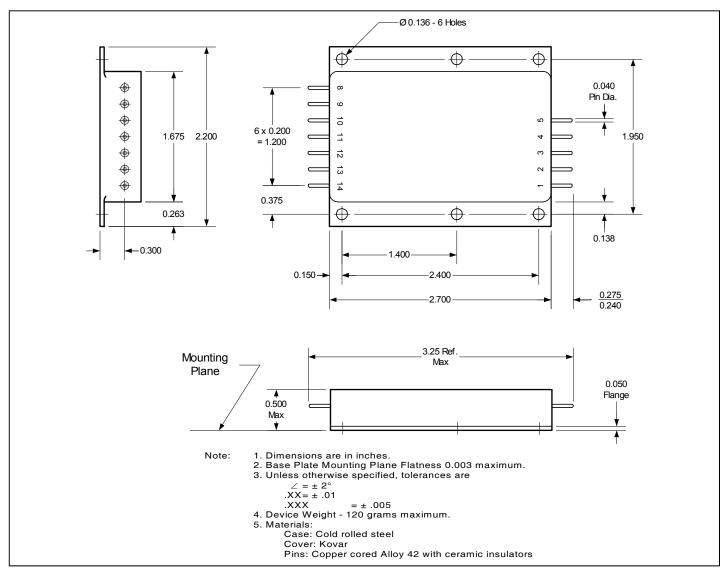

### **Mechanical Outline**

### **Pin Designation**

| Pin # | Designation  | Pin # | Designation                           |

|-------|--------------|-------|---------------------------------------|

| 1     | + Input      | 8     | NC                                    |

| 2     | Input Return | 9     | -12 / -15V <sub>DC</sub> Output       |

| 3     | Enable       | 10    | +12 /+15V <sub>DC</sub> Output Return |

| 4     | Sync In      | 11    | +12 / +15V <sub>DC</sub> Output       |

| 5     | NC           | 12    | Chassis                               |

| 6     |              | 13    | +5V <sub>DC</sub> Output              |

| 7     |              | 14    | Output Return                         |

# **Device Screening**

| Requirement                   | MIL-STD-883 Method               | No Suffix ②                      | CK @                             | EM 3                   |

|-------------------------------|----------------------------------|----------------------------------|----------------------------------|------------------------|

| Temperature Range             | —                                | -55°C to +85°C                   | -55°C to +85°C                   | -55°C to +85°C         |

| Element Evaluation            | MIL-PRF-38534                    | Class K                          | Class K                          | N/A                    |

| Non-Destructive Bond Pull     | 2023                             | Yes                              | Yes                              | N/A                    |

| Internal Visual               | 2017                             | Yes                              | Yes                              | 0                      |

| Temperature Cycle             | 1010                             | Cond C                           | Cond C                           | Cond C                 |

| Constant Acceleration         | 2001, Y1 Axis                    | 3000 Gs                          | 3000 Gs                          | 3000 Gs                |

| PIND                          | 2020                             | Cond A                           | Cond A                           | N/A                    |

| Burn-In                       | 1015                             | 320 hrs @ 125°C<br>(2 x 160 hrs) | 320 hrs @ 125°C<br>(2 x 160 hrs) | 48 hrs @ 125°C         |

| Final Electrical<br>(Group A) | MIL-PRF-38534<br>& Specification | -55°C, +25°C,<br>+85°C           | -55°C, +25°C,<br>+85°C           | -55°C, +25°C,<br>+85°C |

| PDA                           | MIL-PRF-38534                    | 2%                               | 2%                               | N/A                    |

| Seal, Fine and Gross          | 1014                             | Cond A, C                        | Cond A, C                        | Cond A                 |

| Radiographic                  | 2012                             | Yes                              | Yes                              | N/A                    |

| External Visual               | 2009                             | Yes                              | Yes                              | $\bigcirc$             |

#### Notes:

- ① Best commercial practice.

- ② CK is a DLA class K compliant without radiation performance. No suffix is a radiation rated device but not available as a DLA qualified SMD per MIL-PRF-38534.

- ③ Any Engineering Model (EM) build with the "EM" Suffix shall only be form, fit and functional equivalent to its Flight Model (FM) counterpart, and it may not meet the radiation performance. The EM Model shall not be expected comply with MIL-PRF-38534 flight quality/workmanship standards, and configuration control. An EM build may use electrical equivalent commercial grade components. IR HiRel will provide a list of non-compliance items upon request.

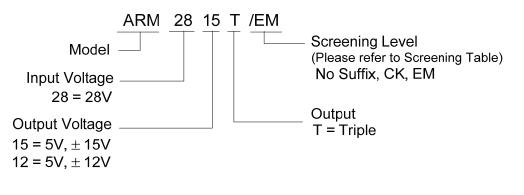

# Part Numbering

#### An Infineon Technologies Company

IR HiRel Headquarters: 101 N. Sepulveda Blvd., El Segundo, California 90245, USA Tel: (310) 252-7105 IR HiRel Leominster: 205 Crawford St., Leominster, Massachusetts 01453, USA Tel: (978) 534-5776 IR HiRel San Jose: 2520 Junction Avenue, San Jose, California 95134, USA Tel: (408) 434-5000 Data and specifications subject to change without notice.

#### **IMPORTANT NOTICE**

The information given in this document shall be in no event regarded as guarantee of conditions or characteristic. The data contained herein is a characterization of the component based on internal standards and is intended to demonstrate and provide guidance for typical part performance. It will require further evaluation, qualification and analysis to determine suitability in the application environment to confirm compliance to your system requirements.

With respect to any example hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind including without limitation warranties on non- infringement of intellectual property rights and any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's product and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of any customer's technical departments to evaluate the suitability of the product for the intended applications and the completeness of the product information given in this document with respect to applications.

For further information on the product, technology, delivery terms and conditions and prices, please contact your local sales representative or go to (<u>www.infineon.com/hirel)</u>.

#### WARNING

Due to technical requirements products may contain dangerous substances. For information on the types in question, please contact your nearest Infineon Technologies office.