## ModelGauge m3 Fuel Gauge

#### **General Description**

The MAX17047/MAX17050 incorporate the Maxim ModelGauge<sup>™</sup> m3 algorithm that combines the excellent short-term accuracy and linearity of a coulomb counter with the excellent long-term stability of a voltage-based fuel gauge, along with temperature compensation to provide industry-leading fuel-gauge accuracy. ModelGauge m3 cancels offset accumulation error in the coulomb counter, while providing better short-term accuracy than any purely voltage-based fuel gauge. Additionally, the ModelGauge m3 algorithm does not suffer from abrupt corrections that normally occur in coulomb-counter algorithms, since tiny continual corrections are distributed over time.

The device automatically compensates for aging, temperature, and discharge rate and provides accurate state of charge (SOC) in mAh or %, as well as time-to-empty over a wide range of operating conditions. The device provides two methods for reporting the age of the battery: reduction in capacity and cycle odometer.

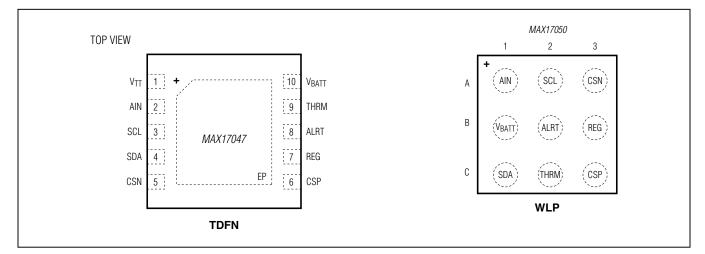

The device provides precision measurements of current, voltage, and temperature. Temperature of the battery pack is measured using an external thermistor supported by ratiometric measurements on an auxiliary input. A 2-wire (I<sup>2</sup>C) interface provides access to data and control registers. The MAX17047 is available in a lead(Pb)-free, 3mm x 3mm, 10-pin TDFN package. The MAX17050 is available in a 0.4mm pitch 9-bump WLP package.

#### Applications

| 2.5G/3G/4G Wireless  | Portable Game Players      |

|----------------------|----------------------------|

| Handsets             | e-Readers                  |

| Smartphones/PDAs     | Digital Still and Video    |

| Tablets and Handheld | Cameras                    |

| Computers            | Portable Medical Equipment |

#### Features

- Accurate Battery-Capacity and Time-To-Empty Estimation

- ♦ Temperature, Age, and Rate Compensated

- ♦ Does Not Require Empty, Full, or Idle States to Maintain Accuracy

- Precision Measurement System

- ♦ No Calibration Required

- ModelGauge m3 Algorithm

- ♦ Long-Term Influence by Voltage Fuel Gauge Cancels Coulomb-Counter Drift

- Short-Term Influence by Coulomb Counter Provides Excellent Linearity

- Adapts to Cell Characteristics

- External Temperature-Measurement Network

Actively Switched Thermistor Resistive Divider Reduces Current Consumption

- ♦ Low Quiescent Current

♦ 25µA Active, < 0.5µA Shutdown</li>

- Alert Indicator for SOC, Voltage, Temperature, and Battery Removal/Insertion Events

- AtRate Estimation of Remaining Capacity

- 2-Wire (I<sup>2</sup>C) Interface

- Tiny, Lead(Pb)-Free, 3mm x 3mm, 10-Pin TDFN Package or Tiny 0.4mm Pitch 9-Bump WLP Package

Ordering Information appears at end of data sheet.

For related parts and recommended products to use with this part, refer to: <u>www.maximintegrated.com/MAX17047.related</u>

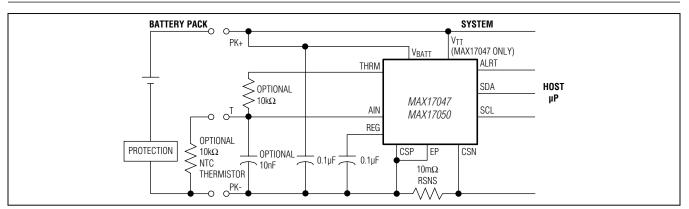

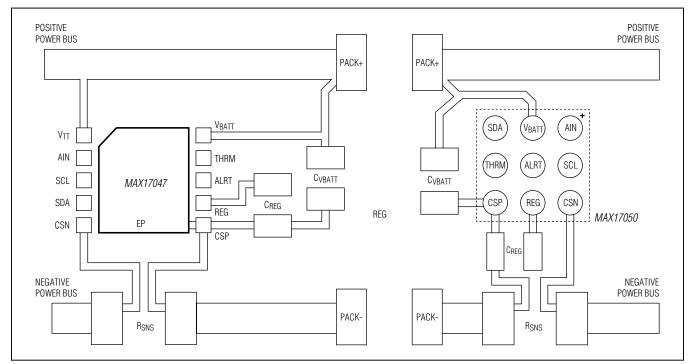

### **Simplified Operating Circuit**

ModelGauge is a trademark of Maxim Integrated Products, Inc.

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maximintegrated.com.

## **ModelGauge m3 Fuel Gauge**

#### **ABSOLUTE MAXIMUM RATINGS**

| VBATT, SDA, SCL, ALRT to CSP               | 0.3V to +6V                      |

|--------------------------------------------|----------------------------------|

| REG to CSP                                 | 0.3V to +2.2V                    |

| V <sub>TT</sub> to CSP                     | 0.3V to +6V                      |

| THRM, AIN to CSP                           | 0.3V to (V <sub>TT</sub> + 0.3V) |

| CSN to CSP                                 | 2V to +2V                        |

| Continuous Sink Current (V <sub>TT</sub> ) | 20mA                             |

| Continuous Sink Current (SCL, SDA, A       |                                  |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                 |

|-------------------------------------------------------|-----------------|

| TDFN (derate 24.4mW/°C above +70°C)                   | 1951.2mW        |

| WLP (derate 11.9mW/°C above +70°C)                    | 952.0mW         |

| Operating Temperature Range                           | 40°C to +85°C   |

| Junction Temperature                                  | +150°C          |

| Storage Temperature Range                             | -55°C to +125°C |

| Lead Temperature (soldering 10s)                      | +300°C          |

| Soldering Temperature (reflow)                        | +260°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### PACKAGE THERMAL CHARACTERISTICS (Note 1)

TDFN

WLP

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

### **ELECTRICAL CHARACTERISTICS**

$(V_{BATT} = 2.5V \text{ to } 4.5V, T_A = -20^{\circ}C \text{ to } +70^{\circ}C, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.)$  (Note 2)

| PARAMETER                                  | SYMBOL            | CONDITIONS                                      | MIN  | ТҮР    | МАХ  | UNITS           |

|--------------------------------------------|-------------------|-------------------------------------------------|------|--------|------|-----------------|

| Supply Voltage                             | V <sub>BATT</sub> | (Note 3)                                        | 2.5  |        | 4.5  | V               |

| Supply Current                             | I <sub>DD0</sub>  | Shutdown mode, $T_A \le +50^{\circ}C$           |      | 0.5    | 2    |                 |

| Supply Current                             | I <sub>DD1</sub>  | Active mode, average current                    |      | 25     | 42   | μA              |

| REG Regulation Voltage                     | V <sub>REG</sub>  |                                                 | 1.5  |        | 1.9  | V               |

| Magguramont Error V                        |                   | $T_{A} = +25^{\circ}C$                          | -7.5 |        | +7.5 | - mV            |

| Measurement Error, V <sub>BATT</sub>       | V <sub>GERR</sub> |                                                 | -20  |        | +20  |                 |

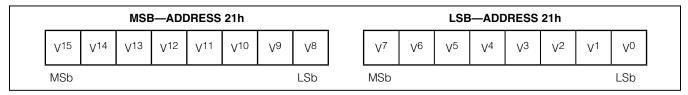

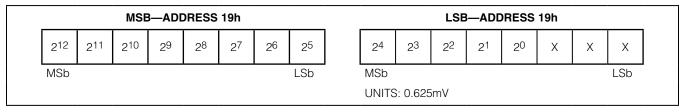

| Measurement Resolution, VBATT              | V <sub>LSb</sub>  |                                                 |      | 0.625  |      | mV              |

| V <sub>BATT</sub> Measurement Range        | V <sub>FS</sub>   |                                                 | 2.5  |        | 4.98 | V               |

| Input Resistance CSN, AIN                  |                   |                                                 | 15   |        |      | MΩ              |

| Ratiometric Measurement<br>Accuracy, AIN   | T <sub>GERR</sub> |                                                 | -0.5 |        | +0.5 | %               |

| Ratiometric Measurement<br>Resolution, AIN | T <sub>LSb</sub>  |                                                 |      | 0.0244 |      | % Full<br>Scale |

| Current Register Resolution                | I <sub>LSb</sub>  |                                                 |      | 1.5625 |      | μV              |

| Current Full-Scale Magnitude               | I <sub>FS</sub>   |                                                 |      | ±51.2  |      | mV              |

| Current Offset Error                       | IOERR             |                                                 |      | ±1.5   |      | μV              |

| Current Gain Error                         | IGERR             |                                                 | -1   |        | +1   | % of<br>Reading |

|                                            |                   | $V_{DD} = 3.6V \text{ at } T_A = +25^{\circ}C$  | -1   |        | +1   |                 |

| Time-Base Accuracy                         | t <sub>ERR</sub>  | $T_A = 0^{\circ}C \text{ to } +50^{\circ}C$     | -2.5 |        | +2.5 | %               |

|                                            |                   | $T_{A} = -20^{\circ}C \text{ to } +70^{\circ}C$ | -3.5 |        | +3.5 |                 |

## ModelGauge m3 Fuel Gauge

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{BATT} = 2.5V \text{ to } 4.5V, T_A = -20^{\circ}C \text{ to } +70^{\circ}C, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.)$  (Note 2)

| PARAMETER                                                       | SYMBOL            | CONDITIONS                                                                                                                           | MIN                   | TYP | MAX      | UNITS |

|-----------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|----------|-------|

| THRM Output Drive                                               |                   | $I_{OUT} = 0.5 \text{mA}$                                                                                                            | V <sub>TT</sub> - 0.1 |     |          | V     |

| THRM Precharge Time                                             | t <sub>PRE</sub>  |                                                                                                                                      | 8.48                  |     |          | ms    |

| SDA, SCL, ALRT<br>Input Logic High                              | V <sub>IH</sub>   |                                                                                                                                      | 1.5                   |     |          | V     |

| SDA, SCL, ALRT Input Logic Low                                  | VIL               |                                                                                                                                      |                       |     | 0.5      | V     |

| SDA, ALRT Output Logic Low                                      | V <sub>OL</sub>   | $I_{OL} = 4mA$                                                                                                                       |                       |     | 0.4      | V     |

| SDA, ALRT Pulldown Current                                      | I <sub>PD</sub>   | Active mode, $V_{SDA} = 0.4V$ , $V_{ALRT} = 0.4V$                                                                                    | 0.05                  | 0.2 | 0.4      | μA    |

| ALRT Leakage                                                    |                   |                                                                                                                                      |                       |     | 1        | μA    |

| THRM Operating Range                                            |                   |                                                                                                                                      | 2.5                   |     | $V_{TT}$ | V     |

| Battery-Removal Detection<br>Threshold—V <sub>AIN</sub> Rising  | V <sub>DETR</sub> | V <sub>THRM</sub> - V <sub>AIN</sub>                                                                                                 | 40                    | 125 | 200      | mV    |

| Battery-Removal Detection<br>Threshold—V <sub>AIN</sub> Falling | V <sub>DETF</sub> | V <sub>THRM</sub> - V <sub>AIN</sub>                                                                                                 | 70                    | 150 | 230      | mV    |

| Battery-Removal Detection<br>Comparator Delay                   | <sup>t</sup> TOFF | V <sub>AIN</sub> step from 70% to 100% of V <sub>THRM</sub> to<br>ALRT falling; Alrtp = logic 0;<br>EnAIN = logic 1; FTHRM = logic 1 |                       |     | 100      | μs    |

| External AIN Capacitance                                        |                   | $R_{THM} = 10k\Omega NTC$                                                                                                            |                       |     | 100      | nF    |

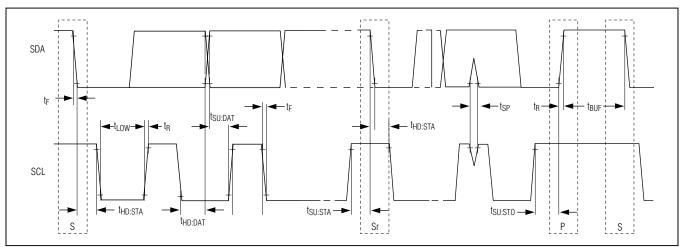

### **ELECTRICAL CHARACTERISTICS (2-WIRE INTERFACE)**

(2.5V  $\leq$  V<sub>BATT</sub>  $\leq$  4.5V, **T<sub>A</sub> = -20°C to +70°C**.) (Note 2)

| PARAMETER                                        | SYMBOL              | CONDITIONS   | MIN                       | ТҮР | MAX | UNITS |

|--------------------------------------------------|---------------------|--------------|---------------------------|-----|-----|-------|

| SCL Clock Frequency                              | fSCL                | (Note 4)     | 0                         |     | 400 | kHz   |

| Bus Free Time Between a STOP and START Condition | t <sub>BUF</sub>    |              | 1.3                       |     |     | μs    |

| Hold Time (Repeated)<br>START Condition          | <sup>t</sup> HD:STA | (Note 5)     | 0.6                       |     |     | μs    |

| Low Period of SCL Clock                          | t <sub>LOW</sub>    |              | 1.3                       |     |     | μs    |

| High Period of SCL Clock                         | thigh               |              | 0.6                       |     |     | μs    |

| Setup Time for a Repeated START Condition        | <sup>t</sup> SU:STA |              | 0.6                       |     |     | μs    |

| Data Hold Time                                   | thd:dat             | (Notes 6, 7) | 0                         |     | 0.9 | μs    |

| Data Setup Time                                  | t <sub>SU:DAT</sub> | (Note 6)     | 100                       |     |     | ns    |

| Rise Time of Both SDA and SCL Signals            | t <sub>R</sub>      |              | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

## ModelGauge m3 Fuel Gauge

### ELECTRICAL CHARACTERISTICS (2-WIRE INTERFACE) (continued)

(2.5V  $\leq$  V\_BATT  $\leq$  4.5V,  $\textbf{T_A}$  = -20°C to +70°C.) (Note 2)

| PARAMETER                                        | SYMBOL           | CONDITIONS | MIN                       | TYP | MAX | UNITS |

|--------------------------------------------------|------------------|------------|---------------------------|-----|-----|-------|

| Fall Time of Both SDA and SCL<br>Signals         | t <sub>F</sub>   |            | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

| Setup Time for STOP Condition                    | tsu:sto          |            | 0.6                       |     |     | μs    |

| Spike Pulse Widths<br>Suppressed by Input Filter | t <sub>SP</sub>  | (Note 8)   | 0                         |     | 50  | ns    |

| Capacitive Load for Each Bus<br>Line             | CB               | (Note 9)   |                           |     | 400 | рF    |

| SCL, SDA Input Capacitance                       | C <sub>BIN</sub> |            |                           |     | 60  | pF    |

**Note 2:** Specifications are 100% tested at  $T_A = +25$ °C. Limits over the operating range are guaranteed by design and characterization.

Note 3: All voltages are referenced to CSP.

Note 4: Timing must be fast enough to prevent the device from entering shutdown mode due to bus low for a period > 45s minimum.

Note 5: f<sub>SCL</sub> must meet the minimum clock low time plus the rise/fall times.

Note 6: The maximum t<sub>HD:DAT</sub> has only to be met if the device does not stretch the low period (t<sub>LOW</sub>) of the SCL signal.

Note 7: This device internally provides a hold time of at least 100ns for the SDA signal (referred to the minimum VIH of the SCL signal) to bridge the undefined region of the falling edge of SCL.

Note 8: Filters on SDA and SCL suppress noise spikes at the input buffers and delay the sampling instant.

Note 9:  $C_B$ —total capacitance of one bus line in pF.

### **I<sup>2</sup>C Bus Timing Diagram**

Figure 1. I<sup>2</sup>C Bus Timing Diagram

### **ModelGauge m3 Fuel Gauge**

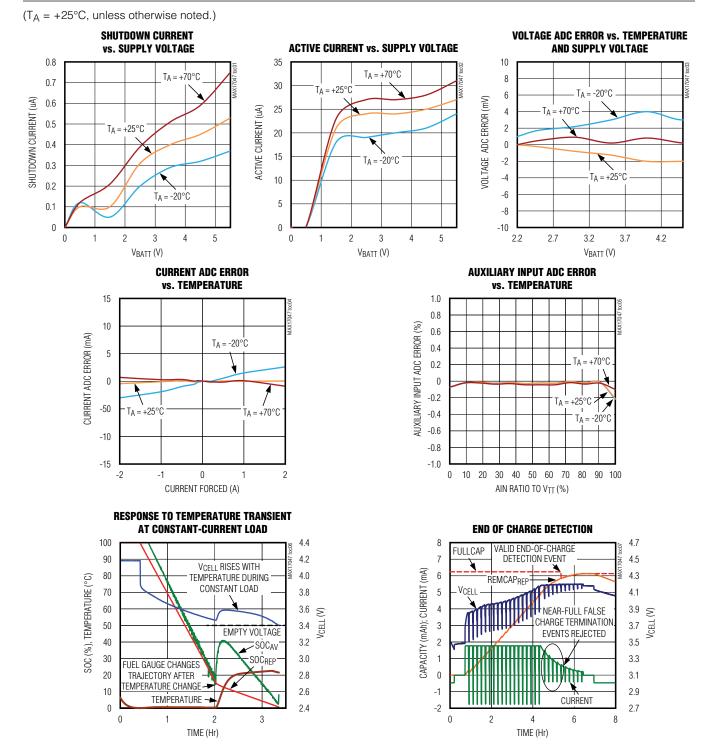

### **Typical Operating Characteristics**

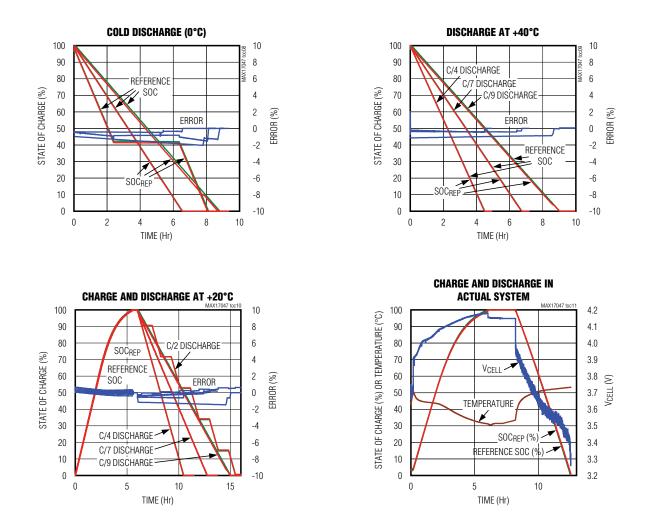

### **ModelGauge m3 Fuel Gauge**

### **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

## ModelGauge m3 Fuel Gauge

### **Pin/Bump Configurations**

### **Pin/Bump Descriptions**

| PIN  | BUMP |                   |                                                                                                                                                                                                                                                                                        |

|------|------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDFN | WLP  | NAME              | FUNCTION                                                                                                                                                                                                                                                                               |

| 1    |      | V <sub>TT</sub>   | Supply Input for Thermistor Bias Switch (MAX17047 Only.) $V_{TT}$ is connected internally to $V_{BATT}$ on the MAX17050. Connect to supply for ratiometric AIN pin-voltage measurements. In most applications, connect $V_{TT}$ to $V_{BATT}$ .                                        |

| 2    | A1   | AIN               | Auxiliary Voltage Input. Auxiliary voltage input from external thermal-measurement network. AIN also provides battery insertion/removal detection. Connect to V <sub>BATT</sub> , if not used.                                                                                         |

| 3    | A2   | SCL               | Serial Clock Input. 2-wire clock line. Input only.                                                                                                                                                                                                                                     |

| 4    | C1   | SDA               | Serial Data Input/Out. 2-wire data line. Open-drain output driver.                                                                                                                                                                                                                     |

| 5    | A3   | CSN               | Sense Resistor Connection. System ground connection and sense resistor input.                                                                                                                                                                                                          |

| 6    | C3   | CSP               | Chip Ground and Sense Resistor Input                                                                                                                                                                                                                                                   |

| 7    | B3   | REG               | Voltage Regulator Bypass. Connect a 0.1µF capacitor from REG to CSP.                                                                                                                                                                                                                   |

| 8    | B2   | ALRT              | Alert Indication. An open-drain n-channel output used to indicate specified condition thresholds have been met. A 200k $\Omega$ pullup resistor to power rail is required for use as an output. Alternatively, ALRT can operate as a shutdown input with the output function disabled. |

| 9    | C2   | THRM              | Thermistor Bias Connection. Supply for thermistor resistor-divider. Connect to the high side of the thermistor/resistor-divider. THRM connects internally to $V_{TT}$ during temperature measurement.                                                                                  |

| 10   | B1   | V <sub>BATT</sub> | Power-Supply and Battery Voltage-Sense Input. Kelvin connect to positive terminal of battery pack. Bypass with a $0.1\mu$ F capacitor to CSP.                                                                                                                                          |

|      | _    | EP                | Exposed Pad (TDFN Only). Connect to CSP.                                                                                                                                                                                                                                               |

### ModelGauge m3 Fuel Gauge

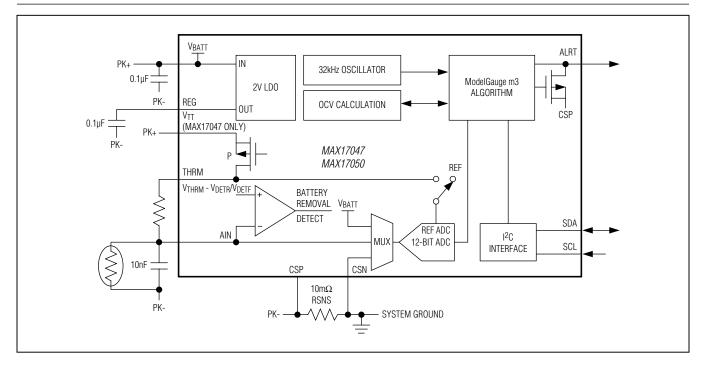

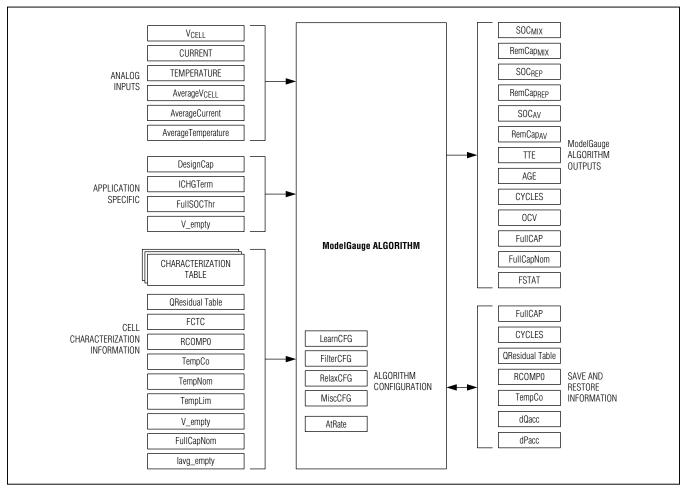

#### **Block Diagram**

#### **Detailed Description**

The MAX17047/MAX17050 incorporate the Maxim ModelGauge m3 algorithm that combines the excellent short-term accuracy and linearity of a coulomb counter with the excellent long-term stability of a voltage-based fuel gauge, along with temperature compensation to provide industry-leading fuel-gauge accuracy. ModelGauge m3 cancels offset accumulation error in the coulomb counter, while providing better short-term accuracy than any purely voltage-based fuel gauge. Additionally, the ModelGauge m3 algorithm does not suffer from abrupt corrections that normally occur in coulomb-counter algorithms, since tiny continual corrections are distributed over time.

The device automatically compensates for aging, temperature, and discharge rate and provides accurate state-of-charge (SOC) in mAh or % over a wide range of operating conditions. The device provides two methods for reporting the age of the battery: reduction in capacity and cycle odometer.

The device provides precision measurements of current, voltage, and temperature. Temperature of the battery

Maxim Integrated

pack is measured using an external thermistor supported by ratiometric measurements on an auxiliary input. A 2-wire (I<sup>2</sup>C) interface provides access to data and control registers. The MAX17047 is available in a 3mm x 3mm, 10-pin TDFN package. The MAX17050 is available in a 0.4mm pitch 9-bump WLP package.

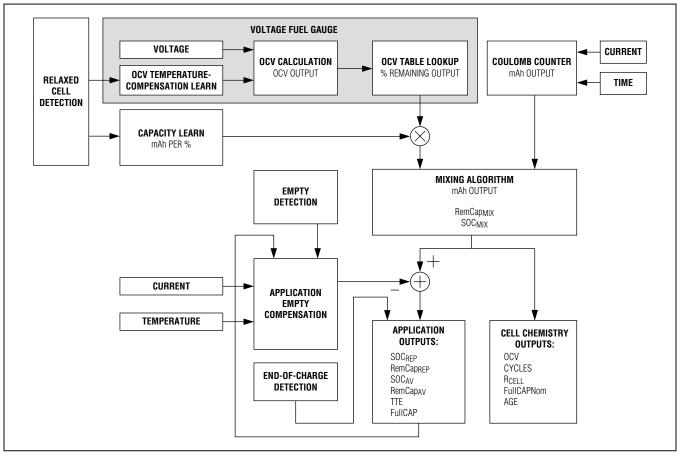

#### ModelGauge m3 Algorithm

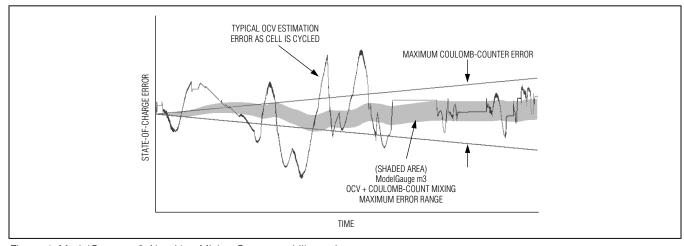

The ModelGauge m3 algorithm combines a high-accuracy coulomb counter with a voltage fuel gauge (VFG) as represented in Figure 2.

Classical coulomb-counter-based fuel gauges have excellent linearity and short-term performance. However, they suffer from drift due to the accumulation of the offset error in the current-sense measurement. Although the offset error is often very small, it cannot be eliminated, causes the reported capacity error to increase over time, and requires periodic corrections. Corrections are usually performed at full or empty. Some other systems also use the relaxed battery voltage to perform corrections. These systems determine the SOC based on the battery voltage after a long time of no current flow. Both have the same limitation: if the correction condition is not

### ModelGauge m3 Fuel Gauge

Figure 2. ModelGauge m3 Overview

observed over time in the actual application, the error in the system is **boundless**. The performance of classic coulomb counters is dominated by the accuracy of such corrections.

Classical voltage-measurement-based SOC estimation has poor accuracy due to inadequate cell modeling, but does not accumulate offset error over time.

The device includes an advanced VFG, which estimates open-circuit voltage (OCV), even during current flow, and simulates the nonlinear internal dynamics of a lithium-ion (Li+) battery to determine the SOC with improved accuracy. The model considers the time effects of a battery caused by the chemical reactions and impedance in the battery to determine SOC based on table lookup. This SOC estimation does not accumulate offset error over time.

The ModelGauge m3 algorithm combines a high-accuracy coulomb counter with a VFG. The complementary

Maxim Integrated

combined result eliminates the weaknesses of both the coulomb counter and the VFG, while providing the strengths of both. A mixing algorithm combines the VFG capacity with the coulomb counter and weighs each result so that both are used optimally to determine the battery state. In this way, the VFG capacity result is used to continuously make small adjustments to the battery state, canceling the coulomb-counter drift.

The ModelGauge m3 algorithm uses this battery state information and accounts for temperature, battery current, age, and application parameters to determine the remaining capacity available to the system.

The ModelGauge m3 algorithm continually adapts to the cell and application through independent learning routines. As the cell ages, its change in capacity is monitored and updated and the VFG dynamics adapt based on cell-voltage behavior in the application.

### ModelGauge m3 Fuel Gauge

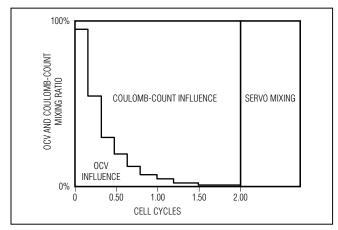

#### **OCV Estimation and Coulomb-Count Mixing**

The core of the ModelGauge m3 algorithm is a mixing algorithm that combines the OCV state estimation with the coulomb counter. After power-on reset of the IC, coulomb-count accuracy is unknown. The OCV state estimation is weighted heavily compared to the coulomb-count output. As the cell progresses through cycles in the application, coulomb-counter accuracy improves and the mixing algorithm alters the weighting so that the coulomb-counter result is dominant. From this point forward, the IC switches to servo mixing. Servo mixing provides a fixed magnitude continuous error correction to the coulomb count, up or down, based on the direction of error from the OCV estimation. This allows differences between the coulomb count and OCV estimation to be corrected quickly. See Figure 3.

Figure 3. ModelGauge m3 OCV and Coulomb-Count Mixing

The resulting output from the mixing algorithm does not suffer drift from current measurement offset error and is more stable than a stand-alone OCV estimation algorithm; see Figure 4. Initial accuracy depends on the relaxation state of the cell. The highest initial accuracy is achieved with a fully relaxed cell.

#### **Fuel-Gauge Empty Compensation**

As the temperature and discharge rate of an application changes, the amount of charge available to the application also changes. The ModelGauge m3 algorithm distinguishes between remaining capacity of the cell (RemCap<sub>MIX</sub>) and remaining capacity of the application (RemCap<sub>AV</sub>) and reports both results to the user.

**Fuel-Gauge Learning and Age Support** The device periodically makes internal adjustments to cell characterization and application information to remove initial error and maintain accuracy as the cell ages. These adjustments always occur as small undercorrections to prevent instability of the system and prevent any noticeable jumps in the fuel-gauge outputs. Learning occurs automatically without any input from the host. To maintain learned accuracy through power loss, the host must periodically save learned information and then restore after power is returned. See the <u>Power-Up</u> and Power-On Reset section for details:

• Full Capacity Available to Application (FullCAP). This is the total capacity available to the application at full. FullCAP is updated near the end of charging when termination is detected. See the <u>End-of-Charge</u> Detection section.

Figure 4. ModelGauge m3 Algorithm Mixing Conceptual Illustration

## ModelGauge m3 Fuel Gauge

- Cell Capacity (FullCapNom). This is the total cell capacity at full, according to the VFG. This includes some capacity that is not available to the application at high loads and/or low temperature. The device periodically compares percent change based on OCV measurement vs. coulomb-count change as the cell charges and discharges. This information allows the device to maintain an accurate estimation of the cell's capacity in mAh as the cell ages.

- Voltage Fuel-Gauge Adaptation. The device observes the battery's relaxation response and adjusts the dynamics of the VFG. This adaptation adjusts the RCOMP0 register during qualified cell relaxation events.

- Empty Learning. The device updates internal data whenever cell empty is detected (V<sub>CELL</sub> < V\_empty) to account for cell age or other cell deviations from the characterization information. This maintains SOC accuracy as the battery ages.</li>

#### **Determining Fuel-Gauge Accuracy**

To determine the true accuracy of a fuel gauge, as experienced by end users, the battery should be exercised in a dynamic manner. The end-user accuracy cannot be understood with only simple cycles.

To challenge a correction-based fuel gauge, such as a coulomb counter, test the battery with partial loading sessions. For example, a typical user may operate the device for 10min and then stop use for an hour or more. A robust test method includes these kinds of sessions many times at various loads, temperatures, and duration. Refer to Application Note 4799: *Cell Characterization Procedure for a ModelGauge m3 Fuel Gauge*.

#### Initial Accuracy

The device uses the first voltage reading after power-up or after cell insertion to determine the starting output of the fuel gauge. It is assumed that the cell is fully relaxed prior to this reading; however, this is not always the case. If the cell was recently charged or discharged, the voltage measured by the device may not represent the true state of charge of the cell, resulting in initial error in the fuel gauge outputs. In most cases, this error is minor and is quickly removed by the fuel gauge algorithm during normal operation.

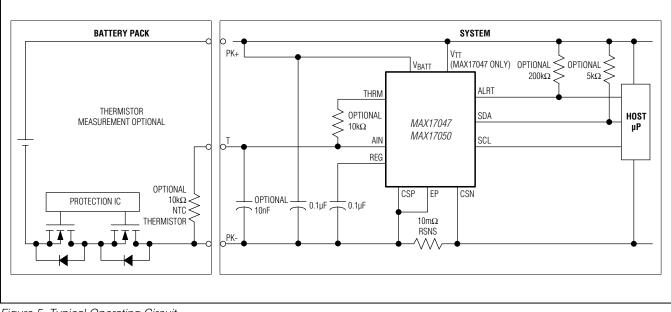

### **Typical Operating Circuit**

The device is designed to mount outside the cell pack that it monitors. Voltage of the battery pack is measured directly at the pack terminals by the  $V_{BATT}$  and CSP connections. Current is measured by an external sense resistor placed between the CSP and CSN pins. An external resistor-divider network allows the device to measure temperature of the cell pack by monitoring the AIN pin. The THRM pin provides a strong pullup for the resistor-divider that is internally disabled when temperature is not being measured.

Communication to the host occurs over a standard I<sup>2</sup>C interface. SCL is an input from the host, and SDA is an open-drain I/O pin that requires an external pullup. The ALRT pin is an output that can be used as an external interrupt to the host processor if certain application conditions are detected. ALRT can also function as an input, allowing the host to shut down the device. This pin is also open drain and requires an external pullup resistor. Figure 5 is the typical operating circuit.

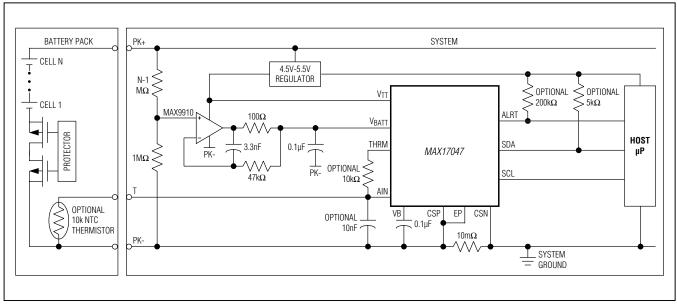

#### **Multicell Circuit**

The MAX17047 can be used in multicell pack applications. A resistor-divider network divides the pack voltage down so that the IC monitors the equivalent voltage of a single cell. The MAX9910 buffers the divider output so that loading by the MAX17047 does not affect accuracy.  $V_{TT}$  must be connected to a regulated supply in the system to prevent overloading the MAX9910. Contact the factory for a MAX17050 multicell application circuit. See Figure 6.

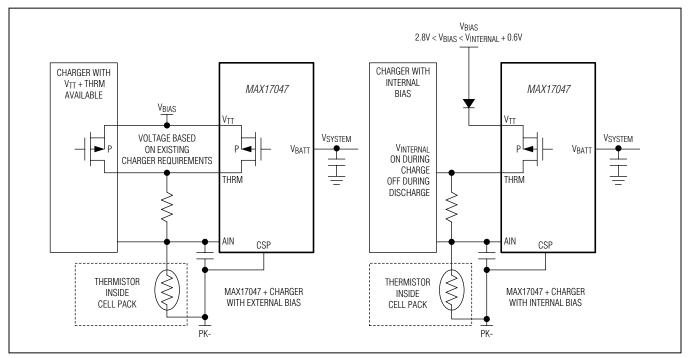

#### **Thermistor Sharing Circuit**

The MAX17047 can share the cell thermistor circuit with the system charger. In this circuit, there is a single thermistor inside the cell pack and a single bias resistor external to the cell pack. The device shares the same external bias as the charger circuit and measurement point on the thermistor. In this configuration, each device can measure temperature individually or simultaneously without interference. Alternatively, if the bias voltage in the charger circuit is not available to the device, a separate bias voltage on the V<sub>TT</sub> pin can be used. For proper operation, the separate bias voltage must be larger than the minimum operating voltage of the device, but no larger than one diode drop above the charger circuit bias voltage. The MAX17050 cannot be operated in his configuration. See Figure 7.

## ModelGauge m3 Fuel Gauge

Figure 5. Typical Operating Circuit

Figure 6. Multicell Application Circuit

### ModelGauge m3 Fuel Gauge

#### **Recommended Layout**

Proper circuit layout (see Figure 8) is essential for measurement accuracy when using the MAX17047/MAX17050 ModelGauge m3 ICs. The recommended layout guidelines are as follows:

- Mount R<sub>SNS</sub> as close as possible to PACK-. The device shares both voltage and current measurements on the CSP pin. Therefore, it is important to limit the amount of trace resistance between the currentsensing resistor and PACK-.

- 2)  $V_{BATT}$  trace should make a Kelvin connection to PACK+. The device shares the  $V_{BATT}$  pin for both voltage measurement and IC power. Limiting the voltage loss through this trace is important to voltage measurement accuracy. PCB resistance that cannot be removed can be compensated for during characterization of the application cell.

- 3) CSN and CSP traces should make Kelvin connections to R<sub>SNS</sub>. The device measures current differentially through the CSN and CSP pins. Any shared highcurrent paths on these traces will affect currentmeasurement gain accuracy. PCB resistance that cannot be removed can be compensated for during characterization of the application cell.

- V<sub>BATT</sub> capacitor trace loop area should be minimized. The device shares the V<sub>BATT</sub> pin for both voltage measurement and IC power. Limiting noise at the V<sub>BATT</sub> pin is important to current-measurement accuracy.

- 5) REG capacitor trace loop area should be minimized. The helps filter any noise from the internal regulated supply.

- 6) There are no limitations on any other IC connection. Connections to THRM, ALRT, SDA, SCL, V<sub>TT</sub>, and AIN, as well as any external components mounted to these pins, have no special layout requirements.

Figure 7. Operating Circuits that Share Pack Thermistor with System Charger

### ModelGauge m3 Fuel Gauge

Figure 8. Proper Board Layout

#### ModelGauge m3 Registers

To calculate accurate results, ModelGauge m3 requires information about the cell, the application, and real-time information measured by the device. Figure 9 shows all inputs and outputs to the algorithm grouped by category. Analog input registers are the real-time measurements of voltage, temperature, and current performed by the device. Application-specific registers are programmed by the customer to reflect the operation of the application. The Cell Characterization Information registers hold characterization data that models the behavior of the cell over the operating range of the application. The Algorithm Configuration registers allow the host to adjust performance of the device for its application. The Save and Restore registers allow an application to maintain accuracy of the algorithm after the device has been power cycled. The following sections describe each register in detail.

### ModelGauge Algorithm Output Registers

The following registers hold the output results from the ModelGauge m3 algorithm.

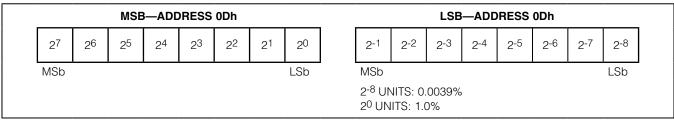

#### SOC<sub>MIX</sub> Register (0Dh)

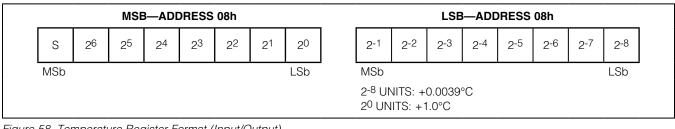

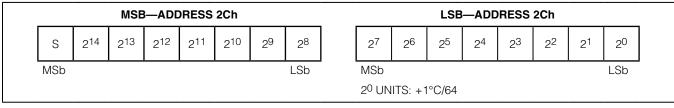

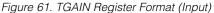

The SOC<sub>MIX</sub> register holds the calculated present state of charge of the cell before any empty compensation adjustments are performed. The register value is stored as a percentage with a resolution of 0.0039% per LSb. If an 8-bit state-of-charge value is desired, the host can discard the lower byte and use only the upper byte of the register with a resolution of 1.0%. Figure 10 shows the SOC<sub>MIX</sub> register format.

### ModelGauge m3 Fuel Gauge

Figure 9. ModelGauge m3 Register Map

## ModelGauge m3 Fuel Gauge

#### RemCap<sub>MIX</sub> Register (0Fh)

The RemCap<sub>MIX</sub> register holds the calculated remaining capacity of the cell before any empty compensation adjustments are performed. The value is stored in terms of  $\mu$ Vh and must be divided by the application sense-resistor value to determine remaining capacity in mAh. Figure 11 shows the RemCap<sub>MIX</sub> register format.

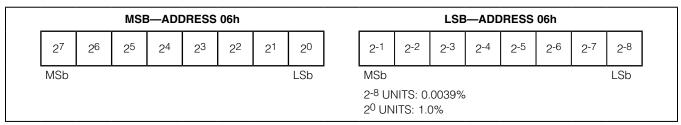

#### **SOC<sub>REP</sub> Register (06h)**

$SOC_{REP}$  is a filtered version of the  $SOC_{AV}$  register that prevents large jumps in the reported value caused by changes in the application such as abrupt changes in load current. The register value is stored as a percentage with a resolution of 0.0039% per LSb. If an 8-bit SOC value is desired, the host can discard the lower byte and

use only the upper byte of the register with a resolution of 1.0%. Figure 12 shows the SOC<sub>REP</sub> register format.

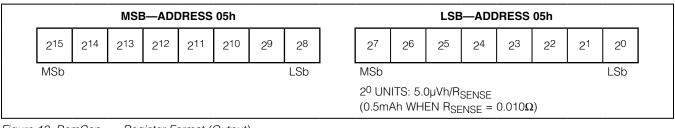

#### RemCap<sub>REP</sub> Register (05h)

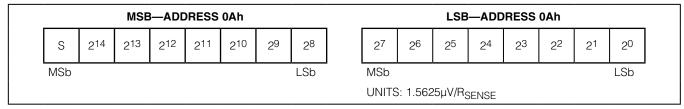

RemCap<sub>REP</sub> is a filtered version of the RemCap<sub>AV</sub> register that prevents large jumps in the reported value caused by changes in the application such as abrupt changes in load current. The value is stored in terms of  $\mu$ Vh and must be divided by the application sense-resistor value to determine remaining capacity in mAh. During application idle periods where the AverageCurrent Register value is less than ±6 LSbs, RemCap<sub>REP</sub> does not change. The measured current during this period is still accumulated into RemCap<sub>MIX</sub> and is slowly reflected in RemCap<sub>REP</sub> once cell loading or charging occurs. Figure 13 shows the RemCap<sub>REP</sub> register format.

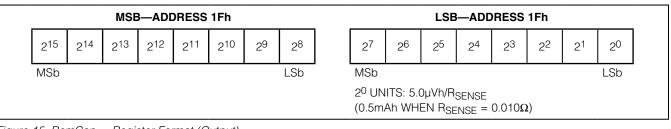

Figure 11. RemCap<sub>MIX</sub> Register Format (Output)

Figure 13. RemCap<sub>REP</sub> Register Format (Output)

### **ModelGauge m3 Fuel Gauge**

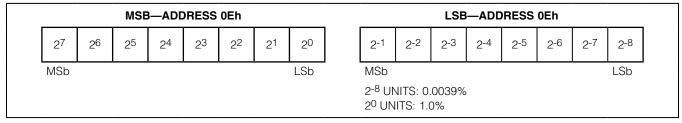

#### SOC<sub>AV</sub> Register (0Eh)

The SOC<sub>AV</sub> register holds the calculated present state of charge of the cell based on all inputs from the ModelGauge m3 algorithm including empty compensation. The register value is stored as a percentage with a resolution of 0.0039% per LSb. If an 8-bit state-of-charge value is desired, the host can discard the lower byte and use only the upper byte of the register with a resolution of 1.0%. The SOC<sub>AV</sub> register value is an unfiltered calculation. Jumps in the value can be caused by changes in the application such as abrupt changes in load current. Figure 14 shows the SOC<sub>AV</sub> register format.

#### RemCap<sub>AV</sub> Register (1Fh)

The RemCap<sub>AV</sub> register holds the calculated remaining capacity of the cell based on all inputs from the ModelGauge m3 algorithm including empty compensation. The value is stored in terms of  $\mu$ Vh and must be divided by the application sense-resistor value to determine the remaining capacity in mAh. The register

value is an unfiltered calculation. Jumps in the value can be caused by changes in the application such as abrupt changes in load current. Figure 15 shows the RemCap<sub>AV</sub> register format.

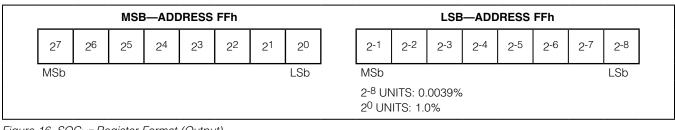

#### SOC<sub>VF</sub> Register (FFh)

The SOC<sub>VF</sub> register holds the calculated present SOC of the battery according to the voltage fuel gauge. The register value is stored as a percentage with a resolution of 0.0039% per LSb. If an 8-bit SOC value is desired, the host can discard the lower byte and use only the upper byte of the register with a resolution of 1.0%. Figure 16 shows the SOC<sub>VF</sub> register format.

#### **TTE Register (11h)**

The TTE register holds the estimated time to empty for the application under present conditions. The TTE value is determined by dividing the RemCap<sub>AV</sub> register by the AverageCurrent register. The result is stored in the TTE register with a resolution of 5.625s per LSb.

Figure 14. SOC<sub>AV</sub> Register Format (Output)

Figure 16. SOC<sub>VF</sub> Register Format (Output)

### ModelGauge m3 Fuel Gauge

#### **Cycles Register (17h)**

Alternatively, the TTE register can be used to estimate time to empty for any given current load. Whenever the AtRate register is programmed to a negative number, representing a discharge current, the TTE register displays the estimated time to empty for the application based on the AtRate register value. Figure 17 shows the TTE register format.

#### Age Register (07h)

The Age register contains a calculated percentage value of the application's present cell capacity compared to its expected capacity. The result can be used by the host to gauge the cell's health as compared to a new cell of the same type. The result is displayed as a percentage value from 0 to 256% with a 0.0039% LSb. Figure 18 shows the Age register format. The equation for the register output is:

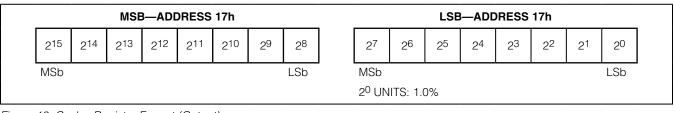

Age Register = 100% x (FullCAP Register/ DesignCap Register) The Cycles register accumulates total percent change in the cell during both charging and discharging. The result is stored as a total count of full charge/discharge cycles. For example, a full charge/discharge cycle results in the Cycles register incrementing by 100%. The Cycles register has a full range of 0 to 65535% with a 1% LSb. This register is reset to 0% at power-up. To maintain the lifetime cycle count of the cell, this register must be periodically saved by the host and rewritten to the device at power-up. See the <u>Save and Restore Registers</u> section for details. See Figure 19 for the Cycles register format.

#### **VFOCV Register (FBh)**

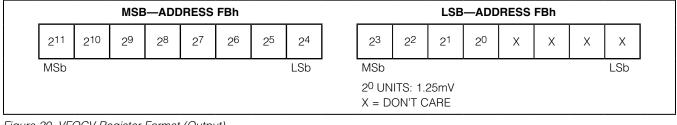

The VFOCV register contains the raw open-circuit voltage output of the voltage fuel gauge. This value is used in other internal calculations and can be read for debug purposes. The result is a 12-bit value ranging from 2.5V to 5.119V where 1 LSb is 1.25mV. The bottom 4 bits of this register are don't care bits. See <u>Figure 20</u> for the VFOCV register format.

|   |      |                | MSE            | 3—ADI | DRESS | 11h            |    |                |                   |                | LSE  | B—ADE | RESS            | 11h |                 |     |                 |

|---|------|----------------|----------------|-------|-------|----------------|----|----------------|-------------------|----------------|------|-------|-----------------|-----|-----------------|-----|-----------------|

| 2 | 210  | 2 <sup>9</sup> | 2 <sup>8</sup> | 27    | 26    | 2 <sup>5</sup> | 24 | 2 <sup>3</sup> |                   | 2 <sup>2</sup> | 21   | 20    | 2 <sup>-1</sup> | 2-2 | 2 <sup>-3</sup> | 2-4 | 2 <sup>-5</sup> |

| M | /ISb |                |                |       |       |                |    | LSb            | 3                 | MSb            |      |       |                 |     | 1               |     | LSb             |

|   |      |                |                |       |       |                |    |                | 2 <sup>0</sup> UN | ITS: 3.0       | Omin |       |                 |     |                 |     |                 |

Figure 17. TTE Register Format (Output)

| MSB—ADDRESS 07h |    |                |    |                |                |    |     |  |          | LSB—ADDRESS 07h |                 |     |                 |     |     |                 |  |  |

|-----------------|----|----------------|----|----------------|----------------|----|-----|--|----------|-----------------|-----------------|-----|-----------------|-----|-----|-----------------|--|--|

| 27              | 26 | 2 <sup>5</sup> | 24 | 2 <sup>3</sup> | 2 <sup>2</sup> | 21 | 20  |  | 2-1      | 2-2             | 2 <sup>-3</sup> | 2-4 | 2 <sup>-5</sup> | 2-6 | 2-7 | 2 <sup>-8</sup> |  |  |

| MSb             |    |                |    |                |                |    | LSb |  | MSb      |                 |                 |     |                 |     |     | LSb             |  |  |

|                 |    |                |    |                |                |    |     |  | ITS: 1.0 |                 |                 |     |                 |     |     |                 |  |  |

Figure 18. Age Register Format (Output)

Figure 19. Cycles Register Format (Output)

### **ModelGauge m3 Fuel Gauge**

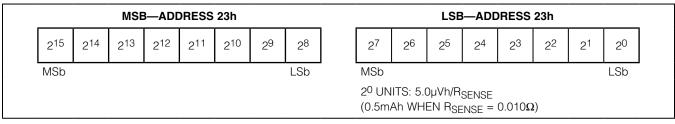

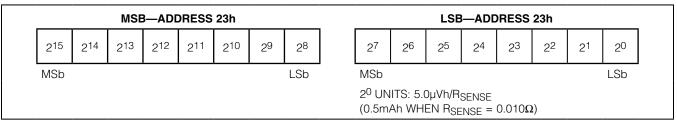

#### FullCapNom Register (23h)

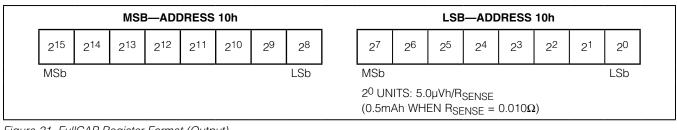

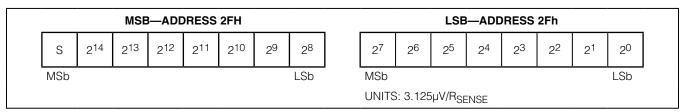

#### **FullCAP Register (10h)**

This register holds the ModelGauge m3 algorithm calculated full capacity of the cell under best-case conditions (light load, hot). A new full-capacity value is calculated after the end of every charge cycle in the application. The value is stored in terms of  $\mu$ Vh and must be divided by the application sense-resistor value to determine capacity in mAh. Figure 21 is the FullCAP register format. See the End-of-Charge Detection

This register holds the calculated full capacity of the cell, not including temperature and charger tolerance. New full capacity values are calculated periodically by the IC during operation. The value is stored in terms of  $\mu$ Vh and must be divided by the application sense resistor value to determine capacity in mAh. This register is used to calculate the outputs of the ModelGauge m3 algorithm and is available to the user only for debug. Figure 22 is the FullCapNom register format.

Figure 20. VFOCV Register Format (Output)

Figure 21. FullCAP Register Format (Output)

Figure 22. FullCapNom Register Format (Output)

### ModelGauge m3 Fuel Gauge

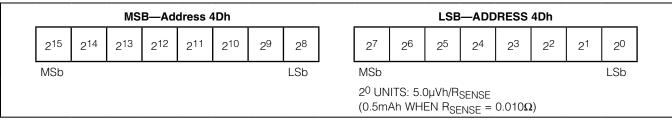

#### **QH Register (4Dh)**

The QH register displays the raw coulomb count generated by the device. This register is used internally as an input to the mixing algorithm. Monitoring changes in QH over time can be useful for debugging device operation. The QH register is set to 0000h at power-up. The QH register format is shown in Figure 23.

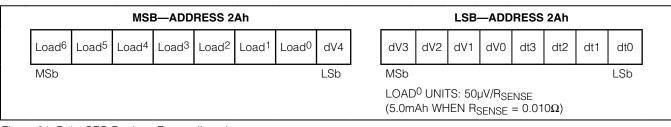

#### **Application-Specific Registers**

The following registers define the behavior of the application. They must be programmed by the user before the ModelGauge m3 algorithm is accurate. Any changes to these register values require recharacterization of the cell.

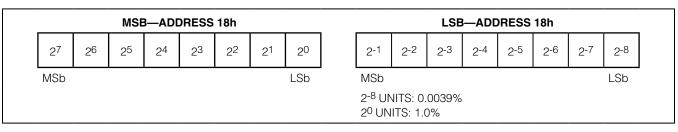

#### DesignCap Register (18h)

The DesignCap register holds the expected capacity of the cell. This value is used to determine age and health of the cell by comparing against the calculated present capacity stored in the FullCAP register. DesignCap has an LSb equal to  $5.0\mu$ Vh and a full range of 0 to 327.68mVh. The user should multiply the mAh capacity of the cell by the sense resistor value to determine the  $\mu$ Vh value to store in the DesignCap register. The DesignCap register format is shown in Figure 24.

#### FullSOCThr Register (13h)

The FullSOCThr register gates detection of end-ofcharge. SOC<sub>VF</sub> must be larger than the FullSOCThr value before ICHGTerm is compared to the AverageCurrent register value. The recommended FullSOCThr register setting for most applications is 95%. See the ICHGTerm register description for details. The FullSOCThr register is 70% at power-up. Figure 25 is the FullSOCThr register format.

Figure 23. QH Register Format (Output)

Figure 24. DesignCap Register Format (Input)

Figure 25. FullSOCThr Register Format (Input)

## **ModelGauge m3 Fuel Gauge**

#### **End-of-Charge Detection**

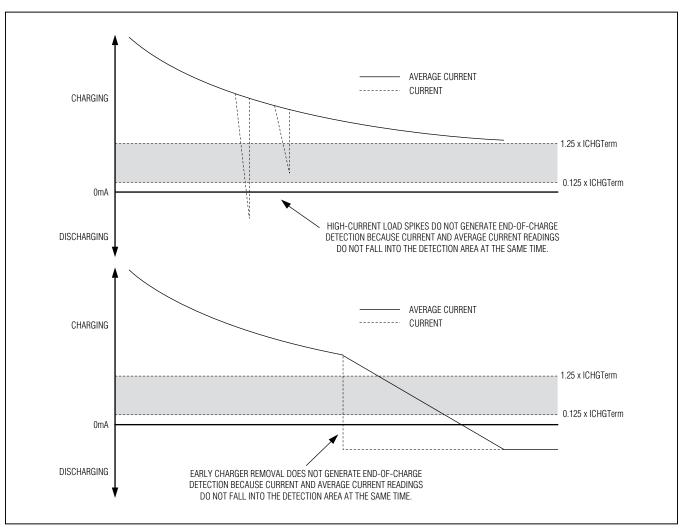

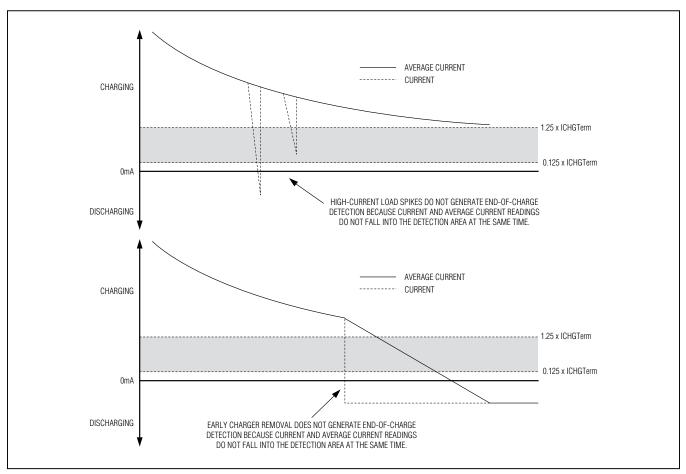

The device detects the end of a charge cycle when the application current falls into the band set by the ICHGTerm register value. By monitoring both the Current and AverageCurrent registers, the device can reject false end-of-charge events such as application load spikes or early charge-source removal. See the End-of-Charge Detection graph in the <u>Typical Operating Characteristics</u> and <u>Figure 26</u>.

Figure 26. False End-of-Charge Events

### ModelGauge m3 Fuel Gauge

When a proper end-of-charge event is detected, the device learns a new FullCAP register value based on the RemCap<sub>REP</sub> output. If the old FullCAP value was too high, it is adjusted downward after the last valid end-of-charge detection. If the old FullCAP was too low, it is adjusted upward to match RemCap<sub>REP</sub>. This prevents the calculated state of charge from ever reporting a value greater than 100%. See Figure 27.

#### **ICHGTerm Register (1Eh)**

The ICHGTerm register allows the device to detect when a charge cycle of the cell has completed. The host should set the ICHGTerm register value equal to the exact charge termination current used in the application. The device detects end of charge if all the following conditions are met:

- SOC<sub>VF</sub> > FullSOCThr

- AND ICHGTerm x 0.125 < Current < ICHGTerm x 1.25

- AND ICHGTerm x 0.125 < AverageCurrent < ICHGTerm x 1.25

Values are stored in  $\mu$ V. Multiply the termination current by the sense resistor to determine the desired register value. This register has the same range and resolution as the Current register. Figure 28 shows the ICHGTerm register format. ICHGTerm defaults to 150mA (03C0h) at power-up.

Figure 27. FullCAP Learning at End of Charge

### **ModelGauge m3 Fuel Gauge**

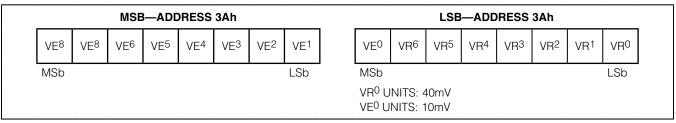

#### V\_empty Register (3Ah)

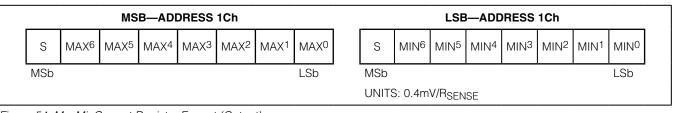

The V\_empty register sets thresholds related to empty detection during operation. Figure 29 is the V\_empty register format.

**VE<sup>8</sup>:VE0**—Empty Voltage. Sets the voltage level for detecting empty. A 10mV resolution gives a 0 to 5.11V range. This value is written to 3.12V at power-up.

**VR6:VR0**—Recovery Voltage. Sets the voltage level for clearing empty detection. Once the cell voltage rises above this point, empty voltage detection is reenabled. A 40mV resolution gives a 0 to 5.08V range. This value is written to 3.68V at power-up.

#### Cell Characterization Information Registers

Proper cell characterization is required to achieve accuracy. The following registers (<u>Table 1</u>) hold information that must be generated through a cell-characterization procedure. Maxim provides a cell-characterization service. Contact the factory for details.

# Table 1. Cell Characterization InformationRegisters

| REGISTER                          | ADDRESS    |

|-----------------------------------|------------|

| Characterization Table (48 words) | 80h to AFh |

| FullCap                           | 10h        |

| DesignCap                         | 18h        |

| ICHGTerm                          | 1Eh        |

| FullCapNom                        | 23h        |

| RCOMP0                            | 38h        |

| lavg_empty                        | 36h        |

| TempCo                            | 39h        |

| QResidual 00                      | 12h        |

| QResidual 10                      | 22h        |

| QResidual 20                      | 32h        |

| QResidual 30                      | 42h        |

|   |     |                 | MSB—ADDRESS 1Eh LSB—ADDRESS 1Eh |     |     |     |                |                |       |          |         |                |    |                |                |    |     |

|---|-----|-----------------|---------------------------------|-----|-----|-----|----------------|----------------|-------|----------|---------|----------------|----|----------------|----------------|----|-----|

|   | S   | 2 <sup>14</sup> | 2 <sup>13</sup>                 | 212 | 211 | 210 | 2 <sup>9</sup> | 2 <sup>8</sup> |       | 27       | 26      | 2 <sup>5</sup> | 24 | 2 <sup>3</sup> | 2 <sup>2</sup> | 21 | 20  |

| L | MSb |                 |                                 |     |     |     |                | LSb            |       | MSb      |         |                |    |                |                |    | LSb |

|   |     |                 |                                 |     |     |     |                |                | UNITS | 6: 1.562 | 25µV/Rg | SENSE          |    |                |                |    |     |

#### Figure 28. ICHGTerm Register Format (Input)

## ModelGauge m3 Fuel Gauge

### **Algorithm Configuration Registers**

The following registers allow operation of the ModelGauge m3 algorithm to be adjusted for the application. It is recommended that the default values for these registers be used.

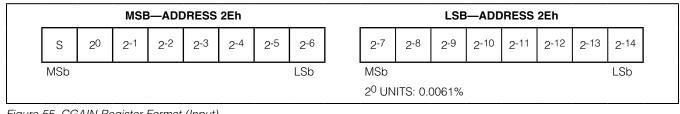

#### FilterCFG Register (29h)

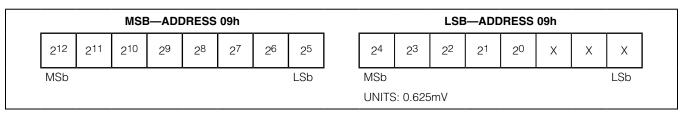

The FilterCFG register sets the averaging time period for all A/D readings, for mixing OCV results and coulombcount results. It is recommended that these values are not changed unless absolutely required by the application. Figure 30 shows the FilterCFG register format:

**CURR3:CURR0**—Sets the time constant for the AverageCurrent register. The default POR value of 4h gives a time constant of 11.25 seconds. The equation setting the period is:

AverageCurrent time constant = 175.8ms x 2(2+CURR)

**VOLT2:VOLT0**—Sets the time constant for the AverageV<sub>CELL</sub> register. The default POR value of 2h gives a time constant of 45.0s. The equation setting the period is:

AverageV<sub>CELL</sub> time constant = 175.8ms x 2<sup>(6+VOLT)</sup>

**MIX3:MIX0**—Sets the time constant for the mixing algorithm. The default POR value of Dh gives a time constant of 12.8 hours. The equation setting the period is:

Mixing Period = 175.8ms x 2(5+MIX)

**TEMP2:TEMP0**—Sets the time constant for the AverageTemperature register. The default POR value of 1h gives a time constant of 12min. The equation setting the period is:

AvergeTemperature time constant = 175.8ms x  $2^{(8 + TEMP)}$

**X**—Reserved. Do not modify.

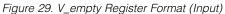

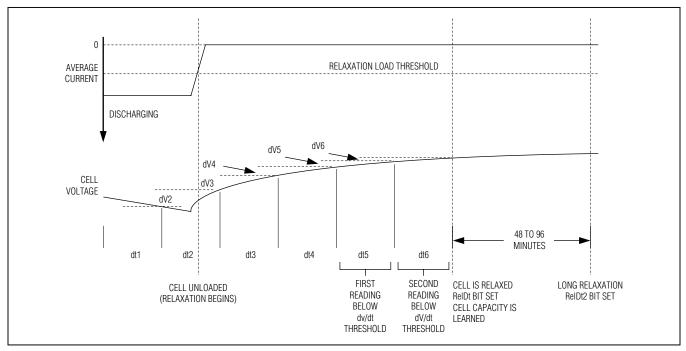

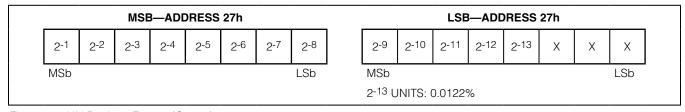

#### **RelaxCFG Register (2Ah)**

The RelaxCFG register defines how the device detects if the cell is in a relaxed state. See Figure 32. For a cell to be considered relaxed, current flow through the cell must be kept at a minimum while the change in the cell's voltage over time, dV/dt, shows little or no change. If AverageCurrent remains below the Load threshold while V<sub>CELL</sub> changes less than the dV threshold over two consecutive periods of dt, the cell is considered relaxed. Figure 31 shows the RelaxCFG register format:

**Load6:Load0**—Sets the threshold, which the AverageCurrent register is compared against. The AverageCurrent register must remain below this threshold value for the cell to be considered unloaded. Load is an unsigned 7-bit value where  $1 \text{ LSb} = 50 \mu \text{V}$ . The default value is  $800 \mu \text{V}$ .

|     |   | MSB- | -ADDR | ESS 29h | า       |        |      |     |         |       | LS    | SB—ADD | RESS 29 | 9h   |      |      |

|-----|---|------|-------|---------|---------|--------|------|-----|---------|-------|-------|--------|---------|------|------|------|

| X   | X | TEMP | TEMP  | TEMP    | МІХЗ    | MIX2   | MIX1 | 1 [ | MIXO    | VOLT2 | VOLT1 | VOLTO  | CURR    | CURR | CURR | CURR |

|     |   | 2    | 1     | 0       | 1111/10 | NUD CE |      | lL  | 1117.00 | VOLIE | VOEIT | VOLIO  | 3       | 2    | 1    | 0    |

| MSb |   |      |       |         |         |        | LSb  |     | MSb     |       |       |        |         |      |      | LSb  |

Figure 30. FilterCFG Register Format (Input)

### ModelGauge m3 Fuel Gauge

LearnCFG Register (28h)

**dV4:dV0**—Sets the threshold, which  $V_{CELL}$  is compared against. If the cell's voltage changes by less than dV over two consecutive periods set by dt, the cell is considered relaxed; dV has a range of 0 to 40mV where 1 LSb = 1.25mV. The default value is 1.75mV.

**dt3:dt0**—Sets the time period over which change in  $V_{CELL}$  is compared against dV. If the cell's voltage changes by less than dV over two consecutive periods set by dt, the cell is considered relaxed. The default value is 6 minutes. The comparison period is calculated as:

Relaxation Period =  $2^{dt} \times 0.1758s$

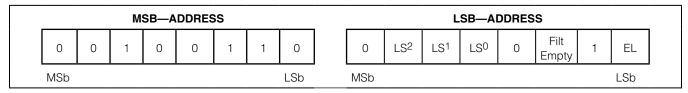

The LearnCFG register controls all functions relating to adaptation during operation. The LearnCFG register default values should not be changed unless specifically required by the application. Figure 33 is the LearnCFG register format:

**0**—Bit must be written 0. Do not write 1.

**1**—Bit must be written 1. Do not write 0.

**Filt Empty**—Empty Detect Filter. This bit selects whether empty is detected by a filtered or unfiltered voltage reading. Setting this bit to 1 causes the empty detection algorithm to use the AverageV<sub>CELL</sub> register. Setting this bit to 0 forces the empty detection algorithm to use the V<sub>CELL</sub> register. This bit is written to 0 at power-up.

Figure 32. Cell Relaxation Detection

Figure 33. LearnCFG Register Format (Input/Output)

### ModelGauge m3 Fuel Gauge

**LS2:LS0**—Learn Stage. See Figure 3 The Learn Stage value controls the influence of the VFG on the mixing algorithm. At power-up, Learn Stage defaults to 0h, making the voltage fuel gauge dominate. Learn Stage then advances to 7h over the course of two full cell cycles to make the coulomb counter dominate. Host software can write the Learn Stage value to 7h to advance to the final stage at any time. Writing any value between 1h and 6h is ignored. Learn Stage reflects the D5, D6, and D7 bits of the Cycles register. Update the Cycles register to advance to an intermediate state. For example, set Cycles = 160% to advance to Learn Stage 5.

**EL**—Empty Learning. Set this bit to 1 to turn on the Empty Learning feature. When enabled, the QResidual table is automatically adjusted at each empty event to compensate for the age of battery.

#### **MiscCFG Register (2Bh)**

The MiscCFG control register enables various other functions of the device. The MiscCFG register default values should not be changed unless specifically required by the application. Figure 34 is the MiscCFG register format:

- 0—Bit must be written 0. Do not write 1.

- 1—Bit must be written 1. Do not write 0.

- **X**—Don't Care. Bit may read 0 or 1.

**SACFG1:SACFG0**—SOC Alert Config. SOC Alerts can be generated by monitoring any of the SOC registers as follows. SACFG defaults to 00 at power-up:

**00** SOC Alerts are generated based on the SOC<sub>REP</sub> register.

- **01** SOC Alerts are generated based on the SOC<sub>AV</sub> register.

- **10** SOC Alerts are generated based on the SOC<sub>MIX</sub> register.

- **11** SOC Alerts are generated based on the SOC<sub>VF</sub> register.

**MR4:MR0**—Mixing Rate. This value sets the strength of the servo mixing rate after the final mixing state has been reached (> 2.08 complete cycles). The units are MR0 =  $6.25\mu$ V, giving a range up to 19.375mA with a standard 0.010 $\Omega$  sense resistor. Setting this value to 00000b disables servo mixing and the IC continues with time-constant mixing indefinitely. The default setting is 18.75 $\mu$ V or 1.875mA with a standard sense resistor.

**enBi1**—Enable reset on battery-insertion detection. Set this bit to 1 to force a reset of the fuel gauge whenever a battery insertion is detected based on AIN pin monitoring. This bit is written to 1 at power-up.

#### FSTAT Register (3Dh)

The FSTAT register is a read-only register that monitors the status of the ModelGauge algorithm. Do not write to this register location. Figure 35 is the FSTAT register format:

**RelDt**—Relaxed cell detection. This bit is set to a 1 whenever the ModelGauge m3 algorithm detects that the cell is in a fully relaxed state. This bit is cleared to 0 whenever a current greater than the Load threshold is detected. See Figure 32.

|   |     |   | MSE | B—AD | DRESS | 2Bh |                 |                 |   |                   |                 | LS              | SB—A | DDRE | SS 2BI | า          |            |

|---|-----|---|-----|------|-------|-----|-----------------|-----------------|---|-------------------|-----------------|-----------------|------|------|--------|------------|------------|

|   | 0   | 0 | Х   | х    | enBi1 | 0   | MR <sup>4</sup> | MR <sup>3</sup> | М | 1R2               | MR <sup>1</sup> | MR <sup>0</sup> | 1    | 0    | 0      | SACFG<br>1 | SACFG<br>0 |

| M | ISb |   |     | •    |       |     |                 | LSb             | M | ISb               |                 |                 |      |      |        | •          | LSb        |

|   |     |   |     |      |       |     |                 |                 | M | IR <sup>0</sup> L | JNITS:          | 6.25µ∖          | /    |      |        |            |            |

Figure 34. MiscCFG Register Format (Input)

|     |   | MSE | B—ADI | DRESS | 3Dh |       |      |     |        | LSB- | -ADDI | RESS | BDh |   |     |

|-----|---|-----|-------|-------|-----|-------|------|-----|--------|------|-------|------|-----|---|-----|

| Х   | Х | х   | х     | х     | х   | RelDt | EDet | х   | RelDt2 | х    | Х     | х    | Х   | Х | DNR |

| MSb |   |     |       |       |     |       | LSb  | MSb |        |      |       |      |     |   | LSb |

Figure 35. FSTAT Register Format (Output)

### ModelGauge m3 Fuel Gauge

**ReIDt2**—Long Relaxation. This bit is set to a 1 whenever the ModelGauge m3 algorithm detects that the cell has been relaxed for a period of 48 to 96 minutes or longer. This bit is cleared to 0 whenever the cell is no longer in a relaxed state. See Figure 32.

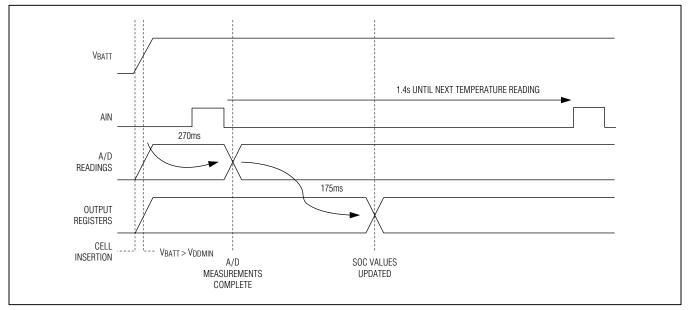

**DNR**—Data Not Ready. This bit is set to 1 at cell insertion and remains set until the output registers have been updated. Afterwards, the IC clears this bit indicating the fuel gauge calculations are now up to date. This takes between 445ms and 1.845s depending on whether the IC was in a powered state prior to the cell-insertion event.

**EDet**—Empty Detection. This bit is set to 1 when the IC detects that the cell empty point has been reached. This bit is reset to 0 when the cell voltage rises above the recovery threshold. See the V\_empty register for details.

**X**—Don't Care. This bit is undefined and can be logic 0 or 1.

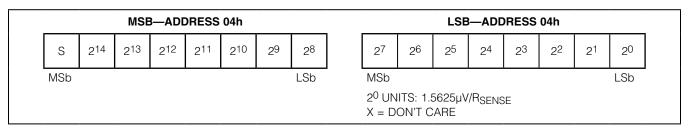

#### **AtRate Register (04h)**

The AtRate register allows host software to estimate remaining capacity, SOC, and time to empty for a theoretical load current. Whenever the AtRate register is programmed to 0 or a positive value, the device uses A/D measurements for determining the SOC<sub>AV</sub>, RemCap<sub>AV</sub>, and TTE register values. Whenever the AtRate register is programmed to a negative value indicating a hypothetical discharge current, the SOC<sub>AV</sub>, RemCap<sub>AV</sub>, and TTE

registers calculate their values for the AtRate register theoretical current instead. The AtRate register holds a two's-complement 16-bit value. Do not write 8000h to this register. Figure 36 shows the AtRate register format.

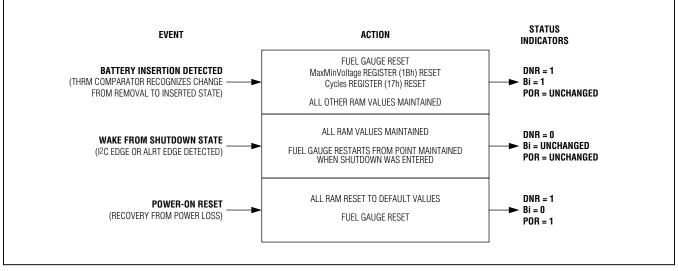

#### **Power-Up and Power-On Reset**

Any power-on reset (POR) of the device resets all memory locations to their default POR value. This removes any custom cell characterization and application data, affects ALRT interrupt and shutdown mode settings, and resets all learned adjustments made by the fuel gauge. To maintain accuracy of the fuel gauge and reset operation settings of the device, the host must reload all application memory data and restore all learned fuel-gauge information. Note that the device may take up to 445ms to completely reset operation after a POR event occurs. See Figure <u>37</u>. Saved data should not be restored until after this period is over. The following procedure is recommended:

- 1) Read Status register. If POR = 0, exit.

- 2) Wait 600ms for POR operation to fully complete.

- 3) Restore all application register values.

- 4) Restore fuel gauge learned-value information (see the *Save and Restore Registers* section).

- 5) Clear POR bit.

Figure 36. AtRate Register Format (Input)

### ModelGauge m3 Fuel Gauge

Figure 37. Power-Up Operation

#### **Save and Restore Registers**

The device is designed to operate outside the battery pack and can therefore be exposed to power loss when in the application. To prevent the loss of learned information during power cycles, a save-and-restore procedure can be used to maintain register values in nonvolatile memory external to the device. The registers (Table 2) must be stored externally and then rewritten to the device after power-up to maintain a learned state of operation.

Note that some registers are application outputs, some registers are for internal calculations, and some are characterization setup registers. Registers that are not internal are described in their own sections. These values should be stored by the application at periodic intervals. Some recommended back-up events are:

- End-of-charge

- End-of-discharge

- Prior to application entering shutdown state

The host is responsible for loading the default characterization data at first power-up of the device, and restoring the default characterization data plus learned information on subsequent power-up events.

#### Table 2. Save and Restore Registers

| REGISTER     | ADDRESS |  |  |  |  |  |

|--------------|---------|--|--|--|--|--|

| FullCap      | 10h     |  |  |  |  |  |

| Cycles       | 17h     |  |  |  |  |  |

| RCOMP0       | 38h     |  |  |  |  |  |

| TempCo       | 39h     |  |  |  |  |  |

| QResidual 00 | 12h     |  |  |  |  |  |

| QResidual 10 | 22h     |  |  |  |  |  |

| QResidual 20 | 32h     |  |  |  |  |  |

| QResidual 30 | 42h     |  |  |  |  |  |

| dQacc        | 45h     |  |  |  |  |  |

| dPacc        | 46h     |  |  |  |  |  |

#### **Battery Removal and Insertion**

The device detects when a cell has been removed or inserted into the application. This allows the device to adjust to the new cell to maintain accuracy. The removaldetection feature also allows the device to quickly warn the host processor through interrupt of impending power loss if enabled.

### **ModelGauge m3 Fuel Gauge**

Detection occurs by monitoring the AIN pin voltage compared to the THRM pin. Whenever a cell is present, the external resistor-divider network sets the voltage of AIN. When the cell is removed, the remaining external resistor pulls AIN to the THRM pin voltage level. Whenever V<sub>AIN</sub> < V<sub>THRM</sub> - V<sub>DETF</sub>, the device determines that a cell is present in the application. If V<sub>AIN</sub> > V<sub>THRM</sub> - V<sub>DETR</sub>, the device determines that no cell is present at that time.

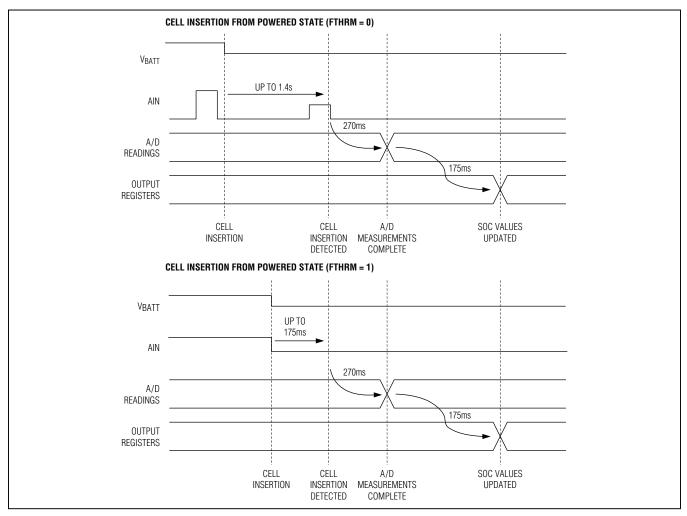

#### **Cell Insertion (IC Already Powered)**

The device is ready to detect a cell insertion if either the ETHRM or FTHRM bits of the CONFIG register are set to enable the THRM pin output. See Figure 38. When a cell insertion is detected, the fuel gauge is reset and all fuel-gauge outputs are updated to reflect the SOC of the

newly inserted cell. This process can take up to 1.845s (FTHRM = 0) or 620ms (FTHRM = 1) from time of insertion. Note that the device uses the cell voltage as a starting point for the fuel gauge. If the cell voltage is not fully relaxed at time of insertion, the fuel gauge begins with some initial error. See the *Fuel-Gauge Learning* section for details. The host can disable this feature by clearing the enBi1 bit in the MiscCFG register.

The device can also be configured to alert the host when cell insertion occurs. When Bei = 1 in the CONFIG register, the device generates an interrupt on the ALRT pin at the start of the first temperature conversion after insertion. This could take up to 1.4s to occur. This feature is useful if the application uses more than one cell type and the IC must be reconfigured at each insertion.

Figure 38. Operation After Cell Insertion

### ModelGauge m3 Fuel Gauge

#### **Cell Removal**

The device detects a cell removal if either the ETHRM or FTHRM bits of the CONFIG register are set to enable the THRM pin output. Cell removal does not affect IC operation. The device continues to update fuel-gauge outputs. The host should monitor the Br and Bst bits of the Status register to determine if the fuel-gauge outputs are valid.

The device can also be configured to alert the host when cell removal occurs. When Ber = 1 in the CONFIG register, the device generates an interrupt on the ALRT pin at the start of the first temperature conversion after removal. This could take up to 1.4s to occur. This feature is useful if the application uses more than one cell type and the IC must be reconfigured at each insertion.

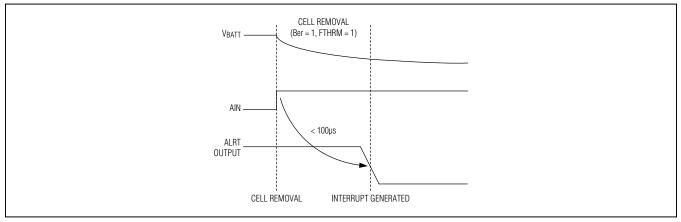

#### **Fast Detection of Cell Removal**

The device can be configured to quickly alert the host of impending power loss on cell removal. This fast response allows the system to quickly and gracefully hibernate to prevent power loss during battery swap. When Ber = 1, FTHRM = 1, and ALRTp = 0 in the CONFIG register, an interrupt on the ALRT pin is generated within 100µs after  $V_{AIN}$  becomes greater than  $V_{THRM}$  -  $V_{DETR}$ . If fast detection is used, it is recommended that all other IC interrupts are disabled to prevent the host from spending time determining the cause of the interrupt. Fast detection of cell removal has no affect on fuel-gauge operation, but leaving the external resistor-divider active increases current consumption of the application. See Figure 39.

#### **Modes of Operation**

The device operates in one of two power modes: active and shutdown. While in active mode, the device operates as a high-precision battery monitor with temperature, voltage, auxiliary inputs, current, and accumulated current measurements acquired continuously, and the resulting values updated in the measurement registers. READ and WRITE access is allowed only in active mode.

In shutdown mode, the LDO is disabled and all activity stops, although **volatile RAM contents remain preserved**. All A/D register and fuel-gauge output values are maintained. There are several options for entering shutdown:

Entering shutdown:

- **SHUTDOWN command**—Write the CONFIG register SHDN = 1 through the I<sup>2</sup>C interface; wait for longer than the SHDNTIMER register value.

- Pack removal—Pack removal detection is valid for longer than the SHDNTIMER register value and the CONFIG register AINSH = 1.

- I<sup>2</sup>C shutdown—I<sup>2</sup>C lines both persist low for longer than the SHDNTIMER register value and the CONFIG register I2CSH = 1.

- ALRT shutdown—Shutdown occurs when the ALRT line is externally driven low for longer than the SHDNTIMER register value (ALSH = 1 and ALRTp = 0), or the ALRT line is externally driven high for longer than the SHDNTIMER register value (ALSH = 1 and ALRTp = 1). See the *CONFIG Register (1Dh)* section.

Figure 39. Fast Detection of Cell Removal

## ModelGauge m3 Fuel Gauge

These shutdown entry modes are all programmable according to application. Shutdown events are gated by the SHDNTIMER register, which allows a long delay between the shutdown event and the actual shutdown. By behaving this way, the device takes the best reading of the relaxation voltage.

Exiting shutdown:

- I2C Wakeup—Any edge on SCL/SDA.

- **ALRT Wakeup**—Any edge on ALRT line and (ALSH = 1 or I2CSH = ALSH = 0).

- Reset—IC is power cycled.

See the <u>Status and Configuration</u> section for detailed descriptions of the SHDNTIMER and CONFIG registers.

The state of the device when returning to active mode differs depending on the triggering event. See Figure 40. Host software can monitor the POR and Bi status bits to determine what type of event has occurred.

#### **ALRT Function**

The Alert Threshold registers allow interrupts to be generated by detecting a high or low voltage, a high or low temperature, or a high or low SOC. Interrupts are generated on the ALRT pin open-drain output driver. An external pullup is required to generate a logic-high signal. Note that if the pin is configured to be logic-low when inactive, the external pullup increases current drain.

The ALRTp bit in the CONFIG register sets the polarity of the ALRT pin output. Alerts can be triggered by any of the following conditions:

- Battery removal—(V<sub>AIN</sub> > V<sub>THRM</sub> V<sub>DETR</sub>) and battery removal detection enabled (Ber = 1).

- Battery insertion—(V<sub>AIN</sub> < V<sub>THRM</sub> V<sub>DETF</sub>) and battery insertion detection enabled (Bei = 1).

- **Over-/undervoltage**—V<sub>ALRT</sub> threshold violation (upper or lower) and alerts enabled (Aen = 1).

- Over-/undertemperature—T<sub>ALRT</sub> threshold violation (upper or lower) and alerts enabled (Aen = 1).

- Over/under SOC—S<sub>ALRT</sub> threshold violation (upper or lower) and alerts enabled (Aen = 1).

To prevent false interrupts, the threshold registers should be initialized before setting the Aen bit. Alerts generated by battery insertion or removal can only be reset by clearing the corresponding bit in the Status register. Alerts generated by a threshold-level violation can be configured to be cleared only by software, or cleared automatically when the threshold level is no longer violated. See the CONFIG (1Dh) register description for details of the alert function configuration.

Figure 40. Device State Based on Shutdown Exit Condition

### ModelGauge m3 Fuel Gauge

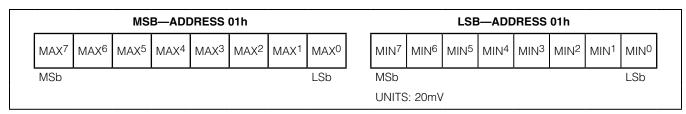

#### V<sub>ALRT</sub> Threshold Register (01h)

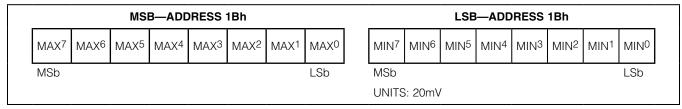

The V<sub>ALRT</sub> Threshold register (Figure 41) sets upper and lower limits that generate an ALRT pin interrupt if exceeded by the V<sub>CELL</sub> register value. The upper 8 bits set the maximum value and the lower 8 bits set the minimum value. Interrupt threshold limits are selectable with 20mV resolution over the full operating range of the V<sub>CELL</sub> register. At power-up, the thresholds default to their maximum settings—FF00h (disabled).

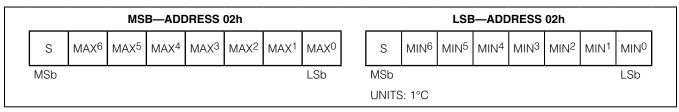

#### T<sub>ALRT</sub> Threshold Register (02h)

The  $T_{ALRT}$  Threshold register sets upper and lower limits that generate an ALRT pin interrupt if exceeded by the Temperature register value. The upper 8 bits set the maximum value and the lower 8 bits set the minimum value. Interrupt threshold limits are stored in two's-complement format and are selectable with 1°C resolution over the full

operating range of the Temperature register. At powerup, the thresholds default to their maximum settings— 7F80h (disabled). <u>Figure 42</u> shows the T<sub>ALRT</sub> Threshold register format.

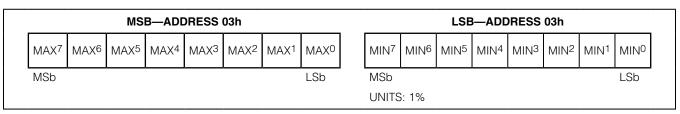

#### S<sub>ALRT</sub> Threshold Register (03h)

The S<sub>ALRT</sub> Threshold register (Figure 43) sets upper and lower limits that generate an ALRT pin interrupt if exceeded by the selected SOC<sub>REP</sub>, SOC<sub>AV</sub>, SOC<sub>MIX</sub>, or SOC<sub>VF</sub> register values. See the SACFG bits in the MiscCFG register description for details. The upper 8 bits set the maximum value and the lower 8 bits set the minimum value. Interrupt threshold limits are selectable with 1% resolution over the full operating range of the selected SOC register. At power-up, the thresholds default to their maximum settings—FF00h (disabled).

Figure 41. V<sub>ALRT</sub> Threshold Register Format (Input)

Figure 42. T<sub>ALRT</sub> Threshold Register Format (Input)

### ModelGauge m3 Fuel Gauge

#### **Status and Configuration**

The following registers control operation of the ALRT interrupt feature, control transition between active and shutdown modes of operation, and provide status updates to the host processor.

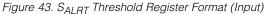

#### **CONFIG Register (1Dh)**

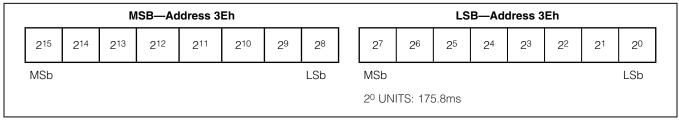

The CONFIG register holds all shutdown enable, alert enable, and temperature enable control bits. Writing a bit location enables the corresponding function within a 175.8ms task period. <u>Figure 44</u> shows the CONFIG register format.

0—Bit must be written 0. Do not write 1.

**Ber**—Enable alert on battery removal. When Ber = 1, a battery-removal condition, as detected by the AIN pin voltage, triggers an alert. Set to 0 at power-up. Note that if this bit is set to 1, the ALSH bit should be set to 0 to prevent an alert condition from causing the device to enter shutdown mode.

**Bei**—Enable alert on battery insertion. When Bei = 1, a battery-insertion condition, as detected by the AIN pin voltage, triggers an alert. Set to 0 at power-up. Note that if this bit is set to 1, the ALSH bit should be set to 0 to prevent an alert condition from causing the device to enter shutdown mode.

**Aen**—Enable alert on fuel-gauge outputs. When Aen = 1, violation of any of the alert threshold register values by temperature, voltage, or SOC triggers an alert. This bit affects the ALRT pin operation only. The Smx, Smn, Tmx, Tmn, Vmx, and Vmn bits are not disabled. This bit is set to 0 at power-up. Note that if this bit is set to 1, the ALSH bit should be set to 0 to prevent an alert condition from causing the device to enter shutdown mode.

**FTHRM**—Force Thermistor Bias Switch. This allows the host to control the bias of the thermistor switch or enable fast detection of battery removal (see the *Fast Detection of Cell Removal* section). Set FTHRM = 1 to always

enable the thermistor bias switch. With a standard  $10k\Omega$  thermistor, this adds an additional ~ $200\mu$ A to the current drain of the circuit. This bit is set to 0 at power-up.

**ETHRM**—Enable Thermistor. Set to logic 1 to enable the automatic THRM output bias and AIN measurement every 1.4s. This bit is set to 1 at power-up.

**ALSH**—ALRT Shutdown. Set to logic 1 and clear the Aen, Ber, and Bei bits to configure the ALRT pin as an input to control shutdown mode of the device. The device enters shutdown if the ALRT pin is held active for longer than timeout of the SHDNTIMER register. The device enters active mode immediately on the opposite edge of the ALRT pin. When set to logic 0, the ALRT pin can function as an interrupt output. This bit is set to 0 at power-up. Note that if this bit is set to 1, the Bei, Ber, and Aen bits should be set to 0 to prevent an alert condition from causing the device to enter shutdown mode.