CML Microcircuits

COMMUNICATION SEMICONDUCTORS

#### D/910/6 March 2009

#### Features:

- Half-Duplex GM(F)SK, FSK and DSC Capabilities

- Slot/Sample Counter with UTC Timing Interface

- Optimum Co-channel and Adjacent-channel Performance

- Flexible Signal Channels

- Two Simultaneous Rx

- One Tx

- Optional FSK Interface

- AIS Data Formatted and Raw Data Modes

- Supports Carrier-Sensing Channel Access (CSTDMA) Operation

- RF Device-Enable Facilities

- C-BUS Serial Interface with Expansion Port

- I and Q Radio Interface

- Low-Power (3.0 to 3.6V) Operation

- Low Profile, 64-lead LQFP (L9) and Leadless VQFN (Q1) Packages

- Auxiliary ADC and DAC Functions - 5 x (10-bit) DACs

- 5-Input MUX (10-bit) ADC

### **Applications:**

- Automatic Identification System (AIS) for Marine Safety

- Class A or B AIS Transponders

- AIS Rx-only Modules

#### 1. Brief Description

A highly integrated Baseband Signalling Processor IC, the CMX910 fulfils the requirements of the class A and class B marine Automatic Identification System (AIS) transponder market. The CMX910 is half duplex in operation, comprising two parallel I+Q Rx paths and one Tx path. These are configurable for AIS or DSC operation. The device performs channel filtering and signal modulation/demodulation with associated AIS functions, such as training sequence detection, NRZI conversion and HDLC processing (flags, bit stuffing/de-stuffing, CRC generate/check). An external 1200bps FSK demodulator interface provides a third parallel decode path for DSC, as required by the class A market. Integrated Rx/Tx data buffers and a flexible slot/sample timer are also provided, all of which greatly reduce the processing requirements of the host  $\mu$ C. Provision of a C-BUS expansion port, an RF device enable port and a number of auxiliary ADCs and DACs further simplifies the system hardware design, reducing the overall equipment cost and size.

© 2009 CML Microsystems Plc

# **CMX910** AIS Baseband Processor

**Provisional Issue**

#### CONTENTS

| Sectior | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | e |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 1.      | Brief Description1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

| 2.      | Block Diagram4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |

| 3.      | Signal List5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

| 4.      | External Components7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |

| 5.      | General Description       8         5.1       Overview of CMX910 Operation       8         5.2       C-BUS Interface       9         5.3       Reset and Power Control       12         5.3.1       RESETN pin       12         5.3.2       General Reset Command       12         5.3.3       Clock Control       12         5.4       Slot and Sample Timer       13         5.4.1       Manual Nudge       16         5.4.2       Auto Nudge       17         5.4.3       Sleep Mode       17         5.4.4       Selecting the Nudge_Trigger Value       18         5.5       Transmit Operation       19         5.5.1       Transmitter Registers       19         5.5.2       AIS Raw Mode Transmit       24         5.5.3       AIS Burst Mode Transmit       24         5.5.4       DSC Transmit       27         5.5.5       Transmitter Timing Control       29         5.6       Receive Operation       32         5.6.1       Receiver Registers       33         5.6.2       AIS Raw Mode Receive       37         5.6.3       AIS Burst Mode Receive       38         5.6.4 |   |

| 6.      | <ul> <li>5.12 Special Command Interface</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |

| 7       | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |

| 7.      | Performance Specification547.1Electrical Performance547.1.1Absolute Maximum Ratings547.1.2Operating Limits547.1.3Operating Characteristics557.2Packaging60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

| Table   |                                 | Page |

|---------|---------------------------------|------|

| Table 1 | Summary of C-BUS Registers      | 11   |

| Table 2 | Example Tx Event Sequence Setup | 31   |

| <u>Figure</u>                                               | <u>Page</u> |

|-------------------------------------------------------------|-------------|

| Figure 1 CMX910 Block Diagram                               | 4           |

| Figure 2 Recommended External Components                    | 7           |

| Figure 3 Basic C-BUS Transactions                           | 9           |

| Figure 4 C-BUS Data-Streaming Operation                     | 10          |

| Figure 5 Slot and Sample Timer Circuit                      | 13          |

| Figure 6 Transmit Channel                                   | 19          |

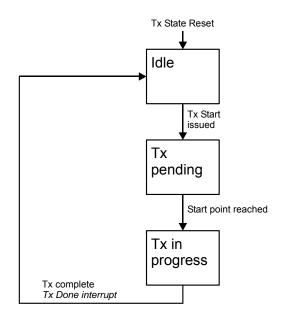

| Figure 7 Tx (AIS raw mode) state transitions                | 25          |

| Figure 8 Tx (AIS burst mode) state transitions              |             |

| Figure 9 Tx (DSC mode) state transitions                    | 28          |

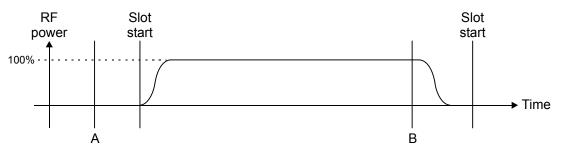

| Figure 10 Typical AIS Transmission                          | 29          |

| Figure 11 Receive Channel                                   | 32          |

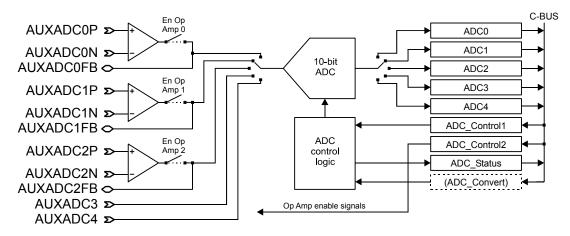

| Figure 12 Auxiliary ADC                                     | 40          |

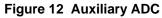

| Figure 13 Auxiliary DACs                                    | 42          |

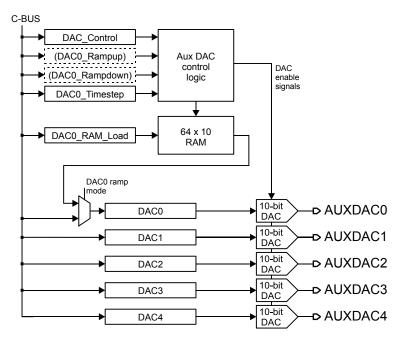

| Figure 14 RAMDAC Values                                     | 45          |

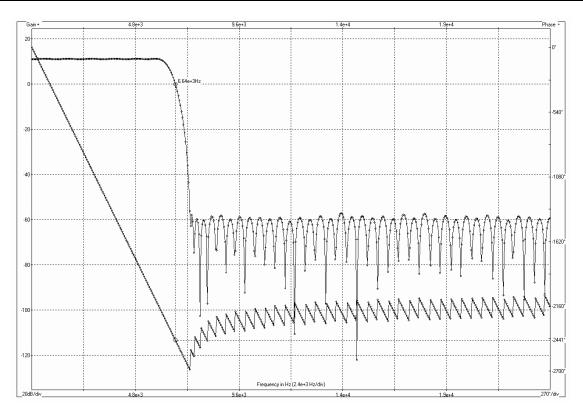

| Figure 15 I/Q Filter response in 25kHz operation            | 59          |

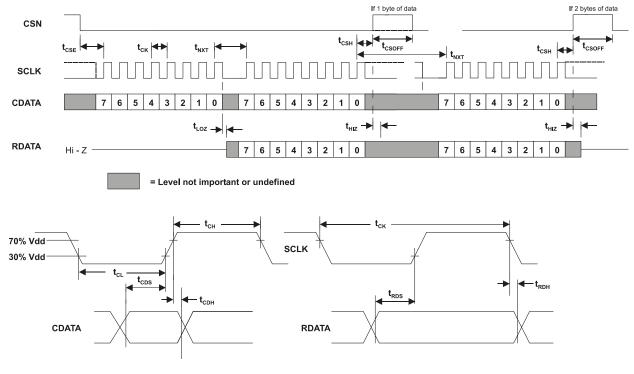

| Figure 16 C-BUS Timing                                      | 59          |

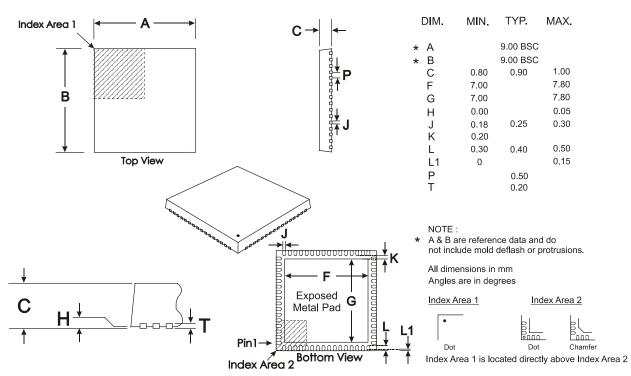

| Figure 17 Q1 Mechanical Outline: Order as part no. CMX910Q1 | 60          |

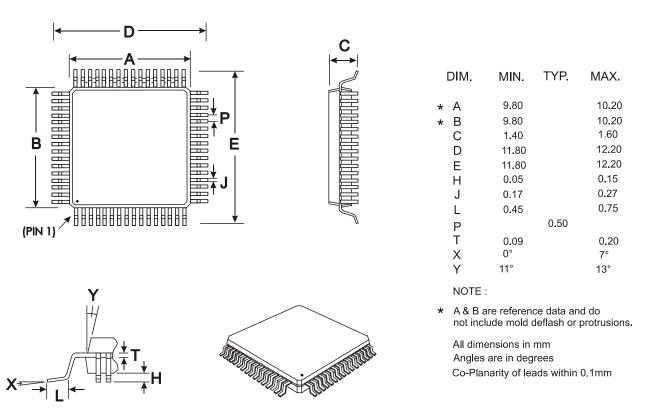

| Figure 18 L9 Mechanical Outline: Order as part no. CMX910L9 | 61          |

# History

| Version | Changes                                                                                                             | Date         |

|---------|---------------------------------------------------------------------------------------------------------------------|--------------|

| 1 - 5   | Earlier versions, for which a history file is not maintained.                                                       | 20/11/0      |

|         |                                                                                                                     | 8            |

| 6       | <ul> <li>Corrected description of the operation of the Auto Nudge Acquire sequence in<br/>section 5.4.2.</li> </ul> | 26/03/0<br>9 |

|         |                                                                                                                     |              |

|         |                                                                                                                     |              |

It is always recommended that you check for the latest product datasheet version from the Datasheets page of the CML website: [www.cmlmicro.com].

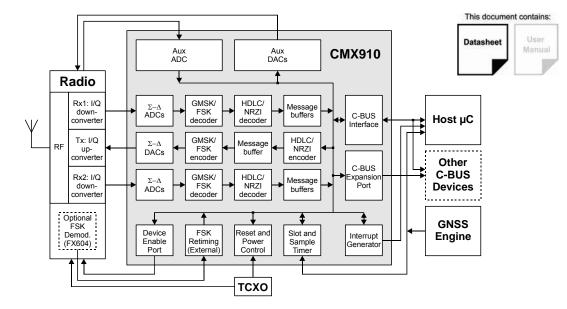

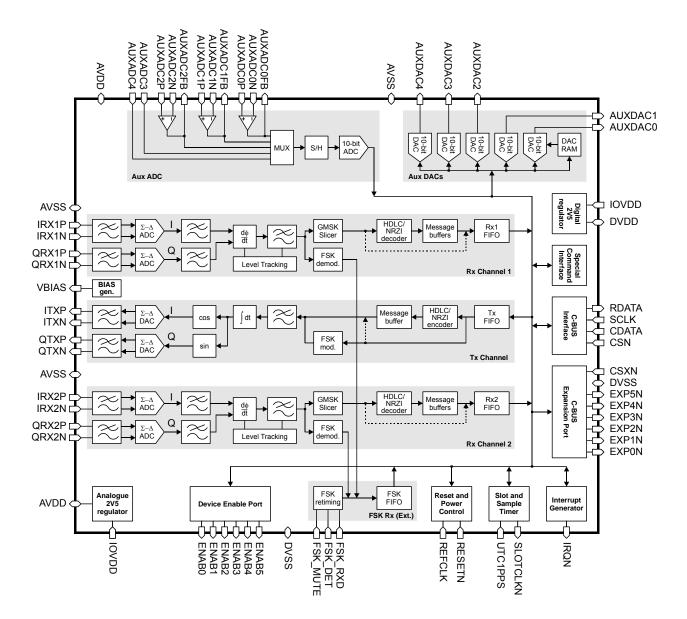

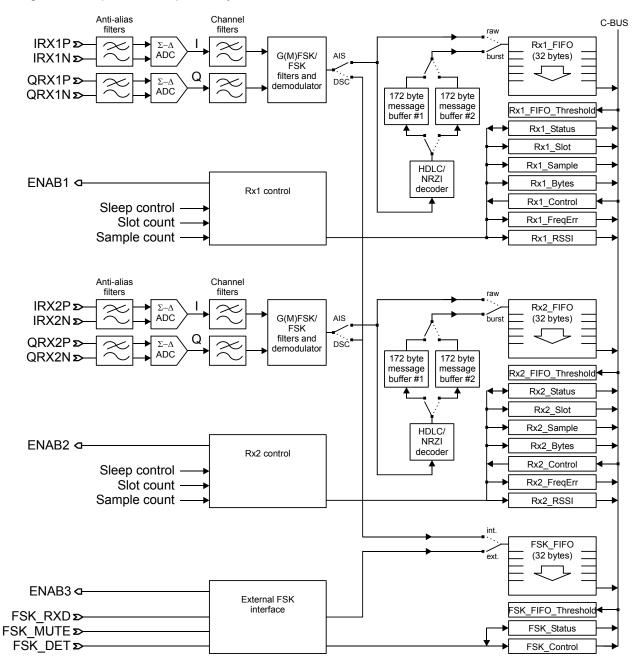

## 2. Block Diagram

Figure 1 CMX910 Block Diagram

| Package<br>Q1 or L9 | Signal           |       | - Signal Description                                                                                                                                                                                                                                  |  |  |  |

|---------------------|------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                     |                  |       |                                                                                                                                                                                                                                                       |  |  |  |

| Pin No.             | Name             | Туре  |                                                                                                                                                                                                                                                       |  |  |  |

| 1                   | AV <sub>SS</sub> | Power | Analogue negative supply rail (ground)                                                                                                                                                                                                                |  |  |  |

| 2                   | IRX1P            | I/P   | Receive "I" channel 1, positive input                                                                                                                                                                                                                 |  |  |  |

| 3                   | IRX1N            | I/P   | Receive "I" channel 1, negative input                                                                                                                                                                                                                 |  |  |  |

| 4                   | QRX1P            | I/P   | Receive "Q" channel 1, positive input                                                                                                                                                                                                                 |  |  |  |

| 5                   | QRX1N            | I/P   | Receive "Q" channel 1, negative input                                                                                                                                                                                                                 |  |  |  |

| 6                   | VBIAS            | O/P   | A bias line for the internal circuitry, held at $\frac{1}{2}$ AV <sub>DD</sub> . This pin must be decoupled to AV <sub>SS</sub> by a capacitor mounted close to the device pins                                                                       |  |  |  |

| 7                   | ITXP             | O/P   | Transmit "I" channel, positive output                                                                                                                                                                                                                 |  |  |  |

| 8                   | ITXN             | O/P   | Transmit "I" channel, negative output                                                                                                                                                                                                                 |  |  |  |

| 9                   | QTXP             | O/P   | Transmit "Q" channel, positive output                                                                                                                                                                                                                 |  |  |  |

| 10                  | QTXN             | O/P   | Transmit "Q" channel, negative output                                                                                                                                                                                                                 |  |  |  |

| 11                  | AV <sub>SS</sub> | Power | Analogue negative supply rail (ground)                                                                                                                                                                                                                |  |  |  |

| 12                  | IRX2P            | I/P   | Receive "I" channel 2, positive input                                                                                                                                                                                                                 |  |  |  |

| 13                  | IRX2N            | I/P   | Receive "I" channel 2, negative input                                                                                                                                                                                                                 |  |  |  |

| 14                  | QRX2P            | I/P   | Receive "Q" channel 2, positive input                                                                                                                                                                                                                 |  |  |  |

| 15                  | QRX2N            | I/P   | Receive "Q" channel 2, negative input                                                                                                                                                                                                                 |  |  |  |

| 16                  | AV <sub>DD</sub> | Power | Analogue positive supply rail. Decouple to AV <sub>SS</sub>                                                                                                                                                                                           |  |  |  |

| 17                  |                  | Power | Digital I/O positive supply rail. Decouple to DV <sub>SS</sub>                                                                                                                                                                                        |  |  |  |

| 18                  | ENAB0            | O/P   | Enable output 0                                                                                                                                                                                                                                       |  |  |  |

| 19                  | ENAB1            | O/P   | Enable output 1                                                                                                                                                                                                                                       |  |  |  |

| 20                  | ENAB2            | O/P   | Enable output 2                                                                                                                                                                                                                                       |  |  |  |

| 21                  | ENAB3            | O/P   | Enable output 3                                                                                                                                                                                                                                       |  |  |  |

| 22                  | ENAB4            | O/P   | Enable output 4                                                                                                                                                                                                                                       |  |  |  |

| 23                  | ENAB5            | O/P   | Enable output 5                                                                                                                                                                                                                                       |  |  |  |

| 24                  | DV <sub>SS</sub> | Power | Digital negative supply rail (ground)                                                                                                                                                                                                                 |  |  |  |

| 25                  | FSK_MUTE         | I/P   | FSK RF squelch indicator                                                                                                                                                                                                                              |  |  |  |

| 26                  | FSK_DET          | I/P   | FSK baseband energy detect indicator                                                                                                                                                                                                                  |  |  |  |

| 27                  | FSK_RXD          | I/P   | Raw FSK demodulator input data                                                                                                                                                                                                                        |  |  |  |

| 28                  | REFCLK           | I/P   | Master input clock (multiple of 2.4MHz)                                                                                                                                                                                                               |  |  |  |

| 29                  | RESETN           | I/P   | Active low chip reset                                                                                                                                                                                                                                 |  |  |  |

| 30                  | UTC1PPS          | I/P   | 1Hz UTC sync pulse, typically from GNSS receiver                                                                                                                                                                                                      |  |  |  |

| 31                  | SLOTCLKN         | O/P   | Slot clock output (active low), pulses at the start of each AIS slot.<br>Configurable as a 'wire-ORable' output, requiring an external pullup<br>resistor, or as an active pullup/pulldown.                                                           |  |  |  |

| 32                  | IRQN             | O/P   | A 'wire-ORable' output for connection to the host $\mu$ C's Interrupt<br>Request input. This output has a low impedance pull down to DV <sub>SS</sub><br>when active and is high impedance when inactive. An external<br>pullup resistor is required. |  |  |  |

| Package<br>Q1 or L9     | Signal           |       | Description                                                                                                            |

|-------------------------|------------------|-------|------------------------------------------------------------------------------------------------------------------------|

| Pin No.                 | Name             | Туре  |                                                                                                                        |

| 33                      | EXPON            | O/P   | Chip Select expansion output 0 (active low)                                                                            |

| 34                      | EXP1N            | O/P   | Chip Select expansion output 1 (active low)                                                                            |

| 35                      | EXP2N            | O/P   | Chip Select expansion output 2 (active low)                                                                            |

| 36                      | EXP3N            | O/P   | Chip Select expansion output 3 (active low)                                                                            |

| 37                      | EXP4N            | O/P   | Chip Select expansion output 4 (active low)                                                                            |

| 38                      | EXP5N            | O/P   | Chip Select expansion output 5 (active low)                                                                            |

| 39                      | DV <sub>SS</sub> | Power | Digital negative supply rail (ground)                                                                                  |

| 40                      | CSXN             | I/P   | Chip Select expansion input (active low)                                                                               |

| 41                      | CSN              | I/P   | Chip Select input (active low), used to enable a C-BUS data read or write operation on the chip.                       |

| 42                      | CDATA            | I/P   | The C-BUS serial data input from the $\mu$ C.                                                                          |

| 43                      | SCLK             | I/P   | The C-BUS serial clock input from the $\mu$ C.                                                                         |

| 44                      | RDATA            | T/S   | A 3-state C-BUS serial data output to the $\mu$ C. This output is high impedance when not sending data to the $\mu$ C. |

| 45                      |                  | Power | Digital core positive supply rail. Decouple to DV <sub>SS</sub>                                                        |

| 46                      |                  | Power | Digital I/O positive supply rail. Decouple to DV <sub>SS</sub>                                                         |

| 47                      | AUXDAC0          | O/P   | Auxiliary D-to-A converter output 0 (with ramp)                                                                        |

| 48                      | AUXDAC1          | O/P   | Auxiliary D-to-A converter output 1                                                                                    |

| 49                      | AUXDAC2          | O/P   | Auxiliary D-to-A converter output 2                                                                                    |

| 50                      | AUXDAC3          | O/P   | Auxiliary D-to-A converter output 3                                                                                    |

| 51                      | AUXDAC4          | O/P   | Auxiliary D-to-A converter output 4                                                                                    |

| 52                      | AV <sub>SS</sub> | Power | Analogue negative supply rail (ground)                                                                                 |

| 53                      | AUXADC0FB        | O/P   | Auxiliary A-to-D converter 0, amplifier feedback                                                                       |

| 54                      | AUXADC0N         | I/P   | Auxiliary A-to-D converter 0, amplifier -ve input                                                                      |

| 55                      | AUXADC0P         | I/P   | Auxiliary A-to-D converter 0, amplifier +ve input                                                                      |

| 56                      | AUXADC1FB        | O/P   | Auxiliary A-to-D converter 1, amplifier feedback                                                                       |

| 57                      | AUXADC1N         | I/P   | Auxiliary A-to-D converter 1, amplifier -ve input                                                                      |

| 58                      | AUXADC1P         | I/P   | Auxiliary A-to-D converter 1, amplifier +ve input                                                                      |

| 59                      | AUXADC2FB        | O/P   | Auxiliary A-to-D converter 2, amplifier feedback                                                                       |

| 60                      | AUXADC2N         | I/P   | Auxiliary A-to-D converter 2, amplifier -ve input                                                                      |

| 61                      | AUXADC2P         | I/P   | Auxiliary A-to-D converter 2, amplifier +ve input                                                                      |

| 62                      | AUXADC3          | I/P   | Auxiliary A-to-D converter input 3                                                                                     |

| 63                      | AUXADC4          | I/P   | Auxiliary A-to-D converter input 4                                                                                     |

| 64                      | AV <sub>DD</sub> | Power | Analogue positive supply rail. Decouple to $AV_{SS}$                                                                   |

| Exposed<br>Metal<br>Pad | $DV_{SS}$        | Power | This pad (which is only present on the Q1 package) must be connected to Digital Ground (0V).                           |

| Notes: | I/P | = | Input          |

|--------|-----|---|----------------|

|        | O/P | = | Output         |

|        | BI  | = | Bidirectional  |

|        | T/S | = | 3-state Output |

|        | NC  | = | No Connection  |

|        |     |   |                |

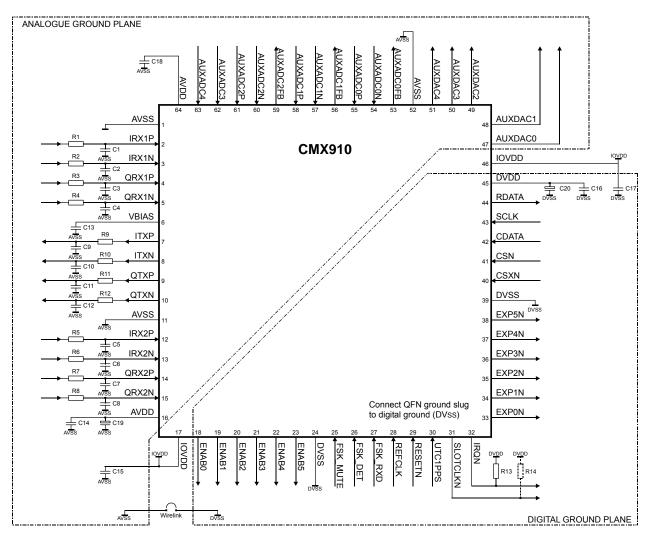

#### 4. External Components

#### Figure 2 Recommended External Components

| C1-C8  | 1nF | C14-C18 | 10nF | R1-R8   | $1$ k $\Omega$ |

|--------|-----|---------|------|---------|----------------|

| C9-C12 | 1nF | C19     | 10µF | R9-R12  | $1$ k $\Omega$ |

| C13    | 1µF | C20     | 22µF | R13-R14 | 10k $\Omega$   |

A regulated 3.3V supply must be connected to the CMX910's  $IOV_{DD}$  pins in order to supply the digital I/O pad circuitry. This 3.3V supply is also used by two on-chip 2.5V regulators which are used to generate the separate  $AV_{DD}$  and  $DV_{DD}$  supplies (used by the CMX910's on-chip analogue and digital circuitry), the only external components needed are the decoupling capacitors. The  $AV_{DD}$  and  $DV_{DD}$  supplies are *not* intended to provide current to any external circuits, but may be buffered if required for use as a reference.

To achieve good noise performance,  $AV_{DD}/DV_{DD}$  and VBIAS decoupling and protection of the receive path from extraneous in-band signals are very important. It is recommended that the printed circuit board is laid out with separate analogue and digital ground planes in the CMX910 area to provide a low impedance connection between  $AV_{SS}$  and the  $AV_{DD}/VBIAS$  decoupling capacitors, and between  $DV_{SS}$  and the  $DV_{DD}$  decoupling capacitors.

### 5. General Description

#### 5.1 Overview of CMX910 Operation

The CMX910 IC has two main receiver circuits that support simultaneous reception of two AIS channels, or one AIS and one DSC channel. When the two main receive channels are configured for AIS reception, a supplementary DSC-only receiver can be supported by using a separate external FSK demodulator (such as the FX604) interfaced to the CMX910. Data bits received on this FSK interface get packed into bytes and passed through to the host  $\mu$ C. Transmission on a single channel (AIS or DSC) is supported, during which all reception ceases. The main receive and transmit channels use differential I + Q signalling, and digital filtering and signal processing techniques are used to obtain a high level of performance.

The CMX910 also supports the proposed carrier-sensing channel access scheme (CSTDMA) for the AIS class B standard.

Overall timing synchronisation centres around two counters, one counting the number of samples per slot, the other the number of slots in a minute. These allow the  $\mu$ C to retrieve slot and sample timing information for any received message as well as specifying transmit timing accurately. Counters can be synchronised to an external 1 pulse per second UTC reference signal or allowed to run free, in which case they must be kept in alignment by the  $\mu$ C.

The CMX910 offers full frame-formatting (HDLC-type) support for AIS receive and transmit, including NRZI coding, bit stuffing and de-stuffing, training sequence, start/stop flag insertion and deletion, and CRC generation and checking. A raw mode is also provided allowing greater flexibility. DSC transmission and reception is only supported in the equivalent of the AIS raw mode.

The transmit channel and three receive channels interface to the  $\mu$ C through individual 32-deep, byte wide first-in first-out data buffers. These alleviate latency problems and allow higher data rates between the  $\mu$ C and the CMX910. To allow system performance to be further enhanced, the CMX910 can be configured to cause an interrupt if the transmit FIFO fill level drops below a user-defined threshold or any of the receive FIFOs' fill levels exceed a user-defined threshold.

The CMX910 also assists with power saving and control of critical external RF circuits by providing a flexible device enable port. Further monitoring and control functions can be implemented using the integrated auxiliary ADC and DAC circuits.

Communication between the CMX910 and the host  $\mu$ C is done through CML's standard C-BUS interface and interrupt pin. The C-BUS interface is SPI compatible, and can be driven by an SPI master controller. A C-BUS expansion port is also provided which allows the connection of up to six further C-BUS or SPI compatible devices to the  $\mu$ C.

**NOTE:** To further enhance the CMX910, its Special Command Interface (see section 5.12) can be used to reconfigure the CMX910's functionality to fully implement and improve its CS-TDMA reception capability and slot-clock synchronisation.

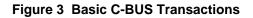

#### 5.2 C-BUS Interface

This block provides for the transfer of data and control or status information between the CMX910's internal registers and the host  $\mu$ C over the C-BUS serial bus. Each transaction consists of a single Register Address byte sent from the  $\mu$ C which may be followed by a data word sent from the  $\mu$ C to be written into one of the CMX910's Write Only Registers, or a data word read out from one of the CMX910's Read Only Registers; all C-BUS data words are a multiple of 8 bits wide, the width depending on the source or destination register. Note that certain C-BUS transactions require only an address byte to be sent from the  $\mu$ C, no data transfer being required. The operation of the C-BUS is illustrated in Figure 3.

Data sent from the  $\mu$ C on the CDATA (command data) line is clocked into the CMX910 on the rising edge of the SCLK input. Data sent from the CMX910 to the  $\mu$ C on the RDATA (reply data) line is valid when SCLK is high. The CSN line must be held low during a data transfer and kept high between transfers. The C-BUS interface is compatible with most common  $\mu$ C serial interfaces and may also be easily implemented with general purpose  $\mu$ C I/O pins controlled by a simple software routine. Figure 16 gives detailed C-BUS timing requirements.

| C-BUS single byte command (no data)                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CSN                                                                                                                                                                                                                            |

| SCLK       Note:         CDATA       7       6       5       4       3       2       1       0       Note:       The SCLK line may be high or low at the start and end of each transaction. See Figure 16.                     |

| MSB Address LSB                                                                                                                                                                                                                |

| RDATA Hi-Z = Level not important                                                                                                                                                                                               |

| C-BUS n-bit register write                                                                                                                                                                                                     |

| CSN                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                |

| T         6         5         4         3         2         1         0         n-1         n-2         n-3         2         1         0           MSB         Address         LSB         MSB         Write data         LSB |

| RDATA Hi-Z                                                                                                                                                                                                                     |

| C-BUS n-bit register read                                                                                                                                                                                                      |

| CSN                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                |

| T         6         5         4         3         2         1         0           MSB         Address         LSB                                                                                                              |

| RDATA Hi-Z     n-1 n-2 n-3     2     1     0       MSB     Read data     LSB                                                                                                                                                   |

To increase the data bandwidth between the  $\mu$ C and the CMX910, certain of the C-BUS read and write registers are capable of data-streaming operation. This allows a single address byte to be followed by the transfer of multiple read or write data words, all within the same C-BUS transaction. This can significantly increase the transfer rate of large data blocks, as shown in Figure 4.

| Example of C-BUS data-streaming (8-bit write register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CDATA       7       6       5       4       3       2       1       0       7       6       5       4       3       2       1       0       7       6       5       4       3       2       1       0       7       6       5       4       3       2       1       0       7       6       5       4       3       2       1       0       7       6       5       4       3       2       1       0       7       6       5       4       3       2       1       0       7       6       5       4       3       2       1       0       7       6       5       4       3       2       1       0       7       6       5       4       3       2       1       0       7       6       5       4       3       2       1       0       7       6       5       4       3       2       1       0       7       6       5       4       3       2       1       0       7       6       5       4       3       2       1       0       7       6       5       4       3       2 |

| RDATA Hi-z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Example of C-BUS data-streaming (8-bit read register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CDATA 7 6 5 4 3 2 1 0<br>Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RDATA Hi-Z       7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0         First byte       Second byte          Last byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

Figure 4 C-BUS Data-Streaming Operation

A summary of the CMX910's C-BUS addresses and registers are shown in Table 1. Note: the CMX910's internal clock must be running before any C-BUS access is attempted, with the exception of the General\_Reset command and the Clock\_Control and CBUS\_Expand registers.

#### AIS Baseband Processor

| C-BUS register name      | Addr | R/W/<br>Cmd   | Size | C-BUS register name       | Addr | R/W/<br>Cmd | Size |

|--------------------------|------|---------------|------|---------------------------|------|-------------|------|

| Reset and power control  |      | FSK Interface |      |                           |      |             |      |

| General_Reset            | \$01 | Cmd           | -    | FSK_FIFO (DS)             | \$50 | R           | 8    |

| Clock_Control            | \$02 | W             | 8    | FSK_FIFO_Threshold        | \$51 | W           | 8    |

| Slot and Sample Timer    |      |               |      | FSK_Status                | \$52 | R           | 16   |

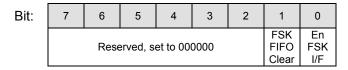

| Slot_Sample_Control      | \$10 | W             | 8    | FSK_Control               | \$53 | W           | 8    |

| Slot_Sample_Count        | \$11 | R             | 32   | Auxiliary ADC             |      |             |      |

| Sleep_Sample             | \$12 | W             | 16   | ADC0                      | \$60 | R           | 16   |

| Wakeup_Sample            | \$13 | W             | 16   | ADC1                      | \$61 | R           | 16   |

| Slot_Sample_UTC1PPS      | \$14 | R             | 32   | ADC2                      | \$62 | R           | 16   |

| Slot_Nudge               | \$15 | W             | 16   | ADC3                      | \$63 | R           | 16   |

| Sample_Nudge             | \$16 | W             | 16   | ADC4                      | \$64 | R           | 16   |

| Nudge_Trigger            | \$17 | W             | 16   | ADC_Control1              | \$65 | W           | 8    |

| Max_Auto_Nudge           | \$18 | W             | 16   | ADC_Control2              | \$66 | W           | 8    |

| Transmit Channel         |      |               |      | ADC_Status                | \$67 | R           | 8    |

| Tx_FIFO (DS)             | \$20 | W             | 8    | ADC_Convert               | \$68 | Cmd         | -    |

| Tx_FIFO_Threshold        | \$21 | W             | 8    | Auxiliary DACs            |      |             |      |

| Tx_Status                | \$22 | R             | 16   | DAC0                      | \$70 | W           | 16   |

| Tx_Slot                  | \$23 | W             | 16   | DAC1                      | \$71 | W           | 16   |

| Tx_Bits                  | \$24 | W             | 16   | DAC2                      | \$72 | W           | 16   |

| Tx_Control               | \$25 | W             | 16   | DAC2                      | \$73 | W           | 16   |

| CSTDMA_Threshold         | \$26 | W             | 16   | DAC4                      | \$74 | W           | 16   |

| Receive Channel 1        |      |               |      | DAC_Control               | \$75 | W           | 8    |

| Rx1_FIFO (DS)            | \$30 | R             | 8    | DAC0_Rampup               | \$76 | Cmd         | -    |

| Rx1_FIFO_Threshold       | \$31 | W             | 8    | DAC0_Rampdown             | \$77 | Cmd         | -    |

| Rx1_Status               | \$32 | R             | 16   | DAC0_Timestep             | \$78 | W           | 8    |

| Rx1_Slot                 | \$33 | R             | 16   | DAC_RAM_Load (DS)         | \$79 | W           | 16   |

| Rx1_Sample               | \$34 | R             | 16   | Interrupts                |      | •           |      |

| Rx1_Bytes                | \$35 | R             | 16   | Interrupt                 | \$80 | R           | 16   |

| Rx1_Control              | \$36 | W             | 8    | Interrupt_Enable          | \$81 | W           | 16   |

| Rx1_FreqErr              | \$37 | R             | 16   | Device Enable Port        |      |             |      |

| Rx1_RSSI                 | \$38 | R             | 16   | ENAB                      | \$90 | W           | 8    |

| Receive Channel 2        |      |               |      | ENAB_Mask                 | \$91 | W           | 8    |

| Rx2_FIFO <sup>(DS)</sup> | \$40 | R             | 8    | ENAB_Invert               | \$92 | W           | 8    |

| Rx2_FIFO_Threshold       | \$41 | W             | 8    | C-BUS Expansion Port      |      |             |      |

| Rx2_Status               | \$42 | R             | 16   | CBUS_Expand               | \$A0 | W           | 8    |

| Rx2_Slot                 | \$43 | R             | 16   | Special Command Interface |      |             |      |

| Rx2_Sample               | \$44 | R             | 16   | SPC_In0                   | \$B0 | W           | 16   |

| Rx2_Bytes                | \$45 | R             | 16   | SPC_In1                   | \$B1 | W           | 16   |

| Rx2_Control              | \$46 | W             | 8    | SPC_Out0                  | \$B2 | R           | 16   |

| Rx2_FreqErr              | \$47 | R             | 16   | Special_Command           | \$B4 | W           | 8    |

| Rx2_RSSI                 | \$48 | R             | 16   |                           |      |             |      |

(DS) - These registers are capable of data-streaming transactions.

Note: C-BUS addresses \$F0 to \$FE are allocated for production testing and should not be accessed in normal operation.

#### Table 1 Summary of C-BUS Registers

#### 5.3 Reset and Power Control

#### 5.3.1 RESETN pin

The CMX910 is reset by taking RESETN low, which causes all internal clocks and bias currents to be disabled and all C-BUS registers to be reset. To bring the CMX910 out of this quiescent state after RESETN is pulled high, a stable clock signal must first be applied to the REFCLK input pin (any multiple of 2.4MHz up to a maximum of 24MHz), then the Clock\_Control register must be programmed with the frequency of the applied REFCLK. A period of 10ms must then elapse to allow the CMX910 to initialise, after which time the device is ready for operation. During operation the main Rx and Tx channel analogue circuits and auxiliary ADC and DAC circuits will be powered up as required, depending on how the host  $\mu$ C sets various C-BUS control and configuration registers.

#### 5.3.2 General\_Reset Command

#### General\_Reset command (no data)

This command disables all internal bias currents and resets all C-BUS registers *except* for CBUS\_Expand and Clock\_Control. This means that if the CMX910's internal clocks are running, they will remain running when General\_Reset is applied. After a General\_Reset command, a period of 10ms must elapse to allow the CMX910 to initialise before any further C-BUS operations are attempted.

#### 5.3.3 Clock Control

The CMX910 can be put back into a low power state at any time by writing \$00 to the Clock\_Control register. This will disable all internal clocks and bias currents and reset all internal C-BUS registers *except* for CBUS\_Expand. To subsequently bring the CMX910 out of this low power state requires the same sequence of operations as if a RESETN pulse had been applied.

#### Clock\_Control register: 8-bit write only.

#### C-BUS Address \$02

C-BUS Address \$01

All bits cleared to 0 when RESETN pin asserted. Register contents are not affected by a General\_Reset command. This register can be written while the CMX910's internal clocks are disabled.

| Bit: | 7   | 6       | 5        | 4   | 3  | 2      | 1         | 0   |

|------|-----|---------|----------|-----|----|--------|-----------|-----|

|      | Res | served, | set to 0 | 000 | RE | FCLK r | nult. fac | tor |

#### Clock\_Control register b3-0: REFCLK Multiplication Factor

| b3   | b2     | b1                  | b0                 |                                                         |

|------|--------|---------------------|--------------------|---------------------------------------------------------|

| 0    | 0      | 0                   | 0                  | Internal clocks disabled, device held in low power mode |

| 0    | 0      | 0                   | 1                  | REFCLK = 2.4MHz                                         |

| 0    | 0      | 1                   | 0                  | REFCLK = 4.8MHz                                         |

| 0    | 0      | 1                   | 1                  | REFCLK = 7.2MHz                                         |

| 0    | 1      | 0                   | 0                  | REFCLK = 9.6MHz                                         |

| 0    | 1      | 0                   | 1                  | REFCLK = 12.0MHz                                        |

| 0    | 1      | 1                   | 0                  | REFCLK = 14.4MHz                                        |

| 0    | 1      | 1                   | 1                  | REFCLK = 16.8MHz                                        |

| 1    | 0      | 0                   | 0                  | REFCLK = 19.2MHz                                        |

| 1    | 0      | 0                   | 1                  | REFCLK = 21.6MHz                                        |

| 1    | 0      | 1                   | 0                  | REFCLK = 24.0MHz                                        |

| Code | es 101 | 1 <sub>2</sub> to 1 | 111 <sub>2</sub> a | are reserved, do not use                                |

#### 5.4 Slot and Sample Timer

The Slot and Sample Timer circuit contains two counters that are used to control and sequence operations in the three main channels (Rx1, Rx2, Tx).

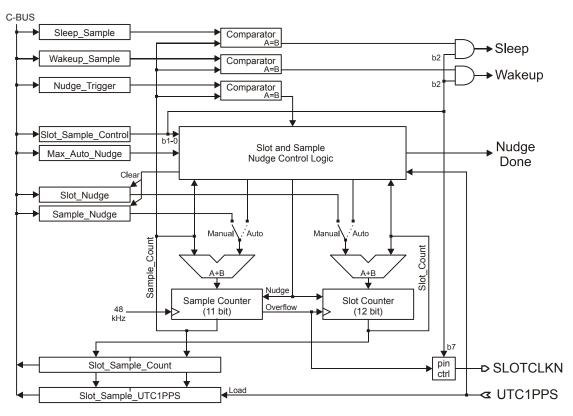

Figure 5 Slot and Sample Timer Circuit

The clock for the slot and sample counters is derived from the REFCLK input pin. The *sample* counter is an 11 bit counter which increments at 48kHz, i.e. five times per AIS data bit, and is used to time various Rx and Tx operations within a slot period. Since there are 256 bit periods per AIS slot, the sample counter increments from 0 to 1279 before rolling over to 0. The *slot* counter is a 12 bit counter and is used to count the slot number in an AIS frame, which lasts for a minute. It is incremented at the beginning of each AIS slot period, i.e. when the sample counter rolls over. There are  $37\frac{1}{2}$  slots per second, resulting in 2250 slots per minute. Therefore the slot counter increments from 0 to 2249 before rolling over to 0. When operating correctly, the slot counter rollover should be aligned to the start of the UTC minute. The current value of the slot and sample counters are available to the  $\mu$ C by reading the Slot\_Sample\_Count register.

The CMX910 produces a pulse on its SLOTCLKN output pin during the first sample period within each slot, this can be used as general timing reference by the  $\mu$ C. Each pulse is active low and lasts for approximately 20.83  $\mu$ s, and the pulses repeat at 37.5Hz. The signal appearing on the SLOTCLKN pin can be configured to be open-drain pull-down or have active pull-up and pull-down drivers.

When the CMX910 comes out of reset the slot and sample counters will be free running but not synchronised to anything. The  $\mu$ C must synchronise them to an appropriate timing source, either UTC (direct or indirect) or to an appropriate base station as required by Recommendation ITU-R M1371-1. Once initial synchronisation has been established, occasional minor adjustments, or "nudges", to the sample counter must be made to keep it locked to the chosen timing source – this compensates for any slight drift caused by inaccuracy in the REFCLK frequency. Nudge values can be calculated and applied directly by the  $\mu$ C in a software control loop ("manual nudge", section 5.4.1). Alternatively, the CMX910 can be configured into certain "auto nudge" modes to establish initial synchronisation and subsequent

tracking of the slot and sample counters with minimal  $\mu$ C intervention, using the UTC1PPS signal as a timing reference (section 5.4.2).

A "Sleep Control" feature is provided which can reduce power consumption significantly when the CMX910 is enabled for AIS reception. This operates by automatically turning off the internal receiver circuits during inactive slots. Sleep Control is described in more detail in section 5.4.3.

The Slot and Sample Timer circuit is configured and controlled through nine C-BUS registers:

#### Slot\_Sample\_Control register: 8-bit write only. C-BUS Address \$10 Register reset to \$80.

Bit:

| 7                     | 6  | 5       | 4        | 3   | 2                   | 1     | 0    |  |

|-----------------------|----|---------|----------|-----|---------------------|-------|------|--|

| Slot<br>clock<br>ctrl | Re | served, | set to 0 | 000 | En<br>sleep<br>mode | Nudge | mode |  |

#### Slot\_Sample\_Control register b7: SLOTCLKN Pin Control

With b7 = 0 the SLOTCLKN pin will be configured to have active pull-up and pull-down drivers. If b7 = 1 the pin will have an open-drain pull-down, requiring an external pull-up resistor.

#### Slot\_Sample\_Control register b2: Enable Sleep Mode

Setting b2 = 1 enables AIS sleep mode on receive channels Rx1 and Rx2.

#### Slot\_Sample\_Control register b1-0: Nudge Mode

The Nudge Mode bits control how the CMX910 achieves and maintains synchronisation of the slot and sample counters with the UTC timing reference.

| b1 | b0 |                                    |

|----|----|------------------------------------|

| 0  | 0  | Manual nudge (auto nudge disabled) |

| 0  | 1  | Auto nudge acquire                 |

| 1  | 0  | Auto nudge track                   |

| 1  | 1  | Reserved, do not use               |

#### Slot\_Sample\_Count register: 32-bit read only. All bits cleared to 0 on reset.

#### C-BUS Address \$11

Bit: Slot count Bit: Sample count

The Slot\_Sample\_Count register holds the current value of the slot and sample counters.

#### Sleep\_Sample register: 16-bit write only.

#### C-BUS Address \$12

All bits cleared to 0 on reset.

| Bit: | 15                     | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7     | 6      | 5     | 4 | 3 | 2 | 1 | 0 |

|------|------------------------|----|----|----|----|----|---|---|-------|--------|-------|---|---|---|---|---|

|      | Reserved, set to 00000 |    |    |    |    |    |   |   | Sleep | sample | value |   |   |   |   |   |

The Sleep Sample register holds the sample value at which the CMX910's Rx1 or Rx2 circuits enter sleep mode during an inactive slot.

#### Wakeup\_Sample register: 16-bit write only.

#### C-BUS Address \$13

All bits cleared to 0 on reset.

| Bit: | 15                     | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7     | 6       | 5       | 4 | 3 | 2 | 1 | 0 |

|------|------------------------|----|----|----|----|----|---|---|-------|---------|---------|---|---|---|---|---|

|      | Reserved, set to 00000 |    |    |    |    |    |   |   | Wakeu | p sampl | e value |   |   |   |   |   |

The Wakeup\_Sample register holds the sample value at which the CMX910's Rx1 or Rx2 circuits leave sleep mode after an inactive slot, in time to detect a training sequence in the next slot.

#### Slot\_Sample\_UTC1PPS register: 32-bit read only. C-BUS Address \$14 All bits cleared to 0 on reset.

| Bit: | 31 | 30 | 29 | 28 | 27                                            | 26 | 25 | 24     | 23      | 22         | 21      | 20     | 19   | 18 | 17 | 16 |

|------|----|----|----|----|-----------------------------------------------|----|----|--------|---------|------------|---------|--------|------|----|----|----|

|      | 0  | 0  | 0  | 0  |                                               |    |    | Slot c | ount at | last risir | ng edge | of UTC | 1PPS |    |    |    |

|      |    | -  | -  | -  |                                               |    |    | -      |         | -          |         |        |      |    |    |    |

| Bit: | 15 | 14 | 13 | 12 | 11                                            | 10 | 9  | 8      | 7       | 6          | 5       | 4      | 3    | 2  | 1  | 0  |

|      | 0  | 0  | 0  | 0  | 0 Sample count at last rising edge of UTC1PPS |    |    |        |         |            |         |        |      |    |    |    |

The Slot Sample UTC1PPS register indicates the value that the slot and sample counters held at the last rising edge of the UTC1PPS pin.

#### Slot\_Nudge register: 16-bit write only.

#### C-BUS Address \$15

All bits cleared to 0 on reset.

| Bit: | 15                                  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------|-------------------------------------|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|      | Slot nudge value (two's complement) |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

The Slot Nudge register is written with the amount that the slot counter is to be adjusted at the next nudge trigger point.

#### Sample\_Nudge register: 16-bit write only.

#### C-BUS Address \$16

All bits cleared to 0 on reset.

| Bit: | 15                                    | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------|---------------------------------------|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|      | Sample nudge value (two's complement) |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

The Sample Nudge register is written with the amount that the sample counter is to be adjusted at the next nudge trigger point (only in manual nudge mode, the Sample\_Nudge register is ignored when in either of the auto nudge modes).

<sup>© 2009</sup> CML Microsystems PIc

Nudge\_Trigger register: 16-bit write only. All bits cleared to 0 on reset.

C-BUS Address \$17

C-BUS Address \$18

| Bit: | 15                     | 14 | 13 | 12 | 11 | 10 | 9 | 8  | 7       | 6         | 5        | 4       | 3        | 2   | 1 | 0 |  |

|------|------------------------|----|----|----|----|----|---|----|---------|-----------|----------|---------|----------|-----|---|---|--|

|      | Reserved, set to 00000 |    |    |    |    |    |   | Sa | mple co | ount at w | /hich to | add nuo | dge valu | ies |   |   |  |

The Nudge Trigger register holds the sample count at which the slot and sample counter nudge values get added.

#### Max\_Auto\_Nudge register: 16-bit write only. All bits cleared to 0 on reset.

| Bit: | 15                     | 14 | 13 | 12 | 11 | 10 | 9 | 8  | 7      | 6       | 5       | 4  | 3 | 2 | 1 | 0 |

|------|------------------------|----|----|----|----|----|---|----|--------|---------|---------|----|---|---|---|---|

|      | Reserved, set to 00000 |    |    |    |    |    |   | Ma | aximum | auto nu | dge val | ue |   |   |   |   |

The Max Auto Nudge register is used to set the magnitude of the maximum sample counter nudge in auto nudge track mode.

#### 5.4.1 Manual Nudge

Manual nudge mode is enabled by setting Slot Sample Control b1-0 to 00 (auto nudge disabled). It is then the responsibility of the µC to keep the slot and sample counters aligned to the relevant timing reference. To assist with manual nudge mode in the case where a UTC time reference is available, the CMX910 copies the value of the Slot Sample Count register into the Slot Sample UTC1PPS register on each rising edge of the UTC1PPS input pin, from where it can be read by the  $\mu$ C; the UTC1PPS pin should be connected to a 1Hz signal whose rising edge is accurately aligned to the UTC second. Any error in the slot and sample counter values can then be easily determined. If the accurate 1Hz signal is lost or not available, the same information must be derived from timing information received on the AIS channels; this is made available in the RX1\_Slot / RX1\_Sample and RX2\_Slot / Rx2\_Sample registers (see section 5.6.1). Note: since there are 371/2 slots per second, "even" seconds correspond to a slot boundary and "odd" seconds correspond to the middle of a slot.

In manual nudge mode, the µC initially synchronises the slot and sample counters, and can subsequently make minor adjustments to the sample counter, using the same mechanism in each case: the µC loads the Slot Nudge and Sample Nudge registers with two's-complement values indicating by how much the slot and sample counters should be adjusted, and the Nudge Trigger register is loaded with the exact sample time within a slot that these nudge values should be added to the counters - typically, the Nudge Trigger value will need to be initialised only once. As soon as the nudge has been done, a "Nudge Done" interrupt will be generated by the CMX910 and the Slot Nudge and Sample Nudge registers will be cleared to \$0000, ready for new values to be written.

The slot counter usually needs adjusting only after a device reset, or if slot alignment has been lost for some reason, e.g. a GNSS timing signal has been lost for some time and has just been re-acquired. If the slot counter needs adjusting, the µC should write to the Slot\_Nudge register first, then to the Sample Nudge register. The act of writing to the Sample\_Nudge register indicates to the CMX910 that both nudge values are ready, and they get applied simultaneously at the next nudge trigger point. If, however, only the sample counter needs adjusting then the µC need only write to the Sample\_Nudge register, since Slot\_Nudge will have been previously auto-cleared. Depending on the accuracy of the REFCLK input signal, it may be necessary to make several adjustments to the sample counter every minute. For instance, a 5ppm error in REFCLK will cause the sample counter to drift by 14.4 counts (nearly 3 bit periods) per minute.

Note that the slot counter "wraps" properly when it is nudged forwards past 2249 or backwards past 0, but the same does not apply to the sample counter - it can get it into an illegal state by nudging forward past 1279 or backwards past 0. Avoid this by ensuring that  $0 \le (Nudge\_Trigger + Sample\_Nudge) \le 1279$ .

#### 5.4.2 Auto Nudge

Two auto nudge modes are provided which assist the  $\mu$ C with the initial synchronisation of the slot and sample counters, and allow the CMX910 to subsequently keep the sample counter aligned without further intervention. This requires an accurate UTC1PPS signal to be applied to the CMX910:

Auto nudge acquire (Slot\_Sample\_Control b1-0 = 01). This mode can be used for initial counter synchronisation after a device reset or in the case where the slot and sample counters have become grossly misaligned for some reason. Auto nudge acquire should be enabled when the CMX910 has just received a UTC1PPS rising edge from an "even" UTC second, which means that the next UTC1PPS rising edge will be an "odd" second. The CMX910 will calculate the error in the sample counter latched in from the "even" UTC second and will apply the required correction to the sample counter at the next Nudge\_Trigger point. A Nudge\_Done interrupt is then generated, indicating that sample counter alignment has been achieved.

Auto nudge track (Slot\_Sample\_Control b1-0 = 10). In this mode, the CMX910 calculates the correction needed for the sample counter once per second (on the rising edge of UTC1PPS). "Odd" and "even" UTC seconds are treated differently: if  $320 \le$  Sample\_Count < 960 when the rising edge of UTC1PPS occurs, the CMX910 assumes it to be an "odd" UTC second and calculates a sample nudge value of (640 - Sample\_Count). Otherwise, the sample nudge value is calculated as (-1 × Sample\_Count). This calculated value (or ±Max\_Auto\_Nudge, whichever is smaller in magnitude) is then added to the sample counter at the next Nudge\_Trigger point. Note: if the µC writes a non-zero value to the Slot\_Nudge register when in auto nudge track mode, this will be added to the slot counter at the same time that the sample counter value is updated. The Slot\_Nudge register gets auto-cleared after being used which causes a Nudge\_Done interrupt, otherwise Nudge Done interrupts are not generated in auto nudge track mode.

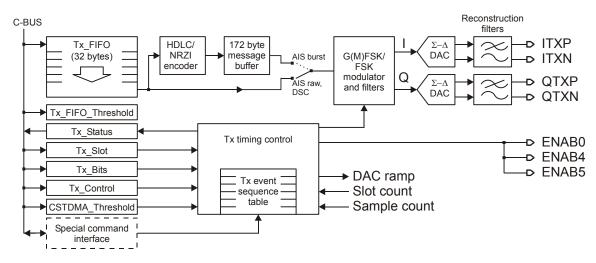

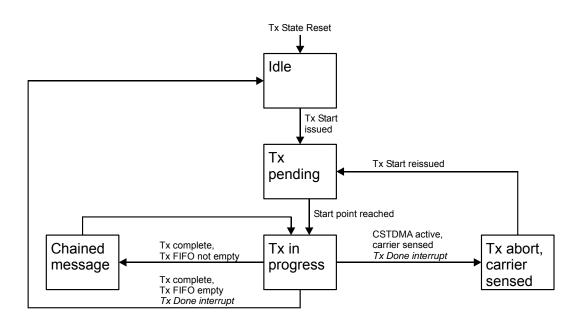

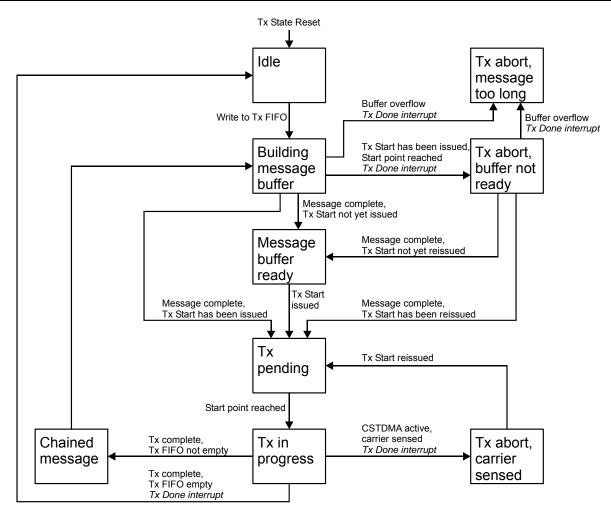

The Max\_Auto\_Nudge register is used to limit the magnitude of the allowed nudge in order to avoid potential timing problems. The Max\_Auto\_Nudge register is ignored in manual nudge and auto nudge acquire mode.