# High Performance Synchronous SRAM

# 256Kx4 Monolithic High Speed Synchronous Static RAM

ADVANCE INFORMATION

The EDI2040C is a high performance, 1 megabit synchronous static RAM organized as 256Kx4, available in six versions.

Inputs are registered or latched on the rising edge of CLK (K), depending on version. The output can be self-timed, registered, or latched, also depending on version.

Address, Data, and Control need to be held valid for a small percentage of cycle time and output timing can be matched to very tight system constraints.

These options allow the designer tremendous flexibility in the design of very high speed computer systems.

#### Features

256Kx4 bit Synchronous Static Random Access Memory

- Fast Access Times 15, 20 and 25ns

- Works with System Clocks to 65Mhz

- · Separate Data Input/Output

Thru-hole and Surface Mount Package Options

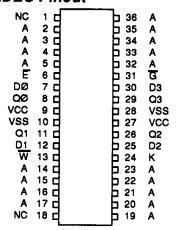

JEDEC Pinout

- 36 Pin DIP, 400 mils Wide

- 36 Lead SOJ

Single +5V (±10%) Supply Operation

| Part No. | Input      | Output       | #CLK |

|----------|------------|--------------|------|

| EDI2040C | Latched    | Latched      | 1    |

| EDI2041C | Registered | Registered   | 1    |

| EDI2042C | Latched    | Asynchronous | 1    |

| EDI2043C | Registered | Asynchronous | 1    |

| EDI2044C | Latched    | Registered   | 2    |

| EDI2045C | Registered | Registered   | 2    |

### Pin Names

| <u>A</u> Ø-A15 | Address Inputs  |

|----------------|-----------------|

| E<br>W         | Chip Enable     |

|                | Write Enable    |

| G1-G2          | Output Enables  |

| K1-K2          | Clock           |

| DØ-D3          | Data Input      |

| QØ-Q3          | Data Output     |

| VCC            | Power (+5V±10%) |

| VSS            | Ground          |

| NC             | No Connection   |

### JEDEC Pinout

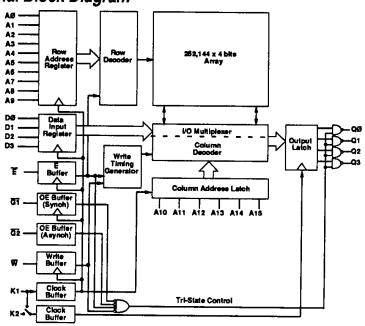

### Functional Block Diagram