# **GigabitCAM**

# **KE5BGCA256**

**Preliminary**

Ver. 1.1.1

# **Contents**

| 1.    | Features                                 | 5.3. | 3 CPU Port in a Cascaded System        |

|-------|------------------------------------------|------|----------------------------------------|

| 2.    | Block Diagram                            | 5.3. | ·                                      |

| 3.    | Pin Assignment and Pin De-               | 6.   | <b>Command Descriptions</b>            |

|       | scriptions                               | 6.1  | <b>Command Functions</b>               |

| 3.1   | Pin Assignment                           | 6.2  | <b>Command Format</b>                  |

| 3.2   | Pin Descriptions                         |      |                                        |

|       |                                          | 7.   | <b>Register Descriptions</b>           |

| 4.    | <b>Functional Descriptions</b>           | 7.1  | Overview                               |

| 4.1   | Access from CPU Port                     | 7.2  | Register Addresses                     |

| 4.2   | Read/Write Registers                     | 7.3  | Register Bit Maps                      |

| 4.3   | Access to the CAM Memory                 | 7.4  | <b>Conditions for Accessing Regis-</b> |

| 4.4   | Search                                   |      | ters                                   |

| 4.5   | <b>Data Management by Commands</b>       |      |                                        |

| 4.6   | <b>Restriction in Pipeline Operation</b> | 8.   | <b>Package Information</b>             |

| 4.7   | Latency                                  | 8.1  | Ordering Information                   |

|       |                                          | 8.2  | Package Drawing                        |

| 5. (  | Connection                               |      |                                        |

|       |                                          | 9.   | <b>Electrical Characteristics</b>      |

| 5.1   | Initialization                           | 9.1  | <b>Absolute Maximum Rating</b>         |

| 5.2   | Single Device Operation                  | 9.2  | Operating Range                        |

|       | <b>Cascade Connection</b>                | 9.3  | DC Characteristics                     |

|       | 1 Device ID Registration                 | 9.4  | AC Characteristics                     |

| 5.3.2 | 2 Priority                               | 9.5  | <b>Power Consumption</b>               |

# **Preliminary**

### 1. Features

The KE5BGCA256 provides best solution to the fast "Address Filtering" requirements of today's internetworking switching equipment with the following outstanding functions.

## • 256k-bit capacity of table

- 64-bit x 4096 entries

- CAM/RAM substitution

### Dual Port Architecture

- 32-bit I/O Port

- 16-bit Output Port

### 12 Search Conditions

- -12 Mask registers selected by the external pins (MS<3:0>) and the CNTL1 register

- Access bit can be set for data aging

- Permanent bit can be set for permanent entry

- Automatic output of the contents of the Hit entry and the Empty entry address from the 16-bit Output Port

# Cascading

- Table size is expandable.

- A cascaded table acts as one integral search data table by internal device priority control.

### Commands

- Useful commands for table management such as aging and purging.

- Useful command for Source Address Learning

### • Synchronous Operation

- 30ns cycle time

- 64-bit input/30ns

- Search, data read/write, and command operations are executed at high speed.

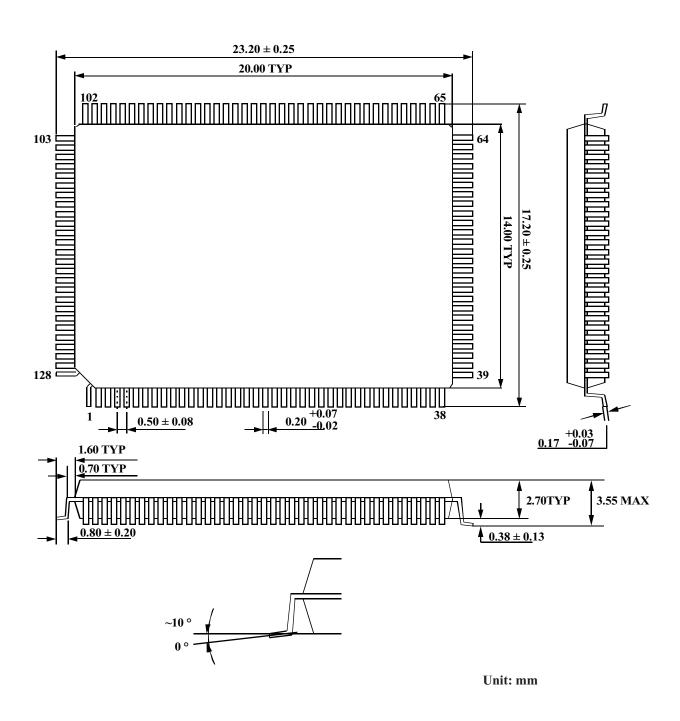

### • 128-pin SQFP Package

# • 3.3 v CMOS technology

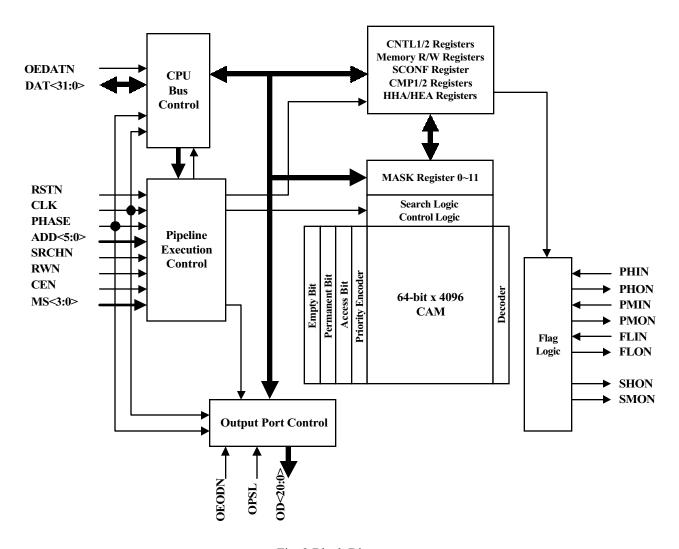

# 2. Block Diagram

This device consists of the following blocks as shown.

### **CPU Bus Control Block**

An access to the search key data, commands, or internal registers are executed through the CPU Bus.

### **Pipeline Execution Control**

This block controls the pipeline operation of this device.

### CNTL1/2 Registers

These registers define the mask registers and the input modes, etc.

Fig. 2 Block Diagram

### **Memory R/W Registers**

These registers are used to access the CAM table.

### **SCONF Register**

This register defines the configuration of the search operation.

### CMP1/2 Registers

These two registers store the search key data and both are 64 bits in width.

### **HHA/HEA Registers**

These two registers respectively store the hit address and the empty address of the CAM table.

### **MASK Registers**

These 12 registers are used to mask the data bit by bit in the search operation or the write operation to the CAM table.

### **CAM**

The capacity of the CAM table is 64 bits x 4096 entries.

### Flag Logic

This block outputs the search result and the status of the CAM table and has the interface function for a cascade connection.

### **Output Port Control**

This block controls the Output Port which outputs the search result.

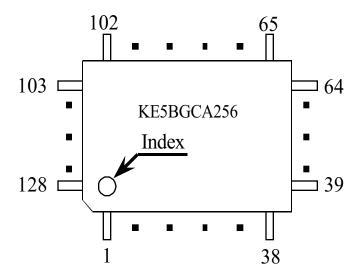

# 3. Pin Assignment and Pin Descriptions

# 3.1 Pin Assignment

# KE5BGCA256 (128pinSQFPtype)

Fig. 3.1.1 Pin Assignment

| Pin No. | Signal Name | I/O type |

|---------|-------------|----------|

| 1       | GND         | -        |

| 2       | OD<0>       | OUT      |

| 3       | OD<1>       | OUT      |

| 4       | VDD         | -        |

| 5       | VDD         | -        |

| 6       | OD<2>       | OUT      |

| 7       | OD<3>       | OUT      |

| 8       | OD<4>       | OUT      |

| 9       | GND         | -        |

| 10      | OD<5>       | OUT      |

| 11      | OD<6>       | OUT      |

| 12      | OD<7>       | OUT      |

| 13      | GND         | -        |

| 14      | OD<8>       | OUT      |

| 15      | VDD         | -        |

| 16      | OD<9>       | OUT      |

| 17      | OD<10>      | OUT      |

| 18      | GND         | -        |

| 19      | GND         | -        |

| 20      | GND         | -        |

| 21      | OD<11>      | OUT      |

| 22      | VDD         | =        |

| 23      | OD<12>      | OUT      |

| 24      | VDD         | =        |

| 25      | OD<13>      | OUT      |

| 26      | OD<14>      | OUT      |

| 27      | GND         | =        |

| 28      | OD<15>      | OUT      |

| 29      | OD<16>      | OUT      |

| 30      | OD<17>      | OUT      |

| 31      | OD<18>      | OUT      |

| 32      | GND         | -        |

| 33      | OD<19>      | OUT      |

| 34      | VDD         | -        |

| 35      | VDD         | -        |

| 36      | OD<20>      | OUT      |

| 37      | GND         | -        |

| 38      | FLON        | OUT      |

| 39      | SMON        | OUT      |

| 40      | SHON        | OUT      |

| Pin No. | Signal Name | I/O type |  |

|---------|-------------|----------|--|

| 41 GND  |             | -        |  |

| 42      | PMON        | OUT      |  |

| 43      | PHON        | OUT      |  |

| 44      | FLIN        | IN       |  |

| 45      | PMIN        | IN       |  |

| 46      | PHIN        | IN       |  |

| 47      | VDD         | -        |  |

| 48      | OPSL        | IN       |  |

| 49      | OEODN       | IN       |  |

| 50      | GND         | -        |  |

| 51      | GND         | -        |  |

| 52      | GND         | -        |  |

| 53      | MS<0>       | IN       |  |

| 54      | MS<1>       | IN       |  |

| 55      | MS<2>       | IN       |  |

| 56      | MS<3>       | IN       |  |

| 57      | DAT<0>      | I/O      |  |

| 58      | DAT<1>      | I/O      |  |

| 59      | VDD         | -        |  |

| 60      | DAT<2>      | I/O      |  |

| 61      | DAT<3>      | I/O      |  |

| 62      | GND         | -        |  |

| 63      | DAT<4>      | I/O      |  |

| 64      | DAT<5>      | I/O      |  |

| 65      | GND         | -        |  |

| 66      | DAT<6>      | I/O      |  |

| 67      | DAT<7>      | I/O      |  |

| 68      | VDD         | -        |  |

| 69      | VDD         | -        |  |

| 70      | DAT<8>      | I/O      |  |

| 71      | DAT<9>      | I/O      |  |

| 72      | GND         | -        |  |

| 73      | DAT<10>     | I/O      |  |

| 74      | DAT<11>     | I/O      |  |

| 75      | DAT<12>     | I/O      |  |

| 76      | GND         | -        |  |

| 77      | DAT<13>     | I/O      |  |

| 78      | VDD         | -        |  |

| 79      | DAT<14>     | I/O      |  |

| 80      | VDD         | -        |  |

Table.3.1 Pin Assignment

|         | 1           |          |

|---------|-------------|----------|

| Pin No. | Signal Name | I/O type |

| 81      | PHASE       | IN       |

| 82      | CLK         | IN       |

| 83      | GND         | -        |

| 84      | GND         | -        |

| 85      | GND         | -        |

| 86      | DAT<15>     | I/O      |

| 87      | DAT<16>     | I/O      |

| 88      | VDD         | -        |

| 89      | DAT<17>     | I/O      |

| 90      | DAT<18>     | I/O      |

| 91      | DAT<19>     | I/O      |

| 92      | GND         | -        |

| 93      | DAT<20>     | I/O      |

| 94      | DAT<21>     | I/O      |

| 95      | DAT<22>     | I/O      |

| 96      | GND         | -        |

| 97      | DAT<23>     | I/O      |

| 98      | VDD         | -        |

| 99      | VDD         | -        |

| 100     | DAT<24>     | I/O      |

| 101     | DAT<25>     | I/O      |

| 102     | GND         | -        |

| 103     | DAT<26>     | I/O      |

| 104     | DAT<27>     | I/O      |

| 105     | GND         | -        |

| 106     | DAT<28>     | I/O      |

| 107     | DAT<29>     | I/O      |

| 108     | DAT<30>     | I/O      |

| 109     | DAT<31>     | I/O      |

| 110     | VDD         | -        |

| 111     | ADD<0>      | IN       |

| 112     | ADD<1>      | IN       |

| 113     | ADD<2>      | IN       |

| 114     | ADD<3>      | IN       |

| 115     | GND         | -        |

| 116     | GND         | -        |

| 117     | GND         | -        |

| 118     | ADD<4>      | IN       |

| 119     | ADD<5>      | IN       |

| 120     | RSTN        | IN       |

| Pin No. | Signal Name | I/O type |

|---------|-------------|----------|

| 121     | CEN         | IN       |

| 122     | RWN         | IN       |

| 123     | SRCHN       | IN       |

| 124     | OEDATN      | IN       |

| 125     | NC          | OPEN*1   |

| 126     | GND         | =        |

| 127     | GND         | -        |

| 128     | GND         | -        |

<sup>\*1</sup> NC pins must be open. (Do not connect.)

Table 3.1 Pin Assignment (cont'd)

# 3.2 Pin Descriptions

| Pin name                                                                                                                    | Attribute                               | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK                                                                                                                         | <b>CLOCK</b><br>Input<br>LVTTL          | CLK is the master clock input. Other input signals are referred to the rising edge of CLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PHASE                                                                                                                       | PHASE<br>Input<br>LVTTL                 | PHASE determines the action timing of the device. The latency of the output is also determined by the relationship between PHASE and CLK.  Regardless of whether the input mode is 32 bits (Normal Access Mode) or 64 bits (First Access Mode), two cycles of the CLK signals are necessary. PHASE regulates the input timing of the data input from 32-bit DAT<31:0> when the input mode is 64 bits.  When PHASE is high, the data on DAT<31:0> is input in the 32 bits on the MSB side of 64 bits. When PHASE is low, the data is input in the 32 bits on the LSB side. When the input mode is 32 bits, the 32-bit data is written in the register designated by ADD<5:0> on the rising edge of CLK while PHASE is low. |

| DAT<31:0>                                                                                                                   | CPU Bus Input/Output Tristate LVTTL     | DATA<31:0> is a 32-bit, bidirectional data bus used to convey data, to execute commands, and to write/read to and from the registers. The direction is controlled by RWN and there is latency when the bus is switched.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ADD<5:0>                                                                                                                    | CPU Bus Address Bus Input LVTTL         | ADD<5:0> is a 6-bit address bus used to select registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CEN                                                                                                                         | <b>Device Enable</b><br>Input<br>LVTTL  | CEN is used to access the CPU port. The active CEN enables the input operation of data and command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Read/Write selects a write latency between                                                                                  |                                         | RWN is used to determine the direction of the CPU bus. RWN low selects a write cycle, and RWN high selects a read cycle. There is latency between the RWN change and the output as the result of the data bus change.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

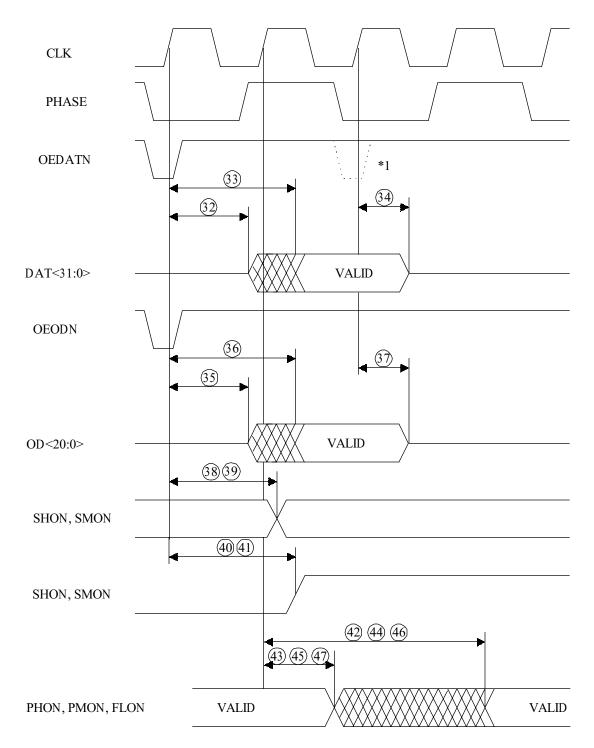

| OEDATN                                                                                                                      | CPU Bus Output Enable<br>Input<br>LVTTL | OEDATN controls the CPU bus output. OEDATN low enables the output of the CPU bus by the read operation, and OEDATN high makes the CPU bus have high impedance despite the output indication by the read operation. There is latency between the OEDATN change and its result.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SRCHN  Search Enable Input LVTTL  SRCHN enables the search operation together with the operation to the comparand register. |                                         | SRCHN enables the search operation together with the write operation to the comparand register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Pin name | Attribute                                    | Function                                                                                                                                                                                                                                                                                                                                    |

|----------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MS<3:0>  | Mask Select<br>Input<br>LVTTL                | MS<3:0> is a mask select signal. One of 12 Mask registers is selected by the MS<3:0>.                                                                                                                                                                                                                                                       |

| RSTN     | Hardware Reset<br>Input<br>LVTTL             | RSTN is used to reset the hardware.                                                                                                                                                                                                                                                                                                         |

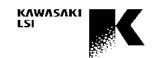

| OD<20:0> | Output Port Output Tristate LVTTL            | OD<20:0> is a 21-bit output port. The device ID is output in the 5 bits, OD<20:16> from the MSB, and HHA, HEA, or MEMHHA is output in the 16 bits from the LSB.                                                                                                                                                                             |

| OEODN    | Output Port Output Enable Input LVTTL        | OEODN controls the Output Port. OEODN low enables the output, and OEODN high disables the output (i.e. the Output Port is made high impedance). There is latency between the OEODN change and its result.                                                                                                                                   |

| OPSL     | Output Port Select Input LVTTL               | OPSL low enables the output of MEMHHA from the Output Port. There is latency between the OPSL change and its result.                                                                                                                                                                                                                        |

| SHON     | Synchronous Hit Output Output LVTTL          | SHON outputs the search results in the device synchronous with the master clock. This pin is low when even one hit occurs in the search operation. This pin is high when no entry is hit.                                                                                                                                                   |

| SMON     | Synchronous Multi-hit Output Output LVTTL    | SMON outputs the search results in the device synchronous with the master clock. This pin is low when multi-hit occurs in the search operation. This pin is high when no multi-hit occurs.                                                                                                                                                  |

| PHON     | Priority Hit Output<br>Output<br>LVTTL       | PHON outputs the search results. This pin is not synchronous with the master clock. This pin is low when even one hit occurs in the search operation. This pin is high when no entry is hit.  In a cascaded system, the hit signal of the cascade configuration appears in the PHON pin of the lowest priority device (Last Device).        |

| PMON     | Priority Multi-hit Output<br>Output<br>LVTTL | PMON outputs the search results. This pin is not synchronous with the master clock. This pin is low when multi-hit occurs in the search operation. This pin is high when no multi-hit occurs.  In a cascaded system, the multi-hit signal of the cascade configuration appears in the PMON pin of the lowest priority device (Last Device). |

| Pin name                   | Attribute                                  | Function                                                                                                                                                                                                                                                                                                            |

|----------------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PHIN                       | Priority Hit Input<br>Input<br>LVTTL       | PHIN is used to connect plural devices in a cascaded system.                                                                                                                                                                                                                                                        |

| PMIN                       | Priority Multi-hit Input<br>Input<br>LVITL | PMIN is used to connect plural devices in a cascaded system.                                                                                                                                                                                                                                                        |

| FLON                       | <b>Full Flag Output</b><br>Output<br>LVTTL | FLON outputs the search results. This pin is low when all entries in the CAM are filled with valid entries (full status) and there is no more entry for a new registration. In a cascaded system, the full signal of the cascade configuration appears in the FLON pin of the lowest priority device (Last Device). |

| FLIN                       | <b>Full Flag Input</b><br>Input<br>LVITL   | FLIN is used in a cascaded system.                                                                                                                                                                                                                                                                                  |

| VDD                        | Supply                                     | Power supply: 3.3V±0.3V                                                                                                                                                                                                                                                                                             |

| GND (Supply) Ground Ground |                                            | Ground                                                                                                                                                                                                                                                                                                              |

# 4. Functional Descriptions

### 4.1 Access from CPU Port

This device has a 32-bit data bus as a CPU port. Data read/write is performed by the registers that are mapped with 32-bit width (Refer to Chapter 7.2). To access registers wider than 32 bits or to access the CAM memory, two data read/write accesses are required. A special high speed write mode (Fast Write Mode) is provided for the data write.

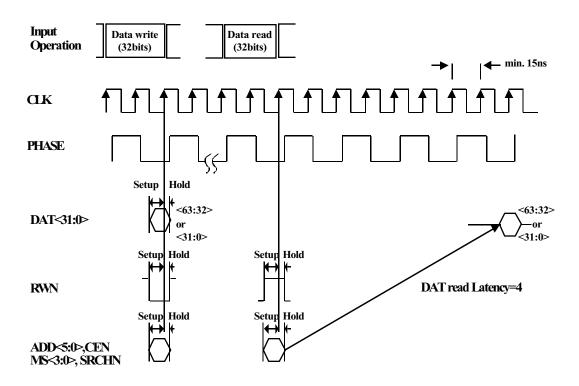

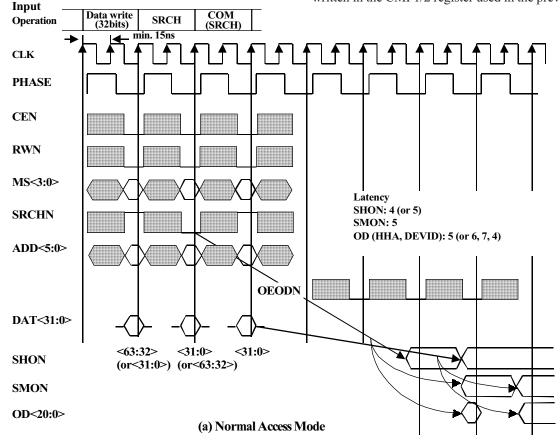

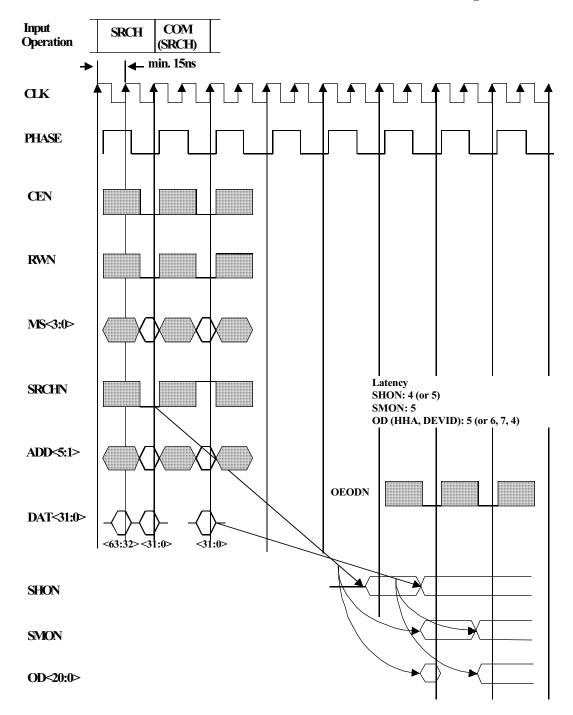

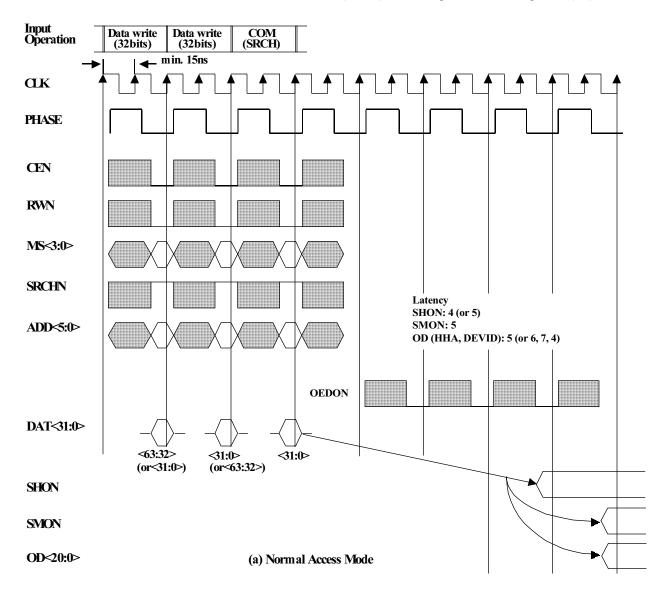

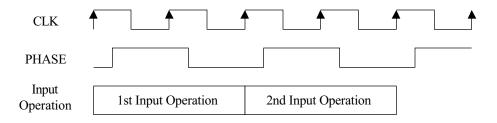

#### • Normal Access Mode

In this mode, one 32-bit data read/write is done with one PHASE signal cycle. Data, address and control signals must be input synchronously with the rising edge of CLK when the PHASE signal, which is a double cycle signal of the CLK, is low. (See Fig. 4.1.1 (a))

All the bits of each register address are valid in this mode. Each 32-bit register is defined by the address pins ADD<5:0>. Two accesses cycles are required for the read/write of 64-bit registers and the CAM memory.

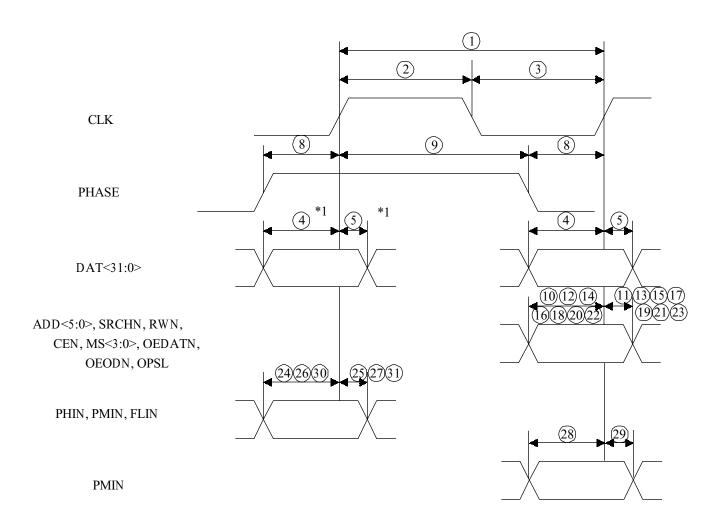

Fig. 4.1.1 (a) CPUAccessMode (NormalAccessMode)

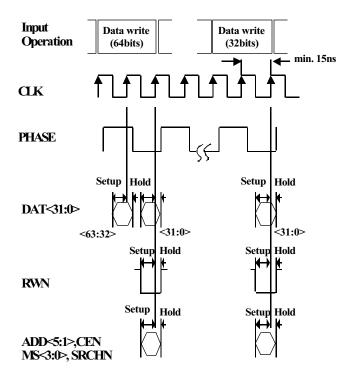

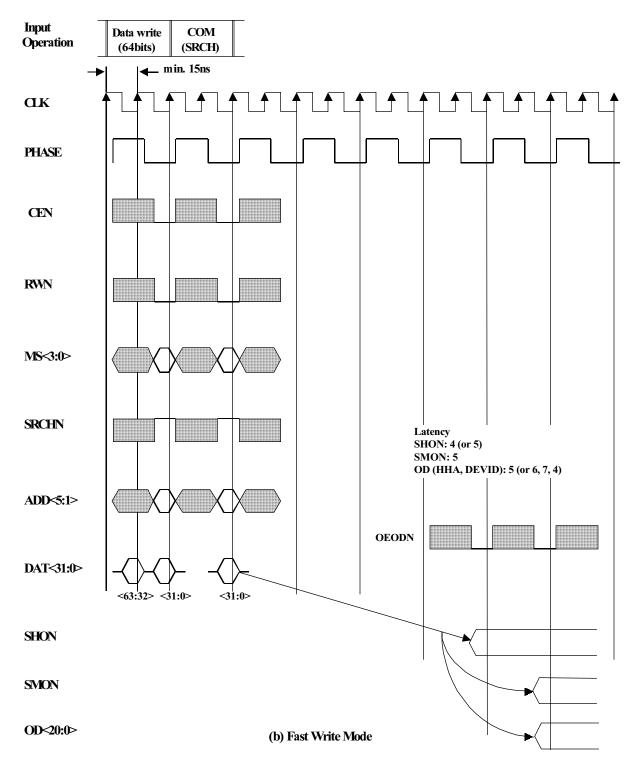

#### • Fast Write Mode

In this mode, one 64-bit data read/write is done within one PHASE signal cycle. The upper 32-bit data of the 64-bit register is input synchronously with the rising edge of CLK when the PHASE signal, which is a double cycle signal of the CLK, is high. The lower 32-bit data of the 64-bit register, address, and control signals are input synchronously with the rising edge of the CLK signal when the PHASE signal is low. (See Fig. 4.1.1 (b)) The LSB of the address is ignored in

this case. If a 32-bit register is accessed in this mode, only the data, the address, and the control signals that are input with the rising edge of CLK while the PHASE signal is low, are valid. (See Fig. 4.1.1 (b)) The LSB of the address is also ignored in this case.

Normal Access or Fast Write Mode is selected by the definition of the CNTL1 register. The initial definition after the device reset is Normal Access Mode.

Fig. 4.1.1 (b) CPUAccessMode (FastWriteMode)

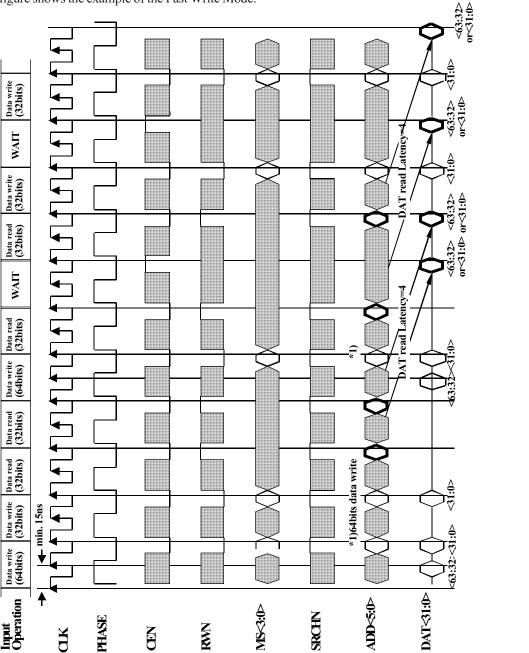

Fig. 4.2.1 Data read/write Timing Chart (Fast Write Mode)

### 4.2 Read/Write Registers

The register address is designated by the address pins of the CPU port, and the data is inputted on the DAT bus. (See Fig. 4.2.1) The function of each register is described in Chapter 7. This figure shows the example of the Fast Write Mode. In case of the Normal Access Mode, data write is the same as the Fast Write Mode shown in Fig. 4.2.1 if you exclude the write of the upper 32 bits of the 64-bit word.

**Preliminary**

# 4.3 Access to the CAM Memory

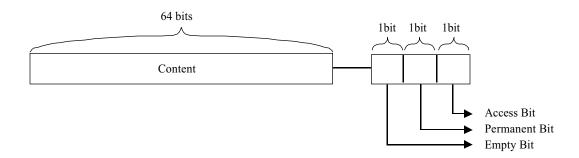

#### Word Structure of CAM

One word of the CAM is made up of 64-bit CAM memory and 3 attribute bits (1 bit each). The 64-bit CAM memory stores the users data to be searched. The attribute bits are

the Empty Bit, the Permanent Bit, and the Access Bit. (See Fig. 4.3.1):

Fig.4.3.1 Word Structure of CAM

**The Empty Bit:** The Empty Bit is a flag that indicates the validity of the CAM word. An invalid word is excluded from the search target and is recognized as a candidate for memory for a new registration of valid data.

The flag logic is:

0 : valid (Valid data is written);

1: invalid (Memory is a space).

**The Permanent Bit:** The entry whose Permanent Bit is set to "1" will not become invalid (Empty Bit = 1) by any purge commands. In order to clear this bit, users can use the reset command.

The Access Bit: The Access Bit is provided for the management of the hit career of each entry. Users can specify whether the hit career is held in the Access Bit or not for each search cycle. Once the Access Bit is set to "1," however, it holds "1" until an Access Bit reset command is executed.

These attribute bits can be directly modified by accessing the MEMAR\_AT, MEMHHA\_AT, and MEMHEA\_AT registers.

These bits are reset by the reset signal from the RSTN pin as follows:

• The Empty Bit : 1 (Invalid)

• The Permanent Bit: 0 (Impermanent)

• The Access Bit: 0 (No hit career)

### • Read/Write CAM Memory

Read/write of the entry data is executed not by direct address indication, but by indirect address indication through specific registers (MEMAR, MEMARAI, MEMAR\_AT, MEMHHA, MEMHHA\_AT, MEMHEA, MEMHEAAI, and MEMHEA\_AT). When writing through MEMAR, MEMARAI, MEMHHA, MEMHEA, and MEMHEAAI, 12 kinds of mask conditions can be selected. Mask in the data write operation means that the data of masked bit is not changed by the write operation. There are two ways to select the mask condition from the 12 mask registers (MASK0 - MASK11). One way is to select it with 4 single pins, MS<3:0> applied dynamically in data write. The other way is to select by the definition in the CNTL1 register statically

The read/write of the CAM memory is basically the same as the read/write of the registers. As shown in Fig. 4.2.1, the mask condition in the write operation is selected by MS<3:0>, the status of these select control signals is latched by the rising edge of CLK while the PHASE signal is low, and the data is written to the memory with Latency 2. The read data is output from the CPU port with Latency 4. (See Section 4.7 about Latency.)

# • Read/Write CAM Data through the MEMAR register

Read/write operation of the CAM word, whose address is designated by the AR register, is executed by the MEMAR register. Write through the MEMAR register changes the attribute bits in the CAM word as follows:

- Empty Bit : 0 (Entry is valid.)

- Permanent Bit : Return to the default value defined in the CNTL1 register

- Access Bit: Return to the default value defined in the CNTL1 register.

# •Read/Write CAM Data through the MEMARAI register

Read/write operation of the CAM word, whose address is designated by the AR register, is executed by the MEMARAI register. One read/write to the MEMARAI register increments the value of the AR register automatically. Write through the MEMARAI register changes the attribute bits in the CAM word as follows:

- Empty Bit : 0 (Entry is valid.)

- Permanent Bit : Return to the default value defined in the CNTL1 register.

- Access Bit: Return to the default value defined in the CNTL1 register.

# •Read/Write CAM Data through the MEMHHA register

Read/write operation of the CAM word, whose address is designated by the HHA register, is executed by the MEMHHA register. Read/write through the MEMHHA register is prohibited when the address stored in the HHA register is invalid, because this may cause an access to the undesired CAM word and the data in it might be destroyed. Read/write through the MEMHHA register does not change the attribute bits in the CAM word.

# •Read/Write CAM Data through the MEMHEA register

Read/write operation of the CAM word, whose address is designated by the HEA register, is executed by the MEMHEA register. Read/write through the MEMHEA register is prohibited when the address stored in the HEA register is invalid, because this may cause an access to the undesired CAM word and the data in it might be destroyed. Write through the MEMHEA register changes the attribute bits in the CAM word as follows:

- Empty Bit : 0 (Entry is valid.)

- Permanent Bit : Return to the default value defined in the CNTL1 register.

- Access Bit: Return to the default value defined in the CNTL1 register.

# •Read/Write CAM Data through the MEMHEAAI register

Read/write operation of the CAM word, whose address is designated by the HEA register, is executed by the MEMHEAAI register. One read/write to the MEMHEAAI register shifts the value of the HEA register to the value of the next HEA automatically. Write through the MEMHEAAI register changes the attribute bits in the CAM word as follows:

- Empty Bit : 0 (Entry is valid.)

- Permanent Bit : Return to the default value defined in the CNTL1 register.

- Access Bit: Return to the default value defined in the CNTL1 register.

# •Read/Write CAM Data through the MEMAR\_AT, MEMHHA\_AT, and MEMHEA AT registers

Read/Write operation to the attribute bits of the CAM word, whose address is designated by the AR, the HHA, and the HEA registers respectively, is executed by these registers. Examples of this operation would be to make the designated CAM word Invalid, to make the designated CAM word Permanent, and/or to change the Access bit of the designated CAM word. Users can mask each attribute bit. (Refer to Chapter 7 for more details.)

This capability also enables the attribute of the CAM word to be read.

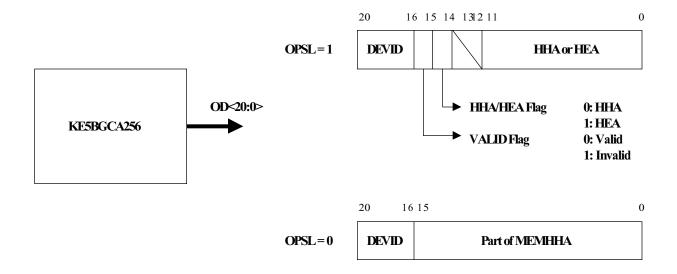

### 4.4 Search

# • Search Operation through the CMP 1/2 register

The key data should be written to the CMP1/2 register from the CPU bus. The low pulse of the SRCHN pin synchronized with the rising edge of CLK while the PHASE signal is low activates the search operation when the key data is written. The mask condition for the search is also chosen from 12 kinds of mask conditions defined by the MASK registers (MASK0 - MASK11), dynamically by the status of the MS<3:0> pins or statically by the CNTL1 register.

The CMP1/2 register stores the key data until the next write

operation is done. Users can choose to perform a Search Operation in the Normal Access mode or the Fast Write mode. The example is shown in Fig. 4.4.1 (a/b).

In Fig. 4.4.1, the search operation is started by the data write to the CMP1/2 register and the synchronous low pulse to the SRCHN pin. As a result, the Hit flag is output on the SHON pin with Latency 4, the Multi-Hit flag is output on the SMON pin with Latency 5, and the HHA and the DEVID of the device which has a hit are output on the OD<20:0> with Latency 5. Fig. 4.4.1 shows two methods for searching the CAM. In this example, the first search is executed by a pulse from the SRCHN pin using the data previously written to the CMP1/2 register. The second search operation is executed by the command, SRCH 1/2. This time, the search operation by command is executed with the data already written in the CMP1/2 register used in the previous search.

Fig. 4.4.1 SRCHOperationthrough CMPRegister Write

Fig. 4.4.1 SRCH Operation through CMP Register Write

(b) Fast Write Mode

### Search Operation by commands

The search command, SRCH 1/2, written to the command register (COM register) activates the search operation using the key data stored in the CMP1/2 register.

The mask condition for the search is chosen at the time of command write from 12 kinds of mask conditions defined by the MASK registers (MASK0 - MASK11). The mask register is chosen dynamically by the status of the MS<3:0> pins on the rising edge of the CLK signal while the PHASE signal is low or statically by the CNTL1 register. Like the search operation above, users can choose the write mode from the Normal Access mode or the Fast Write mode. In both modes, the search operation is started by the command (SRCH). The example is shown in Fig. 4.4.2 (a/b).

Fig. 4.4.2 SRCH Operation with COMMAND

Fig. 4.4.2 SRCH Operation with COMMAND

### Access Bit set while searching

When a hit occurs in the CAM word while searching, the hit result of the entry can be stored as the Access Bit data. This means the past career of the hit results can be managed. For every 12 MASK registers, the determination of whether the search result is stored in the Access Bits or not (whether the Access Bits must be set according to the hit result) can be done using the SCONF register. (Refer to Chapter 7 for more details.)

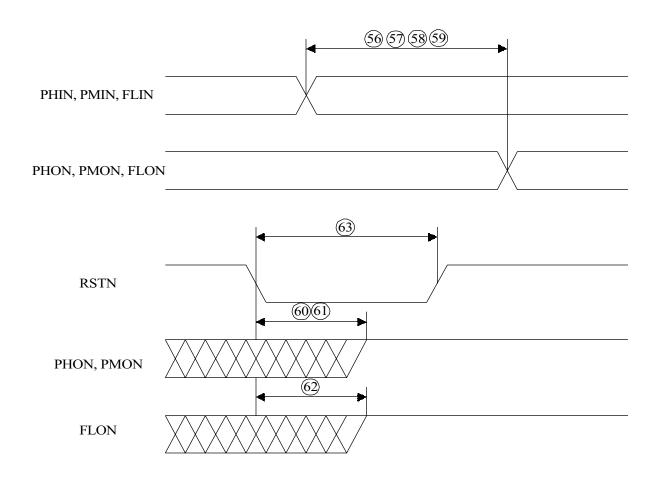

# • Search Result Flag pins (PHON, PMON, SHON, SMON)

The PHON and SHON pins indicate if the Hit word (the CAM word which is hit) exists. A high level on the PHON pin indicates that a single hit does not exist and a low level on this pin indicates that a single hit exists and multi-hit does not exist. A high level on the SHON pin indicates that no hit exist and a low level on this pin indicates that a single hit or Multi-Hit exist. The PHON pin goes to an unknown status when the search operation starts, and it outputs high or low level according to the search result. The PHON pin outputs the search results asynchronously with the CLK. The SHON outputs the corresponding search result synchronously with CLK. (See Fig. 4.4.2. Refer to Chapter 5 for more details)

The PMON and SMON pins indicate if Multi-Hit entries exist. A high level of these pins indicates that a multi-hit does not exist and the low level of this pin indicates that a multi-hit exists. The PMON and SMON pin goes to an unknown status when the search operation starts, and it outputs high or low level according to the search result The PMON pin outputs the search results asynchronously with the CLK. The SHON outputs the corresponding search result synchronously with CLK. (See Fig. 4.4.2.)

### **HHA** register

The HHA register stores the address of the CAM word that is hit by the search operation. The HHA register has the valid bit that indicates the validity of the data stored in the HHA register. This valid bit becomes "0" if single hit (no multi-hit word exist) exists. If a multi-hit or no hit exists, the valid bit becomes "1", invalid. The HHA register also stores the data output to the PHON and PMON pins according to the search result, namely Hit and Multi-Hit flag data (Labeled SYH and SYM in section 7.3 Register Bit Maps). In a cascaded system in which multiple devices are interconnected, the Last Device in the chain holds the Hit and Multi-Hit flags of the total system.

Careful consideration is required for the HHA register, because the HHA (Highest Hit Address) becomes invalid data when a multi-hit exists. The search configuration register, SCONF, allows the user to set the Access Bit according to the search operation results. Even though a multi-hit is set as invalid, all the Access Bits of Hit words are still set.

Hit and Multi-Hit status of the total system is valid only when the HHA register in the Last Device is accessed with the timing which considers the propagation delay between the devices.

### **MEMHHA** register

The MEMHHA register is used to read and write the hit CAM. The mask condition in the 12 MASK registers is also used for a partial write to modify part of the hit CAM word. The write through the MEMHHA register is prohibited when the address stored in the HHA register is invalid, because this may cause access to the undesired CAM word and the data in it might be destroyed.

### **Output from Output Port**

The Output port is a 21-bit output bus used for the search result. The main purpose of this port is to output the HHA. Usually, 5 bits out of the 21 indicate the Device ID (the ID data provided to recognize the device in the system with multiple devices), and the other 16 bits output the HHA that indicates the hit address in the device. The Output port is controlled by the OEODN pin.

The HHA, the HEA, and part of the MEMHHA (16 bits) can be output from the Output port. The SCONF register defines which data set listed above will be output.

The SCONF register holds the following 5-bit information for each of the 12 mask conditions. These bits determine what kind of search result is output from the Output port, caused by the corresponding mask condition:

AS\* (1bit): Whether the Access Bits are set or not HE\* (1bit): Whether the HEA is output or not when no hit MH\* (1bit): Whether part of the MEMHHA is output or not S\*<1:0> (2bits): Which part of the MEMHHA is output 00:MEMHHA<15:0>, 01:MEMHHA<31:16>, 10:MEMHHA<47:32>,11:MEMHHA<63:48> (\*:00-11)

The output data selection with the OPSL pin is necessary to output the MEMHHA. (See Fig. 4.4.3)

Fig.4.4.3OutputPortFormat

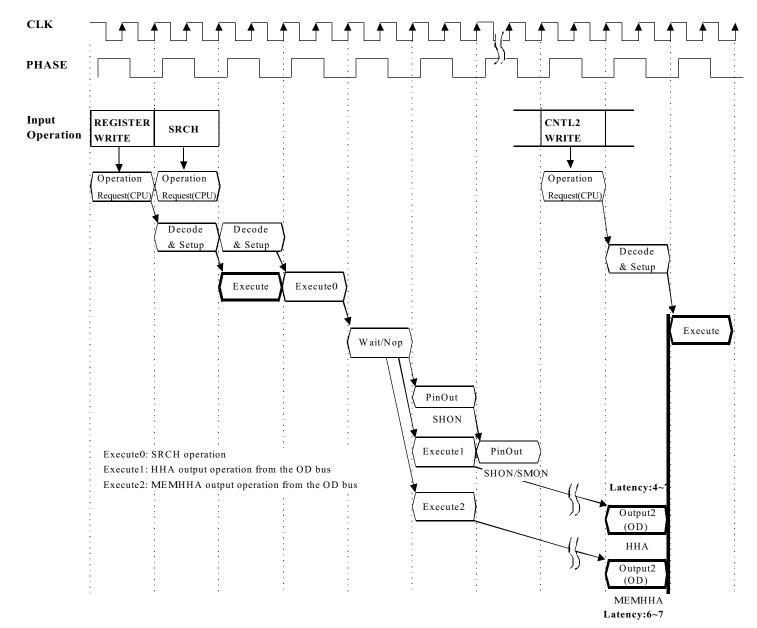

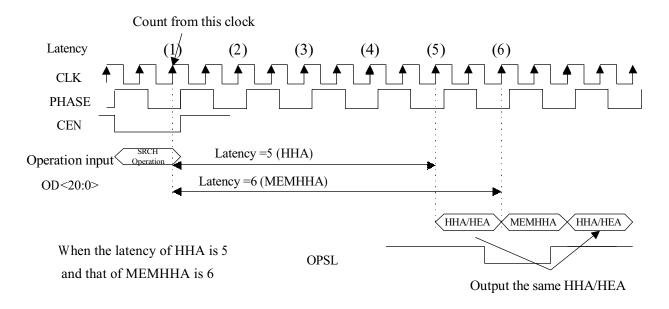

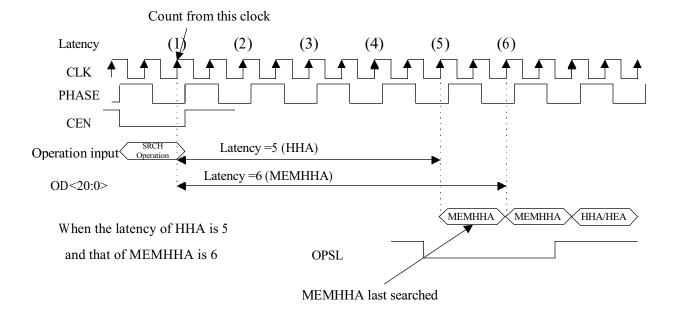

The latency (how many clock cycles of delay from the data input) can be defined by the CNTL2 register. The latency of the HHA output (or the HEA output) can be selected from 4, 5, 6 and 7. The latency of the MEMHHA output can be selected from 6 and 7. (See Fig. 4.4.4)

If the Output port is connected to the same bus in a cascaded system, the output control with the OEODN pin or with the latency selection is required so that the bus conflict does not occur. (Refer to Chapter 5 for more details.)

### Definition of the Mask Register for Search and Write

KE5BGCA256 has 12 Mask registers. There are two methods of Mask selection for each of the four register groups. One way is to select it dynamically with MS<3:0> pins. The other way is to select it statically by the definition in the CNTL1 register.

The registers are broken up into four groups as follows: A Group: The search (or write) with the CMP1 or CMP2 register

B Group: The search with the SRCH1 command or the SRCH2 command

Fig. 4.4.4 Output Latency of SRCHO peration

C Group: The write with the STR commands D Group: The write with the MEM registers

Each of these groups has one bit in the CNTL1 register that is used to define the method of selection, either from the pin MS<3:0>, or from the register. If the mask condition is selected from the register, there are four bits for each group in the CNTL1 register that selects one of the 12 Mask registers. (Refer to Chapter 7 for more details.)

If the mask condition is defined to be selected by the pins, following bits corresponds to each Mask register.

The data of MS<3:0> pins should be input synchronously with the rising edge of CLK when the PHASE signal is low level as described above.

| MS<3:0> pins | s MASK register                                    |

|--------------|----------------------------------------------------|

| 0000         | MASK 0 register defines the mask condition.        |

| 0001         | MASK1 register defines the mask condition.         |

| 0010         | MASK2 register defines the mask condition.         |

| 0011         | MASK3 register defines the mask condition.         |

| 0100         | MASK4 register defines the mask condition.         |

| 0101         | MASK5 register defines the mask condition.         |

| 0110         | MASK6 register defines the mask condition.         |

| 0111         | MASK7 register defines the mask condition.         |

| 1000         | MASK8 register defines the mask condition.         |

| 1001         | MASK9 register defines the mask condition.         |

| 1010         | $MASK10\ register\ defines\ the\ mask\ condition.$ |

| 1011         | $MASK11\ register\ defines\ the\ mask\ condition.$ |

|              |                                                    |

If the bit of the MASK register is "1," the bit is "don't care" and not searched. If the bit of the MASK register is "0," the bit is "care" and searched. One of the 12 MASK registers must always be defined in the search operation.

MASK registers are also used for the mask condition of the write operation to the CAM memory. If the mask is set (The bit is "1."), the corresponding bit of the CAM memory is not changed by the write operation. One of the 12 MASK registers must always be defined in the write operation.

### 4.5 Data Management by Commands

KE5BGCA256 has several commands for data management. This chapter describes the important points. (Refer to Chapter 6 for more details.)

### • Data management using Access Bits

The following three commands are provided regarding the Access Bits:

PRG\_AC: Erases all the CAM words whose Access Bits are "1."

PRG\_NAC: Erases all the CAM words whose Access Bits are "0."

RST\_AC: Clears all the Access Bits (Access Bit: 0).

An example of using these commands would be to perform a search with the definition that the hit career is being held in the Access Bit, then delete unnecessary CAM words whose Access Bits are "1" (or "0"). Another example is to delete all the CAM words which hit (or did not hit) after the search with certain data.

### • Data management using Store Commands

### STR1/2 HHAcommand

This command overwrites the data of the CMP1/2 register to the hit CAM word using the mask condition of the defined Mask register. In other words, this command is a partial (maskable) write to the hit address, and it is useful for time stamping to the CAM word. The time stamping data can be used, for example, to find the oldest CAM words by searching this, and delete them.

### STR1/2 HEAcommand

This command overwrites the data of the CMP1/2 register to the empty CAM word using the mask condition of the defined Mask register. In other words, this command is a partial (maskable) write to the empty address, and it is useful to register new CAM word data when there is no hit CAM word in the search.

The commands STR1/2\_HHA and STR1/2\_HEA should be executed according to the search result. KE5BGCA256 op-

erates with the Pipeline method synchronously with the external system clock causing multiple steps of latency before receiving the results of each operation. If the command is executed after receiving the result of each operation, it will affect the performance.

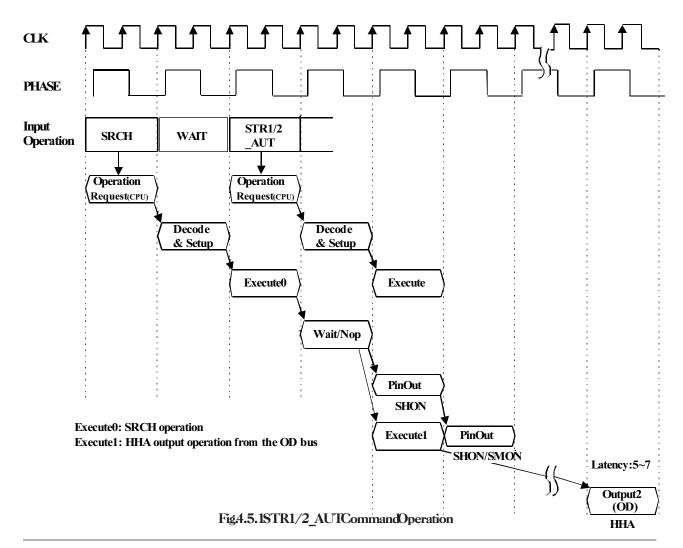

### STR1/2\_AUTcommand

To avoid the performance problem described above, the STR1/2\_AUT command is provided in this device.

This command executes the same operation as the STR1/2\_HHA command if the device has a hit, and executes the

same operation as the STR1/2\_HEA command if the device does not have a hit. Users can execute this command regardless of whether the device has a hit or not, so that the overhead caused by the unnecessary judging cycles can be reduced.

The example is shown in Fig. 4.5.1. The status of the internal pipeline is also shown in the example. (Refer to Chapter 4.6 for more details.) The STR1/2\_AUT command is executed one wait after the external request for the search. The one wait in this example is inserted because the idle time of one PHASE signal is necessary to utilize the search result information such as a Hit. However, the STR\_AUT command should only be used when the cascade connection uses external logic. (Refer to Chapter 5 for more details.)

For these STR commands, users can use the mask condition defined by MS<3:0> pins or the CNTL1 register. When using the CNTL1 register, this would be group C.

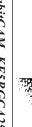

### 4.6 Restriction in Pipeline Operation

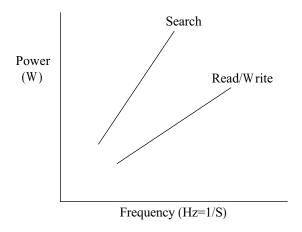

KE5BGCA256 is designed to use a maximum main clock of 66 MHz. This clock is synchronized with external requests, resulting in operations which are processed by the internal Pipeline. Internal Pipeline processing has several stages corresponding to various requests for operation. When users request multiple operations continuously from the outside, these operations must be requested so that a conflict between the Pipeline stages does not occur.

This Chapter describes the ways the internal pipeline stages work to process the external request, and the rules for continuous input of the various operations.

### • Stages of pipeline

The following are five groups of stages of the Pipeline for the operation request:

#### (1) Operation Request Stage

In this stage, the operation is requested through the CPU bus, with the data and the address input being latched. There are two kinds of stages, Read request stage and Write request stage. The difference between these two stages depends upon whether the DAT bus is occupied. The Read request stage does not occupy the DAT bus, but the Write request stage occupies the DAT bus.

### (2) Decode & Setup Stage

This stage follows the Operation Request Stage. The data or the address that is latched in the Operation Request Stage is decoded to recognize the request, and then the necessary data is set up in this stage.

### (3) Execute Stage

In this stage, the external request for operation is executed. There are two kinds of operations, the operations that can be executed with the other pipeline stage, See Fig. 4.5.1, and the operations that cannot be executed with the other pipeline stage, according to which block in the device is executed.

### (4) Wait/Nop Stage

This stage is for the timing adjustment of the internal bus driving.

#### (5) Output Stage

Two stages, Output1 and Output2, are included. Output1 is the stage for the output of the DAT bus, and Output2 is the stage for the output of the OD bus. Output1 and Output2 can be executed simultaneously because these ports, DAT bus and OD bus, are different ports.

### Processing and Pipeline Stages

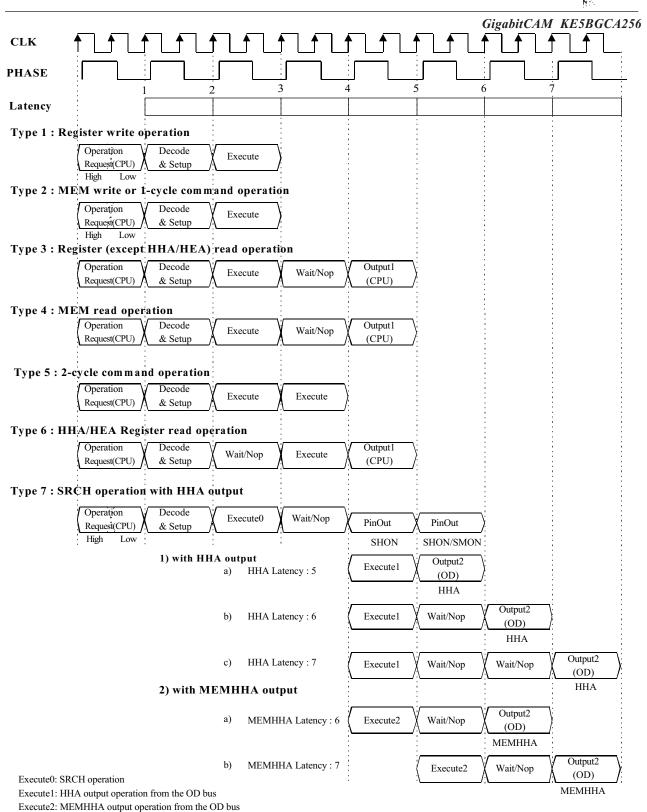

The following seven Types are the categories of operation according to the Pipeline Stages:

Fig. 4.6.1(a) Pipeline Operation Stage Chart

Type1: Registers write operation

Type2: MEM\* write operation \*1 or 1 cycle command operation

Type3: Registers (except HHA and HEA) read operation

Type4: MEM\* read operation \*1

Type5: 2 -cycle command operation \*2

Type6: HHA/HEA register read operation

Type7: SRCH operation with HHA read (with HEA read)

- \*1): The read/write of the MEMHEAAI register is in Type5.

- \*2): SRST, GEN\_FL, NXT\_HE, STR1\_HEAAI, STR1\_AUTAI, STR2\_HEAAI, STR2\_AUTAI commands

The Pipeline Stage timing of each Type is shown in Fig. 4.6.1. As shown in Fig. 4.6.1(a), the Operation Request Stage in Type 1, 2, 7 is divided into two stages (High and Low) because the 64-bit data could possibly be written to the register or to the CAM word using the Fast Write Mode (64-bit access per one PHASE signal cycle).

# Restriction of simultaneous execution of Pipeline Stages

There are some restrictions of simultaneous executions of the internal Pipeline Stages. Basically, the simultaneous execution of the different Pipeline Stages is possible if they are in different Pipelines, but the simultaneous execution must meet the following restrictions:

- 1) The Write Request of the Operation Request Stage and the Outputl Stage must not be executed simultaneously because they use the same bus (DAT bus).

- 2) Any operation can execute simultaneously during Wait/Nop Stages.

- 3) The possible simultaneous operations of the Execute Stages between the multiple Pipelines are restricted to the following 3 cases:

- a) The Execute of Type5 and the Execute of Types 1-7

- b) The Execute of Type6 and the Execute of Types 1-7

- c) The Execute1 and the Execute2 of Type7 and the Execute of Types 1-6

These executions must follow the restriction shown in Table 4.6.1. The column of the Table 4.6.1 means Execute stage which is possible to simultaneously execute. As shown in Fig. 4.6.1 (b), the the column of the table means 1st Input Operation, and the row of the table means 2nd Input Operation.

Fig. 4.6.1(b) Restriction of pipeline

| 1st Input<br>Operation<br>2nd Input<br>Operation                      | Type 5: 2-cycle command operation *4) | Type 6 : HHA/HEA Register read operation | Type 7 : SRCH operation with HHA output | with MEMHHA output |

|-----------------------------------------------------------------------|---------------------------------------|------------------------------------------|-----------------------------------------|--------------------|

| Type 1 :<br>Register write operation                                  | 0                                     | 0                                        | O *3)                                   | O *3)              |

| Type 2 : MEM_HHA, _HEA, _AR, _ARAI write or 1-cycle command operation | <b>△</b> *1)                          | 0                                        | 0                                       | X                  |

| Type 3 :<br>Register (except HHA/HEA)<br>read operation               | 0                                     | 0                                        | 0                                       | 0                  |

| Type 4:  MEM_HHA, _HEA, _AR, _ARAI read operation                     | 0                                     | 0                                        | 0                                       | 0                  |

| Type 5: 2-cycle command operation, MEMHEAAI                           | X                                     | <b>△</b> *5)                             | 0                                       | 0                  |

| Type 6 :<br>HHA/HEA Register<br>read operation                        | 0                                     | X                                        | 0                                       | 0                  |

| Type 7 :<br>SRCH operation with HHA output                            | X *2)                                 | △ *6)                                    | X                                       | X                  |

| with MEMHHA output                                                    | X                                     | △ *6)                                    | X                                       | X                  |

<sup>\*1)</sup> Only the NXT\_HE command and MEM write can be simultaneously executed.

<sup>\*6)</sup> Execute of the HHA read operation cannot be simultaneously executed Execute of search operation.

0

Δ

X

: allowed

: not allowed

: allowed partially

<sup>\*2)</sup> Impossible to simultaneously execute with the Execute 0 of the SRCH operation.

<sup>\*3)</sup> Impossible to simultaneously execute with the write to the CNTL2 register.

<sup>\*4)</sup> In case of the SRST command, reset operation has priority.

<sup>\*5)</sup> Execute of the HEA read operation cannot be simultaneously executed Execute of

the GEN\_FL, NXT\_HE, STR1/2\_HEAAI, STR1/2\_AUTAI (mis-hit case), and MEMHEAAI access.

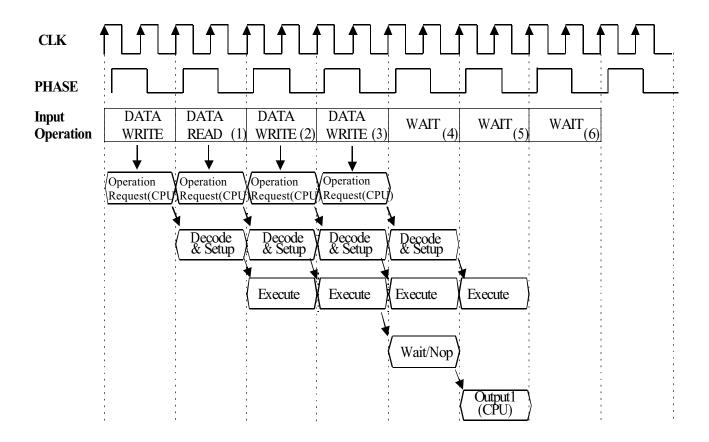

# • Restriction in usage of the result of data operation in each Pipeline

#### **Data Write and Read**

The write and read operations of the data are classified into Type 1/2 and Type 3/4. As shown in Fig. 4.6.2, DATA WRITE (2), (3) Input Operation can be put on after DATA READ Input Operation to use pipeline of the device effectually. However, (4) ~ (5) Input Operation stage cannot be used because data output of DATA READ (1) starts on the WAIT stage (5).

# **Definition of Search Condition and Search Operation**

The search operation can executed immediately after the search condition has been changed with the write to the CNTL1 register, the MASK register, or to the SCONF register. It is not possible to change the output latency during the search operation. The search condition (latency) must be kept unchanged until the Output operation of the search result has been completed (See Fig. 4.6.4).

The output latency is defined in the CNTL2 register.

Fig.4.6.2 Restrictions between Data Read/Write Operations

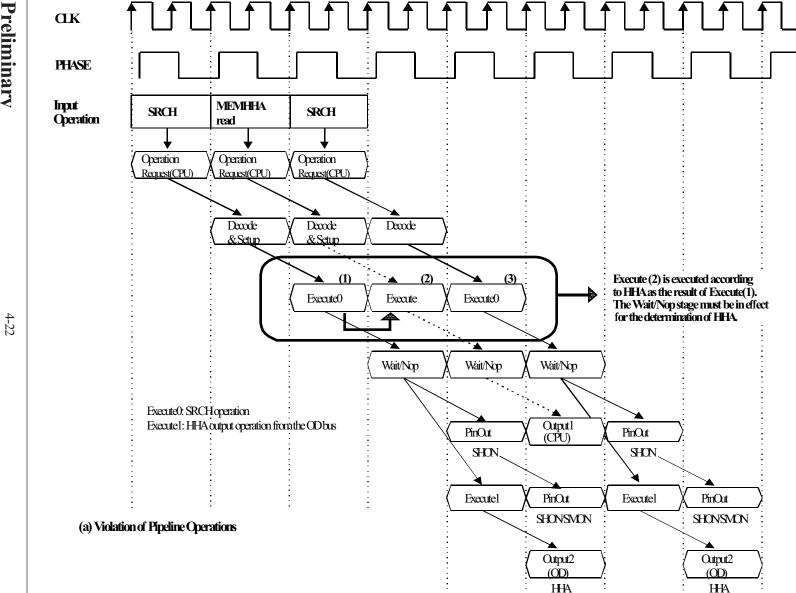

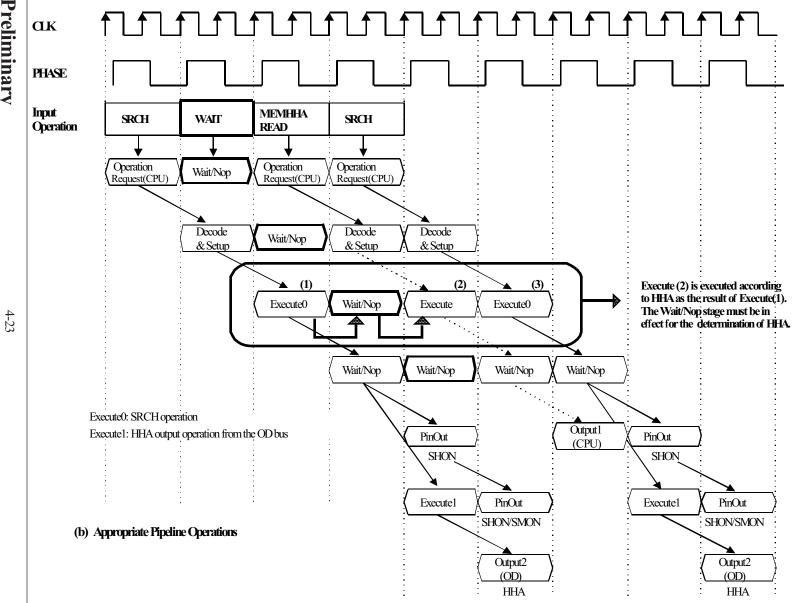

#### Search and Use of the Search Result

For continuous operations executed through the CPU, some operations are restricted. These types of operations must be executed according to the result of the previous operation. An example would be when reading the HHA through the CPU port using the MEMHHA register after the search operation. Using this example, the restriction of the usage of the result of data processing is described. As shown in Fig. 4.6.1, the HHA is determined in the Wait/Nop Stage, one cycle after the Execute0 stage for a search operation which is Type7. If the reading of the MEMHHA is requested right after the request of the search operation, as shown in Fig. 4.6.3 (a), the Execute of the read operation of the MEMHHA is executed at the same time as the Wait/Nop stage of the SRCH. The value in the HHA has not been decided yet, so this Execute is not executed correctly. This is because the reading operation of the MEMHHA uses the HHA. In the cases as above, one wait is necessary before an operation which uses the HHA, such as the request for reading the MEMHHA register (See Fig. 4.6.3 (b).). If the search is performed after an operation which uses the HHA, such as reading the MEMHHA register, one wait is not necessary.

#### Change the HEA and Use of the HEA

In the same way as the HHA, two waits are necessary before an operation which uses the HEA, such as the request for reading the MEMHEA register (See Fig. 4.6.3 (c).). If an operation which changes the HEA is performed after an operation which uses the HEA, two waits are not necessary.

# Operations which change the HHA or the HEA and Operations which use the HHA or the HEA

The operations which change the HHA or change the HEA and the operation which use the HHA or use the HEA, are listed as follows.

Operations which change the HHA Search operation with the SRCHN pin SRCH1/2command

Operations which change the HEA

MEMHEAAI register access

GEN\_FL,NXT\_HE,STR1/2\_HEAAI,STR1/2\_AUTAI

commands

Operations which use the HHA MEMHHA register access STR1/2\_HHA, STR1/2\_AUT (hit case), STR1/2\_AUTAI (hit case) commands

Operations which use the HEA

MEMHEA register access

MEMHEAAI register access

STR1/2\_HEA, STR1/2\_AUT (mis-hit case),

STR1/2\_AUTAI (mis-hit case) commands

Fig. 4.6.3(a) Restriction Example between Pipeline Operations

Fig. 4.6.3 (b) Restriction Example between Pipeline Operations (cont'd)

Output 1

(CPU)

(c) Appropriate Pipeline Operations

Fig. 4.6.3 (c) Restriction Example between Pipeline Operations (cont'd)

Fig. 4.6.4Restrictions between SRCHO peration and Search Condition Definition Operation

## 4.7 Latency

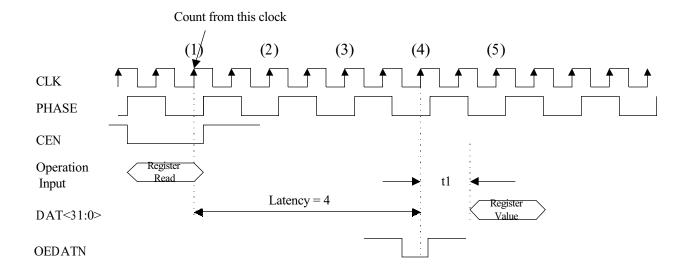

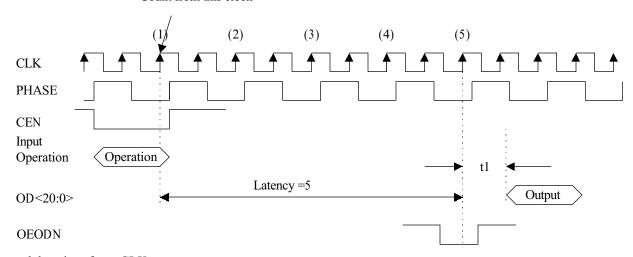

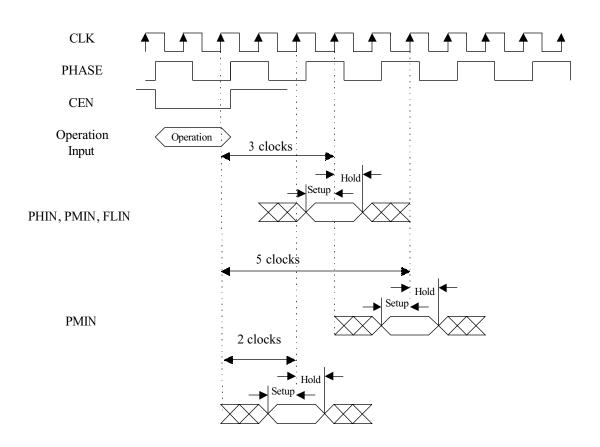

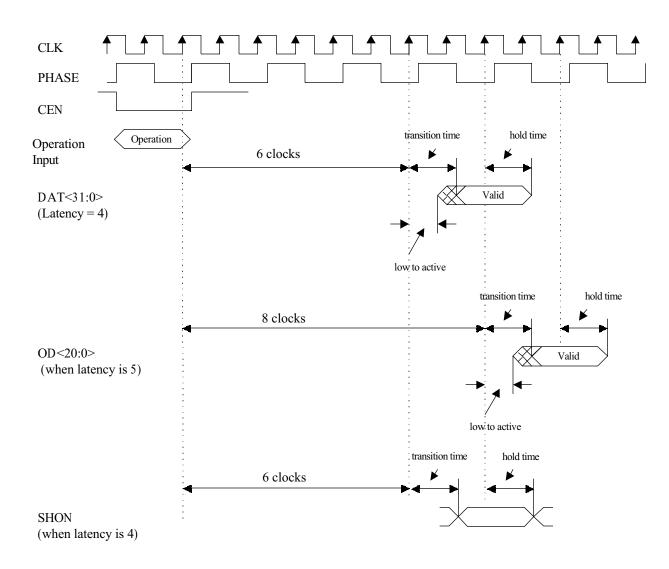

This device operates with the CLK signals as the master clock. Therefore, there is latency which is characteristic for a synchronous circuit between some action and the following action. Latency is counted by the number of rising edge of the CLK signals when the PHASE signal is low from the input operation, as shown in Fig. 4.7.1, 4.7.2 For example, Fig. 4.7.1 shows that the output latency of the CPU port is 4.

Fig. 4.7.2 shows that the output latency of the Output port is 5.

Table 4.7.1 shows the output latency.

There is also execution latency in read/write operation by commands or registers. (See Fig. 4.6.1)

The user that the values for latency can be modified by writing to the CNTL2 register.

t1: output delay time from CLK which is provided in Chapter 9

Fig. 4.7.1 Output Latency on the CPU Port

## Count from this clock

t1: output delay time from CLK which is provided in Chapter 9

Fig. 4.7.2 Output Latency on the Output Port

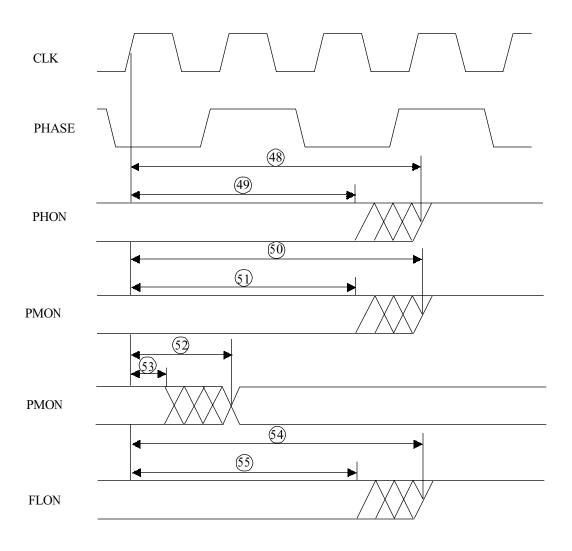

| Pins      | Latency                                                                                       |  |  |  |

|-----------|-----------------------------------------------------------------------------------------------|--|--|--|

| DAT<31:0> | · Latency is fixed to be 4.                                                                   |  |  |  |

|           | · Latency (OEDATN => DAT<31:0>) is 1.                                                         |  |  |  |

|           | · Latency can be selected from 4, 5, 6, and 7 in HHA/HEA output.                              |  |  |  |

| OD<20:0>  | · Latency from the operation to renew the HEA is equal to the HEA/HHA latency.                |  |  |  |

|           | · Latency can be selected from 6 and 7 in MEMHHA output.                                      |  |  |  |

|           | · Latency (OEODN => OD<20:0>) is 1.                                                           |  |  |  |

|           | · Latency can be selected from 4 and 5.                                                       |  |  |  |

| SHON      | · Latency is 2.5 when the SRST command is executed. (See Fig. 9.4.3)                          |  |  |  |

|           | · Latency is 0.5 from the RSTN low pulse. (See Fig. 9.4.3)                                    |  |  |  |

|           | · Latency is fixed to be 5.                                                                   |  |  |  |

| SMON      | · Latency is 2.5 when the SRST command is executed. (See Fig. 9.4.3)                          |  |  |  |

|           | · Latency is 0.5 from the RSTN low pulse. (See Fig. 9.4.3)                                    |  |  |  |

|           | · When MEM_HEAAI is accessed or the GEN_FL, NXT_HE, STR1_HEAAI,                               |  |  |  |

| FLON      | STR2_HEAAI, STR1_AUTAI, or STR2_AUTAI command is executed, latency is 2.5.                    |  |  |  |

|           | · Latency is 2 when the SRST command is executed.                                             |  |  |  |

|           | · Latency is 0 from the RSTN low pulse.                                                       |  |  |  |

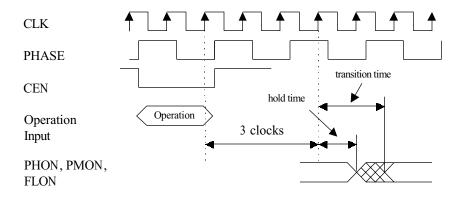

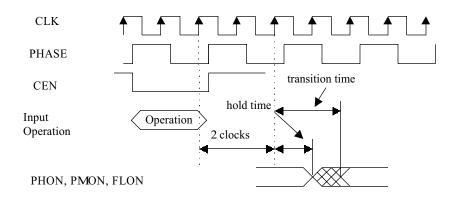

| BHON      | · When the search operation by the SRCHN pin or the SRCH command is executed,                 |  |  |  |

| PHON      | latency is 2.5.                                                                               |  |  |  |

|           | Latency is 0 from the RSTN low pulse.                                                         |  |  |  |

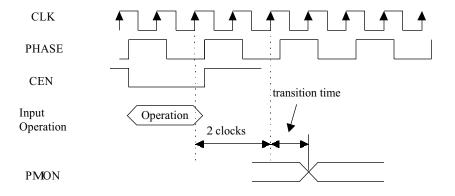

| PMON      | · When the search operation by the SRCHN pin or the SRCH command is executed, latency is 2.5. |  |  |  |

| 1 IVION   | Latency is 0 from the RSTN low pulse.                                                         |  |  |  |

|           | · When the SRST, STR_DEVID, END_DEVID, and NXT_PR command is executed,                        |  |  |  |

|           | latency is 2.                                                                                 |  |  |  |

Table 4.7.1 Output Latency

## 5. Connection

## 5.1 Initialization

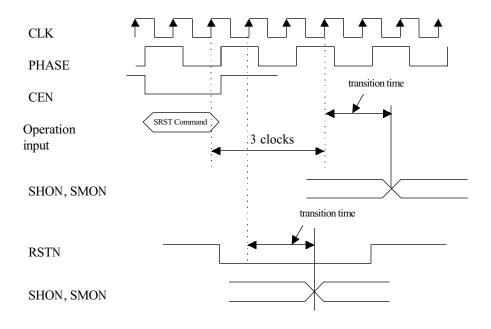

There are two types of initialization for this device: Hardware reset by setting the RSTN pin to a low level, and Software reset by executing the SRST command.

Hardware reset must be done after the power is on.

Hardware reset or Software reset executes the following initialization:

- 1) Initializes Device ID \*1

- 2) Initializes registers

- 3) Sets Empty Bits of all entries (all entries are empty)

- 4) Clears Permanent Bits of all entries

- 5) Clears Access Bits of all entries

- 6) PHON = 1, SHON = 1

- 7) PMON = 1, SMON = 1

- 8) FLON=1

- \*1 Device ID must be registered after reset when devices are cascaded.

Fig 5.3.1.1 Device ID registration

# **5.2** Single Device Operation

to the CAM table.

A device reset either by a Hardware reset using the RSTN low pulse or software reset using the SRST command automatically sets the Device ID to "00000" and the LD bit to "1". The LD bit means the Last Device in a cascaded system. Therefore, it is not necessary to set the Device ID by using the DEVID mode in the single device operation. The PHIN and PMIN pins must be pulled up and the FLIN pin must be pulled down with a single device.

The GEN FL command must be executed after registration

When used in a single device operation, the device acts as one with hit/empty priority if there is any hit/empty entry in the device. On the other hand, it acts as the Last Device if there is no hit/empty entry in the device. Therefore, the behavior is the same in the broadcast method as in the device select method, but some commands must be executed in the device select method according to the condition of Table 6.2, and some registers must be accessed in the device select method according to the condition of Table 7.4.1, even in

Fig.5.3.1.2 Device ID registration procedure

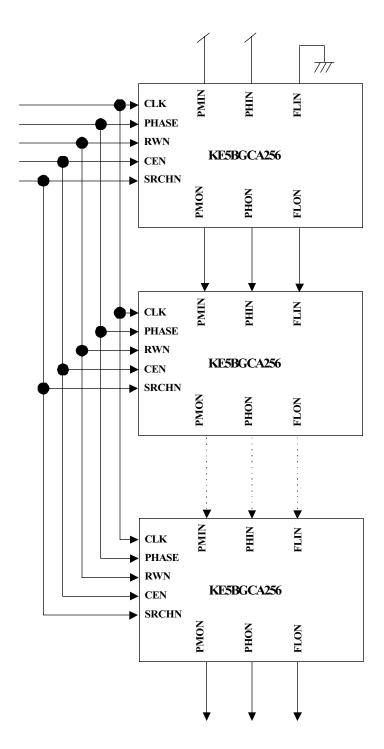

#### 5.3 Cascade Connection

### **5.3.1 Device ID Registration**

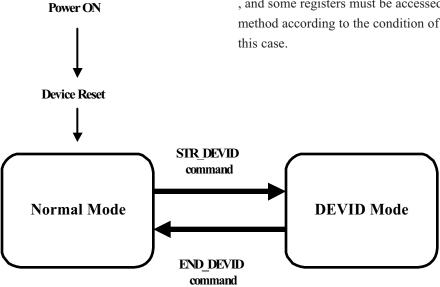

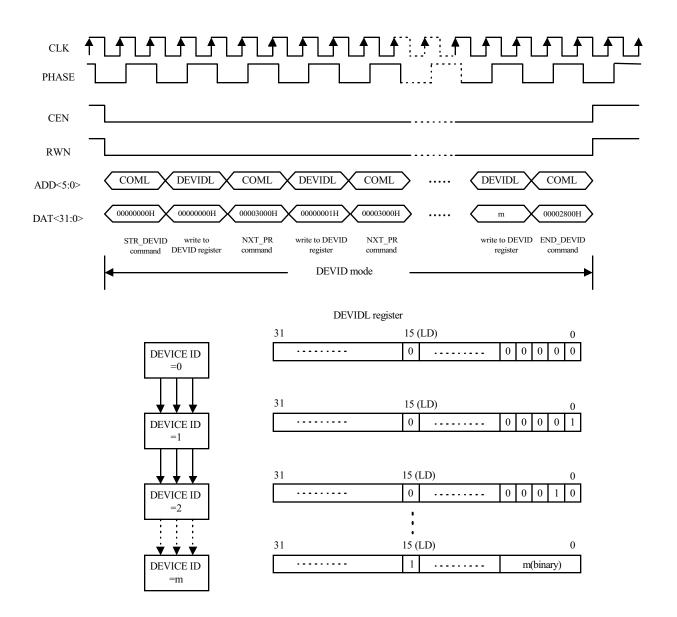

The device can be cascaded to use a maximum of 32 devices. A cascaded system can be treated as one device which has a larger table size. It is necessary to define the Device ID in the DEVID register in order to identify each device in the operation of a cascaded system. The procedure for registration of the Device ID is shown in Fig. 5.3.1.2.

In order to set the Device ID, the devices in a cascaded system must be moved into the DEVID mode by the STR\_DEVID command as shown in Fig. 5.3.1.1. The STR\_DEVID command enables the user to apply read/write operations to the DEVID register of the highest (top) device in the cascaded system. The Device ID is set in the DI<4:0> of the register. After that, the Device ID of the next device can be set by the NXT\_PR command. The registration should be repeated down the chain until each device is given a unique Device ID by repeating these operations. If the STR\_DEVID command is executed among these operations, it returns to the status where the DEVID register of the highest (top) device can be read/written.

The Device ID must be a continuous number starting from the top device. The LD in the Last Device DEVID register must be set to "1." This bit indicates that the device has the lowest priority, and it is used to control the data outputs. The LD bits of all devices except the Last Device must be set to "0."

After the DEVID registers of all devices are set, the devices should be moved out of the DEVID mode and into the normal operation mode by executing the END\_DEVID command. The devices must leave the DEVID mode after all Device IDs are set, because operations like Table Configuration or search cannot be executed correctly in the DEVID

mode. Waiting time is recommended to ensure that the PMIN and PMON pins become stable.

The Device IDs of all devices are initialized to the same value of "00000" after device reset. The operations described above, from the STR\_DEVID command, must be executed after device reset. If only one device is used, the Device ID registration is not necessary.

Do not register the Device ID in normal operation mode once the Device ID is set after device reset.

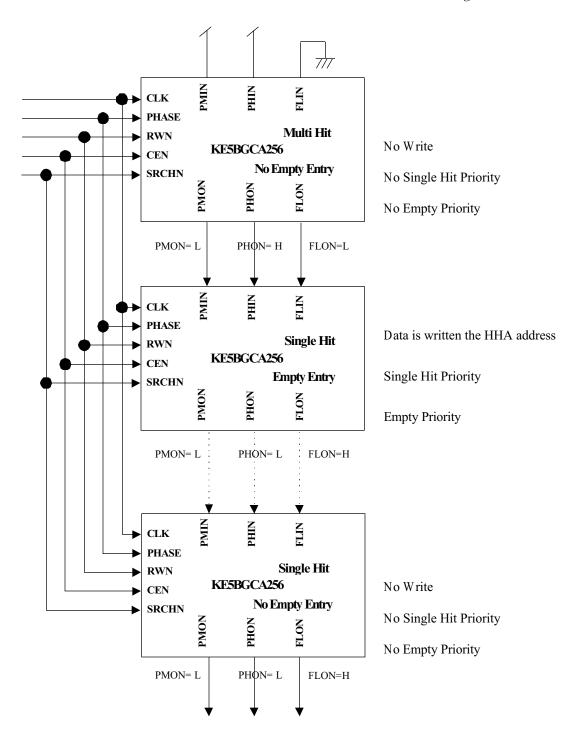

## 5.3.2 Priority

In a cascaded system, the data buses of the CPU Port and the Output Port must be connected to all devices. As for the CPU Port, the same data is written to all devices through DAT<31:0> and the same Pipeline is executed in all devices. The output device is automatically determined in the broadcast method and the device in which the MEMHHA or the MEMHEA register is written, or the device in which the STR\_HHA, the STR\_HEA, or the STR\_AUT command is executed, is also determined automatically. As for the Output Port, all devices output the search results respectively. The Output Port must therefore be controlled by the users' logic using the SHON when there is a multi-hit in the system, when there are many devices with a single hit, or when HEA is set to be output in a no hit case.

The empty priority is controlled in this device, but the hit priority is not controlled in order to realize a higher speed. The HHA as a result of the multi-hit in the device therefore becomes invalid, and the write operation to the entry designated by the HHA is not executed. The above-mentioned priority control is, however, executed in the cascaded system including the device in which the multi-hit occurs. It is also possible not to write, regarding the multi-hit in the system as illegal status by the cascade connection method described later.

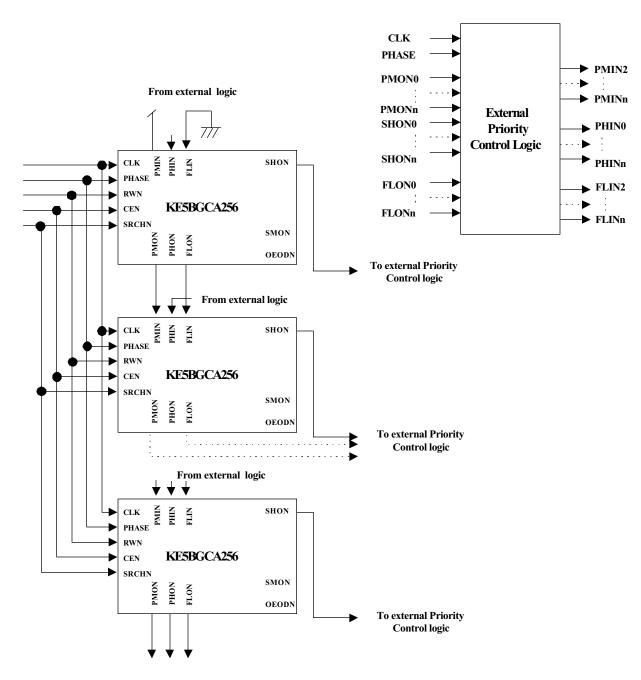

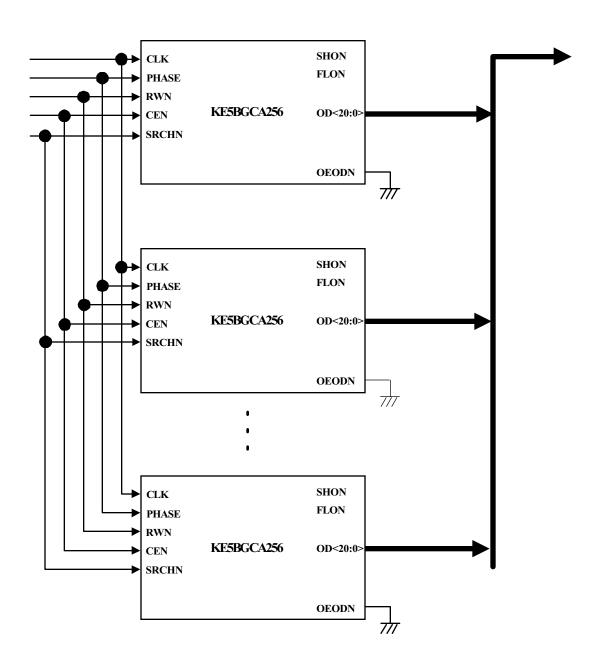

Fig.5.3.2.1 Cascade Connection

Three priorities are used for these controls: the single-hit priority, the empty priority, and the DEVID priority. THE PHIN, PMIN, FLIN, PHON, PMON, and FLON pins are used to propagate the priorities.

#### (1) Single Hit Priority

In a cascaded system, the uppermost located device among all devices that have hit entries, except the devices in which the multi-hit occurs, is defined as having hit priority. (See Fig. 5.3.2.1) This priority is propagated through the PHON and the PHIN. When a multi-hit does not occur in a device and the upper devices have single hit priority, the PHON of the device outputs "0." When neither single hit nor multi-hit occurs in the device and the upper devices do not have single hit priority, the PHON of the device outputs "1." In order to have a device having single hit priority, the PHIN of the device must be set to "1."

#### (2) Empty Priority

In a cascaded system, the uppermost located device among all devices that have empty entries is defined as having empty priority (See Fig.5.3.2.1). This priority is propagated through the FLON and the FLIN. When a device is full status and the upper devices are full, the FLON of the device outputs "0." When the device is not full or the upper devices are not full, the FLON of the device outputs "1." In order to have a device having empty priority, the FLIN of the device must be set to "0."

#### (3) DEVID Priority

DEVID priority specifies which device accepts the Device ID data in the DEVID mode. DEVID priority is propagated through the PMIN and PMON pins in the DEVID mode. However, the PMIN and PMON pins propagate multi-hit information in something other than the DEVID mode.

#### (4) Last Device

The device located at the bottom of the cascaded chain must be known in order to perform internal control of the device. The LD bit in the DEVID register of the bottom device must be set to "1" to indicate that it is the "Last Device."

For example, the Last Device stores the total hit and empty information of the cascaded system in the HHA and HEA registers. The Last Device outputs the bits: HV, EV, SYH, SYM, SYE, HT, MH, the address with hit priority or empty priority when the HHA or HEA register is read in the broadcast method. If there is no device having single hit priority, the Last Device outputs the data of the HHA register in the broadcast method. The HV flag of the output data is "1" and that indicates that the HHA is invalid. In the same manner, if there is no device having empty priority, the Last Device outputs the data of the HEA register in the broadcast method. The EV flag of the output data is "1" and that indicates that the HEA is invalid. In a cascade system, for registers that have the same data in each device, such as the CNTL1/2 and the SCONF register, when these registers are read in the broadcast method, the Last Device outputs the register's data.

# 5.3.3 CPU Port in a Cascaded System

#### Read/Write Registers

Read/write operations (including command execution) can be performed by both the broadcast and the device select method.

This selection is defined in the DEVSEL register. The BR bit in the DEVSEL register must be set to "0" in the device select method. The selected device can be specified by the DS<4:0> in the DEVSEL register. The BR must be set to "1"

in the broadcast method. When data is written to a register, one of the following operations is executed according to the attribute of the register:

- (1) Write to all devices simultaneously

- (2) Write to the device which has single hit priority

- (3) Write to the device which has empty priority

When data is read from a register, one of the following operations is executed according to the attribute of the register:

- (1) Read from the Last Device

- (2) Read from the device which has single hit priority

- (3) Read from the device which has empty priority

For registers which must have common data for all devices, the device select method is invalid and data is written to appropriate register of all the devices. Some registers must be accessed by the device select method. See Table 7.4.1 in Chapter 7 for Read/Write availability of each register in the broadcast method/device select method and the output device that is accessed in the broadcast method.

#### **Command Execution**

The command of the device should be executed by the broadcast method in a cascaded system. The device to which the command execution applies is automatically decided internally in this case.

#### Cascade Connection of the CPU Port

Cascade connection methods of multiple devices are shown below:

- (1) Priority control without the external logic

- (2) Priority control with the external logic

A cascade connection can be realized by either of the two methods. Table 5.3.3.1 shows the relationship between cascade input pins and their actions. When the priority is controlled by the external logic, the external circuit must be designed referring to Table 5.3.3.1 and Fig. 5.3.3.3.

#### (1) Connection without the External Logic

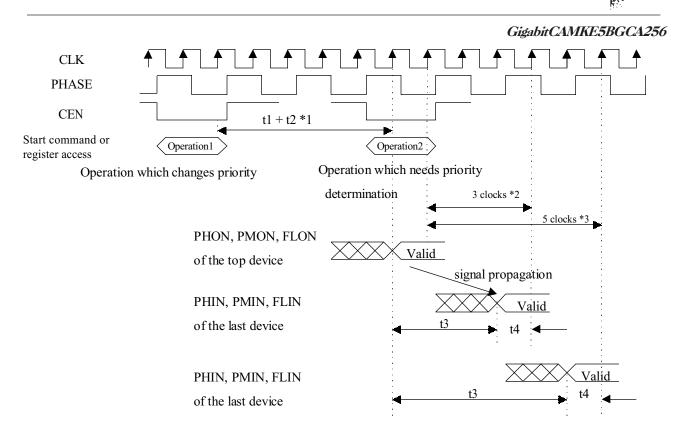

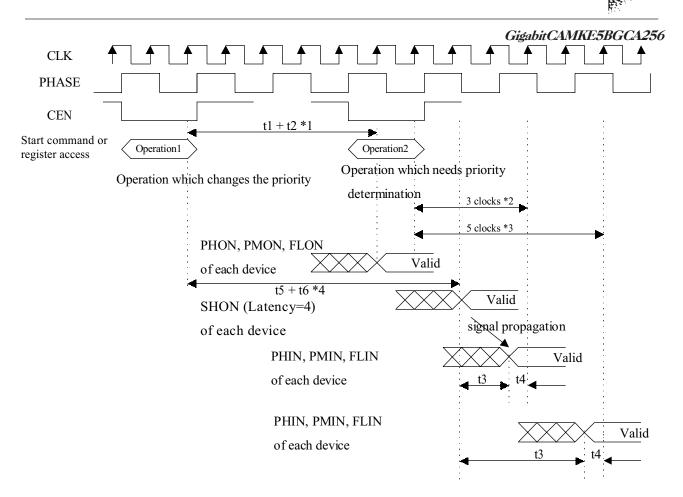

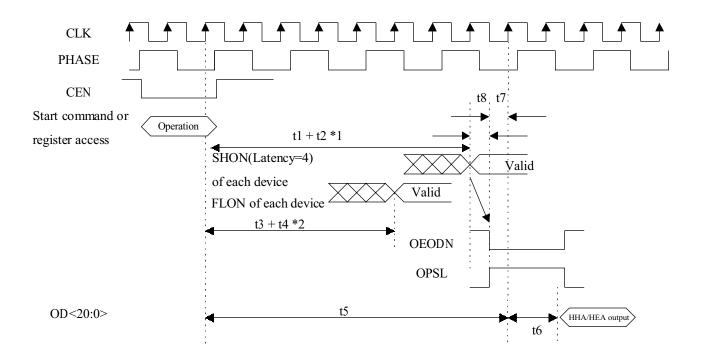

In this method, the external logic is not necessary to control the priority (See Fig. 5.3.3.1). However, additional propagation time is needed according to the number of cascaded devices. This is because the priority signal is cascaded through each of the devices. We define two types of multihit's: When there are multiple hits within a single device, or when there are two devices in a cascaded system that have a single hit. When two devices have a single multi-hit, the data is written in the HHA address of the uppermost single hit priority device in the cascaded system. For devices that have multiple hits within a single device, data will not be written to the HHA address. Data will be written to the HHA address in the next device in the cascade chain that has a single hit priority. (See Fig. 5.3.2.1) The commands STR1\_AUT, STR2\_AUT, STR1\_AUTAI, and STR2 AUTAI cannot be executed in this connection method.

#### AC Characteristics in this method

This device can automatically perform its internal control function by using respective priority signals. After the priority is changed by some action, the next operation which needs priority determination must wait a certain time according to the number of cascaded devices. As shown in Fig. 5.3.3.2, the total time between some action and the next operation which needs priority determination is required for priority determination.

- t1: latency of the action in the top device

- t2: delay time after latency of the action in the top device

t3: propagation delay of priority signal from the top device to the Last Device

t4: setup time for the action which needs priority determination in the Last Device

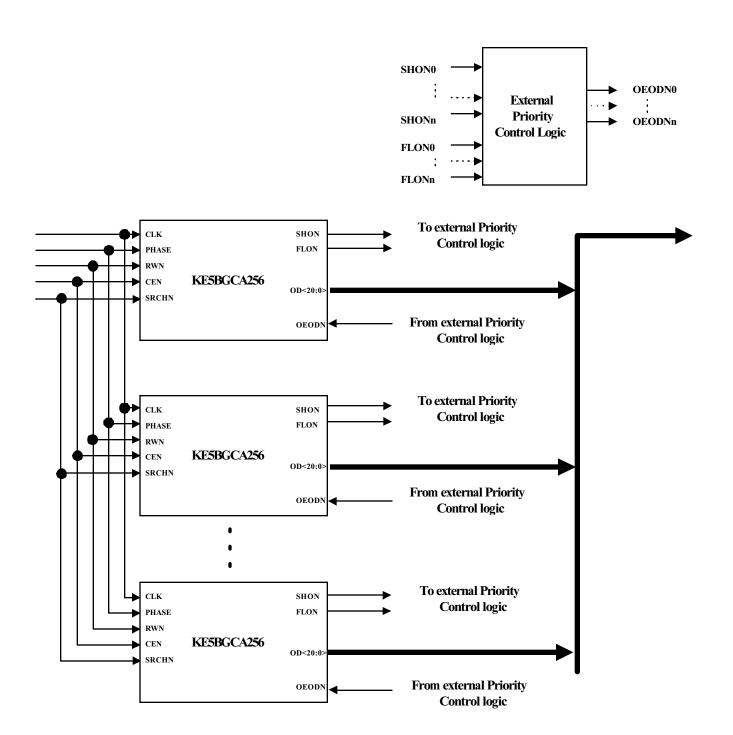

## (2) Connection with the External Logic

In this method, external priority control logic is used to minimize the cascade delay of the system (See Fig. 5.3.3.3). The external control logic must generate the priority signal of each device, PHIN. This is determined from the SHON pin, which is output by each device in hit priority control. In the case of writing to the MEM\_HHA register or writing by the STR1\_HHA or the STR2\_HHA command, the PHIN signal is made with consideration of the writing timing in the device as shown in Fig. 5.3.3.4. When the STR1\_AUT or the STR2\_AUT command is used in a cascaded system, the PHIN of each device must be controlled with consideration of the action timing in each device as shown in Fig. 5.3.3.4.

#### AC Characteristics in this method

This device can automatically perform its internal control function by using respective priority signals. After the priority is changed by some action, the next operation which needs priority determination must wait a certain time according to the number of cascaded devices. As shown in Fig. 5.3.3.4, the total time between some action and the next operation which needs priority determination is required for priority determination.

- t1: latency of the action in each device

- t2: delay time after latency of the action in each device

- t3: propagation delay of priority signal from the external priority control circuit to each device

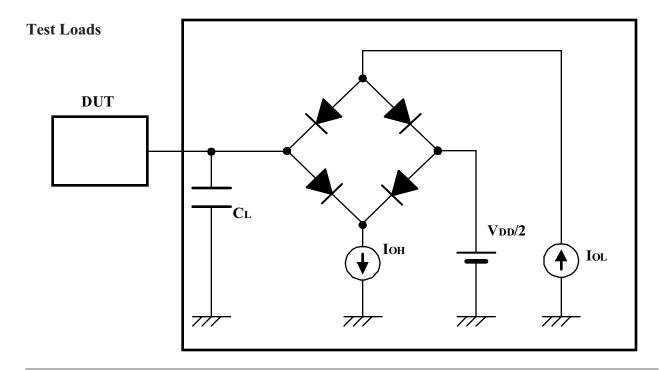

- t4: setup time for the action which needs priority determination in each device