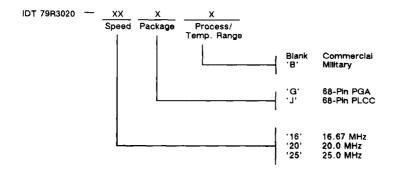

#### RISC CPU WRITE BUFFER

#### PRELIMINARY IDT 79R3020

#### **FEATURES**

- Temporary storage buffers to enhance the performance of the IDT79R3000 RISC CPU processor

- Allows for write operations by the RISC CPU processor during Run cycles

- Each Write Buffer has four locations to handle an 8-bit address slice and a 9-bit data slice (including a parity bit)

- High-speed CEMOS<sup>™</sup> technology

- Pin, functionally and software compatible with the MIPS Computer Systems R2020 Write Buffer

- Military product compliant to MIL-STD-883, Class B

#### DESCRIPTION

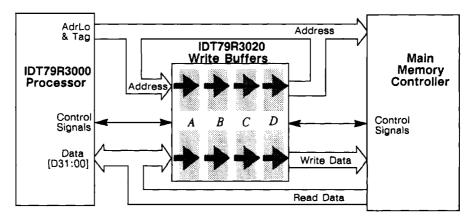

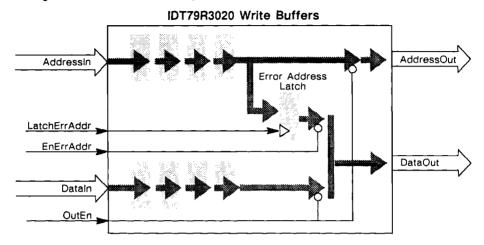

The IDT79R3020 Write Buffer enhances the performance of IDT79R3000 systems by allowing the processor to perform write operations during Run cycles instead of resorting to time-consuming stall cycles. Each IDT79R3020 device handles an 8-bit slice of address, and a 9-bit slice of data (one parity bit per byte); thus, four IDT79R3020s provide 4-deep buffering of 32 bits of address and 36 bits of data and parity. Figure 1 illustrates the functional position of the Write Buffer in an IDT79R3000 system.

Whenever the processor performs a write operation, the Write Buffer captures the output data and its address (including the access type bits). The Write Buffer can hold up to four data-address sets while it waits to pass the data on to main memory. Transfers from the processor to the write buffers occur synchronously at the cycle rate of the processor and the write buffer signals the processor if it is unable to accept data. The write buffer also provides a set of handshake signals to communicate with a main memory controller and coordinate the transfer of write data to main memory.

The sections that follow describe these IDT79R3020 Write Buffer Interfaces:

- · the processor-Write Buffer interface

- the Write Buffer-main memory interface

- a miscellaneous, Write Buffer-board control interface.

Figure 1. The IDT79R3020 Write Buffer in an IDT79R3000 System

CEMOS is a trademark of integrated Device Technology, Inc.

## WRITE BUFFER - IDT79R3000 PROCESSOR INTERFACE

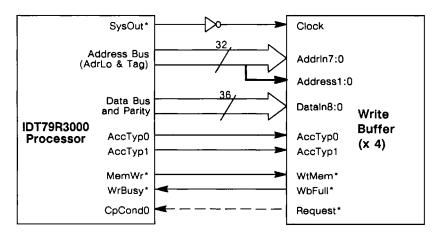

Figure 2 shows the signals comprising the Write Buffer interface to the IDT79R3000 (all descriptions assume that four IDT79R3020 Write Buffers are used to implement a 32-bit, buffered interface). The AdrLo bus and Tag bus bits from the processor are both

connected to the Write Buffer to form a 32-bit physical address that is captured by the buffers. Thirty-two bits of data, four bits of parity, and two access type bits are also captured by the Write Buffer. The paragraphs that follow describe the Write Buffer-processor interface signals and the timing of processor-to-Write Buffer data transfers.

Figure 2. Write Buffer-IDT79R3000 Processor Interface

#### Write Buffer-Processor Interface Signals

#### Clock

An inverted version of the IDT79R3000's SysOut\* signal from the IDT79R3000 processor that synchronizes data transfers. The Write Buffer uses the trailing edge of *Clock* to latch the contents of the AdrLo bus and uses the leading *Clock* edge to latch the contents of the Data and Tag buses.

#### Datain8:0

Nine input data lines from the IDT79R3000 processor's Data bus (eight bits of data and one bit of parity).

#### Addrln7:0

Eight input address lines from the IDT79R3000 processor. The address lines are taken from the AdrLo and Tag buses.

#### Address1:0

The two least significant address bits from the IDT79R3000 processor. These two address bits must be connected to all four Write Buffers and are used in conjunction with the access type (AccTyp1:0) signals, the Position1:0 signals, and the BigEndian signal to determine which byte(s) in a word are being written into a particular Write Buffer.

#### AccTypIn1:0

The access type signals from the IDT79R3000 processor specifying the size of a data access: word, tri-byte, half-word, or byte.

#### WtMem\*

This input is connected to the MemWr\* signal from the IDT79R3000 processor that is asserted whenever the processor is performing a store (write) operation.

#### Request\*

The primary purpose of this signal is to request access to memory and is described later when the Write Buffer-Main Memory Interface is discussed. The Request\* signal can also be connected to the CpCond0 input of the IDT79R3000 and can then

be tested by software to determine if there is any data in the Write Buffer. Since Request\* is deasserted if there is no data in the Write Buffer, software can determine if a previous write operation (for example, to an I/O device) has been completed before initiating a read or read status operation from that device.

#### WbFull\*

The Write Buffer asserts this signal to the IDT79R3000's WrBusy\* input whenever it cannot accept any more data; that is, when the current write will fill the buffer or the buffer has all address-data pairs occupied. The IDT79R3000 processor performs a write-busy stall if it needs to store data while the WbFull\*/WrBusy\* signal is asserted.

#### **Data & Address Connections**

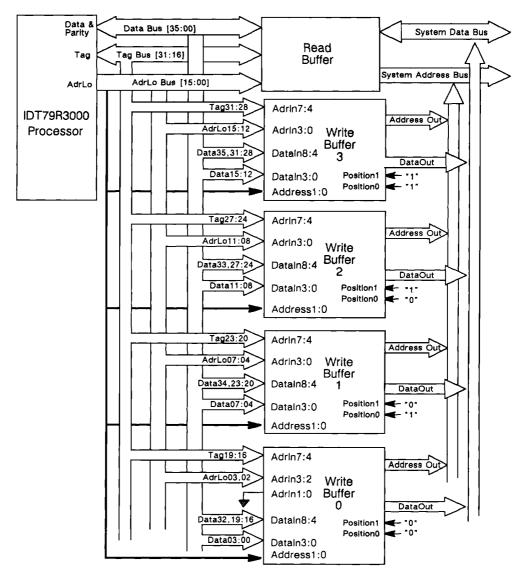

Figure 3 illustrates how four Write Buffers are connected to the address and data outputs of the IDT79R3000 processor.

#### **Address Inputs**

Each Write Buffer device has eight address inputs (AdrIn7:0). The four low-order bits (AdrIn3:0) are clocked into the device on the trailing edge of the Clock signal and are taken from the IDT79R3000's AdrLo bus. The four high-order bits (AdrIn7:4) are clocked into the device on the rising edge of the Clock signal and are taken from the IDT79R3000's Tag bus.

Each device also has separate inputs (Address1, Address0) for the two low-order bits from the AdrLo bus. These bits must be input to each device since they comprise the byte pointer. Note in Figure 3 that the two low-order Adrln inputs (AdrIn1:0) to Write Buffer device 0 are connected to ground since the Address1, Address0 inputs already supply these bits to the device.

#### Data Inputs

Each Write Buffer device has nine data inputs that are clocked into the device on the leading edge of the Clock signal and are taken from the IDT79R3000's Data bus. In Figure 3, each device captures eight bits of data and one bit of parity. Also note that the data bits assigned to each device correspond to the address bits

9

connected to the device. This arrangement is required since data selection is dependent on a combination of the AccType signals and the two low order address bits. The arrangement also

simplifies system utilization of the "Read Error Address" feature described later.

Figure 3. Write Buffer Data and Address Line Connections

The Position1 and Position0 signals shown in Figure 3 specify the nibble position within a halfword that each write buffer device comprises.

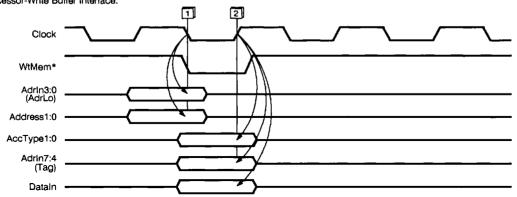

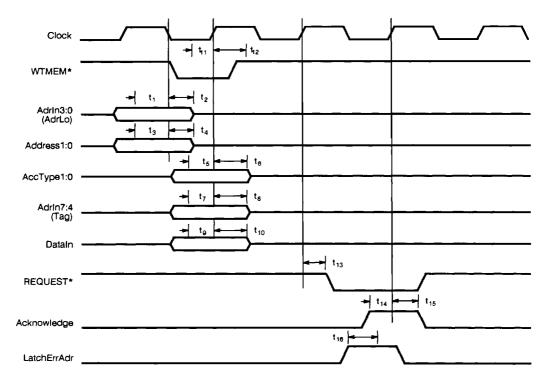

#### Write Buffer - Processor Timing

Transfers between the processor and the Write Buffers occur synchronously: the Clock signal from the processor is input to the Write Buffers and used to clock the address and data information into the Write Buffers' latches. Figure 4 illustrates the timing for the processor-Write Buffer interface.

When the WrtMem\* signal is asserted, the low-order address bits, and the Address 1:0 inputs, are latched on the trailing edge of the Clock signal (1). The rising edge of Clock (2) is used to latch the high-order address bits, the access type inputs and the contents of the data bus.

Figure 4. Processor - Write Buffer Interface Timing

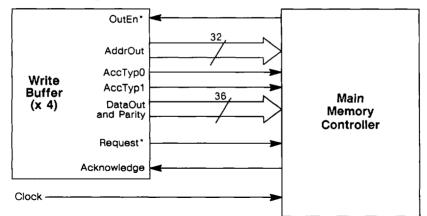

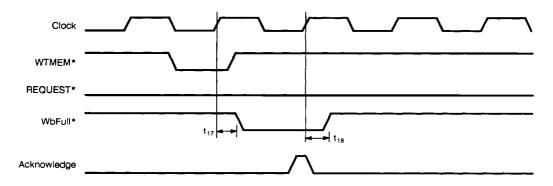

#### WRITE BUFFER - MAIN MEMORY INTERFACE

Figure 5 shows the signals comprising the Write Buffer interface to main memory. This interface is essentially decoupled from the Write Buffer-processor interface: although some synchronization

of the memory interface signals and the Clock signal is required, the handshaking signals in this interface have no direct connection to the operation of the Write Buffer-processor interface.

Figure 5. Write Buffer-Main Memory Interface

#### Write Buffer - Main Memory Interface Signals

Each Write Buffer provides the following signals that comprise the interface to a main memory controller:

#### AddrOut 7:0

Eight address line output from each Write Buffer.

#### DataOut 8:0

Nine data lines from each Write Buffer (eight bits of data and one bit of parity).

#### AccTvp 1:0

The access type signals from the Write Buffer specifying the size of a data access: word, tri-byte, half-word, or byte.

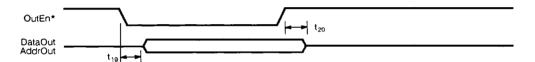

#### OutEn\*

The memory controller asserts this write input to enable the tri-state outputs of the IDT79R3020 address and data signals.

#### Request\*

The Write Buffer asserts this signal to inform the main memory system that it has data to be written to memory.

#### Acknowledge

The main memory system asserts this signal when it has captured the data presented by the Write Buffer on the DataOut lines.

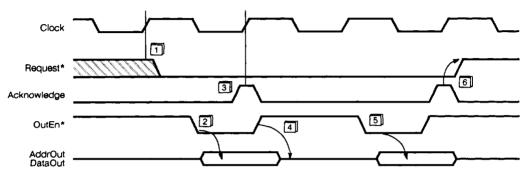

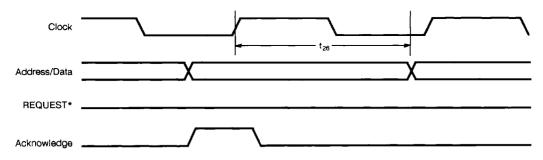

#### Write Buffer - Main Memory Interface Timing

Figure 6 illustrates the timing for the transfer of data from the Write Buffer to the main memory system. The sequence illustrated in this figure is as follows:

- When the Write Buffer has a data-address pair for transfer to the memory system, it asserts the Request\* signal.

- When memory system is ready to handle the Write Buffer data, it asserts the OutEn\* signal to enable the Write Buffers' address and data outputs onto the system buses.

- When memory system no longer requires the Write Buffer address and data outputs, it asserts the Acknowledge signal.

- The Write Buffer responds to this signal by discarding the address-data pair that was just output.

- The memory system can deassert the OutEn\* signal to return the Write Buffers' address and data outputs to their tristate condition.

- Since the Request\* signal remains asserted, the memory system asserts the OutEn\* signal again to enable the next address-data pair onto the system buses.

- When memory system has accepted the second address-data pair, it again asserts the Acknowledge signal. If the Write Buffer is now empty, it responds to this signal by deasserting the Request\* signal.

Figure 6. Write Buffer - Main Memory Interface Timing

Note that the buffer's interface to main memory is not completely asynchronous: assertion of the Request\* signal by the Write Buffer is synchronized with the rising edge of Clock, and the Acknowledge signal input by main memory has a minimum set up and hold time in relation to the Clock signal.

## MISCELLANEOUS WRITE BUFFER - BOARD LOGIC INTERFACE

The Write Buffers support several functions that utilize signals that do not fit neatly into the descriptions of either the processor or main memory interfaces. These functions and signals typically involve miscellaneous logic on a CPU board and include the following:

- byte gathering

- configuration connections (Big Endian, Position 1:0)

- address matching logic

- error address latch logic

The sections that follow describe each of these categories.

#### Byte Gathering

The Write Buffers perform byte (half-word, tri-byte and word) gathering to decrease the number of write transfers to same location; that is, sequential writes to the same WORD address have their data combined into the same address-data pair buffer.

Byte gathering is prohibited in the address-data pair that is currently available to the memory controller. Thus, the first write into an empty Write Buffer will not have subsequent writes gathered into it because it is currently available for output to memory. Writes to the same location (byte) may be overwritten in the Write Buffer if the gathering is not prohibited by the preceding rule.

The Write Buffers present address-data pairs to the main memory controller in the sequence in which they were received from the processor except in the case of gathered data, where bytes or half words can be collected and written to main memory in a single write operation. If the address-data pair buffer is scheduled to be

output, then gathering is inhibited and the buffer contents are presented to the main memory controller. Subsequent writes are then placed in another buffer. No reliance should be placed in any aspect of gathering (except that it only involves sequential writes to the same word address) as it is not readily deterministic. Non-sequential writes to the same word address are not gathered.

Note that gathering can require that two main memory controller references be used to empty a single Write Buffer entry. For example, this can occur if Bytes 0 and 3 of a word are sequentially written. Where order in writing is important, such as in I/O controllers, software should avoid sequential accesses to the same word. In cases where write-read access ordering is important but reading of the write location is not desired, such as during I/O, then a write followed by a write to a dummy location followed by a read of the dummy location will insure the first write has occurred before continuing. Alternatively, the REQUEST signal can be tested to determine that the Write Buffer is empty.

#### **Configuration Logic Connections**

Because of their byte gathering capability, each buffer device internally maintains a record of each valid byte in an address/data pair. To do this, each device must have a way of determining which data bits within a word it is handling. The following signals determine how the write buffers handle data that is written to the devices:

- Position 1, Position 0 these signals (in conjunction with Big Endian\*) determine how each Write Buffer decodes the Address 1/0 and AccType 1/0 to determine if it should store the data inputs. Refer to Figure 3 for an illustration of how data bits are assigned to Write Buffer devices based on their position.

- Big Endian\* When asserted, byte 0 is the leftmost, most significant byte (big-endian): when deasserted, byte 0 is the rightmost, least-significant byte (little-endian).

- Address 1, Address 0 these signals (taken from the AdrLo bus) must be connected to all buffer devices since they determine which byte within a word is being accessed.

AccType 1, AccType 0 - these inputs signals specify the data size of a write operation as shown in Table 1. Table 1 shows how these signals operate to specify how bytes are saved within the Write Buffers.

| Access        | Δdd | dress | Bytes Accessed |       |       |   |    |         |        |   |

|---------------|-----|-------|----------------|-------|-------|---|----|---------|--------|---|

| Type<br>1 0   | 1   | 0     | 31             | Big-E | ndian | o | 31 | Little- | Endian | o |

| 1 1<br>(word) | 0   | 0     | 0              | 1     | 2     | 3 | 3  | 2       | 1      | 0 |

| 1 0           | 0   | 0     | 0              | 1     | 2     |   |    | 2       | 1      | 0 |

| (triple-byte) | 0   | 1     |                | 1     | 2     | 3 | 3_ | 2       | 1_1_   |   |

| 0 1           | 0   | 0     |                | 1_1_  |       |   |    | 1       | 1      | 0 |

| (halfword)    | 1   | 0     |                |       | 2     | 3 | 3  | 2       |        |   |

| 0 0           | 0   | 0     | 0              |       |       |   |    |         |        | 0 |

| (byte)        | 0   | 1     |                | 1     |       |   |    |         | 1      |   |

|               | 1   | 0     |                |       | 2     |   |    | 2       |        |   |

| Į.            | 1   | 1     |                |       | I     | 3 | 3  | I       |        | ] |

Table 1. Byte Specifications for Write Operations

The lower two address bits of the device in position zero (as determined by the two POSITION inputs) are inhibited; that is, they are not stored directly as they are output on the AdrLo bus. Instead, on output, the lower two address bits are generated from the indication of the positions of the valid data bytes as determined by above table.

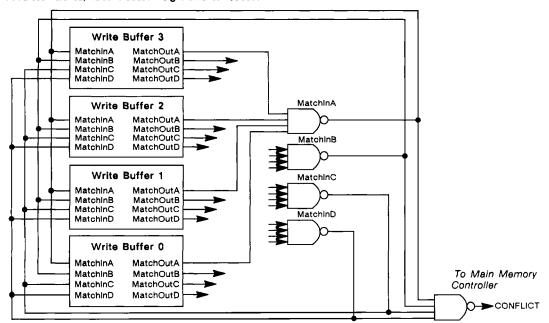

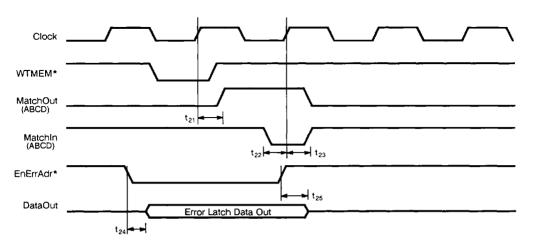

#### MatchOut/Matchin Logic and Read Conflicts

Whenever the processor references main memory (either a write or a read reference), the Write Buffers compare the word address from the CPU with the word addresses stored in the buffers. If any word address matches, the buffers asserts signals that can be used

by the main memory controller to ensure that the Write Buffer is emptied before the read access with the conflicting address has been performed.

Figure 7 illustrates the Write Buffer signals involved in address comparison logic. Each write buffer provides four output signals (MatchOut A, B, C, and D) which correspond to the four buffer ranks (A, B, C, D) in each device as shown in Figure 1. These MatchOut signals can be externally NAND'ed as shown in Figure 7 to determine if the address being input matches those in any rank of the Write Buffer.

Figure 7. Write Buffer MatchOut/Matchin Logic

The outputs of the NAND gates are fed into Write Buffers via the MatchIn A, B, C, and D signals and are used within each device as part of the byte gathering logic. The NAND gate outputs can be NAND'ed together as shown in Figure 7 with the resultant signal used (in conjunction with the processor's MEMRD signal) to alert the main memory controller logic that there is a pending buffered write that conflicts with a just-issued read. The main memory controller can then delay the read access until the Request signal is deasserted indicating that the Write Buffer has been emptied.

#### **Error Address Latch**

The write buffer incorporates an internal latch that can be loaded with one of the buffered addresses and subsequently enabled out onto the data lines. This feature can be used by error handling routines to read an address back from the Write Buffer and analyze or recover from certain bus errors. Figure 8 shows the signals involved in operation of this latch.

Figure 8. The Write Buffer Error Address Latch

When the LatchErrAddr signal is asserted, the address currently available to the address outputs of the Write Buffer is latched into the internal latch. This address can then be output on the DataOut lines by asserting the EnErrAdr signal so that the processor can

read the address in as data. Refer to the AC specifications for timing parameters of the signals associated with the error address latch.

#### ABSOLUTE MAXIMUM BATINGS (1.3)

| SYMBOL            | RATING                                     | COMMERCIAL   | MILITARY     | UNIT |  |  |  |  |  |  |

|-------------------|--------------------------------------------|--------------|--------------|------|--|--|--|--|--|--|

| V <sub>TERM</sub> | Terminal Voltage<br>with Respect to<br>GND | -0.5 to +7.0 | -0.5 to +7.0 | ٧    |  |  |  |  |  |  |

| TA                | Operating<br>Temperature                   | 0 to +70     | -55 to +125  | °C   |  |  |  |  |  |  |

| TBIAS             | Temperature<br>Under Bias                  | -55 to + 125 | -65 to + 135 | °C   |  |  |  |  |  |  |

| T <sub>STG</sub>  | Storage<br>Temperature                     | -55 to +125  | -65 to + 150 | ့င   |  |  |  |  |  |  |

| V <sub>IN</sub>   | Input Voltage (2)                          | -0.5 to +7.0 | -0.5 to +7.0 | ٧    |  |  |  |  |  |  |

#### NOTES:

- 1. Stresses greater than those listed under ABSOLUTE MAXIMUM RAT-INGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2.  $V_{\rm IN}$  minimum = 3.0V for pulse width less than 15ns.  $V_{\rm IN}$  maximum should not exceed  $V_{\rm CC}$  + 0.5 volts.

- Not more than one output should be shorted at a time. Duration to the short should no exceed 30 seconds.

#### **RECOMMENDED OPERATING TEMPERATURE AND SUPPLY VOLTAGE**

| GRADE      | AMBIENT<br>TEMPERATURE | GND | V <sub>CC</sub> |  |

|------------|------------------------|-----|-----------------|--|

| Military   | -55°C to +125°C        | ٥٧  | 5.0V ± 10%      |  |

| Commercial | 0°C to +70°C           | 0V  | 5.0V ± 5%       |  |

### DC ELECTRICAL CHARACTERISTICS -

| SYMBOL           | PARAMETER                | TEST CONDITIONS                                |     | 16.67 MHz<br>MIN. MAX. |     | 20.0 MHz<br>MIN. MAX. |     | 25.0 MHz<br>MIN. MAX. |    |

|------------------|--------------------------|------------------------------------------------|-----|------------------------|-----|-----------------------|-----|-----------------------|----|

| V <sub>OH</sub>  | Output HIGH Voltage      | V <sub>CC</sub> = Min, I <sub>OH</sub> = -4mA  | 3.5 | -                      | 3,5 | -                     | 3.5 |                       | v  |

| Vol              | Output LOW Voltage       | V <sub>CC</sub> = Min, I <sub>OL</sub> = 4mA   | _   | 0.4                    | -   | 0.4                   | -   | 0.4                   | ν  |

| V <sub>IH</sub>  | Input HIGH Voltage(1)    |                                                | 2.4 | _                      | 2.4 | _                     | 2.4 |                       | ٧  |

| V <sub>IL</sub>  | Input LOW Voltage(2)     |                                                | _   | 0.8                    |     | 0.8                   | -   | 0.8                   | v  |

| Cin              | Input Capacitance        |                                                | 10  | _                      | 10  | _                     | 10  | _                     | pF |

| C <sub>OUT</sub> | Output Capacitance       |                                                | 10  | _                      | 10  | _                     | 10  |                       | рF |

| Icc              | Operating Current        | V <sub>CC</sub> = Max                          | -   | 50                     | _   | 60                    |     | 70                    | mA |

| lн               | Input HIGH Leakage       | V <sub>IH</sub> = V <sub>CC</sub>              | T - | 10                     | ~   | 10                    |     | 10                    | μА |

| l <sub>iL</sub>  | Input LOW Leakage        | V <sub>iL</sub> ≈ Gnd                          | -10 |                        | -10 | _                     | -10 | _                     | μA |

| loz              | Output Tri-state Leakage | V <sub>OH</sub> = 2.4V, V <sub>OL</sub> = 0.5V | -40 | 40                     | -40 | 40                    | -40 | 40                    | μА |

#### DC ELECTRICAL CHARACTERISTICS -

MILITARY TEMPERATURE RANGE (TA = -55°C to 125°C, Vcc = +5.0 V ± 10%

| SYMBOL          | PARAMETER                | TEST CONDITIONS                               | 16.67 |      |      |

|-----------------|--------------------------|-----------------------------------------------|-------|------|------|

| STMBUL          | PARAMEIER                | TEST CONDITIONS                               | MIN.  | MAX. | UNIT |

| V <sub>OH</sub> | Output HIGH Voltage      | V <sub>CC</sub> = Min, I <sub>OH</sub> = -4mA | 3.5   | -    | ٧    |

| V <sub>OL</sub> | Output LOW Voltage       | V <sub>CC</sub> = Min, I <sub>OL</sub> = 4mA  |       | 0.4  | . v  |

| V <sub>IH</sub> | Input HIGH Voltage(1)    |                                               | 2.4   |      | V    |

| V <sub>IL</sub> | Input LOW Voltage(2)     |                                               | _     | 0.8  | V    |

| Cin             | Input Capacitance        |                                               | 10    |      | pF   |

| Cour            | Output Capacitance       |                                               | 10    | -    | pF   |

| lcc             | Operating Current        | V <sub>CC</sub> = Max                         |       | 90   | mA   |

| l <sub>tH</sub> | Input HIGH Leakage       | V <sub>IH</sub> = V <sub>CC</sub>             |       | 10   | μА   |

| l <sub>IL</sub> | Input LOW Leakage        | V <sub>IL</sub> = Gnd                         | -10   | _    | μA   |

| loz             | Output Tri-state Leakage | $V_{OH} = 2.4V, V_{OL} = 0.5V$                | -40   | 40   | Αu   |

#### NOTES:

- 1. V<sub>IH</sub> should be held above V<sub>CC</sub> + 0.5 Volts.

- 2. V<sub>IL</sub> Min. = -3.0V for pulse width less than 15ns. V<sub>IL</sub> should not fall below -0.5 Volts for longer periods.

#### AC ELECTRICAL CHARACTERISTICS (TA = 0°C to 70°C, V<sub>CC</sub> = +5.0 V ± 5%

| SYMBOL | PARAMETER                                       |           | 16.67 MHz |           | MHz  | 25.0 | TINU |     |

|--------|-------------------------------------------------|-----------|-----------|-----------|------|------|------|-----|

|        |                                                 | MIN.<br>8 | MAX.      | MIN.<br>7 | MAX. | MIN. | MAX. |     |

| t1     | Addrin (3:0) to Clock falling setup             | 4         |           | 4         |      | 4    |      | ns  |

| t2     | Addrin (3:0) from Clock falling hold            |           |           | ļ         |      |      |      | ns  |

| t3     | Address 1:0 to Clock falling setup              | 8         |           | 7         |      | 6    |      | ns  |

| 14     | Address 1:0 from Clock falling hold             | 4         |           | 4         |      | 4    |      | ns  |

| t5     | Access Type 1:0 to Clock rising setup           | 7         | -         | 6         |      | 5    | -    | ns  |

| t6     | Access Type 1:0 from Clock rising hold          | 3         |           | 3         |      | 2    | _    | ns  |

| t7     | Addrin (7:4) to Clock rising setup              | 7         |           | 5         |      | 5    |      | ns  |

| t8     | Addrin (7:4) from Clock rising hold             | 3         |           | 3         |      | 2    |      | ns  |

| t9     | Datain (8:0) to Clock rising setup              | 7         |           | 5         |      | 5    |      | ns  |

| t10    | Datain (8:0) from Clock rising hold             | 3         | _         | 3         |      | 2    | -    | ns  |

| t11    | WrtMem* to Clock rising setup                   | 10        |           | 8         | _    | 7    | -    | ns  |

| 112    | WrtMem* from Clock rising hold                  | 6         |           | 5         |      | 4    | -    | ns  |

| t13    | Request from Clock rising                       |           | 32        | -         | 30   | _    | 27   | ns  |

| t14    | Acknowledge to Clock rising setup               | 12        |           | 11        |      | 10   | -    | ns  |

| t15    | Acknowledge from Clock rising hold              | 7         | -         | 6         | _    | 5    | -    | ns  |

| t16    | LatchErrAdr to Acknowledge rising               | 5         |           | 5         | _    | 5    | -    | ns  |

| 117    | WbFull* active from Clock rising                | -         | 32        | _         | 30   |      | 27   | ns  |

| 118    | WbFull* inactive from Clock rising              |           | 32        | _         | 30   |      | 27   | ns  |

| t19    | OutEn to AddrOut (7:0), DataOut (8:0) valid     | 2         | 15        | 2         | 15   | 2    | 15   | ns  |

| t20    | OutEn to AddrOut (7:0), DataOut (8:0) tri-state | 2         | 15        | 2         | 15   | 2    | 15   | ns  |

| t21    | MatchOut (ABCD) from Clock rising               | -         | 25        | _         | 24   |      | 23   | ns  |

| 122    | Matchin (ABCD) to Clock rising setup            | 10        |           | 9         |      | 8    |      | ns  |

| t23    | Matchin (ABCD) from Clock rising hold           | 3         |           | 3         |      | 3    |      | ns  |

| t24    | EnErrAdr* to Data (error latch) valid           | 2         | 15        | 2         | 15   | 2    | 15   | ns  |

| 125    | EnErrAdr* to Data (error latch) tri-state       | 2         | 15        | 2         | 15   | 2    | 15   | ns  |

| 126    | Address/Data out from Clock rising              | _         | 32        |           | 30   | _    | 27   | ns  |

| 127    | Reset* to Clock rising, set-up                  | 8         |           | 7         |      | 5    |      | ns  |

| t28    | Reset* from Clock rising, hold                  | 3         |           | 2         |      | 1    |      | ns  |

| 129    | Reset low pulse width                           | 10        |           | 10        |      | 10   | _    | ns  |

| 130    | WbFull* High from Clock rising (after Reset*)   | 3         | 22        | 3         | 21   | 3    | 20   | ns  |

| t31    | Request* High from Reset* low                   | 3         | 20        | 3         | 19   | 3    | 18   | ns  |

| t32    | Access Type 1:0 low from Reset* low             | 3         | 28        | 3         | 26   | 3    | 25   | ns  |

|        |                                                 |           |           |           |      | L    | ~~   | 113 |

9

#### AC ELECTRICAL CHARACTERISTICS - MILITARY TEMPERATURE RANGE (TA = -55°C to 125°C, V<sub>CC</sub> = +5.0V ± 10%

| SYMBOL | DADAMETER                                       | 16.67 | 16.67 MHz |      |  |  |

|--------|-------------------------------------------------|-------|-----------|------|--|--|

| SYMBOL | PARAMETER                                       | MIN.  | MAX.      | UNIT |  |  |

| t1     | Addrin (3:0) to Clock falling setup             | 8     |           | ns   |  |  |

| 12     | Addrin (3:0) from Clock falling hold            | 4     |           | ns   |  |  |

| t3     | Address 1:0 to Clock falling setup              | 8     |           | ns   |  |  |

| t4     | Address 1:0 from Clock falling hold             | 4     |           | ns   |  |  |

| t5     | Access Type 1:0 to Clock rising setup           | 7     | _         | ns   |  |  |

| t6     | Access Type 1:0 from Clock rising hold          | 3     |           | ns   |  |  |

| t7     | Addrin (7:4) to Clock rising setup              | 7     |           | ns   |  |  |

| t8     | Addrin (7:4) from Clock rising hold             | 3     |           | ns   |  |  |

| t9     | Datain (8:0) to Clock rising setup              | 7     | -         | ns   |  |  |

| 110    | Datain (8:0) from Clock rising hold             | 3     | _         | ns   |  |  |

| t11    | WrtMem* to Clock rising setup                   | 10    | _         | ns   |  |  |

| t12    | WrtMem* from Clock rising hold                  | 6     |           | ns   |  |  |

| t13    | Request from Clock rising                       |       | 32        | ns   |  |  |

| 114    | Acknowledge to Clock rising setup               | 12    |           | ns   |  |  |

| t15    | Acknowledge to Clock rising hold                | 7     | _         | ns   |  |  |

| t16    | LatchErrAdr to Acknowledge rising               | 5     | _         | ns   |  |  |

| t17    | WbFull* active from Clock rising                |       | 32        | ns   |  |  |

| t18    | WbFull* inactive from Clock rising              | _     | 32        | ns   |  |  |

| t19    | OutEn to AddrOut (7:0), DataOut (8:0) valid     | 2     | 15        | ns   |  |  |

| 120    | OutEn to AddrOut (7:0), DataOut (8:0) tri-state | 2     | 15        | ns   |  |  |

| t21    | MatchOut (ABCD) from Clock rising               | _     | 25        | ns   |  |  |

| 122    | Matchin (ABCD) to Clock rising setup            | 10    |           | ns   |  |  |

| t23    | Matchin (ABCD) from Clock rising hold           | 3     | _         | ns   |  |  |

| t24    | EnErrAdr* to Data (error latch) valid           | 2     | 15        | ns   |  |  |

| t25    | EnErrAdr* to Data (error latch) tri-state       | 2     | 15        | ns   |  |  |

| t26    | Address/Data out from Clock rising              | _     | 32        | ns   |  |  |

| 127    | Reset* to Clock rising, set-up                  | 8     | _         | ns   |  |  |

| 128    | Reset* from Clock rising, hold                  | 3     | _         | ns   |  |  |

| 129    | Reset low pulse width                           | 10    |           | ns   |  |  |

| t30    | WbFull* High from Clock rising, (after Reset*)  | 3     | 22        | ns   |  |  |

| t31    | Request* High from Reset* low                   | 3     | 20        | ns   |  |  |

| 132    | Access Type 1:0 Low from Reset* low             | 3     | 28        | ns   |  |  |

| t33    | Match Out (ABCD) Low from Reset* low            | 3     | 21        | ns   |  |  |

Figure 9. Write Buffer Timing Specifications

Figure 10. WBFULL\* Signal Timing Specifications

Figure 11. OUTEN\* Timing Specifications

Figure 12. Match and Error Latch Timing Specifications

Figure 13. Address/Data Out

#### 68-Pin CPGA for R3020 Pin Grid Array (Ceramic) – Bottom View

|   |                      |                      |                       |               |                | ,                    |                |              |                |               |                       |

|---|----------------------|----------------------|-----------------------|---------------|----------------|----------------------|----------------|--------------|----------------|---------------|-----------------------|

| L |                      | ACC-<br>TYPE0        | AC-<br>KNOWL-<br>EDGE | AD-<br>DRESS1 | CLOCK          | DATA-<br>INO         | DATA-<br>IN2   | DATA-<br>IN4 | DATA-<br>IN6   | VCC2          |                       |

| κ | GND1                 | VCC1                 | ACC-<br>TYPE1         | AD-<br>DRESSO | BIGEN-<br>DIAN | EN-<br>ERROR-<br>ADR | DATA-<br>IN1   | DATA-<br>IN3 | DATA-<br>IN5   | GND2          | DATA-<br>IN7          |

| J | ADDR-<br>OUT5        | ADDR-<br>OUT4        |                       |               |                |                      |                |              |                | DATA-<br>IN8  | ADDR-<br>INO          |

| н | ADDR-<br>OUT3        | ADDR-<br>OUT2        |                       |               |                |                      |                |              |                | ADDR-<br>IN1  | ADDR-<br>IN2          |

| G | ADDR-<br>OUT1        | ADDR-<br>OUTO        |                       |               |                |                      |                |              |                | ADDR-<br>IN3  | ADDR-<br>IN4          |

| F | DATA-<br>OUT8        | DATA-<br>OUTO        |                       |               |                |                      |                |              |                | ADDR-<br>IN5  | ADDR-<br>IN6          |

| E | DATA-<br>OUT1        | DATA-<br>OUT2        |                       |               |                |                      |                |              |                | ADDR-<br>IN7  | LATCH-<br>ERR-<br>ADR |

| D | DATA-<br>OUT3        | ADDR-<br>OUT6        |                       |               |                |                      |                |              |                | MATCH-<br>INA | MATCH-<br>INB         |

| С | ADDR-<br>OUT7        | ACC-<br>TYPE<br>OUT1 |                       |               |                |                      |                |              |                | MATCH-<br>INC | MATCH-<br>IND         |

| В | ACC-<br>TYPE<br>OUT0 | GND0                 | DATA-<br>OUT7         | DATA-<br>OUT4 | RE-<br>QUEST   | MATCH-<br>OUTC       | MATCH-<br>OUTA | RESET        | PO-<br>SITIONO | VCC3          | GND3                  |

| А |                      | VCC0                 | DATA-<br>OUT5         | DATA-<br>OUT6 | WBFULL         | MATCH-<br>OUTD       | MATCH-<br>OUTB | WTMEM        | PO-<br>SITION1 | OUTEN         |                       |

|   | 1                    | 2                    | 3                     | 4             | 5              | 6                    | 7              | 8            | 9              | 10            | 11                    |

<sup>\* =</sup> TRI-STATE OUTPUT 35 INPUTS, 25 OUTPUTS 4 VCC, 4 VSS

# PIN CONFIGURATION Plastic Leaded Chip Carrier (Top View)

#### **ORDERING INFORMATION**