# **3888 Group**

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

#### DESCRIPTION

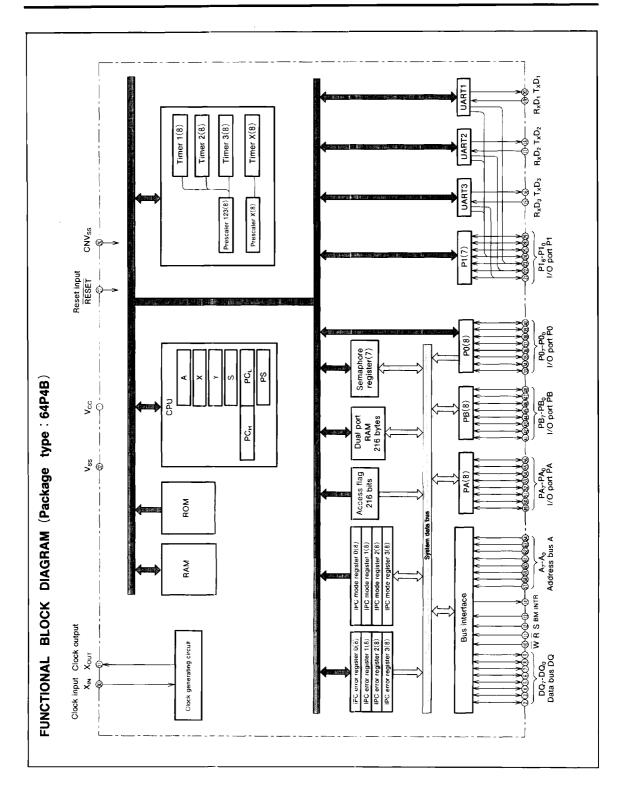

The 3888 group is the 8-bit microcomputer based on the 740 family core technology.

The 3888 group is a protocol controller for data communication between processors in the multi-processor system and includes a 3-channel UART and a dual port RAM

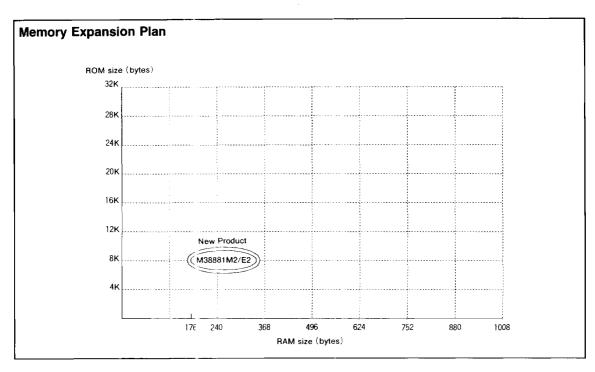

For details on availability of microcomputers in the 3888 group, refer to the section on group expansion.

#### **FEATURES**

| • | Basic machine-language instructions ····· 71                      |

|---|-------------------------------------------------------------------|

| • | The minimum instruction execution time $\cdots 0.32 \mu$ s        |

|   | (at 12.5MHz oscillation frequency)                                |

|   | Memory size                                                       |

|   | ROM ······ 8K bytes                                               |

|   | RAM····· 240 bytes                                                |

|   | Programmable I/O ports                                            |

|   | (System data bus) 16                                              |

|   | (Local data bus) ······ 15                                        |

| • | Interrupts ······ 14 sources, 14 vectors                          |

|   | Timers 8 bit×4                                                    |

| • | UART ······3-channel                                              |

| • | Bus interface                                                     |

|   | (RD/WR separate mode bus or 7700 mode bus)                        |

| • | Dual port RAM······216 bytes                                      |

| • | Communication registers                                           |

| • | Clock generating circuit ······ Internal feedback amplifier       |

|   | (connect to an external ceramic resonator or a quartz-            |

|   | crystal oscillator)                                               |

| • | Power source voltage ·······4.5 to 5.5V                           |

| • | Power dissipation 45mW                                            |

| • | Operating temperature range $-20 \text{ to } +85^{\circ}\text{C}$ |

#### **APPLICATIONS**

Office equipment, etc.

## PIN DESCRIPTION

| Pin                               | Name                                      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Alternate Function           |  |  |  |

|-----------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--|--|--|

| V <sub>CC</sub> , V <sub>SS</sub> | Power source                              | • Apply voltage of 4.5 to 5.5V to V <sub>CC</sub> , and 0V to V <sub>SS</sub> .                                                                                                                                                                                                                                                                                                                                                                                                |                              |  |  |  |

| CNV <sub>ss</sub>                 | CNV <sub>SS</sub>                         | Controls the operation mode of the chip.     This pin must be connected with V <sub>SS</sub> .                                                                                                                                                                                                                                                                                                                                                                                 |                              |  |  |  |

| RESET                             | Reset input                               | · Active "L"-type reset input pin                                                                                                                                                                                                                                                                                                                                                                                                                                              |                              |  |  |  |

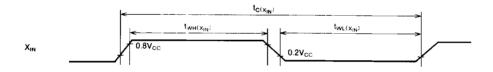

| X <sub>IN</sub>                   | Clock input                               | <ul> <li>Input and output signals for the internal clock generating circuit.</li> <li>Connect a ceramic resonator or a quartz-crystal oscillator between the X<sub>IN</sub> and X<sub>OUT</sub> pins to set the oscillation</li> </ul>                                                                                                                                                                                                                                         |                              |  |  |  |

| X <sub>OUT</sub>                  | Clock output                              | quency.  • When an external r-lock is used, connect the clock source to the X <sub>IN</sub> pin and leave the X <sub>OUT</sub> pin open.                                                                                                                                                                                                                                                                                                                                       |                              |  |  |  |

| P0 <sub>0</sub> -P0 <sub>7</sub>  | I/O port P0                               | 8-bit I/O port connected to the local data bus I/O direction register allows each pin to be individually programmed as either input or output. The local bus port pull-up register allows each pin to be individually programmed to connect to a pull-up transistor or not. This port is also connected to the system data bus. From the system data bus, the contents of each port can be read (it is used as an input port). CMOS compatible input level CMOS 3-state output |                              |  |  |  |

| P1 <sub>0</sub>                   | I/O port P1                               | 7-bit I/O port connected to the local data bus as the                                                                                                                                                                                                                                                                                                                                                                                                                          |                              |  |  |  |

| P1 <sub>1</sub> /INT              |                                           | same function as Pt)  CMOS compatible input level  CMOS 3-state output                                                                                                                                                                                                                                                                                                                                                                                                         | External interrupt input pin |  |  |  |

| P1 <sub>2</sub>                   |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              |  |  |  |

| P1 <sub>3</sub> /CLK              |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | UART1-3 function input pin   |  |  |  |

| P1 <sub>4</sub> /CTS <sub>1</sub> |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | UART1 function input pin     |  |  |  |

| P1 <sub>5</sub> /CTS <sub>2</sub> | ,                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | UART2 function input pin     |  |  |  |

| P1 <sub>6</sub> /CTS <sub>3</sub> |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | UART3 function input pin     |  |  |  |

| PA <sub>0</sub> -PA <sub>7</sub>  | I/O port PA                               | 8-bit I/O ports connected to the system data bus with the same function as P0                                                                                                                                                                                                                                                                                                                                                                                                  |                              |  |  |  |

| PB <sub>0</sub> -PB <sub>7</sub>  | I/O port PB                               | CMOS compatible input level     CMOS 3-state output                                                                                                                                                                                                                                                                                                                                                                                                                            |                              |  |  |  |

| A <sub>0</sub> -A <sub>7</sub>    | Address input                             | Input 8-bit system addresses.     TTL compatible input level.                                                                                                                                                                                                                                                                                                                                                                                                                  |                              |  |  |  |

| DQ <sub>0</sub> -DQ <sub>7</sub>  | Data input/output                         | Input or output 8-bit system data.     TTL compatible input level                                                                                                                                                                                                                                                                                                                                                                                                              |                              |  |  |  |

| s                                 | Chip select input                         | When "L" is input to this pin, read and write of system dat     TTL compatible input level                                                                                                                                                                                                                                                                                                                                                                                     | ta are enabled.              |  |  |  |

| R(E)                              | Read control input<br>(Enable input)      | When "L" is input to this pin, the contents of the memory or register specified by A <sub>0</sub> -A <sub>7</sub> are read from DQ <sub>0</sub> -DQ <sub>7</sub> .  (In the 7700 mode, when "L" is input to this pin, read and write of system data are enabled.)  TTL compatible input level                                                                                                                                                                                  |                              |  |  |  |

| W (R/W)                           | Write control input<br>(Read/write input) | When "L" is input to this pin, data input from DQ <sub>0</sub> -DQ <sub>7</sub> is written into the memory or register specified by A <sub>0</sub> -A <sub>7</sub> .  (In the 7700 mode, when "H" is input to this pin, read of system data is enabled,and when "L" is input to this pin, write of system data is enabled.)  TTL compatible input level                                                                                                                        |                              |  |  |  |

| вм                                | Bus mode control input                    | The input level to this pin controls the functions of R and the CMOS compatible input level.                                                                                                                                                                                                                                                                                                                                                                                   | w                            |  |  |  |

# PIN DESCRIPTION (CONTINUED)

| Pin                                | Name                     | Function                                                                                                                                                        |                    |  |  |

|------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|--|

|                                    |                          |                                                                                                                                                                 | Alternate Function |  |  |

| INTR                               | Interrupt request output | When the contents of IPC error register are modified by the internal CPU, "H" is output.     When the register is read by the external host CPU, "L" is output. |                    |  |  |

| TxD <sub>1</sub> -TxD <sub>3</sub> | UART transmit output     | · Output pin for UART transmit data                                                                                                                             |                    |  |  |

| RxD <sub>1</sub> -RxD <sub>3</sub> | UART receive input       | Input pin for UART receive data CMOS compatible input level                                                                                                     |                    |  |  |

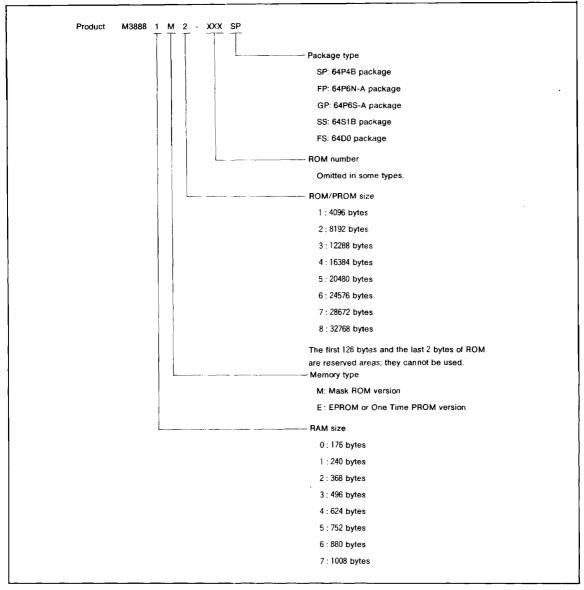

## PART NUMBERING

## **GROUP EXPANSION**

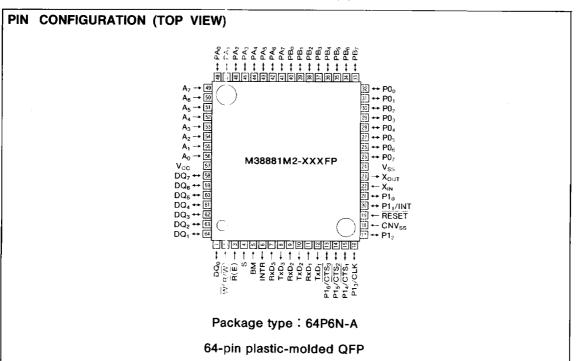

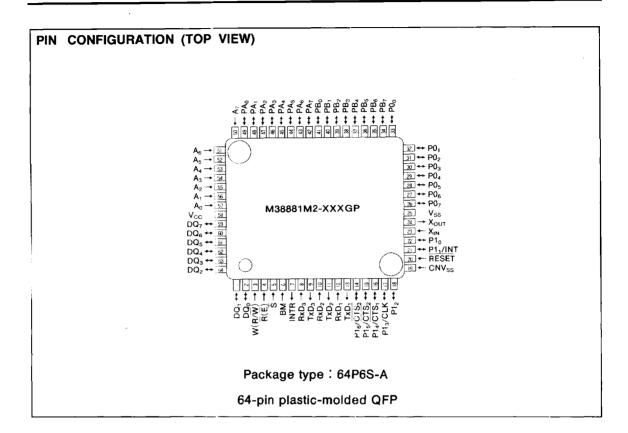

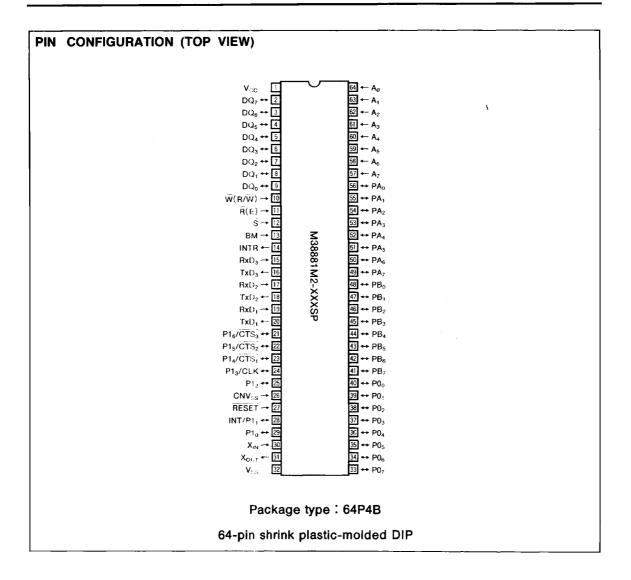

Mitsubishi plans to expand the 3888 group as follows:

- (1) Support for mask ROM, One Time PROM, and EPROM versions

| (2) | Packages                                            |

|-----|-----------------------------------------------------|

|     | 64P4B ····· Shrink plastic molded DIP               |

|     | 64P6N-A ····· 0.8mm-pitch plastic molded QFP        |

|     | 64P6S-A ······ 0.65mm-pitch plastic molded QFP      |

|     | 64S1B ····· Shrink ceramic DIP (EPROM version)      |

|     | 64D0 ······ 0 8mm-nitch ceramic LCC (EPROM version) |

#### Currently supported products are listed below.

#### As of September 1994

| Product        | (P) ROM size (bytes) ROM size for User in ( ) | RAM size (bytes) | Package  | Remarks                       |

|----------------|-----------------------------------------------|------------------|----------|-------------------------------|

| M38881M2-XXXSP |                                               |                  |          | Mask ROM version              |

| M38881E2-XXXSP | 8192                                          | 240              | 64F4B    | One Time PROM version         |

| M38881E2SP     | (8062)                                        | 240              | !        | One Time PROM version (blank) |

| M38881E2SS     |                                               |                  | 64S1B    | EPROM version                 |

| M38881M2-XXXFP | T                                             |                  |          | Mask ROM version              |

| M38881E2-XXXFP | 8192                                          | 240              | 64P6N-A  | One Time PROM version         |

| M38881E2FP     | (8062)                                        |                  |          | One Time PROM version (blank) |

| M38881E2FS     |                                               |                  | 64100    | EPROM version                 |

| M38881M2-XXXGP | 8192                                          |                  |          | Mask ROM version              |

| M38881E2-XXXGP | (8062)                                        | 240              | 64P6S-A  | One Time PROM version         |

| M38881E2GP     |                                               |                  | <u> </u> | One Time PROM version (blank) |

# FUNCTIONAL DESCRIPTION CENTRAL PROCESSING UNIT (CPU)

The 3888 group uses the standard 740 family instruction set. Refer to the table of 740 family addressing modes and machine instructions or the SERIES 740 (Software) User's Manual for details on the instruction set.

Machine-resident 740 family instructions are as follows:

The FST and SLW instruction cannot be used

The STP, WIT, MUL, and DIV instruction can be used.

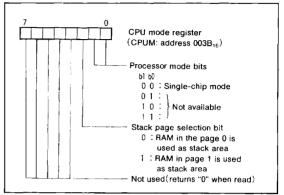

## **CPU Mode Register**

The CPU mode register is allocated at address  $003B_{16}$ . The CPU mode register contains the stack page selection bit and the processor mode bits.

Fig. 1 Structure of CPU mode register

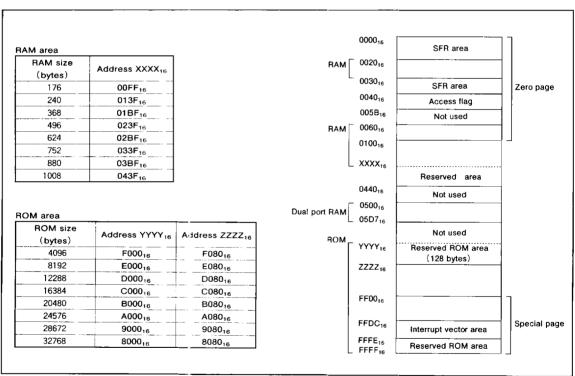

## **MEMORY**

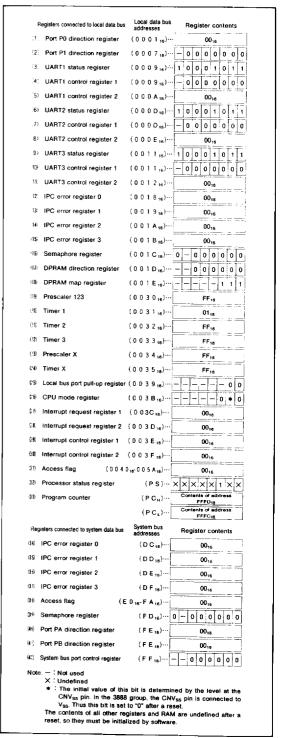

## Special Function Register (SFR) Area

The Special Function Register area in the zero page contains control registers such as I/O ports and timers.

#### RAM

RAM is used for data storage and for stack area of subroutine calls and interrupts.

#### **ROM**

The first 128 bytes and the last 2 bytes of ROM are reserved for device testing and the rest is user area for storing programs.

## **Interrupt Vector Area**

The interrupt vector area contains reset and interrupt vectors.

## Zero Page

The 256 bytes from addresses 0000<sub>16</sub> to 00FF<sub>16</sub> are called the zero page area. The internal RAM and the special function registers (SFR) are allocated to this area.

The zero page addressing mode can be used to specify memory and register addresses in the zero page area. Access to this area with only 2 bytes is possible in the zero page addressing mode.

## Special Page

The 256 bytes from addresses FF00<sub>16</sub> to FFFF<sub>16</sub> are called the special page area. The special page addressing mode can be used to specify memory addresses in the special page area. Access to this area with only 2 bytes is possible in the special page addressing mode.

Fig. 2 Memory map diagram

| 000016             | Port P0 (P0)                                      | 002016             | RAM                                  |

|--------------------|---------------------------------------------------|--------------------|--------------------------------------|

| 000116             | Port P0 direction register (P0D)                  | 002116             | RAM                                  |

| 000216             |                                                   | 002216             | RAM                                  |

| 000316             |                                                   | 002316             | RAM                                  |

| 000416             |                                                   | 002416             | RAM                                  |

| 000516             |                                                   | 002516             | RAM                                  |

| 000616             | Port P1 (P1)                                      | 002616             | RAM                                  |

| 000716             | Port P1 direction register (P1D)                  | 002716             | RAM                                  |

| 000816             | UART1 transmit/receive buffer register(U1TB/U1RB) | 002816             | RAM                                  |

| 00916              | UART1 status/control register 1(U1STS/U1CON1)     | 002916             | RAM                                  |

| 00A <sub>16</sub>  | UART1 control register 2(U1CON2)                  | 002A <sub>16</sub> | RAM                                  |

| 000B <sub>16</sub> | UART1 baud rate generator(U1BRG)                  | 002B <sub>16</sub> | RAM                                  |

| 00C <sub>16</sub>  | UART2 transmit/receive buffer register(U2TB/U2RB) | 002C <sub>16</sub> | RAM                                  |

| 00D <sub>16</sub>  | UART2 status/control register 1(U2STS/U2CON1)     | 002D <sub>16</sub> | RAM                                  |

| 00E <sub>16</sub>  | UART2 control register 2(U2CON2)                  | 002E <sub>16</sub> | RAM                                  |

| 00F <sub>16</sub>  | UART2 baud rate generator(U2BRG)                  | 002F <sub>16</sub> | RAM                                  |

| 01016              | UART3 transmit/receive buffer register(U3TB/U3RB) | 003016             | Prescaler 123(PRE123)                |

| 01116              | UART3 status/control register 1 (U3STS/U3CON1)    | 003116             | Timer 1(T1)                          |

| 01216              | UART3 control register 2(U3CON2)                  | 003216             | Timer 2(T2)                          |

| 01316              | UART3 baud rate genarator(U3BRG)                  | 003316             | Timer 3(T3)                          |

| 01416              | IPC mode register 0(IPCM0)                        | 003416             | Prescaler X(PREX)                    |

| 015 <sub>16</sub>  | IPC mode register 1(IPCM1)                        | 003516             | Timer X(TX)                          |

| 01616              | IPC mode register 2(IPCM2)                        | 003616             |                                      |

| 017 <sub>16</sub>  | IPC mode register 3(IPCM3)                        | 003716             |                                      |

| 018 <sub>16</sub>  | IPC error register 0(IPCER0)                      | 003816             |                                      |

| 01916              | IPC error register 1(IPCER1)                      | 003916             | Local bus port pull-up register(LPU) |

| 01A,6              | IPC error register 2(IPCER2)                      | 003A <sub>16</sub> |                                      |

| 01B <sub>16</sub>  | IPC error register 3(IPCER3)                      | 003B <sub>16</sub> | CPU mode register (CPUM)             |

| 01C <sub>16</sub>  | Semaphore register(SEM)                           | 003C <sub>16</sub> | Interrupt request register 1 (IREQ1) |

| 01D <sub>16</sub>  |                                                   | 903D <sub>16</sub> | Interrupt request register 2 (IREQ2) |

| 01E <sub>16</sub>  | DPRAM map register(DPRM)                          | 003E <sub>16</sub> | Interrupt control register 1 (ICON1) |

| 01F <sub>16</sub>  | Reserved area(Do not access)                      | 003F <sub>16</sub> | Interrupt control register 2 (ICON2) |

Fig. 3 Memory map of special function register (SFR)

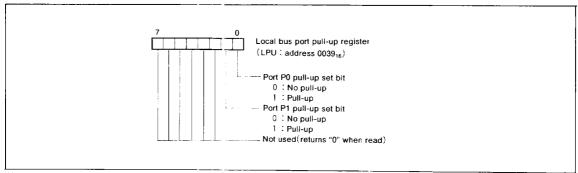

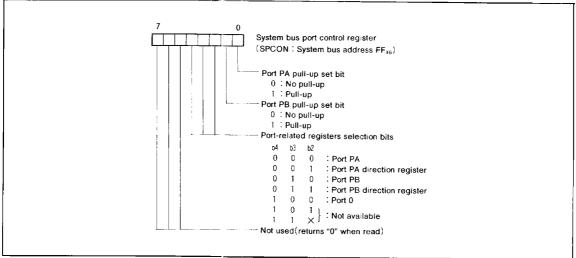

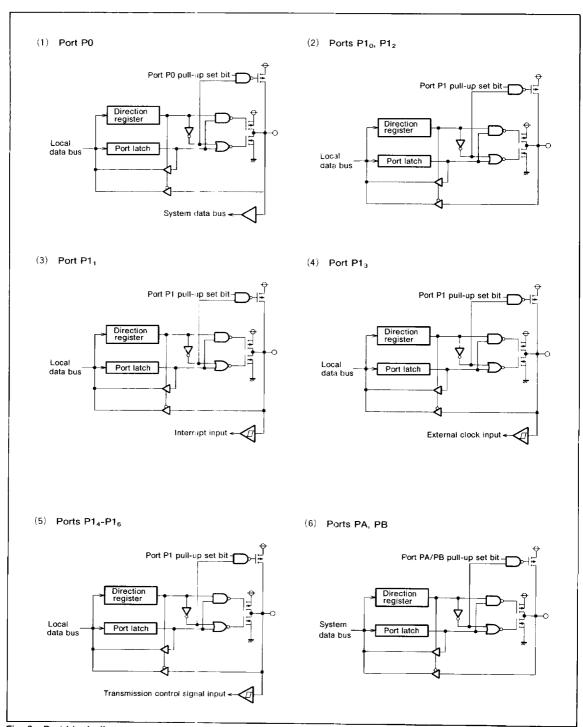

#### I/O PORTS

## Port to be Accessed from System Bus or Local Bus

The port PA and port PB are connected to the system bus. The port P1 is connected to the local bus. The port P0 is connected to the local bus and system bus.

When accessing the port P0 from the system bus, only data reading (a function as an input port) is enabled.

To access a port connected to the system bus, select a port-related register to be accessed by the system bus port control register (system bus address  $FF_{16}$ ), then access the port through the system bus port data register (system bus address  $FE_{16}$ ).

## **Direction Registers**

The 3888 group has 31 programmable I/O pins arranged in 4 I/O ports (ports P0, P1, PA, and PB). The I/O ports have direction registers which determine the input/output direction

of each individual pin. Each bit in a direction register corresponds to one pin, each pin can be set to be input or output. When "0" is written into the bit corresponding to a pin, that pin becomes an input pin. When "1" is written into that bit, that pin becomes an output pin.

If data is read from a pin which is set for output, the value of the port output latch is read, not the value of the pin itself. Pins set to input are floating. If a pin set to input is written to, only the port output latch is written to and the pin remains floating. However, when a pin of port P0 is read from the system bus side, the value of the pin is read regardless of the value of port P0 direction register.

## Pull-up Control

Every port can be connected to a pull-up transistor when the corresponding pull-up set bit is "1".

Every I/O port is set to be an input port at reset, and then is disconnected from a pull-up transistor.

| Pin                               | Name    | input/Output    | I/O Format                          | Non-Port Function        | Related SFRs         | Diagram No. |

|-----------------------------------|---------|-----------------|-------------------------------------|--------------------------|----------------------|-------------|

| P0 <sub>0</sub> -P0 <sub>7</sub>  | Port P0 |                 |                                     |                          |                      | (1)         |

| P1 <sub>0</sub> , P1 <sub>2</sub> |         |                 |                                     | L                        | Local bus port       | (2)         |

| P1 <sub>1</sub> /INT              |         |                 | CMOS competible                     | External interrupt input | pull-up register     | (3)         |

| P1 <sub>3</sub> /CLK              | Port P1 | Input/Output,   | CMOS compatible                     | i                        | UARTi status/control | (4)         |

| P1 <sub>4</sub> /CTS <sub>1</sub> |         | individual bits | input level,<br>CMOS 3-state output | UART function            | register 1           | (5)         |

| P1 <sub>5</sub> /CTS <sub>2</sub> |         |                 | CMOS 3-state output                 | input                    | Local bus port       | (5)         |

| PI <sub>6</sub> /CTS <sub>3</sub> |         | !               |                                     |                          | pull-up register     | (5)         |

| PA <sub>0</sub> -PA <sub>7</sub>  | Port PA |                 | 1                                   |                          |                      | (6)         |

| PB <sub>0</sub> -PB <sub>7</sub>  | Port PB | Ì               |                                     |                          |                      | (6)         |

Note: Make sure that the input level at each pin is either 0V or V<sub>CC</sub> during execution of the STP instruction. When an input level is at the intermediate potential, a current will flow from V<sub>CC</sub> to V<sub>SS</sub> through the input-stage gate.

Fig. 4 Structure of local bus port pull-up register

Fig. 5 Structure of System bus port control register

Fig. 6 Port block diagram

#### **INTERRUPTS**

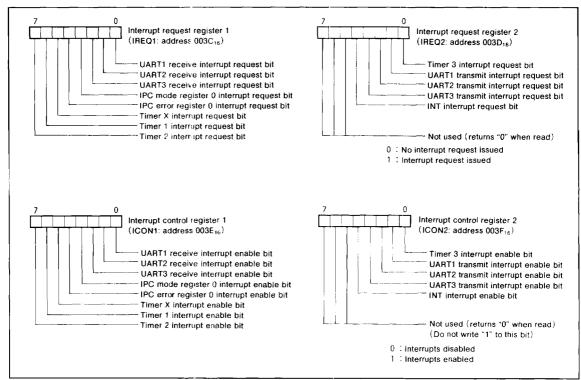

A total of 14 sources can generate interrupts: 2 system bus, 1 external, 10 internal, and 1 software.

## **Interrupt Control**

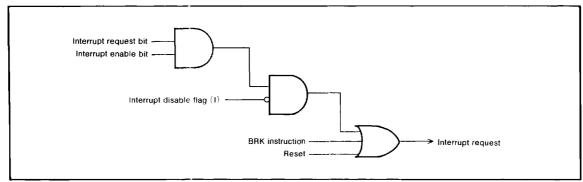

Each interrupt is controlled by an interrupt request bit, an interrupt enable bit, and the interrupt disable flag-except for the software interrupt set by the BRK instruction. An interrupt occurs when the corresponding interrupt request and enable bits are "1" and the interrupt disable flag is "0". Interrupt enable bits can be set or cleared by software. Interrupt request bits can be cleared by software, but cannot be set by software.

The I flag disables all interrupts except the  $\ensuremath{\mathsf{BR}}\xspace^{-1}$  instruction interrupt.

## Interrupt Operation

When an interrupt is honored, the contents of the program counter and processor status register are automatically stored into the stack. The interrupt disable flag is set to inhibit other interrupts from interfering. The corresponding interrupt request bit is cleared and the interrupt jump destination address is read from the vector table into the program counter.

Table 1. Interrupt vector addresses and priorities

| Interrupt source     | Priority | Vector addr        | ess (Note 1)       | Interrupt request                                        | D                                    |  |

|----------------------|----------|--------------------|--------------------|----------------------------------------------------------|--------------------------------------|--|

| interrupt source     | Filolity | High               | L.ow               | generating conditions                                    | Remarks                              |  |

| Reset (Note 2)       | 1.       | FFFD <sub>16</sub> | FFFC <sub>16</sub> | At reset                                                 | Non-maskable                         |  |

| UART1 receive        | 2        | FFFB <sub>16</sub> | FFFA <sub>16</sub> | At completion of UART1 re-<br>ception                    |                                      |  |

| UART2 receive        | 3        | FFF9 <sub>16</sub> | FFF8 <sub>16</sub> | At completion of UART2 re-<br>ception                    |                                      |  |

| UART3 receive        | 4        | FFF7 <sub>16</sub> | FFF6 <sub>16</sub> | At completion of UART3 re-<br>ception                    |                                      |  |

| IPC mode register 0  | 5        | FFF5 <sub>16</sub> | FFF4 <sub>16</sub> | At writing into IPC mode register 0 from system data bus |                                      |  |

| IPC error register 0 | 6        | FFF3 <sub>16</sub> | FFF2 <sub>16</sub> | At reading IPC error register 0 from system data bus     |                                      |  |

| Timer X              | 7        | FFF1 <sub>16</sub> | FFF0 <sub>16</sub> | At timer X underflow                                     |                                      |  |

| Timer 1              | 8        | FFEF <sub>16</sub> | FFEE <sub>16</sub> | At timer 1 underflow                                     | STP release timer underflow          |  |

| Timer 2              | 9        | FFED <sub>16</sub> | FFEC <sub>16</sub> | At timer 2 underflow                                     |                                      |  |

| Timer 3              | 10       | FFEB <sub>16</sub> | FFEA <sub>16</sub> | At timer 3 underflow                                     |                                      |  |

| UART1 transmit       | 11       | FFE9 <sub>16</sub> | FFE8 <sub>16</sub> | At UART1 transmit buffer emptying                        |                                      |  |

| UART2 transmit       | 12       | FFE7 <sub>16</sub> | FFE6 <sub>16</sub> | At UART2 transmit buffer emptying                        |                                      |  |

| UART3 transmit       | 13       | FFE5 <sub>16</sub> | FFE4 <sub>16</sub> | At UART3 transmit buffer emptying                        |                                      |  |

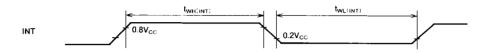

| INT                  | 14       | FFE3 <sub>16</sub> | FFE2 <sub>16</sub> | At detection of rising edge of INT input                 |                                      |  |

| BRK instruction      | 15       | FFDD <sub>16</sub> | FFDC <sub>16</sub> | At BRK instruction execution                             | Non-maskable software inter-<br>rupt |  |

Note 1: Vector addresses contain interrupt jump destination addresses.

2: Reset function in the same way as an interrupt with the highest priority.

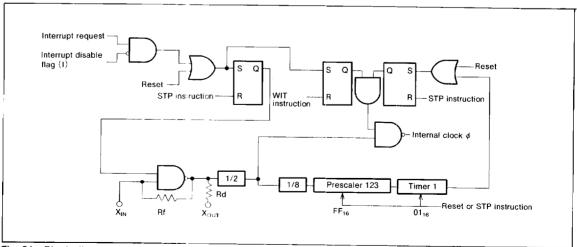

Fig. 6 Interrupt control

Fig. 7 Structure of interrupt-related registers

#### **TIMERS**

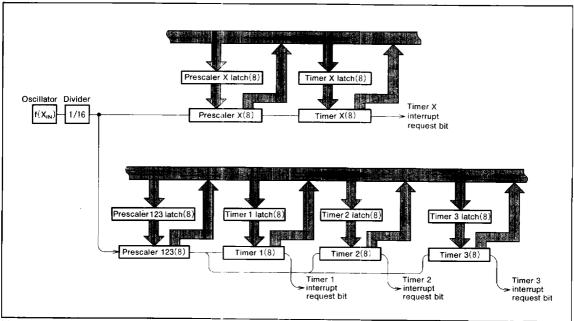

The 3888 group has 4 timers: timer X, timer 1, timer 2, and timer 3.

The timers count down. Once the contents of a timer counter reache "00<sub>16</sub>", the next count pulse reloads the contents of the corresponding timer latch into the timer, and sets the corresponding interrupt request bit to "1".

The division ratio of each timer or prescaler is given by 1/(n+1), where n is the value set in the corresponding timer or prescaler latch.

#### Timer 1, Timer 2, and Timer 3

The count source of prescaler 123 is the oscillation frequency divided by 16. The output of prescaler 123 is counted by timer 2 and timer 3, and a timer underflow sets the corresponding interrupt request bit.

#### Timer X

The count source of prescaler X is the oscillation frequency divided by 16. The output of prescaler X is counted by timer X, and the timer X underflow sets the timer X interrupt request bit.

Fig. 8 Timer block diagram

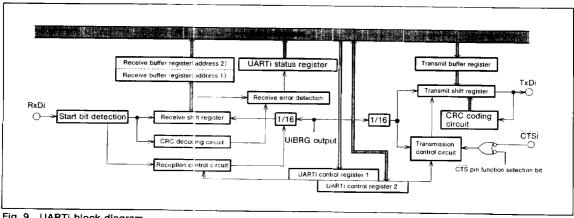

#### UART

The 3888 group contains three channels of UART's (UARTi (i=1, 2, 3)). Functionally, they are all equal and can be separately operated. Each channel includes following:

- Transmit output pin TxDi

- Receive input pin RxDi

- Transmit control input pin CTSi

- Receive/Transmit shift register

- Receive/Transmit buffer register

- UARTi control register 1

- UARTi control register 2

- UARTi status register

- Divider for baud rate generation

It also has a CLK pin (the input pin of the external clock for baud rate generation) which is shared by three channels. The CTSi or CLK shares the same pin position with the port P1. An interrupt request can occur on each channel independently when the reception or transmission is completed. Because the differences between the channels are only pin numbers and internal addresses, the following description uses UART1 for reference

#### **Data Format**

A data format for reception or transmission can be selected by setting the following bits:

- Parity enable bit (PARE)

- Parity selection bit (PARS)

- Character length selection bit (CHA\$)

- Stop bit length selection bit (STPS)

Parity generation or detection is performed by hardware. When the character length is specified in 7 bits, "0" is read from bit 7 of the receive buffer register at receiving and the value of bit 7 in the transmit data is not transmitted.

When the stop bit length is specified in 2 bits, only the first stop bit is checked at receiving.

#### CRC

When transmitting or receiving multiple characters in a lump (block data), the CRC (Cyclic Redundancy Check) method can be used for error detection.

The generating polynomial is shown below:

$$P(X) = X^8 + X^4 + X^3 + X^2 + 1$$

The target data for CRC does not include the start bit, stop bit and parity bit.

To use the error detecting function of the CRC method, it is necessary to control the start and end of the block data by software

The transmitter side transmits BBC (Block Check Character (Note 1)) after completion of the block data transmis-

The receiver side detects the completion of the block data reception by software, and detects whether or not any error exists, by the CRC remainder (Note 2) at that point of time. Take the following items into consideration when using the CRC method.

- Specify data length in 8 bits.

- A parity bit can be appended.

Note 1: Generated by the CRC coding circuit.

Note 2: Generated by the CRC decoding circuit.

Fig. 9 UARTi block diagram

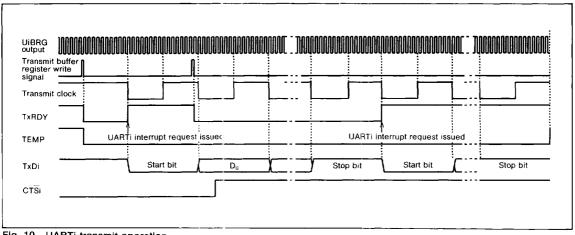

## (Transmit operation)

When data (to be transmitted) is written into the transmit buffer register after writing "1" in the transmit initialize bit (MR), the data to which the start bit (or parity bit depending on transmission condition setting) and the stop bit are appended is transferred to the transmit shift register. The transmit shift register begins shifting when it becomes transmit enable status (refer to Table 2) and transmits serial data from the TxDi pin.

In the transmit enable status, each time transmission of the stop bit of the serial data being transmitted has been completed, it is checked whether the next data has been written to the transmit buffer register. If next data is found written, transmission of that data begins. If next data is found not written, TxDi pin is held at "H" level until the next data is written, setting the transmitter empty flag (TEMP) to "1". When the transmit enable status is reset during transmission, the transmission is stopped after completing the transmission of the data already written into the transmit buffer register.

When the transmit initialize bit  $(\overline{\text{MR}})$  is "0", transmitter side is in the initial status (Note 3). At this time, the transmitter ready flag (TxRDY) is "1" and the transmitter empty flag (TEMP) is "1", and the transmit shift register is at a stop.

Note 1: When the transmitter ready flag (TxRDY) is "1", data can be written into the transmit buffer register. After data is written into the transmit buffer register, the transmitter ready flag (TxRDY) becomes "0".

Note 2: Each time data is transferred from the transmit buffer register to the transmit shift register and the start bit is output from the TxDi pin, the transmitter ready flag (TxRDY) becomes "1" and the UARTi transmission interrupt request bit is set to "1". An interrupt is honored when the UARTi transmission interrupt enable bit is "1" and the interrupt disable flag (1) is "0".

Note 3: When the transmit initialize bit (MR) is cleared to "0" during transmission, the transmission breaks.

Table 2. Conditions of transmit enable status

| TE | CTSE | CTS pin input level | Transmit enable status |

|----|------|---------------------|------------------------|

| [  | 0    | x                   | enabled                |

| 1  |      | "H"                 | disabled               |

|    | i    | "L"                 | enabled                |

| 0  | X    | X                   | disabled               |

TE: Transmit enable bit

CTSE: CTS pin function selection bit

Fig. 10 UARTi transmit operation

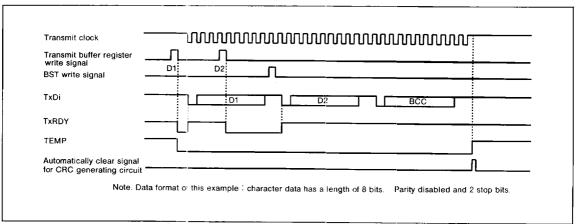

## [Transmit Operation Using CRC Method]

During transmission using the CRC method, the first block data is transmitted and then BCC is transmitted.

When the transmission of the block data is started, the CRC coding circuit (Note 1) is initialized by writing "0" in the transmit initialize bit (MR), and the first data of the block data is written into the transmit buffer register after the transmit initialize bit (MR) is reset to "1". However, if the previous transmitted data is BCC, the CRC coding circuit is automatically initialized.

The transmission of each data of block data is performed in the same way as ordinary transmission (without using the CRC method).

By writing "1" in the BCC transmission start bit (BST) after the last data of the block data is written into the transmit buffer register, the BCC is transmitted after the start bit (or parity bit depending on transmission condition setting) and stop bit are appended to the 8-bit CRC remainder that is held internally (Note 2).

At this time, it is not necessary to wait until the transmitter ready flag (TxRDY) is set to "1".

During transmission using the CRC method, when BCC has been transmitted, the transmitter empty flag (TEMP) becomes "1". The data to be transmitted following BCC is written into the transmit buffer register after the transmitter empty flag (TEMP) becomes "1".

If data is written into the transmit buffer register during the period from the writing to "1" in the BCC transmission start bit (BST) until the completion of BCC transmission, the written data is invalid and the transmission stops at the completion of BCC transmission.

The receiver side must initialize the CRC decoding circuit by software between the reception of BCC and the reception of next data. Therefore, the transmitter side must exert control to put a necessary interval between the transmission of BCC and the transmission of next data by software. The CRC coding circuit is initialized by resetting.

Note 1: The CRC coding circuit performs division with the generating polynomial for data (to be transmitted) as well as transmission and always holds its remainder in the internal register.

Note 2: The BCC value to be transmitted cannot be read out.

Fig. 11 UART transmit operation (CRC method)

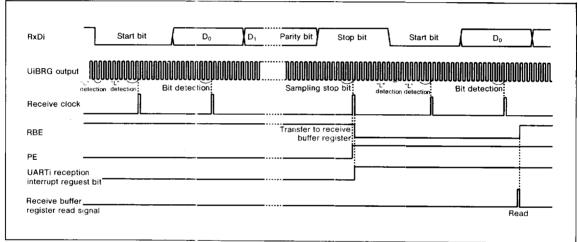

## [Receive Operation]

When "1" is written into the receive enable bit (RE), the 3888 group is put into the receive enable status (Note 1). When a start bit is detected (Note 2), the data bits (and also the parity bit depending on reception condition setting) are taken into the receive shift register. When a stop bit is detected, the reception of 1-byte data is completed (Note 3), and then the data is transferred to the receive buffer register.

When the receive enable bit (RE) is cleared to "0", the 3888 group is put into the receive disable status. At this time, the receive buffer empty flag (RBE) is "1" (empty status), the receive buffer full flag (RBF) is "0" the receive shift register is at a stop, and start bit detection is stopped.

## Receive Buffer Register

The receive buffer register is a FIFO type 2-byte (address 1 and address 2) register. A write/read operation is performed for the address specified by the write address pointer/read address pointer. (For resetting, the write address pointer/read address pointer points to address 1.)

Each time received data is written into the receive buffer register, the write address pointer is reversed. Accordingly, 2-byte data can be written. Each time the receive buffer register is read, the read address pointer is reversed. Accordingly, 2-byte data can be read out by reading the contents of the receive buffer register (UIRB) twice.

Table 3. Relationship between status flags and status of receive buffer register

| RBE | RBF | Number of left data(before writing)in receive buffer register |

|-----|-----|---------------------------------------------------------------|

| 1   | 0   | 0                                                             |

| 0   | 0   | 1                                                             |

| 0   | 1   | 2                                                             |

(Unit: byte)

RBE : Receive buffer empty flag RBF : Receive buffer full flag

# **Error during Data Reception**

When an error occurs during data reception, the corresponding error flag is set to "1" but has no effect on the receive operation. Every error flag can be reset by writing "1" into the error reset bit (ERST).

Overrun error (Flag OE)

When the next data has been received while there remains 2-byte data to be read in the receive buffer register, an overrun error occurs. To initialize the receive buffer register, clear the overrun error flag (OE) to "0" and also write "1" into the receive buffer clear bit (RBC).

Parity error (Flag PE)

This error occurs when a parity error is detected in received data.

#### Framing error (Flag FE)

This error occurs when the first stop bit is detected as "L".

## Interrupt Source Selection

When the receive interrupt source selection bit (RIS) is "0", the UARTi receive interrupt request bit is set to "1" each time data is put into the empty receive buffer register. Accordingly, the receive interrupt request can occur upon reception of each 1-byte data.

When the receive interrupt source selection bit (RIS) is "1", the UARTi receive interrupt request bit is set to "1" each time 2-byte data is arranged in the receive buffer register. Accordingly, the frequency of occurrence of receive interrupt can be reduced.

Note 1: When no data is received, "H" is input to the RxDi

Note 2: When a falling edge is input to the RxDi pin, sampling is performed with a frequency clock that is 16 times as large as the baud rate. At this time, if an "L" input is detected 2 times continuously, the start bit is detected. Furthermore, sampling is performed 3 times, approximately in the middle of the "Start bit". (Refer to Figure 12.) At this time, if "L" is detected twice or more, data reception is started and data bits are taken into the receive shift register. If "L" is not detected twice or more, the processing is returned to start bit detection.

Note 3: To judge the value of data bits, parity bit or stop bit, sampling is performed 3 times each in the middle of each bit period. When "L" or "H" is detected twice or more, each is judged as "0" or "1". (Refer to Figure 12.)

Note 4: When "1" is written into the receive buffer clear bit, both of the write address pointer and the read address pointer are cleared to address 1.

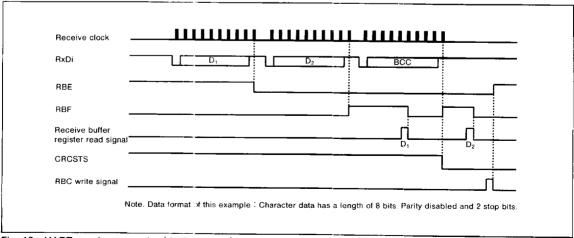

## [Receive Operation Using CRC Method]

At data reception using the CRC method, the completion of the block data and BCC reception is detected by software. Whether or not any error exists in the received data is detected by the contents of the CRC status flag (CRCSTS). At a start of the block data reception, the CRC decoding cricuit (Note 1) is cleared by writing "1" into the receive buffer clear bit (RBC). At that time, the CRC status flag (CRCSTS) becomes "1" and the receive buffer register and receive status flags (RBE, RBF) are initialized. When the CRC status flag (CRCSTS) (Note 3) is "0" after completion of BCC reception (Note 2) following the block data reception, this is regarded as no error. Otherwise, it is

The CRC decoding circuit is cleared by resetting.

regarded as an error.

- Note 1: The CRC decoding circuit performs division on the received data with the same generating polynomial as that on the transmitter side, and transfers the result to the CRC status flag (CRCSTS) upon receipt of each stop bit.

- Note 2: Received BCC is held in the receive buffer register like other received data. Accordingly, discard BCC by software. (Perform a dummy read operation or write "1" into the receive buffer clear bit (RBC) to clear the receive buffer register.)

- Note 3: The CRC status flag is updated upon receipt of each stop bit. Accordingly read the CRC status flag in the period from receipt of BBC until receipt of the stop bit of the next data.

Fig. 12 UART receive operation

Fig. 13 UART receive operation(CRC method)

#### CTSi Pin

This is an input pin for transmission control of the UARTi and also used as the port P1. For transmission control, set the CTSi pin function selection bit to "1" so that the CTSi pin may be used as a transmission control input. By inputting the "L" level to the CTSi pin on the transmitter side when the data receiver side is put into the receive enable status, the transmission from the transmitter side is enabled, so that data is output from the TxDi pin. To set the transmit enable status, the transmit enable bit must be "1".

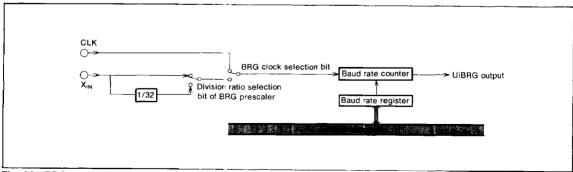

# **UARTI Divider for Baud Rate Generation** (UiBRG)

This is an 8-bit programmable divider to generate baud rate for transmission or reception.

When the set value is N (0 to 255), the division ratio becomes 1/(N+1). A count source is selected from the following by the division ratio selection bit of BRG(ERi) and the BRG clock selection bit (EXi).

- X<sub>IN</sub> clock

- X<sub>IN</sub> clock divided by 32

- External clock input from the CLK pin

When  $X_{\rm IN}$  is selected as a count source, do not set "00<sub>16</sub>" in the UiBRG. Set 4.0MHz (duty: 40-60%) or less as an input clock frequency when selecting the external clock. The transfer rate of data (to be transmitted or received) is 1/16 of the UiBRG output. Before writing data into the divider for baud rate generation, clear the receive enable bit and the transmit initialize bit to "0".

Table 4. Baud rate

| EX | BR | Baud rate(bps)                     |

|----|----|------------------------------------|

| 0  | 0  | $\frac{1(X_{IN})}{16\times(N+1)}$  |

| 0  | 1  | $\frac{f(X_{IN})}{512\times(N+1)}$ |

| 1  | ×  | f(CLK)<br>16×(N+1)                 |

EX BRG clock selection bit

BR : Division ratio selection bit of BRG

## UARTi Transmit Buffer Register (UiTB)

The data written in the transmit buffer register is transferred to the transmit shift register when the transmit shift register becomes empty, and is transmitted out from there. When the transmit shift register is empty during transmission, the data to be transmitted next can be written into the transmit buffer register.

## **UARTI Receive Buffer Register (UIRB)**

The receive buffer register is a FIFO type 2-byte register. Reading can be held up to the time when 3-byte data has been received. This register can also read received data in the order of reception at any timing. However, when an overrun error occurs, already received data is lost. In this case, initialize the receive butter register.

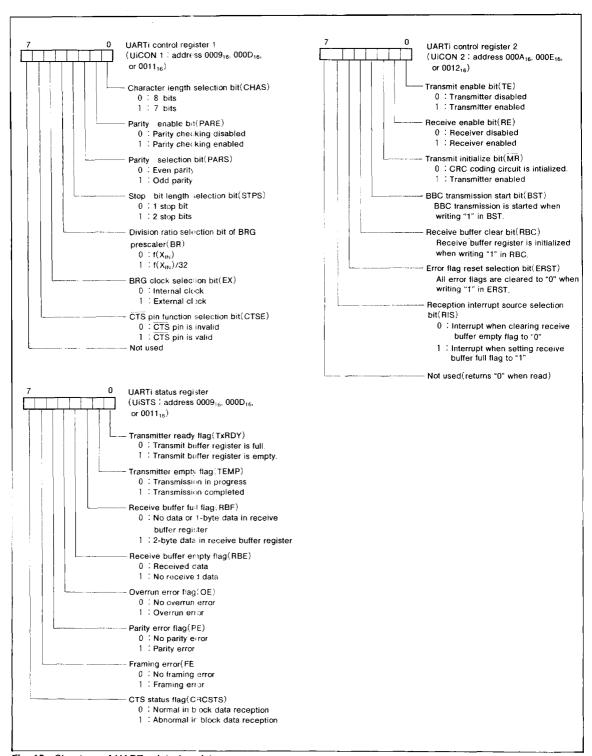

## **UARTi Control Register 1 (UiCON1)**

Only writing is enabled for the UARTi control register 1. Use the LDM or STA instruction to set a value in the UARTi control register. (If the CLB or SEB instruction is used, values other than the specified bit become undefined.)

## **UARTI Control Register 2(UiCON2)**

Both reading and writing are enabled for the UARTi control register 2. However, when reading the following bits, "0" is always read:

- BCC transmission start bit (BST)

- Receive buffer clear bit (RBC)

- Error flag reset selection bit (ERST)

## **UARTi Status Register (UISTS)**

Only reading is enabled for the UARTi status register.

Fig. 14 BRG block diagram

Fig. 15 Structure of UART-related registers

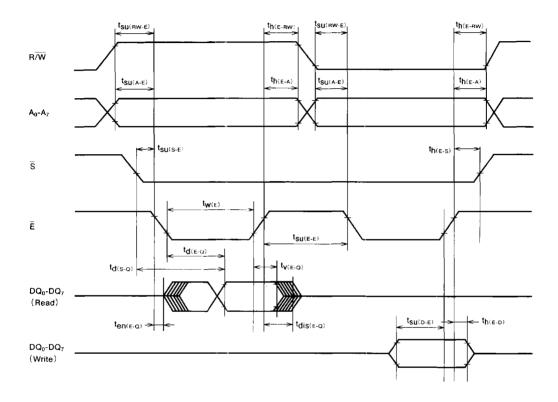

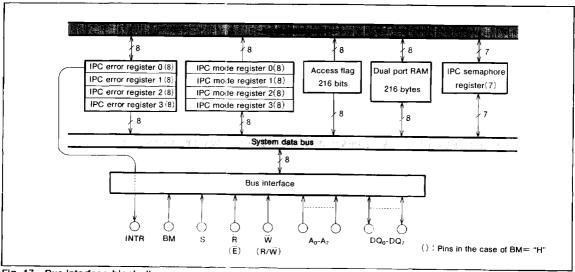

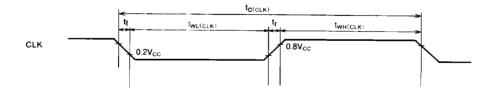

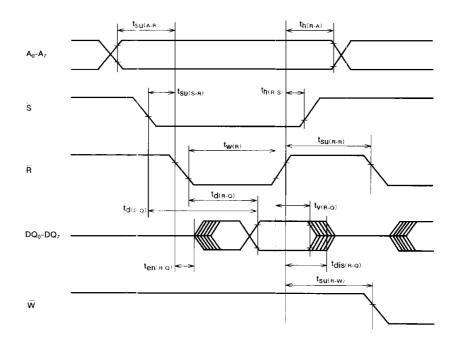

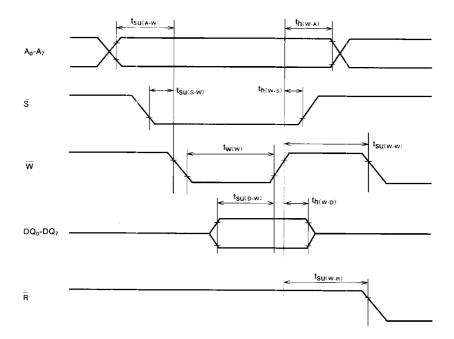

#### **Bus Interface**

The host CPU can access the dual port RAM and registers arranged in the address space of the system bus through the bus interface. The bus interface is provided with address pins  $A_0$  to  $A_7$ , data pins  $DQ_0$  to  $DQ_7$ , and 5 control pins  $\overline{S}$ ,  $\overline{R}$ ,  $\overline{W}$ , BM and INTR. These pins, except the BM pin, can be directly connected to the TTL (BM pin: The input levels are CMOS compatible). When "L" is input to the BM pin, the bus interface enters the RD/WR signal separate connection mode. When "H" is input to the BM pin, the bus interface enters the MITSUBISHI 16-bit microcomputer 7700 series connection mode.

● RD/WR signal separate connection mode

W Memory write pulse

R Memory read pulse

●7700 connection mode

R/W Data bus direction specification

E Bus enable pulse

Fig. 17 shows the bus interface block diagram.

When "L" is input to the S pin, writing/reading from the system bus is enabled.

When "H" is input to the  $\overline{S}$  pin, both writing and reading from the external are disabled. At this time, the output of the data pins DQ<sub>0</sub> to DQ<sub>7</sub> is floating.

Addressing is performed by the address pins A<sub>0</sub> to A<sub>7</sub>.

When  $\overline{W}$  pin is set to "L" in the RD/WR signal separate connection mode, the contents of the data pins  $D_0$  to  $D_7$  are written at the specified address. When the  $\overline{R}$  pin is set to "L", the contents at the specified address are cutput to the data pins  $DQ_0$  to  $DQ_7$ .

When the R/ $\overline{W}$  pin is set to "L" and the  $\overline{E}$  pin is set to "L" in the 7700 connection mode, the contents of data pins DQ<sub>0</sub> to DQ<sub>7</sub> are written at the specified address.

When the R/W pin is set to "H" and the  $\tilde{E}$  pin is set to "L", the contents of the specified address are output to the data pins DQ<sub>0</sub> to DQ<sub>7</sub>.

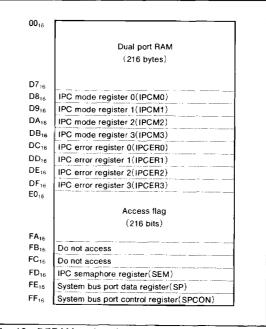

Fig. 16 shows the arrangement of the DPRAM and registers corresponding to the system bus.

Fig. 16 DPRAM and registers arrangement (corresponding to the system bus)

Fig. 17 Bus interface block diagram

## **Dual port RAM**

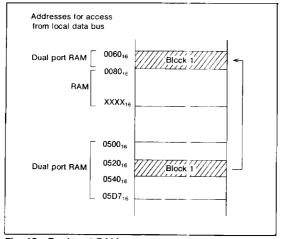

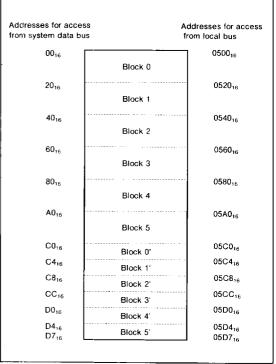

The dual port RAM has a total capacity of 216 bytes and permits reading and writing at any timing from both buses (system data bus and local data bus). Dual port RAM is arranged at addresses  $0500_{16}$  to  $05D7_{16}$  for access from the local data bus, and at addresses  $00_{1\xi}$  to  $D7_{16}$  for access from the system data bus. Fig. 18 shows the dual port RAM arrangement in the zero page area.

When access occurs simultaneously from both buses, the operation shown in Table 5 is performed by the arbitration circuit. When the dual port RAM is read or written from the system data bus, the effective addresses are system bus addresses at the falling time of  $\hat{R}$  or  $\hat{W}$  ( $\hat{E}$  in the 7700 mode).

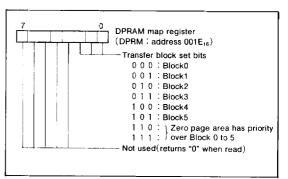

It is also possible to arrange a part of the dual port RAM at  $0060_{16}$  to  $007F_{16}$  in the zero page area on the local data bus side in units of 32-byte blocks. At this time, the zero page RAM and dual port RAM are overlapped at  $0060_{16}$  to  $007F_{16}$ . However, it is possible to read or write specified blocks of the dual port RAM, while reading or writing of the zero page RAM is inhibited. Blocks to be arranged are specified by using the DPRAM map register.

The contents of DPRAM map register becomes "07<sub>16</sub>" at reset.

Flg. 18 Dual port RAM arrangement in zero page area

Fig. 19 Dual port RAM memory map

Fig. 20 Structure of DPRAM map register

Table 5. Data after accessing the same address from system and local data buses simultaneously

| Bus op                         | eration | Data                                         |                                            |  |  |

|--------------------------------|---------|----------------------------------------------|--------------------------------------------|--|--|

| System data bus Local data bus |         | System data bus side                         | Local data bus side                        |  |  |

| Read                           | Read    | Correct data                                 | Correct data                               |  |  |

| Read Write                     |         | Correct data precedent/subsequent to writing | Data written                               |  |  |

| Write                          | Read    | Data written                                 | Correct data precedent/subsequento writing |  |  |

| Write                          | Write   | Data written into dual port RAM later        |                                            |  |  |

## Access Flag

This flag aims at arbitrating dual port RAM access. A 1-bit access flag is assigned to 1 byte of the dual port RAM. All flags comprise 216 bits (27 bytes). Fig. 21 shows the correspondence between dual port RAM addresses and access flags, as viewed from the system data bus side. The access flags can also be read from both system data bus and local data bus. However, writing is disabled. When write access is made to the corresponding dual port RAM from the system data bus or local data bus, each bit is set to "1". When read access is made from the bus specified by the direction register (explained next), each bit is cleared to "0".

The access flag is cleared to "0" by resetting.

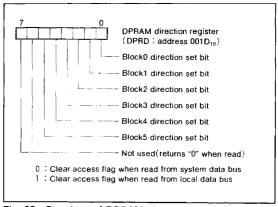

## **DPRAM Direction Register (DPRD)**

This register specifies one of both buses from which each bit of the access flag is to be cleared by reading. As shown in Fig. 19 dual port RAM memory map, 1 bit of the direction register is associated with 1 block, and this register consists of a total of 6 bits.

When the corresponding DPRAM direction register is "0", each access flag is cleared by reading from the system data bus. When this register is "1", each access flag is cleared by reading from the local data bus. When writing from either of these buses, the access flag is set.

The DPRAM direction register is cleared by resetting.

| address            | address           | 7          | 6  | 5  | 4  | 3          | 2  | 1  | 0  |

|--------------------|-------------------|------------|----|----|----|------------|----|----|----|

| 004016             | E0 <sub>16</sub>  | 07         | 06 | 05 | 04 | 03         | 02 | 01 | 00 |

| 004116             | E1 <sub>16</sub>  | 0F         | 0E | 0D | 0C | 0B         | 0A | 09 | 08 |

| 004216             | E2 <sub>16</sub>  | 17         | 16 | 15 | 14 | 13         | 12 | 11 | 10 |

| 004316             | E3 <sub>16</sub>  | 1F         | 1E | 1D | 1C | 1B         | 1A | 19 | 18 |

| 004416             | E4 <sub>16</sub>  | 27         | 26 | 25 | 24 | 23         | 22 | 21 | 20 |

| 004516             | E5 <sub>16</sub>  | 2F         | 2E | 2D | 2C | 2B         | 2A | 29 | 28 |

| 004616             | E616              | 37         | 36 | 35 | 34 | 33         | 32 | 31 | 30 |

| 004716             | £7 <sub>16</sub>  | 3F         | 3E | 3D | 3C | 3B         | 3A | 39 | 38 |

| 004818             | E8 <sub>16</sub>  | 47         | 46 | 45 | 44 | 43         | 42 | 41 | 40 |

| 004916             | E9 <sub>16</sub>  | 4F         | 4E | 4D | 4C | 48         | 4A | 49 | 48 |

| 004A <sub>16</sub> | E:A <sub>16</sub> | 57         | 56 | 55 | 54 | 53         | 52 | 51 | 50 |

| 004B <sub>16</sub> | £B₁6              | 5F         | 5E | 5D | 5C | 5B         | 5A | 59 | 58 |

| 004C <sub>16</sub> | EC <sub>16</sub>  | 67         | 66 | 65 | 64 | 63         | 62 | 61 | 60 |

| 004D <sub>16</sub> | ED,6              | 6F         | 6E | 6D | 6C | 6B         | ôΑ | 69 | 68 |

| 004E <sub>16</sub> | E.E 16            | 77         | 76 | 75 | 74 | 73         | 72 | 71 | 70 |

| 004F <sub>16</sub> | £.F.16            | 7 <b>F</b> | 7E | 7D | 7C | 7B         | 7A | 79 | 78 |

| 005016             | F0 <sub>16</sub>  | 87         | 86 | 85 | 84 | 83         | 82 | 81 | 80 |

| 005116             | F1 <sub>16</sub>  | 8F         | 8E | 8D | 8C | 8B         | 8A | 89 | 88 |

| 005216             | F2 <sub>16</sub>  | 97         | 96 | 95 | 94 | 93         | 92 | 91 | 90 |

| 005316             | F3 <sub>16</sub>  | 9F         | 9E | 9D | 9C | 9B         | 9A | 99 | 98 |

| 005416             | F4,6              | <b>A</b> 7 | A6 | A5 | A4 | <b>A</b> 3 | A2 | A1 | A0 |

| 005516             | F5 <sub>16</sub>  | AF         | ΑE | AD | AC | AB         | AA | A9 | A8 |

| 005616             | F6 <sub>16</sub>  | 87         | B6 | B5 | B4 | В3         | B2 | B1 | ВО |

| 005716             | F7 <sub>16</sub>  | BF         | BE | BD | ВС | 88         | ВА | В9 | В8 |

| 005816             | F8 <sub>16</sub>  | C7         | Ç6 | C5 | C4 | C3         | C2 | C1 | CO |

| 005916             | F9 <sub>16</sub>  | CF         | CE | CD | CC | СВ         | CA | C9 | C8 |

| 005A <sub>16</sub> | FA <sub>16</sub>  | D7         | D6 | D5 | D4 | D3         | D2 | D1 | DO |

Fig. 21 Correspondence between dual port RAM addresses and access flags

Fig. 22 Structure of DPRAM direction register (viewed from system data bus side)

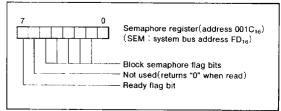

## Semaphore Register (semaphore flag: SEM)

This register is for handshaking of the host CPU and consists of a 6-bit block semaphore flag and a ready flag.

The block semaphore flag can be read and written from both system data bus and local data bus. Reading can be performed in units of byte but writing can be performed only in units of bit.

As shown in Table 6, a bit position to be written is specified in the 3 low-order bits of data, and value 1/0 to be written is specified in bit 7.

The ready flag can be read and written from the local data bus and can be read only from the system bus. Reading/writing is performed in the same way as the block semaphore flag.

When data is written into the IPC mode register 0 from the system data bus, it is cleared to "0".

All the bits of the semaphore register are cleared to "0" by resetting.

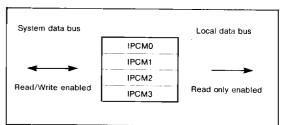

## IPC Mode Register(IPCMi (i==0, 1, 2, 3))

This register consists of 4 bytes, being an 8-bit register that can be freely set by the user.

This register can be read and written from the system data bus, but can be read only from the local data bus.

This register is used to set a mode of the UART and others from the host CPU through the system data bus.

When data is written into the IPC mode register 0 from the system data bus, the ready flag of the semaphore register is cleared to "0" and also an IPC mode register 0 interrupt request occurs.

Fig. 23 Structure of semaphore register

Table 6. Example of writing to semaphore register

|                          | 1-byte data to be        | 1-byte data to be written into SEM  clear each bit to "0" To set each bit to "1"  0016 8016  0116 8116  0216 8216 |  |  |  |

|--------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit position for writing | To clear each bit to "0" | To set each bit to "1"                                                                                            |  |  |  |

| Bit 0                    | 0016                     | 80 <sub>16</sub>                                                                                                  |  |  |  |

| Bit 1                    | 0116                     | 81 <sub>16</sub>                                                                                                  |  |  |  |

| Bit 2                    | 02 <sub>16</sub>         | 82 <sub>16</sub>                                                                                                  |  |  |  |

| Bit 3                    | 0316                     | 83,6                                                                                                              |  |  |  |

| Bit 4                    | 0416                     | 84 <sub>16</sub>                                                                                                  |  |  |  |

| Bit 5                    | 05 <sub>16</sub>         | 8516                                                                                                              |  |  |  |

| Bit 7 (Ready flag)       | 0716                     | 8716                                                                                                              |  |  |  |

Fig. 24 Access to IPC mode register

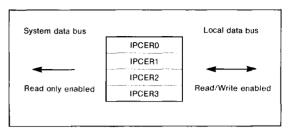

## IPC Error Register(IPCERi (i=0, 1, 2, 3))

This register consists of 4 bytes, being an 8-bit register that can be freely set by the user.

The register can be read only from the system data bus, but can be read and written from the local data bus.

When access is made by reading the contents of IPC error registers 0-3 from the system data bus, only the bits from which "1" is read are cleared to "0" by hardware. When reading from the local data bus, no value change occurs. All the bits of the IPC error registers 0-3 are cleared to "0". When data is written into the IPC error register 0 from the local data bus, the INTR pin becomes "H". When the IPC error register 0 is read from the system data bus, the INTR pin becomes "L" and also an IPC error register 0 interrupt request occurs. The INTR pin becomes "L" by resetting.

#### Caution

The IPC error register is designed on the assumption that access is not made simultaneously from the local data bus and system data bus. Accordingly, in reading this register from the system data bus while writing is performed into the IPC error register from the local data bus, take the following into consideration.

For writing from the local data bus, use the SEB or CLB instruction. If another instruction such as the LDM instruction is used, the value read from the system data bus is undefined. The value read from the system data bus is the data precedent to writing from the local data bus or the data subsequent to writing. In any case, a correct value is read. However, judge by software whether it is the data precedent to writing or the data subsequent to writing.

When access is made by a read modify write instruction such as the SEB instruction from the local data bus and the same register is read from the system data bus between the read cycle and the write cycle, the bit being "1" is cleared to "0" regardless of the value written from the local data bus. The reason is that the 3888 CPU holds the clear signal of hardware until the next instruction is fetched. The value read from the system data bus is one precedent to writing in the write cycle of the local data bus.

Fig. 25 Access to IPC error register

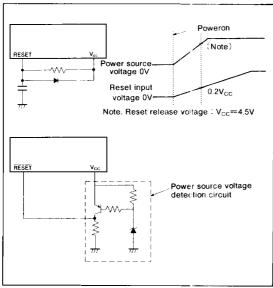

#### RESET CIRCUIT

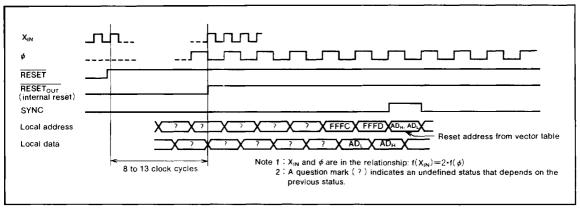

To reset the 3888 group,  $\overline{RESET}$  pin should be held at a "L" level for  $2\mu s$  or more. Then  $\overline{RESET}$  pin is returned to an "H" level (the power source voltage should be between 4.5V and 5.5V, and  $X_{1N}$  oscillation width is stable), reset is released. Internal operation begins after 8 to 13  $X_{1N}$  clock cycles are completed. After the reset is completed, the program starts from the address contained in address FFFD<sub>16</sub> (high-order) and address FFFC<sub>16</sub> (low-order).

Make sure that the reset input voltage is no more than 0.9V for a power source voltage of 4.5V.

Fig. 26 Reset circuit

Fig. 27 Internal status of microcomputer after reset

Fig. 28 Timing of reset

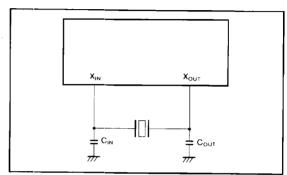

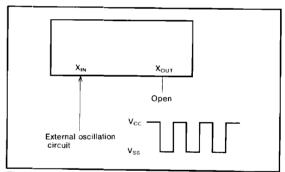

## **CLOCK GENERATING CIRCUIT**

An oscillation circuit can be created by connecting a resonator between  $X_{\text{IN}}$  and  $X_{\text{OUT}}$ . Use the circuit constants in accordance with the resonator manufacture's recommended value. When using an external clock signal, input the clock signal to the  $X_{\text{IN}}$  pin and leave the  $X_{\text{OUT}}$  pin open.

When the STP status is released, timer 1 interrupt request occurs simulaneously with the corresponding interrupt request occurrence, so set the timer 1 interrupt enable bit to "0" before the STP instruction is executed.

#### Oscillation Control

#### (1) Stop Mode

When the STP instruction is executed, oscillation stops with the internal clock  $\phi$  at "H". Timer 1 is set to "01<sub>16</sub>" and prescaler 123 is set to "FF<sub>16</sub>".

Oscillation restarts when an external interrupt is honored, but the internal clock  $\phi$  remains at "H" until timer 1 underflows.

This allows time for the clock circuit oscillation to stabilize. If oscillation is restarted by a reset, no wait time is generated, so keep the RESET pin at "L" level until oscillation has stabilized.

#### (2) Wait Mode

When the WIT instruction is executed, the internal clock  $\phi$  stops at a "H" level, but the oscillator itself does not stop. The internal clock restarts if a reset occurs or when an interrupt is honored.

Since the oscillator does not stop, normal operation can be started immediately after the clock is restarted.

To ensure that interrupts will be honored, to release the STP or WIT state, interrupt enable bits must be set to "1" before the STP or WIT instruction is executed.

Fig. 29 Ceramic resonator circuit

Fig. 30 External clock input circuit

Fig. 31 Block diagram of clock generating circuit

# NOTES ON PROGRAMMING Processor Status Register

The contents of the processor status register (PS) after a reset are undefined, except for the interrupt disable flag (I) which is "1". After a reset, initialize flags which affect program execution.

In particular, it is essential to initialize the index X mode (T) and the decimal operation mode (D) flag because of their effect on calculations.

## Interrupts

The contents of the interrupt request bits are not modified immediately after they have been written. After writing to an interrupt request register, execute at least one instruction before executing a BBC or BBS instruction.

#### **Decimal Calculations**

To calculate in decimal notation, set the decimal mode flag (D) to "1", then execute an ADC or SBC instruction. Only the ADC and SBC instruction yield proper decimal results. After executing an ADC or SBC instruction, execute at least one instruction before executing a SEC, CLC, or CLD instruction.

In decimal mode, the values of the negative (N), overflow (V), and zero (Z) flag are invalid.

The carry flag can be used to indicate whether a carry or borrow has occurred. Initialize the carry flag before each calculation. Clear the carry flag before an ADC and set the flag before an SBC.

#### **Timers**

If a value n (between 0 and 255) is written to a timer latch, the frequency division ratio is 1/(n+1).

## **Multiplication and Division Instructions**

The index X mode (T) and the decimal mode (D) flag do not affect the MUL and DIV instruction.

The execution of these instructions does not modify the contents of the processor status register.

#### **Ports**

The contents of the port direction registers cannot be read. The following cannot be used:

- the data transfer instruction (LDA, etc.)

- the operation instruction when the index X mode flag (T) is "1".

- the addressing mode which uses the value of a direction register as an index

- the bit-test instruction (BBC or BBS, etc.) to a direction register

- the read-modify-write instruction (ROR, CLB, or SEB, etc.) to a direction register

Use instructions such as LDM and STA, etc., to set the port direction registers.

#### Instruction Execution Time

The instruction execution time is obtained by multiplying the frequency of the internal clock  $\phi$  by the number of cycles needed to execute an instruction.

The number of cycles required to execute an instruction is shown in the list of machine instructions.

The frequency of the internal clock  $\phi$  is half of the  $X_{\rm IN}$  frequency.

### DATA REQUIRED FOR MASK ORDERS

The following are necessary when ordering a mask ROM production:

- 1. Mask ROM Order Confirmation Form

- 2. Mark Specification Form

- 3. Data to be written to ROM, in EPROM form (three identical copies)

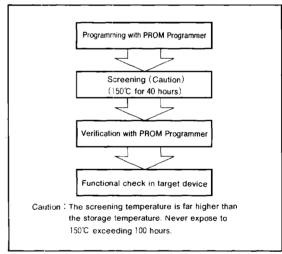

#### PROM PROGRAMMING METHOD

The built-in PROM of the blank One Time PROM version and built-in EPROM version can be read or programmed with a general-purpose PROM programmer using a special programming adapter.

Set the address of PROM programmer in the user ROM area.

| Package      | Name of Programming Adapter |

|--------------|-----------------------------|

| 64P4B, 64S1B | PCA4738S-64A                |

| 64P6N-A      | PCA4738F-64A                |

| 64P6S-A      | PCA4738G-64                 |

| 64D0         | PCA4738L-64A                |

The PROM of the blank One Time PROM version is not tested or screened in the assembly process and following processes. To ensure proper operation after programming, the procedure shown in Figure 32 is recommended to verify programming.

Fig. 32 Programming and testing of One Time PROM version

## ABSOLUTE MAXIMUM RATINGS

| Symbol          | Parameter                                                                                                                                                                                                                                                                     | Conditions                                                                   | Ratings                      | Unit |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------|------|

| V <sub>GG</sub> | Power source voltage                                                                                                                                                                                                                                                          |                                                                              | -0.3 to 7.0                  | V    |

| V <sub>I</sub>  | Input voltage P0 <sub>0</sub> -P0 <sub>7</sub> , P1 <sub>0</sub> -P1 <sub>6</sub> , PA <sub>0</sub> -PA <sub>7</sub> , PB <sub>0</sub> -PB <sub>7</sub> , A <sub>0</sub> -A <sub>7</sub> , DQ <sub>0</sub> -DQ <sub>7</sub> , R. W. S. BM, RxD <sub>1</sub> -RxD <sub>3</sub> |                                                                              | -0.3 to V <sub>cc</sub> +0.3 | v    |

| V <sub>I</sub>  | Input voltage RESET, XIN                                                                                                                                                                                                                                                      | All voltages are based on V <sub>SS</sub> .  Output transistors are cut off. | -0.3 to V <sub>CC</sub> +0.3 | ٧    |

| V.              | Input voltage CNV <sub>SS</sub>                                                                                                                                                                                                                                               |                                                                              | 0.3 to 13                    | V    |

| V <sub>0</sub>  | Output voltage P0 <sub>0</sub> -P0 <sub>7</sub> , P1 <sub>0</sub> -P1 <sub>6</sub> , PA <sub>0</sub> -PA <sub>7</sub> , PB <sub>0</sub> -PB <sub>7</sub> , DQ <sub>0</sub> -DQ <sub>7</sub> , TxD <sub>1</sub> -TxD <sub>3</sub>                                              |                                                                              | -0.3 to V <sub>CC</sub> +0.3 | V    |

|                 | Xour, INTR                                                                                                                                                                                                                                                                    |                                                                              |                              |      |

|                 |                                                                                                                                                                                                                                                                               | DIP (64P4B)                                                                  | 500(1200)(Note)              | mW   |

| Pd              | Power dissipation                                                                                                                                                                                                                                                             | QFP (64P6N-A)                                                                | 300(750)(Note)               | mW   |

| ·u              |                                                                                                                                                                                                                                                                               | QFP (64P6S-A)                                                                | 280(700)(Note)               | mW   |