## CY7C138

# 4K x 8/9 Dual-Port Static RAM with Sem, Int, Busy

### Features

- True dual-ported memory cells that enable simultaneous reads of the same memory location

- 4K x 8 organization (CY7C138)

- 0.65-micron complementary metal oxide semiconductor (CMOS) for optimum speed and power

- High speed access: 25 ns

- Low operating power: I<sub>CC</sub> = 160 mA (max.)

- Fully asynchronous operation

- Automatic power-down

- Transistor transistor logic (TTL) compatible

- Expandable data bus to 32 bits or more using Master/Slave chip select when using more than one device

- On-chip arbitration logic

- Semaphores included to permit software handshaking between ports

- INT flag for port-to-port communication

- Available in 68-pin plastic leaded chip carrier (PLCC)

- Pb-free packages available

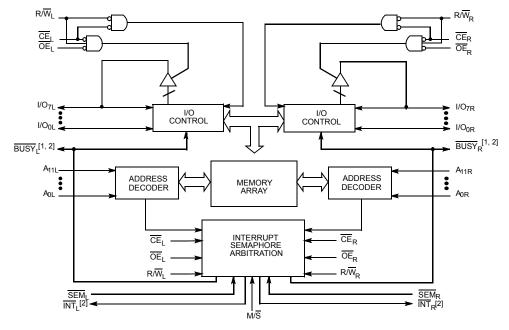

### Logic Block Diagram

### **Functional Description**

The CY7C138 is a high speed CMOS 4K x 8 dual-port static RAM. Various arbitration schemes are included on the CY7C138 to handle situations when multiple processors access the same piece of data. Two ports are provided permitting independent, asynchronous access for reads and writes to any location in memory. The CY7C138 can be used as a standalone 8-bit dual-port static RAM or multiple devices can be combined to function as a 16-bit or wider master/slave dual-port static RAM. An M/S pin is provided for implementing 16-bit or wider memory applications without the need for separate master and slave devices or additional discrete logic. Application areas include interprocessor/multiprocessor designs, communications status buffering, and dual-port video/graphics memory.

Each port has independent control pins: chip enable ( $\overline{CE}$ ), read or write enable (R/W), and output enable ( $\overline{OE}$ ). Two flags are provided on each port (BUSY and INT). BUSY signals that the port is trying to access the same location currently being accessed by the other port. The interrupt flag (INT) permits communication between ports or systems by means of a mail box. The semaphores are used to pass a flag, or token, from one port to the other to indicate that a shared resource is in use. The semaphore logic is comprised of eight shared latches. Only one side can control the latch (semaphore) at any time. Control of a semaphore indicates that a shared resource is in use. An automatic power-down feat<u>ure</u> is controlled independently on each port by a chip enable (CE) pin or SEM pin.

#### Notes

- 1. BUSY is an output in master mode and an input in slave mode.

- 2. Interrupt: push-pull output and requires no pull-up resistor.

Cypress Semiconductor Corporation Document #: 38-06037 Rev. \*G San Jose, CA 95134-1709 • 408-943-2600 Revised December 2, 2010

## Contents

| Pin Configurations         | 3  |

|----------------------------|----|

| Maximum Ratings            |    |

| Operating Range            |    |

| Electrical Characteristics | 4  |

| Capacitance                | 5  |

| Switching Characteristics  |    |

| Architecture               |    |

| Functional Description     | 14 |

| Write Operation            |    |

| Read Operation             |    |

| Interrupts                 |    |

| Busy                       |    |

| Master/Slave               |    |

| Semaphore Operation                     | 14 |

|-----------------------------------------|----|

| Ordering Information                    |    |

| 4K x8 Dual-Port SRAM                    | 17 |

| Ordering Code Definition                | 17 |

| Package Diagram                         | 18 |

| Acronyms                                | 19 |

| Document Conventions                    |    |

| Units of Measure                        | 19 |

| Document History Page                   | 20 |

| Sales, Solutions, and Legal Information |    |

| Worldwide Sales and Design Support      | 21 |

| Products                                |    |

| PSoC Solutions                          | 21 |

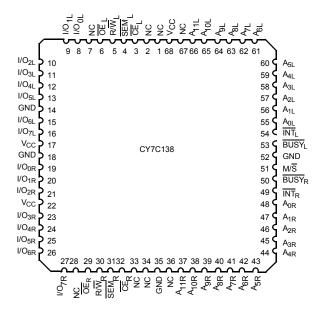

### **Pin Configurations**

#### Figure 1. 68-Pin PLCC (Top View)

#### Table 1. Pin Definitions

| Left Port            | Right Port           | Description                                                                                                                                                                                                                                                                                               |

|----------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/O <sub>0L-7L</sub> | I/O <sub>0R-7R</sub> | Data bus input/output                                                                                                                                                                                                                                                                                     |

| A <sub>0L-11L</sub>  | A <sub>0R-11R</sub>  | Address lines                                                                                                                                                                                                                                                                                             |

| CEL                  | CER                  | Chip enable                                                                                                                                                                                                                                                                                               |

| OEL                  | OE <sub>R</sub>      | Output enable                                                                                                                                                                                                                                                                                             |

| R/W <sub>L</sub>     | R/W <sub>R</sub>     | Read/Write enable                                                                                                                                                                                                                                                                                         |

| SEML                 | SEM <sub>R</sub>     | Semaphore enable. When asserted LOW, allows access to eight semaphores. The three least significant bits of the address lines will determine which semaphore to write or read. The $I/O_0$ pin is used when writing to a semaphore. Semaphores are requested by writing a 0 into the respective location. |

| INTL                 | INT <sub>R</sub>     | Interrupt flag. INT <sub>L</sub> is set <u>when</u> right port writes location FFE and is cleared when left port reads location FFE. INT <sub>R</sub> is set when left port writes location FFF and is cleared when right port reads location FFF.                                                        |

| BUSYL                | BUSYR                | Busy flag                                                                                                                                                                                                                                                                                                 |

| M/S                  |                      | Master or slave select                                                                                                                                                                                                                                                                                    |

| V <sub>CC</sub>      |                      | Power                                                                                                                                                                                                                                                                                                     |

| GND                  |                      | Ground                                                                                                                                                                                                                                                                                                    |

#### Table 2. Selection Guide

| Description                                  | 7C138-25   | Unit |    |

|----------------------------------------------|------------|------|----|

| Maximum access time (ns)                     |            | 25   | ns |

| Maximum operating current                    | Commercial | 180  | mA |

| Maximum standby current for I <sub>SB1</sub> | Commercial | 40   | mA |

### **Maximum Ratings**

Exceeding maximum ratings may impair the useful life of the device. These user guidelines are not tested.<sup>[3]</sup>

| Storage temperature65 °C to +150 °C                             |

|-----------------------------------------------------------------|

| Ambient temperature with power applied–55 °C to +125 °C         |

| Supply voltage to ground potential0.5 V to +7.0 V               |

| DC voltage applied to outputs<br>in High Z state0.5 V to +7.0 V |

| DC input voltage <sup>[4]</sup> 0.5 V to +7.0 V                 |

| Output current into outputs (LOW)                               |

| Static discharge voltage       | >2001 V |

|--------------------------------|---------|

| (per MIL-STD-883, Method 3015) |         |

| Latch-up current               | >200 mA |

### **Operating Range**

| Range      | Ambient<br>Temperature | V <sub>cc</sub> |

|------------|------------------------|-----------------|

| Commercial | 0 °C to +70 °C         | 5 V ± 10%       |

| Industrial | –40 °C to +85 °C       | 5 V ± 10%       |

### Electrical Characteristics Over the Operating Range

| Deremeter        | Decerintien                                  | Test Conditio                                                                                                                                                                                                          | Test Conditions |     |     | Unit |

|------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----|------|

| Parameter        | Description                                  | lest Conditio                                                                                                                                                                                                          |                 |     |     | Unit |

| V <sub>OH</sub>  | Output HIGH voltage                          | V <sub>CC</sub> = Min., I <sub>OH</sub> = -4.0 mA                                                                                                                                                                      |                 | 2.4 | -   | V    |

| V <sub>OL</sub>  | Output LOW voltage                           | V <sub>CC</sub> = Min., I <sub>OL</sub> = 4.0 mA                                                                                                                                                                       |                 | -   | 0.4 | V    |

| V <sub>IH</sub>  |                                              |                                                                                                                                                                                                                        |                 | 2.2 | -   | V    |

| V <sub>IL</sub>  | Input LOW voltage                            |                                                                                                                                                                                                                        |                 | -   | 0.8 | V    |

| I <sub>IX</sub>  | Input leakage current                        | $GND \leq V_I \leq V_{CC}$                                                                                                                                                                                             |                 | -10 | +10 | μA   |

| I <sub>OZ</sub>  | Output leakage current                       | Output disabled, GND $\leq$ V <sub>O</sub> $\leq$                                                                                                                                                                      | V <sub>CC</sub> | -10 | +10 | μA   |

| I <sub>CC</sub>  | Operating current                            | V <sub>CC</sub> = Max.,                                                                                                                                                                                                | Commercial      | -   | 180 | mA   |

|                  | I <sub>OUT</sub> = 0 mA,<br>Outputs disabled | Industrial                                                                                                                                                                                                             | -               | 190 |     |      |

| I <sub>SB1</sub> | Standby current                              |                                                                                                                                                                                                                        | Commercial      | -   | 40  | mA   |

|                  | (Both ports TTL levels)                      | $f = f_{MAX}^{IOJ}$                                                                                                                                                                                                    | Industrial      | -   | 50  |      |

| I <sub>SB2</sub> | Standby current                              | $\overline{CE}_{L}$ and $\overline{CE}_{R} \ge V_{IH}$ ,<br>f = f <sub>MAX</sub> <sup>[5]</sup>                                                                                                                        | Commercial      | -   | 110 | mA   |

|                  | One port TTL level)                          | $f = f_{MAX}^{LOJ}$                                                                                                                                                                                                    | Industrial      | -   | 120 |      |

| I <sub>SB3</sub> | Standby current                              | Both por <u>ts</u>                                                                                                                                                                                                     | Commercial      | -   | 15  | mA   |

|                  | (Both ports CMOS levels)                     | $      \overline{CE} \text{ and } \overline{CE}_R \ge V_{CC} - 0.2 \text{ V}, \\ V_{IN} \ge V_{CC} - 0.2 \text{ V} \\ \text{or } V_{IN} \le 0.2 \text{ V}, \text{ f = 0}^{[5]}                                    $    | Industrial      | -   | 30  |      |

| I <sub>SB4</sub> | Standby current                              | <u>On</u> e po <u>rt</u>                                                                                                                                                                                               | Commercial      | -   | 100 | mA   |

|                  | (One port CMOS level)                        | $\begin{array}{l} CE_{L} \text{ or } CE_{R} \geq V_{CC} - 0.2 \text{ V}, \\ V_{IN} \geq V_{CC} - 0.2 \text{ V or} \\ V_{IN} \leq 0.2 \text{ V}, \text{ Active} \\ Port outputs, \text{ f} = f_{MAX}^{[5]} \end{array}$ | Industrial      | -   | 115 |      |

- Notes

3. The Voltage on any input or I/O pin cannot exceed the power pin during power-up.

4. Pulse width < 20 ns.</li>

- 5. f<sub>MAX</sub> = 1/t<sub>RC</sub> = All inputs cycling at f = 1/t<sub>RC</sub> (except output enable). f = 0 means no address or control lines change. This applies only to inputs at CMOS level standby I<sub>SB3</sub>

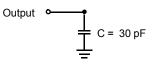

### Capacitance<sup>[6]</sup>

| Parameter        | Description        | Test Conditions                        | Max | Unit |

|------------------|--------------------|----------------------------------------|-----|------|

| C <sub>IN</sub>  | Input capacitance  | $T_A = 25 \circ C, f = 1 \text{ MHz},$ | 10  | pF   |

| C <sub>OUT</sub> | Output capacitance | V <sub>CC</sub> = 5.0 V                | 15  | pF   |

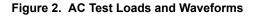

Load (Load 2)

### Switching Characteristics Over the Operating Range<sup>[7]</sup>

| Deremeter                             | Description                     | 70      | 7C138-25 |      |  |

|---------------------------------------|---------------------------------|---------|----------|------|--|

| Parameter                             | Description                     | Min Max |          | Unit |  |

| READ CYCLE                            |                                 |         | •        |      |  |

| t <sub>RC</sub>                       | Read cycle time                 | 25      | -        | ns   |  |

| t <sub>AA</sub>                       | Address to data valid           | -       | 25       | ns   |  |

| t <sub>OHA</sub>                      | Output hold from address change | 3       | -        | ns   |  |

| t <sub>ACE</sub>                      | CE LOW to data valid            | -       | 25       | ns   |  |

| t <sub>DOE</sub>                      | OE LOW to data valid            | -       | 15       | ns   |  |

| t <sub>LZOE</sub> <sup>[8,9,10]</sup> | OE Low to Low Z                 | 3       | -        | ns   |  |

| t <sub>HZOE</sub> <sup>[8,9,10]</sup> | OE HIGH to High Z               | -       | 15       | ns   |  |

| t <sub>LZCE</sub> <sup>[8,9,10]</sup> | CE LOW to Low Z                 | 3       | -        | ns   |  |

| t <sub>HZCE</sub> <sup>[8,9,10]</sup> | CE HIGH to High Z               | -       | 15       | ns   |  |

| t <sub>PU</sub> <sup>[10]</sup>       | CE LOW to Power-up              | 0       | -        | ns   |  |

| t <sub>PD</sub> <sup>[10]</sup>       | CE HIGH to Power-down           | -       | 25       | ns   |  |

| WRITE CYCLE                           | - ·                             |         |          | •    |  |

| t <sub>WC</sub>                       | Write cycle time                | 25      | _        | ns   |  |

| t <sub>SCE</sub>                      | CE LOW to write end             | 20      | -        | ns   |  |

Notes

6. Tested initially and after any design or process changes that may affect these parameters.

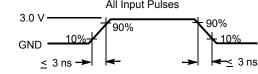

7. Test conditions assume signal transition time of 3 ns or less, timing reference levels of 1.5 V, input pulse levels of 0 to 3.0 V, and output loading of the specified Io//IoH and 30-pF load capacitance.

At any temperature and voltage condition for any device,  $t_{HZCE}$  is less than  $t_{LZCE}$  and  $t_{HZOE}$  is less than  $t_{LZOE}$ . Test conditions used are Load 3 8.

9.

10. This parameter is guaranteed but not tested.

## Switching Characteristics Over the Operating Range<sup>[7]</sup> (continued)

| Parameter                            | Description                         | 70  | 138-25  | Unit |  |

|--------------------------------------|-------------------------------------|-----|---------|------|--|

|                                      | Description                         | Min | Max     | Unit |  |

| t <sub>AW</sub>                      | Address setup to write end          | 20  | _       | ns   |  |

| t <sub>HA</sub>                      | Address hold from write end         | 2   | -       | ns   |  |

| t <sub>SA</sub>                      | Address setup to write start        | 0   | -       | ns   |  |

| t <sub>PWE</sub>                     | Write pulse width                   | 20  | -       | ns   |  |

| t <sub>SD</sub>                      | Data setup to write end             | 15  | -       | ns   |  |

| t <sub>HD</sub>                      | Data hold from write end            | 0   | -       | ns   |  |

| t <sub>HZWE</sub> [11,12]            | $R/\overline{W}$ LOW to High Z      | -   | 15      | ns   |  |

| t <sub>LZWE</sub> <sup>[11,12]</sup> | R/W HIGH to Low Z                   | 3   | -       | ns   |  |

| t <sub>WDD</sub> <sup>[13]</sup>     | Write pulse to data delay           | _   | 50      | ns   |  |

| t <sub>DDD</sub> <sup>[13]</sup>     | Write data valid to read data valid | -   | 30      | ns   |  |

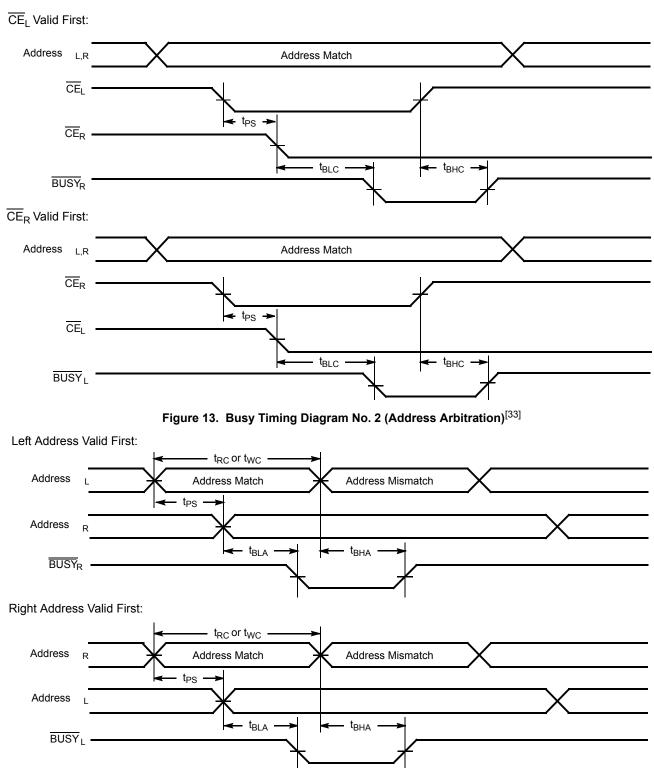

| BUSY TIMING <sup>[14]</sup>          |                                     |     |         | •    |  |

| t <sub>BLA</sub>                     | BUSY LOW from address match         | -   | 20      | ns   |  |

| t <sub>BHA</sub>                     | BUSY HIGH from address mismatch     | -   | 20      | ns   |  |

| t <sub>BLC</sub>                     | BUSY LOW from CE LOW                | -   | 20      | ns   |  |

| t <sub>BHC</sub>                     | BUSY HIGH from CE HIGH              | -   | 20      | ns   |  |

| t <sub>PS</sub>                      | Port setup for priority             | 5   | -       | ns   |  |

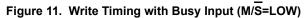

| t <sub>WB</sub>                      | R/W LOW after BUSY LOW              | 0   | -       | ns   |  |

| t <sub>WH</sub>                      | R/W HIGH after BUSY HIGH            | 20  | -       | ns   |  |

| t <sub>BDD</sub> <sup>[15]</sup>     | BUSY HIGH to data valid             | -   | Note 15 | ns   |  |

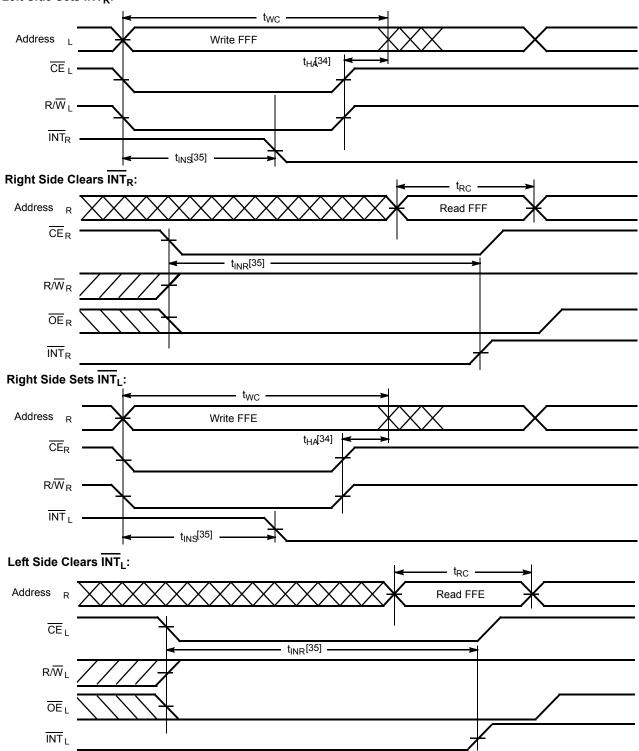

| INTERRUPT TIMIN                      | <b>G</b> <sup>[14]</sup>            |     |         |      |  |

| t <sub>INS</sub>                     | INT set time                        | -   | 25      | ns   |  |

| t <sub>INR</sub>                     | INT reset time                      | _   | 25      | ns   |  |

| SEMAPHORE TIMI                       | NG                                  |     | •       | -    |  |

| t <sub>SOP</sub>                     | SEM flag update pulse (OE or SEM)   | 10  | _       | ns   |  |

| t <sub>SWRD</sub>                    | SEM flag write to read time         | 5   | -       | ns   |  |

| t <sub>SPS</sub>                     | SEM flag contention window          | 5   | _       | ns   |  |

Notes

11. Test conditions used are Load 3.

12. This parameter is guaranteed but not tested.

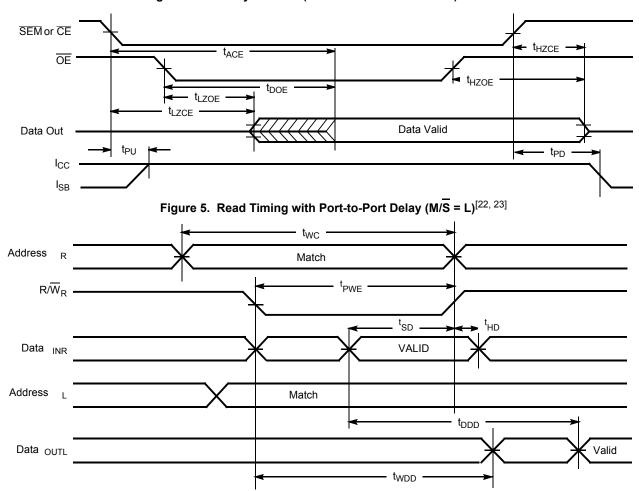

13. For information on part-to-part delay through RAM cells from writing port to reading port, refer to Read Timing with Port-to-Port Delay waveform.

14. Test conditions used are Load 2.

15.  $t_{BDD}$  is a calculated parameter and is the greater of  $t_{WDD} - t_{PWE}$  (actual) or  $t_{DDD} - t_{SD}$  (actual).

# Switching Waveforms

Figure 3. Read Cycle No. 1 (Either Port Address Access)<sup>[16, 17]</sup>

Notes \_\_\_\_\_\_ 16. R/W is HIGH for read cycle. 17. Device is continuously selected  $\overline{CE}$  = LOW and  $\overline{OE}$  = LOW. This waveform cannot be used for semaphore reads

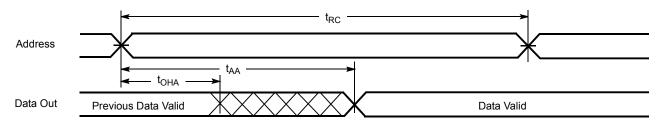

Figure 4. Read Cycle No. 2 (Either Port CE/OE Access)<sup>[18, 19, 20, 21]</sup>

Notes

- 18. R/W is HIGH for read cycle.

- 19. Device is continuously selected  $\overline{CE}$  = LOW and  $\overline{OE}$  = LOW. This waveform cannot be used for semaphore reads.

- 20. Address valid prior to or coincident with  $\overline{CE}$  transition LOW. 21.  $\overline{CE_L} = L$ , SEM = H when accessing RAM.  $\overline{CE} = H$ , SEM = L when accessing semaphores. 22.  $\overline{BUSY} = HIGH$  for the writing port. 23.  $\overline{CE_L} = \overline{CE_R} = LOW.$

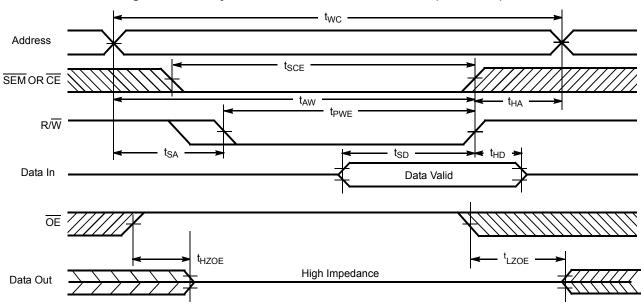

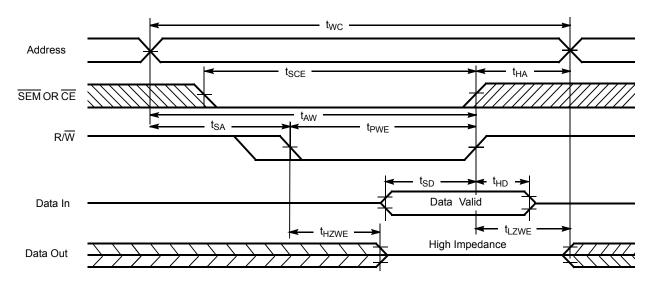

Figure 6. Write Cycle No. 1: OE Three-States Data I/Os (Either Port)<sup>[24, 25, 26]</sup>

Figure 7. Write Cycle No. 2: R/W Three-States Data I/Os (Either Port)<sup>[24, 26, 27]</sup>

#### Notes

- 24. The internal write time of the memory is defined by the overlap of CE or SEM LOW and R/W LOW. Both signals must be LOW to initiate a write, and either signal can terminate a write by going HIGH. The data input setup and hold timing should be referenced to the rising edge of the signal that terminates the write.

25. If OE is LOW during a R/W controlled write cycle, the write pulse width must be the larger of t<sub>PWE</sub> or (t<sub>HZWE</sub> + t<sub>SD</sub>) to allow the I/O drivers to turn off and data to be placed on the bus for the required t<sub>SD</sub>. If OE is HIGH during a R/W controlled write cycle (as in this example), this requirement does not apply and the write pulse can be as short as the specified t<sub>PWE</sub>.

26. R/W must be HIGH during all address transitions.

- 26. R/W must be HIGH during all address transitions.

27. Data I/O pins enter high impedance when OE is held LOW during write.

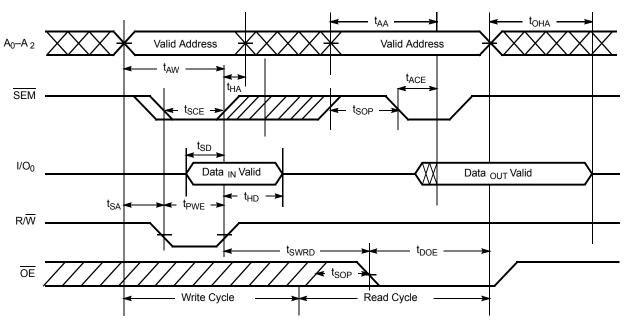

Figure 8. Semaphore Read After Write Timing, Either Side<sup>[28]</sup>

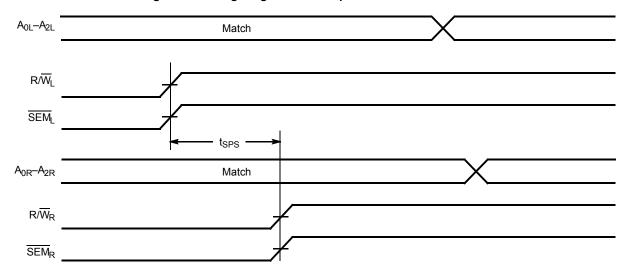

Figure 9. Timing Diagram of Semaphore Contention<sup>[29, 30, 31]</sup>

#### Note<u>s</u>

- 28. CE = HIGH for the duration of the above timing (both write and read cycle).

- 29. I/O<sub>0R</sub> = I/O<sub>0L</sub> = LOW (request semaphore);  $\overline{CE}_R = \overline{CE}_L = HIGH$

- 30. Semaphores are reset (available to both ports) at cycle start.

31. If t<sub>SPS</sub> is violated, the semaphore will definitely be obtained by one side or the other, but there is no guarantee which side will control the semaphore.

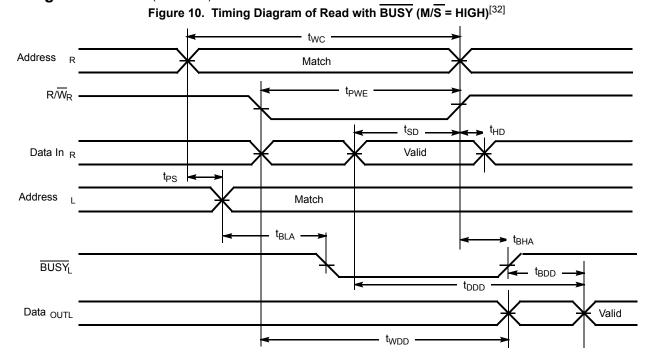

Note 32.  $\overline{CE}_L = \overline{CE}_R = LOW.$

#### Note

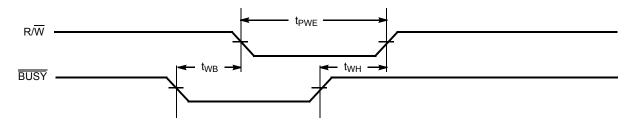

33. If t<sub>PS</sub> is violated, the busy signal will be asserted on one side or the other, but there is no guarantee on which side BUSY will be asserted.

Figure 14. Interrupt Timing Diagrams

Left Side Sets INT<sub>R</sub>:

#### Notes

34. t<sub>HA</sub> depends on which enable pin ( $\overline{CE}_L$  or  $\overline{R/W}_L$ ) is deasserted first. 35. t<sub>INS</sub> or t<sub>INR</sub> depends on which enable pin ( $\overline{CE}_L$  or  $\overline{R/W}_L$ ) is asserted last.

### Architecture

The CY7C138 consists of an array of 4K words of 8 bits each of dual-port RAM cells, I/O and address lines, and control signals (CE, OE, R/W). These control pins permit independent access for reads or writes to any location in memory. To handle simultaneous writes and reads to the same location, a BUSY pin is provided on each port. Two interrupt (INT) pins can be used for port-to-port communication. Two semaphore (SEM) control pins are used for allocating shared resources. With the M/S pin, the CY7C138 can function as a master (BUSY pins are outputs) or as a slave (BUSY pins are inputs). The CY7C138 has an automatic power-down feature controlled by CE. Each port is provided with its own output enable control (OE), which enables data to be read from the device.

### **Functional Description**

#### Write Operation

Data <u>m</u>ust be set up for a duration of  $t_{SD}$  before the rising edge of R/W in order to guarantee a valid write. A write operation is controlled by either the  $\overline{OE}$  pin (see Write Cycle No. 1 waveform) or the R/W pin (see Write Cycle No. <u>2</u> waveform). Data can be written to the device  $t_{HZOE}$  after the  $\overline{OE}$  is deasserted or  $t_{HZWE}$  after the falling edge of R/W. Required inputs for non-contention operations are summarized in Table 3.

If a location is being written to by one port and the opposite port attempts to read that location, a port-to-port flowthrough delay must be met before the data is read on the output; otherwise the data read is not deterministic. Data is valid on the port  $t_{DDD}$  after the data is presented on the other port.

#### **Read Operation**

When reading the device, the user must assert both the  $\overline{OE}$  and  $\overline{CE}$  pins. Data is available  $t_{ACE}$  after  $\overline{CE}$  or  $t_{DOE}$  after  $\overline{OE}$  is asserted. If the user of the CY7C138 wishes to access a semaphore flag, then the SEM pin must be asserted instead of the CE pin.

#### Interrupts

The interrupt flag ( $\overline{\text{INT}}$ ) permits communications between ports. When the left port writes to location FFF, the right port's interrupt flag ( $\overline{\text{INT}}_{\text{R}}$ ) is set. This flag is cleared when the right port reads that same location. Setting the left port's interrupt flag ( $\overline{\text{INT}}_{\text{L}}$ ) is accomplished when the right port writes to location FFE. This flag is cleared when the left port reads location FFE. The message at FFF or FFE is user-defined. See Table 4 for input requirements for INT. INT<sub>R</sub> and INT<sub>L</sub> are push-pull outputs and do not require pull-up resistors to operate. BUSY<sub>L</sub> and BUSY<sub>R</sub> in master mode are push-pull outputs and do not require pull-up resistors to operate.

#### Busy

The CY7C138 provides on-chip arbitration to alleviate simultaneous memory location access (contention). If both ports' CEs are asserted and an address match occurs within  $t_{PS}$  of each other the Busy logic determines which port has access. If  $t_{PS}$  is violated, one port definitely gains permission to the location, but it is not guaranteed which one. BUSY will be asserted  $t_{BLA}$  after an address match or  $t_{BLC}$  after CE is taken LOW.

#### Master/Slave

A  $M/\overline{S}$  pin is provided to expand the word width by configuring the device as either a master or a slave. The BUSY output of the master is connected to the BUSY input of the slave. This enables the device to interface to a master device with no external components.Writing of slave devices must be delayed until after the BUSY input has settled. Otherwise, the slave chip may begin a write cycle during a contention situation.When presented as a HIGH input, the M/<u>S pin a</u>llows the device to <u>be used</u> as a master and therefore the BUSY line is an output. BUSY can then be used to send the arbitration outcome to a slave.

#### **Semaphore Operation**

The CY7C138 provides eight semaphore latches, which are separate from the dual-port memory locations. Semaphores are used to reserve resources that are shared between the two ports. The state of the semaphore indicates that a resource is in use. For example, if the left port wants to request a resource, it sets a latch by writing a zero to a semaphore location. The left port then verifies its success in setting the latch by reading it. After writing to the semaphore, SEM or OE must be deasserted for  $t_{\ensuremath{\mathsf{SOP}}}$  before attempting to read the semaphore. The semaphore value is available t<sub>SWRD</sub> + t<sub>DOE</sub> after the rising edge of the semaphore write. If the left port was successful (reads a zero), it assumes control over the shared resource, otherwise (reads a one) it assumes the right port has control and continues to poll the semaphore. When the right side has relinquished control of the semaphore (by writing a one), the left side succeeds in gaining control of the a semaphore. If the left side no longer requires the semaphore, a 1 is written to cancel its request.

Semaphores are accessed by asserting  $\overline{SEM}$  LOW. The  $\overline{SEM}$  pin functions as a chip enable for the semaphore latches ( $\overline{CE}$  must remain HIGH <u>during SEM</u> LOW). A<sub>0-2</sub> represents the semaphore address.  $\overline{OE}$  and R/W are used in the same manner as a normal memory access. When writing or reading a semaphore, the other address pins have no effect.

When writing to the semaphore, only  $I/O_0$  is used. If a zero is written to the left port of an unused semaphore, a one will appear at the same semaphore address on the right port. That semaphore can now only be modified by the side showing zero (the left port in this case). If the left port now relinquishes control by writing a one to the semaphore, the semaphore is set to 1 for both sides. However, if the right port had requested the semaphore (written a zero) while the left port had control, the right port immediately owns the semaphore after the left port releases it. Table 5 shows sample semaphore operations.

When reading a semaphore, all eight or nine data lines output the semaphore value. The read value is latched in an output register to prevent the semaphore from changing state during a write from the other port. If both ports attempt to access the semaphore within  $t_{SPS}$  of each other, the semaphore is definitely obtained by one side or the other, but there is no guarantee which side controls the semaphore.

Initialization of the semaphore is not automatic and must be reset during initialization program at power-up. All semaphores on both sides should have a 1 written into them at initialization from both sides to assure that they are free when needed.

### Table 3. Non-Contending Read/Write

|    | Inpu | uts |     | Outputs            | Operation              |

|----|------|-----|-----|--------------------|------------------------|

| CE | R/W  | OE  | SEM | I/O <sub>0-7</sub> | Operation              |

| Н  | Х    | Х   | Н   | High Z             | Power-down             |

| Н  | Н    | L   | L   | Data out           | Read data in semaphore |

| Х  | Х    | Н   | Х   | High Z             | I/O lines disabled     |

| Н  | μ    | Х   | L   | Data in            | Write to semaphore     |

| L  | Н    | L   | Н   | Data ut            | Read                   |

| L  | L    | Х   | Н   | Data in            | Write                  |

| L  | Х    | Х   | L   |                    | Illegal condition      |

# Table 4. Interrupt Operation Example (assumes $\overline{\text{BUSY}}_{L} = \overline{\text{BUSY}}_{R} = \text{HIGH}$ )

|                 | Left Port Right Port |    |    |                   |     |     |    |    |                   |     |

|-----------------|----------------------|----|----|-------------------|-----|-----|----|----|-------------------|-----|

| Function        | R/W                  | CE | OE | A <sub>0-11</sub> | INT | R/W | CE | OE | A <sub>0-11</sub> | INT |

| Set left INT    | Х                    | Х  | Х  | Х                 | L   | L   | L  | Х  | FFE               | Х   |

| Reset left INT  | Х                    | L  | L  | FFE               | Н   | Х   | Х  | Х  | Х                 | Х   |

| Set right INT   | L                    | L  | Х  | FFF               | Х   | Х   | Х  | Х  | Х                 | L   |

| Reset right INT | Х                    | Х  | Х  | Х                 | Х   | Х   | L  | L  | FFF               | Н   |

#### Table 5. Semaphore Operation Example

| Function                         | I/O <sub>0-7</sub> Left | I/O <sub>0-7</sub> Right | Status                                    |

|----------------------------------|-------------------------|--------------------------|-------------------------------------------|

| No action                        | 1                       | 1                        | Semaphore free                            |

| Left port writes semaphore       | 0                       | 1                        | Left port obtains semaphore               |

| Right port writes 0 to semaphore | 0                       | 1                        | Right side is denied access               |

| Left port writes 1 to semaphore  | 1                       | 0                        | Right port is granted access to semaphore |

| Left port writes 0 to semaphore  | 1                       | 0                        | No change. Left port is denied access     |

| Right port writes 1 to semaphore | 0                       | 1                        | Left port obtains semaphore               |

| Left port writes 1 to semaphore  | 1                       | 1                        | No port accessing semaphore address       |

| Right port writes 0 to semaphore | 1                       | 0                        | Right port obtains semaphore              |

| Right port writes 1 to semaphore | 1                       | 1                        | No port accessing semaphore               |

| Left port writes 0 to semaphore  | 0                       | 1                        | Left port obtains semaphore               |

| Left port writes 1 to semaphore  | 1                       | 1                        | No port accessing semaphore               |

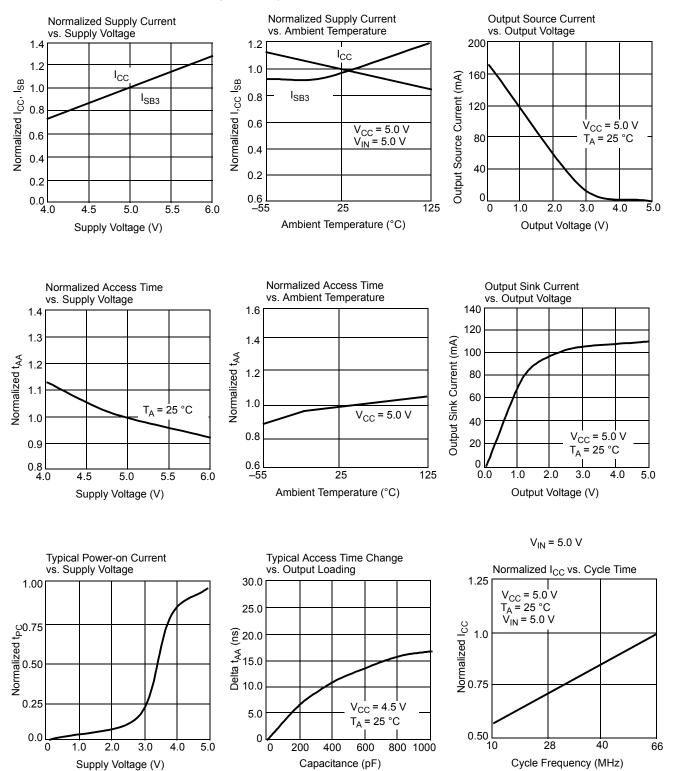

#### Figure 15. Typical DC and AC Characteristics

Page 16 of 21

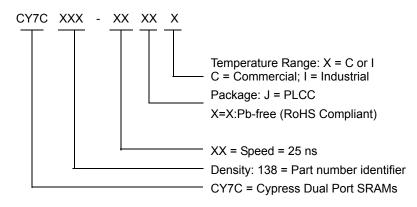

### **Ordering Information**

### 4K x8 Dual-Port SRAM

| Speed<br>(ns) | Ordering Code | Package<br>Diagram | Package Type                                 | Operating<br>Range |  |

|---------------|---------------|--------------------|----------------------------------------------|--------------------|--|

| 25            | CY7C138-25JXC | 51-85005           | 68-Pin Plastic Leaded Chip Carrier (Pb-free) | Commercial         |  |

|               | CY7C138-25JXI | 51-85005           | 68-Pin Plastic Leaded Chip Carrier (Pb-free) | Industrial         |  |

#### Ordering Code Definition

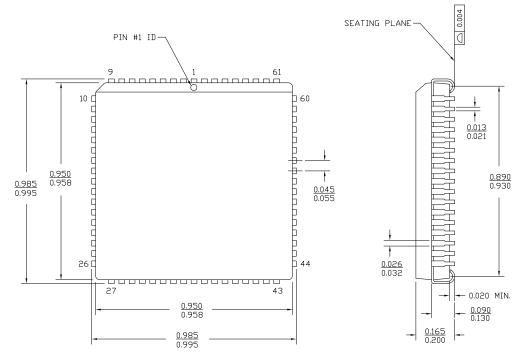

### Package Diagram

Figure 16. 68-Pin Plastic Leaded Chip Carrier (51-85005)

68 Lead Plastic Leaded Chip Carrier J81

DIMENSIONS IN INCHES MIN. MAX.

51-85005 \*B

## Acronyms

| Acronym | Description                             |

|---------|-----------------------------------------|

| CMOS    | complementary metal oxide semiconductor |

| TQFP    | thin quad plastic flatpack              |

| I/O     | input/output                            |

| SRAM    | static random access memory             |

| PLCC    | plastic leaded chip carrier             |

| TTL     | transistor transistor logic             |

### **Document Conventions**

### **Units of Measure**

| Symbol | Unit of Measure |

|--------|-----------------|

| ns     | nano seconds    |

| V      | Volts           |

| μA     | micro Amperes   |

| mA     | milli Amperes   |

| Ω      | Ohms            |

| mV     | milli Volts     |

| MHz    | Mega Hertz      |

| pF     | pico Farad      |

| W      | Watts           |

| °C     | degree Celcius  |

# **Document History Page**

| Document Title: CY7C138 4K x 8/9 Dual-Port Static RAM with Sem, Int, Busy<br>Document Number: 38-06037 |         |                    |                    |                                                                                                                                                                                                                             |  |

|--------------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Rev.                                                                                                   | ECN No. | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                       |  |

| **                                                                                                     | 110180  | SZV                | 09/29/01           | Change from Spec number: 38-00536 to 38-06037                                                                                                                                                                               |  |

| *A                                                                                                     | 122287  | RBI                | 12/27/02           | power-up requirements added to Maximum Ratings Information                                                                                                                                                                  |  |

| *В                                                                                                     | 393403  | YIM                | See ECN            | Added Pb-Free Logo<br>Added Pb-Free parts to ordering information:<br>CY7C138-15JXC, CY7C138-25JXC, CY7C139-25JXC                                                                                                           |  |

| *C                                                                                                     | 2623658 | VKN/PYRS           | 12/17/08           | Added CY7C138-25JXI part<br>Removed CY7C139 from the Ordering information table                                                                                                                                             |  |

| *D                                                                                                     | 2672737 | GNKK               | 03/12/2009         | Corrected title in the Document History table                                                                                                                                                                               |  |

| *E                                                                                                     | 2714768 | VKN/AESA           | 06/04/2009         | Corrected defective Logic Block diagram, Pinouts and Package diagrams                                                                                                                                                       |  |

| *F                                                                                                     | 2898564 | RAME               | 03/24/10           | Removed inactive parts. Updated package diagram.                                                                                                                                                                            |  |

| *G                                                                                                     | 3099184 | ADMU               | 12/02/2010         | Removed information for CY7C139 parts.<br>Removed speed bins -15,-35,-55.<br>Updated datasheet as per new template<br>Added Acronyms and Units of Measure table<br>Added Ordering Code Definition<br>Updated all footnotes. |  |

### Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at cypress.com/sales.

#### Products

| Automotive               | cypress.com/go/automotive |

|--------------------------|---------------------------|

| Clocks & Buffers         | cypress.com/go/clocks     |

| Interface                | cypress.com/go/interface  |

| Lighting & Power Control | cypress.com/go/powerpsoc  |

|                          | cypress.com/go/plc        |

| Memory                   | cypress.com/go/memory     |

| Optical & Image Sensing  | cypress.com/go/image      |

| PSoC                     | cypress.com/go/psoc       |

| Touch Sensing            | cypress.com/go/touch      |

| USB Controllers          | cypress.com/go/USB        |

| Wireless/RF              | cypress.com/go/wireless   |

|                          |                           |

#### **PSoC Solutions**

psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 5

© Cypress Semiconductor Corporation, 2009-2010. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

Document #: 38-06037 Rev. \*G

Revised December 2, 2010

Page 21 of 21

All products and company names mentioned in this document may be the trademarks of their respective holders.