# Am29510/L510

16 X 16 Multiplier Accumulator

#### DISTINCTIVE CHARACTERISTICS

- Uses two's complement or unsigned inputs and

- Round control

- Output register preload

- 35-bit product accumulator result

- 32-bit product

- 3-bit extended product

- IMOX<sup>TM</sup> processing

- ECL internal circuitry for speed

- TTL I/O, Single 5V Supply

- FAST

- High speed version multiply accumulate time 80ns

- Low power version multiply accumulate time 110ns

#### **GENERAL DESCRIPTION**

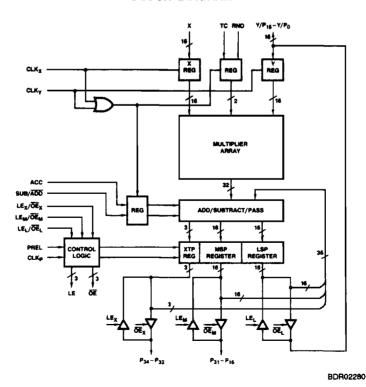

The Am29510 is a high-speed 16 x 16-bit multiplier/accumulator (MAC). The X and Y input registers accept 16-bit inputs in either two's complement or unsigned magnitude format. A third register stores the Two's Complement (TC), Round (RND), Accumulator (ACC), and Subtraction/Addition (SUB/ADD) control bits. This register is clocked whenever the X or Y input registers are clocked.

The 35-bit accumulator/output register contains the full 32-bit multiplier output which is sign extended or zero-filled based on the TC control bit. The accumulator can also be

preloaded from an external source through the bidirectional P port. The operation of the accumulator is controlled by the signals ACC, (Accumulator), SUB/ADD (Subtraction/Addition), and PREL (Preload). Each of the input registers and the output register has independent clocks.

The Am29L510 is a low-power version of the Am29510. The Am29L510 consumes only one-half the power of its standard power counterpart while maintaining nearly two-thirds the speed.

#### **BLOCK DIAGRAM**

IMOX is a trademark of Advanced Micro Devices, Inc.

03563B

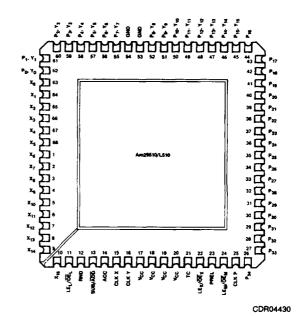

### **CONNECTION DIAGRAM Top View**

**Dual In-Line**

Leadless Chip Carrier

CDR04440

Note: Pin 1 is marked for orientation

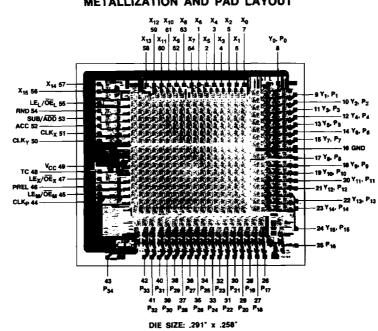

# METALLIZATION AND PAD LAYOUT

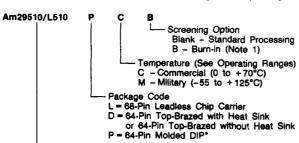

#### ORDERING INFORMATION

AMD products are available in several packages and operating ranges. The order number is formed by a combination of the following: Device number, speed option (if applicable), package type, operating range and screening option (if desired).

Valid Combinations

Am29510 DC, DCB, DMB, LC, LMB, PC\*, PCB\*

**Valid Combinations**

Consult the AMD sales office in your area to determine if a device is currently available in the combination you wish.

Device Type Multiplier Accumulator

Note 1. 180-hour burn-in — Heat sink parts:  $T_A = 125^{\circ}C$ Non-heat sink parts:  $T_A = 85^{\circ}C$

|                | PIN DESCRIPTION                                                    |     |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|----------------|--------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| *Pin No.       | Name                                                               | 1/0 | Description                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| 54             | RND                                                                | ı   | Round When RND is High, a bit with a weight of $P_{15}$ is added to the multiplier product. RND is loaded on the rising edge of $CLK_X$ or $CLK_Y$ .                                                                                                                                                                     |  |  |  |  |  |

| 48             | тс                                                                 | Ï   | Two's Complement When High, the X and Y inputs are defined as two's complement data, or as unsigned data when Low. The TC control is loaded on the rising edge of CLK <sub>X</sub> or CLK <sub>Y</sub> .                                                                                                                 |  |  |  |  |  |

| 46             | PREL                                                               | 1   | Preload  When High, data is preloaded into the specific output register when its respective Load Enable is High. When Low, the accumulator register is available at the P-port when the Output Enables are Low.                                                                                                          |  |  |  |  |  |

| 47             | LEX/OEX                                                            | ''- | Load Enable Extended/Output Enable Extended Active High Load Enable for the XTP port during preloading. Active Low three-state control for the XTP port during normal operation (see Preload Function). (TSX)**                                                                                                          |  |  |  |  |  |

| 45             | LEM/OEM                                                            | 1   | Load Enable Most/Output Enable Most Active High Load Enable for the MSP port during preloading. Active Low three-state control for the MSP port during normal operation (see Preload Function). (TSM)**                                                                                                                  |  |  |  |  |  |

| 55             | LEL/ÖEL                                                            | ١   | Load Enable Least/Output Enable Least Active High Load Enable for the LSP port during preloading. Active Low three-state control for the LSP port during normal operation (see Preload Function). (TSL)**                                                                                                                |  |  |  |  |  |

| 51, 50         | CLKX, CLKY                                                         | ı   | CLOCKS Load X and Y data respectively and TC, RND, ACC and SUB/ADD on the rising edge.                                                                                                                                                                                                                                   |  |  |  |  |  |

| 44             | CLKP                                                               | ı   | CLOCK Loads data into the XTP, MSP and LSP registers on the rising edge.                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 1-7,<br>56-64  | X <sub>15</sub> -X <sub>0</sub>                                    | Ī   | Multiplier Data Input Data is loaded into the X register on the rising edge of CLK <sub>X</sub> .                                                                                                                                                                                                                        |  |  |  |  |  |

| 8-15,<br>17-24 | Y <sub>15</sub> -Y <sub>0</sub><br>P <sub>15</sub> -P <sub>0</sub> | 1/0 | Bidirectional Port Data is loaded into the Y register on the rising edge of CLKy. Product output for Least Significant Product (LSP) and input to preload LSP register.                                                                                                                                                  |  |  |  |  |  |

| 41-43          | P <sub>34</sub> -P <sub>32</sub>                                   | 1/0 | Bidirectional Port Product output for Extended Product (XTP) and input to preload XTP register.                                                                                                                                                                                                                          |  |  |  |  |  |

| 25-40          | P31-P16                                                            | 1/0 | Bidirectional Port Product output for the Most Significant Product (MSP) and input to preload MSP register.                                                                                                                                                                                                              |  |  |  |  |  |

| 52             | ACC                                                                | •   | Accumulate When High, the multiplier product is accumulated in the accumulator. When Low, the multiplier product is written into the accumulator (see Accumulator Function Table). The ACC control is loaded on the rising edge of CLK <sub>Y</sub> .                                                                    |  |  |  |  |  |

| 53             | SUB/ADD                                                            | ŀ   | Subtraction/Addition When High, the accumulator contents are subtracted from the multiplier product and the result written back into the accumulator. When Low, the multiplier product is added into the accumulator (see Accumulator Function Table). The SUB/ADD control is loaded on the rising edge of CLKx or CLKy. |  |  |  |  |  |

\*DIP Configuration

\*\*TRW TDC1010 Pin Designation

# PRELOAD FUNCTION

|             | 1 5 /     | 1 East | 16.7                  | Outp                                      | ut Reg                                        | ister |

|-------------|-----------|--------|-----------------------|-------------------------------------------|-----------------------------------------------|-------|

| PREL        | EX/<br>ŒX | 뜐      |                       | XTP                                       | MSP                                           | LSP   |

| 0           | 0         | 0      | 0                     | α                                         | a                                             | Q     |

| 0           | 0         | 0      | 1                     | Q                                         | Q                                             | Z     |

| 0           | 0         | 1      | 1                     | Q                                         | Z                                             | Q     |

| 0           | 0         | 1      | 1                     | Q                                         | Z                                             | Ż     |

| 0 0 0 0 0 0 | 1         | 0      | 1<br>0<br>1<br>0<br>1 | Z                                         | a                                             | Q     |

| 0           | 1         | 0      | 1                     | Z                                         | l a                                           | Z     |

| 0           | 1         | 1      | 0                     | Z                                         | Z                                             | Q     |

| 0           | 1         | 1 1    | 1                     | Z                                         | Z                                             | Z     |

| 1           | 0         | 0      | 0                     | Z                                         | 2                                             | Z     |

| 1           | 0         | 0      | 1 0                   | Z                                         | Z                                             | PL    |

| 1           | 0         | 1      | 0                     | Z                                         | PL                                            | Ż     |

| 1           | 0         | 1      | 1                     | Q Q Q Q Z Z Z Z Z Z Z Z Z L PL L PL PL PL | Q Q Z Z Q Q Z Z Z Z PL PL Z Z PL PL Z Z PL PL | Q     |

| 1           | 1         | 0      | 0<br>1<br>0           | PL                                        | Z                                             | Z     |

| 1           | 1         | 0      | 1                     | PL                                        | Z                                             | PL    |

| 1           | 1         | 1      | 0                     | PL                                        | PL                                            | Z     |

| 1           | 1         | 1_     | 1                     | PL                                        | PL                                            | PL    |

Z = output buffers at High impedance (disabled).

Q = output buffers at Low impedance. Contents of

output register available through output ports.

PL = output disabled. Preload data supplied to the output pins will be loaded into the output register at the rising edge of CLKp.

# **ACCUMULATOR FUNCTION TABLE**

| PREL | ACC | SUB/ | Р  | OPERATION |

|------|-----|------|----|-----------|

| L    | L   | х    | Q  | Load      |

| L    | н   | L    | a  | Add       |

| L    | н   | Н    | Q  | Subtract  |

| Н    | Х   | X    | PL | Preload   |

#### **DETAILED DESCRIPTION**

The Am29510 is a high-speed 16 x 16-bit multiplier/accumulator (MAC). It comprises a 16-bit parallel multiplier followed by a 35-bit accumulator. Two 16-bit input registers are provided for the X and Y operands. A third register stores two control bits, TC and RND. TC selects either a two's complement or an unsigned magnitude format for both data inputs. The RND control, when High, causes a bit to be added to the multiplier product with the weight of  $P_{15}$ . This causes the most significant 16-bits of the product to be rounded to the value nearest to the full 32-bit product. Using the RND control once during an accumulation causes the most significant 19-bits of the accumulator to be rounded to the value nearest the full 35-bit accumulation. The TC/RND register is clocked whenever the X or Y input registers are clocked.

The 32-bit multiplier output is zero-filled or sign-extended as appropriate to provide a 35-bit input to the accumulator. The accumulator has four functions: the product may be loaded into the accumulator, the product may be added into the

accumulator value, the previous accumulator value may be subtracted from the product and the result stored in the accumulator or the accumulator may be preloaded from an external source. The operation of the accumulator is controlled by the signals ACC, SUB/ADD and PREL. ACC and SUB/ADD are stored in a register clocked whenever the X or Y registers are clocked. ACC in conjunction with SUB/ADD selects one of the first three accumulator functions (see Accumulator Function Table). For output and preloading purposes the accumulator is considered in three sections: Extended Product (XTP, P<sub>34</sub>-P<sub>32</sub>) controlled by LE<sub>X</sub>/OE<sub>X</sub>, Most Significant Product (MSP, P31-P16) controlled by LEM/ OEM and Least Significant Product (LSP, P15-P0) controlled by LEI /OEI. When PREL is Low these controls are active-Low Output Enables for three-state output buffers. When PREL is High the output buffers automatically become high impedance, and the controls operate as active-High Load Enables to the three sections of the accumulator to permit preloading of data applied to the bidirectional P port. The Pport has 35 bits, the least significant 16 of which share pins with the Y input.

#### Am29510/L510 INPUT FORMATS

#### Fractional Two's Complement Input

| 5 14 13<br>2 <sup>0</sup> 2 <sup>-1</sup> 2 <sup>-2</sup> ;<br>Sign)<br>5 14 13<br>15 2 <sup>14</sup> 2 <sup>13</sup> 4 | 2-3 2-4 2  | -5 <sub>2</sub> -6 | 2 <sup>-7</sup> 2<br>XiN | r-8 2 <sup>-9</sup>           | 2 <sup>-10</sup> | 2-11<br>Inte | 2 <sup>-12</sup> | 2 <sup>-13</sup> | 2-14 2 | 2-15 | 15<br>-2 <sup>0</sup><br>(Sign | 2 <sup>-1</sup> | 2-2 | 2-3             | 2-4             | 2.5             | _   | 2-7 | 2-8 |      |                  |      |      |                  |                   |     |

|-------------------------------------------------------------------------------------------------------------------------|------------|--------------------|--------------------------|-------------------------------|------------------|--------------|------------------|------------------|--------|------|--------------------------------|-----------------|-----|-----------------|-----------------|-----------------|-----|-----|-----|------|------------------|------|------|------------------|-------------------|-----|

| 5 14 13<br>15 <sub>2</sub> 14 <sub>2</sub> 13 <sub>4</sub>                                                              | 12 11 1    | 0 9                | X <sub>IN</sub>          | l<br>7 6                      | 5                | Inte         | ge               | r T              |        |      | (Sign                          | )               |     |                 |                 |                 | 2-6 |     |     | 2-9  | 2 <sup>-10</sup> | 2-11 | 2-12 | 2 <sup>-13</sup> | 2 <sup>-1.4</sup> | 2-1 |

| 5 14 13<br>15 <sub>2</sub> 14 <sub>2</sub> 13 <sub>4</sub>                                                              |            |                    | 8                        | 7 6                           | 5                | 4            |                  |                  | wo'    | s Co | _                              |                 | ent | in              | put             |                 |     | v   |     |      |                  |      |      |                  |                   |     |

| 15 214 213 2                                                                                                            |            |                    | 8                        | 7 6                           | 5                | 4            |                  |                  | wo'    | s Co | ompk                           | m               | ent | In              | put             |                 |     | v   |     |      |                  |      |      |                  |                   |     |

| 15 214 213 2                                                                                                            |            |                    | 8                        | 7 6                           |                  |              | 3                |                  |        |      |                                |                 |     |                 |                 |                 |     | v   |     |      |                  |      |      |                  |                   |     |

| 15 214 213 2                                                                                                            |            |                    |                          |                               |                  |              | 3                |                  |        |      |                                |                 |     |                 |                 |                 |     | 7   | iN  |      |                  |      |      |                  |                   |     |

|                                                                                                                         | 212 211 21 | 10 29              | 28 2                     | 2 <sup>7</sup> 2 <sup>8</sup> | 25               | -            |                  | 2                | 1      | 0    | 15                             | 14              | 13  | 12              | 11              | 10              | 9   | 8   | 7   | 6    | 5                | 4    | 3    | 2                | 1                 | 0   |

| gn)                                                                                                                     |            |                    |                          |                               |                  | 24           | 23               | 22               | 21     | 20   | -2 <sup>15</sup>               | 214             | 213 | 2 <sup>12</sup> | 2 <sup>11</sup> | 2 <sup>10</sup> | 29  | 28  | 27  | 26   | 25               | 24   | 23   | 22               | 21                | 20  |

|                                                                                                                         |            |                    |                          |                               |                  |              |                  |                  |        |      | (Sign)                         |                 |     |                 |                 |                 |     |     |     |      |                  |      |      |                  |                   |     |

|                                                                                                                         |            |                    |                          |                               |                  |              | Un               | sig              | ned    | Fra  | ctior                          | ai              | Inp | ut              |                 |                 |     |     |     |      |                  |      |      |                  |                   |     |

|                                                                                                                         |            |                    | XIN                      | ı                             |                  |              |                  |                  |        |      |                                |                 |     |                 |                 |                 |     | Y   | IN  |      |                  |      |      |                  |                   |     |

| 5 14 13                                                                                                                 | 12 11 1    | 0 9                | 8                        | 7 6                           | 5                | 4            | 3                | 2                | 1      | 0    | 15                             | 14              | 13  | 12              | 11              | 10              | 9   | 8   | 7   | 6    | 5                | 4    | 3    | 2                | 1                 | 0   |

| -1 2 <sup>-2</sup> 2 <sup>-3</sup>                                                                                      | 2-4 2-5 2  | -6 <sub>2</sub> -7 | 2-8 2                    | 9 2-10                        | 2-11             | 2-12         | 2-13             | 2-14             | 2-15   | 2-16 | 2-1                            | 2-2             | 2-3 | 2-4             | 2-5             | 2 <sup>-6</sup> | 2.7 | 2-8 | 2-9 | 2-10 | 2-11             | 2-12 | 2-13 | 2-14             | 2-15              | 2-1 |

|                                                                                                                         |            |                    |                          |                               |                  |              | U                | insi             | igne   | d In | tege                           | r le            | npu | t               |                 |                 |     |     |     |      |                  |      |      |                  |                   |     |

|                                                                                                                         |            |                    | XIN                      | •                             |                  |              |                  |                  |        |      |                                |                 |     |                 |                 |                 |     | Y   | IN  |      |                  |      |      |                  |                   |     |

| 5 14 13                                                                                                                 | 12 11 1    | 0 9                | 8                        | 7 6                           | 5                | 4            | 3                | 2                | 1      | 0    | 15                             | 14              | 13  | 12              | 11              | 10              | 9   | 8   | 7   | 6    | 5                | 4    | 3    | 2                | 1                 | 0   |

| 15 214 213                                                                                                              | 212 211 2  | 10 <sub>2</sub> 9  | 28 3                     | 2 <sup>7</sup> 2 <sup>6</sup> | 2 <sup>5</sup>   | 24           | 23               | 22               | 21     | 20   | 215                            | 214             | 213 | 2 <sup>12</sup> | 211             | 210             | 28  | 28  | 27  | 26   | 25               | 24   | 29   | 22               | 21                | 20  |

|                                                                                                                         |            |                    |                          |                               |                  |              |                  |                  |        |      |                                |                 |     |                 |                 |                 |     |     |     |      |                  |      |      |                  |                   |     |

# Am29510/L510 OUTPUT FORMATS

# Two's Complement Fractional Output

| ХТР                                              | MSP                                                                    | LSP                                                                             |

|--------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| 34 33 32                                         | 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16                        | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0                                           |

| -24 23 22                                        | 21 20 2-1 2-2 2-3 2-4 2-5 2-6 2-7 2-8 2-9 2-10 2-11 2-12 2-13 2-14     | 2-15 2-16 2-17 2-18 2-19 2-20 2-21 2-22 2-23 2-24 2-25 2-26 2-27 2-28 2-29 2-30 |

| (Sign)                                           |                                                                        |                                                                                 |

|                                                  | Two's Complemen                                                        | t Integer Output                                                                |

| XTP                                              | MSP                                                                    | LSP                                                                             |

| 34 33 32                                         | 31 30 29 28 27 28 25 24 23 22 21 20 19 18                              | 3 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0                                   |

| -2 <sup>34</sup> 2 <sup>33</sup> 2 <sup>32</sup> | 231 230 229 228 227 228 225 224 223 222 221 220 219 21                 | 8 217 216 215 214 213 212 211 210 29 28 27 26 25 24 23 22 21 20                 |

| (Sign)                                           |                                                                        |                                                                                 |

|                                                  | Unsigned Fract                                                         | tional Output                                                                   |

| XTP                                              | MSP                                                                    | LSP                                                                             |

| 34 33 32                                         | 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16                        | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0                                           |

| 22 21 20                                         | 2-1 2-2 2-3 2-4 2-5 2-6 2-7 2-8 2-9 2-10 2-11 2-12 2-13 2-14 2-15 2-16 |                                                                                 |

|                                                  | Unsigned Inte                                                          | oger Output                                                                     |

| ХТР                                              | MSP                                                                    | LSP                                                                             |

| 34 33 32                                         | 31 30 29 28 27 26 25 24 23 22 21 20 19 18                              | 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0                                     |

| 234 233 232                                      | 231 230 229 228 227 226 225 224 223 222 221 220 219 216                | 3 217 216 215 214 213 212 211 210 29 28 27 26 25 24 23 22 21 20                 |

#### **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature                | -65 to +150°C             |

|------------------------------------|---------------------------|

| Temperature Under Bias-TC          | -55 to +125°C             |

| Supply Voltage to Ground Potential |                           |

| Continuous                         | 0.5 to +7.0V              |

| DC Voltage Applied to Outputs For  |                           |

| High Output State0.5               | √ to +V <sub>CC</sub> max |

| DC Input Voltage                   | 0.5 to +5.5V              |

| DC Output Current, Into Outputs    | 30mA                      |

| DC Input Current                   | -30 to +5.0mA             |

|                                    |                           |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

| Commercial (C) Devices            |                                  |

|-----------------------------------|----------------------------------|

| Temperature                       |                                  |

| DIPs                              | TA = 0 to +70°C                  |

| Chip Carriers                     |                                  |

| Supply Voltage                    | 4.75V to 5.25V                   |

| Military (M) Devices              |                                  |

| Temperature                       | T <sub>C</sub> = -55°C to +125°C |

| Supply Voltage                    | 4.5V to 5.5V                     |

| Operating ranges define those lim | its over which the function-     |

| ality of the device is guaranteed |                                  |

#### DC CHARACTERISTICS over operating range unless otherwise specified Am29510

| Parameters | Description                          | Te                                                                            | at Conditions            | (Note 1)                                | Min | Typ<br>(Note 2) | Max   | Units |

|------------|--------------------------------------|-------------------------------------------------------------------------------|--------------------------|-----------------------------------------|-----|-----------------|-------|-------|

| VOH        | Output HIGH Voltage                  | V <sub>CC</sub> = MIN<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | I <sub>OH</sub> = -0.4mA |                                         | 2.4 |                 |       | Volts |

| VOL        | Output LOW Voltage                   | V <sub>CC</sub> = MIN<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | 1 <sub>OL</sub> = 4.0mA  |                                         | 7   |                 | .5    | Volts |

| VIH        | Input HIGH Level                     | Guaranteed input log                                                          | ical HIGH volta          | ge for all inpate.                      | 21  | d38m            |       | Volts |

| VIL        | Input LOW level                      | Guaranteed input log                                                          | gical LOW voltag         | pe for all inputs                       | 134 |                 | .8    | Volts |

| VI         | Input Clamp Voltage                  | VCC = MIN, IN = -10                                                           | 8mA 🧃                    | h_ to have                              |     |                 | - 1.5 | Volts |

| ИL         | Input LOW Current                    | VCC = MAX, VIN = 0.                                                           | 4V                       | 4.4                                     |     |                 | -0.4  | mA    |

| hн         | Input HIGH Current                   | VCC = MAX, VIN 3-4                                                            | 4V 1                     |                                         |     |                 | 75    | μA    |

|            | input HiGH Current                   | VCC = MAX.                                                                    |                          | <b>₩</b>                                |     |                 | 1     | mA    |

| юхн        | Off State (High Impedance)           |                                                                               | AM B                     | V <sub>O</sub> = 2.4V                   |     |                 | 25    |       |

| lozi       | Output Current                       | VO MAX Pr                                                                     | UCT IF                   | V <sub>O</sub> = 0.4V                   |     |                 | - 25  | μА    |

| Isc        | Output Short Circuit Cut at (Note 3) | AX Y                                                                          | Product                  | V <sub>O</sub> = 0V                     | -3  |                 | -30   | mA    |

|            |                                      | COMIL and MIL                                                                 |                          | T <sub>A</sub> = 25°C                   |     | 750             |       |       |

|            |                                      |                                                                               | _                        | T <sub>A</sub> = 0 to +70°C<br>(Note 4) |     |                 | 900   |       |

| Icc        | Postpoly Commit                      | COM'L Only V <sub>CC</sub> = 1                                                | Max                      | T <sub>A</sub> = +70°C<br>(Note 4)      |     |                 | 725   | mA    |

|            |                                      |                                                                               |                          | T <sub>CC</sub> = -55 to +125°C         |     |                 | 1000  | ]     |

|            |                                      | MIL Only Vcc - Max                                                            | ·                        | T <sub>CC</sub> = + 125°C               |     |                 | 750   |       |

Notes: 1. For conditions shown as MIN or MAX, use the appropriate value specified under Operating Ranges for the applicable device type.

2. Typical limits are at V<sub>C</sub>C = 5.0V, 25°C ambient and maximum loading.

3. Not more than one output should be shorted at a time Duration of the short circuit test should not exceed one second.

4. Chip Carriers: T<sub>A</sub> = 85°C.

#### DC CHARACTERISTICS over operating range unless otherwise specified Am29L510

| Parameters       | Description              |                                                                               | Test Condit    | ons (Note 1)                                     | Min | <b>Typ</b><br>(N 2) | Max  | Units |

|------------------|--------------------------|-------------------------------------------------------------------------------|----------------|--------------------------------------------------|-----|---------------------|------|-------|

| Vон              | Output HIGH Voltage      | V <sub>CC</sub> = MIN<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> |                | I <sub>OH</sub> = -0.4mA                         |     |                     |      | Volts |

| VOL              | Output LOW Voltage       | V <sub>CC</sub> = MIN<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> |                | I <sub>OL</sub> = 4.0mA                          | A   | 7                   | .5   | Volts |

| V <sub>IH</sub>  | Input HIGH Level         | Guaranteed inpu                                                               | t logical HIGH | voltage for all inputs                           | 2.0 |                     |      | Volts |

| VIL              | Input LOW Level          | Guaranteed inpu                                                               |                |                                                  | *** |                     | .8   | Volts |

| V <sub>i</sub>   | Input Clamp Voltage      | VCC = MIN, IN =                                                               | <b>g</b> ¶@mA  |                                                  |     |                     | 1.5  | Volts |

| l <sub>IL</sub>  | Input LOW Current        | VCC = MAX.                                                                    | 44 44          | WA TO                                            |     |                     | -0.4 | mA    |

| I <sub>IH</sub>  | Input HIGH Current       | V <sub>Q</sub> MAX,                                                           | V() 1          | •                                                |     |                     | 75   | μА    |

| 11               | Input HIGH Current       | VCC MAX, VI                                                                   | 5.             |                                                  |     |                     | 1    | mA    |

| ЮZН              | Off State (High Impedant | Vcc -                                                                         | Product        | V <sub>O</sub> = 2.4V                            |     |                     | 25   | μΑ    |

| loz <sub>L</sub> | Output Current           | 700                                                                           |                | V <sub>O</sub> = 0.4V                            |     |                     | -25  | μ.,   |

|                  | Output Chart Charter     | V <sub>CC</sub> = MAX                                                         | Y              | V <sub>O</sub> = 0V                              | -3  |                     | -30  | mA.   |

| lsc              | (N 3)                    | ACC - MVV                                                                     | Product        | V <sub>O</sub> = 0V                              | -3  |                     | -30  | 111/2 |

|                  |                          | COM'L and MIL                                                                 |                | T <sub>A</sub> = 25°C                            |     | 330                 |      |       |

|                  |                          | COM'L Only Vo                                                                 | a = 14av       | T <sub>A</sub> = 0 to +70°C<br>(Note 4)          |     |                     | 450  |       |

| l loc            | Power Supply Current     | COM E Only VO                                                                 | C - Max        | T <sub>A</sub> = +70°C<br>(Note 4)               |     |                     | 350  | mA    |

|                  |                          | 6                                                                             | ***            | $T_{CC} = -55 \text{ to } + 125^{\circ}\text{C}$ |     |                     | 535  | 1     |

|                  |                          | MIL Only V <sub>CC</sub> =                                                    | Max            | T <sub>CC</sub> = + 125°C                        |     |                     | 375  |       |

Notes: 1. For conditions shown as MIN or MAX, use the appropriate value specified under Operating Flanges for the applicable device type.

2. Typical limits are at V<sub>CC</sub> = 5.0V, 25°C ambient and maximum loading.

3. Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

4. Chip Carriers, T<sub>C</sub> = 85°C.

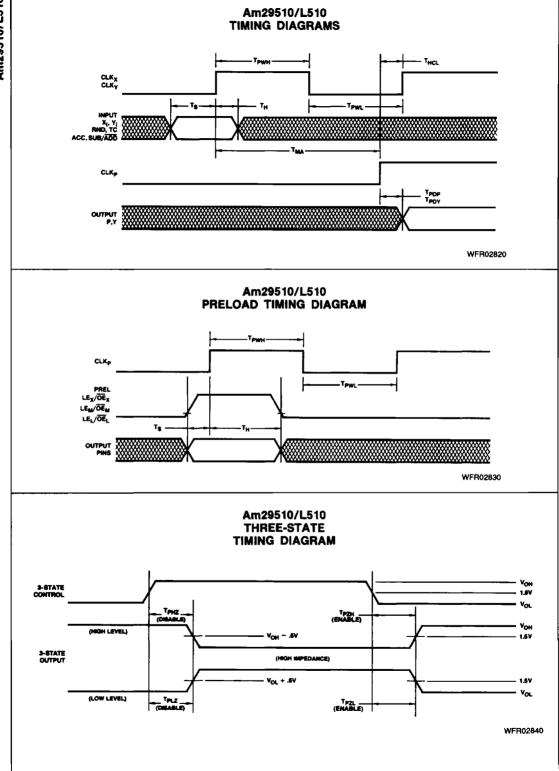

# SWITCHING CHARACTERISTICS over operating range unless otherwise specified

|                  |                                                               |           |            |          | COMM | ERCIAL | MILI | TARY |       |

|------------------|---------------------------------------------------------------|-----------|------------|----------|------|--------|------|------|-------|

|                  |                                                               |           | Test       | Тур      | 29   | 510    | 29   | 510  | ]     |

| Parameters       | Description                                                   | on        | Conditions | (Note 1) | Min  | Max    | Min  | Max  | Units |

| <sup>t</sup> MA  | Multiply Accumulate T                                         | ime       |            | 50       |      | 80     |      | 90   | ns    |

| ts               | X <sub>i</sub> , Y <sub>i</sub> , RND, TC, ACC<br>Set-up Time | SUB/ADD   |            | 12       | 25   |        | 30   |      | ns    |

| ч                | X <sub>i</sub> , Y <sub>i</sub> , RND, TC, ACC<br>Hold Time   | SUB/ADD   |            | 0        | 5    |        | 5    |      | ns    |

| ts               | PREL Setup Time                                               |           | 1          | 10       | 25   |        | 30   |      | ns.   |

| ч                | PREL Hold Time                                                |           | 1          | 0        | 0    |        | 2    |      | ns    |

| <sup>1</sup> PWH | Clock Pulse Width High                                        |           | ]          | 10       | 20   |        | 25   |      | ns    |

| <sup>t</sup> PWL | Clock Pulse Width Lo                                          | N         | ]          | 10       | 20   |        | 25   |      | ns    |

| teDe             | Output Clock to P                                             |           |            | 25       |      | 40     |      | 40   | ns    |

| <sup>t</sup> PDY | Output Clock to Y                                             |           |            | 25       |      | 40     |      | 40   | ns    |

| t <sub>PHZ</sub> | LEX/OEX, LEM/OEM                                              | High to Z | ]          | 21       |      | 35     |      | 40   | ns    |

| t <sub>PLZ</sub> | to P, LEL/OEL<br>to Y Disable Time                            | Low to Z  | ]          | 20       |      | 35     |      | 40   | ns    |

| <b>t</b> РZH     | LEX/OEX, LEM/OEM                                              | Z to High | ]          | 28       |      | AND A  |      | 40   | ns    |

| ΨZL              | to P, LE <sub>L</sub> /OE <sub>L</sub><br>to Y Enable Time    | Z to Low  | ]          | 24       |      | TANK.  |      | 40   | ns    |

| tHCL             | Relative Hold Time                                            |           | ]          |          |      |        | 0    |      | ns    |

# SWITCHING CHARACTERISTICS over of rails and gardness otherwise specified\*

|                  |                                                             |           | 1                  |          | COMM | ERCIAL | MILI | TARY |       |

|------------------|-------------------------------------------------------------|-----------|--------------------|----------|------|--------|------|------|-------|

|                  |                                                             |           |                    | Тур      | 291  | _510   | 291  | .510 |       |

| Parameters       | a bearing                                                   | ort.      | Test<br>Conditions | (Note 1) | Min  | Max    | Min  | Max  | Units |

| <sup>t</sup> MA  | Multip cumula                                               | ime .     |                    | 70       |      | 110    |      | 120  | ns    |

| ts               | X <sub>i</sub> , Y <sub>i</sub> , D, TC, ACC<br>Set-up Me   | , SUB/ADD |                    | 20       | 40   |        | 45   |      | ns    |

| t <sub>H</sub>   | X <sub>i</sub> , Y <sub>i</sub> , RND, TC, ACC<br>Hold Time | , SUB/ADD |                    | -3       | 0    |        | 0    |      | กร    |

| ts               | PREL Set-up Time                                            |           | 1                  | 15       | 27   |        | 35   |      | ns    |

| tн               | PREL Hold Time                                              |           | 1                  | -5       | 0    |        | O    |      | na    |

| <sup>t</sup> PWH | Clock Pulse Width Hi                                        | gh        | ]                  | 15       | 25   |        | 30   |      | na    |

| †PWL             | Clock Pulse Width Lo                                        | w         |                    | 15       | 25   |        | 30   |      | ns    |

| <sup>t</sup> PDP | Output Clock to P                                           |           |                    | 35       |      | 45     |      | 50   | ns    |

| <sup>t</sup> PDY | Output Clock to Y                                           |           |                    | 35       |      | 45     |      | 50   | ns    |

| t <sub>PHZ</sub> | LEX/OEX, LEM/OEM                                            | High to Z | ]                  | 24       |      | 35     |      | 40   | ns    |

| t <sub>PLZ</sub> | to P. LEL/ÖEL<br>to Y Disable Time                          | Low to Z  | ]                  | 25       |      | 35     |      | 40   | ns    |

| tpzH             | LEX/OEX, LEM/OEM                                            | Z to High | ]                  | 38       |      | 45     |      | 50   | ns    |

| †PZL             | to P, LE <sub>L</sub> /OE <sub>L</sub><br>to Y Enable Time  | Z to Low  | ]                  | 32       |      | 40     |      | 45   | ns    |

| thCL             | Relative Hold Time                                          |           | 1                  |          | 0    |        | 0    |      | ns    |

Note: 1. Typical limits are  $V_{CC} = 5V$  and  $T_A = 25$ °C.

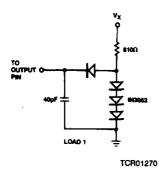

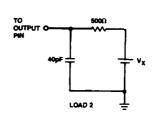

# **SWITCHING TEST CIRCUIT**

#### Normal Load

# Three-State Delay Load

TCR01280

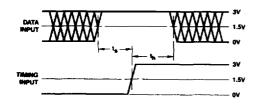

#### SWITCHING TEST WAVEFORMS

| Test                  | V <sub>X</sub> | Output Waveform - Messurement Level |

|-----------------------|----------------|-------------------------------------|

| All t <sub>PD</sub> s | Vcc            | V <sub>OL</sub> 1.5V                |

| t <sub>PHZ</sub>      | 0.0V           | V <sub>OH</sub> 0.5V                |

| t <sub>PLZ</sub>      | 2.6V           | V <sub>OL</sub>                     |

| <sup>‡</sup> РZН      | 0.0 <b>V</b>   | 0.0VVOH                             |

| <sup>t</sup> PZL      | 2.6V           | 2.8V                                |

WFR02810

#### SET-UP AND HOLD TIME

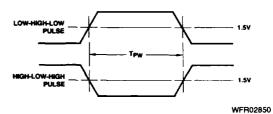

# PULSE WIDTH

WFR02970

- Notes: 1. Diagram shown for HIGH data only. Output transition may be opposite sense.

- 2. Cross hatched area is don't care condition.

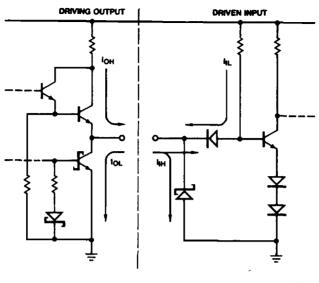

# INPUT/OUTPUT CURRENT INTERFACE CONDITIONS

ICR00490

# RELATED PRODUCTS

| Part No.    | Description                          |

|-------------|--------------------------------------|

| Am29526/527 | High speed Sine function generator   |

| Am29528/529 | High Speed Cosine function generator |

| Am29540     | Programmable FFT address sequencer   |

| Am29520/21  | Multilevel pipeline registers        |