# Multiphase PWM Regulator for IMVP-6.5™ Mobile CPUs and GPUs

#### ISL62882, ISL62882B

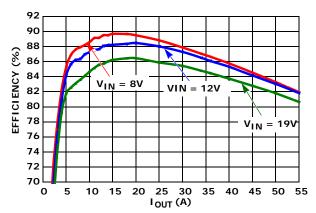

The ISL62882 is a multiphase PWM buck regulator for miroprocessor or graphics processor core power supply. The multiphase buck converter uses interleaved phases to reduce the total output voltage ripple with each phase carrying a portion of the total load current, providing better system performance, superior thermal management, lower component cost, reduced power dissipation, and smaller implementation area. The ISL62882 uses two integrated gate drivers to provide a complete solution. The PWM modulator is based on Intersil's Robust Ripple Regulator (R<sup>3</sup>) technology™. Compared with traditional modulators, the R<sup>3</sup> modulator commands variable switching frequency during load transients, achieving faster transient response. With the same modulator, the switching frequency is reduced at light load, increasing the regulator efficiency.

The ISL62882 can be configured as CPU or graphics Vcore controller and is fully compliant with IMVP-6.5™ specifications. It responds to PSI# and DPRSLPVR signals by adding or dropping Phase 2, adjusting overcurrent protection threshold accordingly, and entering/exiting diode emulation mode. It reports the regulator output current through the IMON pin. It senses the current by using either discrete resistor or inductor DCR whose variation over temperature can be thermally compensated by a single NTC thermistor. It uses differential remote voltage sensing to accurately regulate the processor die voltage. The unique split LGATE function further increases light load efficiency. The adaptive body diode conduction time reduction function minimizes the body diode conduction loss in diode emulation mode. User-selectable overshoot reduction function offers an option to aggressively reduce the output capacitors as well as the option to disable it for users concerned about increased system thermal stress. The ISL62882 offers the FB2 function to optimize 1-phase performance.

The ISL62882B has the same functions as the ISL62882, but comes in a different package.

1

#### **Features**

- Programmable 1- or 2-Phase CPU Mode Operation or 1-Phase GPU Mode Operation

- Precision Multiphase Core Voltage Regulation

- 0.5% System Accuracy Over-Temperature

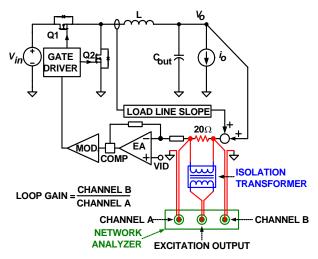

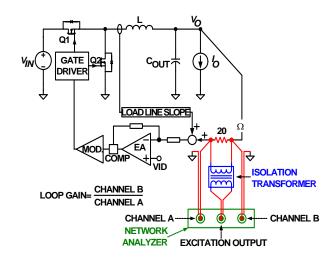

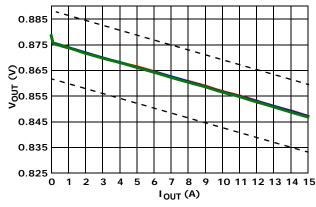

- Enhanced Load Line Accuracy

- · Microprocessor Voltage Identification Input

- 7-Bit VID Input, 0V to 1.500V in 12.5mV Steps

- Supports VID Changes On-The-Fly

- Supports Multiple Current Sensing Methods

- Lossless Inductor DCR Current Sensing

- Precision Resistor Current Sensing

- Supports PSI# and DPRSLPVR modes

- Superior Noise Immunity and Transient Response

- · Current Monitor and Thermal Monitor

- Differential Remote Voltage Sensing

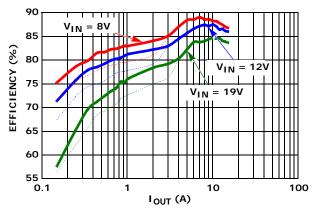

- · High Efficiency Across Entire Load Range

- Programmable 1- or 2-Phase Operation

- Two Integrated Gate Drivers

- Excellent Dynamic Current Balance Between Phases

- Split LGATE1 Drivers Increases Light Load Efficiency

- FB2 Function Optimizes 1-Phase Mode Performance

- Adaptive Body Diode Conduction Time Reduction

- User-selectable Overshoot Reduction Function

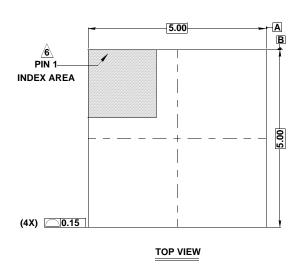

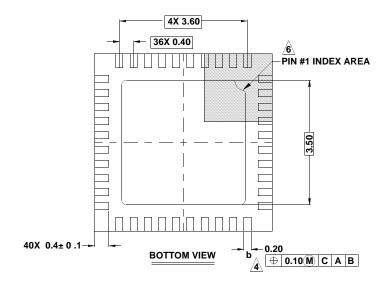

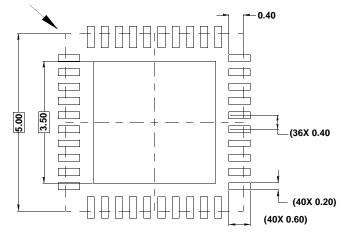

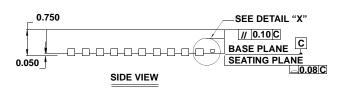

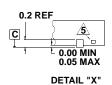

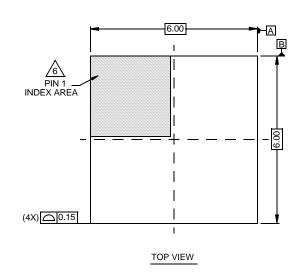

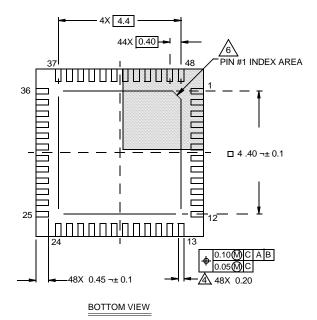

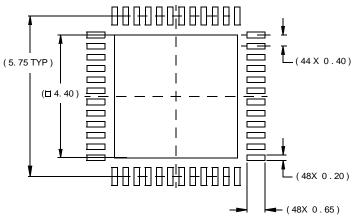

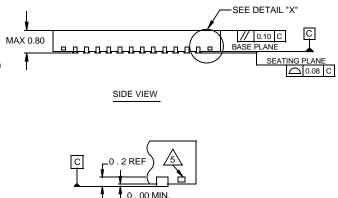

Small Footprint 40 Ld 5y5 or 48 Ld 6y6 TOEN

- Small Footprint 40 Ld 5x5 or 48 Ld 6x6 TQFN Packages

- · Pb-Free (RoHS Compliant)

### **Applications**

- · Notebook Core Voltage Regulator

- Notebook GPU Voltage Regulator

### **Ordering Information**

| PART NUMBER<br>(Notes 1, 2, 3) | PART MARKING | TEMP. RANGE<br>(°C) | PACKAGE<br>(Pb-Free) | PKG.<br>DWG. # |

|--------------------------------|--------------|---------------------|----------------------|----------------|

| ISL62882IRTZ                   | 62882 IRTZ   | -40 to +100         | 40 Ld 5x5 TQFN       | L40.5x5        |

| ISL62882HRTZ                   | 62882 HRTZ   | -10 to +100         | 40 Ld 5x5 TQFN       | L40.5x5        |

| ISL62882BHRTZ                  | 62882 BHRTZ  | -10 to +100         | 48 Ld 6x6 TQFN       | L48.6x6        |

#### NOTES:

- 1. Add "-T\*" suffix for tape and reel. Please refer to TB347 for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level (MSL), please see device information page for <u>ISL62882</u>, <u>ISL62882B</u>. For more information on MSL please see techbrief <u>TB363</u>.

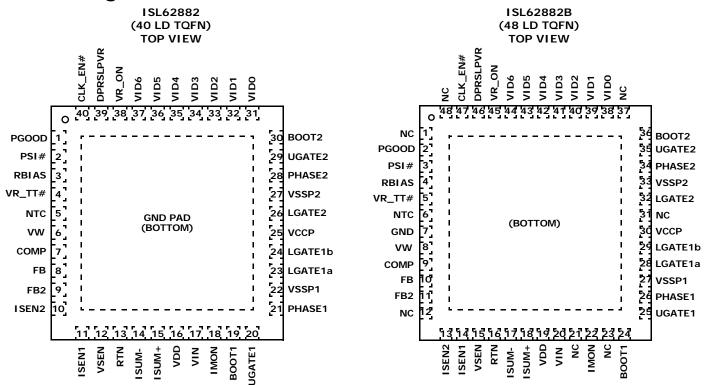

### **Pin Configurations**

### **Functional Pin Descriptions**

| ISL62882 | ISL62882B | SYMBOL          | DESCRIPTION                                                                                                                                                                                                                                                                                                                  |

|----------|-----------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -        | 7         | GND             | Signal common of the IC. Unless otherwise stated, signals are referenced to the GND pin.                                                                                                                                                                                                                                     |

| 1        | 2         | PGOOD           | Power-Good open-drain output indicating when the regulator is able to supply regulated voltage. Pull-up externally with a $680\Omega$ resistor to VCCP or $1.9k\Omega$ to $3.3V$ .                                                                                                                                           |

| 2        | 3         | PSI#            | Low load current indicator input. When asserted low, indicates a reduced load current condition.                                                                                                                                                                                                                             |

| 3        | 4         | RBIAS           | A resistor to GND sets internal current reference. Use 147k $\Omega$ or 47k $\Omega$ . The choice of Rbias value, together with the ISEN2 pin configuration and the external resistance from the COMP pin to GND, programs the controller to enable/disable the overshoot reduction function and to select the CPU/GPU mode. |

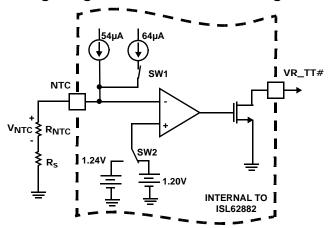

| 4        | 5         | VR_TT#          | Thermal overload output indicator.                                                                                                                                                                                                                                                                                           |

| 5        | 6         | NTC             | Thermistor input to VR_TT# circuit.                                                                                                                                                                                                                                                                                          |

| 6        | 8         | VW              | A resistor from this pin to COMP programs the switching frequency (8k $\Omega$ gives approximately 300kHz).                                                                                                                                                                                                                  |

| 7        | 9         | COMP            | This pin is the output of the error amplifier. Also, a resistor across this pin and GND adjusts the overcurrent threshold.                                                                                                                                                                                                   |

| 8        | 10        | FB              | This pin is the inverting input of the error amplifier.                                                                                                                                                                                                                                                                      |

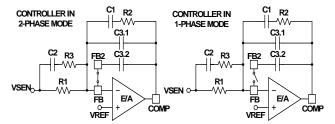

| 9        | 11        | FB2             | There is a switch between the FB2 pin and the FB pin. The switch is on in 2-phase mode and is off in 1-phase mode. The components connecting to FB2 are used to adjust the compensation in 1-phase mode to achieve optimum performance.                                                                                      |

| 10       | 13        | ISEN2           | Individual current sensing for Phase 2. When ISEN2 is pulled to 5V VDD, the controller will disable Phase 2.                                                                                                                                                                                                                 |

| 11       | 14        | ISEN1           | Individual current sensing for phase 1.                                                                                                                                                                                                                                                                                      |

| 12       | 15        | VSEN            | Remote core voltage sense input. Connect to microprocessor die.                                                                                                                                                                                                                                                              |

| 13       | 16        | RTN             | Remote voltage sensing return. Connect to ground at microprocessor die.                                                                                                                                                                                                                                                      |

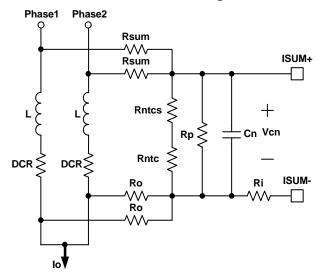

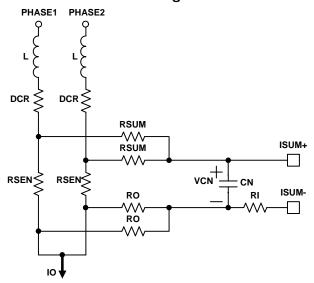

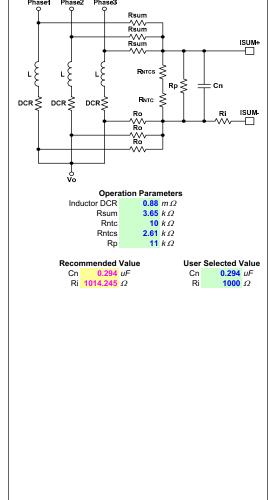

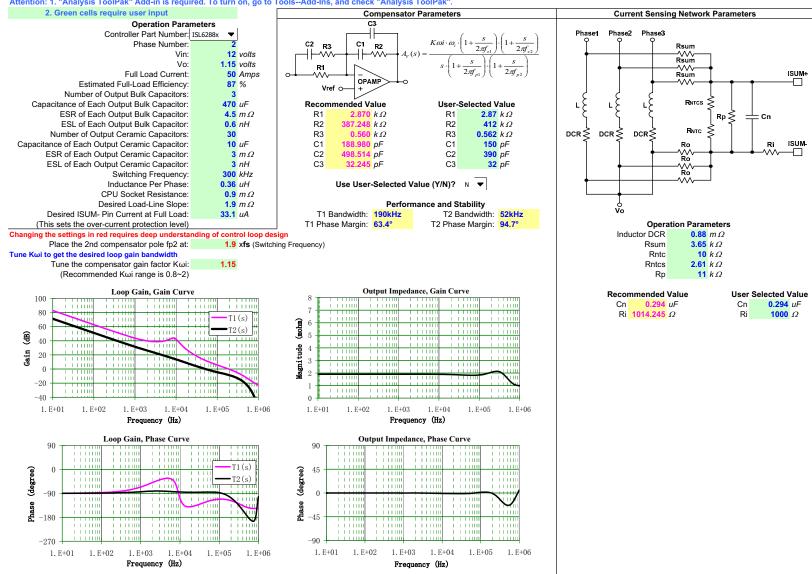

| 14, 15   | 17, 18    | ISUM- and ISUM+ | Droop current sense input.                                                                                                                                                                                                                                                                                                   |

| 16       | 19        | VDD             | 5V bias power.                                                                                                                                                                                                                                                                                                               |

| 17       | 20        | VIN             | Battery supply voltage, used for feed-forward.                                                                                                                                                                                                                                                                               |

| 18       | 22        | IMON            | An analog output. IMON outputs a current proportional to the regulator output current.                                                                                                                                                                                                                                       |

| 19       | 24        | BOOT1           | Connect an MLCC capacitor across the BOOT1 and the PHASE1 pins. The boot capacitor is charged through an internal boot diode connected from the VCCP pin to the BOOT1 pin, each time the PHASE1 pin drops below VCCP minus the voltage dropped across the internal boot diode.                                               |

| 20       | 25        | UGATE1          | Output of the Phase-1 high-side MOSFET gate driver. Connect the UGATE1 pin to the gate of the Phase-1 high-side MOSFET.                                                                                                                                                                                                      |

| 21       | 26        | PHASE1          | Current return path for the Phase-1 high-side MOSFET gate driver. Connect the PHASE1 pin to the node consisting of the high-side MOSFET source, the low-side MOSFET drain, and the output inductor of Phase-1.                                                                                                               |

| 22       | 27        | VSSP1           | Current return path for the Phase-1 low-side MOSFET gate driver. Connect the VSSP1 pin to the source of the Phase-1 low-side MOSFET through a low impedance path, preferably in parallel with the traces connecting the LGATE1a and the LGATE1b pins to the gates of the Phase-1 low-side MOSFETs.                           |

| 23       | 28        | LGATE1a         | Output of the Phase-1 low-side MOSFET gate driver that is always active. Connect the LGATE1a pin to the gate of the Phase-1 low-side MOSFET that is active all the time.                                                                                                                                                     |

### ISL62882, ISL62882B

### Functional Pin Descriptions (Continued)

| ISL62882   | ISL62882B  | SYMBOL         | DESCRIPTION                                                                                                                                                                                                                                                                             |

|------------|------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24         | 29         | LGATE1b        | Another output of the Phase-1 low-side MOSFET gate driver. This gate driver will be pulled low when the DPRSLPVR pin logic is high. Connect the LGATE1b pin to the gate of the Phase-1 low-side MOSFET that is idle in deeper sleep mode.                                               |

| -          | -          | LGATE1         | Output of the Phase-1 low-side MOSFET gate driver. Connect the LGATE1 pin to the gate of the Phase-1 low-side MOSFET.                                                                                                                                                                   |

| 25         | 30         | VCCP           | Input voltage bias for the internal gate drivers. Connect +5V to the VCCP pin. Decouple with at least 1µF of an MLCC capacitor to VSSP1 and VSSP2 pins respectively.                                                                                                                    |

| 26         | 32         | LGATE2         | Output of the Phase-2 low-side MOSFET gate driver. Connect the LGATE2 pin to the gate of the Phase-2 low-side MOSFET.                                                                                                                                                                   |

| 27         | 33         | VSSP2          | Current return path for the Phase-2 converter low-side MOSFET gate driver. Connect the VSSP2 pin to the source of the Phase-2 low-side MOSFET through a low impedance path, preferably in parallel with the trace connecting the LGATE2 pin to the gate of the Phase-2 low-side MOSFET. |

| 28         | 34         | PHASE2         | Current return path for the Phase-2 high-side MOSFET gate driver. Connect the PHASE2 pin to the node consisting of the high-side MOSFET source, the low-side MOSFET drain, and the output inductor of Phase-2.                                                                          |

| 29         | 35         | UGATE2         | Output of the Phase-2 high-side MOSFET gate driver. Connect the UGATE2 pin to the gate of the Phase-2 high-side MOSFET.                                                                                                                                                                 |

| 30         | 36         | BOOT2          | Connect an MLCC capacitor across the BOOT2 and the PHASE2 pins. The boot capacitor is charged through an internal boot diode connected from the VCCP pin to the BOOT2 pin, each time the PHASE2 pin drops below VCCP minus the voltage dropped across the internal boot diode.          |

| 31 thru 37 | 38 thru 44 | VID0 thru VID6 | VID input with VID0 = LSB and VID6 = MSB.                                                                                                                                                                                                                                               |

| 38         | 45         | VR_ON          | Voltage regulator enable input. A high level logic signal on this pin enables the regulator.                                                                                                                                                                                            |

| 39         | 46         | DPRSLPVR       | Deeper sleep enable signal. A high level logic signal on this pin indicates that the microprocessor is in deeper sleep mode.                                                                                                                                                            |

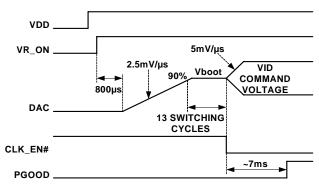

| 40         | 47         | CLK_EN#        | Open drain output to enable system PLL clock. It goes low 13 switching cycles after Vcore is within 10% of Vboot.                                                                                                                                                                       |

| -          | 48         | NC             | No connect.                                                                                                                                                                                                                                                                             |

| pad        | pad        | ВОТТОМ         | The bottom pad of ISL62882B is electrically connected to the GND pin inside the IC.                                                                                                                                                                                                     |

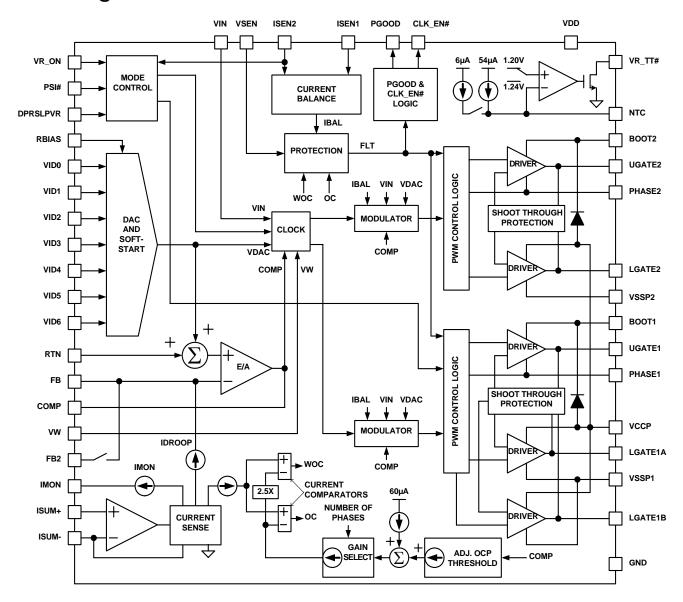

### **Block Diagram**

#### **Absolute Maximum Ratings**

| Supply Voltage, VDD0.3V to +7V                    |

|---------------------------------------------------|

| Battery Voltage, VIN+28V                          |

| Boot Voltage (BOOT)0.3V to +33V                   |

| Boot to Phase Voltage (BOOT-PHASE)0.3V to +7V(DC) |

| 0.3V to +9V(<10ns)                                |

| Phase Voltage (PHASE)7V (<20ns Pulse Width, 10µJ) |

| UGATE Voltage (UGATE) PHASE-0.3V (DC) to BOOT     |

| PHASE-5V (<20ns Pulse Width, 10μJ) to BOOT        |

| LGATE1a and 1b and LGATE2 Voltage                 |

| 0.3V (DC) to VDD+0.3V                             |

| LGATE1a and 1b                                    |

| 2.5V (<20ns Pulse Width, 2.5μJ) to VDD+0.3V       |

| LGATE1a and 1b                                    |

| 2.5V (<20ns Pulse Width, 5μJ) to VDD+0.3V         |

| All Other Pins0.3V to (VDD +0.3V)                 |

| Open Drain Outputs, PGOOD, VR_TT#,                |

| CLK_EN#0.3V to +7V                                |

#### **Thermal Information**

| Thermal Resistance (Typical)       | $\theta_{JA}$ (°C/W) | $\theta_{JC}$ (°C/W) |

|------------------------------------|----------------------|----------------------|

| 40 Ld TQFN Package (Notes 4, 5).   | . 32                 | 3                    |

| 48 Ld TQFN Package (Notes 4, 5).   | . 29                 | 2                    |

| Maximum Junction Temperature       |                      | +150°C               |

| Maximum Storage Temperature Rang   | e65°                 | C to +150°C          |

| Maximum Junction Temperature (Plas | tic Package          | ) +150°C             |

| Storage Temperature Range          | 65°                  | C to +150°C          |

| Pb-Free Reflow Profile             |                      | ee link below        |

| http://www.intersil.com/pbfree/Pb- | FreeReflow.          | <u>asp</u>           |

#### **Recommended Operating Conditions**

| Supply Voltage, VDD         +5V ±5%           Battery Voltage, VIN         +4.5V to 25V |

|-----------------------------------------------------------------------------------------|

| Ambient Temperature                                                                     |

| ISL62882HRTZ, ISL62882BHRTZ10°C to +100°C                                               |

| ISL62882IRTZ40°C to +100°C                                                              |

| Junction Temperature                                                                    |

| ISL62882HRTZ, ISL62882BHRTZ10°C to +125°C                                               |

| ISL62882IRTZ40°C to +125°C                                                              |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

- 4. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 5. For  $\theta_{1C}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

**Electrical Specifications** Operating Conditions: VDD = 5V,  $T_A = -40$ °C to +100°C,  $f_{SW} = 300$ kHz, unless otherwise noted. Boldface limits apply over the operating temperature range, -40°C to +100°C.

| PARAMETER                        | SYMBOL                    | TEST CONDITIONS                         | MIN<br>(Note 6) | TYP   | MAX<br>(Note 6) | UNITS |

|----------------------------------|---------------------------|-----------------------------------------|-----------------|-------|-----------------|-------|

| INPUT POWER SUPPLY               |                           |                                         | •               | '     | 1               |       |

| +5V Supply Current               | I <sub>VDD</sub>          | VR_ON = 3.3V                            |                 | 4     | 4.6             | mA    |

|                                  |                           | VR_ON = OV                              |                 |       | 1               | μΑ    |

| Battery Supply Current           | I <sub>VIN</sub>          | VR_ON = 0V                              |                 |       | 1               | μΑ    |

| V <sub>IN</sub> Input Resistance | R <sub>VIN</sub>          | VR_ON = 3.3V                            |                 | 900   |                 | kΩ    |

| Power-On-Reset Threshold         | POR <sub>r</sub>          | V <sub>DD</sub> rising                  |                 | 4.35  | 4.5             | V     |

|                                  | POR <sub>f</sub>          | V <sub>DD</sub> falling                 | 4.00            | 4.15  |                 | V     |

| SYSTEM AND REFERENCES            |                           |                                         | II.             | I     | I               |       |

| System Accuracy                  | HRTZ<br>%Error            | No load; closed loop, active mode range | 0.5             |       | . 0. 5          | %     |

|                                  | (V <sub>CC_CORE</sub> )   | VID = 0.75V to 1.50V,                   | -0.5            |       | +0.5            |       |

|                                  |                           | VID = 0.5V to 0.7375V                   | -8              |       | +8              | mV    |

|                                  |                           | VID = 0.3V to 0.4875V                   | -15             |       | +15             | mV    |

|                                  | IRTZ<br>%Error            | No load; closed loop, active mode range |                 |       |                 | 0.4   |

|                                  | (V <sub>CC_CORE</sub> )   | VID = 0.75V to 1.50V                    | -0.8            |       | +0.8            | %     |

|                                  |                           | VID = 0.5V to 0.7375V                   | -10             |       | +10             | mV    |

|                                  |                           | VID = 0.3V to 0.4875V                   | -18             |       | +18             | mV    |

| V <sub>BOOT</sub>                |                           |                                         | 1.0945          | 1.100 | 1.1055          | V     |

| Maximum Output Voltage           | V <sub>CC_CORE(max)</sub> | VID = [0000000]                         |                 | 1.500 |                 | V     |

| Minimum Output Voltage           | V <sub>CC_CORE(min)</sub> | VID = [1100000]                         |                 | 0.300 |                 | V     |

| R <sub>BIAS</sub> Voltage        |                           | $R_{BIAS} = 147 \mathrm{k}\Omega$       | 1.45            | 1.47  | 1.49            | V     |

### ISL62882, ISL62882B

Electrical Specifications Operating Conditions: VDD = 5V,  $T_A = -40^{\circ}\text{C}$  to  $+100^{\circ}\text{C}$ ,  $f_{SW} = 300\text{kHz}$ , unless otherwise noted. Boldface limits apply over the operating temperature range,  $-40^{\circ}\text{C}$  to  $+100^{\circ}\text{C}$ . (Continued)

| PARAMETER                               | PARAMETER SYMBOL TEST CONDITIONS |                                                           | MIN<br>(Note 6) | TYP  | MAX<br>(Note 6) | UNITS |

|-----------------------------------------|----------------------------------|-----------------------------------------------------------|-----------------|------|-----------------|-------|

| CHANNEL FREQUENCY                       |                                  |                                                           |                 |      |                 |       |

| Nominal Channel Frequency               | f <sub>SW(nom)</sub>             | Rfset = $7k\Omega$ , 2-channel operation, $V_{COMP} = 1V$ | 285             | 300  | 315             | kHz   |

| Adjustment Range                        |                                  |                                                           | 200             |      | 500             | kHz   |

| AMPLIFIERS                              |                                  | '                                                         | II.             | 1    | II.             | I.    |

| Current-Sense Amplifier Input<br>Offset |                                  | I <sub>FB</sub> = 0A                                      | -0.15           |      | +0.15           | mV    |

| Error Amp DC Gain                       | A <sub>VO</sub>                  |                                                           |                 | 90   |                 | dB    |

| Error Amp Gain-Bandwidth<br>Product     | GBW                              | C <sub>L</sub> = 20pF                                     |                 | 18   |                 | MHz   |

| ISEN                                    |                                  |                                                           |                 | •    |                 |       |

| Imbalance Voltage                       |                                  | Maximum of ISENs - Minimum of ISENs                       |                 |      | 1               | mV    |

| Input Bias Current                      |                                  |                                                           |                 | 20   |                 | nA    |

| POWER-GOOD AND PROTECTION               | ON MONITOR                       | s                                                         |                 |      |                 |       |

| PGOOD Low Voltage                       | V <sub>OL</sub>                  | I <sub>PGOOD</sub> = 4mA                                  |                 | 0.26 | 0.4             | V     |

| PGOOD Leakage Current                   | I <sub>OH</sub>                  | PGOOD = 3.3V                                              | -1              |      | 1               | μА    |

| PGOOD Delay                             | tpgd                             | CLK_ENABLE# LOW to PGOOD HIGH                             | 6.3             | 7.6  | 8.9             | ms    |

| GATE DRIVER                             |                                  |                                                           |                 |      |                 | l     |

| UGATE Pull-Up Resistance                | R <sub>UGPU</sub>                | 200mA Source Current                                      |                 | 1.0  | 1.5             | Ω     |

| UGATE Source Current                    | l <sub>UGSRC</sub>               | UGATE - PHASE = 2.5V                                      |                 | 2.0  |                 | Α     |

| UGATE Sink Resistance                   | R <sub>UGPD</sub>                | 250mA Sink Current                                        |                 | 1.0  | 1.5             | Ω     |

| UGATE Sink Current                      | I <sub>UGSNK</sub>               | UGATE - PHASE = 2.5V                                      |                 | 2.0  |                 | Α     |

| LGATE1a and 1b Pull-Up<br>Resistance    | R <sub>LGPU</sub>                | 250mA Source Current                                      |                 | 2.0  | 3               | Ω     |

| LGATE1a and 1b Source Current           | I <sub>LGSRC</sub>               | LGATE1a and 1b - VSSP1 = 2.5V                             |                 | 1.0  |                 | Α     |

| LGATE1a and 1b Sink Resistance          | R <sub>LGPD</sub>                | 250mA Sink Current                                        |                 | 1    | 1.8             | Ω     |

| LGATE1a and 1b Sink Current             | I <sub>LGSNK</sub>               | LGATE1a and 1b - VSSP1 = 2.5V                             |                 | 2.0  |                 | А     |

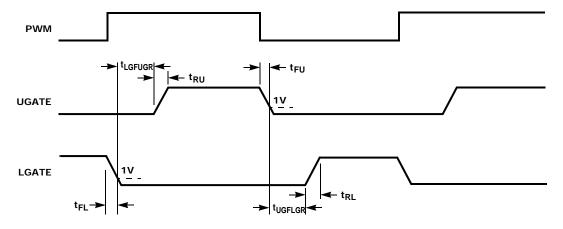

| UGATE1 to LGATE1a and 1b Deadtime       | tugflgr                          | UGATE1 falling to LGATE1a and 1b rising, no load          |                 | 23   |                 | ns    |

| LGATE1a and 1b to UGATE1<br>Deadtime    | t <sub>LGFUGR</sub>              | LGATE1a and 1b falling to UGATE1 rising, no load          |                 | 28   |                 | ns    |

| LGATE Pull-Up Resistance                | R <sub>LGPU</sub>                | 250mA Source Current                                      |                 | 1.0  | 1.5             | Ω     |

| LGATE Source Current                    | I <sub>LGSRC</sub>               | LGATE - VSSP = 2.5V                                       |                 | 2.0  |                 | Α     |

| LGATE Sink Resistance                   | R <sub>LGPD</sub>                | 250mA Sink Current                                        |                 | 0.5  | 0.9             | Ω     |

| LGATE Sink Current                      | I <sub>LGSNK</sub>               | LGATE - VSSP = 2.5V                                       |                 | 4.0  |                 | Α     |

| UGATE to LGATE Deadtime                 | tugflgr                          | UGATE falling to LGATE rising, no load                    |                 | 23   |                 | ns    |

| LGATE to UGATE Deadtime                 | t <sub>LGFUGR</sub>              | LGATE falling to UGATE rising, no load                    |                 | 28   |                 | ns    |

| BOOTSTRAP DIODE                         |                                  |                                                           |                 |      |                 |       |

| Forward Voltage                         | V <sub>F</sub>                   | $PVCC = 5V, I_F = 2mA$                                    |                 | 0.58 |                 | V     |

| Reverse Leakage                         | I <sub>R</sub>                   | $V_R = 25V$                                               |                 | 0.2  |                 | μA    |

| PROTECTION                              |                                  |                                                           |                 |      |                 |       |

| Overvoltage Threshold                   | ov <sub>H</sub>                  | VSEN rising above setpoint for >1ms                       | 150             | 195  | 240             | mV    |

| Severe Overvoltage Threshold            | ov <sub>HS</sub>                 | VSEN rising for >2µs                                      | 1.525           | 1.55 | 1.575           | V     |

### ISL62882, ISL62882B

#### **Electrical Specifications**

Operating Conditions: VDD = 5V,  $T_A = -40^{\circ}\text{C}$  to  $+100^{\circ}\text{C}$ ,  $f_{SW} = 300\text{kHz}$ , unless otherwise noted. Boldface limits apply over the operating temperature range, -40°C to  $+100^{\circ}\text{C}$ . (Continued)

| PARAMETER                                      | SYMBOL                | TEST CONDITIONS                          | MIN<br>(Note 6) | TYP  | MAX<br>(Note 6) | UNITS       |

|------------------------------------------------|-----------------------|------------------------------------------|-----------------|------|-----------------|-------------|

| OC Threshold Offset at<br>Rcomp = Open Circuit |                       | 2-phase configuration, ISUM- pin current | 18.3            | 20.2 | 22.1            | μΑ          |

|                                                |                       | 1-phase configuration, ISUM- pin current | 8.2             | 10.1 | 12.0            | μΑ          |

| Current Imbalance Threshold                    |                       | One ISEN above another ISEN for >1.2ms   |                 | 9    |                 | mV          |

| Undervoltage Threshold                         | UV <sub>f</sub>       | VSEN falling below setpoint for >1.2ms   | -355            | -295 | -235            | mV          |

| LOGIC THRESHOLDS                               |                       | ,                                        |                 | II.  | l .             |             |

| VR_ON Input Low                                | V <sub>IL(1.0V)</sub> |                                          |                 |      | 0.3             | V           |

| VR_ON Input High                               | V <sub>IH(1.0V)</sub> | ISL62882HRTZ                             | 0.7             |      |                 | V           |

|                                                | V <sub>IH(1.0V)</sub> | ISL62882IRTZ                             | 0.75            |      |                 | V           |

| VIDO-VID6, PSI#, and<br>DPRSLPVR Input Low     | V <sub>IL(1.0V)</sub> |                                          |                 |      | 0.3             | V           |

| VIDO-VID6, PSI#, and DPRSLPVR Input High       | V <sub>IH(1.0V)</sub> |                                          | 0.7             |      |                 | V           |

| THERMAL MONITOR                                |                       |                                          |                 |      |                 |             |

| NTC Source Current                             |                       | NTC = 1.3V                               | 53              | 60   | 67              | μΑ          |

| Over-Temperature Threshold                     |                       | V (NTC) falling                          | 1.18            | 1.2  | 1.22            | V           |

| VR_TT# Low Output Resistance                   | R <sub>TT</sub>       | I = 20mA                                 |                 | 6.5  | 9               | Ω           |

| CLK_EN# OUTPUT LEVELS                          |                       |                                          |                 |      |                 | <u> </u>    |

| CLK_EN# Low Output Voltage                     | V <sub>OL</sub>       | I = 4mA                                  |                 | 0.26 | 0.4             | V           |

| CLK_EN# Leakage Current                        | I <sub>OH</sub>       | CLK_EN# = 3.3V                           | -1              |      | 1               | μΑ          |

| CURRENT MONITOR                                | -                     |                                          |                 |      |                 |             |

| IMON Output Current                            | I <sub>IMON</sub>     | ISUM- pin current = 20µA                 | 108             | 120  | 132             | μΑ          |

|                                                |                       | ISUM- pin current = 10µA                 | 51              | 60   | 69              | μΑ          |

|                                                |                       | ISUM- pin current = 5µA                  |                 | 30   |                 | μΑ          |

| IMON Clamp Voltage                             | VIMONCLAMP            |                                          |                 | 1.1  | 1.15            | V           |

| Current Sinking Capability                     |                       |                                          |                 | 275  |                 | μΑ          |

| INPUTS                                         |                       |                                          |                 |      |                 |             |

| VR_ON Leakage Current                          | I <sub>VR_ON</sub>    | VR_ON = 0V                               | -1              | 0    |                 | μΑ          |

| Ü                                              | <u>_</u>              | VR_ON = 1V                               |                 | 0    | 1               | μA          |

| VIDx Leakage Current                           | I <sub>VIDx</sub>     | VIDx = 0V                                | -1              | 0    |                 | μA          |

| _                                              | 1.5x                  | VIDx = 1V                                |                 | 0.45 | 1               | μΑ          |

| PSI# Leakage Current                           | I <sub>PSI#</sub>     | PSI# = 0V                                | -1              | 0    |                 | μΑ          |

|                                                |                       | PSI# = 1V                                |                 | 0.45 | 1               | μA          |

| DPRSLPVR Leakage Current                       | I <sub>DPRSLPVR</sub> | DPRSLPVR = 0V                            | -1              | 0    |                 | μA          |

| j                                              |                       | DPRSLPVR = 1V                            |                 | 0.45 | 1               | μA          |

| SLEW RATE                                      |                       | 1                                        |                 | I    | II.             | 1           |

| Slew Rate (For VID Change)                     | SR                    |                                          | 5               |      | 6.5             | mV/μs       |

|                                                |                       | 1                                        |                 | 1    | 1               | <del></del> |

#### NOTES:

<sup>6.</sup> Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

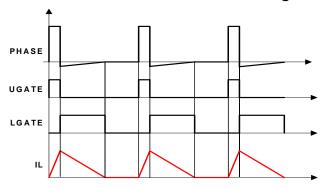

### **Gate Driver Timing Diagram**

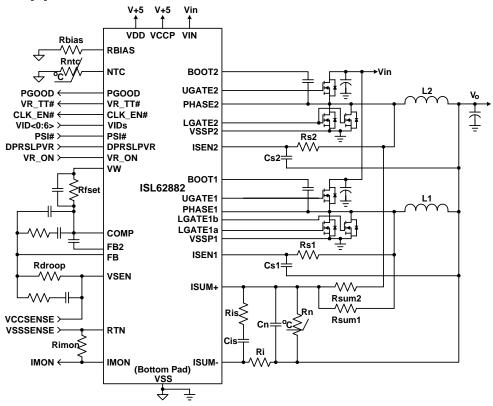

### **Simplified Application Circuits**

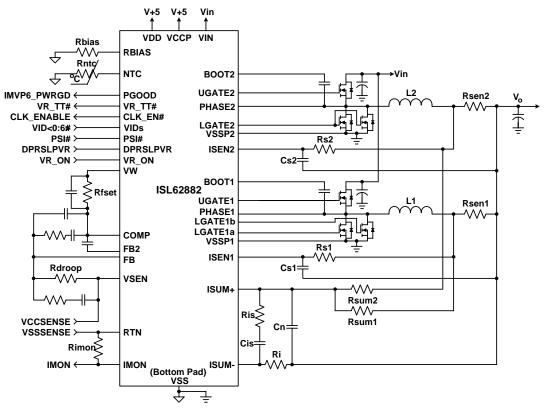

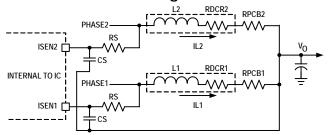

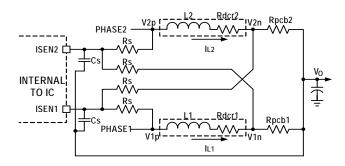

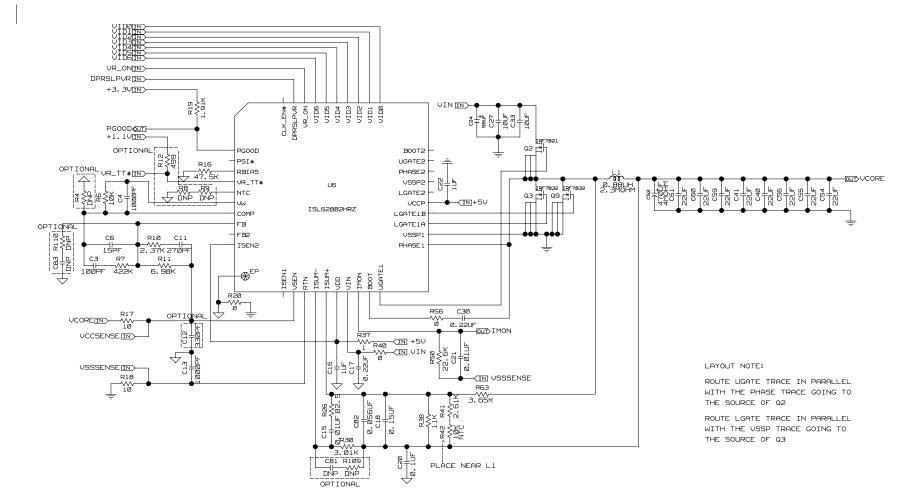

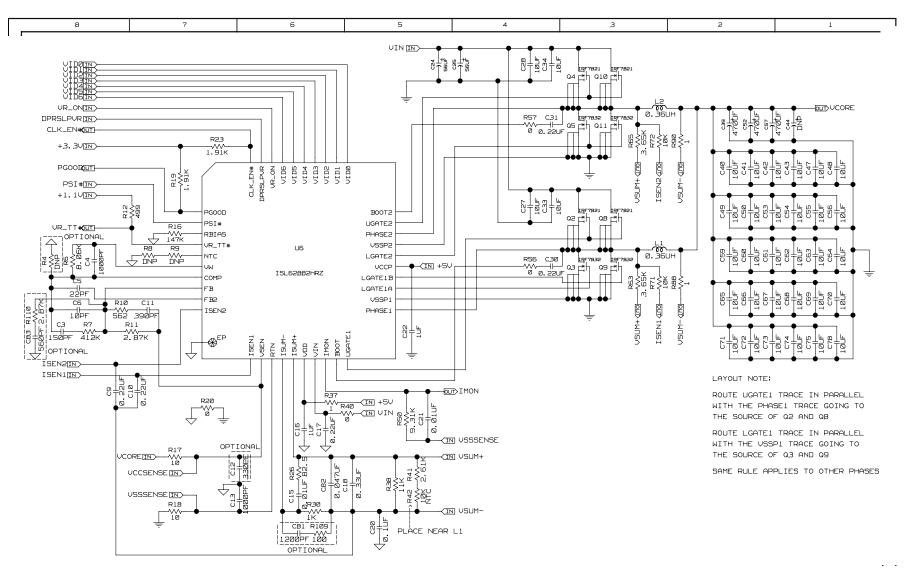

FIGURE 1. TYPICAL CPU APPLICATION CIRCUIT USING DCR SENSING

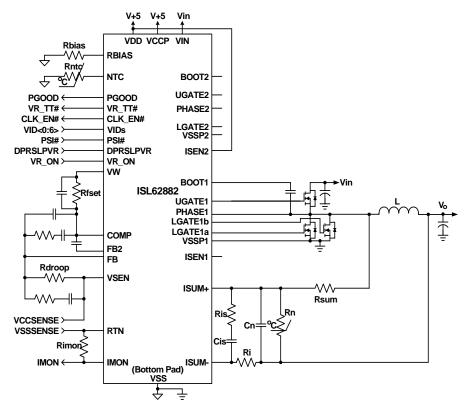

FIGURE 2. TYPICAL CPU APPLICATION CIRCUIT USING RESISTOR SENSING

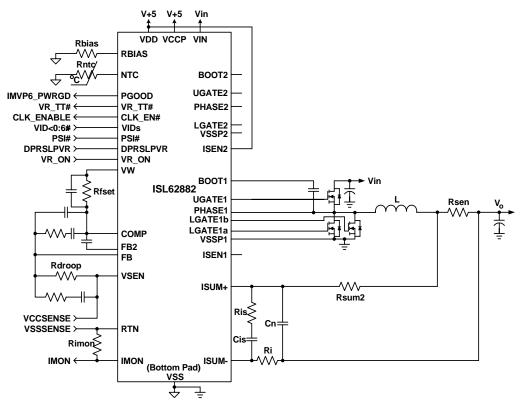

FIGURE 3. TYPICAL GPU APPLICATION CIRCUIT USING DCR SENSING

FIGURE 4. TYPICAL GPU APPLICATION CIRCUIT USING RESISTOR SENSING

### **Theory of Operation**

### Multiphase R<sup>3™</sup> Modulator

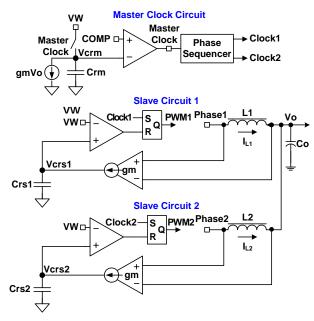

FIGURE 5. R<sup>3™</sup> MODULATOR CIRCUIT

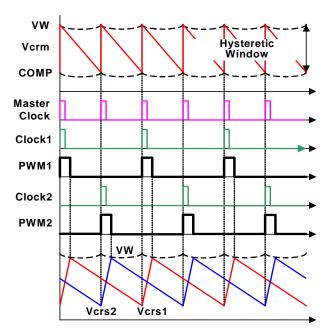

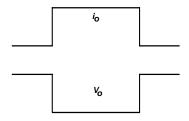

FIGURE 6. R<sup>3™</sup> MODULATOR OPERATION PRINCIPLES IN STEADY STATE

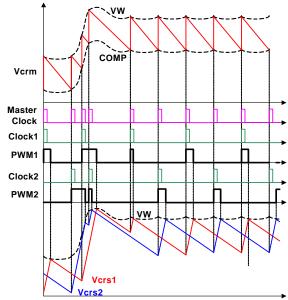

FIGURE 7. R<sup>3™</sup> MODULATOR OPERATION PRINCIPLES IN LOAD INSERTION RESPONSE

The ISL62882 is a multiphase regulator implementing Intel<sup>®</sup> IMVP-6.5<sup>TM</sup> protocol. It can be programmed for 1- or 2-phase operation for microprocessor core applications. It uses Intersil patented  $R^{3^{TM}}$  (Robust Ripple Regulator<sup>TM</sup>) modulator. The  $R^{3^{TM}}$  modulator combines the best features of fixed frequency PWM and hysteretic PWM while eliminating many of their shortcomings. Figure 5 conceptually shows the ISL62882 multiphase  $R^{3^{TM}}$  modulator circuit, and Figure 6 shows the operation principles.

A current source flows from the VW pin to the COMP pin, creating a voltage window set by the resistor between the two pins. This voltage window is called VW window in the following discussion.

Inside the IC, the modulator uses the master clock circuit to generate the clocks for the slave circuits. The modulator discharges the ripple capacitor  $C_{rm}$  with a current source equal to  $g_m V_0$ , where  $g_m$  is a gain factor.  $C_{rm}$  voltage  $V_{crm}$  is a sawtooth waveform traversing between the VW and COMP voltages. It resets to VW when it hits COMP, and generates a one-shot master clock signal. A phase sequencer distributes the master clock signal to the slave circuits. If the ISL62882 is in 2-phase mode, the master clock signal will be distributed to Phases 1 and 2, and the Clock1 and Clock2 signals will be 180° out-of-phase. If the ISL62882 is in 1-phase mode, the master clock signal will be distributed to Phases 1 only and be the Clock1 signal.

Each slave circuit has its own ripple capacitor  $C_{rs}$ , whose voltage mimics the inductor ripple current. A  $g_m$  amplifier converts the inductor voltage into a current source to charge and discharge  $C_{rs}$ . The slave circuit turns on its PWM pulse upon receiving the clock signal, and the current source charges  $C_{rs}$ . When  $C_{rs}$  voltage

$V_{Crs}$  hits VW, the slave circuit turns off the PWM pulse, and the current source discharges  $C_{rs}$ .

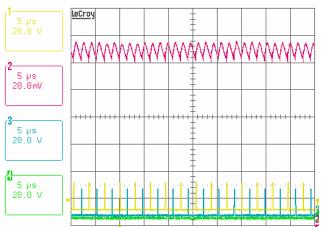

Since the ISL62882 works with  $V_{\text{Crs}}$ , which are large amplitude and noise-free synthesized signals, the ISL62882 achieves lower phase jitter than conventional hysteretic mode and fixed PWM mode controllers. Unlike conventional hysteretic mode converters, the ISL62882 has an error amplifier that allows the controller to maintain a 0.5% output voltage accuracy.

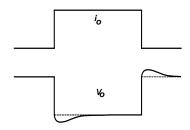

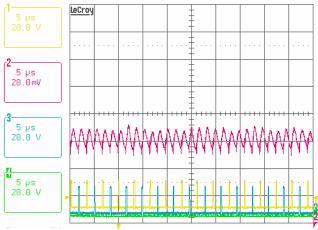

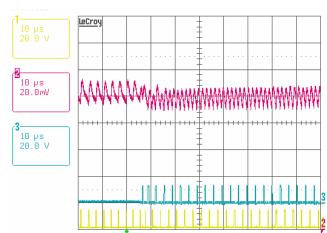

Figure 7 shows the operation principles during load insertion response. The COMP voltage rises during load insertion, generating the master clock signal more quickly, so the PWM pulses turn on earlier, increasing the effective switching frequency, which allows for higher control loop bandwidth than conventional fixed frequency PWM controllers. The VW voltage rises as the COMP voltage rises, making the PWM pulses wider. During load release response, the COMP voltage falls. It takes the master clock circuit longer to generate the next master clock signal so the PWM pulse is held off until needed. The VW voltage falls as the VW voltage falls, reducing the current PWM pulse width. This kind of behavior gives the ISL62882 excellent response speed.

The fact that both phases share the same VW window voltage also ensures excellent dynamic current balance between phases.

#### **Diode Emulation and Period Stretching**

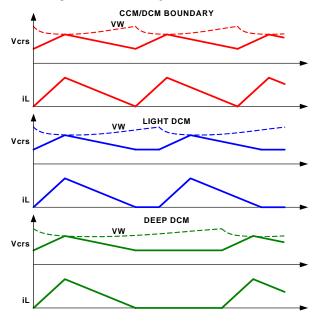

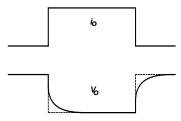

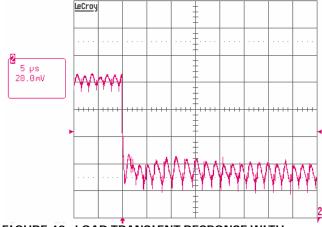

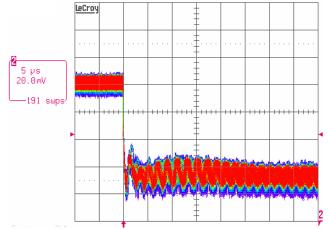

FIGURE 8. DIODE EMULATION

ISL62882 can operate in diode emulation (DE) mode to improve light load efficiency. In DE mode, the low-side MOSFET conducts when the current is flowing from source to drain and does not allow reverse current, emulating a diode. As Figure 8 shows, when LGATE is on, the low-side MOSFET carries current, creating negative voltage on the phase node due to the voltage drop across the ON-resistance. The ISL62882 monitors the current through monitoring the phase node voltage. It turns off LGATE when the phase node voltage reaches zero to prevent the inductor current from reversing the direction and creating unnecessary power loss.

If the load current is light enough, as Figure 8 shows, the inductor current will reach and stay at zero before the next phase node pulse, and the regulator is in discontinuous conduction mode (DCM). If the load

current is heavy enough, the inductor current will never reach OA, and the regulator is in CCM although the controller is in DE mode.

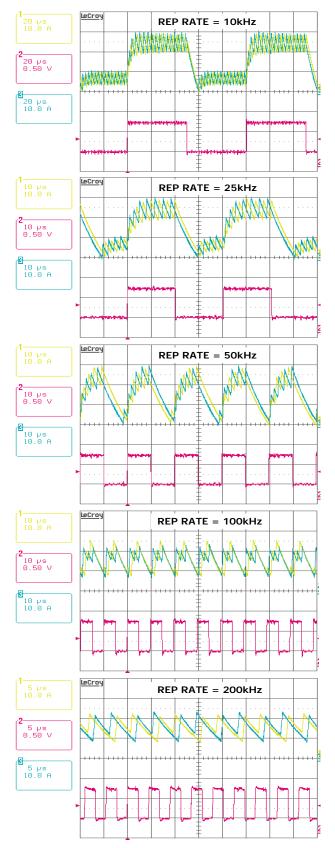

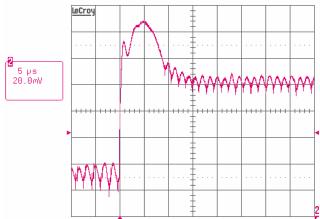

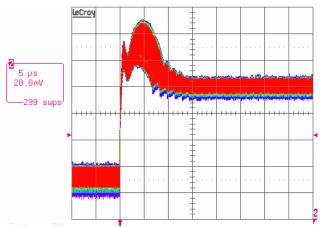

Figure 9 shows the operation principle in diode emulation mode at light load. The load gets incrementally lighter in the three cases from top to bottom. The PWM on-time is determined by the VW window size, therefore is the same, making the inductor current triangle the same in the three cases. The ISL62882 clamps the ripple capacitor voltage V<sub>CrS</sub> in DE mode to make it mimic the inductor current. It takes the COMP voltage longer to hit V<sub>CrS</sub>, naturally stretching the switching period. The inductor current triangles move further apart from each other such that the inductor current average value is equal to the load current. The reduced switching frequency helps to increase light load efficiency.

FIGURE 9. PERIOD STRETCHING

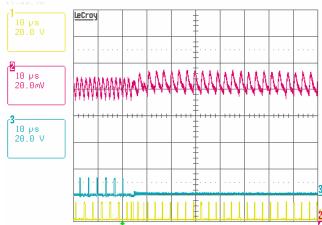

#### Start-up Timing

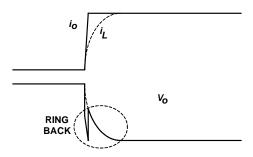

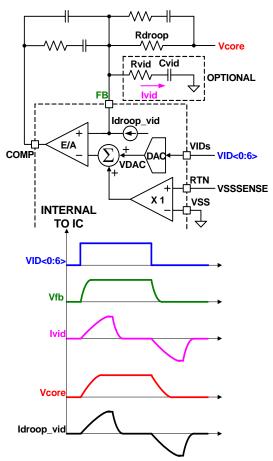

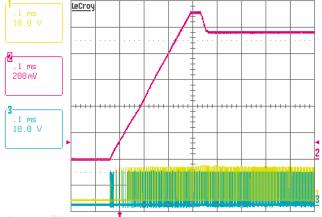

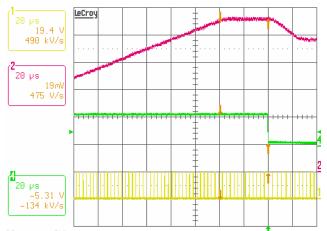

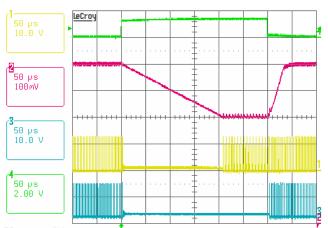

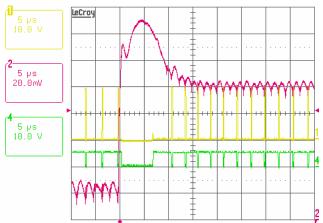

With the controller's  $V_{DD}$  voltage above the POR threshold, the start-up sequence begins when  $VR_{ON}$  exceeds the 3.3V logic high threshold. Figure 10 shows the typical start-up timing when the ISL62882 is configured for CPU VR application. The ISL62882 uses digital soft-start to ramp-up DAC to the boot voltage of 1.1V at about 2.5mV/ $\mu$ s. Once the output voltage is within 10% of the boot voltage for 13 PWM cycles (43 $\mu$ s for frequency = 300kHz), CLK\_EN# is pulled low and DAC slews at 5mV/ $\mu$ s to the voltage set by the VID pins. PGOOD is asserted high in approximately 7ms. Similar results occur if VR\_ON is tied to VDD, with the soft-start sequence starting 120 $\mu$ s after VDD crosses the POR threshold.

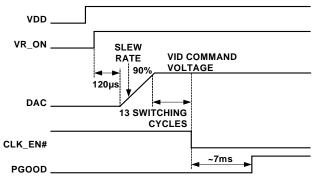

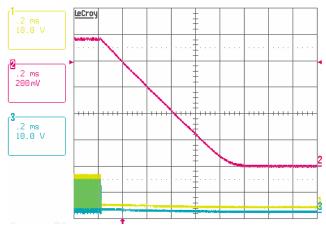

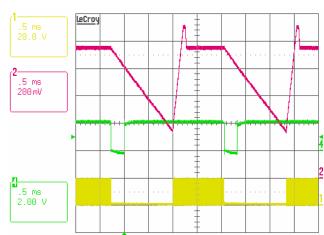

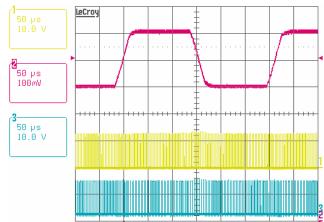

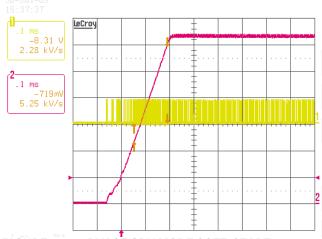

Figure 11 shows the typical start-up timing when the ISL62882 is configured for GPU VR application. The ISL62882 uses digital soft start to ramp up DAC to the

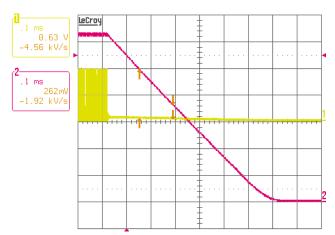

FIGURE 10. SOFT-START WAVEFORMS FOR CPU VR APPLICATION

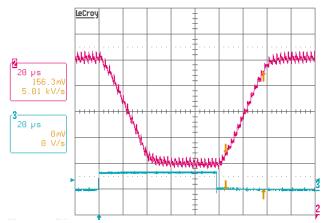

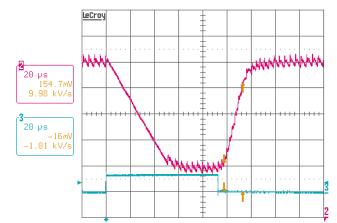

FIGURE 11. SOFT-START WAVEFORMS FOR GPU VR APPLICATION

voltage set by the VID pins. The slew rate is 5mV/µs when there is DPRSLPVR = 0, and is doubled when there is DPRSLPVR = 1. Once the output voltage is within 10% of the target voltage for 13 PWM cycles (43µs for frequency = 300kHz), CLK\_EN# is pulled low. PGOOD is asserted high in approximately 7ms. Similar results occur if VR\_ON is tied to VDD, with the soft-start sequence starting 120µs after VDD crosses the POR threshold.

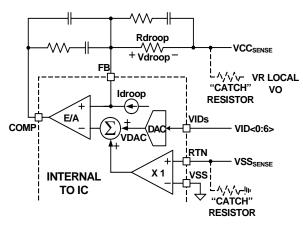

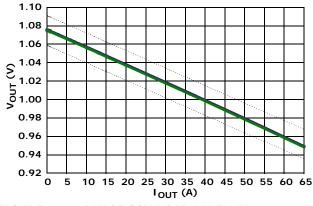

## Voltage Regulation and Load Line Implementation

After the start sequence, the ISL62882 regulates the output voltage to the value set by the VID inputs per Table 1. The ISL62882 will control the no-load output voltage to an accuracy of  $\pm 0.5\%$  over the range of 0.75V to 1.5V. A differential amplifier allows voltage sensing for precise voltage regulation at the microprocessor die.

TABLE 1. VID TABLE

| VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VIDO | ν <sub>ο</sub><br>(ν) |

|------|------|------|------|------|------|------|-----------------------|

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1.5000                |

| 0    | 0    | 0    | 0    | 0    | 0    | 1    | 1.4875                |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | 1.4750                |

| 0    | 0    | 0    | 0    | 0    | 1    | 1    | 1.4625                |

| 0    | 0    | 0    | 0    | 1    | 0    | 0    | 1.4500                |

| 0    | 0    | 0    | 0    | 1    | 0    | 1    | 1.4375                |

TABLE 1. VID TABLE (Continued)

| VID6         VID5         VID4         VID3         VID2         VID1         VID0         VOO (V)           0         0         0         0         1         1         0         1.4250           0         0         0         0         1         1         1         1.4425           0         0         0         0         1         1         1         1.4000           0         0         0         1         0         0         1         1.3875           0         0         0         1         0         1         1         1.3375           0         0         0         1         1         0         1.3500           0         0         0         1         1         0         1.3500           0         0         0         1         1         1         1         1.3500           0         0         0         1         1         0         1.3500           0         0         0         1         1         1         1.3500           0         0         0         1         1         1         1.3500      <                                                                                                              |      | TABLE 1. VID TABLE (Continued) |      |      |      |      |      |        |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------|------|------|------|------|------|--------|--|--|

| 0         0         0         1         1         1         1.4125           0         0         0         1         0         0         0         1.4000           0         0         0         1         0         0         1         1.3875           0         0         0         1         0         1         0         1.3750           0         0         0         1         1         0         0         1.3500           0         0         0         1         1         0         0         1.3500           0         0         0         1         1         0         0         1.3500           0         0         0         1         1         0         0         1.3500           0         0         0         1         1         1         1         1.3500           0         0         0         1         1         1         1.3500           0         0         1         1         1         1.3250           0         0         1         0         0         1.3000           0         0                                                                                                                               | VID6 | VID5                           | VID4 | VID3 | VID2 | VID1 | VIDO |        |  |  |

| 0         0         0         1         0         0         1.4000           0         0         0         1         0         0         1         1.3875           0         0         0         1         0         1         0         1.3750           0         0         0         1         0         1         1         1.3625           0         0         0         1         1         0         0         1.3500           0         0         0         1         1         0         1         1.3375           0         0         0         1         1         1         0         1.3550           0         0         0         1         1         1         1         1.3375           0         0         1         0         0         0         1.3000           0         0         1         0         0         1         1.2875           0         0         1         0         0         1         1.2875           0         0         1         0         0         1         1.2825           0                                                                                                                               | 0    | 0                              | 0    | 0    | 1    | 1    | 0    | 1.4250 |  |  |

| 0         0         0         1         0         0         1         1.3875           0         0         0         1         0         1         0         1.3750           0         0         0         1         0         1         1         1         1         1.3625           0         0         0         1         1         0         0         1.3500           0         0         0         1         1         1         0         1.3375           0         0         0         1         1         1         1         1.3375           0         0         0         1         1         1         1         1.3375           0         0         1         0         0         0         1.3000           0         0         1         0         0         1         1.3000           0         0         1         0         0         1         1.2875           0         0         1         0         0         1         1.2875           0         0         1         0         1         1         1.2500                                                                                                                       | 0    | 0                              | 0    | 0    | 1    | 1    | 1    | 1.4125 |  |  |

| 0         0         0         1         0         1         0         1.3750           0         0         0         1         0         1         1         1.3625           0         0         0         1         1         0         0         1.3500           0         0         0         1         1         1         0         1.3375           0         0         0         1         1         1         1         1         1.3375           0         0         0         1         1         1         1         1         1.3375           0         0         1         0         0         0         1         1.3250           0         0         1         0         0         1         1.22750           0         0         1         0         0         1         1.22750           0         0         1         0         0         1         1.2250           0         0         1         0         1         1.2250           0         0         1         0         1         1.2250           0 <td>0</td> <td>0</td> <td>0</td> <td>1</td> <td>0</td> <td>0</td> <td>0</td> <td>1.4000</td>                                | 0    | 0                              | 0    | 1    | 0    | 0    | 0    | 1.4000 |  |  |

| 0         0         0         1         1         1         1.3625           0         0         0         1         1         0         0         1.3500           0         0         0         1         1         0         0         1.3500           0         0         0         1         1         1         0         1.3375           0         0         0         1         0         0         0         1.3000           0         0         1         0         0         0         1.3000           0         0         1         0         0         0         1.3000           0         0         1         0         0         1.2250           0         0         1         0         0         1.2250           0         0         1         0         1         1.2375           0         0         1         0         1         1.2375           0         0         1         0         1         1.2250           0         0         1         0         1         1.2250           0         0                                                                                                                                  | 0    | 0                              | 0    | 1    | 0    | 0    | 1    | 1.3875 |  |  |

| 0         0         0         1         1         0         0         1.3500           0         0         0         1         1         0         1         1.3375           0         0         0         1         1         1         1         1.33125           0         0         0         1         0         0         0         1.3000           0         0         1         0         0         0         1.3000           0         0         1         0         0         0         1.3000           0         0         1         0         0         1         1.2875           0         0         1         0         1         0         1.2750           0         0         1         0         1         0         1.2500           0         0         1         0         1         0         1.2250           0         0         1         0         1         1         1.2375           0         0         1         0         1         1         1.2250           0         0         1         0 <td>0</td> <td>0</td> <td>0</td> <td>1</td> <td>0</td> <td>1</td> <td>0</td> <td>1.3750</td>                                 | 0    | 0                              | 0    | 1    | 0    | 1    | 0    | 1.3750 |  |  |

| 0         0         0         1         1         0         1         1.3375           0         0         0         1         1         1         0         1.3250           0         0         0         0         0         0         0         1.3000           0         0         1         0         0         0         1.3000           0         0         1         0         0         0         1.3000           0         0         1         0         0         1         1.2875           0         0         1         0         0         1         1.2250           0         0         1         0         1         0         1.2250           0         0         1         0         1         0         1.2250           0         0         1         0         1         1         1.2375           0         0         1         0         1         1         1.2250           0         0         1         0         1         1         1.2250           0         0         1         0         1                                                                                                                               | 0    | 0                              | 0    | 1    | 0    | 1    | 1    | 1.3625 |  |  |

| 0         0         0         1         1         1         1         1         1.3250           0         0         0         0         1         1         1         1         1.3125           0         0         1         0         0         0         1.3000           0         0         1         0         0         1         1.2875           0         0         1         0         0         1         1.2875           0         0         1         0         0         1         1         1.2625           0         0         1         0         1         0         1         1.2500           0         0         1         0         1         0         1         1.2375           0         0         1         0         1         1         0         1.2250           0         0         1         0         1         1         0         1.2250           0         0         1         1         0         1         1.2375           0         0         1         1         0         0         1.2000                                                                                                                       | 0    | 0                              | 0    | 1    | 1    | 0    | 0    | 1.3500 |  |  |

| 0         0         0         1         1         1         1         1.3125           0         0         1         0         0         0         0         1.3000           0         0         1         0         0         0         1.2875           0         0         1         0         0         1         0         1.2750           0         0         1         0         0         1         1         1.2625           0         0         1         0         1         0         1         1.2375           0         0         1         0         1         0         1         1.2375           0         0         1         0         1         0         1         1.2375           0         0         1         0         1         1         0         1.2250           0         0         1         0         1         1         1         1.2375           0         0         1         1         0         0         1.2000           0         0         1         1         0         0         1.2000                                                                                                                       | 0    | 0                              | 0    | 1    | 1    | 0    | 1    | 1.3375 |  |  |

| 0         0         1         0         0         0         1.3000           0         0         1         0         0         0         1.2875           0         0         1         0         0         1         0.2750           0         0         1         0         0         1         1.2625           0         0         1         0         1         0         1.2500           0         0         1         0         1         0         1.2500           0         0         1         0         1         0         1.2500           0         0         1         0         1         0         1.2250           0         0         1         0         1         1         1.2375           0         0         1         0         1         1         1.2250           0         0         1         1         0         0         1.2000           0         0         1         1         0         0         1.2000           0         0         1         1         0         1.2000         1.2000                                                                                                                               | 0    | 0                              | 0    | 1    | 1    | 1    | 0    | 1.3250 |  |  |

| 0         0         1         0         0         1         1.2875           0         0         1         0         0         1         0         1.2750           0         0         1         0         0         1         1         1.2625           0         0         1         0         1         0         0         1.2500           0         0         1         0         1         0         1         1.2375           0         0         1         0         1         1         0         1         1.2375           0         0         1         0         1         1         0         1         1.2375           0         0         1         0         1         1         0         1.2250           0         0         1         1         0         0         1.2000           0         0         1         1         0         0         1.2000           0         0         1         1         0         0         1.2000           0         0         1         1         0         0         1.2000                                                                                                                       | 0    | 0                              | 0    | 1    | 1    | 1    | 1    | 1.3125 |  |  |

| 0         0         1         0         0         1         0         1.2750           0         0         1         0         0         1         1.2625           0         0         1         0         1         0         0         1.2500           0         0         1         0         1         0         1         1.2375           0         0         1         0         1         1         0         1.2375           0         0         1         0         1         1         0         1.2250           0         0         1         0         1         1         0         1.2250           0         0         1         1         0         0         1.2000           0         0         1         1         0         0         1.2000           0         0         1         1         0         0         1.2000           0         0         1         1         0         0         1.2000           0         0         1         1         0         1.2000         1.2000           0         0                                                                                                                          | 0    | 0                              | 1    | 0    | 0    | 0    | 0    | 1.3000 |  |  |

| 0         0         1         0         0         1         1         1.2625           0         0         1         0         1         0         1.2500           0         0         1         0         1         0         1         1.2375           0         0         1         0         1         1         0         1         1.2375           0         0         1         0         1         1         0         1         1.2250           0         0         1         0         1         1         0         1.2250           0         0         1         1         0         0         1.2000           0         0         1         1         0         0         1.2000           0         0         1         1         0         0         1.2000           0         0         1         1         0         0         1.2000           0         0         1         1         0         1.1875           0         0         1         1         1         1         1.1875           0         0                                                                                                                               | 0    | 0                              | 1    | 0    | 0    | 0    | 1    | 1.2875 |  |  |

| 0         0         1         0         1         0         1.2500           0         0         1         0         1         0.2500           0         0         1         0         1         1         0         1.2250           0         0         1         0         1         1         1         1.2250           0         0         1         0         1         1         1         1.2250           0         0         1         1         0         0         0         1.2000           0         0         1         1         0         0         0         1.2000           0         0         1         1         0         0         1.2000           0         0         1         1         0         0         1.2000           0         0         1         1         0         0         1.1750           0         0         1         1         1         1         1.1625           0         0         1         1         1         1         1         1.1375           0         0         1                                                                                                                               | 0    | 0                              | 1    | 0    | 0    | 1    | 0    | 1.2750 |  |  |

| 0         0         1         0         1         1.2375           0         0         1         0         1         1         0.2550           0         0         1         0         1         1         0         1.2250           0         0         1         0         1         1         1         1.2125           0         0         1         1         0         0         1.2000           0         0         1         1         0         0         1.2000           0         0         1         1         0         0         1.2000           0         0         1         1         0         0         1.2000           0         0         1         1         0         0         1.1875           0         0         1         1         1         0         1.1875           0         0         1         1         1         1         1         1.1875           0         0         1         1         1         1         1         1.1375           0         0         1         1         1                                                                                                                               | 0    | 0                              | 1    | 0    | 0    | 1    | 1    | 1.2625 |  |  |

| 0         0         1         0         1         1         0         1.2250           0         0         1         0         1         1         1         1.2125           0         0         1         1         0         0         0         1.2000           0         0         1         1         0         0         1.1200           0         0         1         1         0         0         1.1750           0         0         1         1         0         1         1.1625           0         0         1         1         0         1         1.1625           0         0         1         1         1         0         1.1500           0         0         1         1         1         0         1.1500           0         0         1         1         1         1         1         1.1625           0         0         1         1         1         1         1         1         1.1375           0         0         1         1         1         1         1.1250           0         1                                                                                                                               | 0    | 0                              | 1    | 0    | 1    | 0    | 0    | 1.2500 |  |  |

| 0         0         1         0         1         1         1         1.2125           0         0         1         1         0         0         0         1.2000           0         0         1         1         0         0         1.1200           0         0         1         1         0         1         1.1875           0         0         1         1         0         1         1.1625           0         0         1         1         1         0         1.1500           0         0         1         1         1         0         1.1500           0         0         1         1         1         0         1.1500           0         0         1         1         1         0         1.1500           0         0         1         1         1         1         1         1.1625           0         0         1         1         1         1         1         1.1375           0         1         0         0         0         0         1.1000         1         1.1000           0         1                                                                                                                          | 0    | 0                              | 1    | 0    | 1    | 0    | 1    | 1.2375 |  |  |

| 0         0         1         1         0         0         0         1.2000           0         0         1         1         0         0         1.1875           0         0         1         1         0         1         1.1875           0         0         1         1         0         1         1.1750           0         0         1         1         1         0         0         1.1500           0         0         1         1         1         0         0         1.1500           0         0         1         1         1         0         0         1.1500           0         0         1         1         1         1         0         1.1500           0         0         1         1         1         1         1         1         1.1375           0         0         1         1         1         1         1         1.1250           0         1         0         0         0         0         1.1000         1         1.0000         1.0000           0         1         0         0         0                                                                                                                  | 0    | 0                              | 1    | 0    | 1    | 1    | 0    | 1.2250 |  |  |

| 0         0         1         1         0         0         1         1.1875           0         0         1         1         0         1         0         1.1750           0         0         1         1         0         1         1.1625           0         0         1         1         1         0         0         1.1500           0         0         1         1         1         0         1.1375           0         0         1         1         1         0         1.1375           0         0         1         1         1         1         1         1.1375           0         0         1         1         1         1         1         1.1375           0         0         1         1         1         1         1         1.1375           0         1         0         0         0         0         1.1000           0         1         0         0         0         1.1000           0         1         0         0         1         1.0875           0         1         0         0                                                                                                                               | 0    | 0                              | 1    | 0    | 1    | 1    | 1    | 1.2125 |  |  |

| 0         0         1         1         0         1         0         1.1750           0         0         1         1         0         1         1         1.1625           0         0         1         1         1         0         0         1.1500           0         0         1         1         1         0         1         1.1375           0         0         1         1         1         1         0         1.1250           0         0         1         1         1         1         1         1.1375           0         0         1         1         1         1         1         1.1375           0         0         1         1         1         1         1         1.1375           0         1         0         0         0         0         1.1000           0         1         0         0         0         1.1000         1.0000           0         1         0         0         1         0         1.0500           0         1         0         0         1         0         1.0000         1                                                                                                                  | 0    | 0                              | 1    | 1    | 0    | 0    | 0    | 1.2000 |  |  |

| 0         0         1         1         0         1         1         1.1625           0         0         1         1         1         0         0         1.1500           0         0         1         1         1         0         1.1375           0         0         1         1         1         1         0         1.1375           0         0         1         1         1         1         1         1.1375           0         0         1         1         1         1         1.1375           0         1         0         0         0         0         1.1000           0         1         0         0         0         0         1.1000           0         1         0         0         0         1         0.1000           0         1         0         0         0         1         0         1.0050           0         1         0         0         1         0         1.0050           0         1         0         0         1         0         1.0050           0         1         0                                                                                                                               | 0    | 0                              | 1    | 1    | 0    | 0    | 1    | 1.1875 |  |  |

| 0         0         1         1         1         0         0         1.1500           0         0         1         1         1         0         1.1500           0         0         1         1         1         0         1.1375           0         0         1         1         1         1         1.1125           0         1         0         0         0         0         0         1.1000           0         1         0         0         0         0         1.1000           0         1         0         0         0         1.1000           0         1         0         0         0         1.1000           0         1         0         0         0         1.1000           0         1         0         0         0         1.1000         1.0000           0         1         0         0         0         1.0750         1.0000         1.0000         1.0050           0         1         0         0         1         0         1.0050         1.0000         1.0000         1.0000         1.0000         1.0000 <td< td=""><td>0</td><td>0</td><td>1</td><td>1</td><td>0</td><td>1</td><td>0</td><td>1.1750</td></td<> | 0    | 0                              | 1    | 1    | 0    | 1    | 0    | 1.1750 |  |  |