±1°C Temperature Sensor with ß Compensation

Release Date: May, 2008 Revision: V0.15P

## F75395 Datasheet Revision History

| Version | Date      | Page | Revision History                                        |  |

|---------|-----------|------|---------------------------------------------------------|--|

| V0.10P  | 2007/7/30 |      | Preliminary Version                                     |  |

| V0.11P  | 2007/8/7  | - // | Add function description                                |  |

| V0.12P  | 2007/9/20 |      | Add register description                                |  |

| V0.13P  | 2008/1/8  |      | F75395 won't provide SOP package in the future.         |  |

|         |           | _    | Add ordering information.                               |  |

|         |           | -    | Add Electrical characteristic                           |  |

| V0.14P  | 2008/1/29 | -    | Modify typo.                                            |  |

| V0.15P  | 2008/5/29 | 5    | Modify typo. of Chapter 6.4 for Temperature Range Table |  |

Please note that all data and specifications are subject to change without notice. All the trade marks of products and companies mentioned in this data sheet belong to their respective owners.

### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Fintek for any damages resulting from such improper use or sales.

۰.

## **Table of Contents**

| 1. | Gen  | eral Description                                              | . 1 |

|----|------|---------------------------------------------------------------|-----|

| 2. | Fea  | tures                                                         | . 1 |

| З. | Key  | Specifications                                                | . 2 |

| 4. |      | Configuration                                                 | . 2 |

| 5. | Pin  | Descriptions                                                  | . 2 |

| 6. | Fun  | ctional Description                                           | . 3 |

|    | 6.1  | General Description                                           | . 3 |

|    | 6.2  | The warning message                                           | . 3 |

|    | 6.3  | Access Interface                                              | . 4 |

|    | 6.4  | Temperature Monitoring                                        | . 5 |

|    | 6.5  | Alert#                                                        | . 6 |

|    | 6.6  | THERM#                                                        | . 6 |

|    | 6.7  | ADC Conversion Sequence                                       | . 6 |

|    | 6.8  | Thermal Mass and Self Heating                                 | . 7 |

|    | 6.9  | ADC Noise Filtering                                           | . 7 |

|    | 6.10 | Beta Compensation                                             | . 7 |

|    | 6.11 | Resistor Cancelled Function                                   | . 8 |

|    | 6.12 | PCB Layout Guide                                              | . 8 |

| 7. | Reg  | ister Description                                             | . 9 |

|    | 7.1  | Configuration Register — Index 03h(Read), 09h(Write)          | . 9 |

|    | 7.2  | Status Register — Index 02h                                   | 10  |

|    | 7.3  | Conversion Rate Register — Index 04h(Read), 0Ah(Write)        | 10  |

|    | 7.4  | One-Shot Register — Index 0Fh                                 | 10  |

|    | 7.5  | Alert Queue & Timeout Register — Index 22h                    | 11  |

|    | 7.6  | Status-with-ARA Control Register — Index 24h                  | 11  |

|    | 7.7  | Beta Compensation Register—Index 3Bh                          | 11  |

|    | 7.8  | SST Address Register—Index 3Dh                                |     |

|    | 7.9  | Chip ID (MSB) Register—Index 5Ah                              | 12  |

|    | 7.10 | Chip ID (LSB) Register — Index 5Bh                            | 12  |

|    | 7.11 | Fintek Vendor ID (MSB) (Manufacturer ID) Register — Index 5Dh | 12  |

|    | 7.12 | Fintek Vendor ID (LSB) (Manufacturer ID) Register — Index 5Eh | 12  |

|    | 7.13 | Fintek Vendor ID II (Manufacturer ID) Register—Index FEh      | 12  |

|    |      | Value RAM — Index 10h- 2Fh                                    |     |

|    | 7.15 | SST Command Table                                             | 13  |

| 8. | Elec | trical characteristic                                         | 14  |

| 8.1 Absolute Maximum Ratings |    |

|------------------------------|----|

| 8.2 DC Characteristics       | 14 |

| 8.3 AC Characteristics       |    |

| 9. Ordering Information      |    |

| 9. Ordering Information      |    |

| 11. Application Circuit      |    |

### 1. General Description

The F75395 is a temperature sensor IC with ß compensation and alert signal which is specific designed for notebook, graphic cards etc. An 11-bit analog-to-digital converter (ADC) was built inside F75395. The F75395 can monitor two set of temperature which is very important for the system to work stably and properly. This chip provides 1 remote temperature sensor and 1 local temperature sensor. The remote temperature sensor can be performed by CPU thermal diode or transistor 2N3906. The F75395 also can support new generational 45nm CPU temperature sensing by varied ß of CPU. The users can set up the upper and lower limits (alarm thresholds) of all monitored parameters and this chip can also issue warning messages for system protection when there is something wrong with monitored items.

Through the BIOS or application software, the users can read all the monitored parameters of system all the time. And a pop-up warning can be also activated when the monitored item was out of the proper/pre-setting range. The application software could be Fintek's application utility, or other management application software. The F75395 is in the green package of 8-pin MSOP and powered by 3.3V.

### 2. Features

- Provide 1 on-chip local and 1 remote temperature sensing

- ±1 °C accuarcy on remote channel and ±3 °C accuarcy on local channel

±1 °C (+60 °C to +100 °C, remote)

±3 °C (+60 °C to +100 °C, local)

- Support new generational CPU temperature sensing with ß compensation

- Resistor cancelled function

- ALERT# output for SMBus alert

- Programmable alert queue

- Programmable limited and setting points(alert threshold) for all monitored items

- Provide SST and 2-wire SMBus interfaces for temperature reading by host

- 3VCC operation

- ♦ 8-MSOP Package F75395M

- The SST slave address: 0X4Ch

- The F75395 provides SMBus address ID option by resistor selection and they have the following SMBus slave address: (Default address is 98h)

| Resistor | A6 | A5 | A4 | A3 | A2 | A1 | A0 |

|----------|----|----|----|----|----|----|----|

| 1k       | 1  | 0  | 0  | 1  | 1  | 1  | 1  |

| 4.7k     | 1  | 0  | 0  | 1  | 1  | 0  | 1  |

Noted: Patented TW 235231 TWI263778

| 10k | 1 | 0 | 0 | 1 | 1 | 1 | 0 |

|-----|---|---|---|---|---|---|---|

| 20k | 0 | 1 | 1 | 0 | 1 | 1 | 0 |

| 30k | 0 | 1 | 1 | 0 | 1 | 0 | 1 |

| 47k | 0 | 1 | 1 | 0 | 1 | 0 | 0 |

- 3. Key Specifications

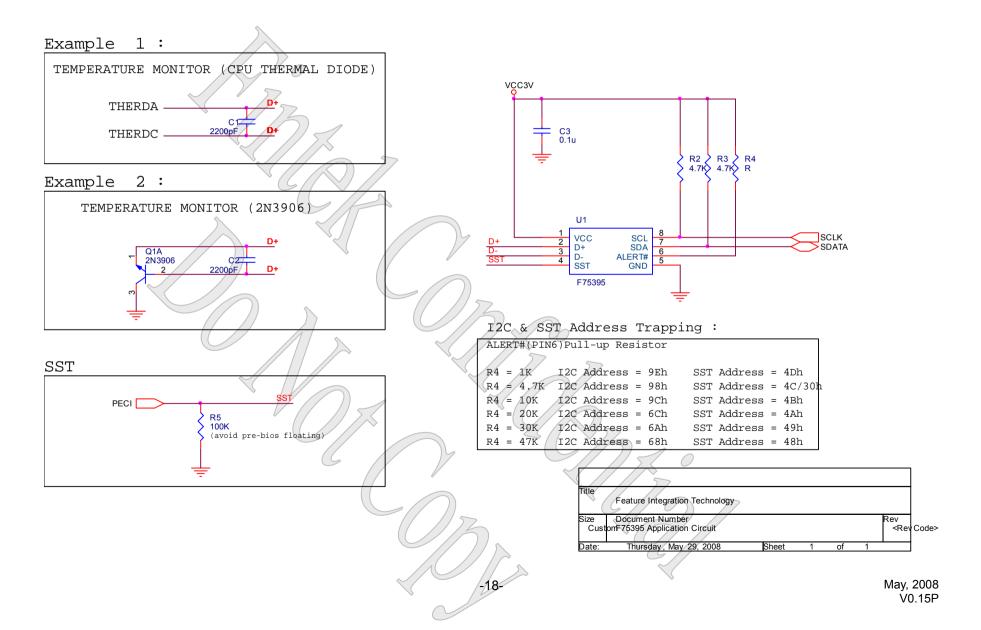

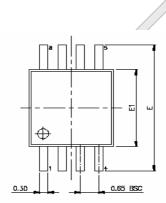

- Supply Voltage 3.0~3.6V Supply Current 180 uA (typ) 4. Pin Configuration 0 VCC SCL 8 D+ 7 SDA 2 F75395 6 D -ALERT# 3 SST 5 GND 4

## **5.** *Pin Descriptions*

- $I/O_{12t} \qquad$  TTL level bi-directional pin with 12 mA source-sink capability

- I/O<sub>12ts</sub> TTL level and schmitt trigger

- $O_{12} \qquad$  Output pin with 12 mA source-sink capability

- O<sub>24V4</sub> Output pin with 24 mA source-sink capability, output 4V

- AOUT Output pin(Analog)

- $\mathsf{OD}_{12} \qquad \text{-} \mathsf{Open-drain} \text{ output pin with } 12 \text{ mA sink capability}$

- $IN_t$  TTL level input pin

- INts TTL level input pin and schmitt trigger

$I_{Lv}/O_{D8-S1}$  Low level bi-directional pin(VIH  $\rightarrow$  0.9V, VIL  $\rightarrow$  0.6V.). Output with 8mA drive and 1mA sink capability. AIN - Input pin(Analog)

|        |          |                                    |      | $\bigcirc$ //                                                              |

|--------|----------|------------------------------------|------|----------------------------------------------------------------------------|

| PIN NO | PIN NAME | TYPE                               | PWR  | DESCRIPTION                                                                |

| 1      | VCC      | PWR                                | 3VCC | Power Pin                                                                  |

| 2      | D+       | AIN                                | 3VCC | Positive connection to remote temperature sensor (ex: thermal diode anode) |

| 3      | D-       | AIN                                | 3VCC | Negative connection to remote temperature sensor(ex: thermal diode         |

|        |          |                                    |      | cathode)                                                                   |

| 4      | SST      | ILv/OD8-S1                         | 3VCC | Intel SST hardware monitor interface.                                      |

| 5      | GND      | PWR                                | зусс | Ground                                                                     |

| 6      | ALERT#   | OD <sub>12</sub>                   | зусс | Active LOW output. Used as SMBus alert or Interrupt                        |

| 7      | SDA      | IN <sub>ts</sub> /OD <sub>12</sub> | зусс | Serial bus data                                                            |

| 8      | SCL      | IN <sub>ts</sub>                   | зусс | Serial bus clock                                                           |

## 6. Functional Description

## 6.1 General Description

The F75395 is a simple temperature sensor with warning signal output. It includes a local and a remote temperature sensor. Both measured temperature are compared with its high, low and THERM limits which are stored in the registers. When one or more out-of-limit events occur, the flags in Status Register will be set and that may cause ALERT output to low. Also, measured temperature exceeding THERM limit may cause THERM output to low.

## 6.2 The warning message

Pin4 and pin6 act as warning message when the temperature exceeds it threshold point.

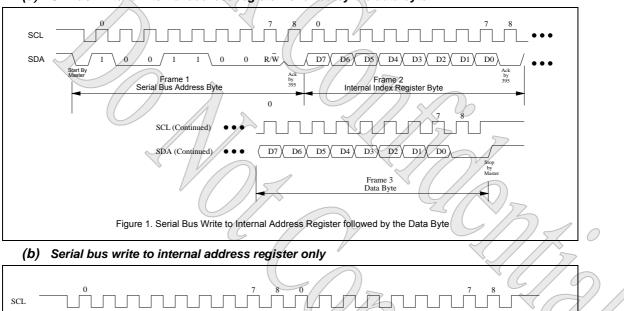

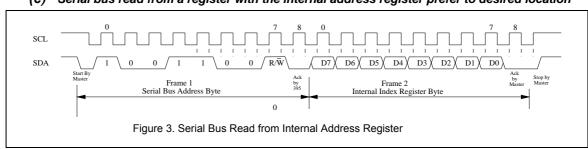

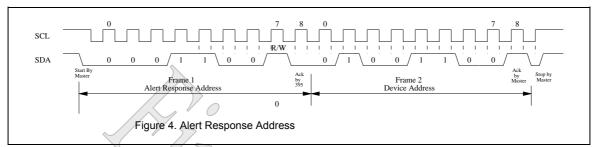

#### 6.3 Access Interface

The F75395 can be connected to a compatible 2-wire serial system management bus as a slave device under the control of the master device, using two device terminals SCL and SDA. The F75395 supports SMBus protocol of, "Write Byte", "Read Byte", both with or without Packet Error checking (PEC) which is calculated using CRC-8. For detail information about PEC, please check SMBus 1.1 specification. F75395 supports 25ms timeout for no activity on the SMBus. This timeout function is programmed at 22h bit7 and default is disabled. F75395 also supports Alert Response Address (ARA) protocol.

The operation of the protocol is described with details in the following sections.

SDA R/W D7 D6 D5 D4 0 D3 D1 D0Stop by Master Frame 1 Serial Bus Address Byt 0 Figure 2. Serial Bus Write to Internal Address Register Only (C) Serial bus read from a register with the internal address register prefer to desired location

(d) Alert Response Address

The F75395 provides SMBus address option function. Pull high register (Alert Pin) to select SMBus address by power on strapping and entry key writing. These two conditions must be done both for address selection. If you only option pull high register without entry key writing, the address will keep default value 98h. For example, use 30k resistor for address 6A selection. User need to write entry key to register CRFAh.

> Ex: Original chip default address is 98h Bus Access Byte Write (98, FA, 19) Bus Access Byte Write (98, FA, 34) Bus Access Byte Write (98, FA, 01) After Entry Key writing, Chip address will change to 6Ah.

The F75395 also support SST interface for PC system of Intel platform. The system can read temperature and related information by SST interface. The F75395 can be read by Intel chipset SST interface. (Direct connect chipset pin SST to the pin SST of F75395). About more detail, please refer Intel SST Spec. document (Protocol is edited by Intel).

#### 6.4 Temperature Monitoring

The F75395 monitors a local and a remote temperature sensor. Both can be measured from -40°C to 127.875°C. The temperature format is as the following table:

| Temperature ( High Byte ) | Digital Output | Temperature ( Low Byte ) | Digital Output |

|---------------------------|----------------|--------------------------|----------------|

| -40°C                     | 1101 1000      | -0.875°C                 | 001 0 0000     |

| -20°C                     | 1110 1100      | -0.325°C                 | 110 0 0000     |

| -1°C                      | 1111 1111      | -0.125°C                 | 111 0 0000     |

| 0°C                       | 0000 0000      | 0°C                      | 000 0 0000     |

| 50°C                      | 0011 0010      | 0.375°C                  | 011 0 0000     |

| 75°C                      | 0100 1011      | 0.500°C                  | 100 0 0000     |

| 100°C                     | 0110 0100      | 0.750°C                  | 110 0 0000     |

| 127°C                     | 0111 1111      | 0.875°C                  | 111 0 0000     |

#### Remote-sensor transistor manufacturers

| Manufacturer | Model Number   |

|--------------|----------------|

| Panasonic    | 2SB0709 2N3906 |

| Philips      | РМВТ3906       |

#### 6.5 Alert#

Five events can trigger ALERT# to low:

- (1). VT1(Local) temperature exceeds High Limit

- (2). VT1(Local) temperature goes below Low Limit

- (3). VT2(Remote) temperature exceeds High Limit

- (4). VT2(Remote) temperature goes below Low Limit

- (5). VT2(Remote) temperature is Open-circuit.

These five events are wired-NOR together. This means that when one of out-of-limit event occurs, the ALERT# output goes low if the MASK control is disabled. ALERT# signal can be used as an IRQ-like interrupt or as an SMBALERT. When ALERT# acts as an IRQ-like interrupt, the ALERT# will be de-asserted until the following 2 conditions are matched:

- (1). The abnormal condition is gone

- (2). Reading the Status register to clear the status

When ALERT# acts as a SMBALERT, the ALERT# will be de-asserted until the following 3 conditions are matched:

- (1). The abnormal condition is gone

- (2). Reading the Status register to clear the status

- (3). The ALERT# has been serviced by the SMBus master reading the device address.

For more information about SMBALERT, please see SMBus 1.1 specification.

#### 6.6 THERM#

Either VT1(Local) or VT2(Remote) temperature exceeds the corresponding THERM limit, the THERM# output will assert low. The asserted output will be de-asserted until the temperature goes below (THERM Limit – Hysteresis). The hysteresis default value is 10°C and it can be programmed. Both VT1 and VT2 have their own THERM limits and Hysteresis values.

#### 6.7 ADC Conversion Sequence

If a START command is written, both channels are converted and the results of both measurements are available after the end of conversion. A BUSY status bit in the status byte shows that the device is actually performing a new conversion; however, even if the ADC is busy, the results of the previous conversion are always available.

#### 6.8 Thermal Mass and Self Heating

Thermal mass effect can seriously degrade the F75395's effective accuracy. The thermal time constant of the MSOP package is about 140 in still air. For the F75395 junction temperature to settle to within  $\pm^{\circ}$ C after a sudden  $\pm^{\circ}$ O°C change requires about five time constants or 12 minutes. The use of smaller packages for remote sensors such as SOT23, improves the situation. Take care to account for thermal gradients between the heat source and the sensor package do not interfere with measurement accuracy. Sel-heating does not significantly affect measurement accuracy. Remote sensor self-heating due to the diode current source is negligible. For the local diode, the worst case error occurs when auto-converting at the fastest rate and simultaneously sinking maximum current at the ALERT# output. For instance, at an 64Hz rate and ALERT# sink around 0.7mA when pull up resistor 4.7K ohm to 3.3VCC, the typical power dissipation is VCC x 220 uA plus 0.4V x 0.7mA. Package JA is about 120 °C/W, so with VCC = 3.3V and no copper PC board heat-sinking, the resulting temperature rise is:

dT = 1.01mW x 120 °C/W = 0.12 °C

Even with these contrived circumstances, it is difficult to introduce significant self-heating errors.

#### 6.9 ADC Noise Filtering

The ADC is integrating type with inherently good noise rejection. Micro-power operation places constraints on high-frequency noise rejection; therefore, careful PCB board layout and suitable external filtering are required for high-accuracy remote measurement in electronically noisy environment. High frequency EMI is best filtered at D+ and D- with an external 2200pF capacitor. Too high capacitance may introduce errors due to the rise time of the switched current source. Nearly all noise sources tested cause the ADC measurement to be higher than the actual temperature, depending on the frequency and amplitude.

#### 6.10 Beta Compensation

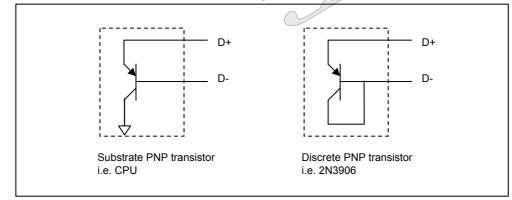

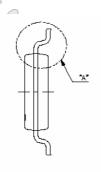

The F75395 is configured to detect the temperature of diodes (e.g. 2N3906) or CPU thermal diodes. The diode can be connected in different way as below Figure.

The basic of the temperature sensor follows mathematical formula as below:

$$\Delta V_{BE} = \frac{KT}{q} \times \ln \frac{Ie_1}{Ie_2} = \frac{KT}{q} \times \ln \frac{\left(\frac{1+\beta_1}{\beta_1}\right)Ic_1}{\left(\frac{1+\beta_2}{\beta_2}\right)Ic_2}$$

The F75395 measures temperature from the thermal diodes by the basic. In traditional case, the F75395 outputs dual currents to a thermal diode. Then the F75395 calculates the absolute temperature by  $V_{BE}$ . For discrete transistor (i.e. 2N3906), the beta is normally very high such that the percent change in beta is very small. For example, 15% variation in beta for two forced I<sub>E</sub> currents and the beta is 50 would contribute about 0.32 error per 100 . For Substrate PNP transistor (i.e. CPU), the beta is very small such that the proportional beta variation will very high, and it will cause large error in temperature measurement. For example, 15% variation in beta for two forced I<sub>E</sub> currents and the beta is 0.5 would contribute about 11.12 error per 100 .

In Order to solve the second issue, the F75395 provides a beta compensation solution for accurate temperature sensing. There is a register (CR30h bit7) for external thermal diode selection by Beta variation. If this bit is enabled, the beta compensation will automate to measure the temperature from substrate transistor (i.e. CPU). The F75395 can support the beta range from 0.05~1.8 for beta compensation. In this new method, the F75395 will provide two  $I_E$  currents, and feedback two  $I_B$  currents. The F75395 will auto-adjust  $I_E$  ( $I_{E1}$  and  $I_{E2}$ ) current and feedback  $I_B$  ( $I_{B1}$  and  $I_{B2}$ ) promptly for getting proper  $I_C$  proportion ( $I_{C1}/I_{C2}$ ), then calculates the accurate temperature. This algorithm of beta compensation is suitable for substrate transistor or new generational CPU (i.e. 45nm CPU) because small beta and high proportional beta variation. The default value of register CR3Bh bit7 is enabled for measure substrate transistor. If user would like to detect discrete transistor and the beta is big enough, please disable this bit for detecting. About this section application, please refer the register description for detail.

#### 6.11 Resistor Cancelled Function

The F75393/F75394 can cancel resistor effect from CPU internal circuit or PCB circuit.

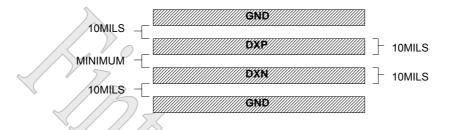

#### 6.12 PCB Layout Guide

PCB can be electrically noisy environments, and the F75395 is measuring very small voltage from the remote sensor, so care must be taken to minimize noise which is occurred at the sensor inputs. The following guideline should be taken to reduce the measurement error of the temperature sensors:

- Place the F75395 as close as practical to the remote sensing diode. In noisy environments, such as a computer main-board, the distance can be 4 to 8 inches. (typ). This length can be increased if the worst noise sources are avoided. Noise sources generally include clock generators, CRTs, memory buses and PCI/ISA bus etc.

- 2. Route the D+ and D- tracks close together, in parallel, with grounded guard tracks on each side. Provide a ground plane under the tracks if possible. Do not route D+ & D- lines next to the deflection coil of the CRT. And also don't route the trace across fast

digital signals which can easily induce bigger error.

- 3. Use wide tracks to minimize inductance and reduce noise pickup. 10 mil track minimum width and spacing is recommended.

- 4. Try to minimize the number of copper/solder joints, which can cause thermocouple effects. Where copper/solder joints are used, make sure that they are in both the D+ and D- path and at the same temperature. Thermocouple effects should not be a major problem as 1 corresponds to about 200µV. It means that a copper-solder thermocouple exhibits 3µV/ , and takes about 200µV of the voltage error at D+ & D- to cause a 1 measurement error. Adding a few thermocouples causes a negligible error.

- Place a 0.1µF bypass capacitor close to the VCC pin. In very noisy environments, place an external 2200pF input filter capacitors across D+, D- close to the F75395.

- 6. If the distance to the remote sensor is more than 8 inches, the use of twisted pair cable is recommended. It will work up to around 6 to 12 feet.

- 7. Because the measurement technique uses switched current sources, excessive cable and/or filter capacitance will affect the measurement accuracy. When using long cables, the filter capacitor may be reduced or removed. Cable resistance can also induce errors. 1 Ω series resistance introduces about 0.5 error.

## 7. Register Description

#### 7.1 Configuration Register — Index 03h(Read), 09h(Write)

| Bit | Name       | R/W | Default | Description                                                  |

|-----|------------|-----|---------|--------------------------------------------------------------|

| 7   | ALERT_MASK | R/W | 0       | Set to 1, mask ALERT# signal output.                         |

| 6   | RUN_STOP   | R/W | 0       | Set to 0, monitor. Set to 1, stop monitor (power down mode). |

| 5-1 | Reserved   | RO  | 0       | Reserved, always return 0.                                   |

| 0   | PWR_DON    | R/W | 0       | Power down this device.                                      |

#### 7.2 Status Register — Index 02h

\$

| Bit | Name     | R/W | Default | Description                                              |

|-----|----------|-----|---------|----------------------------------------------------------|

| 7   | ADC_BUSY | RO  | 0       | Set to 1, ADC is converting.                             |

| 6   | VT1HIGH  | RO  | 0       | Set to 1, VT1 temperature exceeds high limit.            |

|     |          |     | 3       | Set to 0, VT1 temperature does not exceed high limit.    |

| 5   | VT1LOW   | RO  | 0       | Set to 1, VT1 temperature goes below low limit.          |

|     |          |     |         | Set to 0, VT1 temperature does not goes below low limit. |

| 4   | VT2HIGH  | RO  | 0       | Set to 1, VT2 temperature exceeds high limit.            |

|     | 5        |     |         | Set to 0, VT2 temperature does not exceed high limit.    |

| 3   | VT2LOW   | RO  | 0       | Set to 1, VT2 temperature goes below low limit.          |

|     |          |     |         | Set to 0, VT2 temperature does not goes below low limit. |

| 2   | OPEN     | RO  | 0       | Set to 1, VT2 is open-circuit.                           |

| 1   | VT2THERM | RO  | 0       | Set to 1, VT2 temperature exceeds its THERM limit.       |

| 0   | VT1THERM | RO  | 0       | Set to 1, VT1 temperature exceeds its THERM limit.       |

VT1 (Local); VT2 (Remote)

### 7.3 Conversion Rate Register — Index 04h(Read), 0Ah(Write)

| Bit | Name      | R/W | Default | 6 //         | Desci               | ription   | 120            |

|-----|-----------|-----|---------|--------------|---------------------|-----------|----------------|

| 7-0 | CONV_RATE | R/W | 08h     | Set conversi | on times per second | ı. V      | 7              |

|     |           |     |         | Value        | Conversion/Sec      | Value     | Conversion/Sec |

|     |           |     |         | 00h          | 0.0625              | 06h       | 4              |

|     |           |     |         | 01h          | 0.125               | 07h       | 8 6            |

|     |           |     |         | 02h          | 0.25                | 08h       | 16             |

|     |           |     |         | 03h          | 0.5                 | 09h       | 32             |

|     |           |     |         | 04h          | 1                   | 0Ah       | 64             |

|     |           |     |         | 05h          | 2                   | 0Bh ~ FFh | Reserved       |

### 7.4 One-Shot Register — Index 0Fh

| Bit | Name     | R/W | Default | Description                                                       |

|-----|----------|-----|---------|-------------------------------------------------------------------|

| 7-0 | ONE-SHOT | WO  | xxh     | When chip is at standby mode, writing any value to this register  |

|     |          |     |         | will initiate a single conversion and comparison cycle. After the |

|     |          |     |         | single cycle, chip will returns to standby mode.                  |

#### 7.5 Alert Queue & Timeout Register — Index 22h

\$

| Bit | Name        | R/W      | Default | Description                                                       |  |

|-----|-------------|----------|---------|-------------------------------------------------------------------|--|

| 7   | EN_I2CTMOUT | R/W      | 0       | Set to 1, enable serial interface timeout function. (Timeout time |  |

|     |             | $\sum 5$ | 7       | 25ms)                                                             |  |

|     |             |          | 57      | Set to 0, disable.                                                |  |

| 6-4 | Reserved    | RO       | 0       | 1                                                                 |  |

| 3-1 | ALERT_QUEUE | R/W      | 0       | This number determines how many abnormal measurements             |  |

|     |             |          |         | must occur before ALERT signal is generated.                      |  |

|     |             | ~        | G//     | 000 : Once                                                        |  |

|     |             |          |         | 001 : Twice                                                       |  |

|     | $\sum$      |          | $\sim$  | 011 : 3 times                                                     |  |

|     |             |          |         | 111 : 4 times                                                     |  |

| 0   | Reserved    | RO       | 1       | Always read 1.                                                    |  |

### 7.6 Status-with-ARA Control Register — Index 24h

| Bit | Name       | R/W | Default | Description                                                |

|-----|------------|-----|---------|------------------------------------------------------------|

| 7-1 | Reserved   | RO  | 0       | Reserved                                                   |

| 0   | EN_ARA_STS | R/W |         | Set to 1, ALERT de-asserted condition is related with ARA. |

|     |            |     |         | Set to 0, ALERT de-asserted condition is not related with  |

|     |            |     |         | ARA(Alert Response Address).                               |

## 7.7 Beta Compensation Register Index 3Bh

| Bit | Name        | R/W | Default | Description                             |  |  |  |

|-----|-------------|-----|---------|-----------------------------------------|--|--|--|

| 7   | BETA_EN     | R/W | 1       | 1: Enable beta compensation function.   |  |  |  |

|     |             |     |         | 0: Disable beta compensation function.  |  |  |  |

| 6   | BIAS_SEL    | R/W | 0       | 0: DN pad BIAS voltage 150mV            |  |  |  |

|     |             |     |         | 1: DN pad BIAS voltage 220mV            |  |  |  |

| 5-4 | Reserved    | R/W | 0h      | Dummy registers.                        |  |  |  |

| 3   | R_CANCELLED | R/W | 1       | 1: Enable resister cancelled function.  |  |  |  |

|     |             |     |         | 0: Disable register cancelled function. |  |  |  |

| 2-0 | Reserved    | R/W | 2h      | Dummy registers.                        |  |  |  |

57

#### 7.8 SST Address Register—Index 3Dh

| Bit Name R/W Default Description |

|----------------------------------|

|----------------------------------|

170

57

| 7   | Reserved | RO  | 0h  | Always return 0                                  |

|-----|----------|-----|-----|--------------------------------------------------|

| 6-0 | SST_ADDR | R/W | 4ch | User can program this byte to change SST address |

### 7.9 Chip ID (MSB) Register—Index 5Ah

| Bit | Name      | R/W De | efault | Description      |

|-----|-----------|--------|--------|------------------|

| 7-0 | F_CHIP_ID | RO     | 07h    | Eintek Chip ID 1 |

### 7.10 Chip ID (LSB) Register - Index 5Bh

| Bit | Name      | R/W | Default | Description      |

|-----|-----------|-----|---------|------------------|

| 7-0 | F_CHIP_ID | RO  | 07h     | Fintek Chip ID 2 |

## 7.11 Fintek Vendor ID (MSB) (Manufacturer ID) Register — Index 5Dh

| Bit | Name        | R/W Default | Description        |

|-----|-------------|-------------|--------------------|

| 7-0 | F_VENDOR_ID | RO 19h      | Fintek Vendor ID 1 |

## 7.12 Fintek Vendor ID (LSB) (Manufacturer ID) Register — Index 5Eh

| Bit | Name        | R/W | Default |                    | Description |

|-----|-------------|-----|---------|--------------------|-------------|

| 7-0 | F_VENDOR_ID | RO  | 34h     | Fintek Vendor ID 2 |             |

#### 7.13 Fintek Vendor ID II (Manufacturer ID) Register—Index FEh

| -   |           |     |         |             | 7 |

|-----|-----------|-----|---------|-------------|---|

| Bit | Name      | R/W | Default | Description |   |

| 7-0 | VENDOR_ID | R/W | 23h     | Vendor ID   |   |

|     |           |     |         |             |   |

115

#### 7.14 Value RAM — Index 10h- 2Fh

VT1 : Local Temperature

VT2 : Remote Temperature

#### The value in quota is its power-on default value.

| Description | Attribute | Read<br>Address | Read<br>Address | Write<br>Address | Write<br>Address |

|-------------|-----------|-----------------|-----------------|------------------|------------------|

|             |           | (High Byte)     | (Low Byte)      | (High Byte)      | (Low Byte)       |

| VT1 reading | RO        | 00h             | 1Ah             |                  |                  |

| VT2 reading          | RO     | 01h                  | 10h                  |     |     |

|----------------------|--------|----------------------|----------------------|-----|-----|

|                      |        |                      |                      |     |     |

| VT1 High Limit       | R/W    | 05h <sub>(55h)</sub> | 1Bh (00h)            | 0Bh | 1Bh |

| VT1 Low Limit        | R/W    | 06h <sub>(00h)</sub> | 1Ch (00h)            | 0Ch | 1Ch |

| VT2 High Limit       | R/W    | 07h <sub>(55h)</sub> | 13h <sub>(00h)</sub> | 0Dh | 13h |

| VT2 Low Limit        | R/W    | 08h <sub>(00h)</sub> | 14h <sub>(00h)</sub> | 0Eh | 14h |

|                      | //) 5. |                      |                      |     |     |

| VT1 THERM limit      | R/W    | 20h (55h)            |                      | 20h |     |

| VT1 THERM Hysteresis | R/W    | 21h (0Ah)            |                      | 21h |     |

| VT2 THERM limit      | R/W    | 19h (55h)            |                      | 19h |     |

| VT2 THERM Hysteresis | R/W    | 23h <sub>(0Ah)</sub> |                      | 23h |     |

|                      |        |                      |                      |     |     |

| VT1 Offset           | R/W    | 1Dh (00h)            | 1Eh (00h)            | 1Dh | 1Eh |

| VT2 Offset           | R/W    | 11h (00h)            | 12h (00h)            | 11h | 12h |

## 7.15 SST Command Table

| 7.15 SST Cor | nmand Table                      |                                                                                          |

|--------------|----------------------------------|------------------------------------------------------------------------------------------|

| Command      | WL/RL/CC                         | Description                                                                              |

| GetExtTemp() | 0x01/0x02/0x01                   | Use 0x4C SST address (default CR3D) and command 0x01 to get F75395 external temperature. |

| GetIntTemp() | 0x01/0x02/0x02                   | Use 0x4C SST address (default CR3D) and command 0x02 to get F75395 internal temperature. |

| GetAllTemp() | 0x01/0x04/0x01                   | Returns a 4-byte block of data.                                                          |

| GetDIB()     | 0x01/0x08/0xf7<br>0x01/0x10/0xf7 | 8 bytes of DIB information.<br>16 bytes of DIB information.                              |

|              |                                  |                                                                                          |

# 8. Electrical characteristic

## 8.1 Absolute Maximum Ratings

| PARAMETER             | RATING          | UNIT |

|-----------------------|-----------------|------|

| Power Supply Voltage  | -0.5 to 5.5     | V    |

| Input Voltage         | -0.5 to VDD+0.5 | V    |

| Operating Temperature | 0 to 70         | ° C  |

| Storage Temperature   | -55 to 150      | ° C  |

Note: Exposure to conditions beyond those listed under Absolute Maximum Ratings may adversely affect the life and reliability of the device

## 8.2 DC Characteristics

(T\_A = 0° C to 70° C, VDD = 3.3V  $\pm$  10%, VSS = 0V)

| Parameter                        | Conditions                                                                                                      | MIN | ТҮР   | МАХ    | Unit |   |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------|-----|-------|--------|------|---|

| Temperature Error, Remote Diode  | $60 ^{\circ}\text{C} < \text{T}_{\text{D}} < 100 ^{\circ}\text{C}, \text{ VCC} = 3.0 \text{V to } 3.6 \text{V}$ |     | ±1/   | 5      | °С   |   |

|                                  | -40 °C <t<sub>D &lt; 60°C, 100 °C <t<sub>D &lt; 127°C</t<sub></t<sub>                                           |     | ± 1   | ±3     |      |   |

| Temperature Error, Local Diode   | $0^{\circ}C < T_{A} < 100^{\circ}C$ , VCC = 3.0V to 3.6V                                                        |     | ±1    | ± 3    | °C   | 5 |

| Supply Voltage range             |                                                                                                                 | 3.0 | 3.3   | 3.6    | v    |   |

| Average operating supply current | 16 Conversions / Sec Rate                                                                                       |     | 280   | Z      | uA   |   |

|                                  | 0.0625 Conversions / Sec Rate                                                                                   |     | 180   | $\sim$ | uA   |   |

| Standby supply current           |                                                                                                                 |     | 5     |        | uA   |   |

| Resolution                       |                                                                                                                 |     | 0.125 |        | °C   |   |

| Under-voltage lockout threshold  | VDD input, Disables ADC , Rising Edge                                                                           |     | 2.55  |        | V    |   |

| Power on reset threshold         |                                                                                                                 |     | 2.2   | 2.4    | V    |   |

| Diode source current             | High Level                                                                                                      |     | 95    |        | uA   |   |

|                                  | Low Level                                                                                                       |     | 10    |        | uA   |   |

-

| PARAMETER                                       | SYM.         | MIN.         | TYP.         | MAX.       | UNIT     | CONDITIONS            |

|-------------------------------------------------|--------------|--------------|--------------|------------|----------|-----------------------|

| I/O <sub>12t</sub> - TTL level bi-directional p | in with sou  | rce-sink ca  | pability of  | 12 mA      |          |                       |

| Input Low Voltage                               | VIL          |              |              | 0.8        | V        |                       |

| Input High Voltage                              | VIH          | 2.0          |              |            | V        |                       |

| Output Low Current                              | IOL          | 10           | 12           |            | mA       | VOL = 0.4V            |

| Output High Current                             | ЮН           | 1            | -12          | -10        | mA       | VOH = 2.4V            |

| Input High Leakage                              | КІН          |              | 57           | +1         | μA       | VIN = VDD             |

| Input Low Leakage                               | ILIL         | $\sim$       |              | -1         | μA       | VIN = 0V              |

| I/O <sub>12ts</sub> - TTL level bi-directional  | pin with sou | urce-sink c  | apability of | f 12 mA an | d schmit | t-trigger level input |

| Input Low Threshold Voltage                     | Vt-          | 0.5          | 0.8          | 1,1        | V        | VDD = 3.3 V           |

| Input High Threshold Voltage                    | Vt+          | 1.6          | 2.0          | 2.4        | V        | VDD = 3.3 V           |

| Output Low Current                              | IOL          | 10           | 12           | $\bigcirc$ | mA       | VOL = 0.4 V           |

| Output High Current                             | IOH          |              | -12          | -10        | mA       | VOH = 2.4V            |

| Input High Leakage                              | ІЦІН         |              |              | +1         | μA       | VIN = VDD             |

| Input Low Leakage                               | 1LIL         |              |              | -1         | μA       | VIN = 0V              |

| OUT <sub>12t</sub> - TTL level output pin wi    | th source-s  | ink capabil  | lity of 12 m | A          |          | $\sim$                |

| Output Low Current                              | IOL          | 12           | 16           | $\sim$     | mA       | VOL = 0.4V            |

| Output High Current                             | юн           | $//\sim$     | -14          | -12        | mA       | VOH = 2.4V            |

| OD <sub>16</sub> - Open-drain output pin w      | th sink cap  | ability of 1 | 6 mA         | 4          |          |                       |

| Output Low Current                              | IOL          | 12           | 16           |            | mA       | VOL = 0.4V            |

| IN <sub>ts</sub> - TTL level Schmitt-trigg      | ered input   | oin 🤇        | >//          | $\sum$     |          | × C/ S                |

| Input Low Threshold Voltage                     | Vt-          | 0.5          | 0.8          | 1.1        | V        | VDD = 3.3V            |

| Input High Threshold Voltage                    | Vt+          | 1.6          | 2.0          | 2.4        | v        | VDD = 3.3V            |

| Input High Leakage                              | ILIH         |              |              | +1         | μA       | VIN = VDD             |

| Input Low Leakage                               | ILIL         |              |              | 1          | μA       | VIN = 0 V             |

#### (T\_A = 0° C to 70° C, VDD = 3.3V $\pm$ 10%, VSS = 0V)

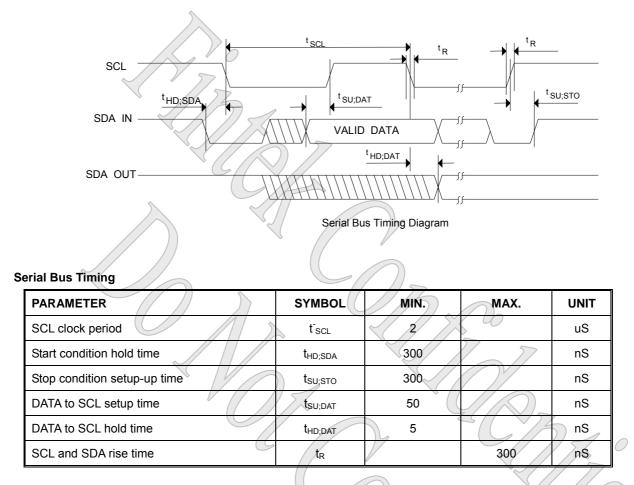

## 8.3 AC Characteristics

## 9. Ordering Information

| Part Number | Package Type         | Production Flow          |

|-------------|----------------------|--------------------------|

| F75395M     | 8-MSOP Green Package | Commercial, 0°C to +70°C |

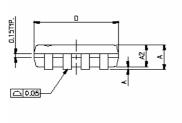

## **10. Package Dimensions**

| SYMBOLS | MIN.      | NOM. | MAX.     |  |  |

|---------|-----------|------|----------|--|--|

| A       | -         | -    | 1.10     |  |  |

| A1      | 0.00      | -    | Ď.15     |  |  |

| A2      | 0.75      | 0.85 | 0.95     |  |  |

| D       | 3.00 BSC  |      |          |  |  |

| E       | 4.90 BSC  |      |          |  |  |

| E1      | 3.00 BSC  |      |          |  |  |

| L       | 0.40 0.60 |      | D.80     |  |  |

| L1      | 0.95 REF  |      |          |  |  |

| θ.      | 0         | —    | 8        |  |  |

|         |           |      | INT . NH |  |  |

UNIT : MM

#### NOTES:

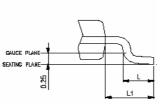

- NOTES: 1.JEDEC OUTLINE : NO-187 AA 2.DIMENSION 'D' DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR CATE BURRS. MOLD FLASH, PROTRUSIONS DR GATE BURRS SHALL NOT EXCEED Q.15 PER SIDE. 3.DIMENSION 'E1' DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL INTERLEAD FLASH OR PROTRUSION SHALL

- NOT EXCEED 0.25 PER SIDE. 4. DIMENSION '0.22' DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE D.O.B MM TOTAL IN EXCESS OF THE '0.22' DIMENSION AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADUS OF THE FOOT. MINIMUM SPAC BETWEEN PROTRUSION AND ADJACENT LEAD IS 0.07 MM. 5.DMENSIONS 'D' AND 'E1' TO BE DETERMINED AT DATUM PLANE TH PLANE III

#### FILE Feature Integration Technology Inc.

Headquarters 3F-7, No 36, Tai Yuan St., Chupei City, Hsinchu, Taiwan 302, R.O.C. TEL: 886-3-5600168 FAX: 886-3-5600166 www: http://www.fintek.com.tw

#### Taipei Office

Bldg. K4, 7F, No.700, Chung Cheng Rd., Chungho City, Taipei, Taiwan 235, R.O.C. TEL: 866-2-8227-8027 FAX: 866-2-8227-8037

Please note that all datasheet and specifications are subject to change without notice. All the trade marks of products and companies mentioned in this datasheet belong to their respective owner

## **11. Application Circuit**