# 16-bit Proprietary Microcontroller

**CMOS**

# F<sup>2</sup>MC-16F MB90210 Series

# MB90214/P214A/P214B/W214A/W214B/V210

#### DESCRIPTION

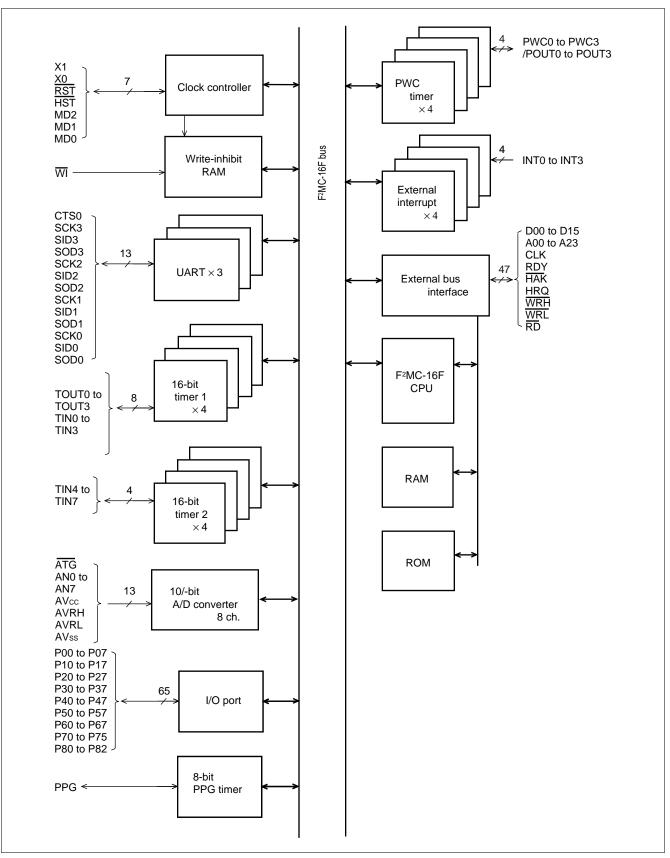

The MB90210 series is a line of 16-bit microcontrollers particularly suitable for system control of video cameras, VTRs, and copiers. The F<sup>2</sup>MC-16F CPU integrated in this series is based on the F<sup>2</sup>MC\*-16, while providing enhanced instructions for high-level languages and supporting extended addressing modes.

The MB90210 series incorporates a variety of peripheral resources such as a PWC timer with 4 channels, a 10/ 8-bit A/D converter with 8 inputs, UART serial ports with 3 channels (1 channel for CTS and 1 channel for dual input/output pin switching), 16-bit reload timers with 8 channels, and an 8-bit PPG timer with 1 channel.

MB90P214B/W214B is under development.

\*: F<sup>2</sup>MC stands for FUJITSU Flexible Microcontroller.

#### PACKAGE

#### ■ FEATURES

#### F<sup>2</sup>MC-16F CPU

- Minimum execution time: 62.5 ns/16-MHz oscillation (using a duty control system)

- Instruction sets optimized for controllers

Upward object-compatible with the F<sup>2</sup>MC-16(H)

Various data types (bit, byte, word, and long-word)

Instruction cycle improved to speed up operation

Extended addressing modes: 25 types

High coding efficiency

Access method (bank access with linear pointer)

Enhanced multiplication and division instructions (with signed instructions added)

Higher-precision operation using a 32-bit accumulator

- Extended intelligent I/O service (Automatic transfer function independent of instructions) access area expanded to 64 Kbytes

- Enhanced instruction set applicable to high-level language (C) and multitasking System stack pointer

Enhanced pointer-indirect instructions

Barrel shift instruction

Stack check function

- Increased execution speed: 8-byte instruction queue

Powerful interrupt functions: 8 levels and 29 sources

- Towerial interrupt functions. O levels and 25

#### **Integrated Peripheral Resources**

- ROM: 64 Kbytes (MB90214)

EPROM: 64 Kbytes (MB90W214A/W214B)

OTPROM: 64Kbytes (MB90P214A/P214B)

- RAM: 3 Kbytes (MB90214) 4 Kbytes (MB90P214A/P214B/W214A/W214B/V210)

- General-purpose ports: max. 65 channels

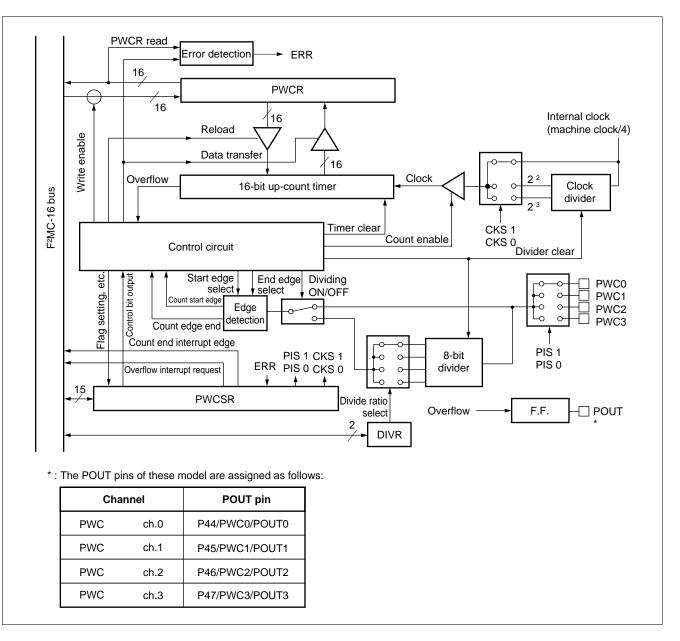

- PWC timer with time measurement function: 4 channels

- 10- or 8-bit A/D converter: 8 channels

- UART: 3 channels

- Including: 1 channel with CTS function

- 1 channel with I/O pin switching function

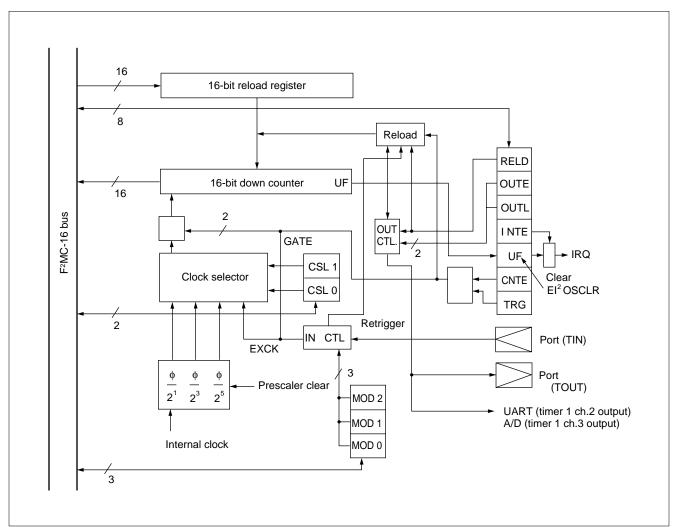

- 16-bit reload timer

Toggled output, external clock, and gate functions: 4 channels

- External clock and gate functions: 4 channels

- 8-bit PPG timer: 1 channel

- External-interrupt inputs: 4 channels

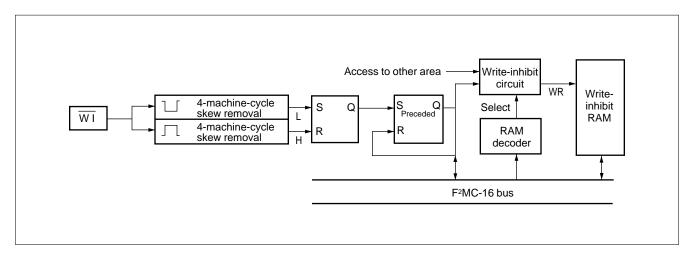

- Write-inhibit RAM: 256 bytes (MB90V210: 512 bytes)

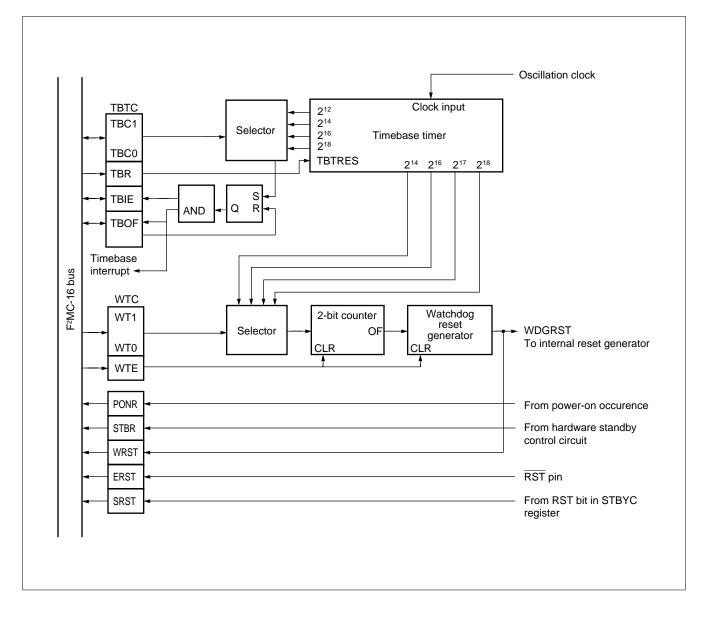

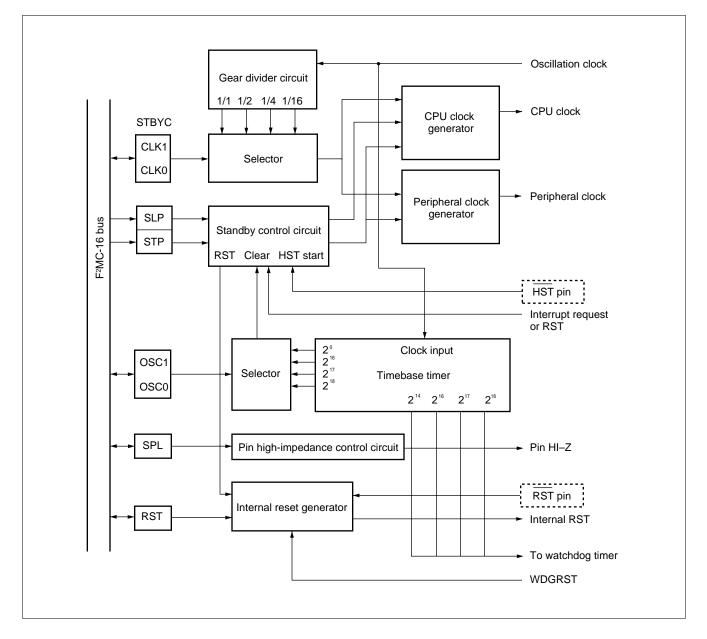

- Timebase counter: 18 bits

- Clock gear function

- Low-power consumption mode

- Sleep mode

- Stop mode

- Hardware standby mode

#### **Product Description**

- MB90214 is a mask ROM product.

- MB90P214A/P214B are OTPROM products.

- MB90W214A/W214B are EPROM products. ES only.

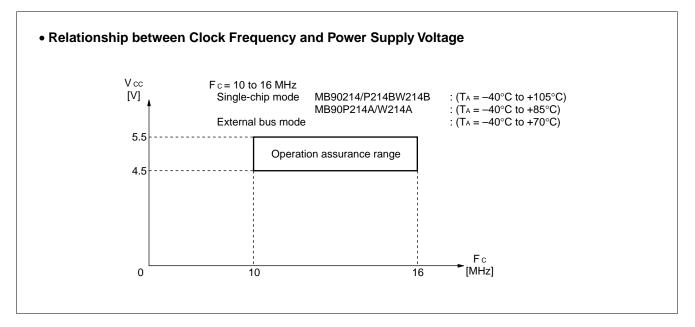

- Operating temperature of MB90P214A/W214A is -40°C to +85°C.

- (However, the AC characteristics is assured in  $-40^{\circ}$ C to  $+70^{\circ}$ C)

- MB90V210 is a evaluation device for the program development. ES only.

#### ■ PRODUCT LINEUP

| Part number<br>Parameter | MB90214                                                                                                                                                                                                                                                                                                                        | MB90P214A<br>MB90P214B                            | MB90W214A<br>MB90W214B                                                                            | MB90V210               |  |  |  |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------|--|--|--|

| Classification           | Mask ROM product                                                                                                                                                                                                                                                                                                               | OTPROM product                                    | EPROM product                                                                                     | For evaluation         |  |  |  |

| ROM size                 | 64 Kbytes                                                                                                                                                                                                                                                                                                                      | 64 Kbytes                                         | 64 Kbytes                                                                                         | —                      |  |  |  |

| RAM size                 | 3 Kbytes                                                                                                                                                                                                                                                                                                                       | 4 Kbytes                                          | 4 Kbytes                                                                                          | 4 Kbytes               |  |  |  |

| CPU functions            | Number of ins<br>Instruction bit<br>Instruction ler<br>Data bit lengtl<br>Minimum exec<br>Interrupt proc                                                                                                                                                                                                                       | length:<br>ngth:<br>h:<br>cution time:            | 420<br>8 or 16 bits<br>1 to 7 bytes<br>1, 4, 8, 16, or 32 l<br>62.5 ns/16 MHz<br>1.0 μs/16 MHz (m |                        |  |  |  |

| Ports                    | I/O ports (N-c<br>I/O ports (CM<br>Total:                                                                                                                                                                                                                                                                                      | h open-drain):<br>OS):                            | 8<br>57<br>65                                                                                     |                        |  |  |  |

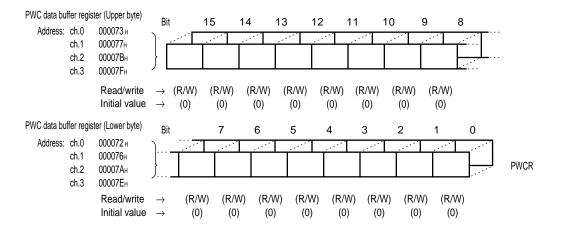

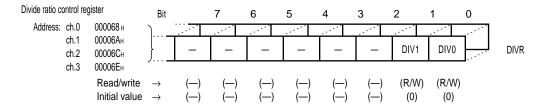

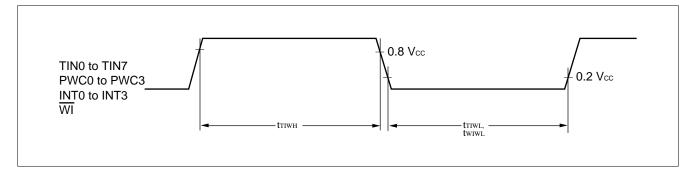

| PWC timer                | 16-bit pulse-width cou                                                                                                                                                                                                                                                                                                         | timer operation (opera<br>int operation (Allowing | channels: 4<br>ting clock cycle: 0.25 μ<br>continuous/one-shot me<br>t, and divided-frequenc      | easurement, H/L width  |  |  |  |

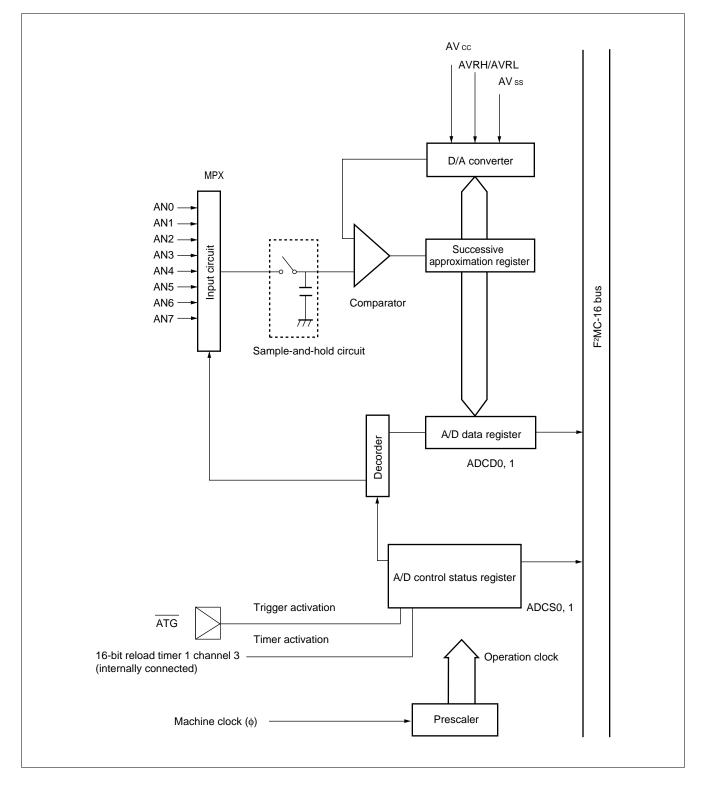

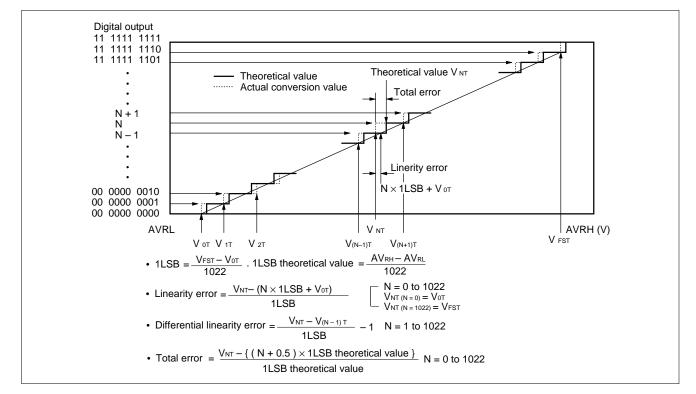

| A/D converter            | Resolution: 10 or 8 bits, Number of inputs: 8<br>Single conversion mode (conversion for each input channel)<br>Scan conversion mode (continuous conversion for up to 8 consecutive channels)<br>Continuous conversion mode (repeated conversion for a selected channel)<br>Stop conversion mode (conversion every fixed cycle) |                                                   |                                                                                                   |                        |  |  |  |

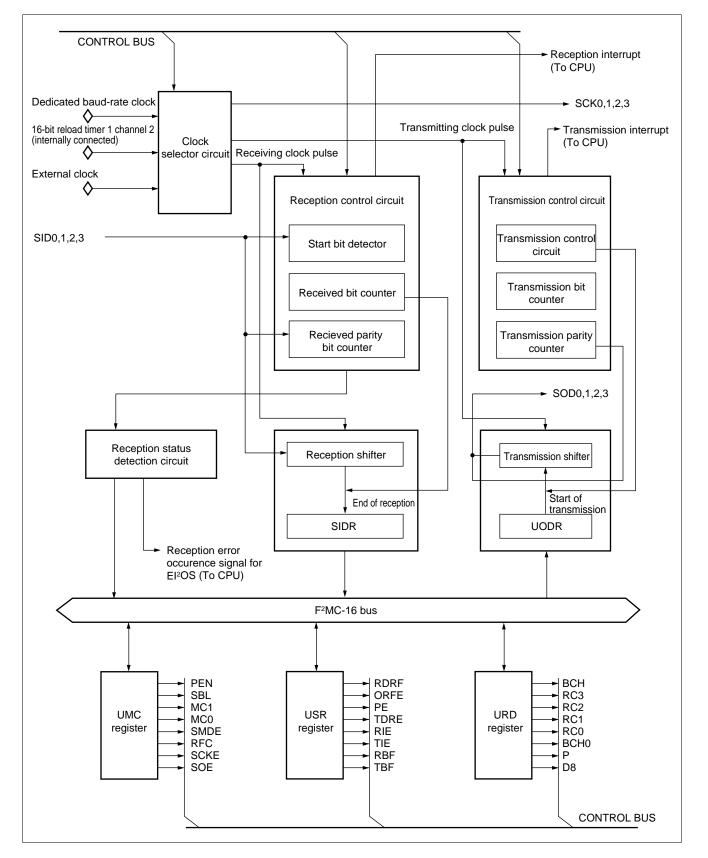

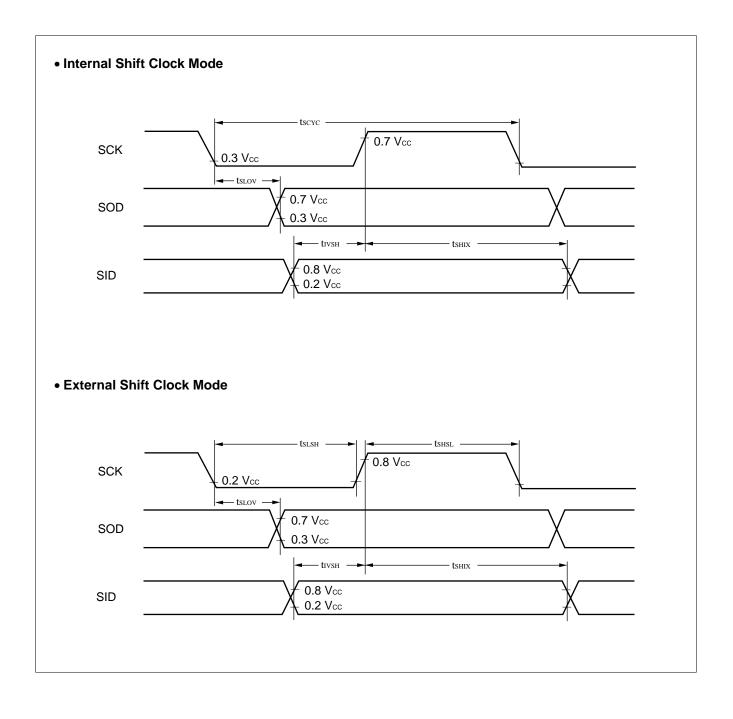

| UART                     | Number of channels: 3<br>(1 channel with CTS function; 1 channel with I/O pin switching function)<br>Clock-synchronous transfer mode<br>(full-duplex double buffering, 7- to 9-bit data length, 2400 to 62500 bps)<br>Asynchronous transfer mode<br>(full-duplex double buffering, 7- to 9-bit data length, 2400 to 62500 bps) |                                                   |                                                                                                   |                        |  |  |  |

| Timer                    | 16-bit reloa                                                                                                                                                                                                                                                                                                                   |                                                   | : 4 channels $\times$ 2 types<br>ating clock cycle: 0.25                                          | us to 1.05 s)          |  |  |  |

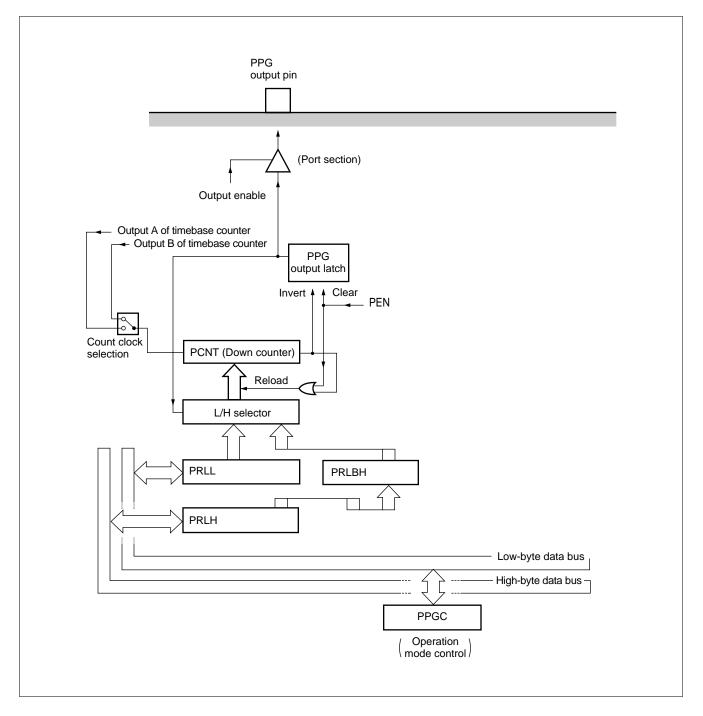

| PPG timer                | Number of channels: 1<br>8-bit PPG operation (operating clock cycle: 0.25 μs to 6 s)                                                                                                                                                                                                                                           |                                                   |                                                                                                   |                        |  |  |  |

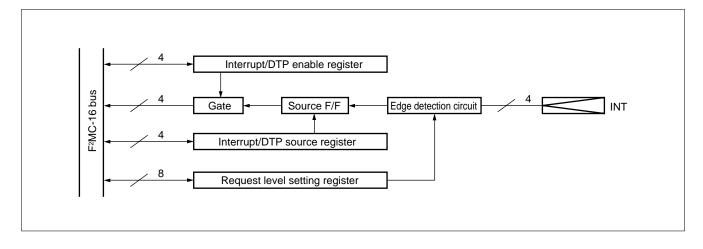

| External interrupt       | Number of inputs: 4<br>External interrupt mode (allowing interrupts to activate at four different request levels)<br>Simple DMA start mode (allowing extended I <sup>2</sup> OS to activate at two different request levels)                                                                                                   |                                                   |                                                                                                   |                        |  |  |  |

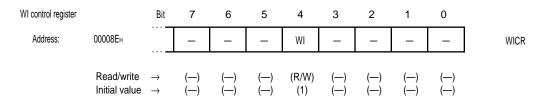

| Write-inhibit RAM        | RAM size: 256 bytes (MB90V210: 512 bytes)<br>RAM write-protectable with WI pin                                                                                                                                                                                                                                                 |                                                   |                                                                                                   |                        |  |  |  |

| Standby mode             | Stop mode (activated by software or hardware) and sleep mode                                                                                                                                                                                                                                                                   |                                                   |                                                                                                   |                        |  |  |  |

| Gear function            | Machine clock opera                                                                                                                                                                                                                                                                                                            | ating frequency switchir                          | ng: 16, 8, 4, or 1 MHz (a                                                                         | at 16 MHz oscillation) |  |  |  |

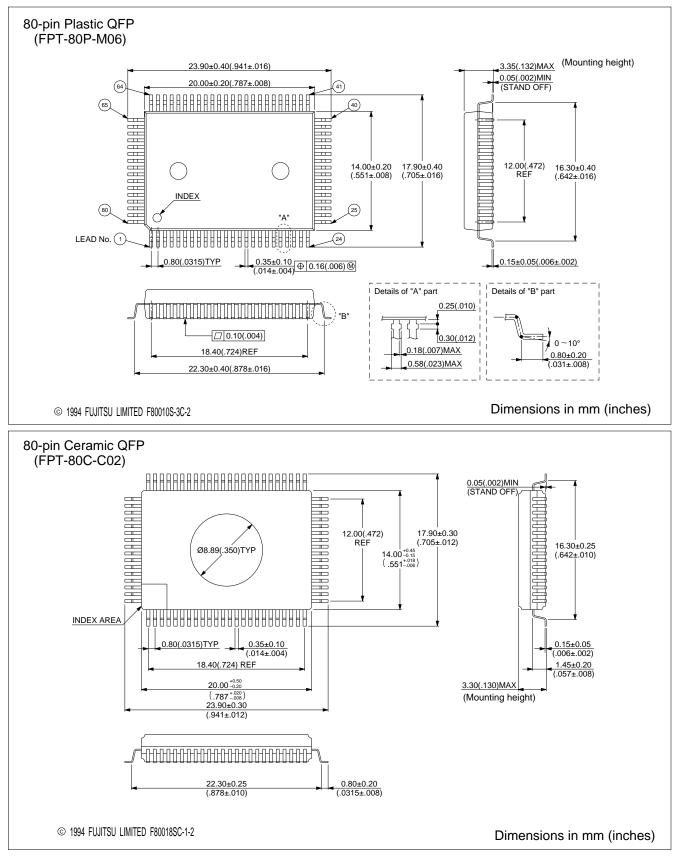

| Package                  | FPT-80                                                                                                                                                                                                                                                                                                                         | DP-M06                                            | FPT-80C-C02                                                                                       | PGA-256C-A02           |  |  |  |

#### ■ DIFFERENCES BETWEEN MB90214 (MASK ROM PRODUCT) AND MB90P214A/P214B/ W214A/W214B

| Part number             | MB90214   | MB90P214A               | MB90W214A |

|-------------------------|-----------|-------------------------|-----------|

| Parameter               |           | MB90P214B               | MB90W214B |

| ROM                     | Mask ROM  | OTPROM                  | EPROM     |

|                         | 64 Kbytes | 64 Kbytes               | 64 Kbytes |

| Pin function<br>43 pins | MD2 pin   | MD2/V <sub>PP</sub> pin |           |

Note: MB90V210, device used for evaluation, is not warranted for electrical specifications.

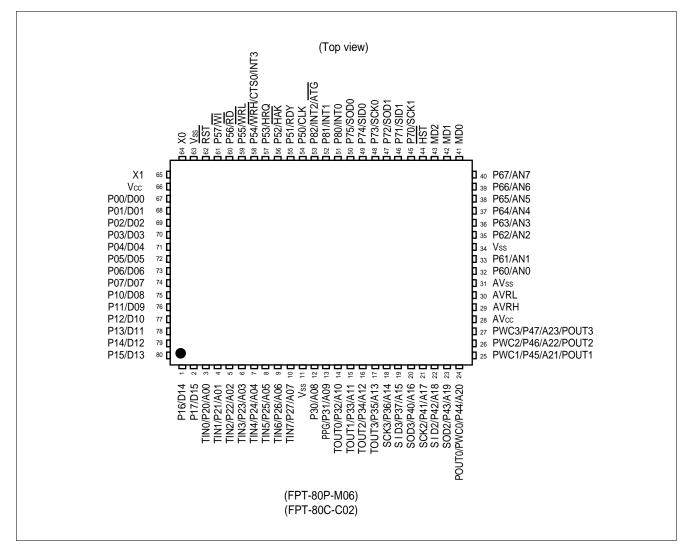

#### ■ PIN ASSIGNMENT

#### ■ PIN DESCRIPTION

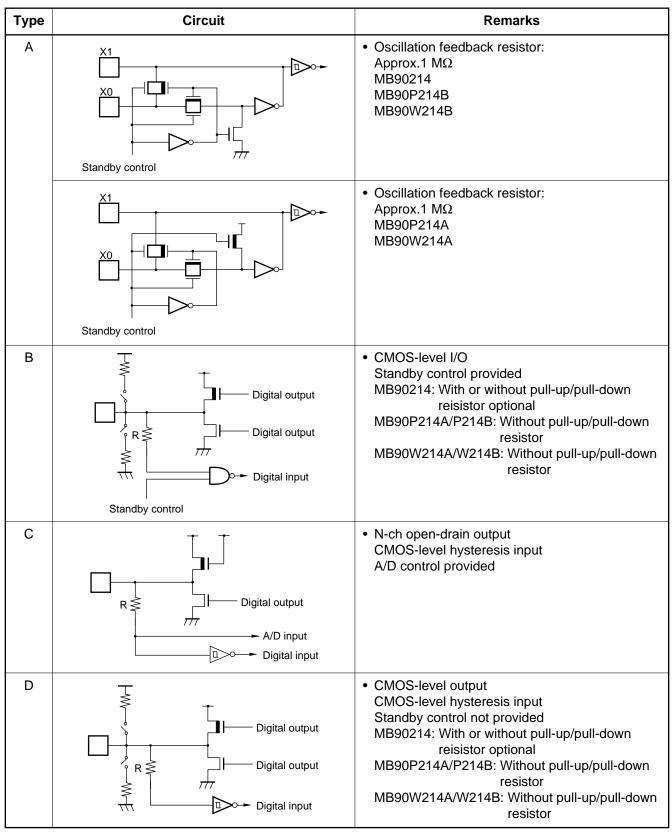

| Pin no.          |              | Circuit |                                                                                                                                                                                                                                                                 |

|------------------|--------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QFP*             | Pin name     | type    | Function                                                                                                                                                                                                                                                        |

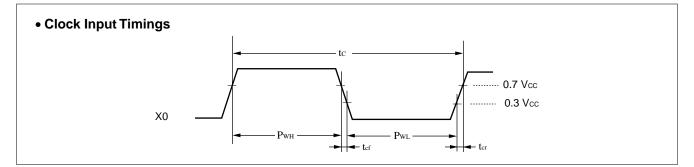

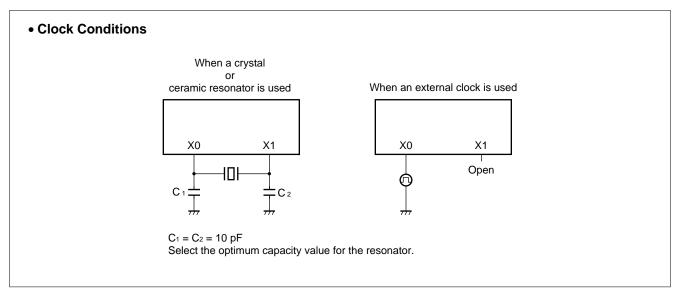

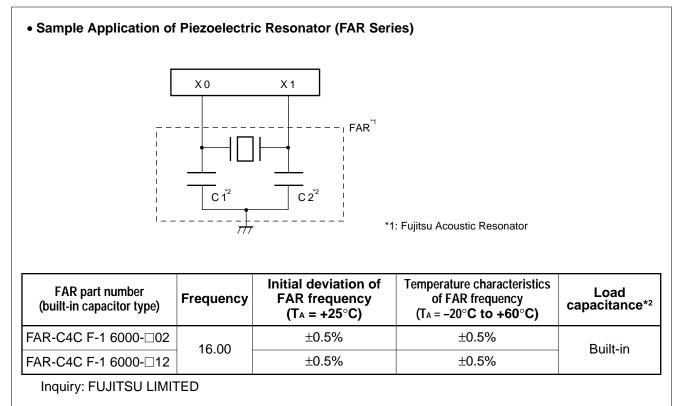

| 64, 65           | X0<br>X1     | A       | Crystal oscillator pins (16 MHz)                                                                                                                                                                                                                                |

| 67 to 74         | P00 to P07   | В       | General-purpose I/O ports<br>These ports are available only in the single-chip mode.                                                                                                                                                                            |

|                  | D00 to D07   |         | I/O pins for the lower eight bits of external data bus<br>These pins are available in an external-bus mode.                                                                                                                                                     |

| 75 to 80<br>1, 2 | P10 to P17   | В       | General-purpose I/O ports<br>These ports are available in the single-chip mode and in an<br>external-bus mode with the 8-bit data bus specified.                                                                                                                |

|                  | D08 to D15   |         | I/O pins for the upper eight bits of external data bus<br>These pins are available in an external-bus mode with the 16-bit<br>data bus specified.                                                                                                               |

| 3 to 6           | P20 to P23   | E       | General-purpose I/O ports<br>These ports are available only in the single-chip mode.                                                                                                                                                                            |

|                  | A00 to A03   |         | Output pins for external address buses A00 to A03<br>These pins are available in an external-bus mode.                                                                                                                                                          |

|                  | TIN0 to TIN3 |         | 16-bit reload timer 1 (ch.0 to ch.3) input pins<br>These pins are available when the 16-bit reload timer 1 (ch.0 to<br>ch.3) input specification is "enabled". The data on the pin is read<br>as the 16-bit reload timer 1 (ch.0 to ch.3) input (TIN0 to TIN3). |

| 7 to 10          | P24 to P27   | E       | General-purpose I/O ports<br>These ports are available only in the single-chip mode.                                                                                                                                                                            |

|                  | A04 to A07   |         | Output pins for external address buses A04 to A07<br>These pins are available in an external-bus mode.                                                                                                                                                          |

|                  | TIN4 to TIN7 |         | 16-bit reload timer 2 (ch.4 to ch.7) input pins<br>These pins are available when the 16-bit reload timer 2 (ch.4 to<br>ch.7) input specification is "enabled". The data on the pin is read<br>as the 16-bit reload timer 2 (ch.4 to ch.7) input (TIN4 to TIN7). |

| 12               | P30          | E       | General-purpose I/O port<br>This port is available in the single-chip mode or when the middle<br>address control register setting is "port."                                                                                                                    |

|                  | A08          |         | Output pin for external address bus A08<br>This pin is available in an external-bus mode and when the middle<br>address control register set to "address."                                                                                                      |

| 13               | P31          | E       | General-purpose I/O port<br>This port is available in the single-chip mode or when the middle<br>address control register setting is "port", with the PPG output is<br>disabled.                                                                                |

|                  | A09          |         | Output pin for external address bus A09<br>This pin is available in an external-bus mode and when the middle<br>address control register setting is "address."                                                                                                  |

|                  | PPG          |         | PPG timer output pin<br>This pin is available when the PPG operation mode control<br>register specification is the PPG output pin.                                                                                                                              |

| Pin no.  | Pin name       | Circuit | Function                                                                                                                                                                                                                                                                          |

|----------|----------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QFP*     | T in name      | type    |                                                                                                                                                                                                                                                                                   |

| 14 to 17 | P32 to P35     | E       | General-purpose I/O ports<br>These ports are available in the single-chip mode or when the<br>middle address control register setting is "port", with the 16-bit<br>reload timer 1 (ch.0 to ch.3) output is disabled.                                                             |

|          | A10 to A13     |         | Output pins for external address buses A10 to A13<br>These pins are available in an external-bus mode and when the<br>middle address control register setting is "address."                                                                                                       |

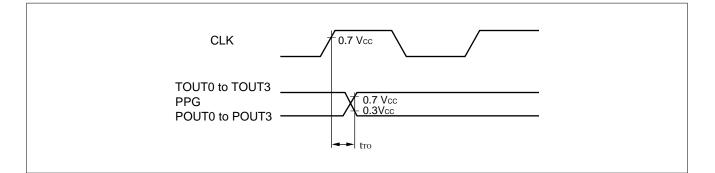

|          | TOUT0 to TOUT3 |         | 16-bit reload timer 1 (ch.0 to ch.3) output pin<br>These pins are available when the 16-bit reload timer 1 (ch.0 to<br>ch.3) is output operation.                                                                                                                                 |

| 18       | P36            | E       | General-purpose I/O port<br>This port is available when the UART (ch.2) clock output is<br>disabled either in the single-chip mode or when the middle<br>address control register setting is "port."                                                                              |

|          | A14            |         | Output pin for external address bus A14<br>This pin is available when the UART (ch.2) clock output is<br>disabled in an external-bus mode and when the middle address<br>control register setting is "address."                                                                   |

|          | SCK3           |         | UART (ch.2) clock output pin (SCK3)<br>This pin is available when the UART (ch.2) clock output is<br>enabled.<br>UART (ch.2) external clock input pin (SCK3)<br>This pin is available when the port is in input mode and the UART<br>(ch.2) specification is external clock mode. |

| 19       | P37            | E       | General-purpose I/O port<br>This port is available in the single-chip mode or when the middle<br>address control register setting is "port."                                                                                                                                      |

|          | A15            |         | Output pin for external address bus A15<br>This pin is available in an external-bus mode and when middle<br>address control register setting is "address."                                                                                                                        |

|          | SID3           |         | UART (ch.2) serial data input pin (SID3)<br>Since this input is used whenever the SID3 is in input operation,<br>the output by any other function must be suspended unless the<br>output is intentionally performed.                                                              |

| 20       | P40            | E       | General-purpose I/O port<br>This port is available when the UART (ch.2) serial data output<br>from SOD3 is disabled either in the single-chip mode or when the<br>upper address control register setting is "port."                                                               |

|          | A16            |         | Output pin for external address bus A16<br>This pin is available when the UART (ch.2) serial data output<br>from SOD3 is disabled in an external-bus mode and when the<br>upper address control register setting is "address."                                                    |

|          | SOD3           |         | UART (ch.2) serial data output pin (SOD3)<br>This pin is available when the UART (ch.2) serial data output is<br>enabled.                                                                                                                                                         |

\* : FPT-80P-M06, FPT-80C-C02

| Pin no. | Pin name | Circuit<br>type | Function                                                                                                                                                                                                                                                                          |  |

|---------|----------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| QFP*    |          | type            |                                                                                                                                                                                                                                                                                   |  |

| 21      | P41      | E               | General-purpose I/O port<br>This port is available when the UART (ch.2) clock output is<br>disabled either in the single-chip mode or when the upper<br>address control register setting is "port."                                                                               |  |

|         | A17      |                 | Output pin for external address bus A17<br>This pin is available when the UART (ch.2) clock output is<br>disabled in an external-bus mode and when the upper address<br>control register setting is "address."                                                                    |  |

|         | SCK2     |                 | UART (ch.2) clock output pin (SCK2)<br>This pin is available when the UART (ch.2) clock output is<br>enabled.<br>UART (ch.2) external clock input pin (SCK2)<br>This pin is available when the port is in input mode and the UART<br>(ch.2) specification is external clock mode. |  |

| 22      | P42      | E               | General-purpose I/O port<br>This port is available in the single-chip mode or when the upper<br>address control register setting is "port."                                                                                                                                       |  |

|         | A18      |                 | Output pin for external address bus A18<br>This pin is available in an external-bus mode and when the upper<br>address control register setting is "address."                                                                                                                     |  |

|         | SID2     |                 | UART (ch.2) serial data input pin (SID2)<br>Since this input is used whenever the SID2 is in input operation,<br>the output by any other function must be suspended unless the<br>output is intentionally performed.                                                              |  |

| 23      | P43      | E               | General-purpose I/O port<br>This port is available when the UART (ch.2) serial data output<br>from SOD2 is disabled either in the single-chip mode or when the<br>upper address control register setting is "port."                                                               |  |

|         | A19      |                 | Output pin for external address bus A19<br>This pin is available when the UART (ch.2) serial data output<br>from SOD2 is disabled in an external-bus mode and when the<br>upper address control register setting is "address."                                                    |  |

|         | SOD2     |                 | UART (ch.2) serial data output pin (SOD2)<br>This pin is available when the UART (ch.2) serial data output<br>from SOD2 is enabled.                                                                                                                                               |  |

\* : FPT-80P-M06, FPT-80C-C02

| Pin no. | Dia      | Circuit | Example 1 and                                                                                                                                                                                                     |

|---------|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QFP*    | Pin name | type    | Function                                                                                                                                                                                                          |

| 24      | PWC0     | E       | PWC timer input pin<br>Since this input is used whenever the PWC0 timer is in input<br>operation, the output by any other function must be suspended<br>unless the output is intentionally performed.             |

|         | POUT0    | _       | PWC timer output pin<br>This pin is available when the PWC0 is output operation.                                                                                                                                  |

| 25      | P45      | E       | General-purpose I/O port<br>This port is available in the single-chip mode or when the upper<br>address control register setting is "port."                                                                       |

|         | A21      |         | Output pin for external address bus A21<br>This pin is available in an external-bus mode and when the upper<br>address control register setting is "address."                                                     |

|         | PWC1     | _       | PWC timer data sample input pin<br>Since this input is used whenever the PWC1 timer is in input<br>operation, the output by any other function must be suspended<br>unless the output is intentionally performed. |

|         | POUT1    | _       | PWC timer output pin<br>This pin is available when the PWC1 is output operation.                                                                                                                                  |

| 26      | P46      | E       | General-purpose I/O port<br>This port is available in the single-chip mode or when the upper<br>address control register setting is "port."                                                                       |

|         | A22      |         | Output pin for external address bus A22<br>This pin is available in an external-bus mode and when the upper<br>address control register setting is "address."                                                     |

|         | PWC2     |         | PWC timer input pin<br>Since this input is used whenever the PWC2 timer is in input<br>operation, the output by any other function must be suspended<br>unless the output is intentionally performed.             |

|         | POUT2    |         | PWC timer output pin<br>This pin is available when the PWC2 is output operation.                                                                                                                                  |

| 27      | P47      | E       | General-purpose I/O port<br>This port is available in the single-chip mode or when the upper<br>address control register setting is "port."                                                                       |

|         | A23      |         | Output pin for external address bus A23<br>This pin is available in an external-bus mode and when the upper<br>address control register setting is "address."                                                     |

|         | PWC3     |         | PWC timer input pin<br>Since this input is used whenever the PWC3 timer is in input<br>operation, the output by any other function must be suspended<br>unless the output is intentionally performed.             |

|         | POUT3    |         | PWC timer output pin<br>This pin is available when the PWC3 is output operation.                                                                                                                                  |

\* : FPT-80P-M06, FPT-80C-C02

| Pin no.             | Din manua  | Circuit      | Francisco e                                                                                                                                                                                                                                                         |  |  |

|---------------------|------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| QFP*                | Pin name   | type         | Function                                                                                                                                                                                                                                                            |  |  |

| 28                  | AVcc       | Power supply | Analog circuit power supply pin<br>This power supply must be turned on or off with a potential equal<br>to or higher than AVcc applied to Vcc.<br>Be sure that AVcc= Vcc before use and during operation.                                                           |  |  |

| 29                  | AVRH       | Power supply | Analog circuit reference voltage input pin<br>This pins must be turned on or off with a potential equal to or<br>higher than AVRH applied to AVcc.                                                                                                                  |  |  |

| 30                  | AVRL       | Power supply | Analog circuit reference voltage input pin                                                                                                                                                                                                                          |  |  |

| 31                  | AVss       | Power supply | Analog circuit grounding level                                                                                                                                                                                                                                      |  |  |

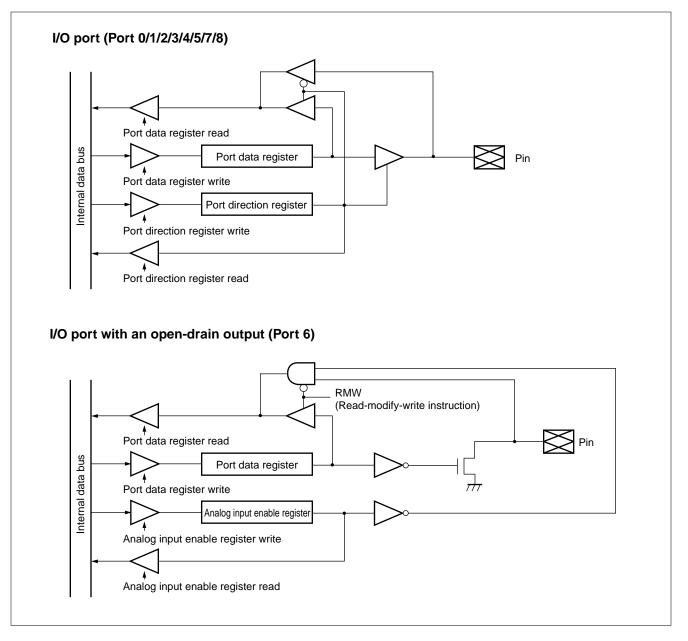

| 32, 33,<br>35 to 40 | P60 to P67 | С            | Open-drain I/O ports<br>These ports are available when the analog input enable register<br>setting is "port."                                                                                                                                                       |  |  |

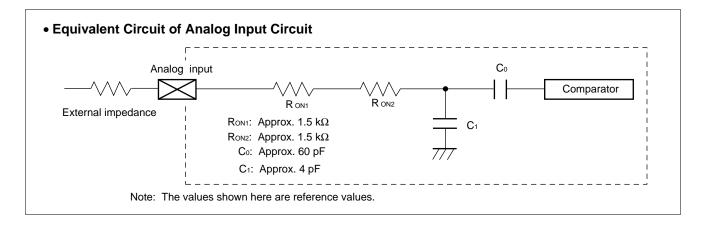

|                     | AN0 to AN7 |              | A/D converter analog input pins<br>These pins are available when the analog input enable register<br>setting is "analog input."                                                                                                                                     |  |  |

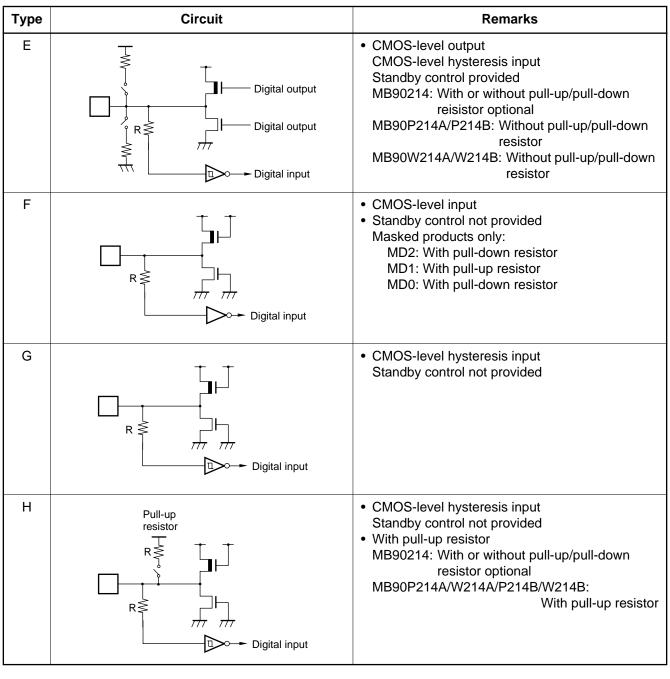

| 41 to 43            | MD0 to MD2 | F            | Operation mode select signal input pins<br>Connect these pins directly to Vcc or Vss.                                                                                                                                                                               |  |  |

| 44                  | HST        | G            | Hardware standby input pin                                                                                                                                                                                                                                          |  |  |

| 45                  | P70        | E            | General-purpose I/O port<br>This port is available when the UART (ch.1) clock output is<br>disabled.                                                                                                                                                                |  |  |

|                     | SCK1       |              | UART (ch.1) clock output pin<br>This pin is available when the UART (ch.1) clock output is<br>enabled.<br>UART (ch.1) external clock input pin<br>This pin is available when the port is in input mode and the UART<br>(ch.1) specification is external clock mode. |  |  |

| 46                  | P71        | E            | General-purpose I/O port<br>This port is always available.                                                                                                                                                                                                          |  |  |

|                     | SID1       |              | UART (ch.1) serial data input pin<br>Since this input is used whenever the UART (ch.1) is in input<br>operation, the output by any other function must be suspended<br>unless the output is intentionally performed.                                                |  |  |

| 47                  | P72        | E            | General-purpose I/O port<br>This port is available when the UART (ch.1) serial data output is<br>disabled.                                                                                                                                                          |  |  |

|                     | SOD1       |              | UART (ch.1) serial data output pin<br>This pin is available when the UART (ch.1) serial data output is<br>enabled.                                                                                                                                                  |  |  |

\* : FPT-80P-M06, FPT-80C-C02

| Pin no. | D'         | Circuit | E un affirm                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QFP*    | Pin name   | type    | Function                                                                                                                                                                                                                                                                                                                                                                                         |

| 48      | P73        | E       | General-purpose I/O port<br>This port is available when the UART (ch.0) clock output is<br>disabled.                                                                                                                                                                                                                                                                                             |

|         | SCK0       | _       | UART (ch.0) clock output pin<br>This pin is available when the UART (ch.0) clock output is<br>enabled.<br>UART (ch.0) external clock input pin<br>This pin is available when the port is in input mode and the UART<br>(ch.0) specification is external clock mode.                                                                                                                              |

| 49      | P74        | E       | General-purpose I/O port<br>This port is always available.                                                                                                                                                                                                                                                                                                                                       |

|         | SIDO       |         | UART (ch.0) serial data input pin<br>Since this input is used whenever the UART (ch.0) is in input<br>operation, the output by any other function must be suspended<br>unless the output is intentionally performed.                                                                                                                                                                             |

| 50      | P75        | E       | General-purpose I/O port<br>This port is available when the UART (ch.0) serial data output is<br>disabled.                                                                                                                                                                                                                                                                                       |

|         | SOD0       |         | UART (ch.0) serial data output pin<br>This pin is available when the UART (ch.0) serial data output is<br>enabled.                                                                                                                                                                                                                                                                               |

| 51, 52  | P80, 81    | D       | General-purpose I/O port<br>This port is always available.<br>When these pins are open in input mode, through current may<br>leak in stop mode/reset mode, be sure to fix these pins to Vcc/Vss<br>level to use these pins in input mode.                                                                                                                                                        |

|         | INTO, INT1 | _       | External interrupt request input pin<br>Since this input is used whenever external interrupts are<br>enabled, the output by any other function must be suspended<br>unless the output is intentionally performed.<br>When these pins are open in input mode, through current may<br>leak in stop mode/reset mode, be sure to fix these pins to Vcc/Vss<br>level to use these pins in input mode. |

| 53      | P82        | D       | General-purpose I/O port<br>This port is always available.<br>When these pins are open in input mode, through current may<br>leak in stop mode/reset mode, be sure to fix these pins to Vcc/Vss<br>level to use these pins in input mode.                                                                                                                                                        |

|         | INT2       |         | External interrupt request input pin<br>Since this input is used whenever external interrupts are<br>enabled, the output by any other function must be suspended<br>unless the output is intentionally performed.<br>When these pins are open in input mode, through current may<br>leak in stop mode/reset mode, be sure to fix these pins to Vcc/Vss<br>level to use these pins in input mode. |

\* : FPT-80P-M06, FPT-80C-C02

| Pin no. | Pin name | Circuit | Function                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QFP*    | Finname  | type    | T unction                                                                                                                                                                                                                                                                                                                                                                                               |

| 53      | ATG      | D       | A/D converter trigger input pin<br>When these pins are open in input mode, through current may<br>leak in stop mode/reset mode, be sure to fix these pins to Vcc/Vss<br>level to use these pins in input mode.                                                                                                                                                                                          |

| 54      | P50      | E       | General-purpose I/O port<br>This port is available in the single-chip mode and when the CLK<br>output is disabled.                                                                                                                                                                                                                                                                                      |

|         | CLK      |         | CLK output pin<br>This pin is available in an external-bus mode with the CLK output<br>enabled.                                                                                                                                                                                                                                                                                                         |

| 55      | P51      | E       | General-purpose I/O port<br>This port is available in the single-chip mode or when the ready<br>function is disable.                                                                                                                                                                                                                                                                                    |

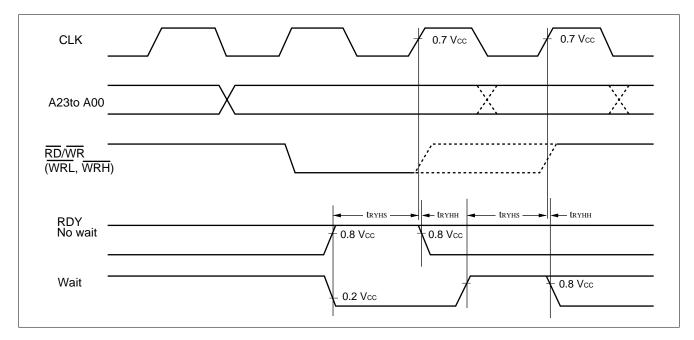

|         | RDY      |         | Ready signal input pin<br>This pin is available in an external-bus mode and when the ready<br>function is enabled.                                                                                                                                                                                                                                                                                      |

| 56      | P52      | E       | General-purpose I/O port<br>This port is available in the single-chip mode or when the hold<br>function is disabled.                                                                                                                                                                                                                                                                                    |

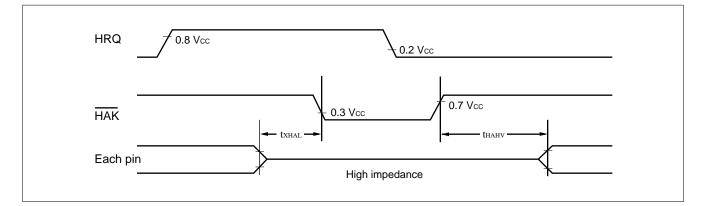

|         | HAK      |         | Hold acknowledge output pin<br>This pin is available in an external-bus mode and when the hold<br>function is enabled.                                                                                                                                                                                                                                                                                  |

| 57      | P53      | E       | General-purpose I/O port<br>This port is available in the single-chip mode or when the hold<br>function is disabled in an external-bus mode.                                                                                                                                                                                                                                                            |

|         | HRQ      |         | Hold request input pin<br>This pin is available in an external-bus mode and when the hold<br>function is enabled.<br>Since this input is used during this operation at any time, the<br>output by any other function must be suspended unless the<br>output is intentionally performed.                                                                                                                 |

| 58      | P54      | D       | General-purpose I/O port<br>This port is available in the single-chip mode, in the external bus<br>8-bit mode, or when the WR pin output is disabled.<br>When these pins are open in input mode, through current may<br>leak in stop mode/reset mode, be sure to fix these pins to Vcc/Vss<br>level to use these pins in input mode.                                                                    |

|         | CTS0     |         | UART (ch.0) clear-to-send input pin<br>Since this input is used whenever the UART (ch.0) CTS function<br>is enabled, the output by any other function must be suspended<br>unless the output is intentionally performed.<br>When these pins are open in input mode, through current may<br>leak in stop mode/reset mode, be sure to fix these pins to Vcc/Vss<br>level to use these pins in input mode. |

\* : FPT-80P-M06, FPT-80C-C02

| Pin no.<br>QFP* | Pin name | Circuit<br>type | Function                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------|----------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 58              | WRH      | D               | Write strobe output pin for the upper eight bits of data bus<br>This pin is available in the external bus 16-bit mode with the WR<br>pin output enabled in an external-bus mode.                                                                                                                                                                                                                 |

|                 | INT3     |                 | External interrupt request input pin<br>Since this input is used whenever external interrupts are<br>enabled, the output by any other function must be suspended<br>unless the output is intentionally performed.<br>When these pins are open in input mode, through current may<br>leak in stop mode/reset mode, be sure to fix these pins to Vcc/Vss<br>level to use these pins in input mode. |

| 59              | P55      | E               | General-purpose I/O port<br>This port is available in the single-chip mode or when the WR pin<br>output is disabled.                                                                                                                                                                                                                                                                             |

|                 | WRL      |                 | Write strobe output pin for the lower eight bits of data bus<br>This pin is available in an external-bus mode and when the WR<br>pin output is enabled.                                                                                                                                                                                                                                          |

| 60              | P56      | E               | General-purpose I/O port<br>This port is available in the single-chip mode.                                                                                                                                                                                                                                                                                                                      |

|                 | RD       |                 | Data bus read strobe output pin<br>This pin is available in an external-bus mode.                                                                                                                                                                                                                                                                                                                |

| 61              | P57      | D               | General-purpose I/O port<br>This port is always available.<br>When these pins are open in input mode, through current may<br>leak in stop mode/reset mode, be sure to fix these pins to Vcc/Vss<br>level to use these pins in input mode.                                                                                                                                                        |

|                 | WI       |                 | RAM write disable request input<br>Since this input is used during this operation at any time, the<br>output by any other function must be suspended unless the<br>output is intentionally performed.<br>When these pins are open in input mode, through current may<br>leak in stop mode/reset mode, be sure to fix these pins to Vcc/Vss<br>level to use these pins in input mode.             |

| 62              | RST      | Н               | External reset request input pin                                                                                                                                                                                                                                                                                                                                                                 |

| 66              | Vcc      | Power supply    | Digital circuit power supply pin                                                                                                                                                                                                                                                                                                                                                                 |

| 11, 34, 63      | Vss      | Power supply    | Digital circuit grounding level                                                                                                                                                                                                                                                                                                                                                                  |

\* : FPT-80P-M06, FPT-80C-C02

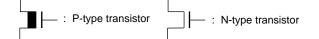

#### ■ I/O CIRCUIT TYPE

#### HANDLING DEVICES

#### 1. Preventing Latchup

CMOS ICs may cause latchup when a voltage higher than Vcc or lower than Vss is applied to input or output pins, or when a voltage exceeding the rating is applied between Vcc and Vss.

If latch-up occurs, the power supply current increases rapidly, sometimes resulting in thermal breakdown of the device. Use meticulous care not to let any voltage exceed the maximum rating.

Also, take care to prevent the analog power supply (AVcc and AVRH) and analog input from exceeding the digital power supply (Vcc) when the analog system power supply is turned on and off.

#### 2. Treatment of Unused Input Pins

Leaving unused input pins open could cause malfunctions. They should be connected to a pull-up or pull-down resistor.

#### 3. Treatment of Pins when A/D is not Used

Connect to be AVcc = AVRH = Vcc and AVss = AVRL = Vss even if the A/D converter is not in use.

#### 4. Precautions when Using an External Clock

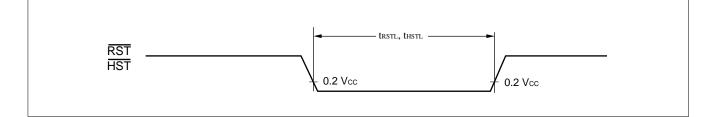

To reset the internal circuit properly by the Low-level input to the  $\overline{RST}$  pin, the "L" level input to the  $\overline{RST}$  pin must be maintained for at least five machine cycles. Pay attention to it if the chip uses external clock input.

#### 5. Vcc and Vss Pins

Apply equal potential to the Vcc and Vss pins.

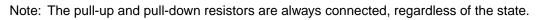

#### 6. Notes on Using an External Clock

When using an external clock, drive the X0 pin as illustrated below. When an external clock is used, oscillation stabilization time is required even for power-on reset and wake-up from stop mode.

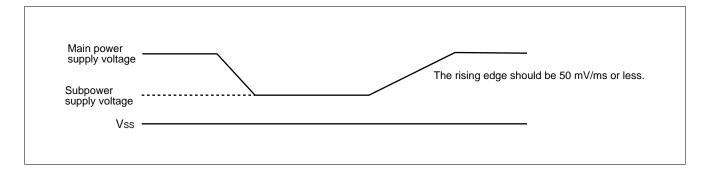

#### 7. Power-on Sequence for A/D Converter Power Supplies and Analog Inputs

Be sure to turn on the digital power supply (Vcc) before applying voltage to the A/D converter power supplies (AVcc, AVRH, and AVRL) and analog inputs (AN0 to AN7).

When turning power supplies off, turn off the A/D converter power supplies (AVcc, AVRH, and AVRL) and analog inputs (AN0 to AN7) first, then the digital power supply (Vcc).

When turning AVRH on or off, be careful not to let it exceed AVcc.

#### ■ PROGRAMMING FOR MB90P214A/P214B/W214A/W214B

In EPROM mode, the MB90P214A/P214B/W214A/W214B functions equivalent to the MBM27C1000. This allows the EPROM to be programmed with a general-purpose EPROM programmer by using the dedicated socket adapter (do not use the electronic signature mode).

#### 1. Program Mode

When shipped from Fujitsu, and after each erasure, all bits ( $64 \text{ K} \times 8 \text{ bits}$ ) in the MB90P214A/P214B/W214A/W214B are in the "1" state. Data is written to the ROM by selectively programming "0's" into the desired bit locations. Bits cannot be set to "1" electrically.

#### 2. Programming Procedure

- (1) Set the EPROM programmer to MBM27C1000.

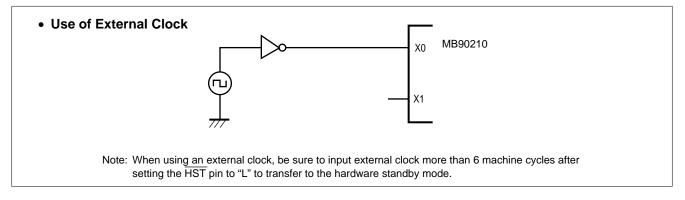

- (2) Load program data into the EPROM programmer at 10000H to 1FFFFH.

Note that ROM addresses FF0000<sub>H</sub> to FFFFF<sub>H</sub> in the operation mode in the MB90P214A/P214B/W214A/ W214B series assign to 10000<sub>H</sub> to 1FFFF<sub>H</sub> in the EPROM mode (on the EPROM programmer).

- (3) Mount the MB90P214A/P214B/W214A/W214B on the adapter socket, then fit the adapter socket onto the EPROM programmer. When mounting the device and the adapter socket, pay attention to their mounting orientations.

- (4) Start programming the program data to the device.

- (5) If programming has not successfully resulted, connect a capacitor of approx. 0.1  $\mu$ F between V<sub>CC</sub> and GND, between V<sub>PP</sub> and GND.

- (6) Since the MB90P214A and MB90W214A have CMOS-level input, programming to them may be impossible depending on the output level of the general-purpose programmer. In that case, connect a pull-up resistor to the adapter socket side.

- Note: The mask ROM products (MB90214) does not support EPROM mode. Data cannot, therefore, be read by the EPROM programmer.

#### 3. EPROM Programmer Socket Adapter

| Part number                                      | Package | Compatible socket adapter<br>Sun Hayato Co., Ltd. |

|--------------------------------------------------|---------|---------------------------------------------------|

| MB90P214A<br>MB90P214B<br>MB90W214A<br>MB90W214B | QFP-80  | ROM-80QF-32DP-16F                                 |

Inquiry: Sun Hayato Co., Ltd.: TEL (81)-3-3986-0403 FAX (81)-3-5396-9106

#### 4. Erase Procedure

Data written in the MB90W214A/W214B are erased (from "0" to "1") by exposing the chip to ultraviolet rays with a wavelength of 2,537 Å through the translucent cover.

Recommended irradiation dosage for exposure is 10 Wsec/cm<sup>2</sup>. This amount is reached in 15 to 20 minutes with a commercial ultraviolet lamp positioned 2 to 3 cm above the package (when the package surface illuminance is 1200  $\mu$ W/cm<sup>2</sup>).

If the ultraviolet lamp has a filter, remove the filter before exposure. Attaching a mirrored plate to the lamp increases the illuminance by a factor of 1.4 to 1.8, thus shortening the required erasure time. If the translucent part of the package is stained with oil or adhesive, transmission of ultraviolet rays is degraded, resulting in a longer erasure time. In that case, clean the translucent part using alcohol (or other solvent not affecting the package).

The above recommended dosage is a value which takes the guard band into consideration and is a multiple of the time in which all bits can be evaluated to have been erased. Observe the recommended dosage for erasure; the purpose of the guard band is to ensure erasure in all temperature and supply voltage ranges. In addition, check the life span of the lamp and control the illuminance appropriately.

Data in the MB90W214A/W214B are erased by exposure to light with a wavelength of 4000 Å or less.

Data in the device is also erased even by exposure to fluorescent lamp light or sunlight although the exposure results in a much lower erasure rate than exposure to 2537 Å ultraviolet rays. Note that exposure to such lights for an extended period will therefore affect system reliability. If the chip is used where it is exposed to any light with a wavelength of 4000 Å or less, cover the translucent part, for example, with a protective seal to prevent the chip from being exposed to the light.

Exposure to light with a wavelength of 4,000 to 5,000 Å or more will not erase data in the device. If the light applied to the chip has a very high illuminance, however, the device may cause malfunction in the circuit for reasons of general semiconductor characteristics. Although the circuit will recover normal operation when exposure is stopped, the device requires proper countermeasures for use in a place exposed continuously to such light even though the wavelength is 4,000 Å or more.

#### 5. Recommended Screening Conditions

High temperature aging is recommended as the pre-assembly screening procedure.

#### 6. Programming Yeild

MB90P214A/P214B cannot be write-tested for all bits due to their nature. Therefore the write yield cannot always be guaranteed to be 100%.

#### 7. Pin Assignment in EPROM Mode

#### (1) Pins compatible with MBM27C1000

| MBM2    | MBM27C1000 |         | MB90P214A, MB90P214B,<br>MB90W214A, MB90W214B |         | MBM27C1000 |         | MB90P214A, MB90P214B,<br>MB90W214A, MB90W214B |  |

|---------|------------|---------|-----------------------------------------------|---------|------------|---------|-----------------------------------------------|--|

| Pin no. | Pin name   | Pin no. | Pin name                                      | Pin no. | Pin name   | Pin no. | Pin name                                      |  |

| 1       | Vpp        | 43      | MD2 (VPP)                                     | 32      | Vcc        |         |                                               |  |

| 2       | OE         | 59      | P55                                           | 31      | PGM        | 60      | P56                                           |  |

| 3       | A15        | 19      | P37                                           | 30      | N.C.       |         |                                               |  |

| 4       | A12        | 16      | P34                                           | 29      | A14        | 18      | P36                                           |  |

| 5       | A07        | 10      | P27                                           | 28      | A13        | 17      | P35                                           |  |

| 6       | A06        | 9       | P26                                           | 27      | A08        | 12      | P30                                           |  |

| 7       | A05        | 8       | P25                                           | 26      | A09        | 13      | P31                                           |  |

| 8       | A04        | 7       | P24                                           | 25      | A11        | 15      | P33                                           |  |

| 9       | A03        | 6       | P23                                           | 24      | A16        | 20      | P40                                           |  |

| 10      | A02        | 5       | P22                                           | 23      | A10        | 14      | P32                                           |  |

| 11      | A01        | 4       | P21                                           | 22      | CE         | 58      | P54                                           |  |

| 12      | A00        | 3       | P20                                           | 21      | D07        | 74      | P07                                           |  |

| 13      | D00        | 67      | P00                                           | 20      | D06        | 73      | P06                                           |  |

| 14      | D01        | 68      | P01                                           | 19      | D05        | 72      | P05                                           |  |

| 15      | D02        | 69      | P02                                           | 18      | D04        | 71      | P04                                           |  |

| 16      | GND        |         |                                               | 17      | D03        | 70      | P03                                           |  |

| Туре         | Pin no. | Pin name |

|--------------|---------|----------|

| Power supply | 41      | MD0      |

|              | 42      | MD1      |

|              | 44      | HST      |

|              | 66      | Vcc      |

| GND          | 11      | Vss      |

|              | 30      | AVRL     |

|              | 31      | AVss     |

|              | 34      | Vss      |

|              | 56      | P52      |

|              | 57      | P53      |

|              | 62      | RST      |

|              | 63      | Vss      |

#### (2) Power supply and ground connection pins

#### (3) Pins other than MBM27C1000-compatible pins

| Pin no.                                                                                                                                                               | Pin name                                                                                                                                                                              | Treatment                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| 64                                                                                                                                                                    | X0                                                                                                                                                                                    | Pull up to 4.7 kΩ.                                                    |

| 65                                                                                                                                                                    | X1                                                                                                                                                                                    | Open                                                                  |

| $ \begin{array}{c} 1\\ 2\\ 21\\ to\\ 27\\ 28\\ 29\\ 32\\ 33\\ 35\\ to\\ 40\\ 45\\ to\\ 50\\ 51\\ to\\ 50\\ 51\\ to\\ 53\\ 54\\ 55\\ 61\\ 75\\ to\\ 80\\ \end{array} $ | P16<br>P17<br>P41<br>to<br>P47<br>AVcc<br>AVRH<br>P60<br>P61<br>P62<br>to<br>P67<br>P70<br>to<br>P75<br>P80<br>to<br>P75<br>P80<br>to<br>P82<br>P50<br>P51<br>P57<br>P10<br>to<br>P15 | Connect a pull-up resistor of approximately 1 M $\Omega$ to each pin. |

#### ■ BLOCK DIAGRAM

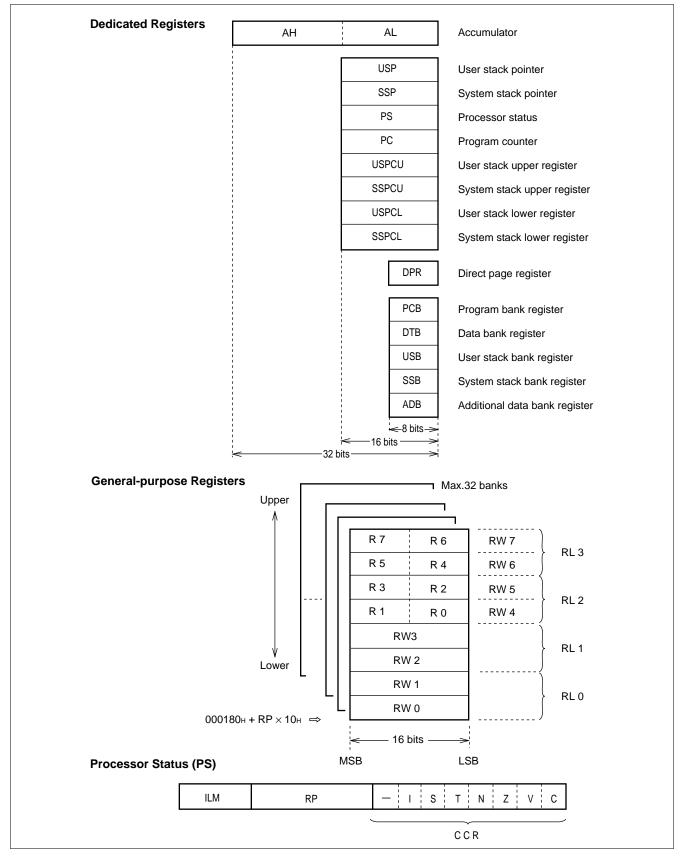

#### PROGRAMMING MODEL

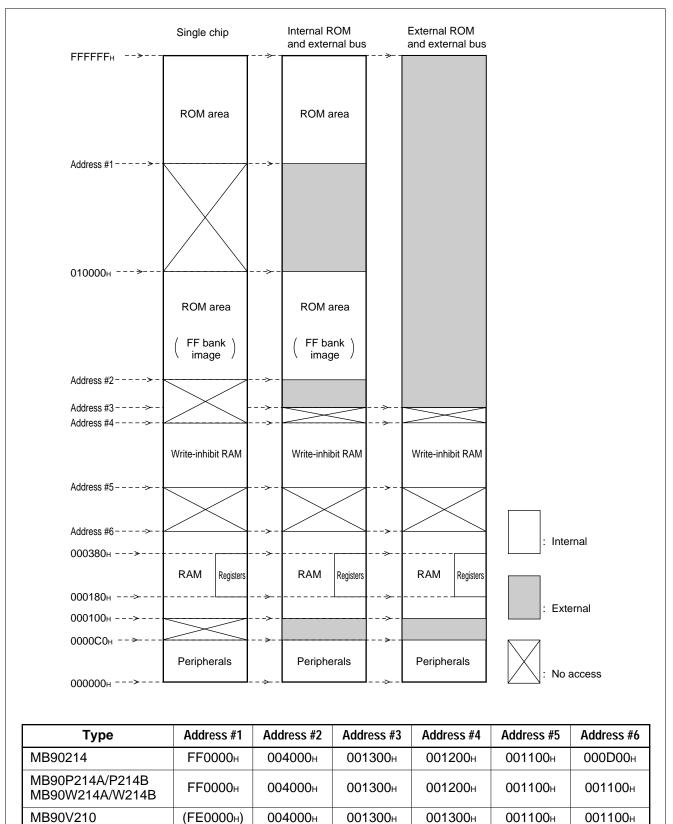

#### MEMORY MAP

#### ■ I/O MAP

| Address                | Register                                     | Register<br>name | Access | Resource<br>name | Initial value |

|------------------------|----------------------------------------------|------------------|--------|------------------|---------------|

| 000000н *3             | Port 0 data register                         | PDR0             | R/W    | Port 0           | XXXXXXXX      |

| 000001н * <sup>3</sup> | Port 1 data register                         | PDR1             | R/W    | Port 1           | XXXXXXXX      |

| 000002н *з             | Port 2 data register                         | PDR2             | R/W    | Port 2           | XXXXXXXX      |

| 000003н * <sup>3</sup> | Port 3 data register                         | PDR3             | R/W    | Port 3           | XXXXXXXX      |

| 000004н * <sup>3</sup> | Port 4 data register                         | PDR4             | R/W    | Port 4           | XXXXXXXX      |

| 000005н * <sup>3</sup> | Port 5 data register                         | PDR5             | R/W    | Port 5           | XXXXXXXX      |

| 00006н                 | Port 6 data register                         | PDR6             | R/W    | Port 6           | 11111111      |

| 000007н                | Port 7 data register                         | PDR7             | R/W    | Port 7           | XXXXXX        |

| 000008н                | Port 8 data register                         | PDR8             | R/W    | Port 8           | XXX           |

| 000009н<br>to 0Fн      | Reserved area *1                             |                  |        |                  |               |

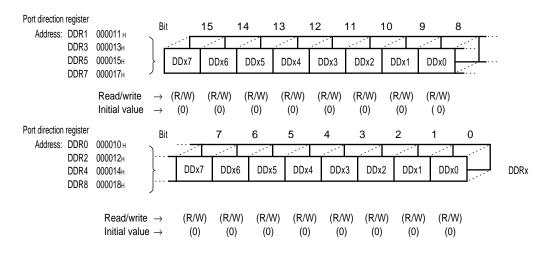

| 000010н * <sup>3</sup> | Port 0 data direction register               | DDR0             | R/W    | Port 0           | 0000000       |

| 000011н * <sup>3</sup> | Port1 data direction register                | DDR1             | R/W    | Port 1           | 0000000       |

| 000012н * <sup>3</sup> | Port 2 data direction register               | DDR2             | R/W    | Port 2           | 0000000       |

| 000013н * <sup>3</sup> | Port 3 data direction register               | DDR3             | R/W    | Port 3           | 0000000       |

| 000014н * <sup>3</sup> | Port 4 data direction register               | DDR4             | R/W    | Port 4           | 0000000       |

| 000015н * <sup>3</sup> | Port 5 data direction register               | DDR5             | R/W    | Port 5           | 0000000       |

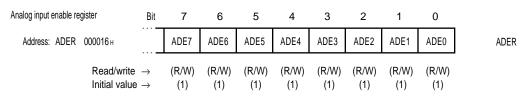

| 000016н                | Analog input enable register                 | ADER             | R/W    | Port 6           | 11111111      |

| <b>000017</b> н        | Port 7 data direction register               | DDR7             | R/W    | Port 7           | 000000        |

| 000018н                | Port 8 data direction register               | DDR8             | R/W    | Port 8           | 000           |

| 000019н<br>to 1Fн      | Reserved area *1                             |                  |        |                  |               |

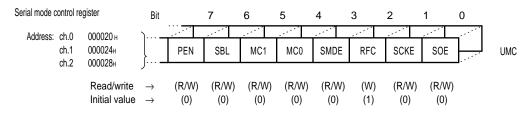

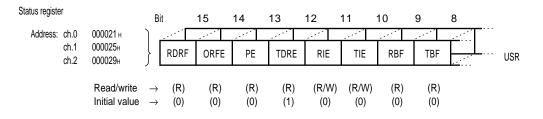

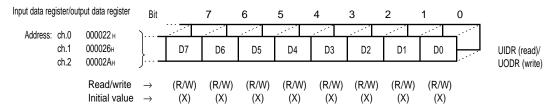

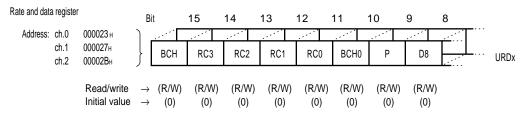

| 000020н                | Mode control register 0                      | UMC0             | R/W    | UART (ch.0)      | 00000100      |

| 000021н                | Status register 0                            | USR0             | R/W    |                  | 00010000      |

| 000022н                | Input data register 0/output data register 0 | UIDR0/<br>UODR0  | R/W    | -                | xxxxxxxx      |

| 000023н                | Rate and data register 0                     | URD0             | R/W    |                  | 0000000       |

| 000024н                | Mode control register 1                      | UMC1             | R/W    | UART (ch.1)      | 00000100      |

| 000025н                | Status register 1                            | USR1             | R/W    |                  | 00010000      |

| 000026н                | Input data register 1/output data register 1 | UIDR1/<br>UODR1  | R/W    |                  | xxxxxxxx      |

| 000027н                | Rate and data register 1                     | URD1             | R/W    |                  | 00000000      |

| Address           | Register                                     | Register<br>name                | Access    | Resource<br>name                | Initial value    |  |

|-------------------|----------------------------------------------|---------------------------------|-----------|---------------------------------|------------------|--|

| 000028н           | Mode control register 2                      | UMC2                            | R/W       | UART (ch.2)                     | 00000100         |  |

| 000029н           | Status register 2                            | USR2                            | R/W       |                                 | 00010000         |  |

| 00002Ан           | Input data register 2/output data register 2 | UIDR2/<br>UODR2                 | R/W       |                                 | XXXXXXXX         |  |

| 00002Вн           | Rate and data register 2                     | URD2                            | R/W       |                                 | 00000000         |  |

| 00002Сн           | UART redirect control register               | 00000                           |           |                                 |                  |  |

| 00002Dн<br>to 2Fн | Reserved area *1                             |                                 | 1         |                                 |                  |  |

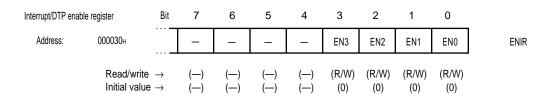

| 000030н           | Interrupt/DTP enable register                | DTP/external                    | 0000      |                                 |                  |  |

| 000031н           | Interrupt/DTP factor register                | pt/DTP factor register EIRR R/W |           | 0000                            |                  |  |

| 000032н           | Request level setting register               | ELVR                            | R/W       |                                 | 00000000         |  |

| 000033н           | Reserved area *1                             |                                 |           |                                 |                  |  |

| 000034н           | AD control status register                   | ADCS                            | R/W       | A/D converter                   | 0000000          |  |

| 000035н           | _                                            |                                 |           |                                 | 00000000         |  |

| 000036н<br>to 37н | AD data register                             | ADCD                            | R/W<br>*4 |                                 | XXXXXXXXX<br>0XX |  |

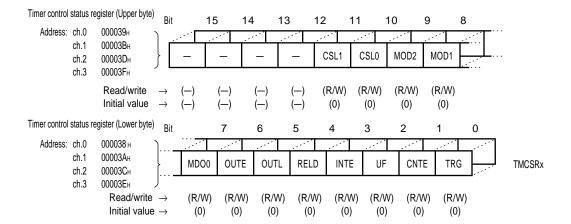

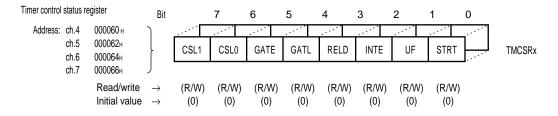

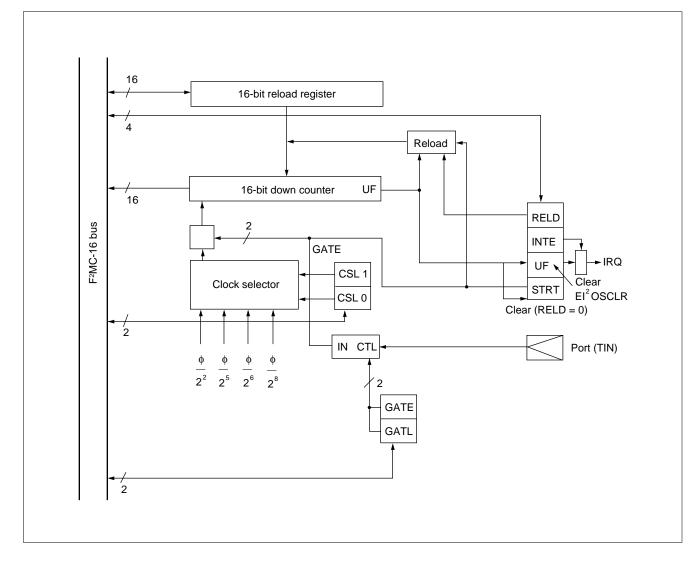

| 000038н<br>to 39н | Timer control status register 0              | TMCSR0                          | R/W       | 16-bit reload<br>timer 1 (ch.0) | 00000000         |  |

| 00003Ан<br>to 3Вн | Timer control status register 1              | TMCSR1                          | R/W       | 16-bit reload<br>timer 1 (ch.1) | 00000000         |  |

| 00003Cн<br>to 3Dн | Timer control status register 2              | TMCSR2                          | R/W       | 16-bit reload<br>timer 1 (ch.2) | 00000000         |  |

| 00003Eн<br>to 3Fн | Timer control status register 3              | TMCSR3                          | R/W       | 16-bit reload<br>timer 1 (ch.3) | 00000000         |  |

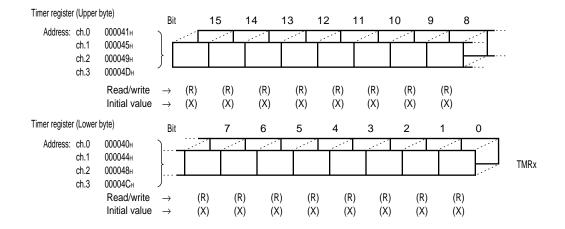

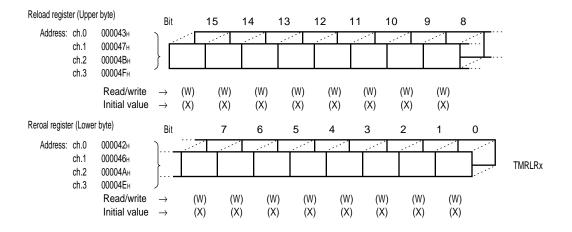

| 000040н           | Timer 0 timer register                       | TMR0                            | R         | 16-bit reload                   | XXXXXXXX         |  |

| 000041н           | _                                            |                                 |           | timer 1 (ch.0)                  | XXXXXXXX         |  |

| 000042н           | Timer 0 reload register                      | TMRLR0                          | W         | 4                               | XXXXXXXX         |  |

| 000043н           |                                              |                                 |           |                                 | XXXXXXXX         |  |

| 000044н           | Timer 1 timer register                       | TMR1                            | R         | 16-bit reload                   | XXXXXXXX         |  |

| 000045н           |                                              |                                 |           | timer 1 (ch.1)                  | XXXXXXXX         |  |

| 000046н           | Timer 1 reload register                      | TMRLR1                          | W         |                                 | XXXXXXXX         |  |

| 000047н           | _                                            |                                 |           |                                 | XXXXXXXX         |  |

| Address | Register                        | Register<br>name      | Access         | Resource<br>name                | Initial value |

|---------|---------------------------------|-----------------------|----------------|---------------------------------|---------------|

| 000048н | Timer 2 timer register          | TMR2                  | R              | 16-bit reload                   | XXXXXXXX      |

| 000049н | _                               |                       |                | timer 1 (ch.2)                  | XXXXXXXX      |

| 00004Ан | Timer 2 reload register         | TMRLR2                | W              | -                               | XXXXXXXX      |

| 00004Вн | _                               |                       |                |                                 | XXXXXXXX      |

| 00004Сн | Timer 3 timer register          | TMR3                  | R              | 16-bit reload                   | XXXXXXXX      |

| 00004Dн | _                               |                       |                | timer 1 (ch.3)                  | XXXXXXXX      |

| 00004Eн | Timer 3 reload register         | TMRLR3                | W              | -                               | XXXXXXXX      |

| 00004Fн | _                               |                       |                |                                 | XXXXXXXX      |

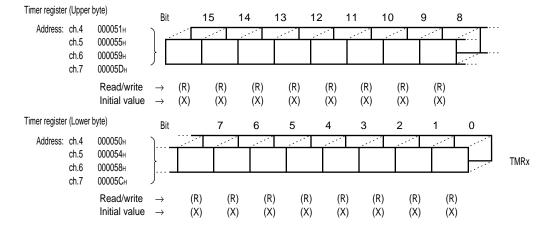

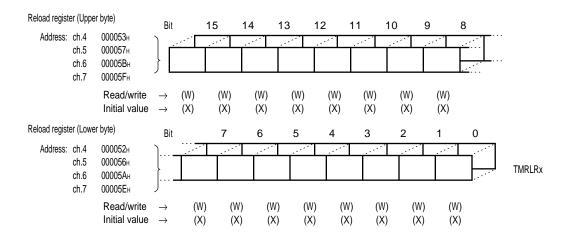

| 000050н | Timer 4 timer register          | TMR4                  | R              | 16-bit reload                   | XXXXXXXX      |

| 000051н | _                               |                       | timer 2 (ch.4) | XXXXXXXX                        |               |