# **TOSHIBA**

## **TOSHIBA CORPORATION**

Semiconductor Company

# **Document Change Notification**

The purpose of this notification is to inform customers about the launch of the Pb-free version of the device. The introduction of a Pb-free replacement affects the datasheet. Please understand that this notification is intended as a temporary substitute for a revision of the datasheet.

Changes to the datasheet may include the following, though not all of them may apply to this particular device.

1. Part number

Example: TMPxxxxxxF **TMPxxxxxxFG**

All references to the previous part number were left unchanged in body text. The new part number is indicated on the prelims pages (cover page and this notification).

2. Package code and package dimensions

Example: LQFP100-P-1414-0.50C \(\triangle\) LQFP100-P-1414-0.50F

All references to the previous package code and package dimensions were left unchanged in body text. The new ones are indicated on the prelims pages.

3. Addition of notes on lead solderability

Now that the device is Pb-free, notes on lead solderability have been added.

4. RESTRICTIONS ON PRODUCT USE

The previous (obsolete) provision might be left unchanged on page 1 of body text. A new replacement is included on the next page.

5. Publication date of the datasheet

The publication date at the lower right corner of the prelims pages applies to the new device.

#### 1. Part number

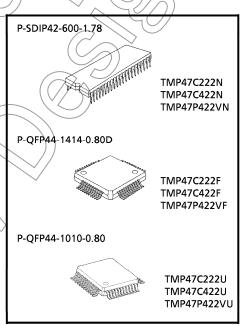

## 2. Package code and dimensions

| Previous Part Number (in Body Text) | Previous Package Code (in Body Text) | New Part Number | New Package Code    | ОТР          |

|-------------------------------------|--------------------------------------|-----------------|---------------------|--------------|

| TMP47C222N                          | P-SDIP42-600-1.78                    | TMP47C222NG     | SDIP42-P-600-1.78   | TMP47P422VNG |

| TMP47C422N                          | P-SDIP42-600-1.78                    | TMP47C422NG     | SDIP42-P-600-1.78   | TMP47P422VNG |

| TMP47C222F                          | P-QFP44-1414-0.80D                   | TMP47C222FG     | QFP44-P-1414-0,80K  | TMP47P422VFG |

| TMP47C422F                          | P-QFP44-1414-0.80D                   | TMP47C422FG     | QFP44-P-1414-0.80K  | TMP47P422VFG |

| TMP47C222U                          | P-QFP44-1010-0.80                    | TMP47C222UG     | LQFP44-P-1010-0.80A | TMP47P422VUG |

| TMP47C422U                          | P-QFP44-1010-0.80                    | TMP47C422UG 〈   | LQFP44-P-1010-0.80A | TMP47P422VUG |

\*: For the dimensions of the new package, see the attached Package Dimensions diagram.

## 3. Addition of notes on lead solderability

The following solderability test is conducted on the new device.

Lead solderability of Pb-free devices (with the G suffix)

| Test          | Test Conditions                                                                                                                                                                                                                                                      | Remark                                                                |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Solderability | (1) Use of Lead (Pb) -solder bath temperature = 230°C -dipping time = 5 seconds -the number of times = once -use of R-type flux (2) Use of Lead (Pb)-Free -solder bath temperature = 245°C -dipping time = 5 seconds -the number of times = once -use of R-type flux | Leads with over 95% solder coverage fill lead forming are acceptable. |

Handbook" etc.

#### 4. RESTRICTIONS ON PRODUCT USE

The following replaces the "RESTRICTIONS ON PRODUCT USE" on page 1 of body text.

#### **RESTRICTIONS ON PRODUCT USE**

20070701-EN

- The information contained herein is subject to change without notice.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in his document shall be made at the customer's own risk.

- The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility

is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its

use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third

parties.

- Please contact your sales representative for product-by-product details in this document regarding RoHS

compatibility. Please use these products in this document in compliance with all applicable laws and regulations that

regulate the inclusion or use of controlled substances. Toshiba assumes no liability for damage or losses occurring

as a result of noncompliance with applicable laws and regulations.

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions.

#### 5. Publication date of the datasheet

The publication date of this datasheet is printed at the lower right corner of this notification.

(Annex)

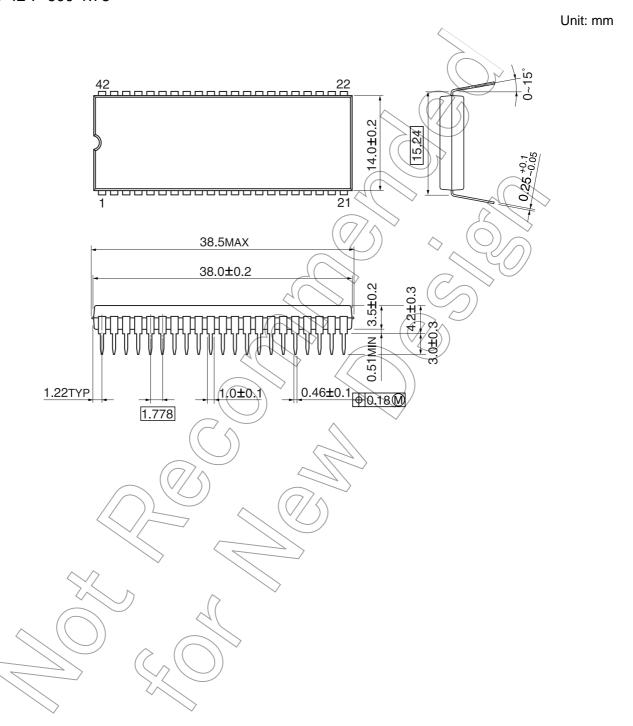

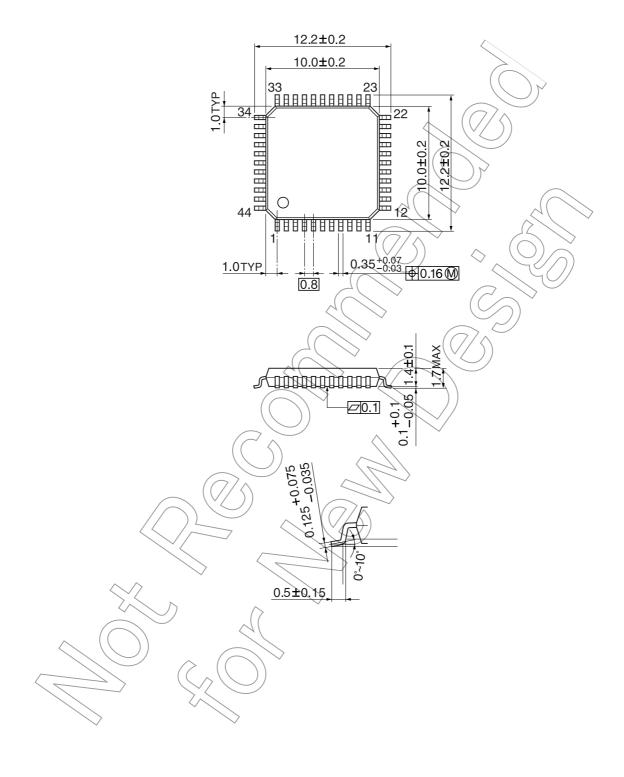

# Package Dimensions

SDIP42-P-600-1.78

IV 2008-03-06

LQFP44-P-1010-0.80A

Unit: mm

V 2008-03-06

CMOS 4-Bit Microcontroller

# TMP47C222N, TMP47C422N TMP47C222F, TMP47C422F TMP47C222U, TMP47C422U

The TMP47C222/422 are high speed and high performance 4-bit single chip micro computers, integrating AD converter, pulse output, zero-cross detector and LCD driver based on the TLCS-470 series.

| Part No.   | ROM          | RAM         | Rackage            | OTP         |

|------------|--------------|-------------|--------------------|-------------|

| TMP47C222N |              |             | P-SDIP42-600-1.78  | TMP47P422VN |

| TMP47C222F | 2048 × 8-bit | 192 × 4-bit | P-QFP44-1414-0.80D | TMP47P422VF |

| TMP47C222U |              |             | P-QFP44-1010-0.80  | TMP47P422VU |

| TMP47C422N |              |             | P-SDIP42-600-1.78  | TMP47P422VN |

| TMP47C422F | 4096 × 8-bit | 256 × 4-bit | P-QFP44-1414-0.80D | TMP47P422VF |

| TMP47C422U |              |             | P-QFP44-1010-0.80  | TMP47P422VU |

#### **Features**

- ◆4-bit single chip microcomputer

- ♦ Instruction execution time: 1.0  $\mu$ s (at 8 MHz)

- ◆Low voltage operation: 2.2 V (at 4.2 MHz)

- ◆92 basic instructions

- Table look-up instructions

- ◆Subroutine nesting: 15 levels max

- ◆6 interrupt sources (External: 2, Internal: 4) All sources have independent latches each, and multiple interrupt control is available.

- ◆I/O port (SDIP: 20 pins, QFP: 22 pins)

- ◆Interval Timer

- ◆Two 12-bit Timer/Counters

Timer, event counter, and pulse width measurement mode

- ◆Watchdog Timer

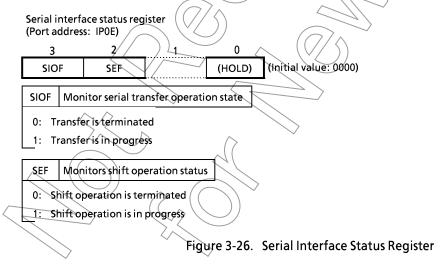

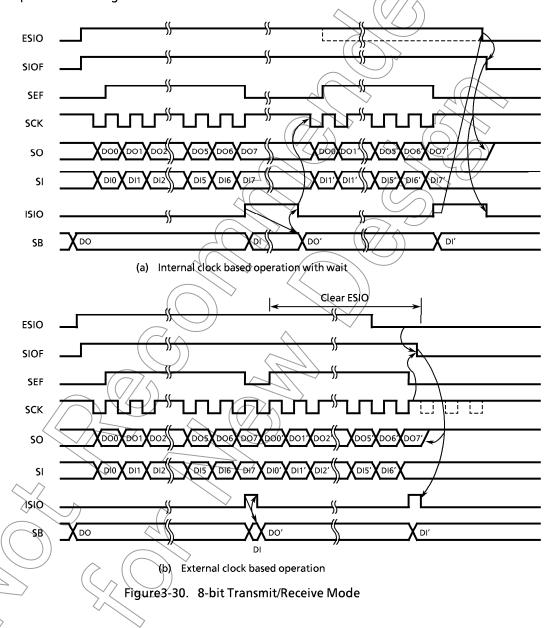

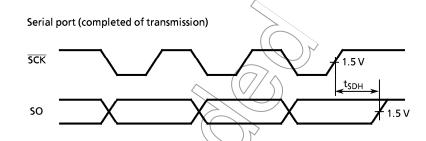

- ◆Serial Interface with 8-bit buffer

- Simultaneous transmission and reception capability

- 8/4-bit transfer, external/internal clock, and leading/trailing edge shift mode

For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance / Handling Precautions.

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc...

The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

2000-10-19 6-22-1

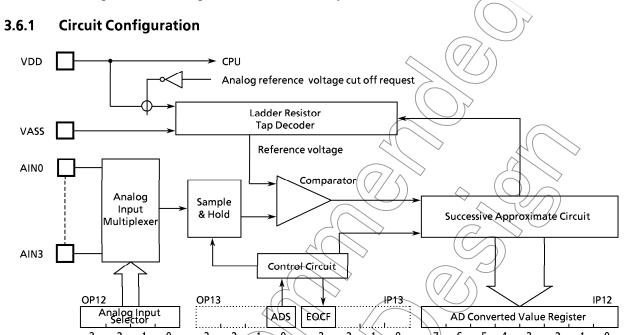

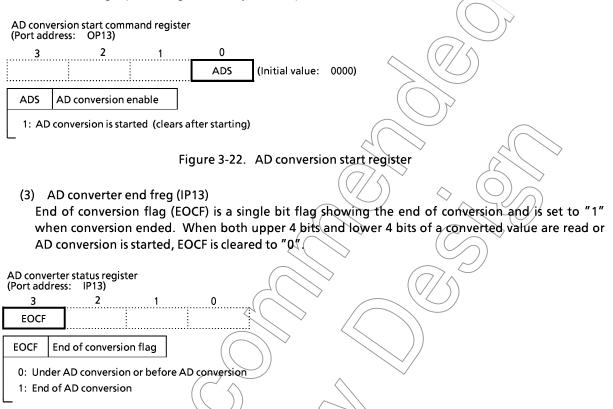

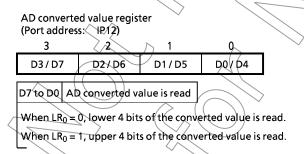

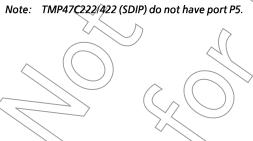

◆8-bit successive approximate type AD converter

• With sample and hold

• 4 analog inputs

• Conversion time: 24  $\mu$ s (at 8 MHz)

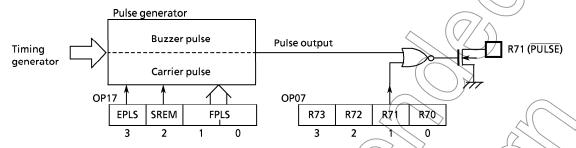

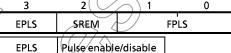

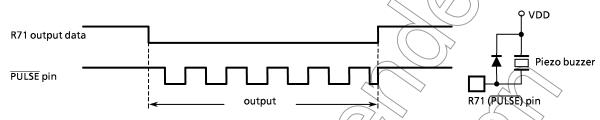

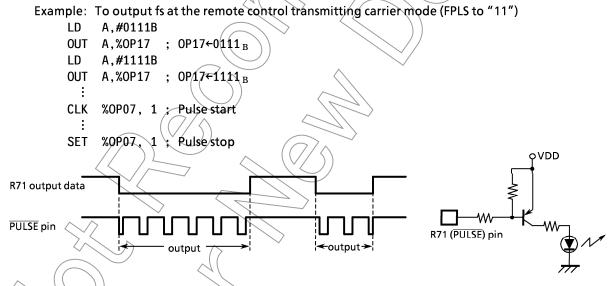

◆Pulse output

Buzzer drive/Remocon carrier

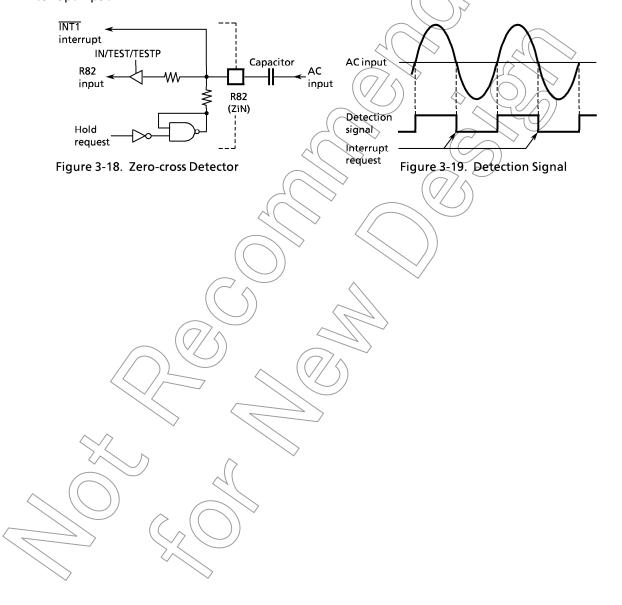

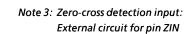

**♦**Zero-cross detector

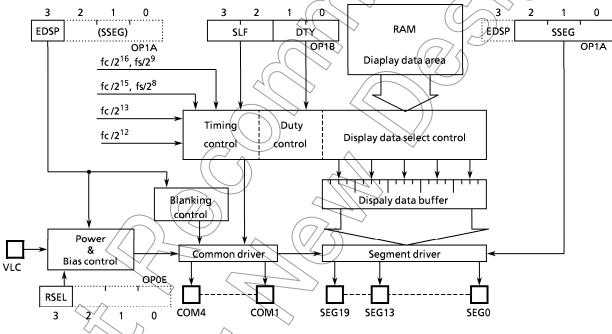

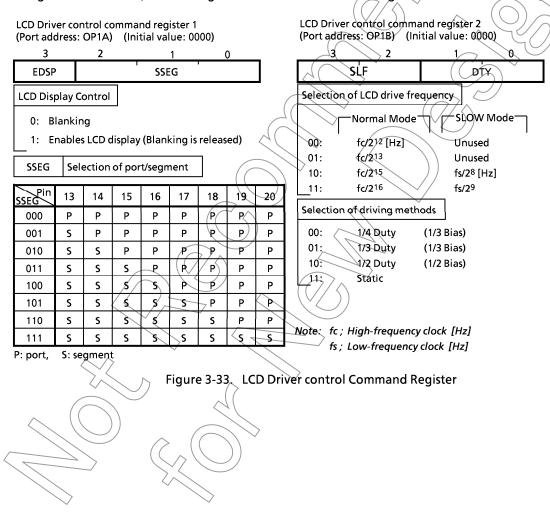

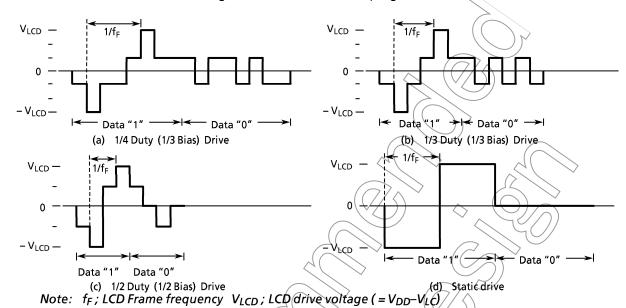

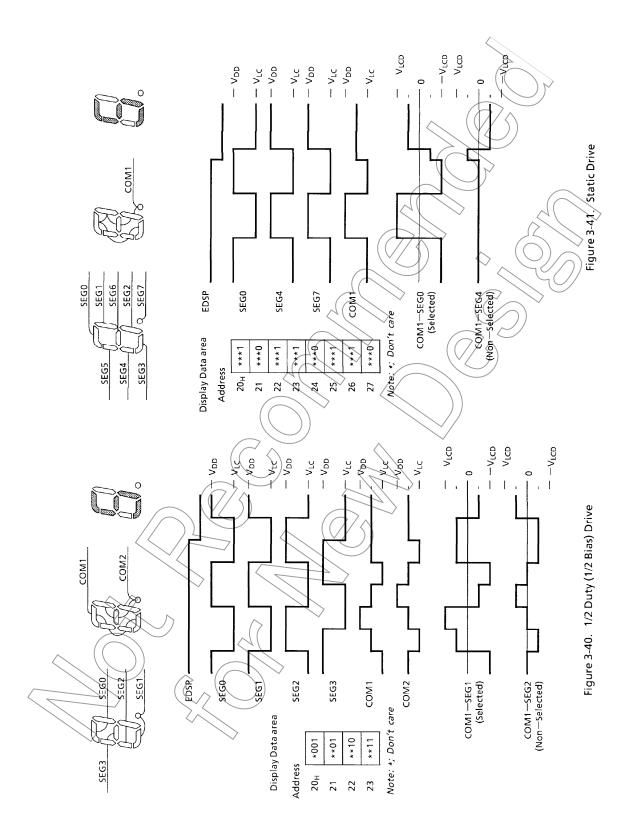

**♦**LCD driver

• LCD direct drive capability (max 10-digit display at 1/4 duty LCD)

• 1/4, 1/3, 1/2 duties or static drive are programmably selectable.

◆Dual-clock operation

High-speed / Low-power-consumption operating mode

◆Hold function

Battery/Capacitor back-up ◆Emulation pod: BM47C422

6-22-3 2000-10-19

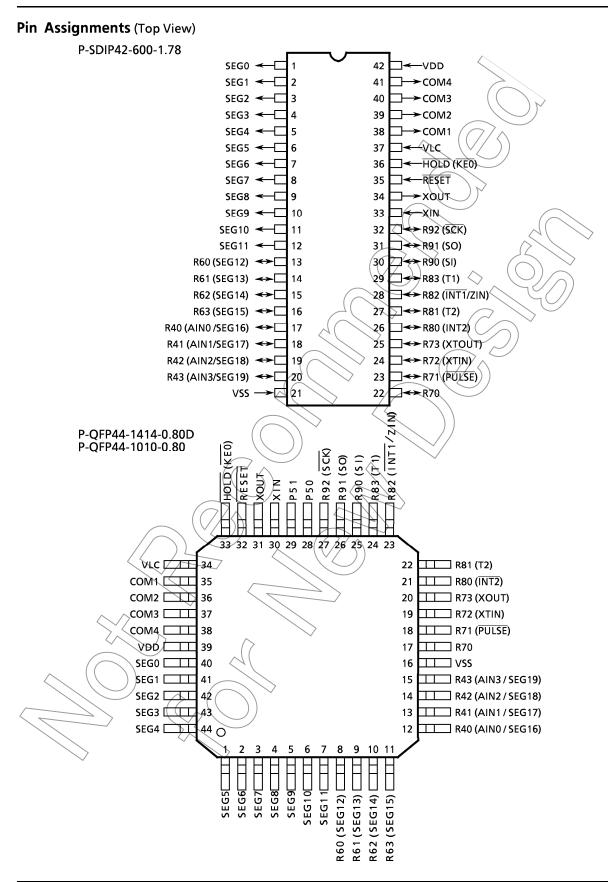

## **Pin Function**

| Pin Name                                | Input / Output     | Function                                                                |                                                         |  |  |  |

|-----------------------------------------|--------------------|-------------------------------------------------------------------------|---------------------------------------------------------|--|--|--|

| R43 (AIN3/SEG19) to<br>R40 (AIN0/SEG16) | I/O<br>(I/O)       | 4-bit I/O ports with latch (P5 port has only                            | AD converter analog input<br>/ LCD segment drive output |  |  |  |

| P51, P50                                | Output             | 2-bit).                                                                 | (Note)                                                  |  |  |  |

| R63 (SEG15) to<br>R60 (SEG12)           | I/O (Output)       | These ports can be set, cleared and tested 〈                            | LCD segment drive output                                |  |  |  |

| R73 (XTOUT)                             | I/O (Output)       | for each bit as specified by L-register                                 | Resonator connecting pins                               |  |  |  |

| R72 (XTIN)                              | I/O (Input)        | indirect addressing bit manipulation                                    | (Low-frequency).                                        |  |  |  |

| R71 (PULSE)                             | I/O (Output)       | instruction.                                                            | Pulse output                                            |  |  |  |

| R70                                     | 1/0                |                                                                         |                                                         |  |  |  |

| R83 (T1)                                |                    | 4-bit I/O ports with latch                                              | Timer / Counter 1 external input                        |  |  |  |

| R82 (INT1/ZIN)                          | 1/0                | When used as input port, external interrupt input pin, or timer/counter | External interrupt1 and zero-cross input                |  |  |  |

| R81 (T2)                                | (Input)            | external input pin, the latch must be set to                            | Timer / Counter2 external input                         |  |  |  |

| R80 (ĪNT2)                              |                    | "1".                                                                    | External interrupt2 input                               |  |  |  |

| R92 ( <del>SCK</del> )                  | 1/0 (1/0)          | 3-bit I/O ports with latch                                              | Serial clock NO                                         |  |  |  |

| R91 (SO)                                | I/O (Output)       | When used as input port or serial port, the                             | Serial data output                                      |  |  |  |

| R90 (SI)                                | I/O (Input)        | latch must be set to "1".                                               | Serial data input                                       |  |  |  |

| SEG11 to SEG0                           |                    | LCD segment drive output                                                | <i>\</i> //                                             |  |  |  |

| COM4 to COM1                            | Output             | LCD Common drive output                                                 | <u> </u>                                                |  |  |  |

| XIN                                     | Input              | Resonator connecting pins (High-frequency)                              | ).                                                      |  |  |  |

| хоит                                    | Output             | For inputting external clock, XIN is used and                           | XOUT is opened                                          |  |  |  |

| RESET                                   | Input              | Reset signal input                                                      |                                                         |  |  |  |

| HOLD (KEO)                              | I/O (Input)        | HOLD request/release signal input                                       | sense input                                             |  |  |  |

| VDD (VAREF)                             |                    | +5V                                                                     | AD converter analog reference voltage                   |  |  |  |

| VSS (VASS)                              | Power Supply       | 0 V (GND)                                                               | AD converter analog reference voltage (GND)             |  |  |  |

| VLC                                     | $\setminus$ $\cap$ | LCD drive power supply                                                  |                                                         |  |  |  |

Note: TMP47C222/422N (SDIP) do not have port P5.

#### **Operational Description**

Concerning the TMP47C222/422 the configuration and functions of hardware are described. The basic instruction of configuration in the TMP47C222/422 is the same as those of TLCS-470 series.

#### 1. System Configuration

- ◆Internal CPU Function

- 2.1 Program Counter (PC)

- 2.2 Program Memory (ROM)

- 2.3 H Register, L Register

- 2.4 Data Memory (RAM)

- a. Stack,

- b. Stack Pointer Word (SPW),

- c. Data Counter (DC)

- 2.5 ALU, Accumulator

- 2.6 Flags

- 2.7 System Clock Controller

- 2.8 Interrupt Controller

- 2.9 Reset Controller

- Watchdog Timer

#### ◆ Peripheral Hardware Function

- 3.1 I/O Ports

- 3.2 Interval Timer

- 3.3 Timer/Counters (TC1, TC2)

- 3.4 Pulse output

- 3.5 Zero-cross detector

- 3.6 AD converter

- 3.7 Serial Interface

- 3.8 LCD Driver

#### 2. Internal CPU Function

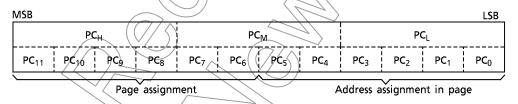

#### 2.1 Program Counter (PC)

The program counter is a 12-bit binary counter which indicates the address of the program memory storing the next instruction to be executed. Normally, the PC is incremented by the number of bytes of the instruction every time it is fetched. When a branch instruction or a subroutine instruction has been executed or an interrupt has been accepted, the specified values listed in Table 2-1 are set to the PC. The PC is initialized to "0" during reset. In the TMP47C222/422, the long franch instruction [BSL a] should not be used.

Figure 2-1. Configuration of Program Counter

The PC can directly address a 4096-byte address space. However, with the short branch and subroutine call instructions, the following points must be considered in the TMP47C222/422, the long branch instruction [BSL a] should not be used.

#### (1) Short branch instruction [BSS a]

In [BSS a] instruction execution, when the branch condition is satisfied, the value specified in the instruction is set to the lower 6 bits of the PC. That is, [BSS a] becomes the in-page branch instruction. When [BSS a] is stored at the last address of the page, the upper 6 bits of the PC point the next page, so that branch is made to the next page.

#### (2) Subroutine call instruction [CALL a]

In [CALL a] instruction execution, the contents of the PC are saved to the stack then the value specified in the instruction is set to the PC. The address which can be specified by the instruction consists of 11 bits and the most significant bit of the PC is always "0". Therefore, the entry address of the subroutine should be within an address range of 000<sub>H</sub> through 7FF<sub>H</sub>.

| In       | struction<br>or   | Condition                                                 | Program Counter (PC)                                                                                                                                                                              |  |  |  |  |  |

|----------|-------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 0        | peration          |                                                           | PC <sub>11</sub> PC <sub>10</sub> PC <sub>9</sub> PC <sub>8</sub> PC <sub>7</sub> PC <sub>6</sub> PC <sub>5</sub> PC <sub>4</sub> PC <sub>3</sub> PC <sub>2</sub> PC <sub>1</sub> PC <sub>0</sub> |  |  |  |  |  |

| 0        | BS a              | SF = 1<br>(Branch condition is satisfied)                 | Immediate data specified by the instruction                                                                                                                                                       |  |  |  |  |  |

| +        |                   | SF = 0 (Branch condition is not satisfied)                | + 2                                                                                                                                                                                               |  |  |  |  |  |

| 2        |                   | Lower 6-bit address $\neq$ 111111                         | Hold Immediate data specified by the instruction                                                                                                                                                  |  |  |  |  |  |

| l n s t  | BSS a             | Lower 6-bit address<br>= 111111<br>(last address in page) | + 1 Immediate data specified by the instruction                                                                                                                                                   |  |  |  |  |  |

| <b> </b> |                   | SF = 0                                                    |                                                                                                                                                                                                   |  |  |  |  |  |

| °        | CALL a            |                                                           | 0 Immediate data specified by the instruction                                                                                                                                                     |  |  |  |  |  |

| <br>0    | CALLS a           |                                                           | 0 0 0 0 (The data generated by the immediate 1 1 0                                                                                                                                                |  |  |  |  |  |

| ت<br>ب   | RET               |                                                           | The return address restored from stack                                                                                                                                                            |  |  |  |  |  |

| 9<br>V   | RETI              |                                                           | The return address restored from stack                                                                                                                                                            |  |  |  |  |  |

| اسُ      | Others            |                                                           | Incremented by the number of bytes in the instruction                                                                                                                                             |  |  |  |  |  |

|          | errupt<br>eptance |                                                           | 0 0 0 0 0 0 0 0 Interrupt vector 0                                                                                                                                                                |  |  |  |  |  |

|          | Reset             |                                                           | 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                               |  |  |  |  |  |

Table 2-1. Status Change of Program Counter

#### 2.2 Program Memory (ROM)

Programs and fixed data are stored in the program memory. The instruction to be executed next is read from the address indicated by the contents of the PC.

The fixed data can be read by using the table look-up

instructions.

## Table look-up instructions

[LDL A, @DC], [LDH A, @DC+]

The table look-up instructions read the lower and upper 4 bits of the fixed data stored at the address specified in the data counter (DC) to place them into the accumulator. [LDL A, @DC] instruction reads the lower 4 bits of fixed data, and [LDH A, @DC+] instruction reads the upper 4 bits.

The DC is a 12-bit register, allowing it to address the entire program memory space.

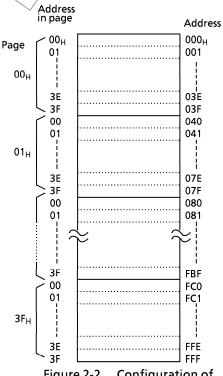

Figure 2-2. Configuration of Program Meory

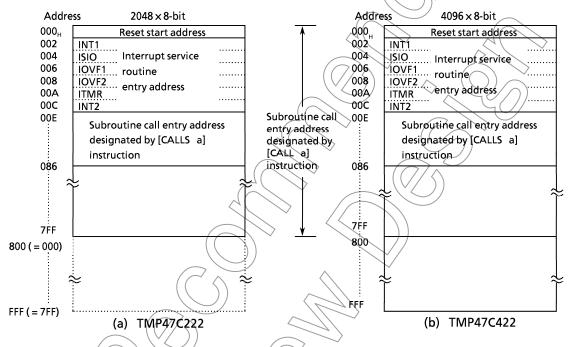

#### 2.2.1 Program Memory Capacity

Figure 2-3 shows the program memory map. Address  $000_H$  to  $086_H$  of the program memory are also used for special purposes.

#### 2.2.2 Program Memory Map

The TMP47C222 has 2048  $\times$  8 bits (addresses 000<sub>H</sub> to 7FF<sub>H</sub>) of program memory (mask ROM), the TMP47C422 has 4096  $\times$  8 bits (addresses 000<sub>H</sub> to FFF<sub>H</sub>).

On the TMP47C222, no physical program memory exists in the address range 800 H to FFF<sub>H</sub>. However, if this space is accessed by program, the most significant bit of each address is always regarded as "0" and the contents of the program memory corresponding to the address 000 H to 7FF<sub>H</sub> are read.

Figure 2-3. Program Memory Map

#### 2.3 H Register and L Register

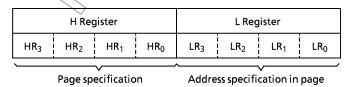

The H register and the L register are 4-bit general registers. They are also used as a register pair (HL) for the data memory (RAM) addressing pointer. The RAM consists of pages, each page being 16 words long (1 word = 4 bits). The H register specifies a page and the L register specifies an address in the page.

The L register has the auto-post-increment/decrement capability, implementing the execution of composite instructions. For example, [ST A, @HL+] instruction automatically increments the contents of the L register after data transfer.

During the execution of [SET @L], [CLR @L], or [TEST @L] instructions, the L register is also used to specify the bits corresponding to I/O port pins R73 through R40 (the indirect addressing of port bits by the L register).

Figure 2-4. Configuration of H and L Registers

6-22-7 2000-10-19

Example 1: To write immediate values "5" and "F" to data memory addresses 18<sub>H</sub> and 11<sub>H</sub>.

LD HL,#10H ; HL←10<sub>H</sub>

ST #5,0HL+ ; RAM  $[10_H] \leftarrow 5_H$ , LR $\leftarrow$ LR + 4ST #0FH,0HL+ ; RAM  $[11_H] \leftarrow F_H$ , LR $\leftarrow$ LR + 1

Example 2: The output latch of R71 pin set "1" by the L register.

LD L,#1101B

SET @L

#### 2.4 Data Memory (RAM)

The data memory stores user-processed data. One page of this memory is 16 words long (1 word = 4 bits). It has 16 pages.

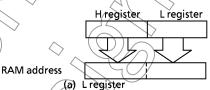

The RAM is addressed in one of the three ways (addressing modes):

(1) Register-indirect addressing mode

In this mode, a page is specified by the H register

and an address in the page by the L register.

Example: LD A, @HL ; Acc←RAM [HL]

Instruction field

XXXX

xxxx

(2) Direct addressing mode

In this mode, an address is directly specified by the 8 bits of the second byte (operand) in the instruction field.

Example: LD A, 2CH ; Acc\( RAM[2CH]

(3) Zero-page addressing mode

In this mode, an address in zero-page (addresses 00<sub>H</sub>

through 0F<sub>H</sub>) is specified by the lower 4 bits of the

second byte (operand) in the instruction field.

Figure 2-5. Addressing mode

#### 2.4.1 Data Memory Map

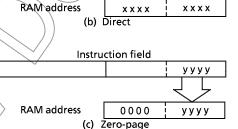

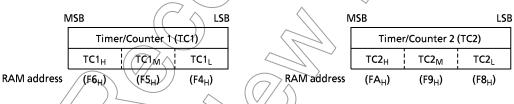

Figure 2-6 shows the data memory map. The data memory is also used for the following special purpose.

- ① Stack and Stack Pointer Word (SPW)

- ② Data Counter (DC)

- 3 Count registers of the timer/counters (TC1, TC2)

- 4 Zero-page

Note2: The TC1 and TC2 areas are shared by the locations 13 and 14.

Figure 2-6. Data Memory Map

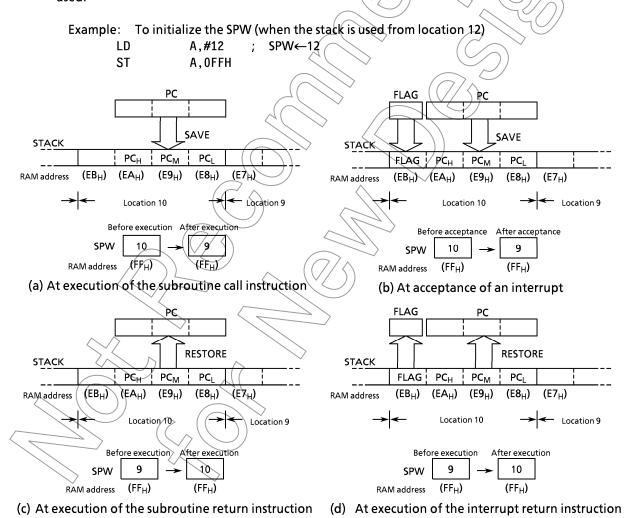

#### (1) Stack

The stack provides the area in which the return address is saved before a jump is performed to the processing routine at the execution of a subroutine call instruction or the acceptance of an interrupt. When a subroutine call instruction is executed, the contents (the return address) of the program counter are saved, when an interrupt is accepted, the contents of the program counter and flags are saved.

When returning from the processing routine, executing the subroutine return instruction [RET] restores the contents of the program counter from the stack; executing the interrupt return instruction [RETI] restores the contents of the program counter and flags.

The stack consists of up to 15 levels (locations 0 through 14) which are provided in the data memory (addresses CO<sub>H</sub> through FB<sub>H</sub>). Each location consists of 4-word data memory. Locations 13 and 14 are shared with the count registers of the timer/counters (TC1, TC2) to be described later.

The save/restore locations in the stack are determined by the stack pointer word (SPW). The SPW is automatically decremented after save, and incremented before restore. That is, the value of the SPW indicates the stack location number for the next save.

6-22-9 2000-10-19

#### (2) Stack Pointer Word (SPW)

Address FF<sub>H</sub> in the data memory is called the stack pointer word, which identifies the location in the stack to be accessed (save or restore).

Generally, location number 0 to 12 can be set to the SPW, providing up to 13 levels of stack nesting. Locations 13 and 14 are shared with the timer/counters to be described later; therefore, when the timer/counters are not used, the stack area of up to 15 levels is available. Address FF<sub>H</sub> is assigned to the SPW, so that the contents of the SPW cannot be set "15" in any case.

The SPW is automatically updated when a subroutine call is executed or an interrupt is accepted. However, if it is used in excess of the stack area permitted by the data memory allocating configuration, the user-processed data may be lost. (For example, when the user-processed data area is in an address range 00<sub>H</sub> through CF<sub>H</sub>, up to location 4 of the stacks are usable. If an interrupt is accepted with location 4 already used, the user-processed data stored in addresses CC<sub>H</sub> through CF<sub>H</sub> corresponding to the location 3 area is lost.)

The SPW is not initialized by hardware, requiring to write the initial value (the location with which the use of the stack starts) by using the initialization routine. Normally, the initial value of "12" is used.

Figure 2-7. Accessing Stack (Save/Restore)

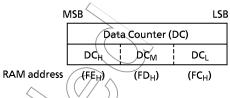

#### (3) Data Counter (DC)

The data counter is a 12-bit register to specify the address of the data table to be referenced in the program memory (ROM). Data table reference is performed by the table look-up instructions [LDL A, @DC] and [LDH A, @DC+]. The data table may be located anywhere within the program memory address space.

The DC is assigned with a RAM address in unit of 4 bits. Therefore, the RAM manipulation instruction is used to set the initial value or read the contents of the DC.

Figure 2-8. Data Counter

Example: To set the DC to  $780_{\text{H}}$ .

LD HL, #0FCH ; Sets RAM address of DC<sub>L</sub> to HL register pair:

ST #0H,@HL+ ; DC ← 780<sub>H</sub>

ST #8H,@HL+

ST #7H,@HL+

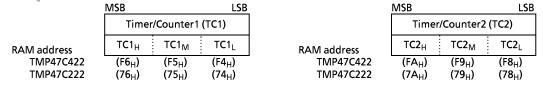

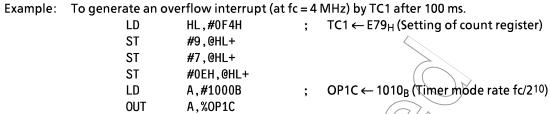

## (4) Count registers of the timer/counters (TC1, TC2)

The TMP47C222/422 has two channels of 12-bit timer/counters. The count register of the timer/counter is assigned with a RAM addresses in unit of 4 bits, so that the initial value is set and the contents are read by using the RAM manipulation instruction.

The count registers are shared with the stack area (locations 13 and 14) described earlier, so that the stack is usable from location 13 when the timer/counter 1 is not used. When none of timer/counter 1 and timer/counter 2 are used, the stack is usable from location 14.

When both timer/counter 1 and timer/counter 2 are used, the data memory locations at addresses F7<sub>H</sub> and FB<sub>H</sub> can be used to store the user processed data.

Figure 2-9. Count Registers of the Timer/Counters (TC1, TC2)

#### (5) Zero-page

The 16 words (at addresses 00<sub>H</sub> through 0F<sub>H</sub>) of the zero page of the data memory can be used as the user flags or pointers by using zero-page addressing mode instructions (comparison, addition, transfer, and bit manipulation), providing enhanced efficiency in programming.

Example: To write immediate data "8" to address 09<sub>H</sub> if bit 2 at address 04<sub>H</sub> in the RAM is "1".

TEST 04H, 2 ; Skips if bit 2 at address 04<sub>H</sub> in the RAM is "0".

B SKIP

ST #8,09H ; Writes "8" to address 09<sub>H</sub> in the RAM

SKIP:

6-22-11 2000-10-19

#### 2.4.2 Data Memory Capacity

The TMP47C422 has 256  $\times$  4 bits (addresses  $00_H$  to FF<sub>H</sub>) of the data memory (RAM), and the TMP47C222 has  $192 \times 4$  bits (addresses  $00_H$  to  $7F_H$ , and  $C0_H$  through FF<sub>H</sub>).

When power-on is performed, the contents of the RAM become unpredictable, so that they must be initialized by the initialization routine.

Example: To clear RAM (use common to the TMP47C222 and TMP47C422)

LD HL, #00H; HL**←**00<sub>H</sub>

SCLRRAM : ST #0, @HL+; RAM [HL]  $\leftarrow$ 0, LR $\leftarrow$ LR +1

B SCLRRAM

ADD H, #1; HR←HR+1

**B SCLRRAM**

Figure 2-10. Data Memory Capacity and Address Assignment

Note: In the TMP47C222, the zero-page and thespecial function shared area (stack location 3 to 0) are overlapped. At programming, note that addresses 10 to 3FH are assigned to address 50 to 1FH in the TMP47C222. The technical data sheets for the TMP47P422V shall also be referred to.

Address 10 to 8FH should not be accessed.

6-22-12 2000-10-19

#### 2.5 **ALU and Accumulator**

#### 2.5.1 Arithmetic / Logic Unit (ALU)

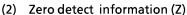

The ALU performs the arithmetic and logic operations specified by instructions on 4-bit binary data and outputs the result of the operation, the carry information (C), and the zero detect information (Z).

#### (1) Carry information (C)

The carry information indicates a carry-out from the most significant bit in an addition. A subtraction is performed as addition of two's complement, so that, with a subtraction, the carry information indicates that there is no borrow to the most significant bit. With a rotate instruction, the information indicates the data to be shifted out from the accumulator.

This information is "1" when the operation result or the data to be transferred to the accumulator/data memory is "0000<sub>B</sub>".

Note: Cin indicates the carry input \_specified by)instruction

Figure 2-11.

Example: The carry information (C) and zero detect information (Z) for 4-bit additions and subtractions.

| Operation | Result                  | Z       |

|-----------|-------------------------|---------|

| 4 + 2 =   | 6 (0                    | 0       |

| 7 + 9 =   | 0                       | ( ) ) 1 |

| 8 - 1 =   | 7                       | 0       |

| 2 - 2 =   | 0 ( ( \)                | 1       |

| 5 - 8 =   | -3 (1101 <sub>B</sub> ) | 0       |

|           |                         |         |

#### Accumulator (Acc) 2.5.2

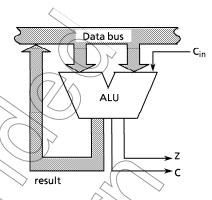

The accumulator is a 4-bit register used to hold source data or results of the operations and data manipulations.

#### 2.6 Flags

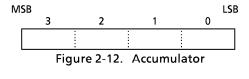

There are a carry flag (CF), a zero flag (ZF) and a status flag (SF), each consisting of 1 bit. These flags are set or cleared according to the condition specified by an instruction. When an interrupt is accepted, the flags are saved on the stack along with the program-counter. When the [RETI] instruction is executed, the flags are restored from the stack to the states set before interrupt acceptance.

Figure 2-13. Flags

#### (1) Carry flag (CF)

The carry flag holds the carry information received from the ALU at the execution of an addition/subtraction with carry instruction, a compare instruction, or a rotate instruction. With a carry flag test instruction, the CF holds the value specified by it.

- ① Addition/subtraction with carry instructions [ADDC A, @HL], [SUBRC A, @HL] The CF becomes the input (C<sub>in</sub>) to the ALU to hold the carry information.

- ② Compare instructions [CMPR A, @HL], [CMPR A, #k] The CF holds the carry information (non-borrow).

- Solution (ROLC A), [RORC A] The CF is shifted into the accumulator to hold the carry information (the data shifted out from the accumulator).

- Carry flag test instructions [TESTP CF], [TEST CF]

With [TESTP CF] instruction, the content of the CF is transferred to the SF then the CF is set to "1".

With [TEST CF] instruction the cubes obtained by invention the content of the CF is

With [TEST CF] instruction, the value obtained by inverting the content of the CF is transferred to the SF then the CF is cleared to "0".

#### (2) Zero flag (ZF)

The zero flag holds the zero detect information (Z) received from the ALU at the execution of an operational instruction, a rotate instruction, an input instruction, or a transfer-to-accumulator instruction.

#### (3) Status flag (SF)

The status flag provides the branch condition for a branch instruction. Branch is performed when this flag is set to "1". Normally the SF is set to "1", so that any branch instruction can be regarded as an unconditional branch instruction. When a branch instruction is executed upon set or clear of the SF according to the condition specified by an instruction, this instruction becomes a conditional branch instruction. During reset, the SF is initialized to "1", other flags are not affected.

Example: When the following instructions are executed with the accumulator, H register, L register, data memory (address 07H), and carry flag being set to "CH", "0", "7", "5", and "1" respectively, the contents of the accumulator and flags become as follows:

| Instruction  | Acc after          | Flag after execution |             |    |  |

|--------------|--------------------|----------------------|-------------|----|--|

| instruction  | execution          | CF                   | ΣF          | SF |  |

| ADDC A, @HL  | 2 <sub>H</sub>     | 1_                   | 0           | /0 |  |

| SUBRC A, @HL | 9 <sub>H</sub>     | 0                    | <b>(0</b> \ | 0  |  |

| CMPR A, @HL  | C <sub>H</sub>     | 6                    | <u>(</u>    | 1  |  |

| AND A, @HL   | 4 <sub>H</sub>     |                      | 0           | 1  |  |

| LD A, @HL    | 5 <sub>H</sub> ( / | // 1                 | 0           | 1  |  |

| la et vi et i a | Acc after      | Flag after execution |    |    |  |

|-----------------|----------------|----------------------|----|----|--|

| Instruction     | execution      | CF                   | ZF | SF |  |

| LD A, #0        | 0 <sub>H</sub> | 1                    | 1  | 1  |  |

| ADD A, #4       | 0 <sub>H</sub> | 1                    | 1  | 0  |  |

| DEC A           | B <sub>H</sub> | 1                    | 0  | 1  |  |

| ROLC A          | 9 <sub>H</sub> | 1                    | 0  | 0  |  |

| RORC A          | E <sub>H</sub> | 0                    | 0  | 1  |  |

#### 2.7 System Clock Controller

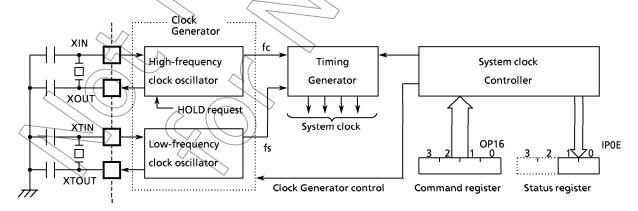

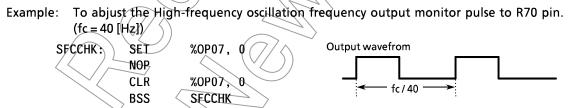

Figure 2-14. Clock Generator, Timing Generator and System Clock Controller

#### 2.7.1 Clock Generator

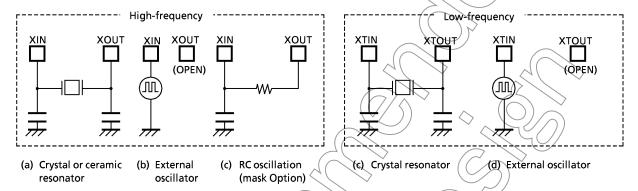

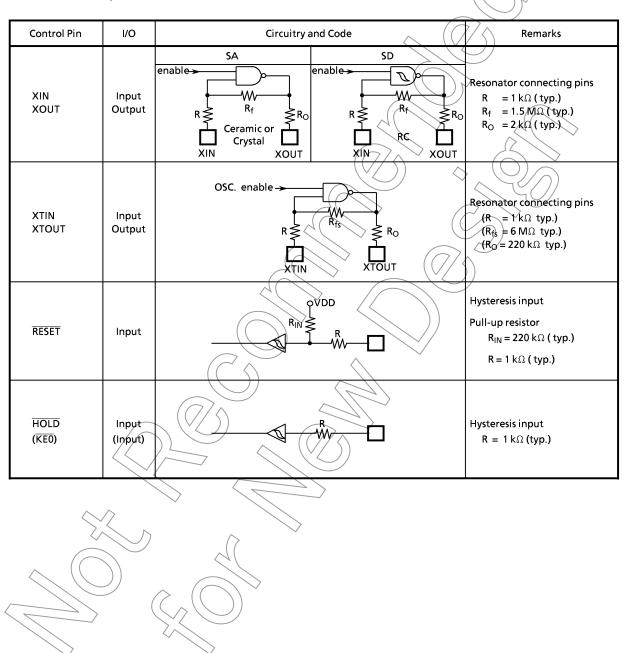

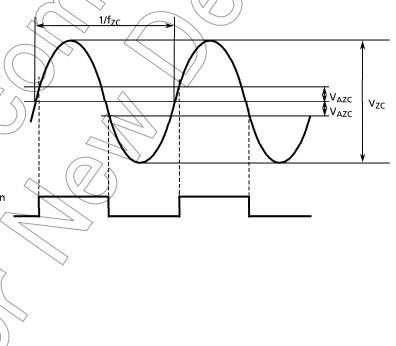

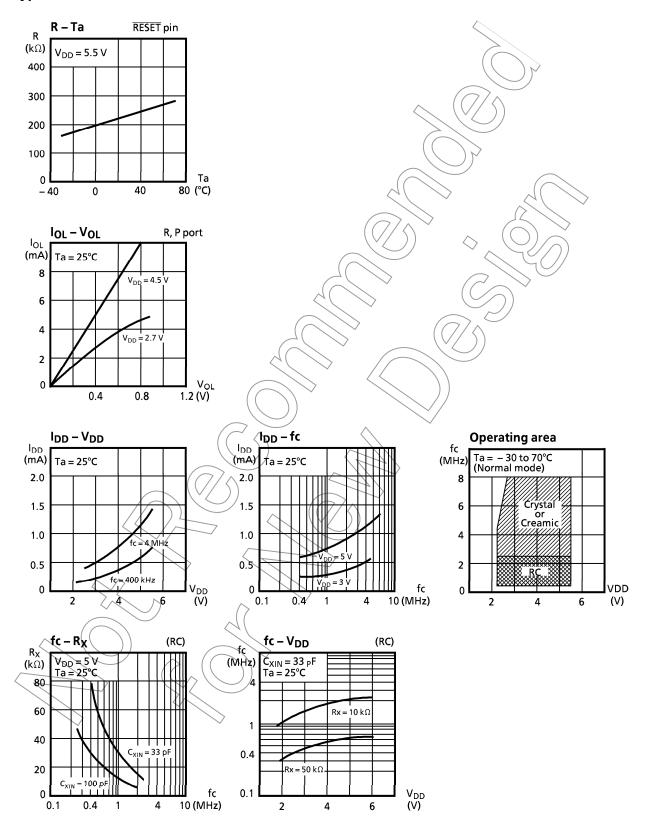

The clock generator produces the basic clock pulses which provide the system clock to be supplied to the CPU and peripheral hardware. It contains two oscillators: a high-frequency clock oscillator and a low-frequency clock oscillator. Power consumption can be reduced by switching to the low power operation based on the low-frequency clock by the system clock controller. The high-frequency clock and the low-frequency clock can be easily obtained by attaching a resonator between the XIN and XOUT pins and the XTIN and XTOUT pins, respectively (At the high-frequency clock, RC oscillation is also posible, depending on the mask option). The system clock can also be obtained from the external oscillator.

Figure 2-15. Examples of Resonator Connection

Note: Accurate adjustment of the oscillation frequency

Although no hardware to externally and directly monitor the clock pulse is not provided, the oscillation frequency can be adjusted by making the program to output the pulse with a fixed frequency to the port with the all interrupts disabled and timer/counters stopped and monitoring this pulse. With a system requiring the oscillation frequency adjustment, the adjusting program must be created beforehand.

#### 2.7.2 Timing Generator (TG)

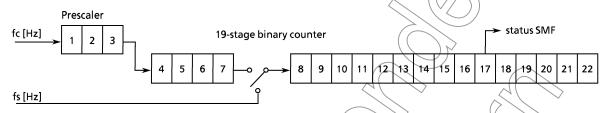

The timing generator produces the system clocks from clock pulse which are supplied to the CPU and peripheral hardweare.

The timing generater consists of a 19-stage binary counter with a divide-by-3 prescaler. The source clock to the timing generater and its input stage depend on the operating mode as shown below.

During reset, the binary counter is cleared to "0". However, the prescaler is not cleared.

- a. Single-clock mode

- ① Normal-1 operating mode

The CPU and the peripheral hardware are operated on the high-frequency clock. At reset release, this mode is set. In this mode, it is necessary to clear SLCK (bit 2 of command register OP16) to "0".

- ② HOLD operating mode

In this mode, the system operations are all stopped, holding the internal states valid immediately before the stop at the low power consumption level.

- b. Dual-clock mode

- ① Normal-2 operating mode

In this mode, the CPU is operated on the high-frequency clock but many peripheral hardware operate on the low-frequency clock.

- ② SLOW operating mode

In this mode, the high-frequency clock oscillation is stopped to operate the CPU and the peripheral hardware on the low-frequency clock, thereby reducing power consumption.

Figure 2-16. Configuration of Timing Generater

- (2) The timing generater provides the following functions:

- ① Instruction cycle

- 4 Internal serial clock for a serial interface

- 2 Internal pulse for interval timer

- **S** Warm-up time at release of the hold operation

- ③ Internal pulse for timer/counters

- © Source clock for a watchdog timer

#### 2.7.3 System Clock Controller

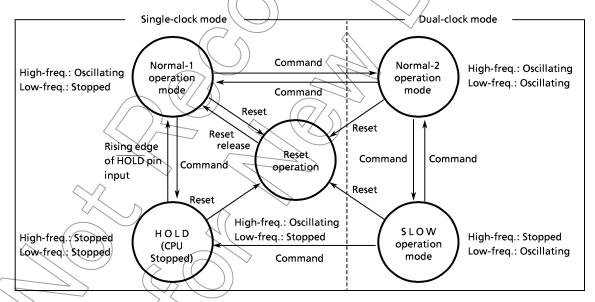

The system clock controller starts or stops the high-frequency and low-frequency clock oscillator and switches between the basic clocks. The operating mode is generally divided into the single-clock mode and the dual-clock mode, which are controlled by command.

Figure 2-17. Operating Mode Transition Diagram

Note: Normal-1 and Normal-2 operating modes are sometimes referred to as the Normal operating mode collectively.

6-22-16 2000-10-19

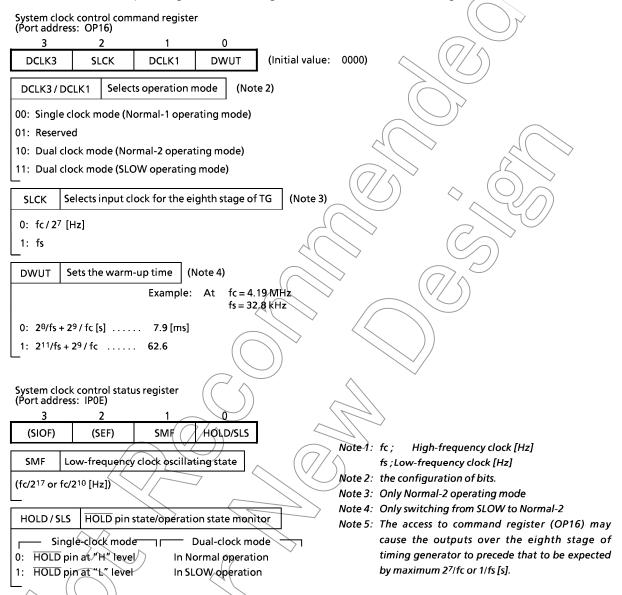

#### (1) System clock control

System clock control is performed by the command register (OP16). During reset, this register is initialized to "0" and the single-clock mode is selected.

Each state at operating mode switching can be read from the status register (IPOE).

Figure 2-18. System Clock Control Command Register/Status Register

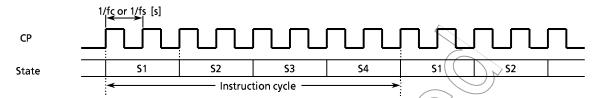

#### (2) Instruction Cycle

The instruction execution and on-chip peripheral hardware operations are performed in synchronization with the basic clock. The smallest unit of instruction execution is called the "instruction cycle". The TLCS-470 series instruction set has 2 kinds of instructions, 1-cycle instruction and 2-cycle instruction. Each instruction cycle consists of 4 states (\$1 through \$4\$). Each state consists of 2 basic clock pulses.

6-22-17 2000-10-19

Figure 2-19. Instruction Cycle

#### 2.7.4 Operation Mode

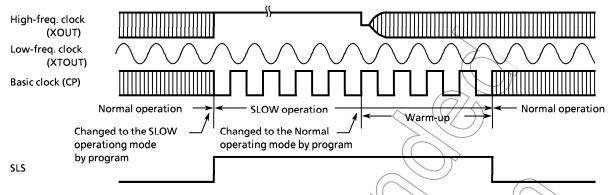

#### (1) Dual-clock mode

In this mode, the Normal-2 operation is generally performed by generating the instruction cycle from the high-frequency clock (fc). As required, the instruction cycle is generated by the low-frequency clock (fs), and the lower consumption power operation is performed by transferring SLOW operation to HOLD operation. The following describes the switching between the Normal-2, SLOW and HOLD operations in the dual clock mode. At reset, the command register is initialized to the single-clock mode. Since the low-frequency clock is not oscillated. Normal-2 operation in the dual clock mode must be set first. The low frequency clock starts oscillating by transferring to Normal-2 operation.

a. Switching from Normal-2 operation to SLOW operation

Setting DCLK1 (bit 1 of OP16) to "1" switches Normal-2 operation to SLOW operation. However it takes a few seconds to get a stable oscillation of the low-frequency clock. Therefore if there is possible to switch from Normal-2 operation to SLOW operation, wait until the low-frequency clock is stable or check the oscillation state by a program. SMF status (bit 1 of 1P0E) is available to check it.

When the high-frequency clock (fc/27) is input to the 8th stage of TG, first sets SLCK (bit 2 of OP16) to "1" ans input the low-frequency clock (fs). Then, SMF is monitored by a program. After confirming that SMF is changed "1" to "0" to "1" or "0" to "1" to "0", set DCLK1 to "1". At this time, the high-frequency clock oscillator stops.

#### b. Returning from SLOW operation to Normal-2 operation

Bit 2 of the command register is cleared to "0" and, at the same time, the warm-up time for return is set to DWUT. When the warm-up time has passed, the Normal-2 operation takes place. By monitoring SLS (bit 0 of the status register), the current operating mode can be known.

Note: The watchdog timer counter is used to count the warming up time.

To count certainly the warming up time, it is neccessary to initialize the counter. When switching from SLOW operation to Normal-2 operation, the watchdog timer must be cleared just before setting of the system clock control command register.

Example: Returning from SLOW operation to Normal-2 operation

LD A, #0000B OUT A, %0P15 LD A, #1100B OUT A, %0P16

Figure 2-20. System Clock Switching Timing

c. Shifting from the SLOW operation to the HOLD operation

By setting the command in the command register (OP10), the low-frequency clock oscillation stops and the HOLD operation starts, refer to subsection "2.7.5 HOLD Operation MODE".

After being released the HOLD operation, the operation mode is NORMAL-1.

Note: In the HOLD and SLOW operating modes, the power consumed by the oscillator and the internal hardware is reduced. However, the power for the pin interface (depending on the external circuitry and program) is not directly associated with the low-power consumption operation. This must be considered in system design as well as interface circuit design.

#### (2) singl-clock mode

In this mode, only the high-frequency clock oscillator is used. Pins R72 (XTIN) and R73 (XTOUT) become the ordinary I/O port. The HOLD operating mode is available for reducing power consumption. It is controlled by the command register (OP10). In this mode, therefore, the system clock control command register (OP16) need not be manipulated. For the details of the HOLD operation, refer to Subsection "2.7.5 HOLD Operating Mode".

#### 2.7.5 HOLD Operating Mode

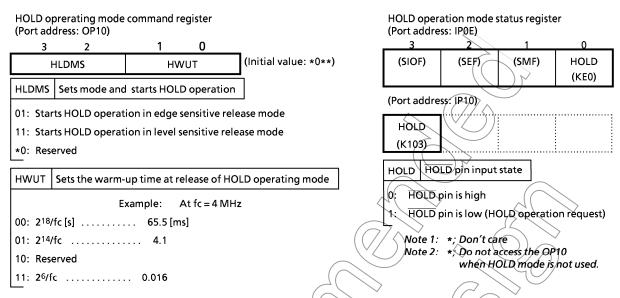

The HOLD feature stops the system and holds the system's internal states active before stop with a low power. The HOLD operation is controlled by the command register (OP10) and the HOLD pin input. The HOLD pin input state can be known by the status register (IP0E or IP10).

Bit 0 of IPOE can be used in the single-clock mode. However the bit 0 of IOOE can not be used in the dual-clock mode, because the bit is used as the operating state monitor (SLS). To monitor the state of HOLD pin input in the dual-clock mode, use bit 3 of IP10. Bit 3 of IP10 can be used in the single-clock mode.

## (1) Starts the HOLD operating mode

Setting the command to the command register starts HOLD operation in Normal-1 or SLOW mode. The following states keep during the HOLD operation.

- ① Oscillator stops and the systems internal operations are all held up.

- 2 The interval timer is cleared to "0".

- The states of the data memory, registers, and latches valid immediately before the system is put in the HOLD state are all held.

- ① The program counter holds the address of the instruction to be executed after the instruction [out A, %OP10] or [OUT @HL, %OP10] which starts the HOLD operating mode.

Figure 2-21. HOLD Operating Mode Command Register / Status Register

The HOLD operating mode consists of the level-sensitive release mode and the edge-sensitive release mode.

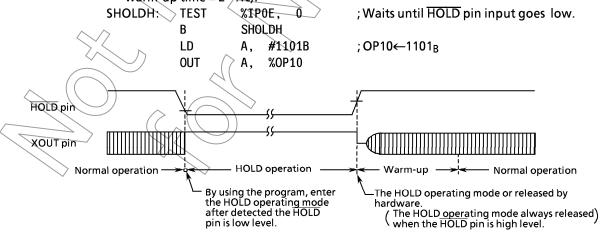

a. Level-sensitive release mode

In this mode, the HOLD operating is released by setting the HOLD pin to the high level. This mode is used for the capacitor backup with the main power off or for the battery backup for long hours.

If the instruction to start the HOLD operation is executed with the HOLD pin input being high, the HOLD operation does not start but the clear sequence (warm-up) sets in immediately. Therefore, to start the HOLD operation in the level-sensitive mode, that the HOLD pin input is low (the HOLD)

operation request) must be recognized in program. This recognition is one of the two ways below:

- 1 Testing HOLD (bit 0 of the status register)

- 2 Applying the HOLD pin input also to the INT1 pin to generate the external interrupt 1 request.

Example: To test HOLD to start the HOLD operation in the level-sensitive release mode (the warm-up time = 214/fc).

Figure 2-22. Level-sensitive Release Mode

6-22-20 2000-10-19

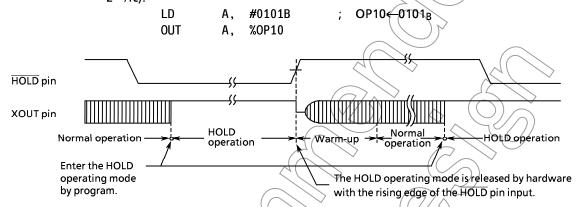

#### b. Edge-sensitive release mode

In this mode, the HOLD operation is released at the rising edge of the HOLD pin input. This mode is used for applications in which a relatively short time program processing is repeated at a certain cycle. This cyclic signal (for example, the clock supplied from the low power dissipation oscillator). In the edge-sensitive release mode, even if the HOLD pin input is high, the HOLD operation is performed.

Example: To start the HOLD operation in the edge-sensitive release mode (the warm-up time = 214/fc).

Figure 2-23. Edge-sensitive Release Mode

Note: In the HOLD operation, the dissipation of the power associated with the oscillator and the internal hardware is lowered; however, the power dissipation associated with the pin interface (depending on the external circuitry and program) is not directly determined by the hardware operation of the HOLD feature.

This point should be considered in the system design and the interface circuit design. In the CMOS circuitry, little current flows when the input level is stable at the power voltage level (V<sub>DD</sub>/V<sub>SS</sub>); however, when the input level gets higher than the power voltage level (by approximately 0.3 to 0.5 V), a current begins to flow. Therefore, if cutting off the output transistor at an I/O port (the open drain output pin with an input transistor connected) puts the pin signal into the high-impedance state, a current flow across the ports input transistor, requiring to fix the level by pull-up or other means.

#### (2) Releases the HOLD operating mode

The HOLD operating mode is released in the following sequence:

- 1) The high-freq. oscillator starts.

- Warm-up is performed to acquire the time for stabilizing oscillation. During the warm-up, the internal operations are all stopped. One of three warm-up times can be selected by program depending on the characteristics of the oscillator used.

- When the warm-up time has passed, an ordinary operation restarts from the instruction next to instruction which starts the HOLD operation.

The warm-up time is obtained by dividing the basic clock by the interval timer, so that, if the frequency at clearing the HOLD operation is unstable, the warm-up time shown in Figure 2-23 includes an error. Therefore, the warm-up time must be handled as an approximate value.

The HOLD operation is also released by setting the RESET pin to the low level. In this case, the normal reset operation follows immediately.

6-22-21 2000-10-19

Note: To release the HOLD operation at a low hold voltage, the following points must be considerred:

To release the HOLD operation, the power voltage needs to be raised to the operating voltage level. If this is done, the RESET pin input, which is at the high level, also rises with the power voltage. In this case, if a time constant circuit or the like is externally attached, the rise of the RESET pin input voltage goes behind the rise of the power voltage. At this time, if the voltage level of the RESET pin input drops below the non-inverted high level input voltage of the RESET pin input (hysteresis input), the reset operation may occur.

#### 2.8 Interrupt Function

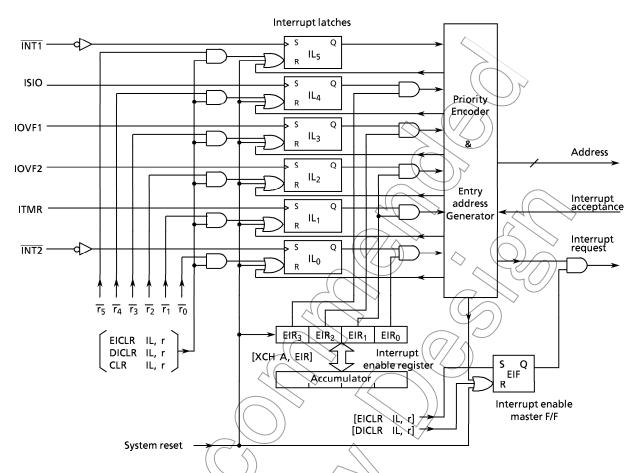

#### (1) Interrupt Controller

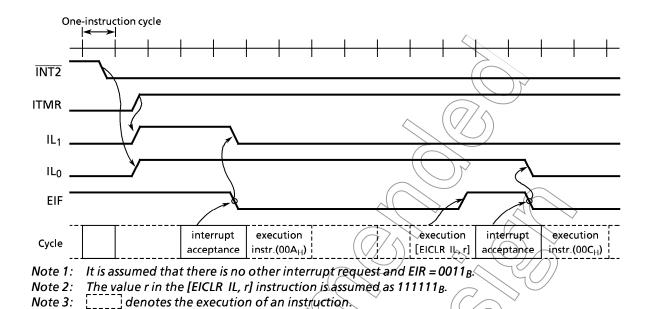

There are 6 interrupt sources (2 external and 4 internal). The prioritized multiple interrupt capability is supported. The interrupt latches (IL<sub>5</sub> through IL<sub>0</sub>) to hold interrupt requests are provided for the interrupt sources. Each interrupt latch is set to "1" when an interrupt request is made, asking the CPU to accept the interrupt. The acceptance of interrupt can be permitted or prohibited by program through the interrupt enable master flip-flop (EIF) and interrupt enable register (EIR). When two or more interrupts occur simultaneously, the one with the highest priority determined by hardware is serviced first.

Table 2-2. Interrupt Sources

|          | Interrupt Source                                               |  | Priority    | Interrupt<br>Latch | Enable conditions             | Entry<br>address |

|----------|----------------------------------------------------------------|--|-------------|--------------------|-------------------------------|------------------|

| External | Extenal Interrupt 1 (INT1)                                     |  | (highest) 1 | IL <sub>5</sub>    | EIF = 1                       | 002 <sub>H</sub> |

|          | Serial Interface Interrupt (ISIQ)                              |  | 2           | IL <sub>4</sub>    | EIF = 1, EIR <sub>3</sub> = 1 | 004 <sub>H</sub> |

| Internal | TC1 overflow Interrupt (IOVF1                                  |  | 3           | 11/3               | $EIF = 1, EIR_2 = 1$          | 006 <sub>H</sub> |

| Internal | TC2 overflow Interrupt (IOVF2) Interval Timer Interrupt (ITMR) |  | 4           | IL <sub>2</sub>    | 515 4 51B 4                   | 008 <sub>H</sub> |

|          |                                                                |  | 5           | IL <sub>1</sub>    | $EIF = 1, EIR_1 = 1$          | 00A <sub>H</sub> |

| External | External Interrupt 2 (INT2)                                    |  | (lowest) 6  | IL <sub>0</sub>    | EIF = 1, EIR <sub>0</sub> = 1 | 00C <sub>H</sub> |

Figure 2-24. Interrupt Controller Block Diagram

#### a. Interrupt enable master flip-flop (EIF)

The EIF controls the enable/disable of all interrupts. When this flip-flop is cleared to "0", all interrupts are disabled; when it is set to "1", the interrupts are enabled.

When an interrupt is accepted, the EIF is cleared to "0", temporarily disabling the acceptance of subsequent interrupts. When the interrupt service program has been executed, the EIF is set to "1" by the execution of the interrupt return instruction [RETI], being put in the enabled state again.

Set or clear of the EIF in program is performed by instructions [EICLR IL, r] and [DICLR IL, r], respectively. The EIF is initialized to "0" during reset.

#### b. Interrupt enable register (EIR)

The EIR is a 4-bit register specifies the enable or disable of each interrupt except INT1. An interrupt is enabled when the corresponding bit of the EIR is "1", and an interrupt is disabled when the corresponding bit of the EIR is "0". Bit 1 of the EIR (EIR<sub>1</sub>) is shared by both IOVF2 and ITMR interrupts. Read/write on the EIR is performed by executing [XCH A, EIR] instruction. The EIR is initialized to "0" during reset.

#### c. Interrupt latch (IL)

An interrupt latch is provided for each interrupt source. The IL is set to "1" when an interrupt request is made to ask the CPU for accepting the interrupt. Each IL is cleared to "0" upon acceptance of the interrupt. It is initialized to "0" during reset.

The ILs can be cleared independently by interrupt latch operation instructions ([EICLR IL, r], [DICLR IL, r], and [CLR IL, r]) to make them cancel interrupt requests or initialize by program. When the value of instruction field (r) is "0", the interrupt latch is cleared; when the value is "1", the IL is held. Note that the ILs cannot be set by instruction.

Example 1: To enable IOVF1, INT1, and INT2 interrupts.

LD A,#0101B ; EIR←0101<sub>B</sub>

XCH A.EIR

EICLR IL,111111B; EIF←1

Example 2: To set the EIF to "1", and to clear the interrupt latches except ISIO to "0".

EICLR IL,010000B;  $E|F \leftarrow 1$ ,  $|L_5 \leftarrow 0$ ,  $|L_3 \rightarrow |L_0 \leftarrow 0|$

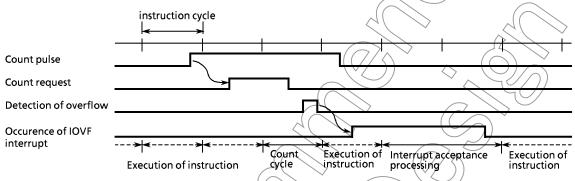

#### (2) Interrupt Processing

An interrupt request is held until the interrupt is accepted or the IL is cleared by the reset or the interrupt latch operation instruction. The interrupt acknowledge processing is performed in 2 instruction cycles after the end of the current instruction execution (or after the timer/counter processing if any). The interrupt service program terminates upon execution of the interrupt return instruction [RETI].

The interrupt acknowledge processing consists of the following sequence:

- ① The contents of the program counter and the flags are saved on the stack.

- ② The interrupt entry address corresponding to the interrupt source is set to the program counter.

- 3 The status flag is set to "1".

- **4** The EIF is cleared to  $^{\circ}0''$ , temporarily disabling the acceptance of subsequent interrupts.

- ⑤ The interrupt latch for the accepted interrupt source is cleared to "0".

- © The instruction stored at the interrupt entry address is executed. (Generally, in the program memory space at the interrupt entry address, the branch instruction to each interrupt processing program is stored.)

To perform the multi-interrupt, the EIF is set to "1" in the interrupt service program, and the acceptable interrupt source is selected by the EIR. However, for the INT1 interrupt, the interrupt service is disabled under software control because it is not disabled by the EIR.

Example: The INT1 interrupt service is disabled under software control (Bit 0 of RAM [05<sub>H</sub>] are assigned to the disabling switch of interrupt service).

PINT1: TEST 05H, 0 ; Skips if RAM  $[05H]_0$  is "1"

RETI SINI.

SINT1:

6-22-24 2000-10-19

Figure 2-25. Interrupt Timing Chart (Example)

The interrupt return instruction [RETI] performs the following operations:

- ① Restores the contents of the program counter and the flags from the stack.

- Sets the EIF to "1" to provide the interrupt enable state again.

Note: When the time required for the interrupt service is longer than that foe the interrupt request, only the interrupt service program is executed without executing the main program.

In the interrupt processing, the program counter and flags are automatically saved or restored but the accumulator and other registers are not. If it is necessary to save or restore them, it must be performed by program as shown in the following example. To perform the multi-interrupt, the saving RAM area never be overlapped.

Example: To save and restore the accumulator and HL register pair.

XCH HL, GSAV1 ; RAM [GSAV1]  $\leftrightarrow$  HL XCH A, GSAV1 + 2 ; RAM [GSAV1 + 2]  $\leftrightarrow$  Acc

Note: The lower 2 bits of GSAV1 should be "0's".

#### (3) External Interrupt

When an external interrupt (INT1 or INT2) occurs, the interrupt latch is set at the falling edge of the corresponding pin-input (INT1 or INT2).

Because the external interrupt input is the hysteresis type, each of high and low level time requires 2 or more instruction cycles for a correct interrupt operation.

the INT1 interrupt cannot be disabled by the EIR, so that it is always accepted in the interrupt enable state (EIF = "1"). Therefore, INT1 is used for an interrupt with high priority such as an emergency interrupt. When R82 (INT1) pin is used for the I/O port, the INT1 interrupt occurs at the falling edge of the pin input, so that the interrupt return [RETI] instruction must be stored at the interrupt entry address to perform dummy interrupt processing.

The INT2 interrupt can be enable/disable by the EIR. Therefor, the INT2 interrupt occurs at the falling edge of the pin input when R80 (INT2) pin is used for the I/O port.

But bit 0 of the EIR is only kept at "0" not accepting the interrupt request.

6-22-25 2000-10-19

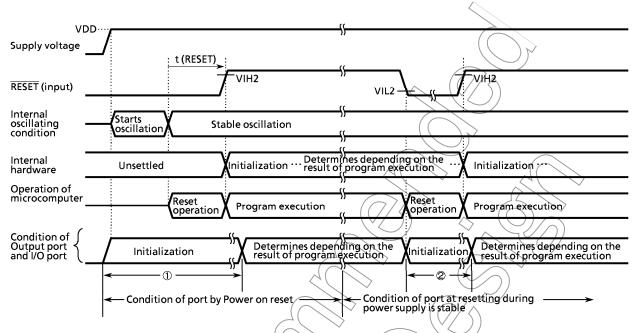

#### 2.9 Reset Function

When the RESET pin is held to the low level for three or more instruction cycles when the power voltage is within the operating voltage range and the oscillation is stable, reset is performed to initialize the internal states.

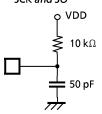

When the  $\overline{\text{RESET}}$  pin input goes high, the reset is cleared and program execution starts from address  $000_H$ . The  $\overline{\text{RESET}}$  pin is a hysteresis input with a pull-up resistor (220 k $\Omega$  typ.). Externally attaching a capacitor and a diode implement a simplified power-on-reset operation.

Figure 2-26. Simplified Power-On-Reset Circuit

Table 2-3. Initialization of Internal States by Reset Operation

| On-chip hardware                        | Initial value    | On-chip hardware Initial value                                  |        |  |  |

|-----------------------------------------|------------------|-----------------------------------------------------------------|--------|--|--|

| Program counter (PC)                    | 000 <sub>H</sub> |                                                                 | $\neg$ |  |  |

| Status flag (SF)                        | 1                | Output latch (I/O ports or Output ports) Refer to "INPUT/OUTPUT | г      |  |  |

| Interrupt enable master flip-flop (EIF) | 0 (              | Circuitry".                                                     |        |  |  |

| Interrupt enable register (EIR)         | 0 <sub>H</sub>   | Refer to the                                                    |        |  |  |

| Interrupt latch (IL)                    | "0"              | Command register description of each relative                   |        |  |  |

| Interval timer                          | "o"              | command regist                                                  | :er.   |  |  |

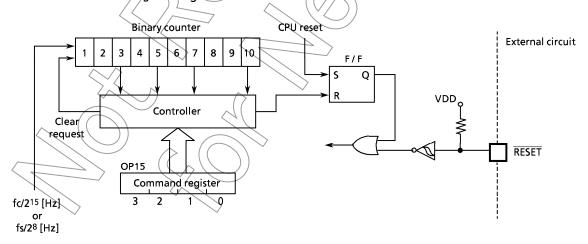

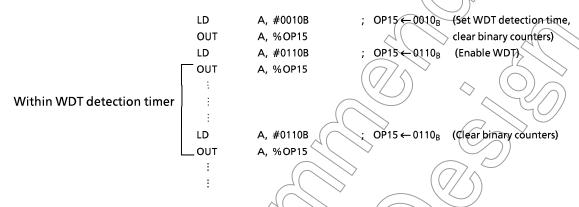

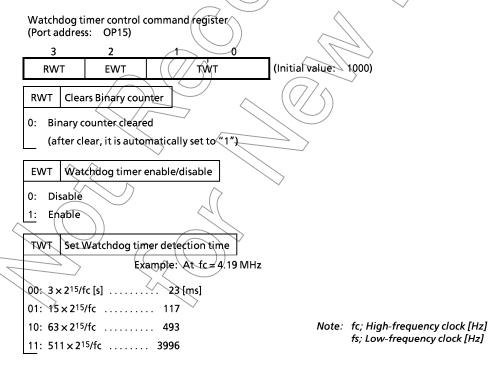

#### 2.9.1 Watchdog Timer (WDT)

The watchdog timer capability is provided to quickly detect the CPU malfunction such as endless looping caused by noises or the like, and restore the CPU to the normal state. The WDT is disabled during reset. The WDT consists of 10 binary counters, a flip-flop, and a controller. Source input clock of binary counters is fc/2<sup>15</sup>[Hz]. The flip-flop is set to "1" during reset, and cleared to "0" on the rising edge of the binary counter output. The WDT is controlled by the command register (OP15). The command register is initialized to "1000g" during reset.

Figure 2-27. Configuration of Watchdog Timer

To detect the CPU malfunction by the WDT:

- ① Set the WDT detection time, and clear the binary counters.

- ② Enable the WDT.

- ③ Clear the binary counters within WDT detection time that was set in ①. If a CPU malfunction occurs, preventing the binary counters from being cleared, the flip-flop is clearred to "0" on the rising edge of the binary counter output, making the malfunction detection signal active.

Example: To enable the with detection time of  $63 \times 2^{15}/f_c$  [s]

Note: It is necessary to clear the binary counter prior to enabling watchdog timer. Further, the Watchdog Timer should be disable by program during warm-up time from SLOW operating mode to Normal-2 operating mode.

(a) Command Register

6-22-27 2000-10-19

| T) 4 /T | Normal-1                  | Normal-2                 | Normal-2 operation                |           | fc = 4.194304 MHz, |

|---------|---------------------------|--------------------------|-----------------------------------|-----------|--------------------|

| TWT     | operation                 | $SLCK = 0 (fc / 2^7)$    | $CK = 0 (fc / 2^7)$ SLCK = 1 (fs) |           | fs = 32.768 kHz    |

| 00      | 3×:                       | 2 <sup>15</sup> / fc [s] | 3×2 <sup>8</sup> /1               | 23.4 [ms] |                    |

| 01      | 15 x                      | 2 <sup>15</sup> / fc     | 15 × 2 <sup>8</sup> /1            | (( 117)   |                    |

| 10      | 63 × 2 <sup>15</sup> / fc |                          | 63 × 2 <sup>8</sup> /fs           |           | 492                |

| 11      | 511×                      | 2 <sup>15</sup> / fc     | 511 × 2 <sup>8</sup> /1           | s (       | 3992               |

(b) WDT detection timer

Figure 2-28. Watchdog Timer Control Command Register

#### 3. Peripheral Hardware Function

#### 3.1 Ports

The data transfer with the external circuit and the command/status/data transfer with the internal circuit are performed by using the I/O instructions (13 kinds). There are 4 types of ports:

① I/O port ; Data transfer with external circuit

② Command register ; Control of internal circuit

Status register ; Reading the status signal from internal circuit

4 Data register ; Data transfer with internal circuit

These ports are assigned with port addresses (00<sub>H</sub> through 1F<sub>H</sub>). Each port is selected by specifying its port address in an I/O instruction. Table 3-2 lists the port address assignments and the I/O instructions that can access the ports.

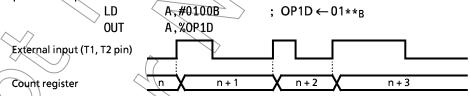

## 3.1.1 I/O Timing

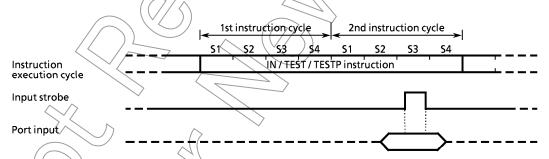

#### (1) Input timing

External data is read from an input port or an I/O port in the S3 state of the second instruction cycle during the input instruction (2-cycle instruction) execution. This timing cannot be recognized from the outside, so that the transient input such as chattering must be processed by program.

Figure 3-1. Input Timing

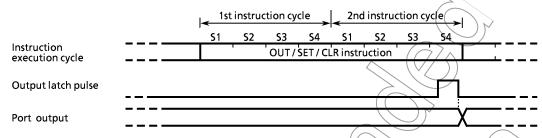

#### (2) Output timing

Data is output to an output port or an I/O port in the S4 state of the second instruction cycle during the output instruction (2-cycle instruction) execution.

Figure 3-2. Output Timing

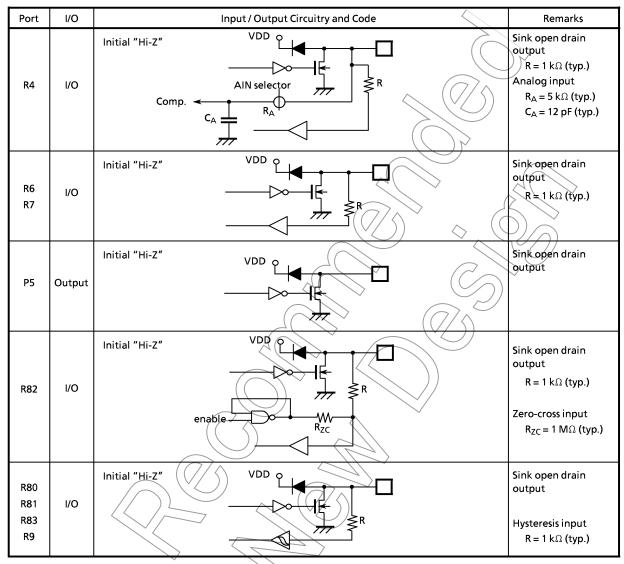

#### 3.1.2 I/O Ports

TMP47C222/422 have 7 I/O ports (22 pins) each as follows:

① R4 ; 4-bit input/output (shared with AD converter analog inputs)

② P5 ; 2-bit output

3 R6 ; 4-bit input/output

; 4-bit input/output (shared with zero-cross input, external interrupt

input and timer/counter input)

© R9 ; 3-bit input/output (shared with serial port)

⑦ KE ; 1-bit sense input (shared with hold request/release signal input)

Each output port contains a latch, which holds the output data. The input ports have no latch; therefore, it is desired to hold data externally until it is read or read twice or more before processing it.

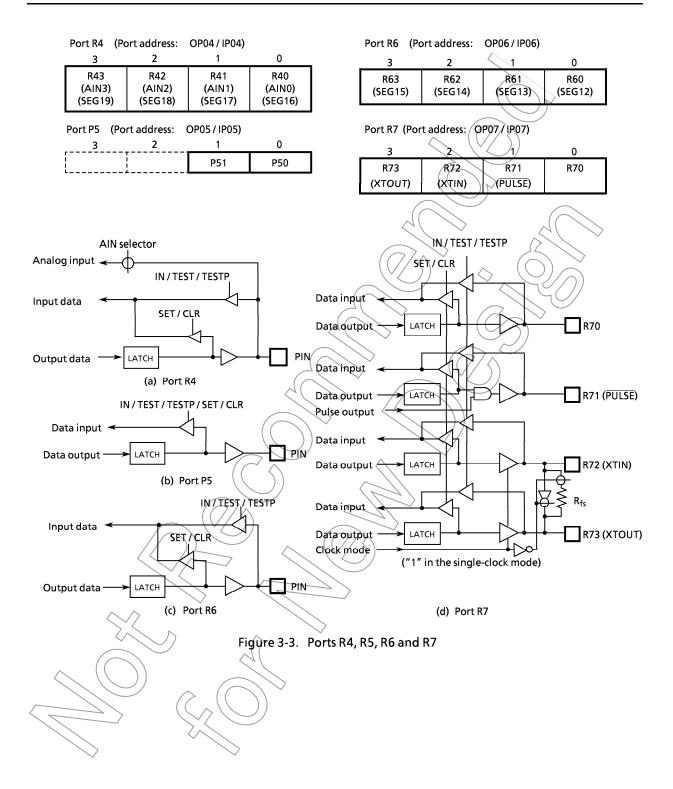

#### (1) Ports R4, R5, R6 and R7

5 R8

These ports are 4-bit I/O ports with a latch (Port R5 is 2-bit). When used as an input port, the latch must be set to "1". The latch is initialized to "1" during reset.

These 4 ports (14 pins) can be set, cleared, and tested for each bit as specified by L register indirect addressing bit manipulation instructions ([SET @L], [CLR @L], and [TEST @L]). Table 3-1 lists the pins (I/O ports) that correspond to the contents of L register.

Example: To clear R43 output as specified by the L register indirect addrressing bit manipulation instruction.

LD L, #0011B ; Sets R43 pin address to L register

Table 3-1. Relationship between L register contents and I/O port bits

|   | $\overline{}$ | $\overline{}$ |       |      |       |           | _              | _   | _     | _   |        |

|---|---------------|---------------|-------|------|-------|-----------|----------------|-----|-------|-----|--------|

|   | L             | . reg         | giste | er 🔪 | PIN ( | $\langle$ | L              | (ré | giste | er\ | PIN    |

| \ | d<br>W        | 2             | 1     | 0    |       |           | <b>\bar{2}</b> | 2   | }     | 9   | ) 1110 |

|   | 0             | Q             | Q     | 0    | R40   | 4         | /0             | 1   | 9     | 0   | P50    |

|   | 0             | 0             | o     | 1    | R41   |           | 0              | 1   | 0     | 1   | P51    |

|   | 0             | 0             | 1     | 0    | R42   |           |                |     |       |     |        |

|   | 0             | 0             | 1     | 1    | R43   |           |                |     |       |     |        |

| L | . reg | giste | er | PIN   |

|---|-------|-------|----|-------|

| 3 | 2     | 1     | 0  | 1 110 |

| 1 | 0     | 0     | 0  | R60   |

| 1 | 0     | 0     | 1  | R61   |

| 1 | 0     | 1     | 0  | R62   |

| 1 | 0     | 1     | 1  | R63   |

| L | . re | giste | er | PIN  |  |  |  |  |

|---|------|-------|----|------|--|--|--|--|

| 3 | 2    | 1     | 0  | FIIN |  |  |  |  |

| 1 | 1    | 0     | 0  | R70  |  |  |  |  |

| 1 | 1    | 0     | 1  | R71  |  |  |  |  |

| 1 | 1    | 1     | 0  | R72  |  |  |  |  |

| 1 | 1    | 1     | 1  | R73  |  |  |  |  |

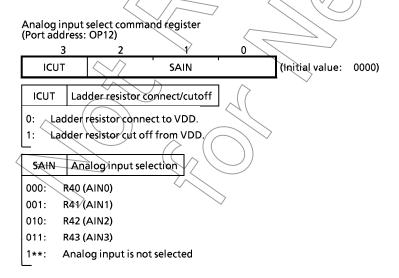

#### (a) Port R4 (R43 to R40)

Port R4 is 4-bit I/O port with latch shared by the analog inputs for AD converter and LCD segment output. When used as an analog inputs or segment output, the latch should be set to "1". If other port is used as an output, be careful not to execute the output instruction for any port during AD conversion in order to keep accuracy of conversion. The latch is initialized to "1" and analog input is selected R40 (AINO) pin during reset.

#### (b) Port P5 (P51, P50)

Port P5 is 2-bit output port with a latch. When an input instruction is executed, the latch data is read. The latch is initialized to "1" during reset. Port P5 is only QFP package type.

## (c) Port R6 (R63 to R60)

Port R6 is 4-bit I/O port with latch shared by the LCD segment output. When used as segment output, the latch should be set to "1". The latch is initialized to "1" during reset.

#### (d) Port R7 (R73 to R70)

Port R7 is shared by the low-frequency resonator connection pins (XTIN, XTOUT) and the pulse output pin (PULSE). For the dual-clock mode operation, the low-frequency resonator (32.768 kHz) is connected to R72 (XTIN) and R73 (XTOUT) pins. For the single-clock mode operation, R72 and R73 pins are used for the ordinary I/O ports. When the pulse output is used, R71 (PULSE) becomes the pulse output pin. The pulse output is the logical AND output with the port R71 output latch. To use the R71 pin for an ordinary I/O port, the pulse output must be disabled.

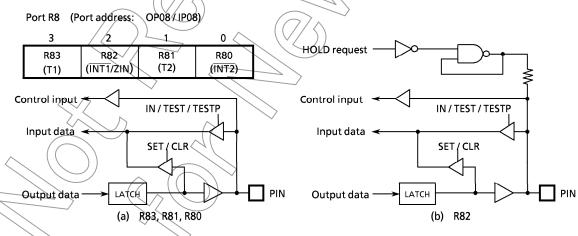

## (2) Port R8 (R83 to R80)

Port R8 is a 4-bit I/O port with a latch. When used as an input port, the latch must be set to "1". The latch is initialized to "1" during reset.

Port R8 is shared with the external interrupt input pin and the timer/counter input pin. To use this port for one of these functional pins, the latch should be set to "1". To use it for an ordinary I/O port, the acceptance of external interrupt should be disabled or the event counter/pulse width measurement modes of the timer/counter should be disabled.

Figure 3-4. Port R8

Note: When R82 (INT1) pin is used for an I/O port, external interrupt 1 occurs upon detection of the falling edge of pin input, and if the interrupt enable master flip-flop is enabled, the interrupt request is always accepted. So that a dummy interrupt processing must be performed (only the interrupt return instruction [RETI] is executed).

With R80 (INT2) pin, external interrupt 2 occurs like R82 in but bit 0 of the interrupt enable register (EIR<sub>0</sub>) is only kept at "0", not accepting the interrupt request.

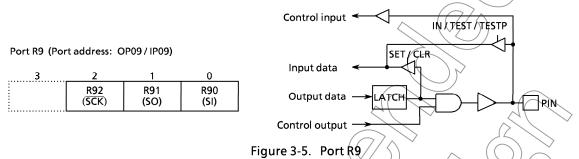

#### (3) Port R9 (R92 to R90)

Port R9 is a 3-bit I/O port with a latch. When used as an input, the latch must be set to "1". The latch is initialized to "1" during reset. Port R9 is shared with the serial port. To use port R9 for the serial port, the latch should be set to "1".

Although R93 pin does not exist actualy. However, other instructions can be used, in which an undefined value is read upon execution of an input instruction.

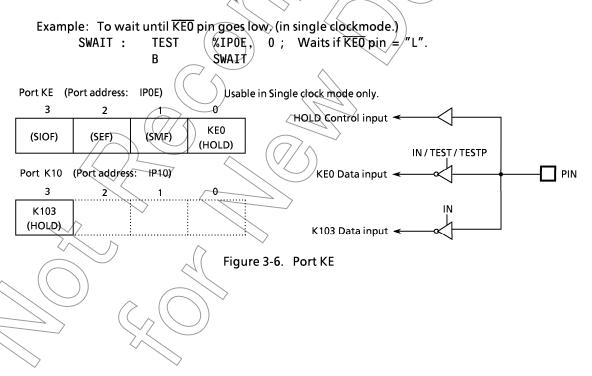

## (4) Port KE (KEO)

Port KE is a 1-bit sense input port shared by the hold request/release signal input pm (HOLD). This input port is assigned to the least significant bit of port address IP0E or the most significant bit of port address IP10 and both input data is processed as the data with inverted polarity. For example, if an input instruction is executed with the pin on the high level, "0" is read. Note that KEO input cannot be used in the dual-clock mode because KEO input monitors the states of SLOW operation mode. To monitor the states of HOLD pin K103 input.

6-22-32 2000-10-19

Note 1: "——" means the reserved state. Unavailable for the user programs. Note 2: Do not use the set and clear instructions with bit 3 of the OP09.

|                                                                    |                          | i                                               |                             |                |                                  |                                |             |        |                                                          | T -                         |                           |                    |                        |                      |                |                                                          | $\langle \cdot \rangle$ | _                                               |                            | _                          |

|--------------------------------------------------------------------|--------------------------|-------------------------------------------------|-----------------------------|----------------|----------------------------------|--------------------------------|-------------|--------|----------------------------------------------------------|-----------------------------|---------------------------|--------------------|------------------------|----------------------|----------------|----------------------------------------------------------|-------------------------|-------------------------------------------------|----------------------------|----------------------------|

|                                                                    |                          | SET @L<br>CLR @L<br>TEST @L                     | 1                           | 100            | 00                               | i I                            | £ 1         |        | I                                                        |                             | ł                         |                    | !                      | I                    | ı              | 1 1                                                      |                         |                                                 | $\nearrow$                 |                            |

|                                                                    |                          | TEST %p, b                                      |                             | 100            | 00                               | 00                             | l .         | }      | 0                                                        |                             | i                         | 1 !                | , <                    | >                    | /_             |                                                          | 7/                      |                                                 |                            |                            |

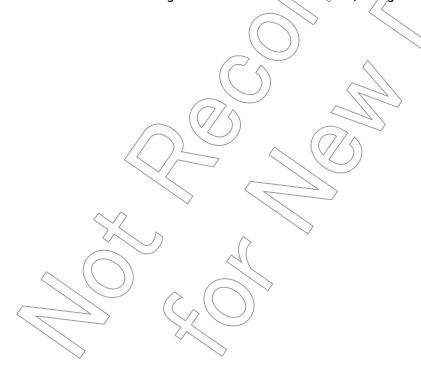

|                                                                    | ion                      | SET %p, b 1<br>CLR %p, b 1                      |                             | 00             | 000                              | 00                             |             |        | + 1                                                      |                             | į                         | 7                  |                        |                      | //-/>          |                                                          | 7                       | ı                                               | 1                          |                            |