# Am25LS2568/Am25LS2569

Four-Bit Up/Down Counters with Three-State Outputs

#### DISTINCTIVE CHARACTERISTICS

- 4-bit synchronous counter, synchronously programmable

- Both synchronous and asynchronous clear inputs

- Three-state counter outputs interface directly with bus organized systems

- Internal look-ahead carry logic and two count enable lines for high speed cascaded operation

- · Ripple carry output for cascading

- Clock carry output for convenient modulo configuration

- Fully buffered outputs

- Second sourced as the 54LS/74LS568 and LS569

- Advanced Low-Power Schottky technology

#### **GENERAL DESCRIPTION**

The Am25LS2568 and Am25LS2569 are programmable up/down BCD and Binary counters respectively with three-state outputs for bus organized systems. All functions except output enable (OE) and asynchronous clear (ACLR) occur on the positive edge of the clock input (CP).

With the LOAD input LOW, the outputs will be programmed by the parallel data inputs (A, B, C, D) on the next clock edge. Counting is enabled only when CEP and CET are LOW and LOAD is HIGH. The up-down input (U/D) controls the direction of count, HIGH counts up and LOW counts down. Internal look-ahead carry logic and an active LOW ripple carry output (RCO) allows for high-speed counting

and cascading. During up-count, the RCO is LOW at binary 9 for the LS2568 (binary 15 for the LS2569) and upon down-count, it is LOW at binary 0. Normal cascaded operations require only the RCO to be connected to the succeeding block at CET. When counting, the clocked carry output (CCO) provides a HIGH-LOW-HIGH pulse for a duration equal to the LOW time of the clock pulse and only when RCO is LOW. Two active LOW reset lines are available, synchronous clear (SCLR) and a master reset asynchronous clear (ACLR). The output control (OE) input forces the counter output into the high-impedance state when HIGH and when LOW, the counter outputs are enabled.

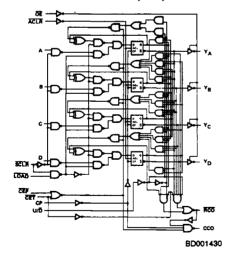

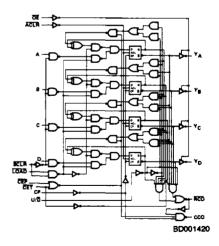

#### **BLOCK DIAGRAM**

#### Am25LS2568 (BCD)

#### Am25LS2569 (BINARY)

036228

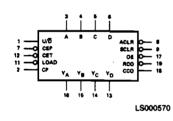

# CONNECTION DIAGRAM TOD View

L-20-1

Note: Pin 1 is marked for orientation

# LOGIC SYMBOL

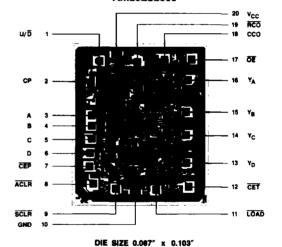

METALLIZATION AND PAD LAYOUT

Am25LS2568

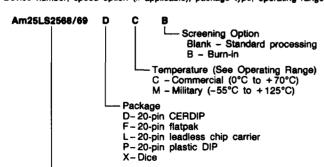

#### ORDERING INFORMATION

AMD products are available in several packages and operating ranges. The order number is formed by a combination of the following: Device number, speed option (if applicable), package type, operating range and screening option (if desired).

Device type

**BCD** and Binary Counters

| Valid Con                 | nbinations                                                         |

|---------------------------|--------------------------------------------------------------------|

| Am25LS2568/<br>Am25LS2569 | DC, DCB, DM,<br>DMB<br>FM, FMB<br>LC, LM, LMB<br>PC, PCB<br>XC, XM |

#### **Valid Combinations**

Consult the AMD sales office in your area to determine if a device is currently available in the combination you wish.

#### PIN DESCRIPTION

| Pin No.          | Name              | 1/0 | Description                                                                                                                   |

|------------------|-------------------|-----|-------------------------------------------------------------------------------------------------------------------------------|

| 3, 4, 5, 6       | A, B, C, D        | ı   | The four programmable data inputs.                                                                                            |

| 7                | CEP               | ı   | Count Enable Parallel. Can be used to enable and inhibit counting in high speed cascaded operation. CEP must be LOW to count. |

| 12               | CET               | ı   | Count Enable Trickle. Enables the ripple carry output for cascaded operation. Must be LOW to count.                           |

| 2                | CP                | ı   | Clock Pulse. All synchronous functions occur on the LOW-to-HIGH transition of the clock.                                      |

| 11               | LOAD              | 1   | Enables parallel load of counter outputs from data inputs on the next clock edge. Must be HIGH to count.                      |

| 1                | U/D               | ì   | Up/Down Count Control. HIGH counts up and LOW counts down.                                                                    |

| 8                | ACLR              | ı   | Asynchronous Clear. Master reset of counters to zero when ACLR is LOW, independent of the clock.                              |

| 9                | SCLA              | ı   | Synchronous clear of counters to zero on the next clock edge when SCLR is LOW.                                                |

| 17               | ŌĒ                | - 1 | A HIGH on the output control sets the four counter outputs in the high-impedance, and a LOW enables the output.               |

| 16, 15<br>14, 13 | YA. YB.<br>YC. YD | 0   | The four counter outputs.                                                                                                     |

| 19               | HCO               | 0   | Ripple Carry Output. Output will be LOW on the maximum count on up-count. Upon down-count, RCO is LOW at 0000.                |

| 18               | cco               | 0   | Clock Carry Output. While counting and RCO is LOW, CCO will follow the clock HIGH-LOW-HIGH transition.                        |

## Am25LS2568/2569 **FUNCTION TABLE**

|                   | INPUTS |             |             |             |                |               |       |             |                |                |                | OUTPUTS     |                |                  |                            |                |                      |                     |

|-------------------|--------|-------------|-------------|-------------|----------------|---------------|-------|-------------|----------------|----------------|----------------|-------------|----------------|------------------|----------------------------|----------------|----------------------|---------------------|

| MODE              | LOAD   | CEP         | CET         | U/Ď         | ASYNC<br>CLEAR | SYNC<br>CLEAR | ŎĔ(1) | Do          | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | СР          | Q <sub>0</sub> | Q <sub>1</sub>   | Q <sub>2</sub>             | Q <sub>3</sub> | RC                   | CLOCK               |

| Clear<br>(ASYNC)  | X<br>X | X           | ×           | 1 0         | 0              | X             | 0     | X           | X              | ×              | X<br>X         | X           | 0              | 0                | 0                          | 0              | 1 0                  | 1 (2)               |

| Clear<br>(SYNC)   | X<br>X | X           | X           | 1 0         | 1              | 0             | 0     | X           | X              | X<br>X         | X              | †<br>†      | 0              | 0                | 0                          | 0              | 1 0                  | 1 (2)               |

| Load              | 0 0 0  | X<br>X<br>X | 1<br>0<br>0 | X<br>0<br>1 | 1<br>1<br>1    | 1<br>1<br>1   | 0 0   | X<br>0<br>1 | X<br>0<br>1    | X<br>0<br>1    | X<br>0<br>1(3) | †<br>†      | 0              | Q <sub>n</sub> : | - D <sub>n</sub><br>0<br>1 | 0<br>1(3)      | 1<br>0<br>0          | 1<br>1 (2)<br>1 (2) |

| Count Up          | 1      | 0           | 0           | 1           | 1              | 1             | 0     | X           | х              | Х              | х              | 1           |                | Qn               | + 1                        |                | (4)                  | (5)                 |

| Count Down        | 1      | 0           | 0           | 0           | 1              | 1             | 0     | X           | х              | Х              | Х              | 1           |                | Qn               |                            |                | (6)                  | (5)                 |

| Inhibit           | 1 1    | 0<br>1<br>1 | 1<br>0<br>1 | X<br>X<br>X | 1<br>1<br>1    | 1<br>1<br>1   | 0     | X<br>X<br>X | X<br>X<br>X    | X<br>X<br>X    | X<br>X<br>X    | †<br>†<br>† | l              | N.               | .C.<br>.C.<br>.C.          |                | N.C.<br>N.C.<br>N.C. | 1 1 1               |

| Output<br>Disable | ×      | ×           | х           | ×           | х              | х             | 1     | х           | x              | х -            | x              | ×           | z              | z                | z                          | z              | N.C.                 | N.C.                |

t = CLOCK LOW-to-HIGH transition X = Don't Care

Dn = Do thru D3 input level prior to clock transition

$Q_{n+1}$  = Next higher count in binary sequence  $Q_{n-1}$  = Next lower count in binary sequence N.C. = No change

- Notes: 1. Register performs all correct logic for any state of  $\overline{OE}$ , but  $\overline{OE} = 0$  to view outputs.

2. Follows CLOCK if  $\overline{CET} = \overline{CEP} = 0$ , otherwise remains HIGH.

3. 1001 for LS88.

4. LOW for one full CLOCK cycle when maximum count is reached, otherwise remains HIGH.

5. Follows CLOCK when RC = 0.

6. LOW for one full CLOCK cycle when minimum count is reached, otherwise remains HIGH.

## **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature                           |

|-----------------------------------------------|

| Continuous0.5V to +7.0V                       |

| DC Voltage Applied to Outputs For             |

| High Output State0.5V to +V <sub>CC</sub> max |

| DC input Voltage0.5V to +7.0V                 |

| DC Output Current, Into Outputs               |

| DC Input Current30mA to +5.0mA                |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

## **OPERATING RANGES**

| Commercial (C) Devices Temperature                                     | 0°C to ±70°C               |

|------------------------------------------------------------------------|----------------------------|

| Supply Voltage                                                         |                            |

| Military (M) Devices                                                   |                            |

| Temperature                                                            | 55°C to +125°C             |

| Supply Voltage                                                         | + 4.5V to + 5.5V           |

| Operating ranges define those limit ality of the device is guaranteed. | s over which the function- |

# DC CHARACTERISTICS over operating range unless otherwise specified

| Parameters      | Description                           | Test Conditions (Note 2)                         |                          |                                                                  |           |       | Min | Typ<br>(Note 1) | Max   | Units      |

|-----------------|---------------------------------------|--------------------------------------------------|--------------------------|------------------------------------------------------------------|-----------|-------|-----|-----------------|-------|------------|

|                 |                                       | 1                                                |                          | MIL, I <sub>OH</sub> = -1.0mA<br>COM'L, I <sub>OH</sub> = -2.6mA |           |       | 2.4 | 3.4             |       |            |

|                 |                                       | V <sub>CC</sub> = MIN                            | Yi                       |                                                                  |           |       | 2.4 | 3.2             |       |            |

| VOH             | Output HIGH Voltage                   | VIN = VIH                                        | RCO.                     |                                                                  |           | MIL   | 2.5 | 3.4             |       | Volts      |

|                 | !                                     | or V <sub>IL</sub>                               | cco                      | IOH = -44                                                        | 0μΑ       | COM'L | 2.7 | 3.4             |       |            |

|                 |                                       | ACC = MIM ===                                    |                          | I <sub>OL</sub> = 4.0mA                                          |           |       |     |                 | 0.4   |            |

| VOL             | Output LOW Voltage                    | VIN - VIH OF                                     | I <sub>OL</sub> = 8.0n   | nA                                                               |           |       |     | 0.45            | Volts |            |

| V <sub>IH</sub> | Input HIGH Level                      | Guaranteed in voltage for all                    |                          | cal HIGH                                                         |           |       | 2.0 |                 |       | Volts      |

|                 |                                       | Guaranteed input logical LOW                     |                          |                                                                  | MIL       |       |     |                 | 0.7   |            |

| VIL             | Input LOW Level                       | voltage for all                                  | ge for all inputs. COM'L |                                                                  |           |       | C   | 8.0             | Volts |            |

| Vį              | Input Clamp Voltage                   | V <sub>CC</sub> = MIN, I <sub>IN</sub> = -18mA   |                          |                                                                  |           |       |     |                 | -1.5  | Volts      |

|                 |                                       | 1                                                |                          | ACLR, OE, U/D, LOAD                                              |           |       |     |                 | -0.3  |            |

| lıL             | Input LOW Current                     | V <sub>CC</sub> = MAX,<br>V <sub>IN</sub> = 0.4V |                          | A, B, C, D, CP, CEP                                              |           |       |     |                 | -0.4  | mA         |

|                 |                                       | VIN - 0.44                                       | 1-0.44                   |                                                                  | CET, SCLR |       |     |                 | -0.65 |            |

| liH             | Input HIGH Current                    | V <sub>CC</sub> = MAX, V                         | IN = 2.7                 | ٧                                                                |           |       |     |                 | 20    | μΑ         |

| lı              | Input HIGH Current                    | V <sub>CC</sub> = MAX, V                         | IN = 7.0                 | ٧                                                                |           |       |     |                 | 0.1   | mA         |

|                 | Off-State (High-Impedance)            |                                                  |                          | V <sub>O</sub> = 0.4V                                            |           |       |     |                 | -20   |            |

| loz             | Output Current                        | V <sub>CC</sub> = MAX                            |                          | V <sub>O</sub> = 2.4V                                            |           |       |     |                 | 20    | μ <b>Α</b> |

| Isc             | Output Short Circuit Current (Note 3) | V <sub>CC</sub> = MAX                            |                          |                                                                  |           | - 15  |     | -85             | mA    |            |

| lcc             | Power Supply Current<br>(Note 4)      | V <sub>CC</sub> = MAX                            |                          | <u> </u>                                                         |           |       |     | 28              | 43    | mA         |

- Notes: 1. Typical limits are at V<sub>CC</sub> = 5.0V, 25°C ambient and maximum loading.

2. For conditions shown as MIN or MAX, use the appropriate value specified under Operating Ranges for the applicable device type.

3. Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

4. OE = HIGH, all other inputs = GND, all outputs open.

# SWITCHING CHARACTERISTICS (T<sub>A</sub> = +25°C, V<sub>CC</sub> = 5.0V)

| Parameters       | Description         |                   | Test Conditions                                 | Min | Тур  | Max  | Units |

|------------------|---------------------|-------------------|-------------------------------------------------|-----|------|------|-------|

| tpLH             | Clock to Any Q; [   |                   |                                                 |     | 12   | 18   |       |

| tPHL             | Clock to Any Q; I   | LOAG = LOW        |                                                 |     | 14   | 21   | ns ns |

| tpLH             | Clock to Any Q; I   | and - UICU        | ]                                               |     | 12   | 18   |       |

| tpHL             | Clock to Arry C; L  | .oau = niGn       |                                                 |     | 14   | 21   | ns    |

| t <sub>PLH</sub> | CET to ACO          |                   |                                                 |     | 11   | 16   | ns    |

| <sup>1</sup> PHL | 7021 10 1100        |                   |                                                 |     | 6    | 10   | lis . |

| t <sub>PLH</sub> | U/D to FICO         |                   |                                                 |     | 15   | 23   | ns    |

| <sup>†</sup> PHL | 070 to 1100         |                   |                                                 |     | 13   | 20   | ] 115 |

| <sup>t</sup> PLH | Clock to FICO       |                   |                                                 |     | 24   | 35   | ns    |

| t <sub>PHL</sub> | CIOCK TO HOC        |                   | ] [                                             |     | 18   | 26   | 115   |

| tplH             | Clock to CCO        |                   |                                                 |     | 10   | 15   | ns    |

| tphl.            | GIOCK TO GOO        |                   |                                                 |     | 10   | 15   | l is  |

| t <sub>PLH</sub> | CET or CEP to CCO   |                   | C <sub>L</sub> = 15pF<br>R <sub>L</sub> = 2.0kΩ |     | 10   | 15   | ns    |

| tPHL .           |                     |                   |                                                 |     | 17   | 25   | 115   |

| t <sub>PLH</sub> | ACLR to Any Q       |                   |                                                 |     | N.A. | N.A. | ns    |

| t <sub>PHL</sub> |                     |                   |                                                 |     | 17   | 26   | ''5   |

|                  |                     | A. B, C, D        |                                                 | 22  |      |      |       |

|                  |                     | SCLR              |                                                 | 20  |      |      | ]     |

| ts               | Set-up              | Load              |                                                 | 30  |      |      | ns    |

|                  |                     | U/D               |                                                 | 30  |      |      |       |

|                  | <u> </u>            | CET, CEP          | ] [                                             | 25  |      |      |       |

| te               | SCLR Recovery (i    | nactive) to Clock |                                                 | 30  |      |      | ns    |

| th               | Data Hold           |                   | ] [                                             | 0   |      |      | ns    |

| fmax             | Maximum Clock F     | requency (Note 1) | ] [                                             | 25  | 40   |      | MHz   |

| t <sub>pw</sub>  | Clock Pulse Width   | 1                 | ] [                                             | 25  |      |      | ns    |

| tеzн             | ŌĒ to Any Q; Enable |                   | ] [                                             |     |      | 11   | ns    |

| tpZL             | OE IO AIII) Q, EIN  |                   |                                                 |     |      | 19   | ] ''s |

| tpHZ             | OE to Any Q; Dis    |                   | C <sub>L</sub> = 5.0pF                          |     |      | 18   | - ns  |

| <sup>t</sup> PLZ | TOE TO Arry CI, Dis | enie              | R <sub>L</sub> = 2.0kΩ                          |     |      | 24   | 1 18  |

Note 1. Per industry convention, f<sub>max</sub> is the worst case value of the maximum device operating frequency with no constraints on t<sub>r</sub>, t<sub>fi</sub>, pulse width or duty cycle.

# SWITCHING CHARACTERISTICS over operating range unless otherwise specified\*

|                  |                                            |              |                                                  | COMM    | ERCIAL | MILI | l     |     |  |

|------------------|--------------------------------------------|--------------|--------------------------------------------------|---------|--------|------|-------|-----|--|

|                  |                                            |              |                                                  | Am:     | 25LS   | Am   | ĺ     |     |  |

| Parameters       | Desc                                       | ription      | Test Conditions                                  | Min Max |        | Min  | Units |     |  |

| †PLH             |                                            |              |                                                  |         | 22     |      | 24    |     |  |

| t <sub>PHL</sub> | Clock to Any Q; Load                       | - LOW        |                                                  |         | 29     |      | 35    | ns  |  |

| tpLH             |                                            |              |                                                  |         | 22     |      | 24    |     |  |

| t <sub>PHL</sub> | Clock to Any Q; Load                       | = HIGH       |                                                  |         | 29     |      | 35    | ns  |  |

| t <sub>PLH</sub> | ABB . BAA                                  | -            |                                                  |         | 18     |      | 19    |     |  |

| t <sub>PHL</sub> | CET to RCO                                 |              |                                                  |         | 17     |      | 21    | ns  |  |

| t <sub>PLH</sub> | 500                                        |              |                                                  |         | 26     |      | 28    |     |  |

| tpHL             | U/D to RCO                                 |              |                                                  |         | 26     |      | 30    | ns  |  |

| tpLH             | Clock to PCO                               |              |                                                  |         | 39     |      | 40    |     |  |

| t <sub>PHL</sub> |                                            |              |                                                  |         | 34     |      | 39    | ns  |  |

| tPLH .           | Clock to CCO                               |              |                                                  |         | 17     |      | 18    |     |  |

| t <sub>PHL</sub> | Clock to CCO                               |              |                                                  |         | 22     |      | 27    | ns  |  |

| tPLH .           | CET or CEP to CCO                          |              | C <sub>L</sub> = 50pF<br>R <sub>L</sub> = 2.0KΩ  |         | 16     |      | 17    | ns  |  |

| t <sub>PHL</sub> |                                            |              | R <sub>L</sub> = 2.0KΩ                           |         | 36     |      | 45    |     |  |

| tpLH             |                                            |              |                                                  |         | N.A.   |      | N.A.  |     |  |

| 1 <sub>PHL</sub> | ACLFI to Any Q                             |              |                                                  |         | 37     |      | 45    | ns  |  |

|                  |                                            | A, B, C, D   |                                                  | 29      |        | 35   |       | ns  |  |

|                  |                                            | SCLA         |                                                  | 25      |        | 30   |       |     |  |

| t <sub>s</sub>   | Set-up                                     | Load         |                                                  | 38      |        | 45   |       |     |  |

| _                |                                            | U/D          |                                                  | 38      |        | 45   |       |     |  |

|                  |                                            | CET, CEP     |                                                  | 33      |        | 40   |       | 1   |  |

| L <sub>B</sub>   | SCLR Recovery (inactiv                     | ve) to Clock |                                                  | 39      |        | 50   |       | ns  |  |

| l <sub>h</sub>   | Data Hold                                  |              |                                                  | 0       |        | 5    |       | ns  |  |

| fmex             | Data Hold Maximum Clock Frequency (Note 1) |              |                                                  | 20      |        | 18   |       | MHz |  |

| tpw              | Clock Pulse Width                          |              |                                                  | 31      |        | 37   |       | ns  |  |

| tzH              |                                            |              |                                                  |         | 16     |      | 20    | ]   |  |

| tZL              | OE to Any Q; Enable                        |              |                                                  |         | 26     |      | 34    | ns  |  |

| Чнz              |                                            |              | C <sub>L</sub> = 5.0pF<br>R <sub>L</sub> = 2.0KΩ |         | 20     |      | 22    |     |  |

| 1LZ              | OE to Any Q; Disable                       |              | R_ = 2.0KΩ                                       |         | 30     |      | 36    | ns  |  |

\*AC performance over the operating temperature range is guaranteed by testing defined in Group A, Subgroup 9. N.A. not applicable.

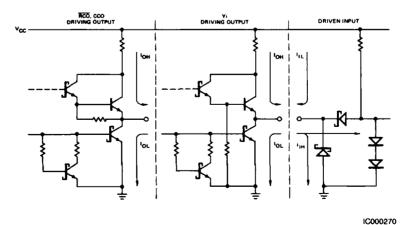

# Am25LS2568/2569 LOW-POWER SCHOTTKY INPUT/OUTPUT CURRENT INTERFACE CONDITIONS

Note: Actual current flow direction shown.