# 12A Analog Pico DLynx<sup>™</sup>: Non-Isolated DC-DC Power Modules 3Vdc −14.4Vdc input; 0.6Vdc to 5.5Vdc output; 12A Output Current

## **RoHS Compliant**

# **Applications**

- Distributed power architectures

- Intermediate bus voltage applications

- Telecommunications equipment

- Servers and storage applications

- Networking equipment

- Industrial equipment

#### **Features**

- Compliant to RoHS EU Directive 2002/95/EC (Z versions)

- Compatible in a Pb-free or SnPb reflow environment (Z versions)

- DOSA based

- Wide Input voltage range (3Vdc-14.4Vdc)

- Output voltage programmable from 0.6Vdc to 5.5Vdc via external resistor

- Tunable Loop<sup>™</sup> to optimize dynamic output voltage response

- Power Good signal

- Fixed switching frequency

- Output overcurrent protection (non-latching)

- Overtemperature protection

- Remote On/Off

- Ability to sink and source current

- Cost efficient open frame design

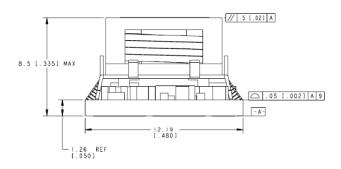

- Small size: 12.2 mm x 12.2 mm x 8.5 mm (0.48 in x 0.48 in x 0.335 in)

- Wide operating temperature range [-40°C to 85°C]

- UL\* 60950-1Recognized, CSA<sup>†</sup> C22.2 No. 60950-1-03 Certified, and VDE<sup>‡</sup> 0805:2001-12 (EN60950-1) Licensed

- ISO\*\* 9001 and ISO 14001 certified manufacturing facilities

# **Description**

The 12A Analog Pico DLynx<sup>TM</sup> power modules are non-isolated dc-dc converters that can deliver up to 12A of output current. These modules operate over a wide range of input voltage (V<sub>IN</sub> = 3Vdc-14.4Vdc) and provide a precisely regulated output voltage from 0.6Vdc to 5.5Vdc, programmable via an external resistor. Features include remote On/Off, adjustable output voltage, over current and over temperature protection. The Tunable Loop<sup>TM</sup> feature allows the user to optimize the dynamic response of the converter to match the load with reduced amount of output capacitance leading to savings on cost and PWB area.

Document No: DS10-008 ver. 1.12 PDF name: PVX012A0X.pdf

<sup>\*</sup> UL is a registered trademark of Underwriters Laboratories, Inc.

CSA is a registered trademark of Canadian Standards Association.

VDE is a trademark of Verband Deutscher Elektrotechniker e.V.

<sup>\*\*</sup> ISO is a registered trademark of the International Organization of Standards

# **Absolute Maximum Ratings**

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only, functional operation of the device is not implied at these or any other conditions in excess of those given in the operations sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect the device reliability.

| Parameter                            | Device     | Symbol           | Min  | Max | Unit |

|--------------------------------------|------------|------------------|------|-----|------|

| Input Voltage                        | All        | V <sub>IN</sub>  | -0.3 | 15  | Vdc  |

| Continuous                           |            |                  |      |     |      |

| Operating Ambient Temperature        | All        | T <sub>A</sub>   | -40  | 85  | °C   |

| (see Thermal Considerations section) | -D version | T <sub>A</sub>   | -40  | 105 | °C   |

| Storage Temperature                  | All        | T <sub>stg</sub> | -55  | 125 | °C   |

# **Electrical Specifications**

Unless otherwise indicated, specifications apply over all operating input voltage, resistive load, and temperature conditions.

| Parameter                                                                                                                                                       | Device                       | Symbol                   | Min | Тур  | Max  | Unit             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------------|-----|------|------|------------------|

| Operating Input Voltage                                                                                                                                         | All                          | V <sub>IN</sub>          | 3   | _    | 14.4 | Vdc              |

| Maximum Input Current (V <sub>IN</sub> =3V to 14V, I <sub>O</sub> =I <sub>O, max</sub> )                                                                        | All                          | I <sub>IN,max</sub>      |     |      | 12   | Adc              |

| Input No Load Current                                                                                                                                           | V <sub>O,set</sub> = 0.6 Vdc | I <sub>IN,No load</sub>  |     | 45   |      | mA               |

| $(V_{IN} = 12.0 \text{Vdc}, I_{O} = 0, \text{module enabled})$                                                                                                  | V <sub>O,set</sub> = 5Vdc    | I <sub>IN,No load</sub>  |     | 75   |      | mA               |

| Input Stand-by Current (V <sub>IN</sub> = 12.0Vdc, module disabled)                                                                                             | All                          | I <sub>IN,stand-by</sub> |     | 0.65 |      | mA               |

| Inrush Transient                                                                                                                                                | All                          | l <sup>2</sup> t         |     |      | 1    | A <sup>2</sup> s |

| Input Reflected Ripple Current, peak-to-peak (5Hz to 20MHz, $1\mu$ H source impedance; $V_{IN}$ =0 to $14V_{.}$ $I_{O}$ = $I_{Omax}$ ; See Test Configurations) | All                          |                          |     | 40   |      | mAp-p            |

| Input Ripple Rejection (120Hz)                                                                                                                                  | All                          |                          |     | -60  |      | dB               |

# **Electrical Specifications** (continued)

| Parameter                                                                                                                                                        | Device                       | Symbol              | Min  | Тур  | Max  | Unit                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------|------|------|------|-----------------------|

| Output Voltage Set-point (with 0.1% tolerance for external resistor used to set output voltage)                                                                  | All                          | V <sub>O, set</sub> | -1.0 |      | +1.0 | % V <sub>O, set</sub> |

| Output Voltage (Over all operating input voltage, resistive load, and temperature conditions until end of life)                                                  | All                          | $V_{O,set}$         | -3.0 | _    | +3.0 | % V <sub>O, set</sub> |

| Adjustment Range (selected by an external resistor) (Some output voltages may not be possible depending on the input voltage – see Feature Descriptions Section) | All                          | Vo                  | 0.6  |      | 5.5  | Vdc                   |

| Remote Sense Range                                                                                                                                               | All                          |                     |      |      | 0.5  | Vdc                   |

| Output Regulation (for V <sub>O</sub> ≥ 2.5Vdc)                                                                                                                  |                              |                     |      |      |      |                       |

| Line $(V_{IN}=V_{IN, min} \text{ to } V_{IN, max})$                                                                                                              | All                          |                     |      | _    | +0.4 | % V <sub>O, set</sub> |

| Load ( $I_O=I_{O, min}$ to $I_{O, max}$ )                                                                                                                        | All                          |                     |      | _    | 10   | mV                    |

| Output Regulation (for V <sub>0</sub> < 2.5Vdc)                                                                                                                  |                              |                     |      |      |      |                       |

| Line $(V_{IN}=V_{IN, min} \text{ to } V_{IN, max})$                                                                                                              | All                          |                     |      | _    | 5    | mV                    |

| Load ( $I_O=I_{O, min}$ to $I_{O, max}$ )                                                                                                                        | All                          |                     |      | _    | 10   | mV                    |

| Temperature ( $T_{ref}=T_{A, min}$ to $T_{A, max}$ )                                                                                                             | All                          |                     |      | _    | 0.4  | % V <sub>O, set</sub> |

| Output Ripple and Noise on nominal output $(V_{IN}=V_{IN, nom}$ and $I_{O}=I_{O, min}$ to $I_{O, max}$ Co = 0.1 $\mu$ F // 22 $\mu$ F ceramic capacitors)        |                              |                     |      |      |      |                       |

| Peak-to-Peak (5Hz to 20MHz bandwidth)                                                                                                                            | All                          |                     | _    | 50   | 100  | $mV_{pk-pk}$          |

| RMS (5Hz to 20MHz bandwidth)                                                                                                                                     | All                          |                     |      | 20   | 38   | $mV_{rms}$            |

| External Capacitance <sup>1</sup>                                                                                                                                |                              |                     |      |      |      |                       |

| Without the Tunable Loop <sup>™</sup>                                                                                                                            |                              |                     |      |      |      |                       |

| ESR ≥ 1 mΩ                                                                                                                                                       | All                          | C <sub>O, max</sub> | 22   | _    | 47   | μF                    |

| With the Tunable Loop <sup>™</sup>                                                                                                                               |                              |                     |      |      |      |                       |

| ESR ≥0.15 mΩ                                                                                                                                                     | All                          | C <sub>O, max</sub> | 22   | _    | 1000 | μF                    |

| ESR ≥ 10 mΩ                                                                                                                                                      | All                          | $C_{\text{O, max}}$ | 22   | _    | 5000 | μF                    |

| Output Current (in either sink or source mode)                                                                                                                   | All                          | I <sub>o</sub>      | 0    |      | 12   | Adc                   |

| Output Current Limit Inception (Hiccup Mode) (current limit does not operate in sink mode)                                                                       | All                          | I <sub>O, lim</sub> |      | 200  |      | % I <sub>o,max</sub>  |

| Output Short-Circuit Current                                                                                                                                     | All                          | I <sub>O, s/c</sub> |      | 1.5  |      | Α                     |

| (V <sub>0</sub> ≤250mV) ( Hiccup Mode )                                                                                                                          |                              |                     |      |      |      |                       |

| Efficiency                                                                                                                                                       | V <sub>O,set</sub> = 0.6Vdc  | η                   |      | 77.5 |      | %                     |

| V <sub>IN</sub> = 12Vdc, T <sub>A</sub> =25°C                                                                                                                    | V <sub>O, set</sub> = 1.2Vdc | η                   |      | 85.9 |      | %                     |

| $I_O = I_{O, max}, V_O = V_{O, set}$                                                                                                                             | V <sub>O,set</sub> = 1.8Vdc  | η                   |      | 89.6 |      | %                     |

|                                                                                                                                                                  | $V_{O,set} = 2.5 Vdc$        | η                   |      | 92.4 |      | %                     |

|                                                                                                                                                                  | V <sub>O,set</sub> = 3.3Vdc  | η                   |      | 93.4 |      | %                     |

|                                                                                                                                                                  | V <sub>O,set</sub> = 5.0Vdc  | η                   |      | 95.0 |      | %                     |

| Switching Frequency                                                                                                                                              | All                          | f <sub>sw</sub>     | _    | 600  | _    | kHz                   |

<sup>&</sup>lt;sup>1</sup> External capacitors may require using the new Tunable Loop<sup>™</sup> feature to ensure that the module is stable as well as getting the best transient response. See the Tunable Loop<sup>™</sup> section for details.

# **General Specifications**

| Parameter                                                                                                          | Device | Min | Тур         | Max | Unit    |

|--------------------------------------------------------------------------------------------------------------------|--------|-----|-------------|-----|---------|

| Calculated MTBF (I <sub>O</sub> =0.8I <sub>O, max</sub> , T <sub>A</sub> =40°C) Telecordia Issue 2 Method 1 Case 3 | All    |     | 16,817,995  |     | Hours   |

| Weight                                                                                                             |        | _   | 2.33(0.082) | _   | g (oz.) |

# **Feature Specifications**

Unless otherwise indicated, specifications apply over all operating input voltage, resistive load, and temperature conditions. See Feature Descriptions for additional information.

| Parameter                                                                                                                                                                      | Device | Symbol    | Min  | Тур         | Max                  | Unit            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------|------|-------------|----------------------|-----------------|

| On/Off Signal Interface                                                                                                                                                        |        |           |      |             |                      |                 |

| $(V_{IN}=V_{IN,min}$ to $V_{IN,max}$ ; open collector or equivalent,                                                                                                           |        |           |      |             |                      |                 |

| Signal referenced to GND)                                                                                                                                                      |        |           |      |             |                      |                 |

| Device is with suffix "4" – Positive Logic (See Ordering Information)                                                                                                          |        |           |      |             |                      |                 |

| Logic High (Module ON)                                                                                                                                                         |        |           |      |             |                      |                 |

| Input High Current                                                                                                                                                             | All    | Іін       |      | _           | 1                    | mA              |

| Input High Voltage                                                                                                                                                             | All    | ViH       | 3.5  | _           | $V_{IN,max}$         | V               |

| Logic Low (Module OFF)                                                                                                                                                         |        |           |      |             |                      |                 |

| Input Low Current                                                                                                                                                              | All    | lıL       | _    | _           | 10                   | μA              |

| Input Low Voltage                                                                                                                                                              | All    | VIL       | -0.2 | _           | 0.3                  | V               |

| Device Code with no suffix – Negative Logic (See Ordering Information)                                                                                                         |        |           |      |             |                      |                 |

| (On/OFF pin is open collector/drain logic input with                                                                                                                           |        |           |      |             |                      |                 |

| external pull-up resistor; signal referenced to GND)                                                                                                                           |        |           |      |             |                      |                 |

| Logic High (Module OFF)                                                                                                                                                        |        |           |      |             |                      |                 |

| Input High Current                                                                                                                                                             | All    | Іін       | _    | _           | 1                    | mA              |

| Input High Voltage                                                                                                                                                             | All    | ViH       | 3.5  | _           | $V_{\text{IN, max}}$ | Vdc             |

| Logic Low (Module ON)                                                                                                                                                          |        |           |      |             |                      |                 |

| Input low Current                                                                                                                                                              | All    | lıL       | _    | _           | 10                   | μA              |

| Input Low Voltage                                                                                                                                                              | All    | VIL       | -0.2 | _           | 0.3                  | Vdc             |

| Turn-On Delay and Rise Times                                                                                                                                                   |        |           |      |             |                      |                 |

| $(V_{IN}=V_{IN, nom}, I_O=I_{O, max}, V_O)$ to within ±1% of steady state)                                                                                                     |        |           |      |             |                      |                 |

| Case 1: On/Off input is enabled and then input power is applied (delay from instant at which $V_{IN} = V_{IN,min}$ until $V_0 = 10\%$ of $V_0, set$ )                          | All    | Tdelay    | _    | 5           | _                    | msec            |

| Case 2: Input power is applied for at least one second and then the On/Off input is enabled (delay from instant at which Von/Off is enabled until $V_0 = 10\%$ of $V_0$ , set) | All    | Tdelay    | _    | 5           | _                    | msec            |

| Output voltage Rise time (time for $V_0$ to rise from 10% of $V_0$ , set to 90% of $V_0$ , set)                                                                                | All    | Trise     | _    | 2           | _                    | msec            |

| Output voltage overshoot (T <sub>A</sub> = 25°C                                                                                                                                |        |           |      |             | 3.0                  | $\% V_{O, set}$ |

| $V_{IN}$ = $V_{IN, min}$ to $V_{IN, max}$ , $I_O$ = $I_{O, min}$ to $I_{O, max}$ )                                                                                             |        |           |      |             |                      |                 |

| With or without maximum external capacitance                                                                                                                                   |        |           |      |             |                      |                 |

| Over Temperature Protection                                                                                                                                                    | All    | $T_{ref}$ |      | 120/<br>130 |                      | °C              |

| (See Thermal Considerations section)                                                                                                                                           |        |           |      |             |                      |                 |

# Feature Specifications (cont.)

| Parameter                                               | Device | Symbol | Min | Тур   | Max | Units         |

|---------------------------------------------------------|--------|--------|-----|-------|-----|---------------|

| Input Undervoltage Lockout                              |        |        |     |       |     |               |

| Turn-on Threshold                                       | All    |        |     |       | 2.9 | Vdc           |

| Turn-off Threshold                                      | All    |        | 2.6 |       |     | Vdc           |

| Hysteresis                                              | All    |        |     | 0.3   |     | Vdc           |

| PGOOD (Power Good)                                      |        |        |     |       |     |               |

| Signal Interface Open Drain, V <sub>supply</sub> ≤ 5VDC |        |        |     |       |     |               |

| Overvoltage threshold for PGOOD                         |        |        |     | 112.5 |     | $%V_{O, set}$ |

| Undervoltage threshold for PGOOD                        |        |        |     | 87.5  |     | $%V_{O, set}$ |

| Pulldown resistance of PGOOD pin                        | All    |        |     | 30    |     | Ω             |

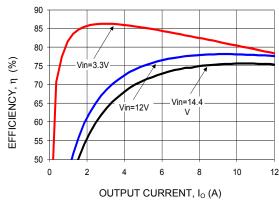

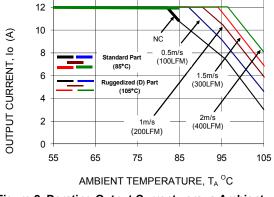

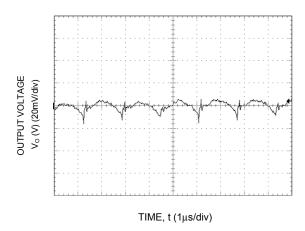

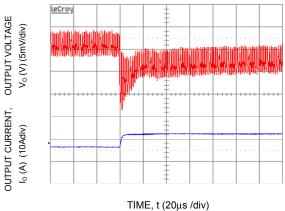

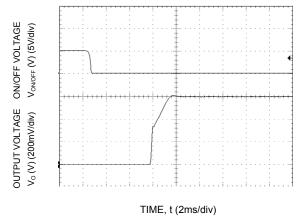

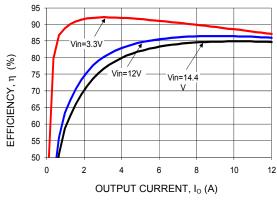

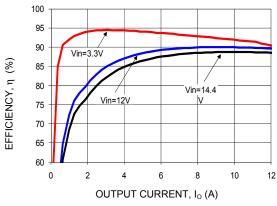

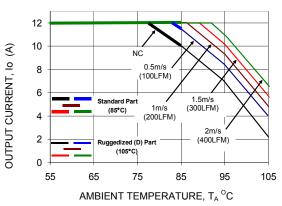

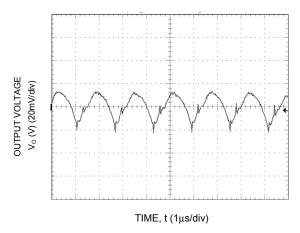

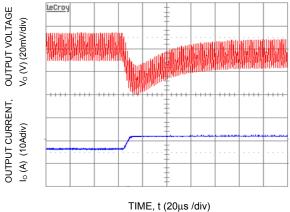

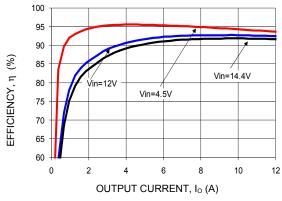

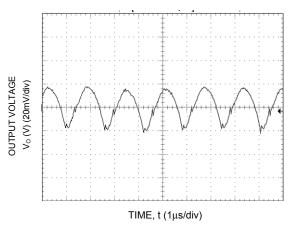

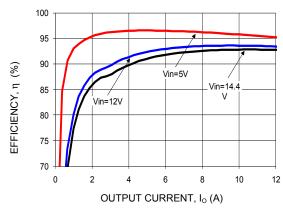

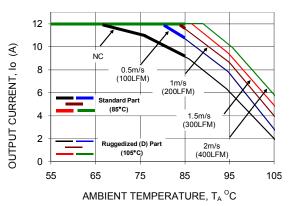

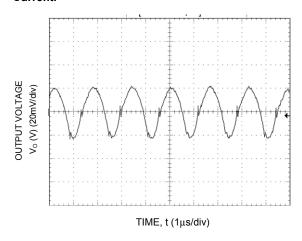

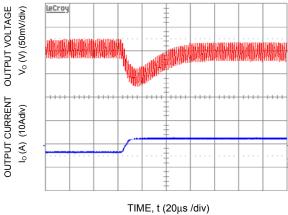

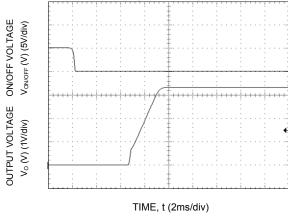

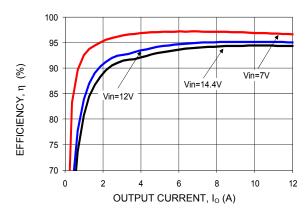

The following figures provide typical characteristics for the 12A Analog Pico DLynx<sup>TM</sup> at 0.6Vo and 25°C.

Figure 1. Converter Efficiency versus Output Current.

Figure 2. Derating Output Current versus Ambient Temperature and Airflow.

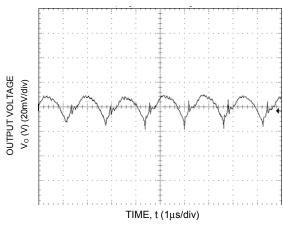

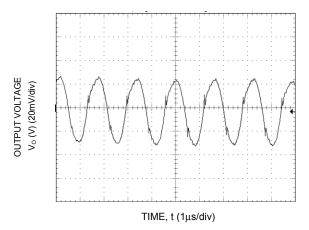

Figure 3. Typical output ripple and noise (Co=22 $\mu$ F ceramic, VIN = 12V, Io = Io,max, ).

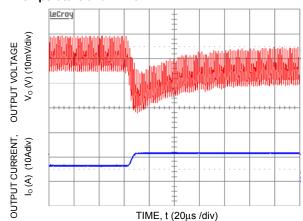

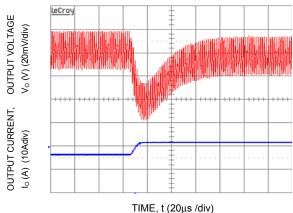

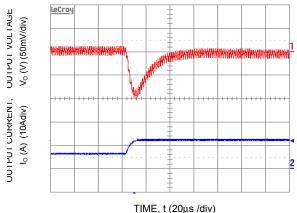

Figure 4. Transient Response to Dynamic Load Change from 50% to 100% at 12Vin, Cout-3x47uF+6x330uF, CTune-47nF, RTune-180ohms

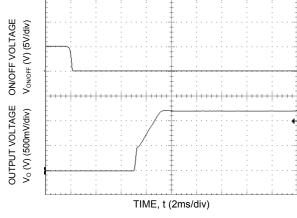

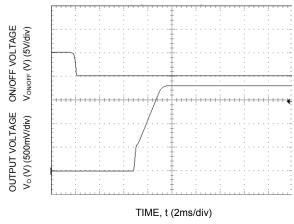

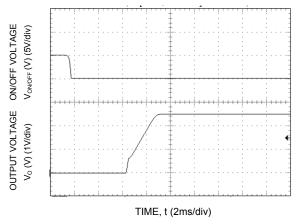

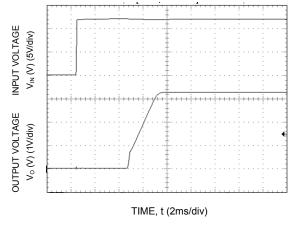

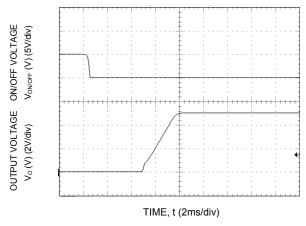

Figure 5. Typical Start-up Using On/Off Voltage ( $I_0 = I_{0,max}$ ).

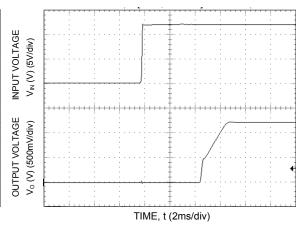

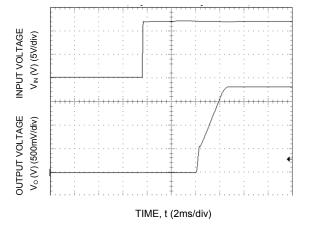

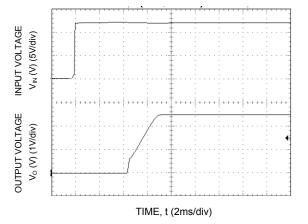

Figure 6. Typical Start-up Using Input Voltage ( $V_{IN} = 12V$ ,  $I_0 = I_{0,max}$ ).

The following figures provide typical characteristics for the 12A Analog Pico DLynx<sup>™</sup> at 1.2Vo and 25°C.

12 10 3 OUTPUT CURRENT, Io 0.5m/s (100LFM) 8 6 1.5m/s (300LFM) 1m/s (200LFM) Standard Part (85 C) 4 2m/s (400LFM) 2 edized (D) Part (105°C 0 55 75 105 AMBIENT TEMPERATURE, T<sub>A</sub> °C

Figure 7. Converter Efficiency versus Output Current.

Figure 8. Derating Output Current versus Ambient Temperature and Airflow.

Figure 9. Typical output ripple and noise ( $C_0$ =22 $\mu$ F ceramic,  $V_{IN}$  = 12V,  $I_0$  =  $I_{0,max}$ ,).

Figure 10. Transient Response to Dynamic Load Change from 50% to 100% at 12Vin, Cout-1x47uF+3x330uF, CTune-10nF & RTune-220ohms

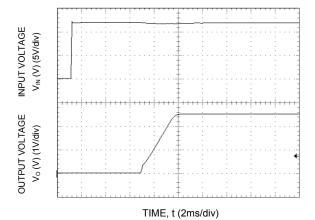

Figure 11. Typical Start-up Using On/Off Voltage ( $I_0 = I_{0,max}$ ).

Figure 12. Typical Start-up Using Input Voltage ( $V_{IN} = 12V$ ,  $I_0 = I_{0,max}$ ).

The following figures provide typical characteristics for the 12A Analog Pico DLynx<sup>™</sup> at 1.8Vo and 25°C.

Figure 13. Converter Efficiency versus Output Current.

Figure 14. Derating Output Current versus Ambient Temperature and Airflow.

Figure 15. Typical output ripple and noise ( $C_0$ =22 $\mu$ F ceramic,  $V_{IN}$  = 12V,  $I_0$  =  $I_{0,max}$ , ).

Figure 16. Transient Response to Dynamic Load Change from 50% to 100% at 12Vin, Cout-1x47uF+2x330uF,CTune-5600pF & RTune-270ohms

Figure 17. Typical Start-up Using On/Off Voltage ( $I_0 = I_{0,max}$ ).

Figure 18. Typical Start-up Using Input Voltage ( $V_{IN} = 12V$ ,  $I_0 = I_{0,max}$ ).

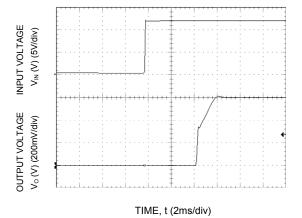

The following figures provide typical characteristics for the 12A Analog Pico DLynx<sup>TM</sup> at 2.5Vo and 25°C.

12 € 10 OUTPUT CURRENT, Io 8 (100LFM) 6 (200LFM) (85°C) 4 1.5m/s 2 Ruggedized (D) 2m/s (400LFM) Part (105°C) 0 55 75 95 105 AMBIENT TEMPERATURE, TA OC

Figure 19. Converter Efficiency versus Output Current.

Figure 20. Derating Output Current versus Ambient Temperature and Airflow.

Figure 21. Typical output ripple and noise ( $C_0$ =22 $\mu$ F ceramic,  $V_{IN}$  = 12V,  $I_0$  =  $I_{O,max}$ ,).

Figure 22. Transient Response to Dynamic Load Change from 50% to 100% at 12Vin, Cout-1x47uF+1x330uF,CTune-3300pF & RTune-270ohms

Figure 23. Typical Start-up Using On/Off Voltage ( $I_0 = I_{0,max}$ ).

Figure 24. Typical Start-up Using Input Voltage ( $V_{IN} = 12V$ ,  $I_0 = I_{0,max}$ ).

The following figures provide typical characteristics for the 12A Analog Pico DLynx<sup>™</sup> at 3.3Vo and 25°C.

Figure 25. Converter Efficiency versus Output Current.

Figure 26. Derating Output Current versus Ambient Temperature and Airflow.

Figure 27. Typical output ripple and noise ( $C_0=22\mu F$  ceramic,  $V_{IN}=12V$ ,  $I_0=I_{0,max}$ ,).

Figure 28. Transient Response to Dynamic Load Change from 50% to 100% at 12Vin, Cout-1x47uF+1x330uF,CTune-2700pF & RTune-330ohms

Figure 29. Typical Start-up Using On/Off Voltage ( $I_0 = I_{0,max}$ ).

Figure 30. Typical Start-up Using Input Voltage ( $V_{IN} = 12V$ ,  $I_0 = I_{0,max}$ ).

The following figures provide typical characteristics for the 12A Analog Pico DLynx<sup>™</sup> at 5Vo and 25°C.

12 OUTPUT CURRENT, Io (A) 10 NC 0.5m/s (100LFM) 8 6 1m/s (200LFM) Standard Part (85°C) 1.5m/s (300LFM) 2 2m/s (400LFM) (105°C) 0 55 65 75 85 105 AMBIENT TEMPERATURE, T<sub>A</sub> °C

Figure 31. Converter Efficiency versus Output Current.

Figure 32. Derating Output Current versus Ambient Temperature and Airflow.

Figure 33. Typical output ripple and noise ( $C_0$ =22 $\mu$ F ceramic,  $V_{IN}$  = 12V,  $I_0$  =  $I_{O,max}$ , ).

Figure 34. Transient Response to Dynamic Load Change from 50% to 100% at 12Vin, Cout-5x47uF, CTune-1500pF & RTune-330ohms

Figure 35. Typical Start-up Using On/Off Voltage ( $I_0 = I_{0,max}$ ).

Figure 36. Typical Start-up Using Input Voltage ( $V_{IN}$  = 12V,  $I_0$  =  $I_{0,max}$ ).

# **Design Considerations**

#### **Input Filtering**

The 12A Analog Pico DLynx<sup>TM</sup> module should be connected to a low ac-impedance source. A highly inductive source can affect the stability of the module. An input capacitance must be placed directly adjacent to the input pin of the module, to minimize input ripple voltage and ensure module stability.

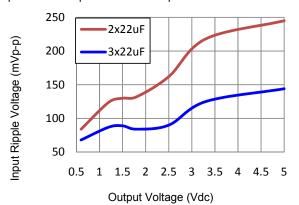

To minimize input voltage ripple, ceramic capacitors are recommended at the input of the module. Figure 37 shows the input ripple voltage for various output voltages at 12A of load current with 2x22  $\mu$ F or 3x22  $\mu$ F ceramic capacitors and an input of 12V.

Figure 37. Input ripple voltage for various output voltages with 2x22  $\mu F$  or 3x22  $\mu F$  ceramic capacitors at the input (12A load). Input voltage is 12V.

#### **Output Filtering**

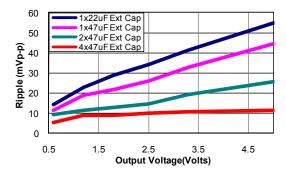

The 12A Analog Pico DLynx<sup>TM</sup> modules are designed for low output ripple voltage and will meet the maximum output ripple specification with 0.1  $\mu F$  ceramic and 22  $\mu F$  ceramic capacitors at the output of the module. However, additional output filtering may be required by the system designer for a number of reasons. First, there may be a need to further reduce the output ripple and noise of the module. Second, the dynamic response characteristics may need to be customized to a particular load step change.

To reduce the output ripple and improve the dynamic response to a step load change, additional capacitance at the output can be used. Low ESR polymer and ceramic capacitors are recommended to improve the dynamic response of the module. Figure 38 provides output ripple information for different external capacitance values at various Vo and a full load current of 12A. For stable operation of the module, limit the capacitance to less than the maximum output capacitance as specified in the electrical specification table. Optimal performance of

the module can be achieved by using the Tunable Loop<sup>TM</sup> feature described later in this data sheet

Figure 38. Output ripple voltage for various output voltages with external 1x22  $\mu$ F, 1x47  $\mu$ F, 2x47  $\mu$ F or 4x47  $\mu$ F ceramic capacitors at the output (12A load). Input voltage is 12V.

#### **Safety Considerations**

For safety agency approval the power module must be installed in compliance with the spacing and separation requirements of the end-use safety agency standards, i.e., UL 60950-1 2nd, CSA C22.2 No. 60950-1-07, DIN EN 60950-1:2006 + A11 (VDE0805 Teil 1 + A11):2009-11; EN 60950-1:2006 + A11:2009-03.

For the converter output to be considered meeting the requirements of safety extra-low voltage (SELV), the input must meet SELV requirements. The power module has extra-low voltage (ELV) outputs when all inputs are ELV.

The input to these units is to be provided with a time delay fuse with a maximum rating of 15 A in the positive input lead.

# **Feature Descriptions**

#### Remote On/Off

The 12A Analog Pico DLynx<sup>TM</sup> power modules feature an On/Off pin for remote On/Off operation. Two On/Off logic options are available. In the Positive Logic On/Off option, (device code suffix "4" – see Ordering Information), the module turns ON during a logic High on the On/Off pin and turns OFF during a logic Low. With the Negative Logic On/Off option, (no device code suffix, see Ordering Information), the module turns OFF during logic High and ON during logic Low. The On/Off signal should be always referenced to ground. For either On/Off logic option, leaving the On/Off pin disconnected will turn the module ON when input voltage is present.

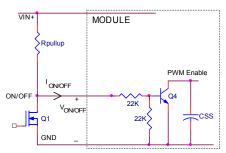

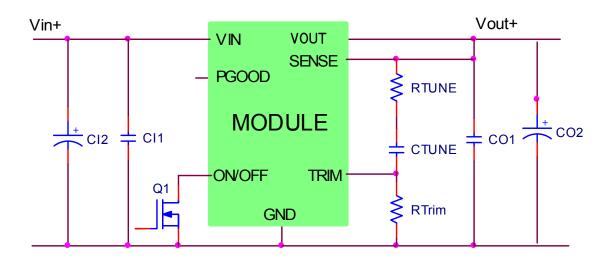

For positive logic modules, the circuit configuration for using the On/Off pin is shown in Figure 39. When the external transistor Q1 is in the OFF state, the internal PWM Enable signal is pulled high through an internal resistor and the external pullup resistor and the module is ON. When transistor Q1 is turned ON, the On/Off pin is pulled low and the module is OFF. A suggested value for  $R_{\text{pullup}}$  is TBD

#### TBA

# Figure 39. Circuit configuration for using positive On/Off logic.

For negative logic On/Off modules, the circuit configuration is shown in Fig. 40. The On/Off pin should be pulled high with an external pull-up resistor (suggested value for the 3V to 14.4V input range is 20Kohms). When transistor Q1 is in the OFF state, the On/Off pin is pulled high, internal transistor Q4 is turned ON and the module is OFF. To turn the module ON, Q1 is turned ON pulling the On/Off pin low, turning transistor Q4 OFF resulting in the PWM Enable pin going high and the module turning ON.

PVX012 NEGATIVE LOGIC FIGURE

Figure 40. Circuit configuration for using negative On/Off logic.

#### **Monotonic Start-up and Shutdown**

The module has monotonic start-up and shutdown behavior for any combination of rated input voltage, output current and operating temperature range.

#### Startup into Pre-biased Output

The modules can start into a prebiased output as long as the prebias voltage is 0.5V less than the set output voltage.

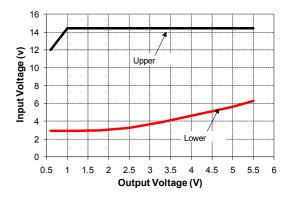

#### **Output Voltage Programming**

The output voltage of the module is programmable to any voltage from 0.6dc to 5.5Vdc by connecting a resistor between the Trim and GND pins of the module. Certain restrictions apply on the output voltage set point depending on the input voltage. These are shown in the Output Voltage vs. Input Voltage Set Point Area plot in Fig. 41. The Upper Limit curve shows that for output voltages lower than 1V, the input voltage must be lower than the maximum of 14.4V. The Lower Limit curve shows that for output voltages higher than 0.6V, the input voltage needs to be larger than the minimum of 3V.

Figure 41. Output Voltage vs. Input Voltage Set Point Area plot showing limits where the output voltage can be set for different input voltages.

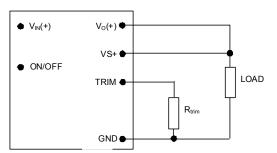

Figure 42. Circuit configuration for programming output voltage using an external resistor.

Without an external resistor between Trim and GND pins, the output of the module will be 0.6Vdc. To calculate the value of the trim resistor, *Rtrim* for a desired output voltage, should be as per the following equation:

$$Rtrim = \left\lceil \frac{12}{(Vo - 0.6)} \right\rceil k\Omega$$

Rtrim is the external resistor in  $k\Omega$

${\it Vo}$  is the desired output voltage. Table 1 provides Rtrim values required for some common output voltages.

Table 1

| V <sub>O, set</sub> (V) | Rtrim (KΩ) |

|-------------------------|------------|

| 0.6                     | Open       |

| 0.9                     | 40         |

| 1.0                     | 30         |

| 1.2                     | 20         |

| 1.5                     | 13.33      |

| 1.8                     | 10         |

| 2.5                     | 6.316      |

| 3.3                     | 4.444      |

| 5.0                     | 2.727      |

#### **Remote Sense**

The power module has a Remote Sense feature to minimize the effects of distribution losses by regulating the voltage at the SENSE pin. The voltage between the SENSE pin and VOUT pin should not exceed 0.5V.

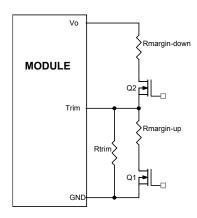

#### Voltage Margining

Output voltage margining can be implemented in the module by connecting a resistor,  $R_{\text{margin-up}}$ , from the Trim pin to the ground pin for margining-up the output voltage and by connecting a resistor,  $R_{\text{margin-down}}$ , from the Trim pin to output pin for margining-down. Figure 43 shows the circuit configuration for output voltage margining. The POL Programming Tool, available at www.lineagepower.com under the Downloads section, also calculates the values of  $R_{\text{margin-up}}$  and  $R_{\text{margin-down}}$  for a specific output voltage and % margin. Please consult your local Lineage Power technical representative for additional details.

Figure 43. Circuit Configuration for margining Output voltage.

#### **Overcurrent Protection**

To provide protection in a fault (output overload) condition, the unit is equipped with internal current-limiting circuitry and can endure current limiting continuously. At the point of current-limit inception, the unit enters hiccup mode. The unit operates normally once the output current is brought back into its specified range.

#### **Overtemperature Protection**

To provide protection in a fault condition, the unit is equipped with a thermal shutdown circuit. The unit will shutdown if the overtemperature threshold of 120(Q1) / 130(L1) $^{\circ}$ C(typ) is exceeded at the thermal reference point  $T_{ref}$ . Once the unit goes into thermal shutdown it will then wait to cool before attempting to restart.

#### **Input Undervoltage Lockout**

At input voltages below the input undervoltage lockout limit, the module operation is disabled. The module will begin to operate at an input voltage above the undervoltage lockout turn-on threshold.

#### **Power Good**

The module provides a Power Good (PGOOD) signal that is implemented with an open-drain output to indicate that the output voltage is within the regulation limits of the power module. The PGOOD signal will be de-asserted to a low state if any condition such as overtemperature, overcurrent or loss of regulation occurs that would result in the output voltage going  $\pm 10\%$  outside the setpoint value. The PGOOD terminal can be connected through a pullup resistor (suggested value  $100 \mathrm{K}\Omega$ ) to a source of 5VDC or lower.

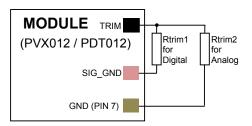

#### **Dual Layout**

Identical dimensions and pin layout of Analog and Digital Pico DLynx modules permit migration from one to the other without needing to change the layout. To support this, 2 separate Trim Resistor locations have to be provided in the layout. For the digital modules, the resistor is connected between the TRIM pad and SGND and in the case of the analog module it is connected between TRIM and GND

**Caution** – Do not connect SIG\_GND to GND elsewhere in the layout

Figure 44. Layout to support either Analog or Digital PicoDLynx on the same pad.

# Tunable Loop<sup>™</sup>

The 12A Pico DLynx<sup>TM</sup> modules have a feature that optimizes transient response of the module called Tunable Loop<sup>TM</sup>.

External capacitors are usually added to the output of the module for two reasons: to reduce output ripple and noise (see Figure 38) and to reduce output voltage deviations from the steady-state value in the presence of dynamic load current changes. Adding external capacitance however affects the voltage control loop of the module, typically causing the loop to slow down with sluggish response. Larger values of external capacitance could also cause the module to become unstable.

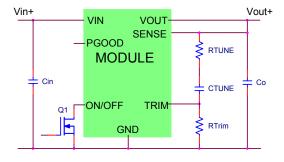

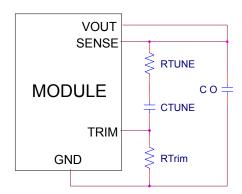

The Tunable Loop<sup>TM</sup> allows the user to externally adjust the voltage control loop to match the filter network connected to the output of the module. The Tunable Loop<sup>TM</sup> is implemented by connecting a series R-C between the SENSE and TRIM pins of the module, as shown in Fig. 45. This R-C allows the user to externally adjust the voltage loop feedback compensation of the module.

Figure. 45. Circuit diagram showing connection of  $R_{\text{TUME}}$  and  $C_{\text{TUNE}}$  to tune the control loop of the module.

Recommended values of R<sub>TUNE</sub> and C<sub>TUNE</sub> for different output capacitor combinations are given in Tables 2 and 3. Table 2 shows the recommended values of  $R_{\text{TUNE}}$  and  $C_{\text{TUNE}}$  for different values of ceramic output capacitors up to 1000uF that might be needed for an application to meet output ripple and noise requirements. Selecting R<sub>TUNE</sub> and C<sub>TUNE</sub> according to Table 2 will ensure stable operation of the module. In applications with tight output voltage limits in the presence of dynamic current loading, additional output capacitance will be required. Table 3 lists recommended values of  $R_{\text{TUNE}}$  and  $C_{\text{TUNE}}$  in order to meet 2% output voltage deviation limits for some common output voltages in the presence of a 6A to 12A step change (50% of full load), with an input voltage of 12V.

Please contact your Lineage Power technical representative to obtain more details of this feature as well as for guidelines on how to select the right value of external R-C to tune the module for best transient performance and stable operation for other output capacitance values or input voltages other than 12V.

Table 2. General recommended values of of  $R_{\text{TUNE}}$  and  $C_{\text{TUNE}}$  for Vin=12V and various external ceramic capacitor combinations.

| Co                | 1x47μF | 2x47μF | 4x47μF | 6x47μF | 10x47μF | 20x47μF |

|-------------------|--------|--------|--------|--------|---------|---------|

| R <sub>TUNE</sub> | 330    | 330    | 330    | 330    | 270     | 180     |

| C <sub>TUNE</sub> | 100pF  | 560pF  | 1500pF | 2200pF | 3900pF  | 6800pF  |

Table 3. Recommended values of  $R_{TUNE}$  and  $C_{TUNE}$  to obtain transient deviation of 2% of Vout for a 6A step load with Vin=12V.

| Vo                | 5V       | 3.3V    | 2.5V    | 1.8V    | 1.2V    | 0.6V    |

|-------------------|----------|---------|---------|---------|---------|---------|

|                   |          | 1x47μF  | 3x47μF  | 1x47μF  | 1x47μF  | 3x47μF  |

| Co                | 5x47μF   | +       | +       | +       | +       | +       |

|                   | οπ τη μι | 330μF   |         |         | 3x330μF |         |

|                   |          | Polymer | Polymer | Polymer | Polymer | Polymer |

| R <sub>TUNE</sub> | 330      | 330     | 270     | 270     | 220     | 180     |

| C <sub>TUNE</sub> | 1500pF   | 2700pF  | 3300pF  | 5600pF  | 10nF    | 47nF    |

| ΔV                | 99mV     | 58mV    | 47mV    | 34mV    | 24mV    | 12mV    |

## **Thermal Considerations**

Power modules operate in a variety of thermal environments; however, sufficient cooling should always be provided to help ensure reliable operation.

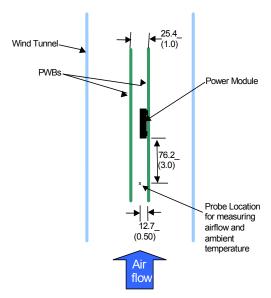

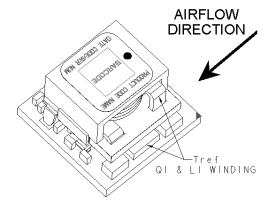

Considerations include ambient temperature, airflow, module power dissipation, and the need for increased reliability. A reduction in the operating temperature of the module will result in an increase in reliability. The thermal data presented here is based on physical measurements taken in a wind tunnel. The test set-up is shown in Figure 46. The preferred airflow direction for the module is in Figure 47.

Figure 46. Thermal Test Setup.

The thermal reference points,  $T_{ref}$  used in the specifications are also shown in Figure 45. For reliable operation the temperature at Q1 should not exceed 120°C and the temperature at L1 should not exceed 130°C. The output power of the module should not exceed the rated power of the module (Vo,set x lo,max).

Please refer to the Application Note "Thermal Characterization Process For Open-Frame Board-Mounted Power Modules" for a detailed discussion of thermal aspects including maximum device temperatures.

Figure 47. Preferred airflow direction and location of hot-spot of the module (Tref).

# **Example Application Circuit**

#### Requirements:

Vin: 12V Vout: 1.8V

lout: 9A max., worst case load transient is from 6A to 9A  $\Delta$ Vout: 1.5% of Vout (27mV) for worst case load transient

Vin, ripple 1.5% of Vin (180mV, p-p)

CI1 2x22µF/16V ceramic capacitor (e.g. Murata GRM32ER61C226KE20)

CI2 47µF/16V bulk electrolytic

CO1 2 x 47μF/6.3V ceramic capacitor (e.g. Murata GRM31CR60J476ME19)

CO2 1 x 330μF/6.3V Polymer (e.g. Sanyo Poscap)

CTune 3300pF ceramic capacitor (can be 1206, 0805 or 0603 size)

RTune 270 ohms SMT resistor (can be 1206, 0805 or 0603 size)

RTrim  $10k\Omega$  SMT resistor (can be 1206, 0805 or 0603 size, recommended tolerance of 0.1%)

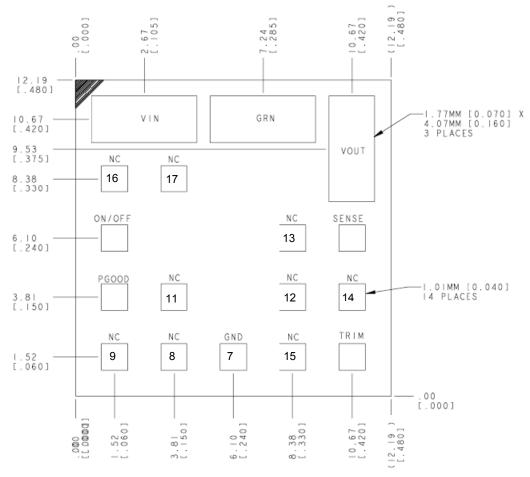

# **Mechanical Outline**

Dimensions are in millimeters and (inches).

Tolerances: x.x mm  $\pm$  0.5 mm (x.xx in.  $\pm$  0.02 in.) [unless otherwise indicated]

x.xx mm  $\pm$  0.25 mm (x.xxx in  $\pm$  0.010 in.)

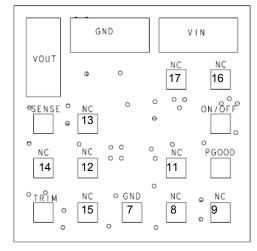

| PIN | FUNCTION       | PIN | FUNCTION |

|-----|----------------|-----|----------|

| 1   | ON/OFF         | 10  | PGOOD    |

| 2   | VIN            | 11  | NC       |

| 3   | GND            | 12  | NC       |

| 4   | VOUT           | 13  | NC       |

| 5   | VS+<br>(SENSE) | 14  | NC       |

| 6   | TRIM           | 15  | NC       |

| 7   | GND            | 16  | NC       |

| 8   | NC             | 17  | NC       |

| 9   | NC             | _   |          |

BOTTOM VIEW

LINEAGE POWER 19

Document No: DS10-008 ver. 1.12

# **Recommended Pad Layout**

Dimensions are in millimeters and (inches).

Tolerances: x.x mm  $\pm$  0.5 mm (x.xx in.  $\pm$  0.02 in.) [unless otherwise indicated] x.xx mm  $\pm$  0.25 mm (x.xxx in  $\pm$  0.010 in.)

RECOMMENDED FOOTPRINT -THROUGH THE BOARD-

| PIN | FUNCTION    | PIN | FUNCTION |

|-----|-------------|-----|----------|

| 1   | ON/OFF      | 10  | PGOOD    |

| 2   | VIN         | 11  | NC       |

| 3   | GND         | 12  | NC       |

| 4   | VOUT        | 13  | NC       |

| 5   | VS+ (SENSE) | 14  | NC       |

| 6   | TRIM        | 15  | NC       |

| 7   | GND         | 16  | NC       |

| 8   | NC          | 17  | NC       |

| 9   | NC          |     |          |

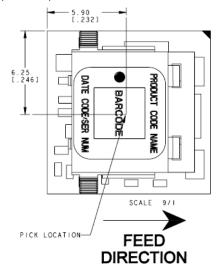

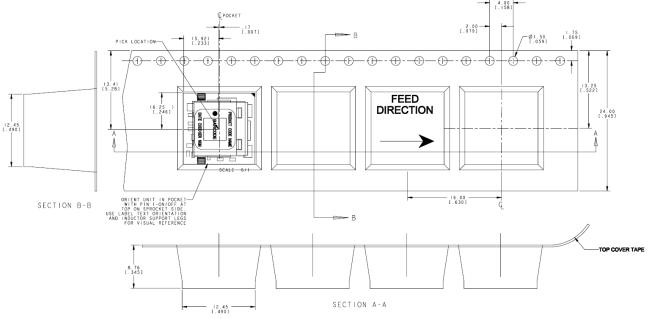

# **Packaging Details**

The 12V Analog Pico DLynx<sup>™</sup> 12A modules are supplied in tape & reel as standard. Modules are shipped in quantities of 200 modules per reel.

All Dimensions are in millimeters and (in inches).

Reel Dimensions:

Outside Dimensions: 330.2 mm (13.00)

Inside Dimensions: 177.8 mm (7.00")

Tape Width: 24.00 mm (0.945")

LINEAGE POWER 21

Document No: DS10-008 ver. 1.12 PDF name: PVX012A0X.pdf

#### **Surface Mount Information**

#### **Pick and Place**

The 12VAnalog Pico DLynxTM 12A modules use an open frame construction and are designed for a fully automated assembly process. The modules are fitted with a label designed to provide a large surface area for pick and place operations. The label meets all the requirements for surface mount processing, as well as safety standards, and is able to withstand reflow temperatures of up to 300°C. The label also carries product information such as product code, serial number and the location of manufacture.

#### **Nozzle Recommendations**

The module weight has been kept to a minimum by using open frame construction. Variables such as nozzle size, tip style, vacuum pressure and placement speed should be considered to optimize this process. The minimum recommended inside nozzle diameter for reliable operation is 3mm. The maximum nozzle outer diameter, which will safely fit within the allowable component spacing, is 7 mm.

#### **Bottom Side / First Side Assembly**

This module is not recommended for assembly on the bottom side of a customer board. If such an assembly is attempted, components may fall off the module during the second reflow process.

#### Lead Free Soldering

The 12VAnalog Pico DLynxTM 12A modules are lead-free (Pb-free) and RoHS compliant and fully compatible in a Pb-free soldering process. Failure to observe the instructions below may result in the failure of or cause damage to the modules and can adversely affect long-term reliability.

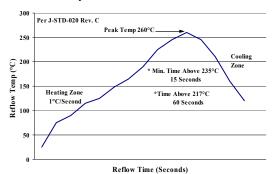

#### **Pb-free Reflow Profile**

Power Systems will comply with J-STD-020 Rev. C (Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices) for both Pb-free solder profiles and MSL classification procedures. This standard provides a recommended forced-air-convection reflow profile based on the volume and thickness of the package (table 4-2). The suggested Pb-free solder paste is Sn/Ag/Cu (SAC). For questions regarding LGA, solder volume; please contact Lineage Power for special manufacturing process instructions.

The recommended linear reflow profile using Sn/Ag/Cu solder is shown in Fig. 48. Soldering outside of the recommended profile requires testing to verify results and performance.

#### **MSL** Rating

The 12VAnalog Pico DLynxTM 12A modules have a MSL rating of 1.

#### Storage and Handling

The recommended storage environment and handling procedures for moisture-sensitive surface mount packages is detailed in J-STD-033 Rev. A (Handling, Packing, Shipping and Use of Moisture/Reflow Sensitive Surface Mount Devices). Moisture barrier bags (MBB) with desiccant are required for MSL ratings of 2 or greater. These sealed packages should not be broken until time of use. Once the original package is broken, the floor life of the product at conditions of  $\leq 30^{\circ}\text{C}$  and 60% relative humidity varies according to the MSL rating (see J-STD-033A). The shelf life for dry packed SMT packages will be a minimum of 12 months from the bag seal date, when stored at the following conditions:  $<40^{\circ}\text{ C},<90\%$  relative humidity.

Figure 48. Recommended linear reflow profile using Sn/Ag/Cu solder.

# Post Solder Cleaning and Drying Considerations

Post solder cleaning is usually the final circuit-board assembly process prior to electrical board testing. The result of inadequate cleaning and drying can affect both the reliability of a power module and the testability of the finished circuit-board assembly. For guidance on appropriate soldering, cleaning and drying procedures, refer to *Board Mounted Power Modules: Soldering and Cleaning* Application Note (AN04-001).

# **Ordering Information**

Please contact your Lineage Power Sales Representative for pricing, availability and optional features.

**Table 4. Device Codes**

| Device Code     | Input<br>Voltage Range | Output<br>Voltage | Output<br>Current | On/Off<br>Logic | Sequencing | Comcodes    |

|-----------------|------------------------|-------------------|-------------------|-----------------|------------|-------------|

| PVX012A0X3-SRZ  | 3 – 14.4Vdc            | 0.6 – 5.5Vdc      | 12A               | Negative        | No         | CC109159686 |

| PVX012A0X3-SRDZ | 3 – 14.4Vdc            | 0.6 – 5.5Vdc      | 12A               | Negative        | No         | CC109168811 |

| PVX012A0X43-SRZ | 3 – 14.4Vdc            | 0.6 – 5.5Vdc      | 12A               | Positive        | No         | TBA*        |

<sup>-</sup>Z refers to RoHS compliant parts

Table 5. Coding Scheme

| Package<br>Identifier                 | Family                                        | Sequencing<br>Option                             | Output<br>current | Output<br>voltage              | On/Off<br>logic                  | Remote<br>Sense        | Options                                          |                                                                                           | ROHS<br>Compliance |

|---------------------------------------|-----------------------------------------------|--------------------------------------------------|-------------------|--------------------------------|----------------------------------|------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------|

| Р                                     | V                                             | X                                                | 012A0             | Х                              |                                  | 3                      | -SR                                              | -D                                                                                        | Z                  |

| P=Pico<br>U=Micro<br>M=Mega<br>G=Giga | D=Dlynx<br>Digital<br>V =<br>DLynx<br>Analog. | T=with EZ<br>Sequence<br>X=without<br>sequencing | 12A               | X =<br>programm<br>able output | 4 = positive No entry = negative | 3 =<br>Remote<br>Sense | S =<br>Surface<br>Mount<br>R =<br>Tape &<br>Reel | D = 105°C<br>operating<br>ambient,<br>40G<br>operating<br>shock as<br>per MIL<br>Std 810F | Z = ROHS6          |

World Wide Headquarters **Lineage Power Corporation** 601 Shiloh Road, Plano, TX 75074, USA +1-888-LINEAGE(546-3243) (Outside U.S.A.: +1-972-244-WATT(9288)) www.lineagepower.com e-mail: techsupport1@lineagepower.com Asia-Pacific Headquarters Tel: +86.021.54279977\*808

Europe, Middle-East and Africa Headquarters

Tel: +49.89.878067-280

**India Headquarters** Tel: +91.80.28411633

Lineage Power reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product(s) or information.

Lineage Power DC-DC products are protected under various patents. Information on these patents is available at www.lineagepower.com/patents.

© 2011 Lineage Power Corporation, (Plano, Texas) All International Rights Reserved.

**LINEAGE POWER** 23 Document No: DS10-008 ver. 1.12

PDF name: PVX012A0X.pdf

<sup>\*</sup>Please contact Lineage Power for more information