# **CXA3541N**

# 2-channel Read/Write Amplifier for GMR-Ind Head Hard Disk Drive

### **Description**

The CXA3541N is a read/write amplifier for GMR-Ind (Giant Magneto Resistive-Inductive) heads used in hard disk drives, and is capable of supporting up to two channels.

#### **Features**

- +5V and -3V power supply

- Current bias voltage sense type

- Low power 180mW at read

- Differential read amplifier gain;  $\times 100/135$  (RMR =  $50\Omega$ )

- Input noise of  $0.77 \text{nV}/\sqrt{\text{Hz}}$  (typ.), RMR =  $50\Omega$ , IB = 5.9 mA

- Recovery time write to read; 300ns (typ.)

- Write data is triggered by differential P-ECL signal

- · Servo bank write

- · Write unsafe detection circuit

- Serial port

Head selection

MR bias

Write current

#### **Applications**

Hard disk drives with GMR-Ind heads

#### Structure

Bipolar silicon monolithic IC

#### **Absolute Maximum Ratings** (Ta = 25°C)

| <ul> <li>Supply voltage</li> </ul>          | Vcc   | -0.3 to +5.8    | V     |

|---------------------------------------------|-------|-----------------|-------|

| <ul> <li>Supply voltage</li> </ul>          | VEE   | -3.7 to +0.3    | V     |

| <ul> <li>Digital input voltage</li> </ul>   | Vdi   | -0.3 to Vcc + 0 | .3 V  |

| <ul> <li>Operating temperature</li> </ul>   | Topr  | 0 to +70        | °C    |

| <ul> <li>Storage temperature</li> </ul>     | Tstg  | -55 to +150     | °C    |

| <ul> <li>Allowable power dissipa</li> </ul> | ation |                 |       |

|                                             | PD    | 800             | mW    |

|                                             |       | (on be          | oard) |

#### **Operating Conditions**

| <ul> <li>Supply voltage</li> </ul>  | Vcc      | 4.4 to 5.5   | V  |

|-------------------------------------|----------|--------------|----|

|                                     | VEE      | -3.5 to -2.6 | V  |

| <ul> <li>MR bias voltage</li> </ul> | $V_{MR}$ | -300 to +300 | m۷ |

| <ul> <li>Bias current</li> </ul>    | lв       | 3 to 8       | mΑ |

| <ul> <li>Write current</li> </ul>   | lw       | 19.5 to 49.5 | mΑ |

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

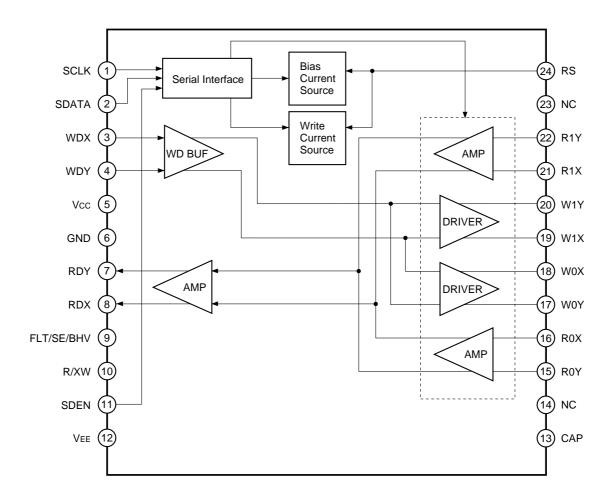

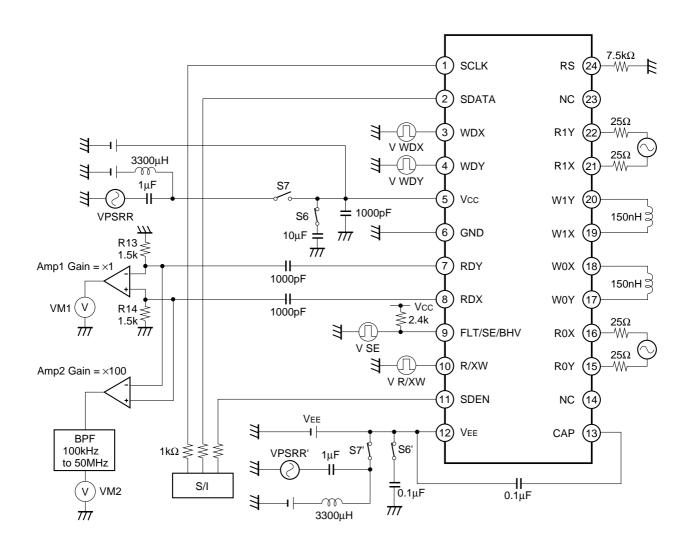

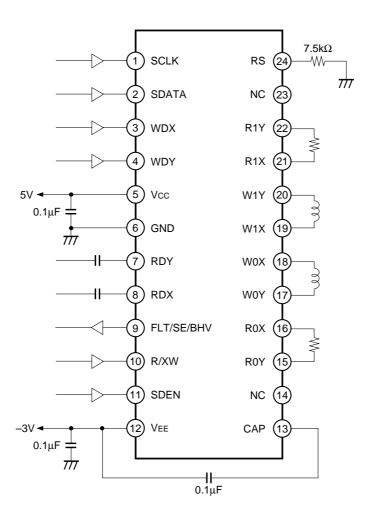

# **Block Diagram and Pin Configuration**

# **Pin Description**

| Pin<br>No.   | Symbol                | Equivalent circuit                          | Description                                                                                |

|--------------|-----------------------|---------------------------------------------|--------------------------------------------------------------------------------------------|

| 1<br>2<br>11 | SCLK<br>SDATA<br>SDEN | 7.5k 2 111 2 Vcc  Figure 14k Figure 2Vf GND | Serial control signal input.                                                               |

| 3 4          | WDX<br>WDY            | 3 Vcc Vcc Vcc Vcc Vcc Vcc Vcc Vcc Vcc Vc    | Differential P-ECL write data input.                                                       |

| 5            | Vcc                   |                                             | 5V power supply.                                                                           |

| 6            | GND                   |                                             | Ground.                                                                                    |

| 7 8          | RDY<br>RDX            | 7<br>8<br>1.8mA<br>GND                      | Read amplifier output with coupling capacitors. High impedance in the write mode.          |

| 9            | FLT/SE/BHV            | 9 Vcc GND                                   | Head unsafe detection output. Servo bank write enable input. Buffered head voltage output. |

| Pin<br>No.           | Symbol                   | Equivalent circuit                                         | Description                                                               |

|----------------------|--------------------------|------------------------------------------------------------|---------------------------------------------------------------------------|

| 10                   | R/XW                     | Vcc<br>3Vf<br>GND                                          | Read/write control signal input. Read when high, write when low.          |

| 12                   | VEE                      |                                                            | -3V power supply.                                                         |

| 13                   | CAP                      | Vcc Vcc Vcc Vcc Vcc Vcc                                    | Connect an external capacitor of read amplifier between this pin and VEE. |

| 14<br>23             | NC                       |                                                            | Non connection.                                                           |

| 16<br>15<br>21<br>22 | R0X<br>R0Y<br>R1X<br>R1Y | 16(21)<br>(15)(22)<br>VEE                                  | MR heads for read.<br>Two channels are provided.                          |

| 18<br>17<br>19<br>20 | W0X<br>W0Y<br>W1X<br>W1Y | (18) (19) (17) (20) (19) (19) (19) (19) (19) (19) (19) (19 | Inductive heads for write. Two channels are provided.                     |

| Pin<br>No. | Symbol | Equivalent circuit                    | Description                                                          |

|------------|--------|---------------------------------------|----------------------------------------------------------------------|

| 24         | RS     | Vcc<br>250<br>VBGR<br>T = 1.3V<br>GND | Bias current setting register is connected between this pin and GND. |

# **Electrical Characteristics**

(Unless otherwise specified; Vcc = 5V, Vee = -3V, Ta = 25°C, CAP =  $0.1\mu F$ , RS =  $7.5k\Omega$ )

| No.                                       | Item                                        | Symbol           | Measurement conditions                                                                                                                                       | Min.         | Тур.   | Max.         | Unit |  |

|-------------------------------------------|---------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------|--------------|------|--|

| Power Dissipation lw = 29.5mA, lb = 5.9mA |                                             |                  |                                                                                                                                                              | 1 7 %        | IVICA. |              |      |  |

| 1-1                                       | W = 20.011                                  | ISP1             | Sleep mode                                                                                                                                                   |              | 2.15   | 2.85         | mA   |  |

| 1-2                                       |                                             | I <sub>ID1</sub> | Idle mode                                                                                                                                                    |              | 22     | 29           | mA   |  |

| 1-3                                       | Vcc power supply current                    | IRE1             | Read mode                                                                                                                                                    |              | 37     | 48           | mA   |  |

| 1-4                                       |                                             | lwr1             | Write mode                                                                                                                                                   |              | 98     | 130          | mA   |  |

| 1-5                                       |                                             | I <sub>ID2</sub> | Idle mode                                                                                                                                                    |              | 10     | 13           | mA   |  |

| 1-7                                       | VEE power supply current                    | IRE2             | Read mode                                                                                                                                                    |              | 10     | 13           | mA   |  |

| 1-8                                       |                                             | lwR2             | Write mode                                                                                                                                                   |              | 10     | 13           | mA   |  |

| 1-9                                       | Bank write mode                             | Іссви            | $\begin{aligned} &\text{Iccbw} = 17 + 17 \times \text{N} + \text{Iw} \times \text{N} \\ &\text{Iw} = 29.5 \text{mA} \end{aligned}$                           | _            | 111    |              | mA   |  |

| Digit                                     | al Inputs                                   |                  |                                                                                                                                                              |              | •      | •            |      |  |

| 2-1                                       | TTL input<br>low input voltage              | VIL              | TTL input; R/XW                                                                                                                                              | 0            |        | 0.8          | V    |  |

| 2-2                                       | TTL input<br>high input voltage             | VIH              | Internal pull-up resistor                                                                                                                                    | 2.0          |        | Vcc<br>+ 0.3 | V    |  |

| 2-3                                       | TTL input input current                     | ITTL             | High voltage: 5V<br>Low voltage: 0V                                                                                                                          | -200         |        | 200          | μA   |  |

| 2-4                                       | Serial interface input low input voltage    | VsIL             | Serial input;                                                                                                                                                |              |        | 0.8          | V    |  |

| 2-5                                       | Serial interface input high input voltage   | VsiH             | SDATA, SCLK, SDEN                                                                                                                                            | 2.35         |        |              | V    |  |

| 2-6                                       | Serial interface input input current        | VsT              | High voltage: 3.3V<br>Low voltage: 0V<br>Pull-down resistor: 14kΩ                                                                                            | -500         |        | 500          | μA   |  |

| 3-1                                       | P-ECL common voltage                        | VPC              | (VH + VL)/2                                                                                                                                                  | 1.55         |        | Vcc          | V    |  |

| 3-2                                       | P-ECL differential voltage                  | VPD              | (VH – VL)                                                                                                                                                    | 0.2          |        | 1.5          | V    |  |

| 3-3                                       | P-ECL high voltage                          | Vрн              |                                                                                                                                                              |              |        | Vcc          | V    |  |

| 3-4                                       | P-ECL input current                         | <b>I</b> WD      | Input voltage: 4V                                                                                                                                            | -20          |        | 20           | μΑ   |  |

| Powe                                      | Power Dissipation   Iw = 29.5mA, IB = 5.9mA |                  |                                                                                                                                                              |              |        |              |      |  |

| 4-1                                       | Bank write enable voltage                   | Vseh             |                                                                                                                                                              | Vcc<br>+ 1.2 |        | Vcc<br>+ 1.4 | V    |  |

| 4-2                                       | Bank write enable current                   | Iseh             |                                                                                                                                                              | 6            |        | 14           | mA   |  |

| 5-1                                       | FLT output low voltage                      | VFLTL            | Open collector output External resistance = $2.4k\Omega$                                                                                                     |              |        | 0.8          | V    |  |

| 5-2                                       | FLT output high voltage                     | VFLTH            | Open collector output<br>External resistance = 2.4kΩ                                                                                                         | 4.5          |        |              | V    |  |

| 6                                         | BHV gain accuracy                           | Евну             | $\begin{aligned} \text{VBHV} &= \text{VCC} - 4 \times \text{IB} \times (\text{RMR} + 5.5\Omega) \\ \text{IB} &= "111", \text{ RMR} = 50\Omega \end{aligned}$ | -8           |        | 8            | %    |  |

| N.    | 14                                   | 0                        | NA                                                      | N 4" -     | т     | N/A s | 1.1                                  |

|-------|--------------------------------------|--------------------------|---------------------------------------------------------|------------|-------|-------|--------------------------------------|

| No.   | Item                                 | Symbol                   | Measurement conditions                                  | Min.       | Тур.  | Max.  | Unit                                 |

| Read  | Characteristics RMR = 5              | $50\Omega$ , $l_B = 5$ . |                                                         |            |       |       |                                      |

| R1    | Low gain                             | Avl                      | Gain = 0<br>RMR = $50\Omega$ , IB = $5.9$ mA            | 82         | 100   | 118   | V/V                                  |

| R2    | High gain                            | А∨н                      | Gain = 1<br>RMR = $50\Omega$ , IB = $5.9$ mA            | 110        | 135   | 160   | V/V                                  |

| R3    | Low frequency cut-off (–3dB)         | FcL                      |                                                         |            | 350   | 550   | kHz                                  |

| R4    | High frequency cut-off (–3dB)        | Fсн                      |                                                         | 140        | 200   |       | MHz                                  |

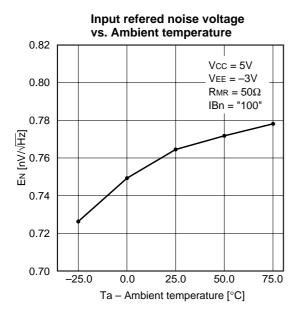

| R5    | Input reflected noise                | Eni                      | Exclusive of head noise RMR = $50\Omega$ , IB = $5.9mA$ |            | 0.77  | 0.95  | $\frac{\text{nV}}{\sqrt{\text{Hz}}}$ |

| R6    | MR bias current range 1              | BR1                      |                                                         | 3          |       | 8     | mA                                   |

| R7    | MR bias accuracy                     | Еів                      |                                                         | -7         |       | +7    | %                                    |

| R8    | MR bias resolution                   | Rıв                      | 3-bit DAC                                               |            | 0.714 | _     | mA                                   |

| R9-1  | Vcc power supply rejection ratio     | PSRR1                    | Ripple voltage: 100mVp-p<br>100kHz to 50MHz             | 38         |       |       | dB                                   |

| R9-2  | VEE power supply rejection ratio     | PSRR2                    | Ripple voltage: 100mVp-p<br>100kHz to 10MHz             | 45         |       |       | dB                                   |

| R10-1 | Common mode rejection ratio 1        | CMRR1                    | Ripple voltage: 100mVp-p<br>100kHz to 50MHz             | 37         |       |       | dB                                   |

| R10-2 | Common mode rejection ratio 2        | CMRR2                    | Ripple voltage: 100mVp-p<br>51MHz to 80MHz              | 27         |       |       | dB                                   |

| R11   | Control line input noise rejection   | CLRR                     | Ripple voltage: 100mVp-p<br>4MHz to 80MHz               | 40         |       |       | dB                                   |

| R12   | RDX/RDY offset difference magnitude  | Voff1                    | Write to read                                           |            |       | 50    | mV                                   |

| R13   | RDX/RDY output impedance             | RDro                     | Differential, read mode                                 | 30         |       | 100   | Ω                                    |

| Read  | Safety Characteristics               |                          |                                                         |            |       |       |                                      |

| P1    | MR head open threshold               | MRop                     | Head X – Head Y                                         | 600        | 750   | 900   | mV                                   |

| P2    | MR head short threshold              | MRsh                     | Head X – Head Y<br>I <sub>B</sub> = "000" to "011"      | 15         | 50    | 90    | mV                                   |

| Write | Characteristics                      |                          |                                                         |            |       |       |                                      |

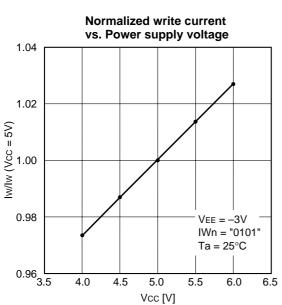

| W1    | Write current range                  | Iwr                      | DAC code = x "0000" to x "1111"                         | 19.5       |       | 49.5  | mA                                   |

| W2    | Write current accuracy               | Eıw                      | $R_H = 0\Omega$                                         | <b>–</b> 7 |       | +7    | %                                    |

| W3    | Write current resolution             | Rıw                      | 4-bit DAC                                               |            | 2     |       | mA                                   |

| W4    | Leakage current                      | ILEAK                    | Unselected head                                         |            |       | 200   | μΑ                                   |

| W6    | Damping resistor                     | Rd                       |                                                         | 800        | 1000  | 1200  | Ω                                    |

| W7    | Write current propagation delay time | Tpd                      | Lн = 0, Rн = 0<br>Write data to 50% of write current    |            |       | 10    | ns                                   |

| W8    | Write current rise/fall time         | Tr/Tf                    | $R_H = 15\Omega$ , $L_H = 150$ nH, $I_W = 25$ mA        |            | 1.9   |       | ns                                   |

| W9    | Erase current accuracy               | EIE                      | Vcc = 3.5V<br>DAC code = x "0101"                       | -18        | -9    | 0     | %                                    |

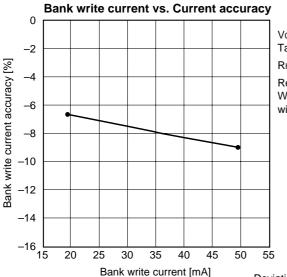

| W10   | Bank write current accuracy          |                          | Refer to Fig.                                           |            |       |       |                                      |

| No.   | Item                                | Symbol               | Measurement conditions                       | Min. | Тур. | Max.        | Unit |

|-------|-------------------------------------|----------------------|----------------------------------------------|------|------|-------------|------|

| Write | Safety Characteristics              |                      |                                              |      |      |             | ı    |

| U1    | Write head open threshold           | Rop                  | Detect open head                             |      | 1.2  | 1.4         | V    |

| U2    | Head voltage when short to GND      | Vg                   | Detect short to GND                          |      |      | 0.1         | ٧    |

| U3    | WD frequency too low                | fwdL                 |                                              | 0.5  |      | 1.8         | MHz  |

| U4    | Write safety detect time            | Tws                  | T1: 2 transitions on WDX/WDY                 |      |      | 300<br>+ T1 | ns   |

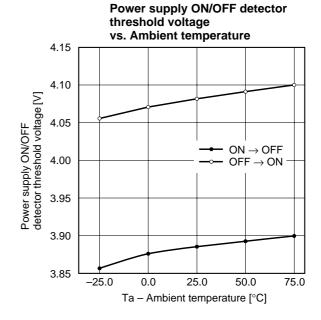

| U5    | Low Vcc threshold                   | VWthL                | Fault detected                               | 3.7  | 3.9  | 4.1         | V    |

| U6    | Low Vcc threshold                   | VWthH                | Fault removed                                | 3.9  | 4.1  | 4.3         | V    |

| U7    | Low Vcc threshold hysteresis        | Vhys                 |                                              |      | 200  |             | mV   |

| Swite | ching Characteristics   lw =        | 29.5mA, Ів =         | = 5.9mA                                      |      |      |             |      |

| S1    | Write to Read                       | Twr                  | Signal on WDX/WDY<br>90% RD signal or 10% lw |      | 300  | 500         | ns   |

| S2    | Read to Write                       | TRW                  | 90% lw                                       |      | 50   | 70          | ns   |

| S3    | Idle to Read                        | Tır                  | 90% RD signal                                |      |      | 1.0         | μs   |

| S4    | Sleep to Read                       | Tsr1                 | 90% RD signal, 90% Ib*1<br>IB = "011"        |      | 600  | 2000        | μs   |

| Bank  | Write Characteristics lw =          | = 29.5mA, <b>І</b> в | = 5.9mA                                      |      | •    |             |      |

| S5    | Read to Bank write                  | Ткв                  | 90% lw                                       |      |      | 100         | ns   |

| S6    | Bank write to Read                  | T <sub>BR</sub>      | 10% lw                                       |      |      | 100         | ns   |

| S7    | Idle to Bank write<br>Idle to Write | Tıw                  | 90% lw                                       |      |      | 300         | μs   |

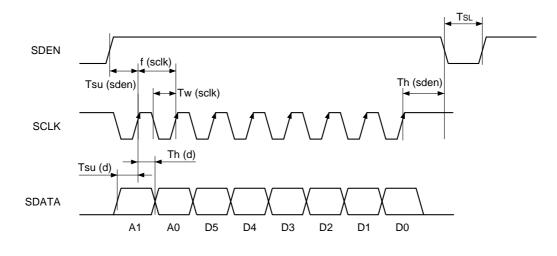

| Seria | I Port Timing                       |                      |                                              |      |      |             |      |

| B1    | Setup time                          | Tsu (sden)           | SDEN to first SCLK                           | 30   |      |             | ns   |

| B2    | Hold time                           | Th (sden)            | Last SCLK to deassert SDEN                   | 15   |      |             | ns   |

| B4    | SCLK frequency                      | f (sclk)             |                                              |      |      | 30          | MHz  |

| B5    | SCLK pulse width                    | Tw (sclk)            |                                              | 10   |      |             | ns   |

| B6    | SCLK – SDATA setup time             | Tsu (d)              |                                              | 10   |      |             | ns   |

| B7    | SCLK – SDATA hold time              | Th (d)               |                                              | 10   |      |             | ns   |

| B8    | SDEN low time                       | TsL                  |                                              | 100  |      |             | ns   |

$<sup>^{*\</sup>mbox{\scriptsize 1}}$  Tsr is proportional to IB and external CAP value.

# **Serial Port Characteristics**

| ADR1 | ADR0 | DATA5 | DATA4 | DATA3 | DATA2 | DATA1 | DATA0 |

|------|------|-------|-------|-------|-------|-------|-------|

| 0    | 0    | XSLP  | XIDL  | N/A   | N/A   | N/A   | HS    |

| 0    | 1    | GAIN  | BHV   | N/A   | IB2   | IB1   | IB0   |

| 1    | 0    | MROPN | MRSHT | IW3   | IW2   | IW1   | IW0   |

$<sup>\</sup>ensuremath{^{*}}$  IB[2:0] bits are initialized by "0" at power on.

# **Code Description**

| Bit     | Function                                                                                 |

|---------|------------------------------------------------------------------------------------------|

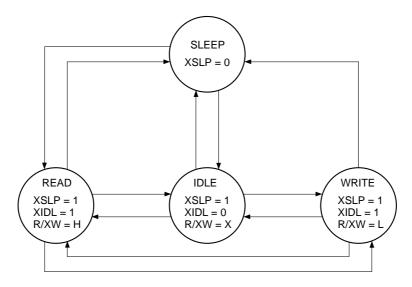

| XSLP    | 0 = Set the pre-amplifier into low power "sleep" mode.                                   |

| XIDL    | 0 = Set pre-amplifier to idle mode.                                                      |

| HS      | Head select bit.                                                                         |

| GAIN    | Set the pre-amplifier to high or low gain mode. 1 = Set pre-amplifier to high gain mode. |

| BHV     | Active the BHV test point pin. "1" active.                                               |

| IB[2:0] | MR bias current set.                                                                     |

| MROPN   | 1 = Set MR head open detector active.                                                    |

| MRSHT   | 1 = Set MR head short detector active.                                                   |

| IW[3:0] | Set write current.                                                                       |

#### **Mode Control**

# **Serial Port Timing Detail**

**Serial Port Timing**

After the SDEN goes high, the last eight bits are transferred into the register. The SCLK will shift the data presented at SDATA into an internal shift register on the rising edge of each clock.

As SCLK initial condition, both of low and high signal is acceptable.

#### **Unsafe Condition**

1. Write fault condition

FLT is a high level in write fault condition.

- Open write head leads. fwp < 15MHz

- Write head leads shorted to ground.

- WD frequency is too low.

- Power supply is out of tolerance.

- 2. Read fault condition

FLT is a low level in read fault condition.

• Open short MR head. (This function is set by serial resister.)

#### Bank Write Control (Refer to Bank "Write current vs. Current accuracy" characteristic curve)

- 1. Set the read mode.

- 2. Force a certain voltage (min. Vcc + 1.2V) to FLT/SE pin by using the pull-up register. (RsE = 820 $\Omega$ ) #This operation disables all fault detection.

- 3. Set Vcc at 3.5V (in case of the erase mode only)

- 4. Start the write operation by setting R/XW = L.

- 5. Terminate the write operation by setting R/XW = H.

- i) Allow 50% write duty or less.

- ii) Low voltage detector is disabled in the bank write mode and erase mode.

- iii) Don't change the serial register data bits in following conditions:

- Vcc = 3.5V

- On entering write data.

#### **BHV (Buffered Head Voltage)**

- 1. Applicable within  $Vcc = 5V \pm 5\%$ .

- 2. Turn BHV on, but turn off MROPN and MRSHT.

- 3. VBHV is determined by basis of Vcc. VBHV = Vcc  $(4 \times IB \times (RMR + 5.5\Omega))$

#### **Head Condition**

- 1. Short X-Y terminal on un-used write head.

- 2. Recommended X-Y terminal on un-used read head short.

#### **Polarity**

- 1. Read output signal on RDX is negative, when MRX is positive by increasing RMR.

- 2. Write current flows into X side, when WDX is high and WDY is low.

#### **Head Select Table**

#### (2ch)

| HS | Normal operation |

|----|------------------|

| 0  | 0                |

| 1  | 1                |

# **MR Bias**

| IB2 | IB1 | IB0 | Iв [mA] |

|-----|-----|-----|---------|

| 0   | 0   | 0   | 3.0     |

| 0   | 0   | 1   | 3.714   |

| 0   | 1   | 0   | 4.429   |

| 0   | 1   | 1   | 5.143   |

| 1   | 0   | 0   | 5.857   |

| 1   | 0   | 1   | 6.571   |

| 1   | 1   | 0   | 7.286   |

| 1   | 1   | 1   | 8.0     |

# **Write Current**

| IW3 | IW2 | IW1 | IWO | Write current<br>[mA <sub>0-P</sub> ] |

|-----|-----|-----|-----|---------------------------------------|

| 0   | 0   | 0   | 0   | 19.5                                  |

| 0   | 0   | 0   | 1   | 21.5                                  |

| 0   | 0   | 1   | 0   | 23.5                                  |

| 0   | 0   | 1   | 1   | 25.5                                  |

| 0   | 1   | 0   | 0   | 27.5                                  |

| 0   | 1   | 0   | 1   | 29.5                                  |

| 0   | 1   | 1   | 0   | 31.5                                  |

| 0   | 1   | 1   | 1   | 33.5                                  |

| 1   | 0   | 0   | 0   | 35.5                                  |

| 1   | 0   | 0   | 1   | 37.5                                  |

| 1   | 0   | 1   | 0   | 39.5                                  |

| 1   | 0   | 1   | 1   | 41.5                                  |

| 1   | 1   | 0   | 0   | 43.5                                  |

| 1   | 1   | 0   | 1   | 45.5                                  |

| 1   | 1   | 1   | 0   | 47.5                                  |

| 1   | 1   | 1   | 1   | 49.5                                  |

Actual head current is defined by the following equation:

IHEAD = IW/(1 + RH/RD)

Rн: Head resistance Rp: Damping resistance

#### **Electrical Characteristics Measurement Circuit**

# **Application Circuit**

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

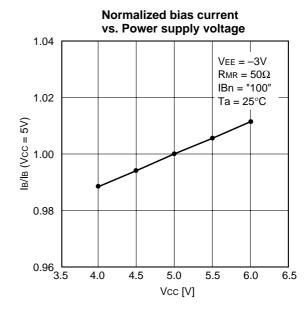

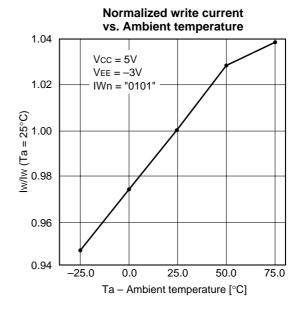

# Normalized bias current vs. Ambient temperature 1.04 Vcc = 5VVEE = -3V $\mathsf{RMR} = 50\Omega$ 1.02 IBn = "100" IB/IB (Ta = 25°C) 1.00 0.98 0.96 -25.0 0.0 25.0 50.0 75.0 Ta – Ambient temperature [°C]

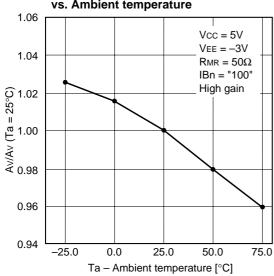

# Normalized read amplifier voltage gain vs. Ambient temperature

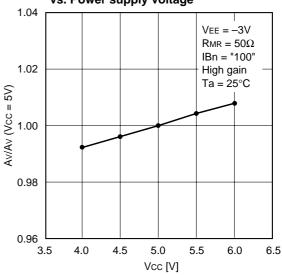

# Normalized read amplifier voltage gain vs. Power supply voltage

Vcc = 5V Ta = 25°C RH =  $0\Omega$  Read 170 $\mu$ s Write 30 $\mu$ s with Write Data

Deviation of bank write current is within  $\pm$  7% at basis of the chart.

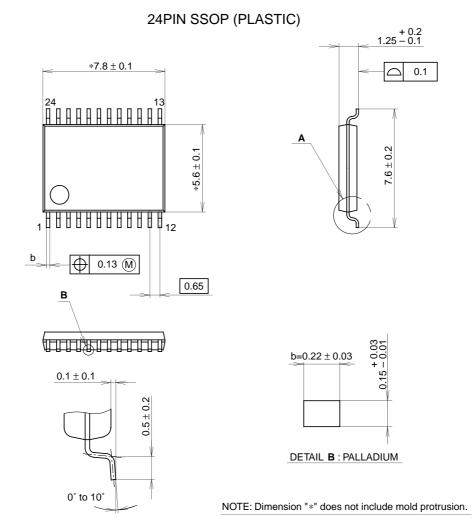

# Package Outline

#### Unit: mm

DETAIL A

| SONY CODE  | SSOP-24P-L01          |

|------------|-----------------------|

| EIAJ CODE  | P-SSOP24-7.8x5.6-0.65 |

| JEDEC CODE |                       |

# PACKAGE STRUCTURE

| PACKAGE MATERIAL | EPOXY RESIN       |

|------------------|-------------------|

| LEAD TREATMENT   | PALLADIUM PLATING |

| LEAD MATERIAL    | COPPER ALLOY      |

| PACKAGE MASS     | 0.1g              |