# TDA7535

## DELTA/SIGMA CASCADE 20 BIT STEREO DAC

- 20-bit resolution single ended output

- Analog reconstruction third order Chebyshev filter

- I<sup>2</sup>S input data format

- On chip PLL

- System clock: 64 Fs

- 2 output channels

- 0.9 VRMS single ended output dynamic

- 3.3V power supply

- Reset

- Sampling rate 36KHz to 48KHz

#### DESCRIPTION

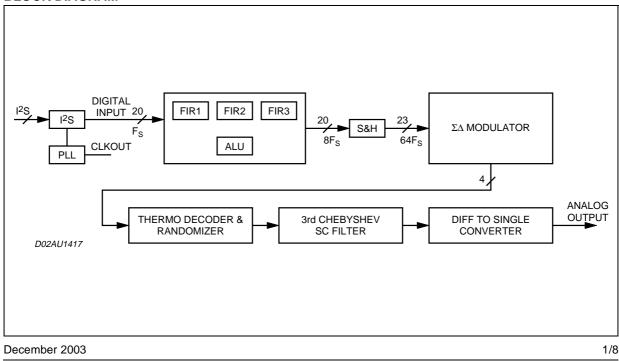

The TDA7535 is a stereo, digital-to-analog converter designed for audio application, including digital interpolation filter, a third order multibit Delta-Sigma DAC, a third order Chebyshev's reconstruction filter and a differential to single ended output converter. This device is fabricated in highly advanced CMOS, where high speed precision analog circuits are combined with high density logic circuits. The TDA7535, according to standard audio converters, can accept any  $I^2S$  data format.

#### **BLOCK DIAGRAM**

The TDA7535 is available in SO-14 package. The total power consumption is less than 75mW.

TDA7535 is suitable for a wide variety of applications where high performance are required. Its low cost and single 3.3V power supply make it ideal for several applications, such as CD players, MPEG audio, MIDI applications, CD-ROM drives, CD-Interactive, digital radio applications and so on. An evaluation board is available to perform measurement and to make listening tests.

#### TDA7535

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                             | Parameter                            | Value                          | Unit   |

|------------------------------------|--------------------------------------|--------------------------------|--------|

| V <sub>DD</sub><br>V <sub>CC</sub> | Power supplies Digital Analog        | -0.5 to +4.6<br>-0.5 to +4.6   | V<br>V |

| Vaio                               | Analog Input and Output Voltage      | -0.5 to (V <sub>CC</sub> +0.5) | V      |

| V <sub>dio</sub>                   | Digital Input and Output Voltage     | -0.5 to (V <sub>DD</sub> +0.5) | V      |

| V <sub>di5</sub>                   | Digital Input Voltage (5V tolerant)  | -0.5 to 6.5                    | V      |

| Tj                                 | Operating Junction Temperature Range | -40 to 125                     | °C     |

| T <sub>stg</sub>                   | Storage Temperature                  | -55 to 150                     | °C     |

Warning: Operation at or beyond these limit may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

#### THERMAL DATA

| Symbol                | Parameter                                             | Value | Unit |

|-----------------------|-------------------------------------------------------|-------|------|

| R <sub>th j-amb</sub> | Thermal resistance junction to ambient <sup>(1)</sup> | 85    | °C/W |

Note: 1. In still air

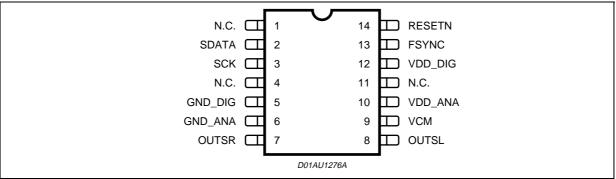

#### **PIN CONNECTIONS (Top view)**

#### **PIN FUNCTION**

| Pin Number | Pin Name | Input/Output Power | Description                         |

|------------|----------|--------------------|-------------------------------------|

| 1          | N.C.     | -                  | -                                   |

| 2          | SDATA    | I                  | I2S Digital Data Input              |

| 3          | SCK      | I                  | I2S Clock Input                     |

| 4          | N.C.     | -                  | -                                   |

| 5          | GND_DIG  | Р                  | Digital Ground                      |

| 6          | GND_ANA  | Р                  | Analog Ground                       |

| 7          | OUTSR    | 0                  | Right Channel single ended Output   |

| 8          | OUTSL    | 0                  | Left Channel single ended Output    |

| 9          | VCM      | Р                  | Reference 1.65V externally filtered |

| 10         | VDD_ANA  | Р                  | Analog 3.3V-Supply                  |

| 11         | N.C.     | -                  | -                                   |

| 12         | VDD_DIG  | Р                  | Digital 3.3V-Supply                 |

| 13         | FSYNC    | I                  | I2S Left-Right Channel selector     |

| 14         | RESETN   | Ι                  | Reset (active low)                  |

57

#### **RECOMMENDED DC OPERATING CONDITIONS**

| Symbol          | Parameter                            | Test Condition | Min. | Тур. | Max. | Unit |

|-----------------|--------------------------------------|----------------|------|------|------|------|

| V <sub>DD</sub> | 3.3V Digital Power Supply<br>Voltage |                | 3.15 | 3.3  | 3.45 | V    |

| V <sub>CC</sub> | 3.3V Analog Power Supply Voltage     |                | 3.15 | 3.3  | 3.45 | V    |

#### POWER CONSUMPTION

| Ī | Symbol          | Parameter             | Test Condition                               | Min. | Тур. | Max. | Unit |

|---|-----------------|-----------------------|----------------------------------------------|------|------|------|------|

| Ī | l <sub>dd</sub> | Total Maximum Current | power supply @ 3.3V and $T_j = 125^{\circ}C$ |      | 21.5 | 25   | mA   |

#### **GENERAL INTERFACE ELECTRICAL CHARACTERISTICS**

| Symbol               | Parameter                                        | Test Condition                            | Min. | Тур. | Max. | Unit |

|----------------------|--------------------------------------------------|-------------------------------------------|------|------|------|------|

| l <sub>il</sub>      | Low Level Input Current without<br>pullup device | V <sub>i</sub> = 0V (note 1)              |      |      | 1    | μΑ   |

| l <sub>ih</sub>      | High Level Input Current without pullup device   | V <sub>i</sub> = V <sub>dd</sub> (note 1) |      |      | 1    | μΑ   |

| I <sub>latchup</sub> | I/O latch-up current                             | $V < 0V, V > V_{dd}$                      | 200  |      |      | mA   |

| V <sub>esd</sub>     | Electrostatic Protection                         | Leakage , 1µA (note 2)                    | 2000 |      |      | V    |

Note: 1. The leakage currents are generally very small, <1nA. The value given here, 1mA, is the maximum that can occur after an Electrostatic Stress on the pin.

2. Human Body Model.

#### LOW VOLTAGE CMOS INTERFACE DC ELECTRICAL CHARACTERISTICS

| Symbol            | Parameter                  | Test Condition | Min.                | Тур. | Max.                | Unit |

|-------------------|----------------------------|----------------|---------------------|------|---------------------|------|

| Vil               | Low Level Input Voltage    |                |                     |      | 0.2*V <sub>dd</sub> | V    |

| Vih               | High Level Input Voltage   |                | 0.8*V <sub>dd</sub> |      |                     | V    |

| V <sub>hyst</sub> | Schmitt trigger hysteresis |                | 0.8                 |      |                     | V    |

#### DAC ELECTRICAL CHARACTERISTICS

Vdd = 3.3V; Tamb = 25°C; Input signal frequency = sinus wave generated by Audio Precision Sys.2; Input Signal Amplitude = see notes; Noise Integration Bandwidth = 20Hz to 22KHz (A- weighted)

| Parameter                 | Test Condition                                      | Min. | Тур. | Max. | Unit |

|---------------------------|-----------------------------------------------------|------|------|------|------|

| Noise + Distortion        | @0dB                                                |      | 89   |      | dB   |

| (see note 1)              | @-6dBb                                              |      | 94   |      | dB   |

|                           | @-40dB                                              |      | 96   |      | dB   |

|                           | @-60dB                                              |      | 96   |      | dB   |

| Total Harmonic Distortion | see note 2                                          |      | 94   |      | dB   |

| Dynamic range             | see note 3                                          |      | 96   |      | dB   |

| Crosstalk                 | see note 4                                          |      | -95  |      | dB   |

| Full Scale Output Voltage | V <sub>dd</sub> = 3.15 to 3.45V<br>Full scale input | 0.8  | 0.9  | 1.0  | Vrms |

| Input Sampling Rate       |                                                     | 36   |      | 48   | kHz  |

57

#### DAC ELECTRICAL CHARACTERISTICS (continued)

Vdd = 3.3V; Tamb = 25°C; Input signal frequency = sinus wave generated by Audio Precision Sys.2; Input Signal Amplitude = see notes; Noise Integration Bandwidth = 20Hz to 22KHz (A- weighted)

| Parameter                  | Test Condition                                                       | Min.  | Тур. | Max.  | Unit |

|----------------------------|----------------------------------------------------------------------|-------|------|-------|------|

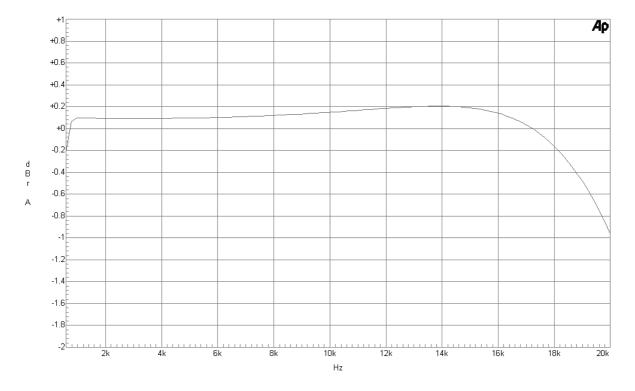

| Passband Ripple            |                                                                      |       | 0.12 |       | dB   |

| Stopband                   | <ul><li>@ 3dB</li><li>@ 90dB</li><li>44.1kHz Sampling Rate</li></ul> | 21.53 |      | 24.80 | kHz  |

| Interchannel Gain Mismatch |                                                                      |       | 0.05 | 0.1   | dB   |

Note1: It is the ratio between the maximum input signal and the integration of the in-band noise after deducing the power of signal fundamental. It depends on the input signal amplitude. In this case 0dB means full scale digital, 1kHz frequency used.

Note 2: It is the ratio of the rms value of the signal fundamental component at 0dB (full scale digital) to the rms value of all of the harmonic components in the band.

Note 3: measured using the SNR at -60dB input signal, with 60dB added to compensate for small input signal.

Note 4: Left channel on with 0dB/1kHz input signal, Right channel on with DC input signal.

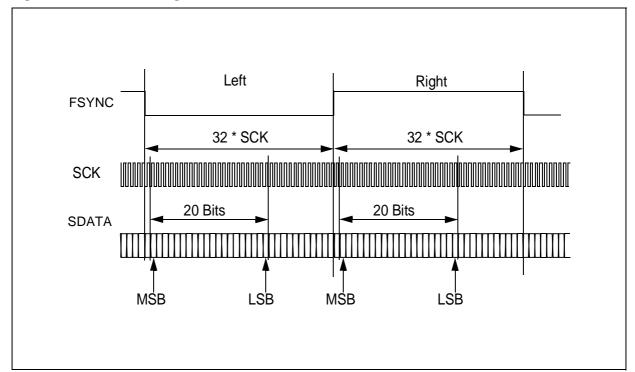

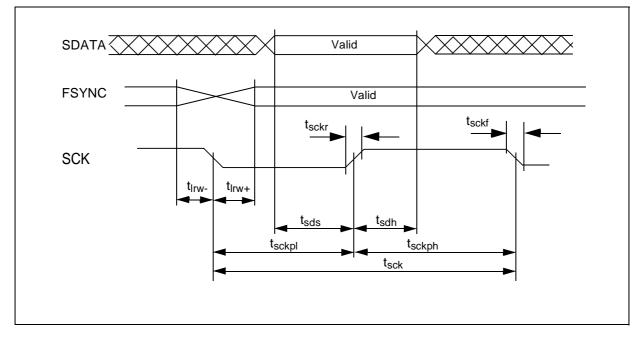

#### Figure 1. I<sup>2</sup>S interface Diagram

### Figure 2. I<sup>2</sup>S Timings

| Timing             | Description                                                        | Minimum                             | Maximum                             | Unit |

|--------------------|--------------------------------------------------------------------|-------------------------------------|-------------------------------------|------|

| t <sub>sck</sub>   | Clock Cycle <sup>(1)</sup>                                         | 1/(64*Fs) -<br>150ps <sub>RMS</sub> | 1/(64*Fs) +<br>150ps <sub>RMS</sub> | ns   |

| t <sub>sckpl</sub> | SCK Phase Low                                                      | 0.5*t <sub>sck</sub> - 1%           | 0.5*t <sub>sck</sub> +1%            | ns   |

| t <sub>sckph</sub> | SCK Phase High                                                     | 0.5*t <sub>sck</sub> - 1%           | 0.5*t <sub>sck</sub> +1%            | ns   |

| t <sub>Irw-</sub>  | FSYNC switching time window before SCK falling edge <sup>(2)</sup> | 0                                   | 0.125*t <sub>sck</sub> -10          | ns   |

| t <sub>Irw+</sub>  | FSYNC switching time window after SCK falling edge <sup>(2)</sup>  | 0                                   | 0.125*t <sub>sck</sub> -10          | ns   |

| t <sub>sds</sub>   | SDATA setup time                                                   | 60                                  |                                     | ns   |

| t <sub>sdh</sub>   | SDATA hold time                                                    | 30                                  |                                     | ns   |

| t <sub>sckr</sub>  | SCK rise time                                                      |                                     | 1.5                                 | ns   |

| t <sub>sckf</sub>  | SCK fall time                                                      |                                     | 1.5                                 | ns   |

SCK clock defines the Fs, being the Sample Rate. This input clock needs a jitter below ~212ps<sub>RMS</sub>

FSYNC switches inside the time window as specified w.r.t. to falling edge of SCK

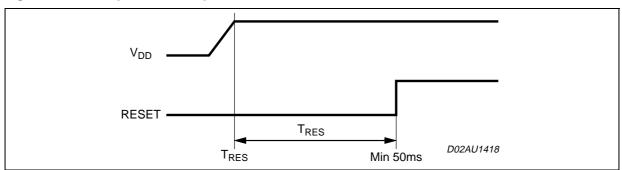

### Figure 3. Power Up & Reset Sequence

$I^2S$  bit clock (SCK) must be present 20ms before reset release to allow PLL locking.

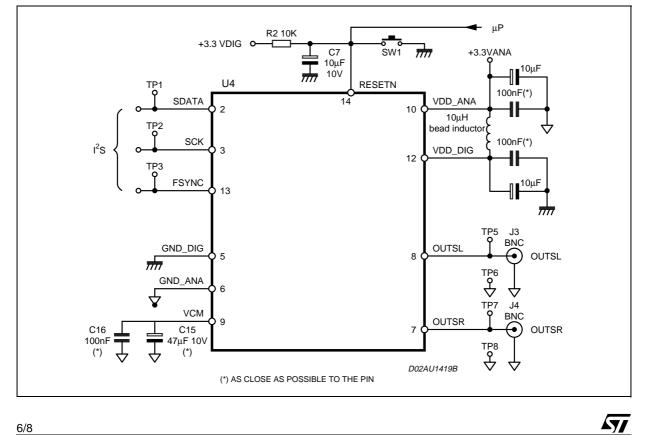

Figure 5.

6/8

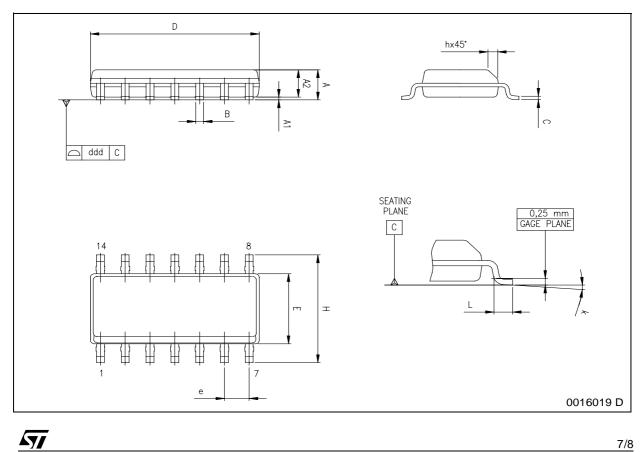

| DIM.             | mm   |            |                        | inch    |       |       |  |

|------------------|------|------------|------------------------|---------|-------|-------|--|

| Dilvi.           | MIN. | TYP.       | MAX.                   | MIN.    | TYP.  | MAX.  |  |

| А                | 1.35 |            | 1.75                   | 0.053   |       | 0.069 |  |

| A1               | 0.10 |            | 0.30                   | 0.004   |       | 0.012 |  |

| A2               | 1.10 |            | 1.65                   | 0.043   |       | 0.065 |  |

| В                | 0.33 |            | 0.51                   | 0.013   |       | 0.020 |  |

| С                | 0.19 |            | 0.25                   | 0.007   |       | 0.01  |  |

| D <sup>(1)</sup> | 8.55 |            | 8.75                   | 0.337   |       | 0.344 |  |

| Е                | 3.80 |            | 4.0                    | 0.150   |       | 0.157 |  |

| е                |      | 1.27       |                        |         | 0.050 |       |  |

| Н                | 5.8  |            | 6.20                   | 0.228   |       | 0.244 |  |

| h                | 0.25 |            | 0.50                   | 0.01    |       | 0.02  |  |

| L                | 0.40 |            | 1.27                   | 0.016   |       | 0.050 |  |

| k                |      | 0          | ° (min.),              | 8° (max | .)    |       |  |

| ddd              |      |            | 0.10                   |         |       | 0.004 |  |

| burr             |      | ash, protu | include m<br>usions or |         |       |       |  |

OUTLINE AND

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners

© 2003 STMicroelectronics - All rights reserved

#### STMicroelectronics GROUP OF COMPANIES

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States

www.st.com