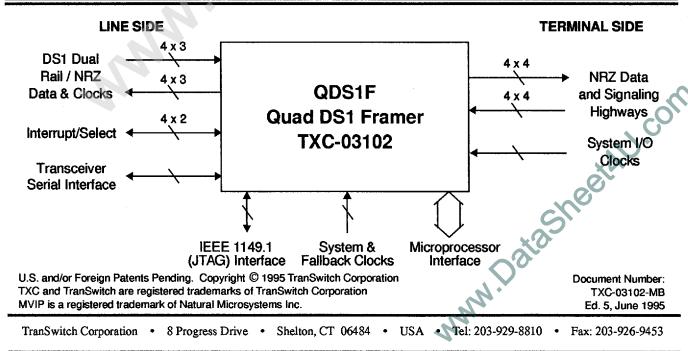

# QDS1F Device QUAD DS1 Framer TXC-03102

# DATA SHEET

Preliminary

### **DESCRIPTION E**

The QDS1F is a 4-channel DS1 (1.544 Mbit/s) framer designed for voice and data communications applications. AMI, B8ZS, and NRZ line codes are supported with full alarm detection and generation per ANSI T1M1.3. The transmit and receive sections of each of the four framers are independent, with individual slip buffers to allow operation in a wide range of switching and transmission products. D4 SF and ESF modes are provided per ANSI T1.403 - 1989 and AT&T PUB 62411, with per DS0 signaling and DS0 data access and control via a Motorola/Intel-compatible microprocessor. For ESF applications, each framer supplies a full duplex HDLC/ bit-oriented message controller in addition to on-board latching of all required performance parameters; minimal software overhead is required to support either ANSI T1.403-1989 or AT&T PUB 54016 protocols. Diagnostic, test, and maintenance functions are provided, including loopbacks and boundary scan (IEEE 1149.1).

# APPLICATIONS =

- SONET/SDH terminal or add/drop multiplexers supporting DS1 byte synchronous operation

- · DCS, digital central office or remote digital terminals

- T1 multiplexers

- T1 and fractional T1 CSUs

- ATM products with integrated DS1 interfaces

- LAN routers with integrated DS1 interfaces

- Multichannel DS1 test equipment

# D4 SF, ESF (including FDL support), and transparent framing modes

FEATURES

Encodes/decodes AMI/B8ZS and forced ones density line codes

Two frame slip buffers in both receive and transmit directions

- Supports channel-associated and robbed-bit signaling (enabled or processor forced on a per DS0 basis)

- Detects and forces yellow and AIS alarms; detects OOF, SEF, and change of frame alignment

- Detects, counts and forces line code errors (BPVs and excess zeros), CRC errors (ESF only), and frame bit errors

- Motorola/Intel compatible microprocessor interface

- One-second interrupt input latches counter values and line events into shadow registers

- · Local, line remote, and payload remote loopback

- Processor forcing/monitoring of DS0s for maintenance purposes

- Boundary scan capability (IEEE 1149.1)

- · 128-pin plastic quad flat package

# TABLE OF CONTENTS

| Section P                                                   | age |

|-------------------------------------------------------------|-----|

| Quad DS1 Framer Features                                    | 3   |

| Block Diagram                                               | 5   |

| Block Diagram Description                                   | 6   |

| Microprocessor Input/Output Interface Block                 | 6   |

| Line Interface Control and DS1 Monitor                      | 7   |

| Pseudo-Random Binary Sequence (PRBS) Generator and Analyzer | 8   |

| Overview of the Receive and Transmit Paths                  |     |

| Per Channel (Framer) Block Operation                        |     |

| Test Access Port                                            |     |

| Pin Diagram                                                 | 27  |

| Pin Descriptions                                            | 28  |

| Absolute Maximum Ratings                                    | 34  |

| Thermal Characteristics                                     | 34  |

| Power Requirements                                          | 34  |

| Input, Output and I/O Parameters                            | 35  |

| Timing Characteristics                                      |     |

| Memory Map                                                  | 52  |

| Memory Map Descriptions                                     | 59  |

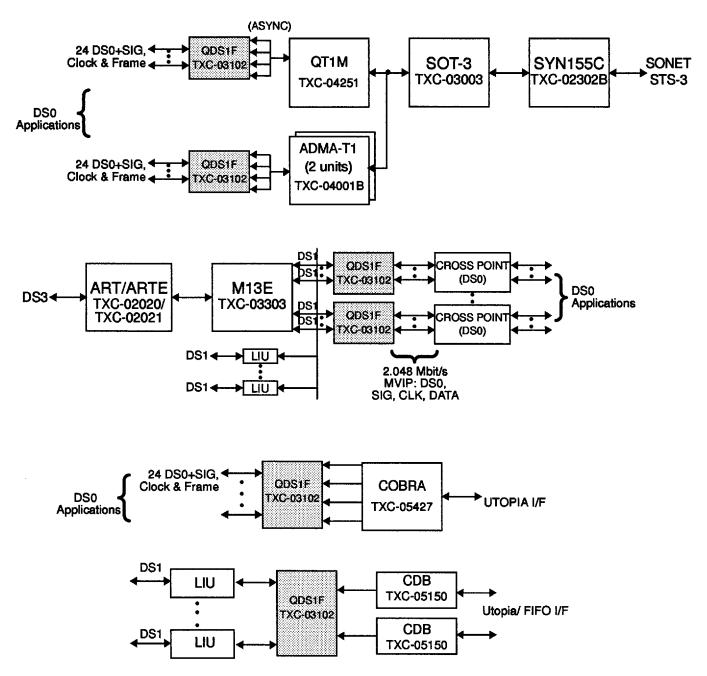

| Application Diagram                                         | 88  |

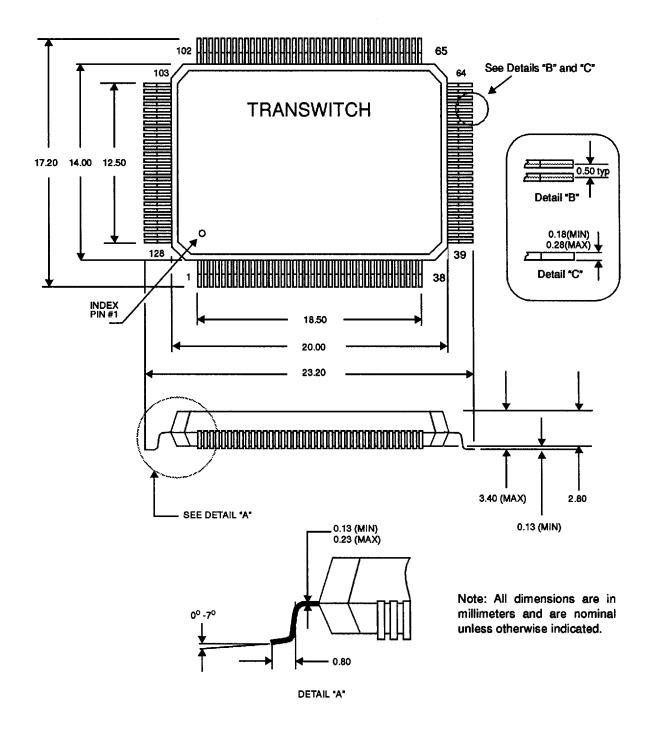

| Package Information                                         | 89  |

| Ordering Information                                        | 90  |

| Related Products                                            | 90  |

| Standards Documentation Sources                             | 92  |

| List of Data Sheet Changes                                  | 93  |

| Documentation Update Registration Form                      | 97  |

#### **LIST OF FIGURES**

| Figure 2.       Serial Interface Operation         Figure 3.       System Interface Transmit Framing Format for Transmission Mode         Figure 4.       System Interface Transmit Signaling Format for Transmission Mode         Figure 5.       System Interface Receive Signaling Format for Transmission Mode         Figure 6.       System Interface Receive Signaling Format for Transmission Mode         Figure 7.       System Interface Receive Signaling Format for Transmission Mode         Figure 8.       System Interface Receive Format for MVIP Mode         Figure 9.       Loopbacks per Channel in QDS1F Device         Figure 10.       D4 SF Framing Structure         Figure 11.       ESF Framing Structure         Figure 12.       Boundary Scan Schematic         Figure 13.       QDS1F TXC-03102 Pin Diagram         Figure 14.       Recovered Clock and Switching Characteristics         Figure 15.       Transmit Clock and Data Switching Characteristics         Figure 16.       Serial Port Write Timing         Figure 17.       Serial Port Read Timing         Figure 21.       Intel Microprocessor Read Cycle Timing         Figure 22.       Motorola Microprocessor Read Cycle Timing         Figure 23.       System Interface Output (MVIP Mode)         Figure 24.       System Interface Output (MVIP Mode)                                | Figure 1.  | QDS1F TXC-03102 Block Diagram                                    | 5  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------------------------------------------------|----|

| Figure 4.       System Interface Transmit Signaling Format for Transmission Mode         Figure 5.       System Interface Receive Framing Format for Transmission Mode         Figure 6.       System Interface Receive Signaling Format for Transmission Mode         Figure 7.       System Interface Receive Signaling Format for Transmission Mode         Figure 8.       System Interface Transmit Format for MVIP Mode         Figure 9.       Loopbacks per Channel in QDS1F Device         Figure 10.       D4 SF Framing Structure         Figure 11.       ESF Framing Structure         Figure 12.       Boundary Scan Schematic         Figure 13.       QDS1F TXC-03102 Pin Diagram         Figure 14.       Recovered Clock and Data Switching Characteristics         Figure 15.       Transmit Clock and Data Switching Characteristics         Figure 16.       Serial Port Write Timing         Figure 17.       Serial Port Read Timing         Figure 18.       Intel Microprocessor Read Cycle Timing         Figure 20.       Motorola Microprocessor Write Cycle Timing         Figure 21.       Motorola Microprocessor Write Cycle Timing         Figure 22.       System Interface Output (MVIP Mode)         Figure 23.       System Interface Output (Transmission Mode / System Clock)         Figure 24.       System Interface Output (Transmission Mode / Sy | Figure 2.  | Serial Interface Operation                                       | 7  |

| Figure 5.       System Interface Receive Framing Format for Transmission Mode         Figure 6.       System Interface Receive Signaling Format for Transmission Mode         Figure 7.       System Interface Receive Signaling Format for Transmission Mode         Figure 8.       System Interface Receive Format for MVIP Mode         Figure 9.       Loopbacks per Channel in QDS1F Device         Figure 10.       D4 SF Framing Structure         Figure 11.       ESF Framing Structure         Figure 12.       Boundary Scan Schematic         Figure 13.       QDS1F TXC-03102 Pin Diagram         Figure 15.       Transmit Clock and Switching Characteristics         Figure 15.       Transmit Clock and Switching Characteristics         Figure 16.       Serial Port Write Timing         Figure 17.       Serial Port Read Timing         Figure 18.       Intel Microprocessor Read Cycle Timing         Figure 20.       Motorola Microprocessor Write Cycle Timing         Figure 21.       Motorola Microprocessor Write Cycle Timing         Figure 22.       System Interface Output (MVIP Mode)         Figure 23.       System Interface Output (MVIP Mode)         Figure 24.       System Interface Output (Transmission Mode / System Clock)         Figure 25.       System Interface Output (Transmission Mode / System Clock)                              | Figure 3.  | System Interface Transmit Framing Format for Transmission Mode   | 10 |

| Figure 6.       System Interface Receive Signaling Format for Transmission Mode         Figure 7.       System Interface Transmit Format for MVIP Mode         Figure 8.       System Interface Receive Format for MVIP Mode         Figure 9.       Loopbacks per Channel in QDS1F Device         Figure 10.       D4 SF Framing Structure         Figure 11.       ESF Framing Structure         Figure 12.       Boundary Scan Schematic         Figure 13.       QDS1F TXC-03102 Pin Diagram         Figure 14.       Recovered Clock and Switching Characteristics         Figure 15.       Transmit Clock and Data Switching Characteristics         Figure 16.       Serial Port Write Timing         Figure 17.       Serial Port Write Timing         Figure 18.       Intel Microprocessor Read Cycle Timing         Figure 20.       Motorola Microprocessor Read Cycle Timing         Figure 21.       Motorola Microprocessor Write Cycle Timing         Figure 22.       System Interface Output (MVIP Mode)         Figure 23.       System Interface Output (MVIP Mode)         Figure 24.       System Interface Output (Transmission Mode / System Clock)         Figure 25.       System Interface Output (Transmission Mode / System Clock)         Figure 26.       System Interface Output (Transmission Mode / Receive Clock)         Figure                           | Figure 4.  | System Interface Transmit Signaling Format for Transmission Mode | 11 |

| Figure 7.       System Interface Transmit Format for MVIP Mode         Figure 8.       System Interface Receive Format for MVIP Mode         Figure 9.       Loopbacks per Channel in QDS1F Device         Figure 10.       D4 SF Framing Structure         Figure 11.       ESF Framing Structure         Figure 12.       Boundary Scan Schematic         Figure 13.       QDS1F TXC-03102 Pin Diagram         Figure 14.       Recovered Clock and Switching Characteristics         Figure 15.       Transmit Clock and Data Switching Characteristics         Figure 16.       Serial Port Write Timing         Figure 17.       Serial Port Read Timing         Figure 18.       Intel Microprocessor Read Cycle Timing         Figure 20.       Motorola Microprocessor Read Cycle Timing         Figure 21.       Motorola Microprocessor Write Cycle Timing         Figure 22.       System Interface Output (MVIP Mode)         Figure 23.       System Interface Output (Transmission Mode / System Clock)         Figure 24.       System Interface Output (Transmission Mode / Setter Clock)         Figure 27.       Boundary Scan Timing         Figure 28.       System Interface Input (Transmission Mode)         Figure 27.       Boundary Scan Timing         Figure 28.       Operation of Performance Monitoring and Fault Monitorin                                    | Figure 5.  | System Interface Receive Framing Format for Transmission Mode    | 12 |

| Figure 8.       System Interface Receive Format for MVIP Mode         Figure 9.       Loopbacks per Channel in QDS1F Device         Figure 10.       D4 SF Framing Structure         Figure 11.       ESF Framing Structure         Figure 12.       Boundary Scan Schematic         Figure 13.       QDS1F TXC-03102 Pin Diagram         Figure 14.       Recovered Clock and Switching Characteristics         Figure 15.       Transmit Clock and Data Switching Characteristics         Figure 16.       Serial Port Write Timing         Figure 17.       Serial Port Read Timing         Figure 18.       Intel Microprocessor Read Cycle Timing         Figure 20.       Motorola Microprocessor Read Cycle Timing         Figure 21.       Motorola Microprocessor Write Cycle Timing         Figure 22.       System Interface Output (MVIP Mode)         Figure 23.       System Interface Output (MVIP Mode)         Figure 24.       System Interface Output (Transmission Mode / System Clock)         Figure 25.       System Interface Input (Transmission Mode)         Figure 27.       Boundary Scan Timing         Figure 28.       Operation of Performance Monitoring and Fault Monitoring Latching for AIS         Figure 28.       Operation of Performance Monitoring and Fault Monitoring Latching for AIS                                                           | Figure 6.  | System Interface Receive Signaling Format for Transmission Mode  | 12 |

| Figure 9.       Loopbacks per Channel in QDS1F Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Figure 7.  | System Interface Transmit Format for MVIP Mode                   | 13 |

| Figure 10.       D4 SF Framing Structure         Figure 11.       ESF Framing Structure         Figure 12.       Boundary Scan Schematic         Figure 13.       QDS1F TXC-03102 Pin Diagram         Figure 14.       Recovered Clock and Switching Characteristics         Figure 15.       Transmit Clock and Data Switching Characteristics         Figure 16.       Serial Port Write Timing         Figure 17.       Serial Port Read Timing         Figure 18.       Intel Microprocessor Read Cycle Timing         Figure 20.       Motorola Microprocessor Read Cycle Timing         Figure 21.       Motorola Microprocessor Write Cycle Timing         Figure 22.       System Interface Output (MVIP Mode)         Figure 23.       System Interface Output (MVIP Mode)         Figure 24.       System Interface Output (Transmission Mode / System Clock)         Figure 25.       System Interface Output (Transmission Mode / Receive Clock)         Figure 26.       System Interface Input (Transmission Mode / System Clock)         Figure 27.       Boundary Scan Timing         Figure 28.       Operation of Performance Monitoring and Fault Monitoring Latching for AIS         Figure 29.       QDS1F TXC-03102 Applications                                                                                                                                        | Figure 8.  | System Interface Receive Format for MVIP Mode                    | 14 |

| Figure 11.       ESF Framing Structure         Figure 12.       Boundary Scan Schematic         Figure 13.       QDS1F TXC-03102 Pin Diagram         Figure 14.       Recovered Clock and Switching Characteristics         Figure 15.       Transmit Clock and Data Switching Characteristics         Figure 16.       Serial Port Write Timing         Figure 17.       Serial Port Read Timing         Figure 18.       Intel Microprocessor Read Cycle Timing         Figure 20.       Motorola Microprocessor Read Cycle Timing         Figure 21.       Motorola Microprocessor Write Cycle Timing         Figure 22.       System Interface Output (MVIP Mode)         Figure 23.       System Interface Output (MVIP Mode)         Figure 24.       System Interface Output (Transmission Mode / System Clock)         Figure 25.       System Interface Output (Transmission Mode / Receive Clock)         Figure 26.       System Interface Input (Transmission Mode / System Clock)         Figure 27.       Boundary Scan Timing         Figure 28.       Operation of Performance Monitoring and Fault Monitoring Latching for AIS         Figure 29.       QDS1F TXC-03102 Applications                                                                                                                                                                                         | Figure 9.  | Loopbacks per Channel in QDS1F Device                            | 22 |

| Figure 12.       Boundary Scan Schematic         Figure 13.       QDS1F TXC-03102 Pin Diagram         Figure 14.       Recovered Clock and Switching Characteristics         Figure 15.       Transmit Clock and Data Switching Characteristics         Figure 16.       Serial Port Write Timing         Figure 17.       Serial Port Read Timing         Figure 18.       Intel Microprocessor Read Cycle Timing         Figure 20.       Motorola Microprocessor Read Cycle Timing         Figure 21.       Motorola Microprocessor Write Cycle Timing         Figure 22.       System Interface Output (MVIP Mode)         Figure 23.       System Interface Output (MVIP Mode)         Figure 24.       System Interface Output (Transmission Mode / System Clock)         Figure 25.       System Interface Input (Transmission Mode / Receive Clock)         Figure 26.       System Interface Input (Transmission Mode / System Clock)         Figure 27.       Boundary Scan Timing         Figure 28.       Operation of Performance Monitoring and Fault Monitoring Latching for AIS         Figure 29.       QDS1F TXC-03102 Applications                                                                                                                                                                                                                                         | Figure 10. | D4 SF Framing Structure                                          | 23 |

| Figure 13.       QDS1F TXC-03102 Pin Diagram         Figure 14.       Recovered Clock and Switching Characteristics         Figure 15.       Transmit Clock and Data Switching Characteristics         Figure 16.       Serial Port Write Timing         Figure 17.       Serial Port Read Timing         Figure 18.       Intel Microprocessor Read Cycle Timing         Figure 19.       Intel Microprocessor Read Cycle Timing         Figure 20.       Motorola Microprocessor Read Cycle Timing         Figure 21.       Motorola Microprocessor Write Cycle Timing         Figure 22.       System Interface Output (MVIP Mode)         Figure 23.       System Interface Output (MVIP Mode)         Figure 24.       System Interface Output (Transmission Mode / System Clock)         Figure 25.       System Interface Output (Transmission Mode / Receive Clock)         Figure 26.       System Interface Input (Transmission Mode / Receive Clock)         Figure 27.       Boundary Scan Timing         Figure 28.       Operation of Performance Monitoring and Fault Monitoring Latching for AIS         Figure 29.       QDS1F TXC-03102 Applications                                                                                                                                                                                                                        | Figure 11. | ESF Framing Structure                                            | 24 |

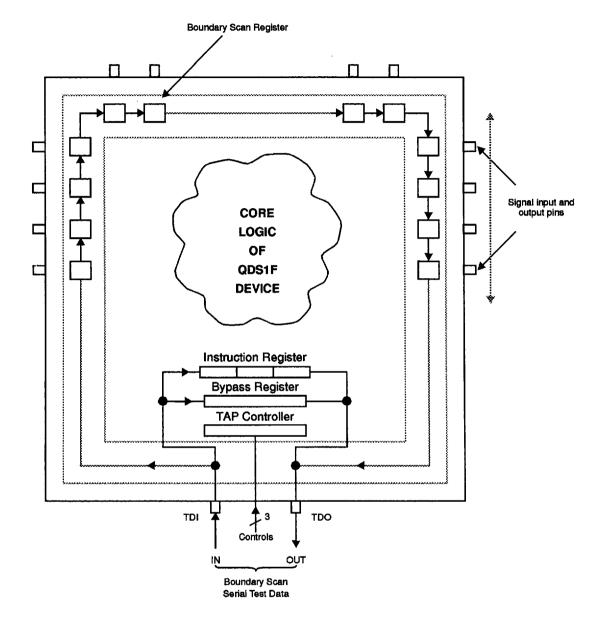

| Figure 14.       Recovered Clock and Switching Characteristics         Figure 15.       Transmit Clock and Data Switching Characteristics         Figure 16.       Serial Port Write Timing         Figure 17.       Serial Port Read Timing         Figure 18.       Intel Microprocessor Read Cycle Timing         Figure 19.       Intel Microprocessor Read Cycle Timing         Figure 20.       Motorola Microprocessor Read Cycle Timing         Figure 21.       Motorola Microprocessor Write Cycle Timing         Figure 22.       System Interface Output (MVIP Mode)         Figure 23.       System Interface Output (MVIP Mode)         Figure 24.       System Interface Output (Transmission Mode / System Clock)         Figure 25.       System Interface Output (Transmission Mode / Receive Clock)         Figure 26.       System Interface Input (Transmission Mode / System Clock)         Figure 27.       Boundary Scan Timing         Figure 28.       Operation of Performance Monitoring and Fault Monitoring Latching for AIS         Figure 29.       QDS1F TXC-03102 Applications                                                                                                                                                                                                                                                                              | Figure 12. | Boundary Scan Schematic                                          | 26 |

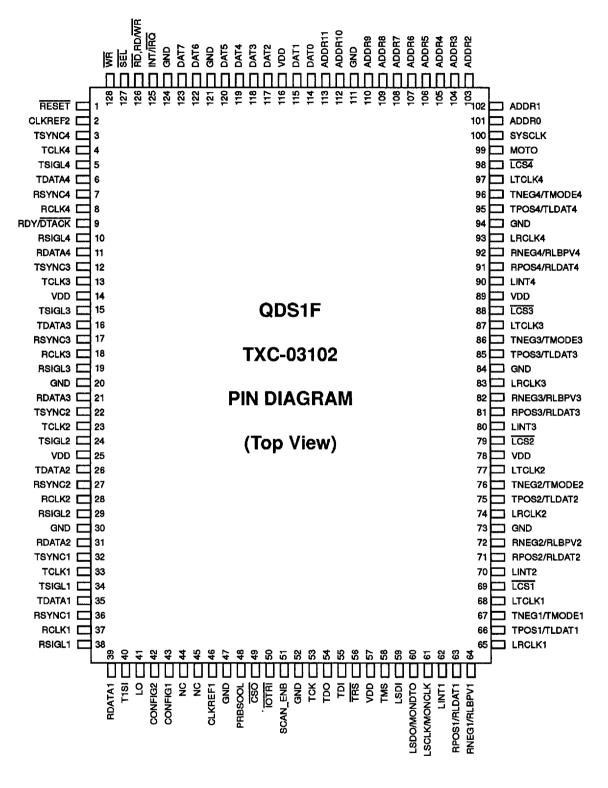

| Figure 15.       Transmit Clock and Data Switching Characteristics         Figure 16.       Serial Port Write Timing         Figure 17.       Serial Port Read Timing         Figure 18.       Intel Microprocessor Read Cycle Timing         Figure 19.       Intel Microprocessor Write Cycle Timing         Figure 20.       Motorola Microprocessor Read Cycle Timing         Figure 21.       Motorola Microprocessor Write Cycle Timing         Figure 22.       System Interface Output (MVIP Mode)         Figure 23.       System Interface Input (MVIP Mode)         Figure 24.       System Interface Output (Transmission Mode / System Clock)         Figure 25.       System Interface Output (Transmission Mode / Receive Clock)         Figure 26.       System Interface Input (Transmission Mode)         Figure 27.       Boundary Scan Timing         Figure 28.       Operation of Performance Monitoring and Fault Monitoring Latching for AIS         Figure 29.       QDS1F TXC-03102 Applications                                                                                                                                                                                                                                                                                                                                                                    | Figure 13. | QDS1F TXC-03102 Pin Diagram                                      | 27 |

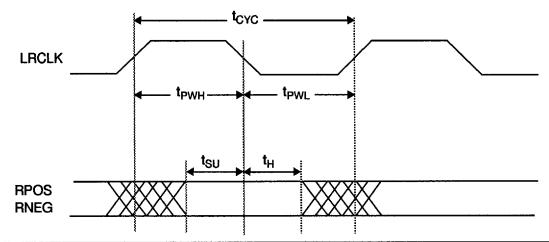

| Figure 16.       Serial Port Write Timing         Figure 17.       Serial Port Read Timing         Figure 18.       Intel Microprocessor Read Cycle Timing         Figure 19.       Intel Microprocessor Read Cycle Timing         Figure 20.       Motorola Microprocessor Read Cycle Timing         Figure 21.       Motorola Microprocessor Write Cycle Timing         Figure 22.       System Interface Output (MVIP Mode)         Figure 23.       System Interface Output (MVIP Mode)         Figure 24.       System Interface Output (Transmission Mode / System Clock)         Figure 25.       System Interface Output (Transmission Mode / Receive Clock)         Figure 26.       System Interface Input (Transmission Mode / Receive Clock)         Figure 27.       Boundary Scan Timing         Figure 28.       Operation of Performance Monitoring and Fault Monitoring Latching for AIS         Figure 29.       QDS1F TXC-03102 Applications                                                                                                                                                                                                                                                                                                                                                                                                                               | Figure 14. | Recovered Clock and Switching Characteristics                    | 38 |

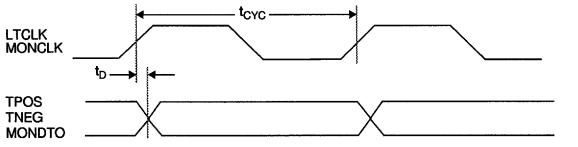

| Figure 17.       Serial Port Read Timing         Figure 18.       Intel Microprocessor Read Cycle Timing         Figure 19.       Intel Microprocessor Write Cycle Timing         Figure 20.       Motorola Microprocessor Read Cycle Timing         Figure 21.       Motorola Microprocessor Write Cycle Timing         Figure 22.       System Interface Output (MVIP Mode)         Figure 23.       System Interface Input (MVIP Mode)         Figure 24.       System Interface Output (Transmission Mode / System Clock)         Figure 25.       System Interface Output (Transmission Mode / Receive Clock)         Figure 26.       System Interface Input (Transmission Mode)         Figure 27.       Boundary Scan Timing         Figure 28.       Operation of Performance Monitoring and Fault Monitoring Latching for AIS         Figure 29.       QDS1F TXC-03102 Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Figure 15. | Transmit Clock and Data Switching Characteristics                | 38 |

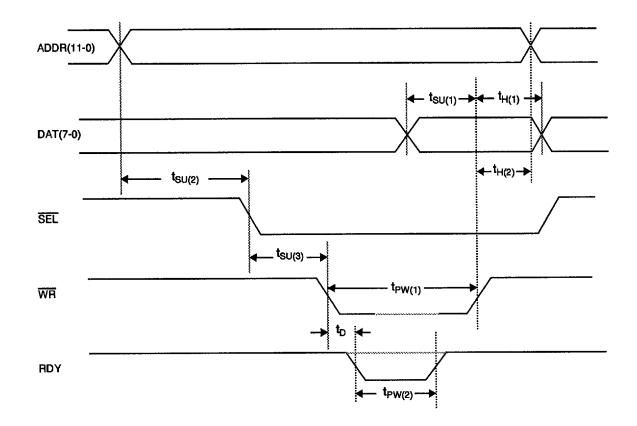

| Figure 18.       Intel Microprocessor Read Cycle Timing         Figure 19.       Intel Microprocessor Write Cycle Timing         Figure 20.       Motorola Microprocessor Read Cycle Timing         Figure 21.       Motorola Microprocessor Write Cycle Timing         Figure 22.       System Interface Output (MVIP Mode)         Figure 23.       System Interface Input (MVIP Mode)         Figure 24.       System Interface Output (Transmission Mode / System Clock)         Figure 25.       System Interface Output (Transmission Mode / Receive Clock)         Figure 26.       System Interface Input (Transmission Mode)         Figure 27.       Boundary Scan Timing         Figure 28.       Operation of Performance Monitoring and Fault Monitoring Latching for AIS         Figure 29.       QDS1F TXC-03102 Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Figure 16. | Serial Port Write Timing                                         | 39 |

| Figure 19.       Intel Microprocessor Write Cycle Timing         Figure 20.       Motorola Microprocessor Read Cycle Timing         Figure 21.       Motorola Microprocessor Write Cycle Timing         Figure 22.       System Interface Output (MVIP Mode)         Figure 23.       System Interface Input (MVIP Mode)         Figure 24.       System Interface Output (Transmission Mode / System Clock)         Figure 25.       System Interface Output (Transmission Mode / Receive Clock)         Figure 26.       System Interface Input (Transmission Mode)         Figure 27.       Boundary Scan Timing         Figure 28.       Operation of Performance Monitoring and Fault Monitoring Latching for AIS         Figure 29.       QDS1F TXC-03102 Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Figure 17. | Serial Port Read Timing                                          | 40 |

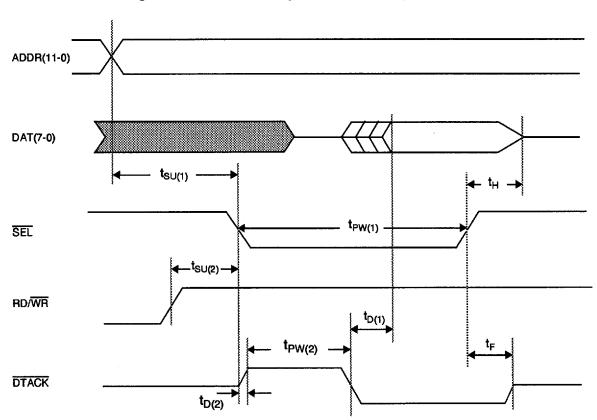

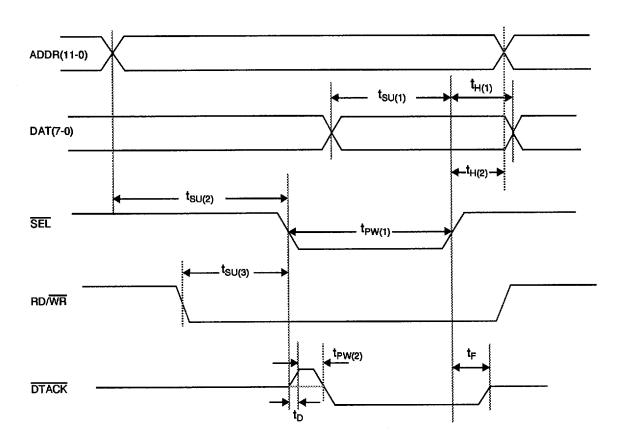

| Figure 20.       Motorola Microprocessor Read Cycle Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Figure 18. | Intel Microprocessor Read Cycle Timing                           | 41 |

| Figure 21.       Motorola Microprocessor Write Cycle Timing         Figure 22.       System Interface Output (MVIP Mode)         Figure 23.       System Interface Input (MVIP Mode)         Figure 24.       System Interface Output (Transmission Mode / System Clock)         Figure 25.       System Interface Output (Transmission Mode / Receive Clock)         Figure 26.       System Interface Input (Transmission Mode)         Figure 27.       Boundary Scan Timing         Figure 28.       Operation of Performance Monitoring and Fault Monitoring Latching for AIS         Figure 29.       QDS1F TXC-03102 Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Figure 19. | Intel Microprocessor Write Cycle Timing                          | 42 |

| Figure 22.       System Interface Output (MVIP Mode)         Figure 23.       System Interface Input (MVIP Mode)         Figure 24.       System Interface Output (Transmission Mode / System Clock)         Figure 25.       System Interface Output (Transmission Mode / Receive Clock)         Figure 26.       System Interface Input (Transmission Mode)         Figure 27.       Boundary Scan Timing         Figure 28.       Operation of Performance Monitoring and Fault Monitoring Latching for AIS         Figure 29.       QDS1F TXC-03102 Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Figure 20. | Motorola Microprocessor Read Cycle Timing                        | 43 |

| Figure 23.       System Interface Input (MVIP Mode)         Figure 24.       System Interface Output (Transmission Mode / System Clock)         Figure 25.       System Interface Output (Transmission Mode / Receive Clock)         Figure 26.       System Interface Input (Transmission Mode)         Figure 27.       Boundary Scan Timing         Figure 28.       Operation of Performance Monitoring and Fault Monitoring Latching for AIS         Figure 29.       QDS1F TXC-03102 Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Figure 21. | Motorola Microprocessor Write Cycle Timing                       | 44 |

| Figure 24.       System Interface Output (Transmission Mode / System Clock)         Figure 25.       System Interface Output (Transmission Mode / Receive Clock)         Figure 26.       System Interface Input (Transmission Mode)         Figure 27.       Boundary Scan Timing         Figure 28.       Operation of Performance Monitoring and Fault Monitoring Latching for AIS         Figure 29.       QDS1F TXC-03102 Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Figure 22. | System Interface Output (MVIP Mode)                              | 45 |

| Figure 25.       System Interface Output (Transmission Mode / Receive Clock)         Figure 26.       System Interface Input (Transmission Mode)         Figure 27.       Boundary Scan Timing         Figure 28.       Operation of Performance Monitoring and Fault Monitoring Latching for AIS         Figure 29.       QDS1F TXC-03102 Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Figure 23. | System Interface Input (MVIP Mode)                               | 46 |

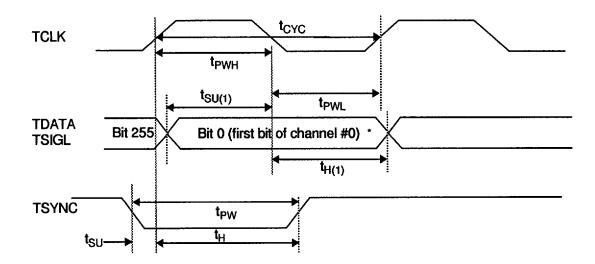

| Figure 26.       System Interface Input (Transmission Mode)         Figure 27.       Boundary Scan Timing         Figure 28.       Operation of Performance Monitoring and Fault Monitoring Latching for AIS         Figure 29.       QDS1F TXC-03102 Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Figure 24. | System Interface Output (Transmission Mode / System Clock)       | 47 |

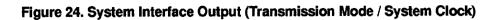

| Figure 26.       System Interface Input (Transmission Mode)         Figure 27.       Boundary Scan Timing         Figure 28.       Operation of Performance Monitoring and Fault Monitoring Latching for AIS         Figure 29.       QDS1F TXC-03102 Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Figure 25. | System Interface Output (Transmission Mode / Receive Clock)      | 48 |

| Figure 28. Operation of Performance Monitoring and Fault Monitoring Latching for AIS<br>Figure 29. QDS1F TXC-03102 Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Figure 26. | System Interface Input (Transmission Mode)                       | 49 |

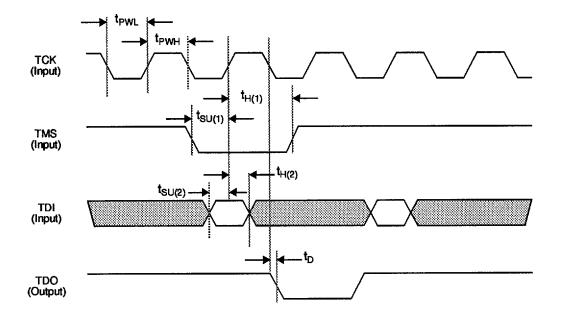

| Figure 28. Operation of Performance Monitoring and Fault Monitoring Latching for AIS<br>Figure 29. QDS1F TXC-03102 Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Figure 27. | Boundary Scan Timing                                             | 50 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Figure 28. |                                                                  |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Figure 29. | QDS1F TXC-03102 Applications                                     | 88 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Figure 30. | QDS1F TXC-03102 128-Pin Plastic Quad Flat Package                |    |

TXC-03102-MB Ed. 5, June 1995

.

# **QUAD DS1 FRAMER FEATURES**

The Quad DS1 Framer (QDS1F) device is a highly-featured DS1 framer for use in a wide variety of interface, transmission and switching applications. Four independent DS1 framers are provided in a single monolithic VLSI device using sub-micron CMOS technology. Powered from a single +5.0 volt supply, the four framers dissipate less than half a watt typically. The QDS1F is provided in a rectangular 128-pin plastic quad flat package. Its operating temperature range extends from -40°C to +85°C.

The QDS1F device has been designed to meet the latest industry standards, namely:

- ANSI T1.403 and T1M1.3

- Bellcore TR-TSY 000499

- AT&T Pub. 62411 and Pub. 54016

- IEEE 1149.1

The following features are independently selectable for each of the four DS1 framers:

Framing Modes:

- D4 SF programmable for Fs, Ft or both frame bits

- ESF with or without CRC

- Unframed (bypass)

- SLC 96, T1DM and other SF modes with external logic

Line Codes:

- AMI

- B8ZS

- · AMI with forced ones density

- NRZ (bypass)

- · Selectable polarity (NRZ) and clock edges

Signaling:

- A, AB (SF)

- A, AB, ABCD (ESF)

- Per DS0 enable with microprocessor read and substitution in both receive and transmit directions

- Signaling freeze on LOS

Clock Management:

- · Flexible receive and transmit clock selection, including local oscillator

- Two frame slip buffers for each of receive and transmit paths, with independent bypass

- · System side and line side clocks on receive and transmit, each independent

Alarms and Errors:

- · Detect and force yellow and blue (AIS) alarms

- Detect Out Of Frame, Loss Of Signal, Severely Errored Frame and Change of Frame Alignment

- Detect, count and force CRC errors (ESF only), frame bit errors and line code errors (bipolar violations, with or without excessive zeros)

- Detect and force frame slips

TRANS

**DS0 Control:**

• Per DS0 enable (independent receive and transmit) with microprocessor read and substitution in both receive and transmit directions

Maintenance:

- · Loopbacks line remote, local and payload (ESF only)

- Detect and transmit SF loop-up and loop-down codes

- Full duplex HDLC controller with bit-oriented code support for facility data link and 16-byte receive and transmit FIFOs

Microprocessor Interface:

- · Eight-bit status register with eight-bit mask register

- · Latched event registers for each status bit

- · CRC (ESF only), code violation and frame bit error counters

- Shadow registers and counters

- · Full control of framing, alarm generation and propagation, codec features

- FDL control, signaling access/control, DS0 access/control

- · Reset, resync, slip buffer and frame bit access

The following features are only selectable for the four framers as a group:

- Transmission mode ("off line" framing) or MVIP mode system interfaces

- Serial port to read/write control up to four line interface transceivers, or selection of one

of four DS1 line interfaces (receive or transmit) to monitor clock and data

- Microprocessor global reset, masks, polling registers, interrupt polarity and latch edge control

- Two reference clock outputs at 8kHz or 1544 kHz with freeze on LOS

- IEEE 1149.1 boundary scan

- · Motorola or Intel microprocessor access with separate address and data buses

- Ability to tri-state all outputs for in-circuit testing

- · Ability to place line side transmit clock and data to logic low for protection switching

- Synchronization start position is programmable to any receive or transmit bit position on the system side

- External shadow register clock input

- Pseudo-Random Binary Sequence (PRBS) generator and analyzer

# **BLOCK DIAGRAM**

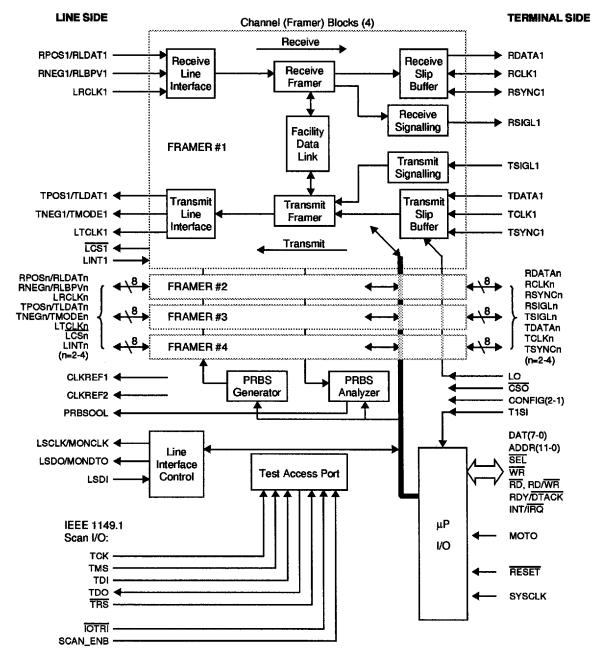

# **BLOCK DIAGRAM DESCRIPTION**

A simplified block diagram of the QDS1F device is shown in Figure 1. The major blocks are the Microprocessor Input/Output Interface ( $\mu$ P I/O), the Line Interface Control, the PRBS generator and the PRBS analyzer, four Channel (Framer) blocks and the Test Access Port. These blocks are described in detail below. For additional information, reference may be made to the Pin Descriptions, Timing Characteristics (Figures 14 - 28), Memory Map and Memory Map Descriptions sections of this Data Sheet.

# MICROPROCESSOR INPUT/OUTPUT INTERFACE BLOCK

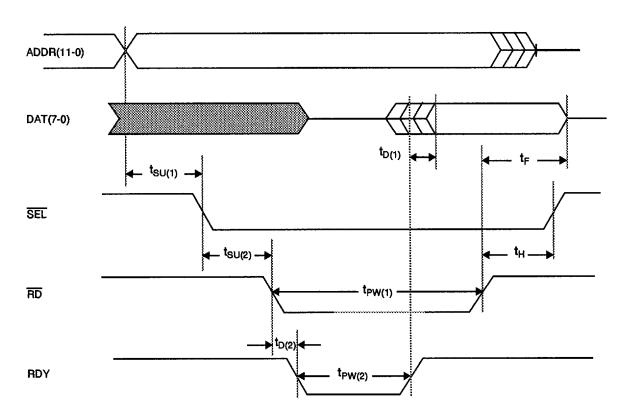

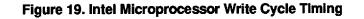

The Microprocessor Input/Output Interface allows access and control for each of the four DS1 framers. Alarm information detected by the framers can be read as current status and latched in event registers. Either the arrival or the departure of a condition can be individually enabled for setting the event register. To facilitate either interrupt or polled systems, global interrupt masks, per channel interrupt masks, global event and global polling registers are provided. To assist in the collection of performance parameters, shadow registers and counter latching are provided. The configuration of each framer is provided by this interface, as well as control of the Facility Data Link block for each framer. The Receive Line Interface and Transmit Line Interface blocks are also controlled by the Microprocessor Input/Output Interface. The microprocessor bus supports both Motorola and Intel style processors with a minimum amount of interface logic. An external pin (MOTO) configures the type of bus supported. The data bus DAT(7-0) is an 8-bit, bi-directional, tri-state port. The internal control and status registers are accessed through this port. When not accessed, this port is in a high impedance state. The address bus ADDR(11-0) is a 12-bit input port. These pins select individual control and status registers within the framer. SEL is the microprocessor port select signal. WR is the Intel microprocessor port write signal and RD,RD/WR is the Intel read and Motorola read/write signal. RDY/ DTACK is used to delay microprocessor access if required to access internal registers. INT/IRQ is the microprocessor port interrupt line. RESET is the overall device reset line and SYSCLK is a high speed system clock used by all blocks.

Global controls for reset are provided at memory address 005H (the suffix H indicates a hexadecimal number throughout this Data Sheet)). Register 006H allows the interrupt to be turned off (GIM bit), the polarity and active edge for latching to be controlled (IPOL, RISE and FALL bits) and performance and fault monitoring functions, together with the hardware mask, to be turned on (ENPMFM and ENHWM bits).

For a view of all QDS1F framers and control the following registers are provided:

Register 00AH is an or-gated value of each framer's event register. Loss Of Signal, Alarm Indication Signal, Out Of Frame, Yellow Alarm, Severely Errored Frame, Change of Frame Alignment, Receive Slip and Transmit Slip are all provided.

Register 00BH provides a mask for each condition covering all four framers (per-framer masks are also provided at register X09H).

Register 00CH contains channel activity indicating interrupts from alarms.

Register 00EH provides activity information, but only for facility data link (FDL) interrupts. This allows software to control line status and FDL status separately.

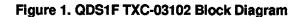

# LINE INTERFACE CONTROL AND DS1 MONITOR

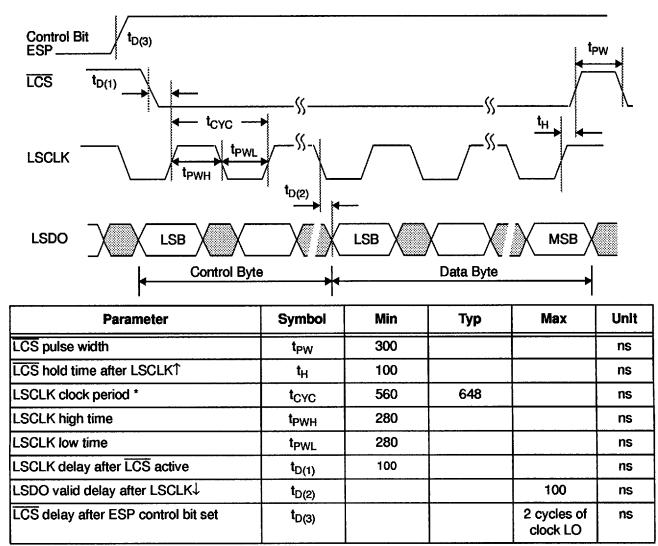

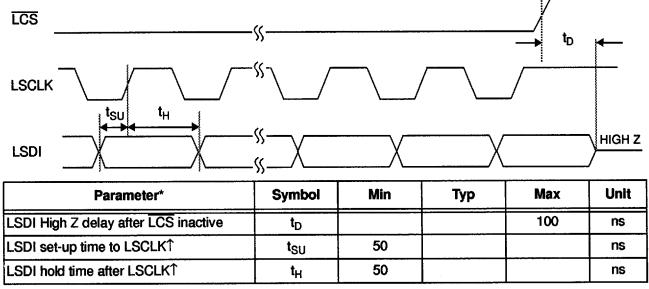

The Line Interface Control block is a serial interface that is used to control and manage the external analog line transceivers operating in the host mode. This allows the system processor to have complete control of the line transceiver through the QDS1F Microprocessor Input/Output Interface. The interface consists of a data input pin (LSDI), data output pin (LSDO), and serial clock (LSCLK) that are shared among all the transceivers. In addition, there is an individual chip select (LCS) for each transceiver, and an individual input from each transceiver that may be used to generate an interrupt (LINT) that is part of the Line Interface block. Figure 2 below shows the serial interface operation. Note that control bit ESP initiates and terminates the sequence.

Figure 2. Serial Interface Operation

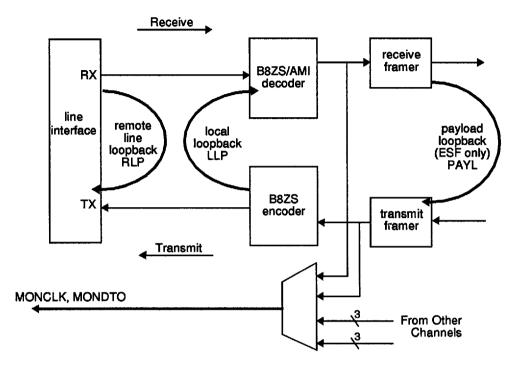

When the serial interface to the line transceivers is not used with the QDS1F (e.g., in an application using the TranSwitch M13E device), access to the DS1 transmit or receive clock and data is provided by microprocessor selection of the channel and direction. The signals are available on pins MONDTO and MONCLK. These pins are tri-stated when not selected, to allow multiple framers to share a DSX-1 line driver if desired. The monitored signals are selected after the decoding and before the encoding. This mode is mutually exclusive with the serial interface.

Control of the serial port or DS1 monitor function is provided by Microprocessor Input/Output Interface registers. "Command Byte" and "Line Interface Serial Data Output" (address 010H and 011H), "Line Interface Serial Data Output" (address 012H) and control bits for DS1 channel number, RXTX, ESP/EMON and BDCST (address 013H).

# **Reference Clock Outputs**

To support system clock reference needs, the QDS1F device can provide two recovered receive clocks, LRCLK, from any of the four lines, as outputs on pins CLKREF1 and CLKREF2. The microprocessor interface can select the output frequency (1544 kHz or 8 kHz), the specific lines, and whether or not to tri-state both CLKREF1 and CLKREF2 to permit multiple QDS1F devices to share a common reference clock line. To facilitate clock holdover requirements, LOS (or LINT if enabled as LOS) will cause the specific CLKREF(1, 2) output to be tri-stated. A register at address 019H provides two pairs of bits that control which DS1 provides CLKREF2. Individual enable bits, ENREF1 and ENREF2, are provided as well as a frequency selection bit, 1544KHZ, covering both reference outputs.

TRAR

### PSEUDO-RANDOM BINARY SEQUENCE (PRBS) GENERATOR AND ANALYZER

The PRBS Generator and Analyzer blocks provide the ability to test each channel (framer) using the local loopback feature provided. The output of the analyzer is brought out to a pin (PRBSOOL). The pattern is 2<sup>15</sup>-1 bit pseudo- random sequence that follows the ITU-T 'O' recommendations (except that it is inverted).

Control bits PRBSFR, PRBSEN and DS1 channel number in a Microprocessor Input/Output Interface register (address 013H) provide control. Per channel bit INSPRBS (address X06H, where X=1 - 4, identifies the channel) controls per-framer insertion, which substitutes the PRBS pattern for the data from TDATAn. The analyzer is connected to the selected RDATAn output.

# **OVERVIEW OF THE RECEIVE AND TRANSMIT PATHS**

#### The Receive and Transmit Line Interface Signals

The Receive Line Interface and Transmit Line Interface blocks of each of the four Channel (Framer) blocks consist of clock and data pins to the external Line Transceiver for each channel. These pins can be configured to operate in two modes, dual unipolar and NRZ. In the dual unipolar mode the individual positive and negative line pulses are converted to CMOS level signals (RPOS, RNEG) by an external Line Transceiver. Similarly, each CMOS output (TPOS, TNEG) is converted to positive and negative line pulses by an external Line Transceiver. In NRZ mode the external Line Transceiver performs the code conversion to/from AMI or B8ZS; here the input (RLDAT) contains a pulse for each line pulse regardless of polarity and the output (TLDAT) contains a pulse for each line pulse regardless of polarity. The Line Interface can be programmed in NRZ mode to handle these signals with either a pulse or lack of pulse as a valid "1" or a rising or falling clock edge as valid for sampling/outputting. Clock extraction (LRCLK) is also handled by the external Line Transceiver and this clock is used by the Line Interface block to clock either NRZ or dual unipolar signals to the Receive Line Interface of the Channel block. Clock from the Transmit Line Interface of the Channel block (LTCLK) is used to clock out the data, programmable on the rising or falling edge. Remote line loopback for each channel is handled in the Line Interface. In the NRZ mode the negative polarity input and output pins are used for other purposes; RLBPV input is used to count bipolar violations from an external Line Transceiver; TMODE is used as a spare output (e.g., to control an external Line Transceiver for AMI/B8ZS selection).

#### System Interface Signals

The system interface interconnects each of the framers with the rest of the system. For each framer there is a separate transmit and receive highway. Each highway consists of a data bus, a signaling bus, a clock, and a synchronization signal. Each data highway is connected to a two-frame slip buffer, and each signaling highway is connected to a 96-bit signaling buffer. There are two modes of operation for the system interface; the transmission mode and the MVIP mode. In the transmission mode, the system interface operates at approximately the same speed as the line, with signaling and alarms on the signaling highway; a 3 millisecond multiframe pulse is used to synchronize the interface, and use of the slip buffers is optional. In MVIP mode, the system interface operates at 2.048 MHz with DSOs on the data highway and signaling on the signaling highway; a 125-microsecond frame pulse is used to synchronize the interface, and use of the slip buffers is mandatory.

# Transmission Mode ("Off Line" Framer Operation)

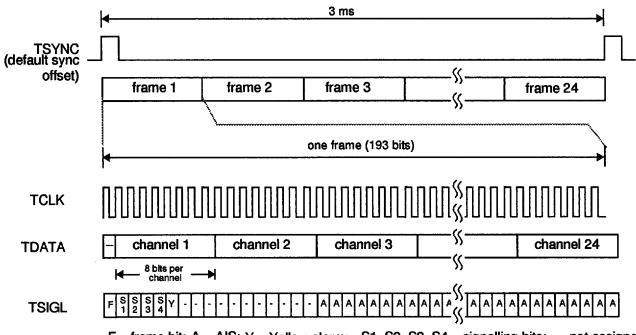

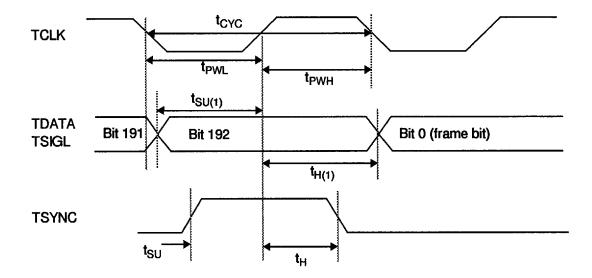

In transmission mode the transmit highway carries information from the system to the framer. The highway is sub-divided into two time division multiplexed buses, one for the data (TDATA), and one for signaling, frame bit and alarms (TSIGL). These two buses are synchronous with the signal TCLK, a 1.544 MHz clock, driven from the system. The transmit framing (data) format and signaling format are shown in the timing diagrams below, Figures 3 and 4.

Tea

The data highway is a single bit-serial bus organized into 193-bit groups called frames. Each frame consists of a spare bit position followed by twenty-four 8-bit data samples representing the 24 DS0s. There are 24 frames that form a multiframe, the beginning of which is identified by a synchronization pulse, TSYNC. TSYNC is programmable for the device to any bit position in the frame; the default position occurs one bit time before the first frame of the multiframe and every 24 frames after that. A register at address 017H provides TSYNC control (TSD7-TSD0).

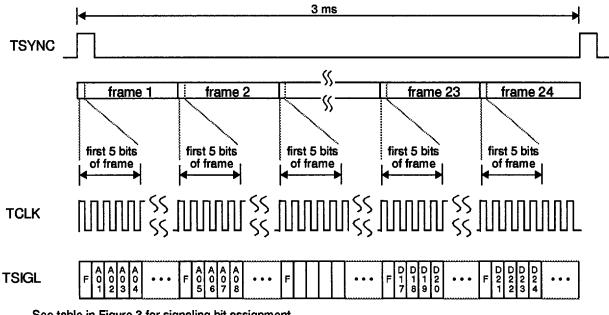

The signaling highway, TSIGL, is also divided into 193-bit frames. Each frame consists of a frame bit followed by 192 bits of signaling and alarm information for the 24 data channels on the data highway. The frame bit pattern tracks the signaling bit pattern received from the system and may be used to send ESF FDL bits or SLC-96 control bits. The alarm bits in the signaling highway follow the signaling bits. In each frame of 193 bits, four signaling bits are transmitted followed by a yellow alarm bit position. The bit positions coincident with DS0 #3 through DS0 #24 are all used for the AIS alarm bit. Signaling bits A1 through A4 occur in frame number one, followed by A5 through A8 in frame number two, ending with D21 through D24 in frame number 24, corresponding to the ESF mode with 16-state signaling. For two- or four-state signaling the B, C and D bits or the C and D bits are replaced by A bits, or A and B bits, respectively. Two control bits in a register at address X00H, ENSYEL and ENSAIS, control the receipt of yellow alarm and AIS over the signaling highway. DS1 yellow will be transmitted if the yellow bit is set on the signaling highway and ENSYEL is set to one. Similarly, if ENSAIS is set to one, DS1 AIS will be transmitted on the line if the AIS bit is set on the signaling highway (TSIGL).

F = frame bit; A = AIS; Y = Yellow alarm; S1, S2, S3, S4 = signalling bits; - = not assigned

| Signaling | bit | positions on | TSIGL and RSIGL |

|-----------|-----|--------------|-----------------|

|-----------|-----|--------------|-----------------|

| Frame | SF/ESF | 16-St. TSIGL; S <sub>1</sub> -S <sub>4</sub> | RSIGL; S <sub>1</sub> -S <sub>4</sub> | 4-State; S <sub>1</sub> -S <sub>4</sub> | 2-State; S <sub>1</sub> -S <sub>4</sub> |

|-------|--------|----------------------------------------------|---------------------------------------|-----------------------------------------|-----------------------------------------|

| 1     | Ft/DI  | A1, A2, A3, A4                               | A1, A2, A3, A4                        | A1, A2, A3, A4                          | A1, A2, A3, A4                          |

| 2     | Fs/CRC | A5, A6, A7, A8                               | A5, A6, A7, A8                        | A5, A6, A7, A8                          | A5, A6, A7, A8                          |

| 3     | Ft/DI  | A9, A10, A11, A12                            | A9, A10, A11, A12                     | A9, A10, A11, A12                       | A9, A10, A11, A12                       |

| 4     | Fs/Ft  | A13, A14, A15, A16                           | A13, A14, A15, A16                    | A13, A14, A15, A16                      | A13, A14, A15, A16                      |

| 5     | Ft/DI  | A17, A18, A19, A20                           | A17, A18, A19, A20                    | A17, A18, A19, A20                      | A17, A18, A19, A20                      |

| 6     | Fs/CRC | A21, A22, A23, A24                           | A21, A22, A23, A24                    | A21, A22, A23, A24                      | A21, A22, A23, A24                      |

| 7     | Ft/DI  | B1, B2, B3, B4                               | B1, B2, B3, B4                        | B1, B2, B3, B4                          | A1, A2, A3, A4                          |

| 8     | Fs/Ft  | B5, B6, B7, B8                               | B5, B6, B7, B8                        | B5, B6, B7, B8                          | A5, A6, A7, A8                          |

| 9     | Ft/DI  | B9, B10, B11, B12                            | B9, B10, B11, B12                     | B9, B10, B11, B12                       | A9, A10, A11, A12                       |

| 10    | Fs/CRC | B13, B14, B15, B16                           | B13, B14, B15, B16                    | B13, B14, B15, B16                      | A13, A14, A15, A16                      |

| 11    | Ft/DI  | B17, B18, B19, B20                           | B17, B18, B19, B20                    | B17, B18, B19, B20                      | A17, A18, A19, A20                      |

| 12    | Fs/Ft  | B21, B22, B23, B24                           | B21, B22, B23, B24                    | B21, B22, B23, B24                      | A21, A22, A23, A24                      |

| 13    | Ft/DI  | C1, C2, C3, C4                               | C1, C2, C3, C4                        | A1, A2, A3, A4                          | A1, A2, A3, A4                          |

| 14    | Fs/CRC | C5, C6, C7, C8                               | C5, C6, C7, C8                        | A5, A6, A7, A8                          | A5, A6, A7, A8                          |

| 15    | Ft/DI  | C9, C10, C11, C12                            | C9, C10, C11, C12                     | A9, A10, A11, A12                       | A9, A10, A11, A12                       |

| 16    | Fs/Ft  | C13, C14, C15, C16                           | C13, C14, C15, C16                    | A13, A14, A15, A16                      | A13, A14, A15, A16                      |

| 17    | Ft/DI  | C17, C18, C19, C20                           | C17, C18, C19, C20                    | A17, A18, A19, A20                      | A17, A18, A19, A20                      |

| 18    | Fs/CRC | C21, C22, C23, C24                           | C21, C22, C23, C24                    | A21, A22, A23, A24                      | A21, A22, A23, A24                      |

| 19    | Ft/DI  | D1, D2, D3, D4                               | D1, D2, D3, D4                        | B1, B2, B3, B4                          | A1, A2, A3, A4                          |

| 20    | Fs/Ft  | D5, D6, D7, D8                               | D5, D6, D7, D8                        | B5, B6, B7, B8                          | A5, A6, A7, A8                          |

| 21    | Ft/DI  | D9, D10, D11, D12                            | D9, D10, D11, D12                     | B9, B10, B11, B12                       | A9, A10, A11, A12                       |

| 22    | Fs/CRC | D13, D14, D15, D16                           | D13, D14, D15, D16                    | B13, B14, B15, B16                      | A13, A14, A15, A16                      |

| 23    | Ft/DI  | D17, D18, D19, D20                           | D17, D18, D19, D20                    | B17, B18, B19, B20                      | A17, A18, A19, A20                      |

| 24    | Fs/Ft  | D21, D22, D23, D24                           | D21, D22, D23, D24                    | B21, B22, B23, B24                      | A21, A22, A23, A24                      |

See table in Figure 3 for signaling bit assignment.

#### Figure 4. System Interface Transmit Signaling Format for Transmission Mode

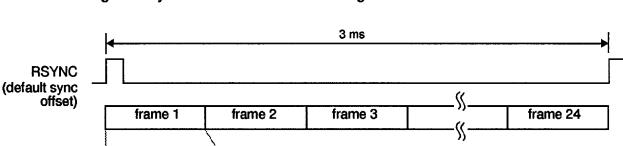

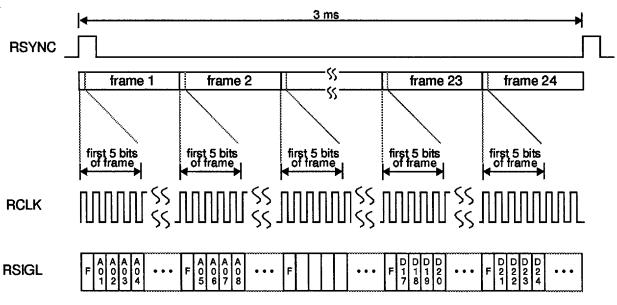

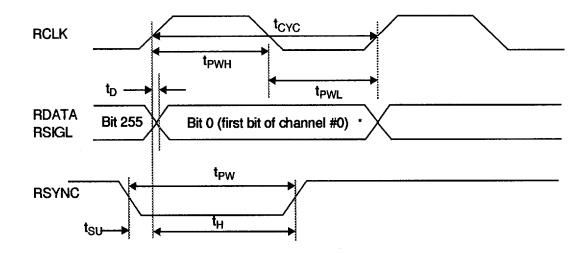

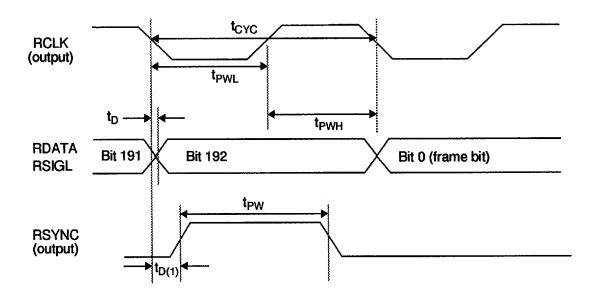

In transmission mode the receive highway carries information from the framer to the system. The highway is sub-divided into two time division multiplexed buses, one for the data (RDATA) and one for signaling, frame bits and alarms (RSIGL). These two buses are synchronous with the signal RCLK, a 1.544 MHz clock that is driven either from the system or the framer. The system interface receive framing (data) format and signaling format are shown in the timing diagrams below, Figures 5 and 6. The system will source the clock when the receive side slip buffer is enabled, and the framer will source the clock when the receive side slip buffer is bypassed.

The data highway is a single bit-serial bus that is organized into 193-bit groups called frames. Each frame consists of a frame bit followed by twenty-four 8-bit data samples. Each of the 8-bit data samples represents a single DS0 on the receive highway. The 193-bit frames are grouped into a 24-frame multiframe. In order to help locate the beginning of a frame and extract signaling information, the system or the framer sources a synchronization signal, RSYNC. RSYNC is programmable to any bit position in the frame; the default value occurs one bit time before the first frame in the multiframe and every 24 frames after that. A register at address 018H provides RSYNC control (RSD7-RSD0).

The signaling highway, RSIGL, is also divided into 193-bit frames and is organized in an identical fashion to TSIGL. AIS or Yellow alarms detected by the framer are sent out in the same positions as for TSIGL. The frame bits received from the line are available on RSIGL; they track the signaling bits and may be used for FDL extraction or SLC-96 control channel extraction.

Several controls are provided for alarms sent on the alarm bit position of the signal highway. Bits ENAIS, ELOS and ENOOF allow AIS, LOS and OOF, respectively to set the AIS bit to 1 on the signaling highway (address X03H). Control bits SYSVTAIS and SYSALL1 (address X07H) allow a DS1 AIS to be generated to the system on receipt of an AIS condition or when forced by the Microprocessor Input/Output Interface.

- 11 -

TXC-03102-MB Ed. 5, June 1995

Tea

Figure 5. System Interface Receive Framing Format for Transmission Mode

Figure 6. System Interface Receive Signaling Format for Transmission Mode

See table in Figure 3 for signaling bit assignment.

#### **MVIP Mode**

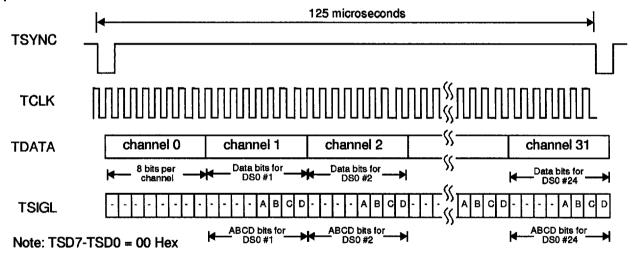

In MVIP mode the transmit highway carries information from the system to the framer. The highway is subdivided into two time division multiplexed buses, one for the data (TDATA), and one for signaling, TSIGL. These two buses are synchronous with the signal TCLK, a 2.048 MHz clock, driven from the system. The data highway is a single bit-serial bus organized into 256-bit groups called frames. Each frame consists of thirty two 8-bit data samples representing 32 DS0s. The 24 DS0s to be transmitted on the line are mapped to the 32 DS0s of the transmit data highway as follows:

| Tran. Hwy<br>Channel<br>No. | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

|-----------------------------|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| DS1 DS0<br>No.              | х | 1 | 2 | 3 | x | 4 | 5 | 6 | х | 7 | 8  | 9  | X  | 10 | 11 | 12 | х  | 13 | 14 | 15 | х  | 16 | 17 | 18 | х  | 19 | 20 | 21 | х  | 22 | 23 | 24 |

The frame start is identified by a synchronization pulse, TSYNC, which occurs once per frame (125 microseconds). TSYNC is programmable for the device to any bit position in the frame; the default position occurs coincident with the first bit of transmit highway channel 0 (see control bits TSD7-TSD0 at address 017H). The signaling highway, TSIGL, is also divided into 256-bit frames. Each frame consists of 32 DS0 positions, 24 of which carry the ABCD signaling bits associated with the DS0s on the data highway. The same positions used for the DS0s are used for the signaling bits. The signaling bits occupy the last four bits of the DS0 on the signaling highway. The QDS1F updates its signaling buffer every other frame. The QDS1F can only update the line once every six frames for signaling. The transmit framing format and signaling format are shown in Figure 7.

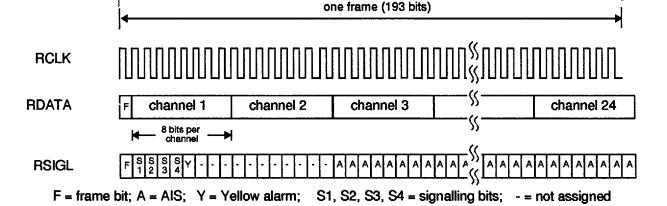

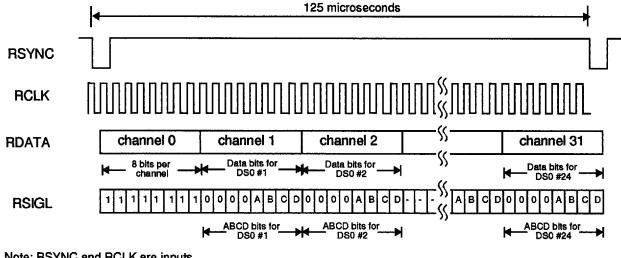

In MVIP mode the receive highway carries information from the framer to the system. The highway is subdivided into two time division multiplexed buses, one for the data (RDATA), and one for signaling, RSIGL. These two buses are synchronous with the signal RCLK, a 2.048 MHz clock, driven from the system. The data highway is a single bit-serial bus organized into 256-bit groups called frames. Each frame consists of thirty two 8-bit data samples representing 32 DS0s. The 24 DS0s received from the line are mapped to the 32 DS0s of the receive data highway as follows:

| Rec. Hwy<br>Channel<br>No. | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

|----------------------------|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| DS1 DS0<br>No.             | х | 1 | 2 | 3 | Х | 4 | 5 | 6 | х | 7 | 8  | 9  | х  | 10 | 11 | 12 | х  | 13 | 14 | 15 | х  | 16 | 17 | 18 | х  | 19 | 20 | 21 | х  | 22 | 23 | 24 |

Taaj

The frame start is identified by a synchronization pulse, RSYNC, which occurs once per frame (125 microseconds) and is supplied by the system. RSYNC is programmable for the device to any bit position in the frame; the default position occurs coincident with the first bit of receive highway channel 0 (see control bits RSD7-RSD0 at address 017H). The signaling highway, RSIGL, is also divided into 256-bit frames. Each frame consists of 32 DS0 positions 24 of which carry the ABCD signaling bits associated with the DS0s on the data highway. The same positions used for the DS0s are used for the signaling bits. The signaling bits occupy the last four bits of the DS0 on the signaling highway. The QDS1F updates the signaling highway from its signaling buffer every frame. The QDS1F receive signaling buffer is only updated by the line once every six frames for signaling. The receive framing format and signaling format are shown in Figure 8.

Note: RSYNC and RCLK are inputs Note: RSD7-RSD0 = 00 Hex

In MVIP mode only, the frame sync pulses, RSYNC and TSYNC, may be delayed up to four clock pulses in integral numbers of clock periods (RCLK or TCLK). This allows the system side to run an overspeed clock. The effect is to always restart the data and signaling highways during transmit or receive highway channel number 0 (if an offset is programmed, the change is delayed by the value of the offset); in effect channel 0 can become 9, 10, 11 or 12 bits long. Since the framer does not process or supply data in channel 0 there is no effect on framer performance.

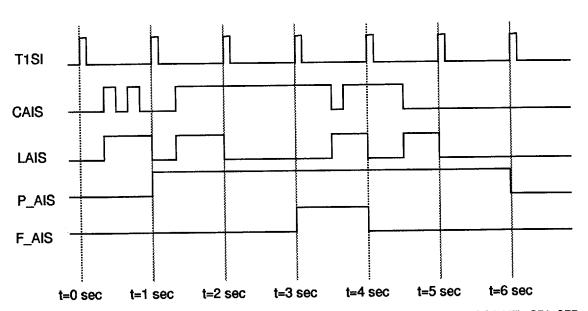

The System Interface provides payload loopbacks for each of the individual framers. The System Interface also accepts a single local oscillator input (LO) for use in the Framer blocks for Transmit Slip Buffer operation or AIS generation without TCLK present. T1SI is a one second clock used to operate shadow registers and freeze counter values, allowing polled service of the framers for performance and fault monitoring. The two mode select pins, CONFIG(2-1), are used to select transmission or MVIP modes and serial interface or DS1 monitor modes. Pin CSO is used to force the line interface output pins (LTCLK, TPOS/TLDAT and TNEG/TMODE) low for redundancy configurations.

Figure 8. System Interface Receive Format for MVIP Mode

## PER CHANNEL (FRAMER) BLOCK OPERATION

Each Framer block consists of a Receive Line Interface, a Receive Framer, a Receive Slip Buffer and a Receive Signaling block for the line to terminal direction. In the terminal to line direction each Framer block consists of a Transmit Slip Buffer, a Transmit Signaling block, a Transmit Framer and a Transmit Line Interface. Each Framer block also has a Facility Data Link block and it provides three forms of loopback. All of these blocks, and the loopback features, framing structure and miscellaneous functions of the Framer blocks, are described in the following subsections.

#### **Receive Line Interface Operation**