## AN1374 APPLICATION NOTE

# VIPower: COMPLEMENTARY DOUBLE OUTPUT NON ISOLATED POWER SUPPLY BASED ON VIPer12A

N. Aiello - F. Gennaro - R. Santori

#### 1. INTRODUCTION

In this paper a low cost solution for power converters with double complementary output is introduced, suitable for low power non isolated applications that require both positive and negative voltage.

The proposed topologies are based on the "Buck" o ("Step-down") or "Buck-boost" (o "Step up/down") converter and use only one inductor to provide double complementary output, and can be easily realized using one of the VIPer family regulators.

Such converters have been implemented with VIPer12A, a very low cost monolithic smart power with an integrated PWM controller. The device is suitable for off-line applications since it consists in a high voltage Power MOSFET with 730V breakdown voltage.

In isolated converters, a second output is usually generated by means of one more winding on the magnetic core of the inductor with a suitable turns ratio n, as shown in figure 1. Although this method is a good solution either for medium-high output current or isolated outputs, it is not cost effective for non isolated low power converters. In fact, for low output current, an off-the-shelf isolated inductor is commonly used, reducing both the cost and the size of the converter.

$\begin{array}{c|c} & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & &$

Figure 1: Typical circuit for double output non isolated converter

April 2001 1/14

#### 2. THE PROPOSED NON ISOLATED SOLUTION

The proposed converter uses only one inductor to provide a double output with reversed polarity. The second complementary output is generated charging a capacitor during the free-wheeling of the inductor current. The voltage across the capacitor is regulated by means of a zener diode of suitable value.

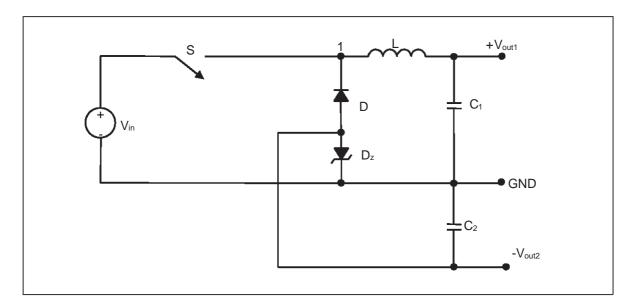

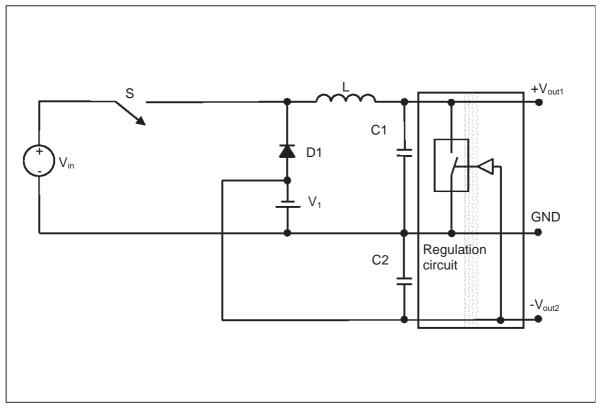

The schematic of the circuit based on Buck converter is shown in figure 2. The power switch is operated at high frequency for power conversion. The voltage is then filtered by the LC filter, L and  $C_1$ . In the standard topology the voltage of the node 1 is clamped by the diode D, allowing the free-wheeling of the inductor current. In the proposed solution, the zener diode,  $D_Z$ , clamps such a voltage to  $(V_d+V_Z)$ , where  $V_d$  is the voltage drop across the diode and  $V_Z$  the zener voltage. If a capacitor is connected across the zener and the ground, a negative voltage source is generated. Of course, due to the principle of operation, the second output cannot supply more current than the first one.

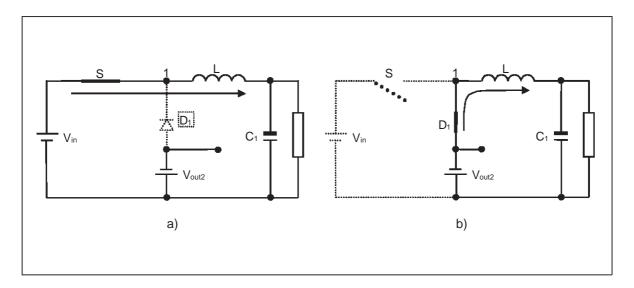

The switching cycle can be basically divided in two periods as shown in figure 3. Considering discontinuous conduction mode, DCM - see AN1357 - during the conduction of the switch S,  $t_{on}$ , the input DC bus is connected to the output and supplies the load, as shown in figure 3a). Once the switch is turned off, the inductor current free-wheels through the diode  $D_1$ , as shown in figure 3b), until it zeroes and the output capacitor  $C_1$  feeds the load.

Figure 2: The proposed solution in Buck configuration

2/14

Figure 3: Functional circuit of the proposed Buck converter: a)  $t_{on}$ , b)  $t_{off}$

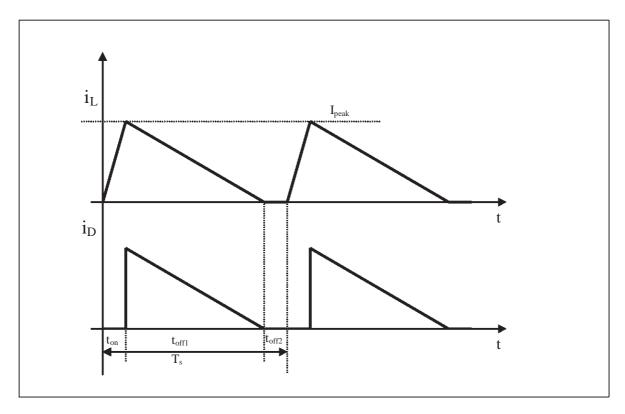

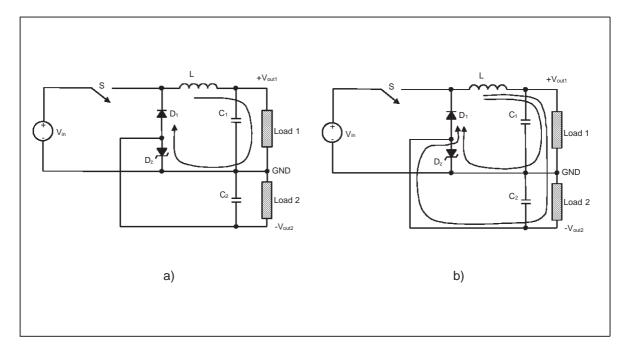

Typical current waveforms in DCM are shown in figure 4. The presence of the zener diode in the free-wheeling path does not affect the basic operation of the converter but it could impact the efficiency. In order to understand how the zener diode affects the efficiency of the converter, figure 5 can be considered. If there is no load on  $OUT_2$ , the free-wheeling current flows through both diodes,  $D_1$  and  $D_2$ , with a power dissipation given by (1) and (2).

$$P_{lossD} = V_f \cdot I_{Davg}$$

(1)

$$P_{lossDz} = V_z \cdot I_{Dzavg}$$

(2)

where:

$$I_{Davg} = I_{Dzavg} = \frac{1}{T_s} \int_0^{T_s} i_D(t) dt$$

(3)

where  $T_s$  is the switching period and  $i_D(t)$  is the diode current. Considering the typical diode current waveform shown in figure 4, (3) can be written as (4).

$$I_{Davg} = I_{Dzavg} = \frac{1}{2} \cdot \frac{1}{T_s} \cdot I_{pk} \cdot t_{off1}$$

(4)

Figure 4: Typical current waveforms

**Figure 5:** Effect of zener diode on power conversion: a)  $I_{load2}$ =0, b)  $I_{load2}$ ≠0

As the current drawn from  $OUT_2$  increases, the free-wheeling current flows through a different path, splitting in two components as shown in figure 5b). In this way the power dissipation in  $D_Z$  is reduced and the efficiency is increased accordingly. Thus the converter performs better if the complementary output is loaded, for a given output current  $I_{out1}$ .

The selection of both output capacitors depends on the output ripple specification. A proper  $C_2$  selection has to be made taking into account that the complementary output is somehow related to the main output. For proper operation of the zener diode, a minimum breakdown current is required, which value is related to the rated power of the device. Since the current flowing through the zener is given by (5), the maximum current drawn from the complementary output at nominal voltage is limited by such a minimum current. Moreover, the precision of  $V_{out2}$  is given by the precision of the zener voltage that depends on the rated power and voltage of the diode, and on the current through it.

$$I_{D_7} = I_{out1} - I_{out2} \tag{5}$$

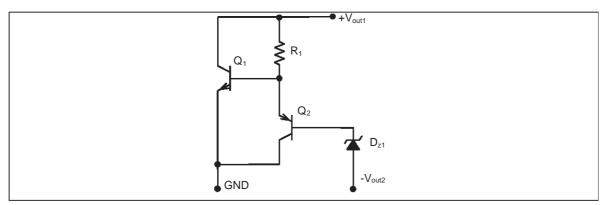

If decoupled outputs are required, a suitable control circuit has to be used, as shown in figure 6. This circuit works like a dummy load and can be easily implemented with very low cost components. As drawn in figure 7, the circuit consists in two transistors,  $Q_1$  and  $Q_2$ , e.g. a pnp and a npn BJT, a resistor  $R_1$  and a zener diode  $D_{Z1}$ . The transistor  $Q_1$ , driven by  $Q_2$  and  $Q_3$ , assures a given current in L regardless of the load supplied by  $V_{out1}$ . Doing so,  $I_{out2}$  can be varied regardless of  $I_{out1}$  and is only limited by the maximum allowable  $I_{out1}$ .

Figure 6: Double-output regulated converter in Buck configuration

5/14

Figure 7: Second output regulation circuit for Buck converter

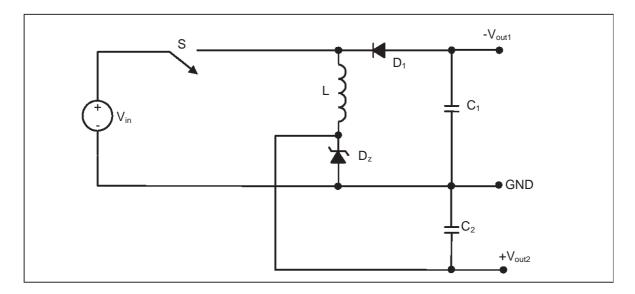

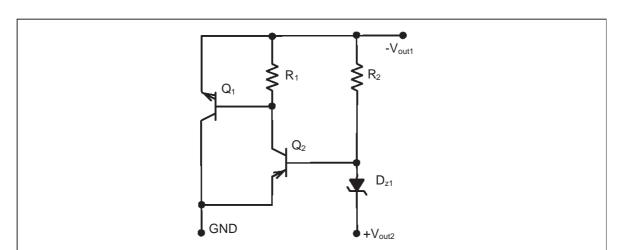

The proposed solution can be used with a Buck-boost converter as well, where the main output has negative polarity, as shown in figure 8. In such a case the regulation circuit can be realized as drawn in figure 9.

Figure 8: The proposed solution in Buck-boost configuration

Figure 9: Second output regulation circuit for Buck-boost converter

#### 3. APPLICATION EXAMPLE WITH VIPer12A

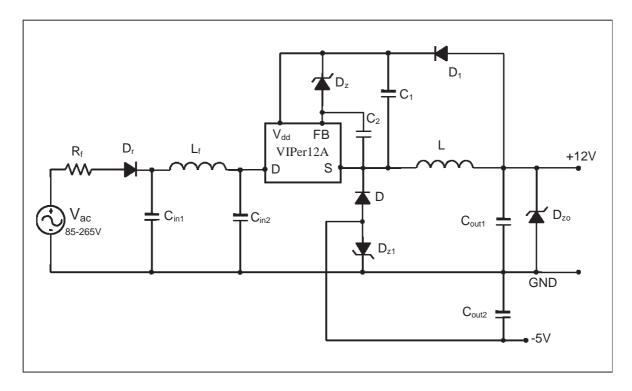

In this section an application example with VIPer12A is described. The converter is based on Buck topology and features two outputs:  $V_{out1}$ =12V-100mA and  $V_{out2}$ =-5V. In table 1 the converter specifications are listed. The power supply operates in wide range voltage, i.e. 85-265Vac, and is designed to operate in DCM.

A single diode rectification is used to limit the cost and the input fuse is replaced with a suitable resistor. A simple input CLC EMI filter is connected but it could be removed thanks to the low emission related to the power level. In table 2 the part list of the considered power supply is given. Details on the design of the input stage as well as layout considerations and VIPer12 basics in non isolated applications, can be found in AN1357. The VIPer12A makes the power supply short circuit protected. In fact if a short circuit appears on  $OUT_1$  the restart mode is entered, limiting the power dissipation. On the other hand, if a short circuit appears on  $OUT_2$ , the converter operates as a conventional Buck converter with  $V_{out1}$  given by  $D_7$ .

Table 1: Buck converter specifications

| AC input voltage                 | 85 - 265Vac |

|----------------------------------|-------------|

| Output current I <sub>out1</sub> | 100mA       |

| Output voltage 1                 | +12V        |

| Output voltage 2                 | -5V         |

Figure 10: Application example: 12V-100mA power supply

Table 2: Components list

| REFERENCE         | VALUE                   | PART NUMBER |

|-------------------|-------------------------|-------------|

| R <sub>f</sub>    | 10Ω / 1/2W              |             |

| C <sub>in1</sub>  | 1μF / 400V Electrolytic |             |

| C <sub>in2</sub>  | 1μF / 400V Electrolytic |             |

| C <sub>1</sub>    | 10μF / 25V Electrolytic |             |

| C <sub>2</sub>    | 22nF / 25V Ceramic      |             |

| C <sub>out1</sub> | 33μF / 25V Electrolytic |             |

| C <sub>out2</sub> | 10μF / 25V Electrolytic |             |

| D <sub>r</sub>    | 1A - 1000V              | 1N4007      |

| D                 | 1A - 600V               | STTA106     |

| D <sub>1</sub>    | 1A - 600V               | STTA106     |

| $D_Z$             | 16V Zener               |             |

| $D_{Z0}$          | 18V Zener               |             |

| $D_{Z1}$          | 5.1V Zener              |             |

| L                 | 1.5mH                   |             |

| L <sub>f</sub>    | 470μΗ                   |             |

| I <sub>C1</sub>   |                         | VIPer12ADIP |

### 3.1 EXPERIMENTAL RESULTS

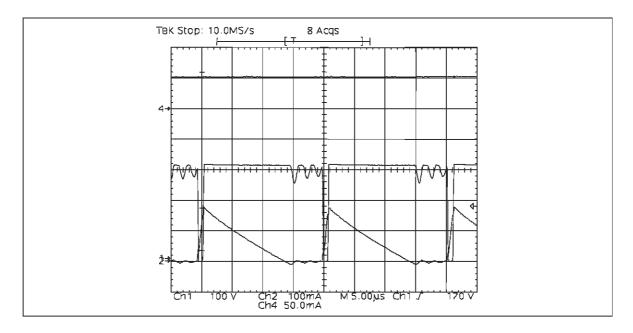

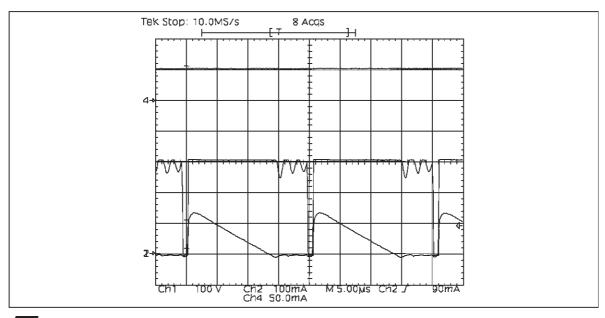

In this section some experimental waveforms are shown and a performance evaluation is carried out in terms of line and load regulation as well as efficiency. In figures 11 and 12 typical waveforms of the Buck based converter are shown: the voltage across the power device,  $V_{DS}$ , the output current, the inductor and the diode currents with  $V_{in(ac)} = 220 V_{rms}$ .

Figure 11:  $I_{out1}$ =50mA (Ch 4):  $V_{ds}$  (Ch 1) at 220Vac and  $I_{L}$  (Ch 2)

Figure 12:  $I_{out1}$ =50mA (Ch 4):  $V_{ds}$  (Ch 1) at 220Vac and  $I_{D}$  (Ch 2)

The static performance of the power supply can be evaluated from figure 13 that shows  $OUT_1$  voltage ripple, limited to  $50mV_{pp}$ , i.e. less than 0.5%, with a small and low cost output capacitor.

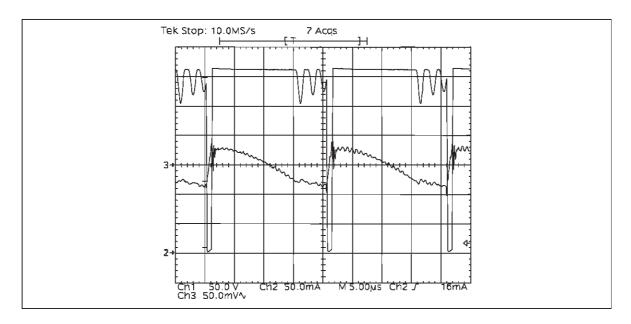

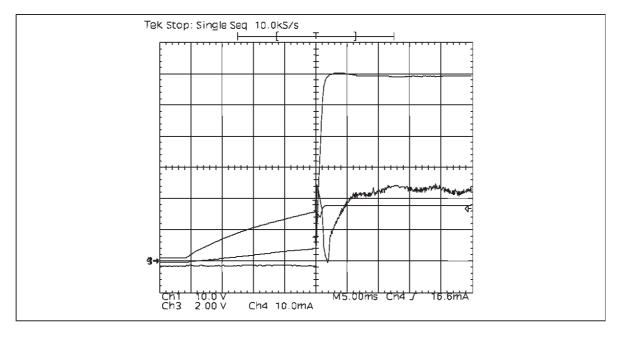

The start-up of the converter is quite fast and takes some ms as shown in figure 14, where are traced  $V_{dd}$  voltage, output voltage and current with  $V_{in(ac)} = 220 V_{rms}$ .

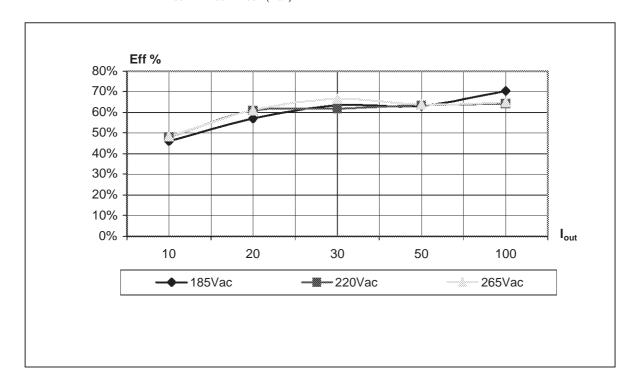

Figure 13: Efficiency Vs.  $I_{out1}$  at  $I_{out2}$ =0A

Figure 14: Start up transient at 220Vac:  $V_{dd}$  (Ch 1),  $V_{out1}$  (Ch 3) =12V and  $I_{out1}$ =25mA (Ch 4).

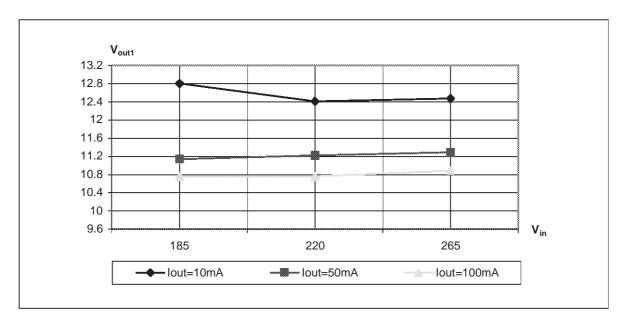

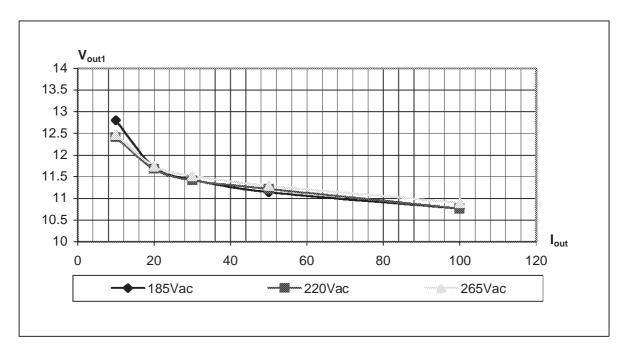

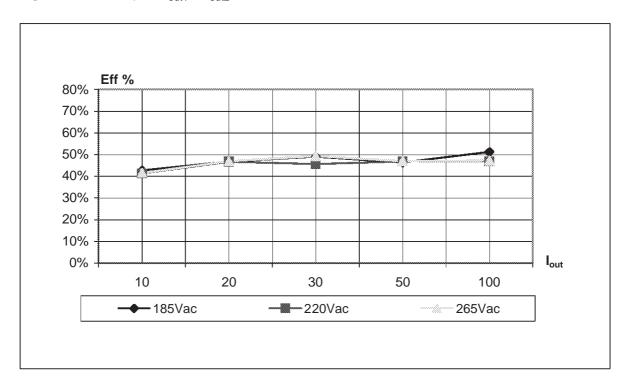

Line and load regulation diagrams are shown in figures 15 and 16 respectively. The efficiency of the power supply has been evaluated under two different operating conditions: 1)  $I_{out2}=0$  and 2)  $I_{out2}=I_{out2(max)}$ . As explained in Section 2, the efficiency improves up to 70% as  $I_{out2}$  increases for a given  $I_{out1}$ .

Figure 15: Line regulation

Figure 16: Load regulation

Figure 17: Efficiency Vs.  $I_{out1}$  at  $I_{out2}$ =0

Figure 18: Efficiency Vs.  $I_{out1}$  at  $I_{out2}$ = $I_{out2(max)}$

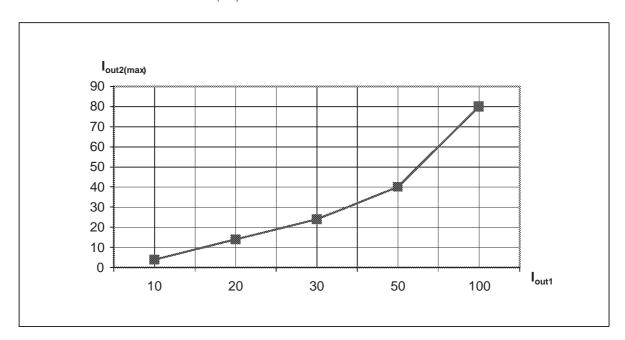

Figure 19 shows the relationship between  $I_{out1}$  and  $I_{out2}$  with no regulation circuit on the second output, where  $I_{out2(max)}$  is the maximum value of the negative output current considering a minimum output voltage as low as 4V, i.e. with 20% voltage decrease. If this value is not suitable for the considered application or the current required from the negative output could be higher than the current drawn from the positive one, the regulation circuit described in Section 2 has to be used.

Figure 19: Maximum I<sub>out2</sub> for V<sub>out2(min)</sub>=4V

#### 4. CONCLUSION

A simple and low cost solution for low power off-line power supplies has been introduced. The topology allows to obtain two complementary outputs by means of a single inductor, with high efficiency and good overall performance in terms of load and line regulation. In such a way there is no need of any linear post regulator improving efficiency and reducing the size and cost of the supply. The considered topology can be realized with other devices of the VIPer family.

For further information about SMPS PWM controller ICs please consult the VIPower web pages at: http://www.st.com/vipower

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may results from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

© 2001 STMicroelectronics - Printed in ITALY- All Rights Reserved.

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.

http://www.st.com