# 256K x 8 CMOS FLASH MEMORY WITH LPC INTERFACE

#### **GENERAL DESCRIPTION**

The W49V002 is a 2-megabit, 3.3V-volt only CMOS flash memory organized as  $256K \times 8$  bits. The device can be programmed and erased in-system with a standard 3.3V power supply. A 12-volt VPP is not required. The unique cell architecture of the W49V002 results in fast program/erase operations with extremely low current consumption. This device can operate at two modes, Programmer bus interface mode and LPC bus interface mode. As in the Programmer interface mode, it acts like the traditional flash but with a multiplexed address inputs. But in the LPC interface mode, this device complies with the Intel LPC specification 1.0. The device can also be programmed and erased using standard EPROM programmers.

#### **FEATURES**

- •Single 3.3-volt operations:

- 3.3-volt Read

- 3.3-volt Erase

- 3.3-volt Program

- Fast Program operation:

- Byte-by-Byte programming: 50 μS (typ.)

- Fast Erase operation: 150 mS (typ.)

- Endurance: 10K cycles (typ.)

- · Twenty-year data retention

- · Hardware data protection

- One 16K bytes Boot Block with lockout protection

- Two 8K bytes Parameter Blocks

- Four Main Memory Blocks (with 32K bytes,

64K bytes, 64K bytes, 64K bytes each)

- Low power consumption

- Active current: 25 mA (typ.)

- Standby current: 20 μA (typ.)

- Automatic program and erase timing with internal VPP generation

- · End of program or erase detection

- Toggle bit

- Data polling

- · Latched address and data

- TTL compatible I/O

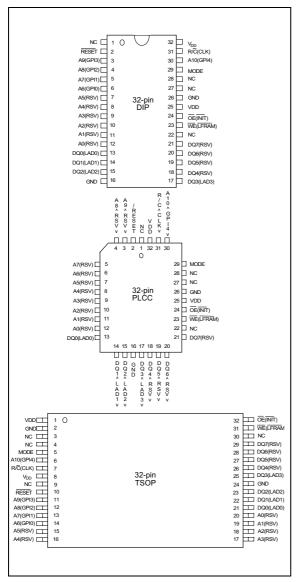

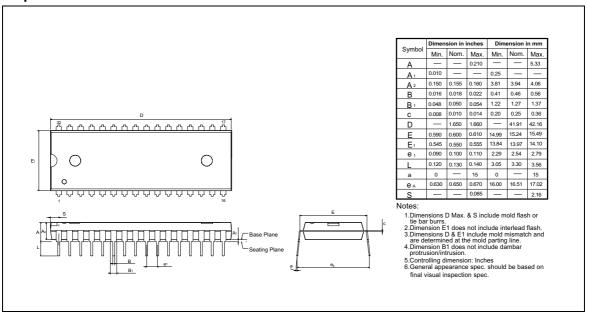

- Available packages: 32-pin DIP and 32-pin TSOP and 32-pin-PLCC

### **PIN CONFIGURATIONS**

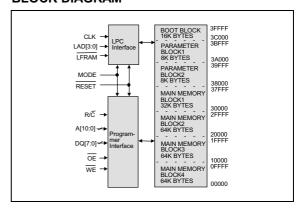

#### **BLOCK DIAGRAM**

#### **PIN DESCRIPTION**

| SYMB         | INTER | FACE | PIN NAME                    |

|--------------|-------|------|-----------------------------|

|              | PGM   | LPC  |                             |

| MODE         | *     | *    | Interface Mode<br>Selection |

| RESET        | *     | *    | Reset                       |

| ĪNIT         |       | *    | Initialize                  |

| CLK          |       | *    | CLK Input                   |

| GPI[4:0]     |       | *    | General Purpose Inputs      |

| LAD[3:0]     |       | *    | Address/Data Inputs         |

| <b>LFRAM</b> |       | *    | LPC Cycle Initial           |

| R/C          | *     |      | Row/Column Select           |

| A[10:0]      | *     |      | Address Inputs              |

| DQ[7:0]      | *     |      | Data Inputs/Outputs         |

| ŌE           | *     |      | Output Enable               |

| WE           | *     |      | Write Enable                |

| VDD          | *     | *    | Power Supply                |

| GND          | *     | *    | Ground                      |

| RSV          | *     | *    | Reserve Pins                |

| NC           | *     | *    | No Connection               |

#### **FUNCTIONAL DESCRIPTION**

#### **Interface Mode Selection And Description**

This device can be operated in two interface modes, one is Programmer interface mode, the other is LPC interface mode. The MODE pin of the device provides the control between these two interface modes. These interface modes need to be configured before power up or return from  $\overline{RESET}$ . When MODE pin is set to high state, the device is in the Programmer mode; while the MODE pin is set to low state(or leaved no connection), it is in the LPC mode. In Programmer mode, this device just behaves like traditional flash parts with 8 data lines. But the row and column address inputs are multiplexed. The row address are mapped to the higher internal address A[17:11]. And the column address are mapped to the lower internal address A[10:0]. For LPC mode, It complies with the LPC Interface Specification Revision 1.0. Through the LAD[3:0] and  $\overline{LFRAM}$  to communicate with the system chipset .

#### Read(Write) Mode

In Programmer interface mode, the read(write) operation of the W49V002 is controlled by OE(WE). The OE(WE) is held low for the host to obtain(write) data from(to) the outputs(inputs). OE is the output control and is used to gate data from the output pins. The data bus is in high impedance state when OE is high. As in the LPC interface mode, the read or write is determined by the "bit 1 of CYCLE TYPER+DIR". Refer to the timing waveforms for further details.

### **Reset Operation**

The  $\overline{RESET}$  input pin can be used in some application. When  $\overline{RESET}$  pin is at high state, the device is in normal operation mode. When  $\overline{RESET}$  pin is at low state, it will halt the device and all outputs will be at high impedance state. As the high state re-asserted to the  $\overline{RESET}$  pin, the device will return to read or standby mode, it depends on the control signals.

#### **Boot Block Operation**

There is a 16K-byte boot block in this device, which can be used to store boot codes. It is located in the first 16K bytes of the memory with the address range from 3C000(hex) to 3FFFF(hex).

See Command Codes for Boot Block Lockout Enable for the specific code. Once this feature is set the data for the designated block cannot be erased or programmed (programming lockout), other memory locations can be changed by the regular programming method.

In order to detect whether the boot block feature is set on the 16K-bytes block or not, users can perform software command sequence: enter the product identification mode (see Command Codes for Identification/Boot Block Lockout Detection for specific code), and then read from address 0002(hex). If the DQ0 of output data is "1," the boot block programming lockout feature will be activated; if the DQ0 of output data is "0," the lockout feature will be inactivated and the block can be erased/programmed.

To return to normal operation, perform a three-byte command sequence (or an alternate single-byte command) to exit the identification mode. For the specific code, see Command Codes for Identification/Boot Block Lockout Detection.

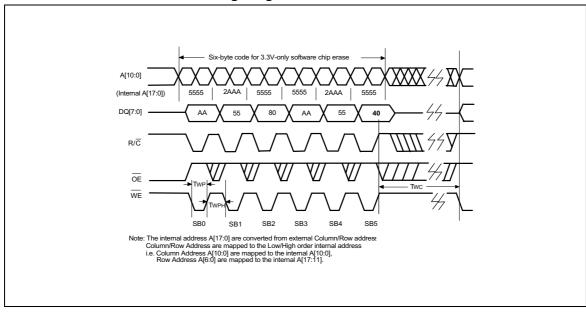

#### **Chip Erase Operation**

The chip-erase mode can be initiated by a six-byte command sequence. After the command loading cycle, the device enters the internal chip erase mode, which is automatically timed and will be

completed within fast 100 mS (typical). The host system is not required to provide any control or timing during this operation. If the boot block programming lockout is activated, only the data in the other memory blocks will be erased to FF(hex) while the data in the boot block will not be erased (remains as the same state before the chip erase operation). The entire memory array will be erased to FF(hex) by the chip erase operation if the boot block programming lockout feature is not activated. The device will automatically return to normal read mode after the erase operation completed. Data polling and/or Toggle Bits can be used to detect end of erase cycle.

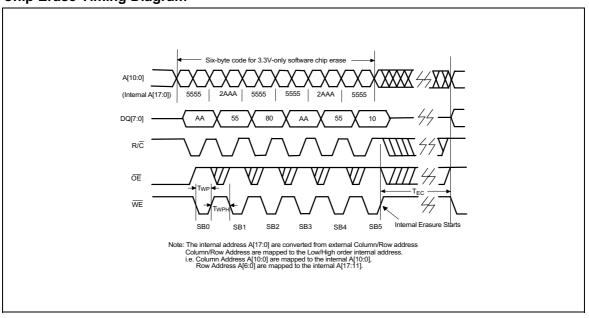

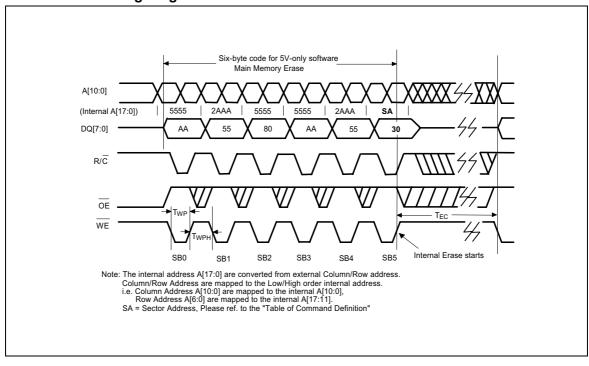

#### **Sector Erase Operation**

The six sectors, two main memory and four parameter blocks, can be erased individually by initiating a six-byte command sequence. Sector address is latched on the falling  $\overline{\text{WE}}$  edge of the sixth cycle, while the 30(hex) data input command is latched at the rising edge of  $\overline{\text{WE}}$ . After the command loading cycle, the device enters the internal sector erase mode, which is automatically timed and will be completed within fast 100 mS (typical). The host system is not required to provide any control or timing during this operation. The device will automatically return to normal read mode after the erase operation completed. Data polling and/or Toggle Bits can be used to detect end of erase cycle.

Whether the boot block is locked or not, only the main memory and parameter blocks will be erased by the execution of sector erase operation. Boot block can only be erased by chip erase command under lock out feature inactivated.

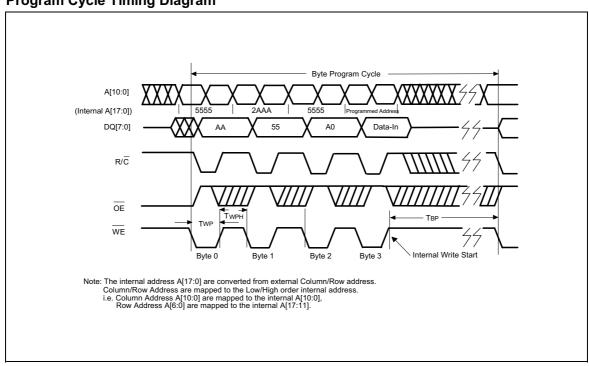

#### **Program Operation**

The W49V002 is programmed on a byte-by-byte basis. Program operation can only change logical data "1" to logical data "0." The erase operation, which changed entire data in main memory and/or boot block from "0" to "1", is needed before programming.

The program operation is initiated by a 4-byte command cycle (see Command Codes for Byte Programming). The device will internally enter the program operation immediately after the byte-program command is entered. The internal program timer will automatically time-out (100  $\mu$ S max. - TBP) once it is completed and then return to normal read mode. Data polling and/or Toggle Bits can be used to detect end of program cycle.

#### **Hardware Data Protection**

The integrity of the data stored in the W49V002 is also hardware protected in the following ways:

- (1) Noise/Glitch Protection: A WE pulse of less than 15 nS in duration will not initiate a write cycle.

- (2)  $\mbox{VDD}$  Power Up/Down Detection: The programming operation is inhibited when  $\mbox{VDD}$  is less than 2.5V typical.

- (3) Write Inhibit Mode: Forcing OE low or WE high will inhibit the write operation. This prevents inadvertent writes during power-up or power-down periods.

- (4) VDD power-on delay: When VDD has reached its sense level, the device will automatically time-out 5 mS before any write (erase/program) operation.

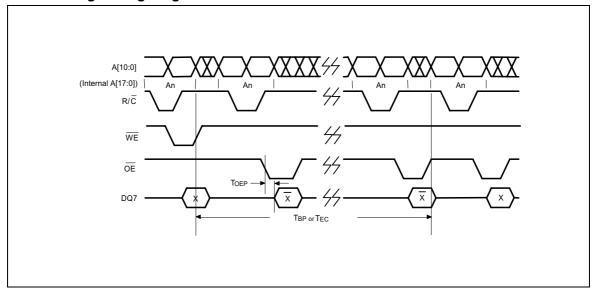

#### **Data Polling (DQ7)- Write Status Detection**

The W49V002 includes a data polling feature to indicate the end of a program or erase cycle. When the W49V002 is in the internal program or erase cycle, any attempts to read DQ7 of the last byte loaded will receive the complement of the true data. Once the program or erase cycle is completed, DQ7 will show the true data. Note that DQ7 will show logical "0" during the erase cycle, and when erase cycle has been completed it becomes logical "1" or true data.

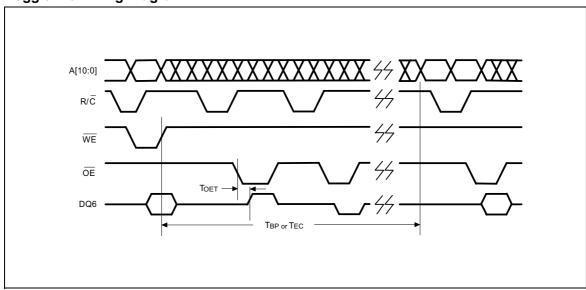

#### Toggle Bit (DQ6)- Write Status Detection

In addition to data polling, the W49V002 provides another method for determining the end of a program cycle. During the internal program or erase cycle, any consecutive attempts to read DQ6 will produce alternating 0's and 1's. When the program or erase cycle is completed, this toggling between 0's and 1's will stop. The device is then ready for the next operation.

#### **Memory Address Map**

There are 8M bytes space reserved for BIOS Addressing. The ROM will respond to 256K byte pages whenever the memory address rang is within the top 4M bytes and bottom 128K bytes.

The 32bit address space is as below:

| Block              | Address Range         |

|--------------------|-----------------------|

| 4M Byte BIOS ROM   | FFFF,FFFFh:FFC0,0000h |

| 128K Byte BIOS ROM | 000F,FFFFh:000E,0000h |

| Registers          | FFBC,0100h            |

#### **General Purpose Inputs Register**

This register reads the GPI[4:0] pins on the W49V002. This is a pass-through register which can read via memory address FFBC0100(hex). Since it is pass-through register, there is no default value.

| Bit | Function             |

|-----|----------------------|

| 7-5 | Reserved             |

| 4   | Read GPI4 pin status |

| 3   | Read GPI3 pin status |

| 2   | Read GPI2 pin status |

| 1   | Read GPI1 pin status |

| 0   | Read GPI0 pin status |

#### **Product Identification**

The product ID operation outputs the manufacturer code and device code. Programming equipment automatically matches the device with its proper erase and programming algorithms.

The manufacturer and device codes can be accessed by software or hardware operation. In the software access mode, a six-byte (or JEDEC 3-byte) command sequence can be used to access the product ID. A read from address 0000(hex) outputs the manufacturer code, DA(hex). A read from address 0001(hex) outputs the device code, B0(hex)." The product ID operation can be terminated by a three-byte command sequence or an alternate one-byte command sequence (see Command Definition table).

#### **TABLE OF OPERATING MODES**

### **Operating Mode Selection - Programmer Mode**

$(V_{HH} = 12V \pm 5\%)$

| 124 2070       |      |     |       |         |             |

|----------------|------|-----|-------|---------|-------------|

| MODE           | PINS |     |       |         |             |

|                | ŌE   | WE  | RESET | ADDRESS | DQ.         |

| Read           | VIL  | VIH | VIH   | AIN     | Dout        |

| Write          | VIH  | VIL | VIH   | AIN     | Din         |

| Standby        | Х    | Х   | VIL   | Х       | High Z      |

| Write Inhibit  | VIL  | Х   | VIH   | Х       | High Z/DOUT |

|                | Χ    | VIH | VIH   | Х       | High Z/DOUT |

| Output Disable | VIH  | Х   | VIH   | X       | High Z      |

### **Operating Mode Selection - LPC Mode**

Operation modes in LPC interface mode are determined by "cycle type" when it is selected. When it is not selected, its outputs (LAD[3:0]) will be disable. Please reference to the "Standard LPC Memory Cycle Definition".

#### **TABLE OF COMMAND DEFINITION**

| COMMAND             | NO. OF | 1ST CYCLE                        | 2ND CYCLE  | 3RD CYCLE  | 4TH CYCLE                       | 5TH CYCLE  | 6TH CYCLE  |

|---------------------|--------|----------------------------------|------------|------------|---------------------------------|------------|------------|

| DESCRIPTION         | Cycles | Addr. Data                       | Addr. Data | Addr. Data | Addr. Data                      | Addr. Data | Addr. Data |

| Read                | 1      | A <sub>IN</sub> D <sub>OUT</sub> |            |            |                                 |            |            |

| Chip Erase          | 6      | 5555 AA                          | 2AAA 55    | 5555 80    | 5555 AA                         | 2AAA 55    | 5555 10    |

| Sector Erase        | 6      | 5555 AA                          | 2AAA 55    | 5555 80    | 5555 AA                         | 2AAA 55    | SA 30      |

| Byte Program        | 4      | 5555 AA                          | 2AAA 55    | 5555 A0    | A <sub>IN</sub> D <sub>IN</sub> |            |            |

| Boot Block Lockout  | 6      | 5555 AA                          | 2AAA 55    | 5555 80    | 5555 AA                         | 2AAA 55    | 5555 40    |

| Product ID Entry    | 3      | 5555 AA                          | 2AAA 55    | 5555 90    |                                 |            |            |

| Product ID Exit (1) | 3      | 5555 AA                          | 2AAA 55    | 5555 F0    |                                 |            |            |

| Product ID Exit (1) | 1      | XXXX F0                          |            |            |                                 |            |            |

Note: 1. The cycle means the write command cycle not the LPC clock cycle.

- 2. The Column Address / Row Address are mapped to the Low / High order Internal Address. i.e. Column Address A[10:0] are mapped to the internal A[10:0], Row Address A[6:0] are mapped to the internal A[17:11]

- 3. Address Format: A14–A0 (Hex); Data Format: DQ7-DQ0 (Hex)

- 4. Either one of the two Product ID Exit commands can be used.

- 5. SA: Sector Address

- SA = 3A000h to 3BFFFh for Parameter Block1

- SA = 38000h to 39FFFh for Parameter Block2

- SA = 30000h to 37FFFh for Main Memory Block1

- SA = 2XXXXh for Main Memory Block2

- SA = 1XXXXh for Main Memory Block3

- SA = 0XXXXh for Main Memory Block4

### STANDARD LPC MEMORY CYCLE DEFINITION

| FIELD            | NO. OF CLOCKS | DESCRIPTION                                                                                                                                                                                                                                    |

|------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Start            | 1             | "0000b" appears on LPC bus to indicate the initial                                                                                                                                                                                             |

| Cycle Type & Dir | 1             | "010Xb" indicates memory read cycle; while "011xb" indicates memory write cycle. "X" mean don't have to care.                                                                                                                                  |

| TAR              | 2             | Turned Around Time                                                                                                                                                                                                                             |

| Addr.            | 8             | Address Phase for Memory Cycle. LPC supports the 32 bits address protocol. The addresses transfer most significant nibble first and least significant nibble last. (i.e. Address[31:28] on LAD[3:0] first, and Address[3:0] on LAD[3:0] last.) |

| Sync.            | N             | Synchronous to add wait state. "0000b" means Ready, "0101b" means Short Wait, "0110b" means Long Wait, "1001b" for DMA only, "1010b" means error, and other values are reserved.                                                               |

| Data             | 2             | Data Phase for Memory Cycle. The data transfer least significant nibble first and most significant nibble last. (i.e. DQ[3:0] on LAD[3:0] first , then DQ[7:4] on LAD[3:0] last.)                                                              |

- 7 -

Note: 1. For detail related LPC specification, please refer to Intel LPC spec. 1.0 or later.

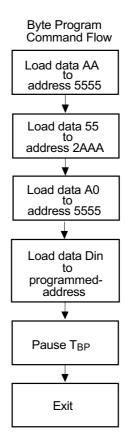

**Command Codes for Byte Program**

| BYTE SEQUENCE | ADDRESS            | DATA            |

|---------------|--------------------|-----------------|

| 0 Write       | 5555H              | AAH             |

| 1 Write       | 2AAAH              | 55H             |

| 2 Write       | 5555H              | A0H             |

| 3 Write       | Programmed-Address | Programmed-Data |

# **Byte Program Flow Chart**

Notes for software program code: Data Format: DQ7–DQ0 (Hex); XX = Don't Care Address Format: A14–A0 (Hex)

# **Command Codes for Chip Erase**

| BYTE SEQUENCE | ADDRESS | DATA |

|---------------|---------|------|

| 1 Write       | 5555H   | AAH  |

| 2 Write       | 2AAAH   | 55H  |

| 3 Write       | 5555H   | 80H  |

| 4 Write       | 5555H   | AAH  |

| 5 Write       | 2AAAH   | 55H  |

| 6 Write       | 5555H   | 10H  |

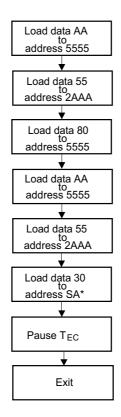

### **Chip Erase Acquisition Flow**

-9-

Notes for chip erase: Data Format: DQ7–DQ0 (Hex) Address Format: A14–A0 (Hex)

### **Command Codes for Sector Erase**

| BYTE SEQUENCE | ADDRESS | DATA |

|---------------|---------|------|

| 1 Write       | 5555H   | AAH  |

| 2 Write       | 2AAAH   | 55H  |

| 3 Write       | 5555H   | 80H  |

| 4 Write       | 5555H   | AAH  |

| 5 Write       | 2AAAH   | 55H  |

| 6 Write       | SA*     | 30H  |

### **Sector Erase Acquisition Flow**

Notes for chip erase:

Data Format: DQ7–DQ0 (Hex) Address Format: A14–A0 (Hex)

SA: Sector Address

SA = 3A000 to 3BFFF for Parameter Block1 SA = 38000 to 39FFF for Parameter Block2 SA = 30000 to 37FFF for Main Memory Block1 SA = 2XXXX for Main Memory Block2 SA = 1XXXX for Main Memory Block3 SA = 0XXXX for Main Memory Block4

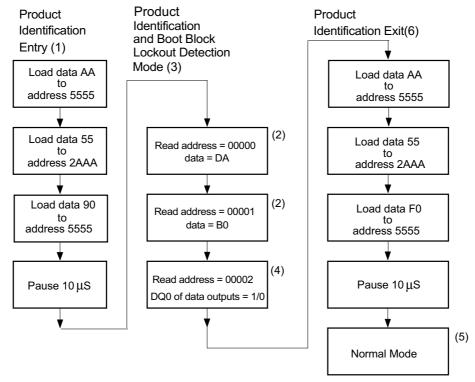

#### Command Codes for Product Identification and Boot Block Lockout Detection

| BYTE<br>SEQUENCE | SOFTWARE PRODUCT IDENTIFICATION / BOOT BLOCK LOCKOUT DETECTION ENTRY |    | SOFTWARE PRODUCT IDENTIFICATION /<br>BOOT BLOCK LOCKOUT DETECTION<br>EXIT (6) |        |

|------------------|----------------------------------------------------------------------|----|-------------------------------------------------------------------------------|--------|

|                  | ADDRESS DATA                                                         |    | ADDRESS                                                                       | DATA   |

| 1 Write          | 5555                                                                 | AA | 5555H                                                                         | AAH    |

| 2 Write          | 2AAA                                                                 | 55 | 2AAAH                                                                         | 55H    |

| 3 Write          | 5555                                                                 | 90 | 5555H                                                                         | F0H    |

|                  | Pause 10μS                                                           |    | Pause                                                                         | e 10μS |

### Software Product Identification and Boot Block Lockout Detection Acquisition Flow

Notes for software product identification/boot block lockout detection:

- (1) Data Format: DQ7-DQ0 (Hex); Address Format: A14-A0 (Hex)

- (2) A1–A17 = VIL; manufacture code is read for A0 = VIL; device code is read for A0 = VIH.

- (3) The device does not remain in identification and boot block lockout detection mode if power down.

- (4) If the DQ0 of output data is "1," the boot block programming lockout feature is activated; if the DQ0 of output data "0," the lockout feature is inactivated and the block can be programmed.

- (5) The device returns to standard operation mode.

- (6) Optional 1-write cycle (write F0 hex at XXXX address) can be used to exit the product identification/boot block lockout detection.

### **Command Codes for Boot Block Lockout Enable**

| BYTE SEQUENCE | BOOT BLOCK LOCKOUT FEATURE SET |      |  |

|---------------|--------------------------------|------|--|

|               | ADDRESS                        | DATA |  |

| 1 Write       | 5555H                          | AAH  |  |

| 2 Write       | 2AAAH                          | 55H  |  |

| 3 Write       | 5555H                          | 80H  |  |

| 4 Write       | 5555H                          | AAH  |  |

| 5 Write       | 2AAAH                          | 55H  |  |

| 6 Write       | 5555H                          | 40H  |  |

|               | Pause = T <sub>BP</sub>        |      |  |

# **Boot Block Lockout Enable Acquisition Flow**

Notes for boot block lockout enable: Data Format: DQ7–DQ0 (Hex) Address Format: A14–A0 (Hex)

### **DC CHARACTERISTICS**

# **Absolute Maximum Ratings**

| PARAMETER                                                  | RATING           | UNIT |

|------------------------------------------------------------|------------------|------|

| Power Supply Voltage to Vss Potential                      | -0.5 to +4.1     | V    |

| Operating Temperature                                      | 0 to +70         | °C   |

| Storage Temperature                                        | -65 to +150      | °C   |

| D.C. Voltage on Any Pin to Ground Potential                | -0.5 to VDD +0.5 | V    |

| Transient Voltage (<20 nS ) on Any Pin to Ground Potential | -1.0 to VDD +0.5 | V    |

Note: Exposure to conditions beyond those listed under Absolute Maximum Ratings may adversely affect the life and reliability of the device.

### **DC Operating Characteristics**

(VDD =  $3.3V \pm 10\%$ , VGND= 0V, TA = 0 to  $70^{\circ}$  C)

| PARAMETER                 | SYM. | TEST CONDITIONS                                                            | LIMITS |      | ITS      | UNIT |

|---------------------------|------|----------------------------------------------------------------------------|--------|------|----------|------|

|                           |      |                                                                            | MIN.   | TYP. | MAX.     |      |

| Power Supply<br>Current   | Icc  | In Read or Write mode, all DQs open Address inputs = 3.0V/0V, at f = 3 MHz | -      | 20   | 30       | mA   |

| Input Leakage<br>Current  | lu   | VIN = GND to VDD                                                           | -      | -    | 10       | μА   |

| Output Leakage<br>Current | ILO  | VOUT = GND to VDD                                                          | -      | -    | 10       | μА   |

| Input Low Voltage         | VIL  | -                                                                          | -0.3   | -    | 0.8      | V    |

| Input High Voltage        | ViH  | -                                                                          | 2.0    | -    | VDD +0.5 | V    |

| Output Low Voltage        | Vol  | IoL = 2.1 mA                                                               | -      | -    | 0.45     | V    |

| Output High Voltage       | Vон  | Iон = -0.1mA                                                               | 2.4    | -    | -        | V    |

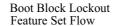

### **AC CHARACTERISTICS**

### **AC Test Conditions**

| PARAMETER                 | CONDITIONS                |

|---------------------------|---------------------------|

| Input Pulse Levels        | 0V to 0.9VDD              |

| Input Rise/Fall Time      | < 5 nS                    |

| Input/Output Timing Level | 1.5V/1.5V                 |

| Output Load               | 1 TTL Gate and CL = 30 pF |

# **AC Test Load and Waveform**

AC Characteristics, continued

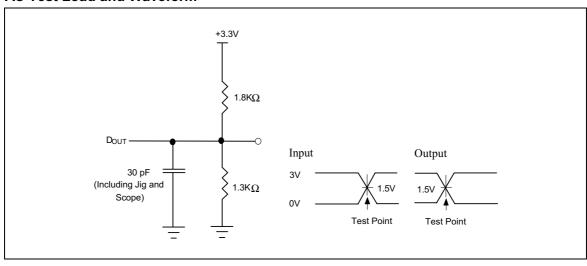

### **Read Cycle Timing Parameters**

(VDD =  $3.3V \pm 10\%$ , VGND = 0V, TA = 0 to  $70^{\circ}$  C)

| PARAMETER                        | SYM. | W49V002 |      | UNIT |

|----------------------------------|------|---------|------|------|

|                                  |      | MIN.    | MAX. |      |

| Read Cycle Time                  | Trc  | 300     | ı    | nS   |

| Row / Column Address Set Up Time | Tas  | 50      | ı    | nS   |

| Row / Column Address Hold Time   | Тан  | 50      | -    | nS   |

| Address Access Time              | Таа  | -       | 150  | nS   |

| Output Enable Access Time        | TOE  | -       | 75   | nS   |

| OE Low to Active Output          | Tolz | 0       | ī    | nS   |

| OE High to High-Z Output         | Тонz | -       | 35   | nS   |

| Output Hold from Address Change  | Тон  | 0       | ı    | nS   |

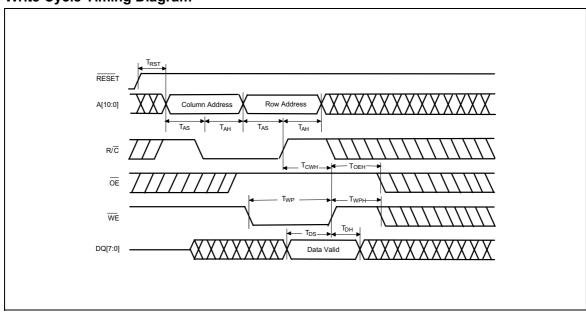

# **Write Cycle Timing Parameters**

| PARAMETER                      | SYMBOL | MIN. | TYP. | MAX. | UNIT |

|--------------------------------|--------|------|------|------|------|

| Reset Time                     | Trst   | 1    | -    | -    | μS   |

| Address Setup Time             | Tas    | 50   | -    | -    | nS   |

| Address Hold Time              | Тан    | 50   | -    | -    | nS   |

| R/ C to Write Enable High Time | Тсwн   | 50   | -    | -    | nS   |

| WE Pulse Width                 | Twp    | 100  | -    | ı    | nS   |

| WE High Width                  | TWPH   | 100  | -    | -    | nS   |

| Data Setup Time                | Tos    | 50   | -    | -    | nS   |

| Data Hold Time                 | TDH    | 50   | -    | -    | nS   |

| OE Hold Time                   | Тоен   | 0    | -    | -    | nS   |

| Byte programming Time          | Твр    | -    | 50   | 100  | μS   |

| Erase Cycle Time               | TEC    | -    | 0.15 | 0.2  | S    |

Note: All AC timing signals observe the following guidelines for determining setup and hold times:

$\begin{tabular}{ll} (a) High level signal's reference level is input high and (b) low level signal's reference level is input low. \\ \end{tabular}$

Ref. to the AC testing condition.

# **Data Polling and Toggle Bit Timing Parameters**

| PARAMETER                       | SYM  | W49Vnn2 |      | IINIT |

|---------------------------------|------|---------|------|-------|

|                                 |      | MIN.    | MAX. |       |

| OE to Data Polling Output Delay | TOEP | -       | 40   | nS    |

| OE to Toggle Bit Output Delay   | Тоет | -       | 40   | nS    |

### TIMING WAVEFORMS FOR PROGRAMMER INTERFACE MODE

# **Read Cycle Timing Diagram**

# **Write Cycle Timing Diagram**

Timing Waveforms for Programmer Interface Mode, continued

### **Program Cycle Timing Diagram**

# **DATA** Polling Timing Diagram

- 17 -

Publication Release Date: March 2000

Revision A1

Timing Waveforms for Programmer Interface Mode, continued

# **Toggle Bit Timing Diagram**

# **Boot Block Lockout Enable Timing Diagram**

Timing Waveforms for Programmer Interface Mode, continued

### **Chip Erase Timing Diagram**

### **Sector Erase Timing Diagram**

- 19 -

### **ORDERING INFORMATION**

| PART NO. | POWER SUPPLY CURRENT MAX. | STANDBY VDD<br>CURRENT MAX. | PACKAGE     |  |

|----------|---------------------------|-----------------------------|-------------|--|

|          | (mA)                      | (μΑ)                        |             |  |

| W49V002  | 25                        | 20                          | 32-pin DIP  |  |

| W49V002P | 25                        | 20                          | 32-pin PLCC |  |

| W49V002T | 2T 25                     |                             | 32-pin TSOP |  |

#### Notes:

- 1. Winbond reserves the right to make changes to its products without prior notice.

- 2. Purchasers are responsible for performing appropriate quality assurance testing on products intended for use in applications where personal injury might occur as a consequence of product failure.

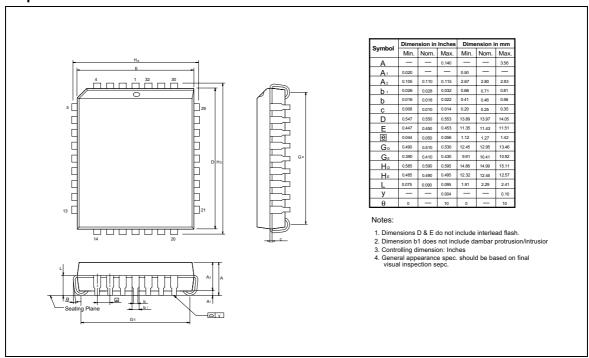

### **PACKAGE DIMENSIONS**

### 32-pin P-DIP

### 32-pin PLCC

- 21 -

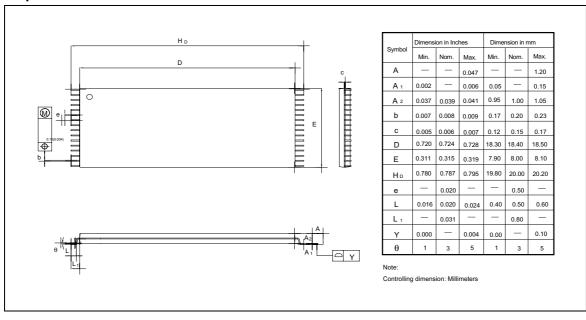

Package Dimensions, continued

# 32-pin TSOP

#### **VERSION HISTORY**

| VERSION | DATE      | PAGE | DESCRIPTION    |

|---------|-----------|------|----------------|

| A1      | Mar. 2000 | -    | Initial Issued |

Headquarters

No. 4, Creation Rd. III, Science-Based Industrial Park, Hsinchu, Taiwan TEL: 886-3-5770066 FAX: 886-3-5796096

http://www.winbond.com.tw/ Voice & Fax-on-demand: 886-2-27197006

**Taipei Office**

11F, No. 115, Sec. 3, Min-Sheng East Rd., Taipei, Taiwan TEL: 886-2-27190505 FAX: 886-2-27197502

Winbond Electronics (H.K.) Ltd. Rm. 803, World Trade Square, Tower II,

- 23 -

123 Hoi Bun Rd., Kwun Tong, Kowloon, Hong Kong TEL: 852-27513100 FAX: 852-27552064

Winbond Electronics North America Corp. Winbond Memory Lab. Winbond Microelectronics Corp.

Winbond Systems Lab. 2727 N. First Street, San Jose,

CA 95134, U.S.A. TEL: 408-9436666 FAX: 408-5441798

Note: All data and specifications are subject to change without notice.