## Freescale Semiconductor Data Sheet

Document Number: MSC7113 Rev. 11, 4/2008

## Low-Cost 16-bit DSP with DDR Controller and 10/100 Mbps Ethernet MAC

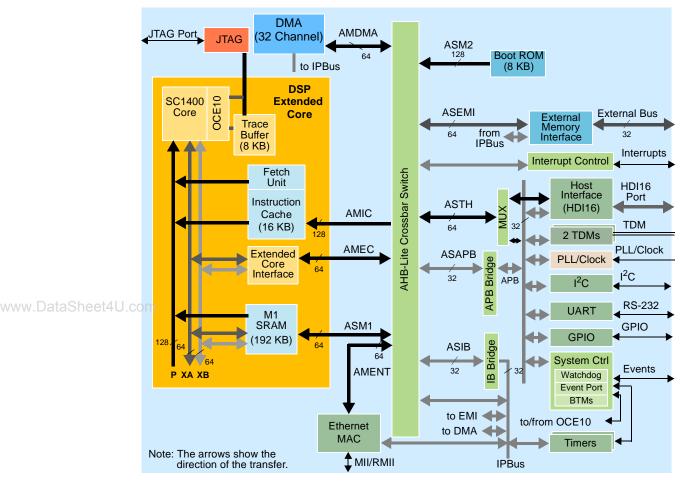

- StarCore<sup>®</sup> SC1400 DSP extended core with one SC1400 DSP core, 192 Kbyte of internal SRAM M1 memory, 16 way 16 Kbyte instruction cache (ICache), four-entry write buffer, programmable interrupt controller (PIC), and low-power Wait and Stop processing modes.

- 8 Kbyte boot ROM.

- www.DataShAHB-Lite crossbar switch that allows parallel data transfers between four master ports and six slave ports, where each port connects to an AHB-Lite bus; fixed or round robin priority programmable at each slave port; programmable bus parking at each slave port; low power mode.

- Internal PLL generates up to 266 MHz clock for the SC1400 core and up to 133 MHz for the crossbar switch, DMA channels, M2 memory, and other peripherals.

- Clock synthesis module provides predivision of PLL input clock; independent clocking of the internal timers and DDR module; programmable operation in the SC1400 low power Stop mode; independent shutdown of different regions of the device.

- Enhanced 16-bit wide host interface (HDI16) provides a glueless connection to industry-standard microcomputers, microprocessors, and DSPs and can also operate with an 8-bit host data bus, making if fully compatible with the DSP56300 HI08 from the external host side.

- DDR memory controller that supports byte enables for up to a 32-bit data bus; glueless interface to 133 MHz 14-bit page mode DDR-RAM; 14-bit external address bus supporting up to 1 Gbyte; and 16-bit or 32-bit external data bus.

- Programmable memory interface with independent read buffers, programmable predictive read feature for each buffer, and a write buffer.

- System control unit performs software watchdog timer function; includes programmable bus time-out monitors on AHB-Lite slave buses; includes bus error detection and programmable time-out monitors on AHB-Lite master buses; and has address out-of-range detection on each crossbar switch buses.

- Event port collects and counts important signal events including DMA and interrupt requests and trigger events such as interrupts, breakpoints, DMA transfers, or wake-up events; units operate independently, in sequence, or triggered externally; can be used standalone or with the OCE10.

# **MSC7113**

- Multi-channel DMA controller with 32 time-multiplexed unidirectional channels, priority-based time-multiplexing between channels using 32 internal priority levels, fixed- or round-robin-priority operation, major-minor loop structure, and DONE or DRACK protocol from requesting units.

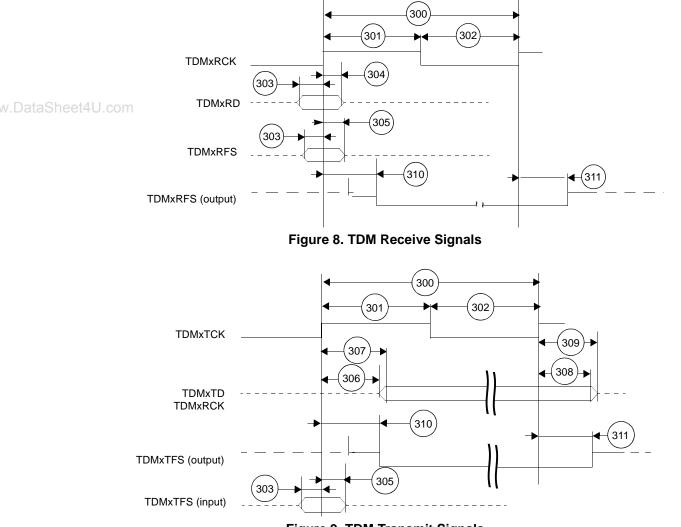

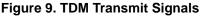

- Two independent TDM modules with independent receive and transmit, programmable sharing of frame sync and clock, programmable word size (8 or 16-bit), hardware-base A-law/µ-law conversion, up to 50 Mbps data rate per TDM, up to 128 channels, with glueless interface to E1/T1 frames and MVIP, SCAS, and H.110 buses.

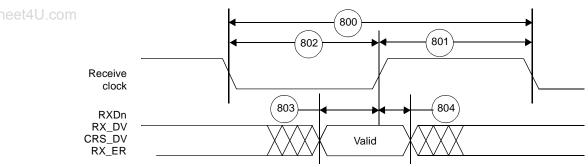

- Ethernet controller with support for 10/100 Mbps MII/RMII designed to comply with IEEE Std. 802.3<sup>TM</sup>, 802.3u<sup>TM</sup>, 802.3x<sup>TM</sup>, and 802.3ac<sup>TM</sup>; with internal receive and transmit FIFOs and a FIFO controller; direct access to internal memories via its own DMA controller; full and half duplex operation; programmable maximum frame length; virtual local area network (VLAN) tag and priority support; retransmission of transmit FIFO following collision; CRC generation and verification for inbound and outbound packets; and address recognition including promiscuous, broadcast, individual address. hash/exact match, and multicast hash match.

- UART with full-duplex operation up to 5.0 Mbps.

- Up to 41 general-purpose input/output (GPIO) ports.

- I<sup>2</sup>C interface that allows booting from EEPROM devices up to 1 Mbyte.

- Two quad timer modules, each with sixteen configurable 16-bit timers.

- fieldBIST<sup>TM</sup> unit detects and provides visibility into unlikely field failures for systems with high availability to ensure structural integrity, that the device operates at the rated speed, is free from reliability defects, and reports diagnostics for partial or complete device inoperability.

- Standard JTAG interface allows easy integration to system firmware and internal on-chip emulation (OCE10) module.

- Optional booting external host via 8-bit or 16-bit access through the HDI16, I<sup>2</sup>C, or SPI using in the boot ROM to access serial SPI Flash/EEPROM devices; different clocking options during boot with the PLL on or off using a variety of input frequency ranges.

# **Table of Contents**

| 1          | Pin Assignments4                       |

|------------|----------------------------------------|

|            | 1.1 MAP-BGA Ball Layout Diagrams       |

|            | 1.2 Signal List By Ball Location       |

| 2          | Electrical Characteristics17           |

|            | 2.1 Maximum Ratings                    |

|            | 2.2 Recommended Operating Conditions   |

|            | 2.3 Thermal Characteristics            |

|            | 2.4 DC Electrical Characteristics      |

|            | 2.5 AC Timings                         |

| 3          | Hardware Design Considerations41       |

|            | 3.1 Thermal Design Considerations      |

|            | 3.2 Power Supply Design Considerations |

|            | 3.3 Estimated Power Usage Calculations |

|            | 3.4 Reset and Boot                     |

|            | 3.5 DDR Memory System Guidelines       |

| 4          | Ordering Information                   |

| 5          | Package Information                    |

| 6          | Product Documentation                  |

| 7          | Revision History                       |

| www.DataSI | ist of Figures                         |

| Figure 1. | MSC7113 Block Diagram                             |

|-----------|---------------------------------------------------|

| Figure 2. | MSC7113 Molded Array Process-Ball Grid Array      |

|           | (MAP-BGA), Top View 4                             |

| Figure 3. | MSC7113 Molded Array Process-Ball Grid Array      |

|           | (MAP-BGA), Bottom View 5                          |

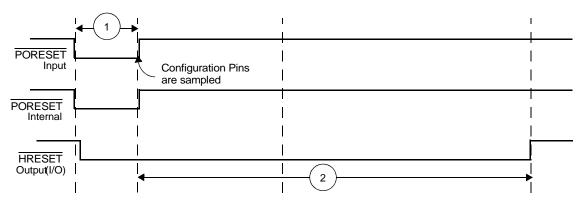

| Figure 4. | Timing Diagram for a Reset Configuration Write 24 |

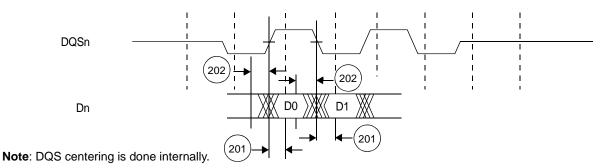

| Figure 5. | DDR DRAM Input Timing Diagram 24                  |

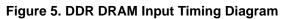

| Figure 6. | DDR DRAM Output Timing Diagram                    |

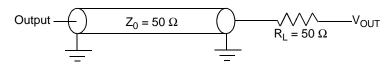

| Figure 7. | DDR DRAM AC Test Load                             |

| Figure 8.  | TDM Receive Signals                            |

|------------|------------------------------------------------|

| Figure 9.  | TDM Transmit Signals                           |

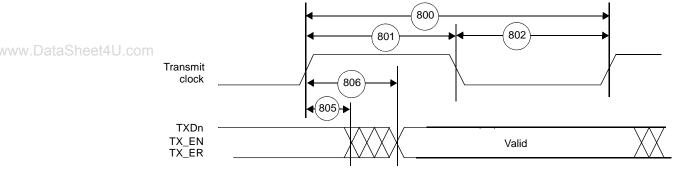

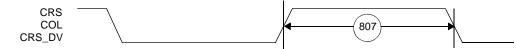

| Figure 10. | Ethernet Receive Signal Timing                 |

| Figure 11. | Ethernet Receive Signal Timing                 |

| Figure 12. | Asynchronous Input Signal Timing               |

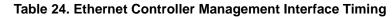

| Figure 13. | Serial Management Channel Timing               |

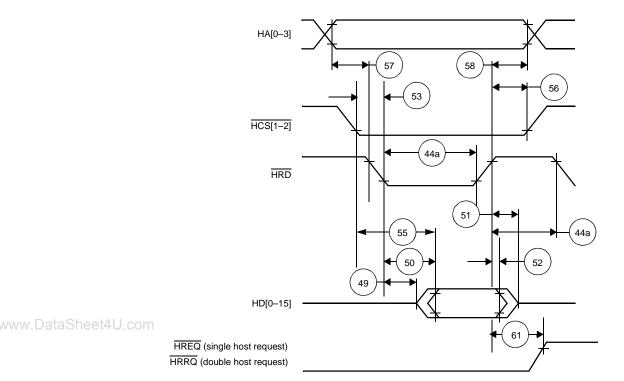

| Figure 14. | Read Timing Diagram, Single Data Strobe        |

| Figure 15. | Read Timing Diagram, Double Data Strobe        |

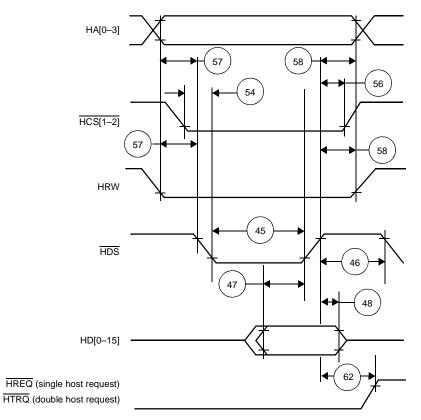

| Figure 16. | Write Timing Diagram, Single Data Strobe       |

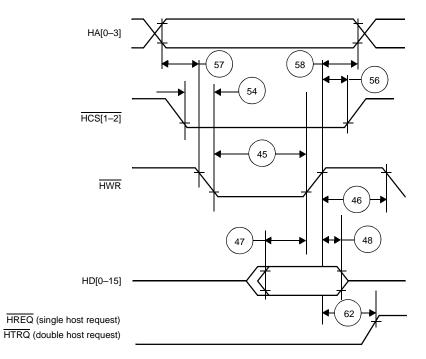

| Figure 17. | Write Timing Diagram, Double Data Strobe       |

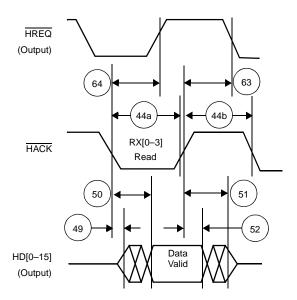

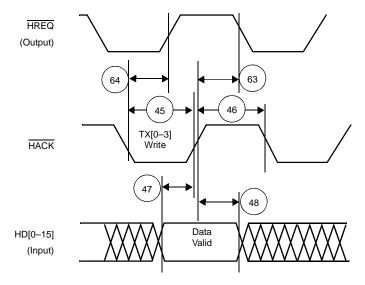

| Figure 18. | Host DMA Read Timing Diagram, HPCR[OAD] = 034  |

| Figure 19. | Host DMA Write Timing Diagram, HPCR[OAD] = 035 |

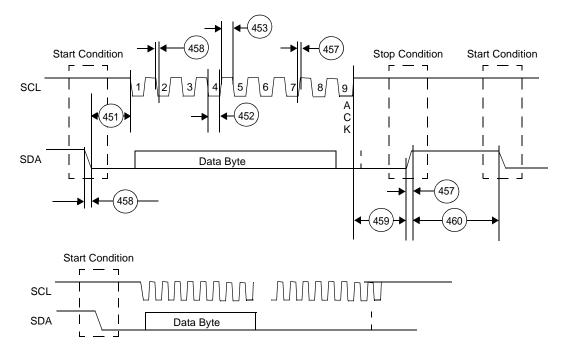

| Figure 20. | I2C Timing Diagram                             |

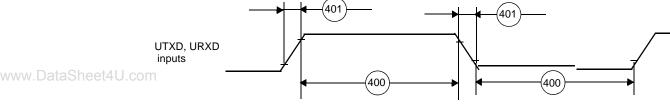

| Figure 21. | UART Input Timing                              |

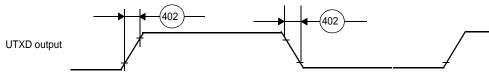

| Figure 22. | UART Output Timing                             |

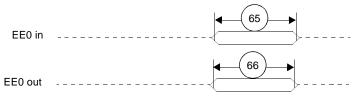

| Figure 23. | EE Pin Timing                                  |

| Figure 24. | EVNT Pin Timing                                |

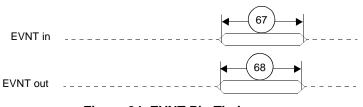

| Figure 25. | GPI/GPO Pin Timing                             |

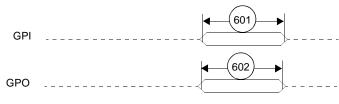

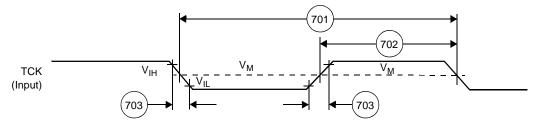

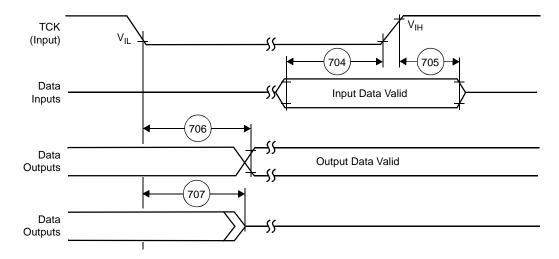

| Figure 26. | Test Clock Input Timing Diagram                |

| Figure 27. | Boundary Scan (JTAG) Timing Diagram 40         |

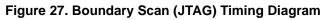

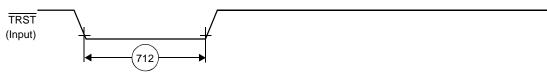

| Figure 28. | Test Access Port Timing Diagram 40             |

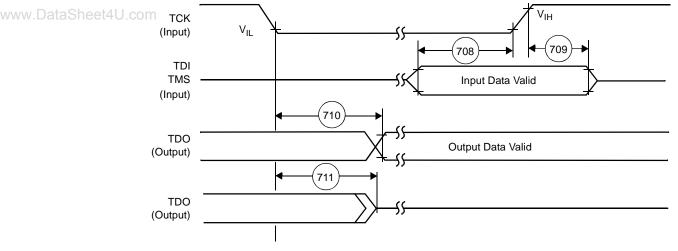

| Figure 29. | TRST Timing Diagram                            |

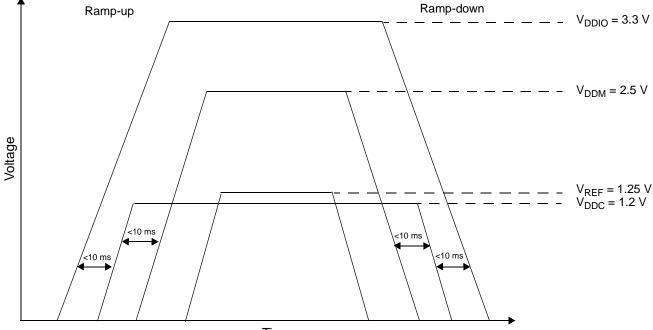

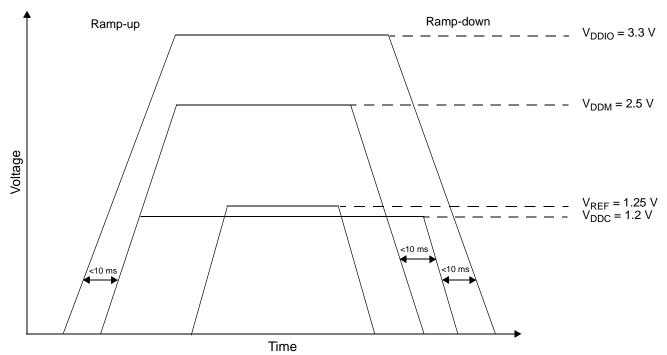

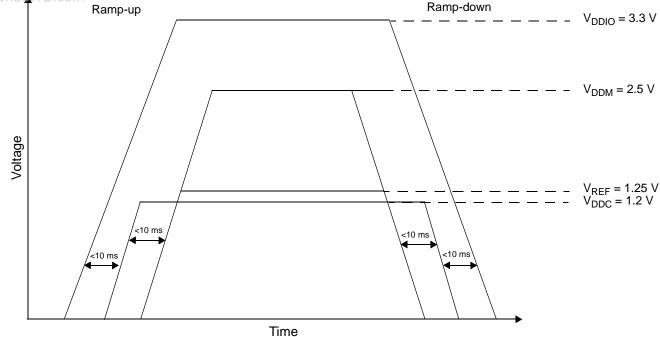

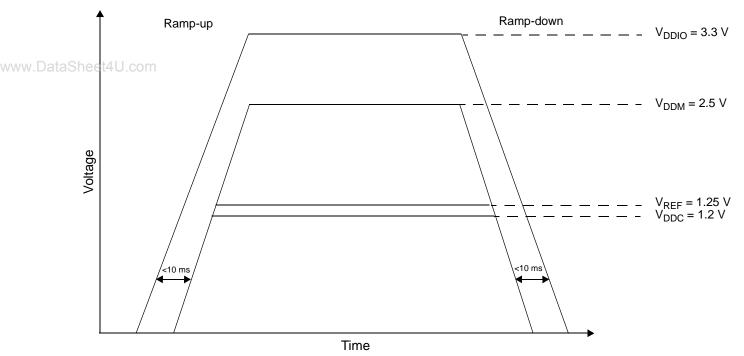

| Figure 30. | Voltage Sequencing Case 1                      |

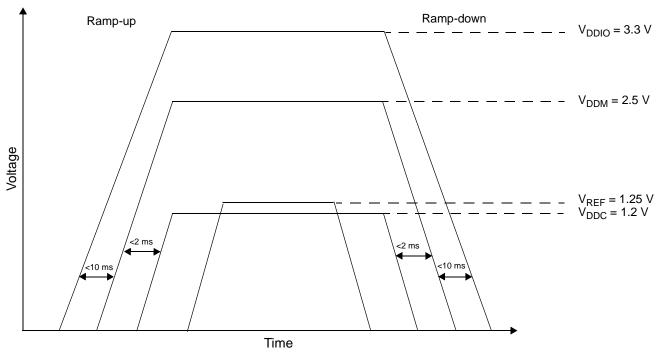

| Figure 31. | Voltage Sequencing Case 2 44                   |

| Figure 32. | Voltage Sequencing Case 3 45                   |

| Figure 33. | Voltage Sequencing Case 4                      |

| Figure 34. | Voltage Sequencing Case 5 47                   |

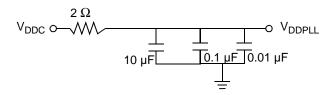

| Figure 35. | PLL Power Supply Filter Circuits               |

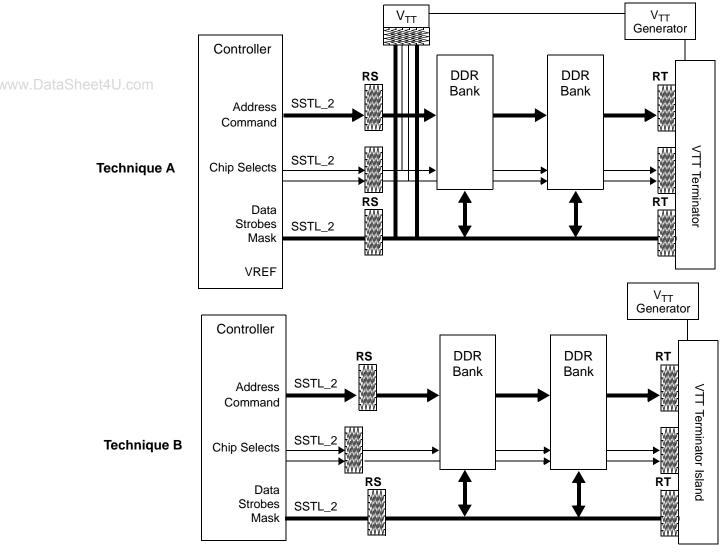

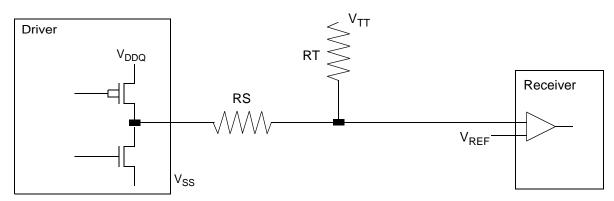

| Figure 36. | SSTL Termination Techniques                    |

| Figure 37. | SSTL Power Value                               |

Figure 1. MSC7113 Block Diagram

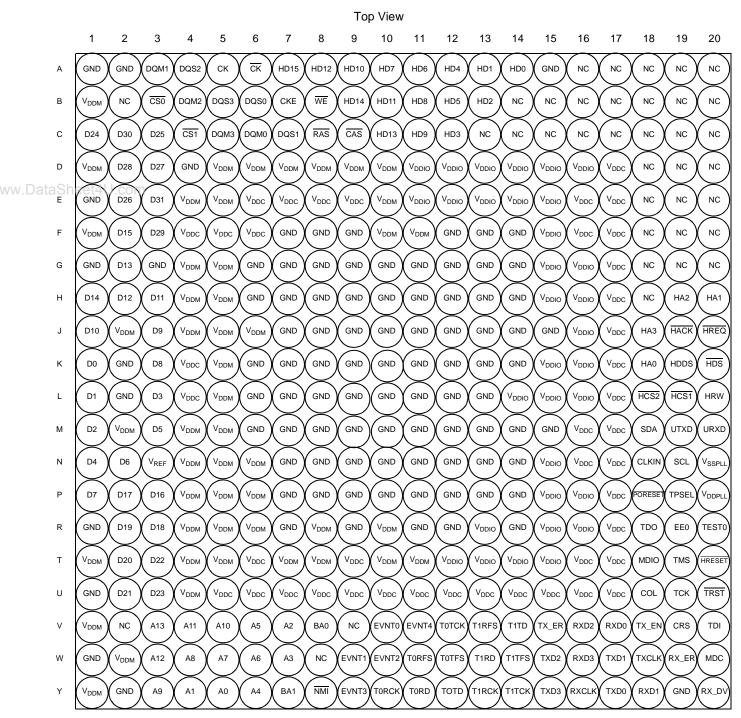

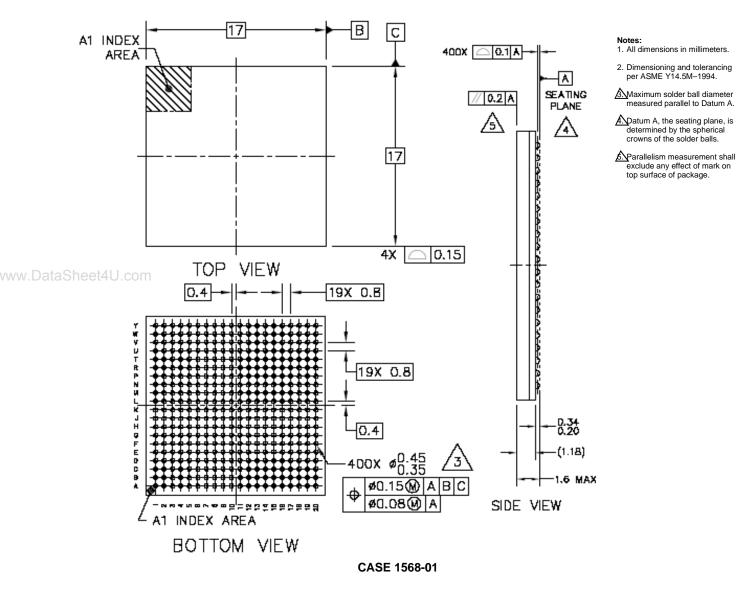

# 1 Pin Assignments

This section includes diagrams of the MSC7113 package ball grid array layouts and pinout allocation tables.

# 1.1 MAP-BGA Ball Layout Diagrams

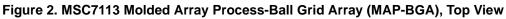

Top and bottom views of the MAP-BGA package are shown in Figure 2 and Figure 3 with their ball location index numbers.

Figure 3. MSC7113 Molded Array Process-Ball Grid Array (MAP-BGA), Bottom View

# 1.2 Signal List By Ball Location

Table 1 lists the signals sorted by ball number and configuration.

| Table 1. | MSC7113 | Signals b | y Ball | Designator |

|----------|---------|-----------|--------|------------|

|----------|---------|-----------|--------|------------|

|                   | Signal Names |                          |                      |             |                   |           |  |  |

|-------------------|--------------|--------------------------|----------------------|-------------|-------------------|-----------|--|--|

| Number            |              | S                        | oftware Controll     | ed          | Hardware Controll |           |  |  |

|                   | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary           | Alternate |  |  |

| A1                |              |                          | G                    | ND          |                   |           |  |  |

| A2                |              |                          | G                    | ND          |                   |           |  |  |

| A3                |              |                          | D                    | QM1         |                   |           |  |  |

| A4                |              |                          | D                    | QS2         |                   |           |  |  |

| A5                |              |                          | (                    | СК          |                   |           |  |  |

| A6                |              |                          | Ū                    | СК          |                   |           |  |  |

| A7<br>Bheet4U.com |              | GPIC7                    |                      | GPOC7       | Н                 | D15       |  |  |

| A8                |              | GPIC4                    |                      | GPOC4       | Н                 | D12       |  |  |

| A9                |              | GPIC2                    |                      | GPOC2       | Н                 | D10       |  |  |

| A10               |              | rese                     | rved                 |             | H                 | ID7       |  |  |

| A11               |              | rese                     | rved                 |             | н                 | ID6       |  |  |

| A12               |              | rese                     |                      | HD4         |                   |           |  |  |

| A13               |              | rese                     | rved                 |             | HD1               |           |  |  |

| A14               |              | rese                     |                      | H           | ID0               |           |  |  |

| A15               |              | GND                      |                      |             |                   |           |  |  |

| A16 (1L44X)       |              |                          | 1                    | NC          |                   |           |  |  |

| A16 (1M88B)       | BM3          | GPI                      | ID8                  | GPOD7       | reserved          |           |  |  |

| A17               |              |                          | I                    | NC          |                   |           |  |  |

| A18               |              |                          | I                    | NC          |                   |           |  |  |

| A19               |              |                          | I                    | NC          |                   |           |  |  |

| A20               |              |                          | I                    | NC          |                   |           |  |  |

| B1                |              |                          | V                    | DDM         |                   |           |  |  |

| B2                |              |                          | 1                    | NC          |                   |           |  |  |

| B3                |              |                          | C                    | SO          |                   |           |  |  |

| B4                |              |                          | D                    | QM2         |                   |           |  |  |

| B5                |              |                          | D                    | 283         |                   |           |  |  |

| B6                |              |                          | D                    | QS0         |                   |           |  |  |

| B7                |              |                          | C                    | KE          |                   |           |  |  |

| B8                |              |                          | V                    | VE          |                   |           |  |  |

| B9                |              | GPIC6                    |                      | GPOC6       | Н                 | D14       |  |  |

| B10               |              | GPIC3                    |                      | GPOC3       | Н                 | D11       |  |  |

| B11               |              | GPIC0                    |                      | GPOC0       | Н                 | ID8       |  |  |

| B12               |              | rese                     | rved                 |             | H                 | ID5       |  |  |

| B13               |              | rese                     | rved                 |             | н                 | ID2       |  |  |

|             | Signal Names |                          |                      |             |         |           |  |  |

|-------------|--------------|--------------------------|----------------------|-------------|---------|-----------|--|--|

| Number      |              | S                        | Hardware             | Controlled  |         |           |  |  |

|             | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary | Alternate |  |  |

| B15 (1L44X) |              |                          | 1                    | 1C          |         |           |  |  |

| B15 (1M88B) | BM2          | GP                       | ID7                  | GPOD7       | res     | erved     |  |  |

| B16         |              |                          | 1                    | 1C          |         |           |  |  |

| B17         |              |                          | 1                    | 1C          |         |           |  |  |

| B18         |              |                          | 1                    | ۱C          |         |           |  |  |

| B19         |              |                          | 1                    | ١C          |         |           |  |  |

| B20         |              |                          | 1                    | ۱C          |         |           |  |  |

| C1          |              |                          | Ľ                    | 24          |         |           |  |  |

| C2          |              |                          | Γ                    | 030         |         |           |  |  |

| C3          |              |                          | [                    | 25          |         |           |  |  |

| C4          |              |                          | ō                    | S1          |         |           |  |  |

| C5          |              |                          | D                    | QM3         |         |           |  |  |

| C6          |              |                          | D                    | QMQ         |         |           |  |  |

| C7          |              |                          | D                    | QS1         |         |           |  |  |

| C8          |              |                          | R                    | AS          |         |           |  |  |

| C9          |              |                          | C                    | AS          |         |           |  |  |

| C10         |              | GPIC5                    |                      | GPOC5       | Н       | D13       |  |  |

| C11         |              | GPIC1                    |                      | GPOC1       | H       | ID9       |  |  |

| C12         |              | rese                     | erved                |             | H       | ID3       |  |  |

| C13         |              |                          | 1                    | ١C          |         |           |  |  |

| C14         |              |                          | 1                    | ١C          |         |           |  |  |

| C15         |              |                          | 1                    | ١C          |         |           |  |  |

| C16         |              |                          | I                    | 1C          |         |           |  |  |

| C17         |              |                          | I                    | 1C          |         |           |  |  |

| C18         |              |                          | 1                    | 1C          |         |           |  |  |

| C19         |              |                          | 1                    | 1C          |         |           |  |  |

| C20         |              |                          | 1                    | 1C          |         |           |  |  |

| D1          |              |                          | V                    | DDM         |         |           |  |  |

| D2          |              |                          | C                    | 28          |         |           |  |  |

| D3          |              |                          | C                    | 027         |         |           |  |  |

| D4          |              |                          |                      | ND          |         |           |  |  |

| D5          |              |                          | V                    | DDM         |         |           |  |  |

| D6          |              |                          | V                    | DDM         |         |           |  |  |

| D7          |              |                          | V                    | DDM         |         |           |  |  |

| D8          |              |                          | V                    | DDM         |         |           |  |  |

| D9          |              |                          | V                    | DDM         |         |           |  |  |

| D10         |              |                          | V                    | DDM         |         |           |  |  |

| D11         |              |                          | VI                   | DIO         |         |           |  |  |

### Table 1. MSC7113 Signals by Ball Designator (continued)

|             |              |                          | Signal               | Names       |         |           |          |            |

|-------------|--------------|--------------------------|----------------------|-------------|---------|-----------|----------|------------|

| Number      |              | Software Controlled      |                      |             |         |           | Hardware | Controlled |

|             | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary | Alternate |          |            |

| D12         |              |                          | V                    | DIO         |         |           |          |            |

| D13         |              |                          |                      | DIO         |         |           |          |            |

| D14         |              |                          |                      | DIO         |         |           |          |            |

| D15         |              |                          |                      | DIO         |         |           |          |            |

| D16         |              |                          |                      | DIO         |         |           |          |            |

| D17         |              |                          |                      | DDC         |         |           |          |            |

| D18         |              |                          |                      | IC          |         |           |          |            |

| D19         |              |                          | ١                    | IC          |         |           |          |            |

| D20         |              |                          | ١                    | IC          |         |           |          |            |

| hoot El com |              |                          | G                    | ND          |         |           |          |            |

| E2          |              |                          | D                    | 26          |         |           |          |            |

| E3          |              |                          | D                    | 31          |         |           |          |            |

| E4          |              |                          | V                    | DDM         |         |           |          |            |

| E5          |              |                          |                      | DDM         |         |           |          |            |

| E6          |              |                          |                      | DDC         |         |           |          |            |

| E7          |              |                          |                      | DDC         |         |           |          |            |

| E8          |              |                          |                      | DDC         |         |           |          |            |

| E9          |              |                          |                      | DDC         |         |           |          |            |

| E10         |              |                          |                      | DDM         |         |           |          |            |

| E11         |              |                          |                      | DIO         |         |           |          |            |

| E12         |              |                          |                      | DIO         |         |           |          |            |

| E13         |              |                          |                      | DIO         |         |           |          |            |

| E14         |              |                          |                      | DIO         |         |           |          |            |

| E15         |              |                          |                      | DIO         |         |           |          |            |

| E16         |              |                          |                      | DDC         |         |           |          |            |

| E17         |              |                          | V                    | DDC         |         |           |          |            |

| E18         |              |                          | N                    | IC          |         |           |          |            |

| E19         |              |                          | N                    | IC          |         |           |          |            |

| E20         |              |                          | N                    | IC          |         |           |          |            |

| F1          |              |                          | V                    | DDM         |         |           |          |            |

| F2          |              |                          | D                    | 15          |         |           |          |            |

| F3          |              |                          | D                    | 29          |         |           |          |            |

| F4          |              |                          | V                    | DDC         |         |           |          |            |

| F5          |              |                          | V                    | DDC         |         |           |          |            |

| F6          |              |                          | VI                   | DDC         |         |           |          |            |

| F7          |              |                          | G                    | ND          |         |           |          |            |

| F8          |              |                          | G                    | ND          |         |           |          |            |

| F9          |              |                          | G                    | ND          |         |           |          |            |

### Table 1. MSC7113 Signals by Ball Designator (continued)

|        | Signal Names |                          |                      |             |            |           |  |  |

|--------|--------------|--------------------------|----------------------|-------------|------------|-----------|--|--|

| Number |              | S                        | ed                   | Hardware    | Controlled |           |  |  |

|        | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary    | Alternate |  |  |

| F10    |              |                          | V                    | DDM         |            |           |  |  |

| F11    |              |                          | V                    | DDM         |            |           |  |  |

| F12    |              |                          | G                    | iND         |            |           |  |  |

| F13    |              |                          | G                    | iND         |            |           |  |  |

| F14    |              |                          | G                    | ND          |            |           |  |  |

| F15    |              |                          | VI                   | סוסכ        |            |           |  |  |

| F16    |              |                          |                      | DDC         |            |           |  |  |

| F17    |              |                          | V                    | DDC         |            |           |  |  |

| F18    |              |                          | 1                    | NC          |            |           |  |  |

| F19    |              |                          | 1                    | NC          |            |           |  |  |

| F20    |              |                          | 1                    | NC          |            |           |  |  |

| G1     |              |                          | G                    | ND          |            |           |  |  |

| G2     |              |                          | C                    | 013         |            |           |  |  |

| G3     |              |                          | G                    | ND          |            |           |  |  |

| G4     |              |                          | V                    | DDM         |            |           |  |  |

| G5     |              |                          | V                    | DDM         |            |           |  |  |

| G6     |              |                          | G                    | ND          |            |           |  |  |

| G7     |              |                          | G                    | ND          |            |           |  |  |

| G8     |              |                          | G                    | ND          |            |           |  |  |

| G9     |              |                          | G                    | ND          |            |           |  |  |

| G10    |              |                          | G                    | ND          |            |           |  |  |

| G11    |              |                          | G                    | ND          |            |           |  |  |

| G12    |              |                          | G                    | ND          |            |           |  |  |

| G13    |              |                          | G                    | ND          |            |           |  |  |

| G14    |              |                          | G                    | ND          |            |           |  |  |

| G15    |              |                          | VI                   | סומכ        |            |           |  |  |

| G16    |              |                          |                      | סוסכ        |            |           |  |  |

| G17    |              |                          | V                    | DDC         |            |           |  |  |

| G18    |              |                          | 1                    | NC          |            |           |  |  |

| G19    |              |                          | 1                    | NC          |            |           |  |  |

| G20    |              |                          | 1                    | NC          |            |           |  |  |

| H1     |              |                          | Ľ                    | 014         |            |           |  |  |

| H2     |              | D12                      |                      |             |            |           |  |  |

| H3     |              | D11                      |                      |             |            |           |  |  |

| H4     |              |                          | V                    | DDM         |            |           |  |  |

| H5     |              |                          | V                    | DDM         |            |           |  |  |

| H6     |              |                          | G                    | ND          |            |           |  |  |

| H7     |              |                          | G                    | iND         |            |           |  |  |

### Table 1. MSC7113 Signals by Ball Designator (continued)

|             | Signal Names |                          |                      |             |            |              |  |  |  |

|-------------|--------------|--------------------------|----------------------|-------------|------------|--------------|--|--|--|

| Number      |              | S                        | ed                   | Hardware    | Controlled |              |  |  |  |

|             | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary    | Alternate    |  |  |  |

| H8          |              |                          | G                    | ND          |            |              |  |  |  |

| H9          |              |                          | G                    | ND          |            |              |  |  |  |

| H10         |              |                          | G                    | ND          |            |              |  |  |  |

| H11         |              |                          | G                    | ND          |            |              |  |  |  |

| H12         |              |                          | G                    | ND          |            |              |  |  |  |

| H13         |              |                          | G                    | ND          |            |              |  |  |  |

| H14         |              |                          | G                    | ND          |            |              |  |  |  |

| H15         |              |                          | VD                   | DIO         |            |              |  |  |  |

| H16         |              |                          | VD                   | DIO         |            |              |  |  |  |

| H17         |              |                          | V                    | DDC         |            |              |  |  |  |

| H18         | 1            |                          | Ν                    | IC          |            |              |  |  |  |

| H19         |              | rese                     | rved                 |             | Н          | A2           |  |  |  |

| H20         |              | rese                     | rved                 |             | Н          | A1           |  |  |  |

| J1          |              |                          | D                    | 10          |            |              |  |  |  |

| J2          |              |                          | V <sub>C</sub>       | DM          |            |              |  |  |  |

| J3          |              |                          |                      | 99          |            |              |  |  |  |

| J4          |              |                          | V <sub>C</sub>       | DM          |            |              |  |  |  |

| J5          |              |                          | V <sub>C</sub>       | DM          |            |              |  |  |  |

| J6          |              |                          | V <sub>C</sub>       | DM          |            |              |  |  |  |

| J7          |              |                          | G                    | ND          |            |              |  |  |  |

| J8          |              |                          | G                    | ND          |            |              |  |  |  |

| J9          |              |                          | G                    | ND          |            |              |  |  |  |

| J10         |              |                          | G                    | ND          |            |              |  |  |  |

| J11         |              |                          | G                    | ND          |            |              |  |  |  |

| J12         |              |                          | G                    | ND          |            |              |  |  |  |

| J13         |              |                          | G                    | ND          |            |              |  |  |  |

| J14         |              |                          | G                    | ND          |            |              |  |  |  |

| J15         |              |                          | G                    | ND          |            |              |  |  |  |

| J16         |              |                          | VD                   | DIO         |            |              |  |  |  |

| J17         |              |                          | V                    | DDC         |            |              |  |  |  |

| J18 (1L44X) |              | rese                     | rved                 |             | Н          | A3           |  |  |  |

| J18 (1M88B) |              | GPIC11 GPOC11 HA3        |                      |             |            |              |  |  |  |

| J19         |              | rese                     | rved                 |             | HACK/HACK  | or HRRQ/HRRQ |  |  |  |

| J20         | HDSP         |                          | reserved             |             | HREQ/HREQ  | or HTRQ/HTRQ |  |  |  |

| K1          |              |                          | [                    | 00          |            |              |  |  |  |

| K2          |              |                          | G                    | ND          |            |              |  |  |  |

| K3          |              |                          | C                    | 08          |            |              |  |  |  |

| K4          |              |                          | Vr                   | DDC         |            |              |  |  |  |

### Table 1. MSC7113 Signals by Ball Designator (continued)

|             | Signal Names |                          |                         |             |            |            |  |  |  |

|-------------|--------------|--------------------------|-------------------------|-------------|------------|------------|--|--|--|

| Number      |              | S                        | ed                      | Hardware    | Controlled |            |  |  |  |

|             | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled    | GPO Enabled | Primary    | Alternate  |  |  |  |

| K5          |              |                          | V                       | DDM         |            |            |  |  |  |

| K6          |              |                          | G                       | IND         |            |            |  |  |  |

| K7          |              |                          | G                       | SND         |            |            |  |  |  |

| K8          |              |                          | G                       | SND         |            |            |  |  |  |

| K9          |              |                          | G                       | SND         |            |            |  |  |  |

| K10         |              |                          | G                       | IND         |            |            |  |  |  |

| K11         |              |                          | G                       | IND         |            |            |  |  |  |

| K12         |              |                          | G                       | IND         |            |            |  |  |  |

| K13         |              |                          | G                       | IND         |            |            |  |  |  |

| K14         |              |                          | G                       | IND         |            |            |  |  |  |

| K15         |              |                          | VI                      | DDIO        |            |            |  |  |  |

| K16         |              |                          | V                       | DDIO        |            |            |  |  |  |

| K17         |              |                          | V                       | DDC         |            |            |  |  |  |

| K18         |              | rese                     | rved                    |             | Н          | IA0        |  |  |  |

| K19         |              | rese                     | rved                    |             | H          | DDS        |  |  |  |

| K20         |              | rese                     | rved                    |             | HDS/HDS of | or HWR/HWR |  |  |  |

| L1          |              |                          |                         | D1          |            |            |  |  |  |

| L2          |              |                          | G                       | ND          |            |            |  |  |  |

| L3          |              |                          |                         | D3          |            |            |  |  |  |

| L4          |              |                          | V                       | DDC         |            |            |  |  |  |

| L5          |              |                          | V                       | DDM         |            |            |  |  |  |

| L6          |              |                          | G                       | ND          |            |            |  |  |  |

| L7          |              |                          | G                       | ND          |            |            |  |  |  |

| L8          |              |                          | G                       | ND          |            |            |  |  |  |

| L9          |              |                          | G                       | ND          |            |            |  |  |  |

| L10         |              |                          |                         | ND          |            |            |  |  |  |

| L11         |              |                          |                         | ND          |            |            |  |  |  |

| L12         |              |                          | G                       | ND          |            |            |  |  |  |

| L13         |              |                          |                         | IND         |            |            |  |  |  |

| L14         |              |                          |                         | DDIO        |            |            |  |  |  |

| L15         |              |                          | VI                      | DDIO        |            |            |  |  |  |

| L16         |              |                          |                         | DDIO        |            |            |  |  |  |

| L17         |              |                          |                         | DDC         |            |            |  |  |  |

| L18 (1L44X) |              | rese                     | rved                    |             |            | 2/HCS2     |  |  |  |

| L18 (1M88B) |              | GPIB11                   |                         | GPOB11      |            | 2/HCS2     |  |  |  |

| L19         |              | rese                     | rved                    |             |            | I/HCS1     |  |  |  |

| L20         |              | rese                     | reserved HRW or HRD/HRD |             |            |            |  |  |  |

### Table 1. MSC7113 Signals by Ball Designator (continued)

|        | Signal Names |                          |                      |              |          |           |  |  |  |

|--------|--------------|--------------------------|----------------------|--------------|----------|-----------|--|--|--|

| Number |              | S                        | Hardware             | e Controlled |          |           |  |  |  |

|        | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled  | Primary  | Alternate |  |  |  |

| M2     |              |                          | V                    | DDM          |          |           |  |  |  |

| М3     |              |                          |                      | 05           |          |           |  |  |  |

| M4     |              |                          | V                    | DDM          |          |           |  |  |  |

| M5     |              |                          | V                    | DDM          |          |           |  |  |  |

| M6     |              |                          | G                    | ND           |          |           |  |  |  |

| M7     |              |                          | G                    | ND           |          |           |  |  |  |

| M8     |              |                          | G                    | ND           |          |           |  |  |  |

| M9     |              |                          | G                    | ND           |          |           |  |  |  |

| M10    |              |                          | G                    | ND           |          |           |  |  |  |

| M11    |              |                          | G                    | ND           |          |           |  |  |  |

| M12    |              |                          | G                    | ND           |          |           |  |  |  |

| M13    |              |                          | G                    | ND           |          |           |  |  |  |

| M14    |              |                          | G                    | ND           |          |           |  |  |  |

| M15    |              |                          | G                    | ND           |          |           |  |  |  |

| M16    |              |                          | V                    | DDC          |          |           |  |  |  |

| M17    |              |                          |                      | DDC          |          |           |  |  |  |

| M18    | GP           | A14                      | IRQ15                | GPOA14       | S        | SDA       |  |  |  |

| M19    | GP           | A12                      | IRQ3                 | GPOA12       | U        | TXD       |  |  |  |

| M20    | GP           | A13                      | IRQ2                 | GPOA13       | U        | RXD       |  |  |  |

| N1     |              |                          | [                    | D4           |          |           |  |  |  |

| N2     |              |                          | [                    | 06           |          |           |  |  |  |

| N3     |              |                          | V                    | REF          |          |           |  |  |  |

| N4     |              |                          |                      | DDM          |          |           |  |  |  |

| N5     |              |                          |                      | DDM          |          |           |  |  |  |

| N6     |              |                          |                      | DDM          |          |           |  |  |  |

| N7     |              |                          |                      | ND           |          |           |  |  |  |

| N8     |              |                          | G                    | ND           |          |           |  |  |  |

| N9     |              |                          | G                    | ND           |          |           |  |  |  |

| N10    |              |                          | G                    | ND           |          |           |  |  |  |

| N11    |              |                          | G                    | ND           |          |           |  |  |  |

| N12    |              |                          | G                    | ND           |          |           |  |  |  |

| N13    |              |                          | G                    | ND           |          |           |  |  |  |

| N14    |              |                          | G                    | ND           |          |           |  |  |  |

| N15    |              |                          | V                    | DDIO         |          |           |  |  |  |

| N16    |              |                          |                      | DDC          |          |           |  |  |  |

| N17    |              |                          |                      | DDC          |          |           |  |  |  |

| N18    | 1            |                          |                      | .KIN         |          |           |  |  |  |

| N19    | GPI          | A15                      | IRQ14                | GPOA15       | <u>,</u> | SCL       |  |  |  |

### Table 1. MSC7113 Signals by Ball Designator (continued)

|        | Signal Names |                          |                      |             |            |           |  |  |

|--------|--------------|--------------------------|----------------------|-------------|------------|-----------|--|--|

| Number |              | S                        | ed                   | Hardware    | Controlled |           |  |  |

|        | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary    | Alternate |  |  |

| N20    |              |                          | Vs                   | SPLL        |            |           |  |  |

| P1     |              |                          |                      | 70          |            |           |  |  |

| P2     |              |                          | C                    | 017         |            |           |  |  |

| P3     |              |                          | C                    | 016         |            |           |  |  |

| P4     |              |                          | V                    | DDM         |            |           |  |  |

| P5     |              |                          | V                    | DDM         |            |           |  |  |

| P6     |              |                          | V                    | DDM         |            |           |  |  |

| P7     |              |                          | G                    | ND          |            |           |  |  |

| P8     |              |                          | G                    | ND          |            |           |  |  |

| P9     |              |                          | G                    | ND          |            |           |  |  |

| P10    |              |                          | G                    | ND          |            |           |  |  |

| P11    |              |                          | G                    | ND          |            |           |  |  |

| P12    |              |                          | G                    | ND          |            |           |  |  |

| P13    |              |                          | G                    | ND          |            |           |  |  |

| P14    |              |                          | G                    | ND          |            |           |  |  |

| P15    |              |                          | V                    | DIO         |            |           |  |  |

| P16    |              |                          | V                    | ΟΠΟ         |            |           |  |  |

| P17    |              |                          | V                    | DDC         |            |           |  |  |

| P18    |              |                          |                      | ESET        |            |           |  |  |

| P19    |              |                          | TP                   | SEL         |            |           |  |  |

| P20    |              |                          | VD                   | DPLL        |            |           |  |  |

| R1     |              |                          | G                    | ND          |            |           |  |  |

| R2     |              |                          | Ľ                    | 019         |            |           |  |  |

| R3     |              |                          | Ľ                    | 018         |            |           |  |  |

| R4     |              |                          | V                    | DDM         |            |           |  |  |

| R5     |              |                          | V                    | DDM         |            |           |  |  |

| R6     |              |                          | V                    | DDM         |            |           |  |  |

| R7     |              |                          | G                    | ND          |            |           |  |  |

| R8     |              |                          | V                    | DDM         |            |           |  |  |

| R9     |              |                          | G                    | ND          |            |           |  |  |

| R10    |              |                          | V                    | DDM         |            |           |  |  |

| R11    |              |                          | G                    | ND          |            |           |  |  |

| R12    |              |                          | G                    | ND          |            |           |  |  |

| R13    |              |                          | V                    | DIO         |            |           |  |  |

| R14    |              |                          | G                    | ND          |            |           |  |  |

| R15    |              |                          | V                    | DDIO        |            |           |  |  |

| R16    |              |                          | V                    | DDIO        |            |           |  |  |

| R17    |              |                          | V                    | DDC         |            |           |  |  |

### Table 1. MSC7113 Signals by Ball Designator (continued)

|        |              |                          | Signa                | l Names     |          |            |

|--------|--------------|--------------------------|----------------------|-------------|----------|------------|

| Number |              | So                       | oftware Controll     | ed          | Hardware | Controlled |

|        | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary  | Alternate  |

| R18    |              |                          | Т                    | DO          |          |            |

| R19    |              | reser                    | rved                 |             | EE0/0    | DBREQ      |

| R20    |              |                          |                      |             |          |            |

| T1     |              |                          | V                    | DDM         |          |            |

| T2     |              |                          | [                    | 020         |          |            |

| Т3     |              |                          | [                    | 022         |          |            |

| T4     |              |                          | V                    | DDM         |          |            |

| T5     |              |                          | V                    | DDM         |          |            |

| T6     |              |                          | V                    | DDC         |          |            |

| T7     |              |                          | V                    | DDM         |          |            |

| T8     |              |                          | V                    | DDM         |          |            |

| Т9     |              |                          | V                    | DDC         |          |            |

| T10    |              |                          | V                    | DDM         |          |            |

| T11    |              |                          | V                    | DDM         |          |            |

| T12    |              |                          | V                    | DDIO        |          |            |

| T13    |              |                          | V                    | DDIO        |          |            |

| T14    |              |                          | V                    | DDIO        |          |            |

| T15    |              |                          | V                    | DDIO        |          |            |

| T16    |              |                          | V                    | DDC         |          |            |

| T17    |              |                          | V                    | DDC         |          |            |

| T18    |              | reser                    | rved                 |             | М        | DIO        |

| T19    |              |                          | Т                    | MS          |          |            |

| T20    |              |                          | HR                   | ESET        |          |            |

| U1     |              |                          | G                    | SND         |          |            |

| U2     |              |                          | Ι                    | D21         |          |            |

| U3     |              |                          | Ι                    | 023         |          |            |

| U4     |              |                          | V                    | DDM         |          |            |

| U5     |              |                          | V                    | DDC         |          |            |

| U6     |              |                          | V                    | DDC         |          |            |

| U7     |              |                          | V                    | DDC         |          |            |

| U8     |              |                          |                      | DDC         |          |            |

| U9     |              |                          | V                    | DDC         |          |            |

| U10    |              |                          | V                    | DDC         |          |            |

| U11    |              |                          | V                    | DDC         |          |            |

| U12    |              |                          | V                    | DDC         |          |            |

| U13    |              |                          | V                    | DDC         |          |            |

| U14    |              |                          | V                    | DDC         |          |            |

| U15    |              |                          | V                    | DDC         |          |            |

### Table 1. MSC7113 Signals by Ball Designator (continued)

|                   |                                                            |                                        | Signal               | Names       |                                 |           |

|-------------------|------------------------------------------------------------|----------------------------------------|----------------------|-------------|---------------------------------|-----------|

| Number            | End of Reset GPI Enabled Interrupt GPO Enabled GPO Enabled |                                        | ed                   | Hardware    | Controlled                      |           |

|                   | End of Reset                                               | GPI Enabled<br>(Default)               | Interrupt<br>Enabled | GPO Enabled | Primary                         | Alternate |

| U16               |                                                            |                                        | V                    | DDC         |                                 |           |

| U17               |                                                            |                                        |                      |             |                                 |           |

| U18               |                                                            | V <sub>DDC</sub><br>reserved CO<br>TCK |                      |             |                                 |           |

| U19               |                                                            |                                        |                      |             |                                 |           |

| U20               |                                                            |                                        | TI                   | RST         |                                 |           |

| V1                |                                                            |                                        | V                    | DDM         |                                 |           |

| V2                |                                                            |                                        | 1                    | ١C          |                                 |           |

| V3                |                                                            |                                        | A                    | 13          |                                 |           |

| V4                |                                                            |                                        | A                    | 11          |                                 |           |

| V5<br>Sheet4U.com |                                                            |                                        | A                    | 10          |                                 |           |

| V6                |                                                            |                                        |                      | 45          |                                 |           |

| V7                |                                                            |                                        |                      | 42          |                                 |           |

| V8                |                                                            |                                        | E                    | A0          |                                 |           |

| V9                |                                                            |                                        | 1                    | ١C          |                                 |           |

| V10               |                                                            | reser                                  | rved                 |             | EV                              | NT0       |

| V11               | SWTE                                                       | GPIA16                                 | IRQ12                | GPOA16      | EVNT4<br>T0TCK<br>T1RFS<br>T1TD |           |

| V12               | GP                                                         | IA8                                    | IRQ6                 | GPOA8       |                                 |           |

| V13               | GP                                                         | IA4                                    | IRQ1                 | GPOA4       |                                 |           |

| V14               | GP                                                         | IAO                                    | IRQ11                | GPOA0       |                                 |           |

| V15               | GPI                                                        | A28                                    | IRQ17                | GPOA28      | TX_ER                           | reserved  |

| V16               |                                                            | GPID6                                  |                      | GPOD6       | RXD2                            | reserved  |

| V17               | GPI                                                        | A22                                    | IRQ22                | GPOA22      | R>                              | KD0       |

| V18               | GPI                                                        | A24                                    | IRQ24                | GPOA24      | TX                              | _EN       |

| V19               |                                                            | reser                                  | rved                 |             | С                               | RS        |

| V20               |                                                            |                                        | r                    | DI          |                                 |           |

| W1                |                                                            |                                        | G                    | ND          |                                 |           |

| W2                |                                                            |                                        | V                    | MDC         |                                 |           |

| W3                |                                                            |                                        | A                    | 12          |                                 |           |

| W4                |                                                            |                                        |                      | 48          |                                 |           |

| W5                |                                                            |                                        |                      | 47          |                                 |           |

| W6                |                                                            |                                        |                      | 46          |                                 |           |

| W7                |                                                            |                                        |                      | 43          |                                 |           |

| W8                |                                                            |                                        | 1                    | ١C          |                                 |           |

| W9                | GPI                                                        | A17                                    | IRQ13                | GPOA17      | EVNT1                           | CLKO      |

| W10               | BM0                                                        | GPI                                    | C14                  | GPOC14      | EV                              | NT2       |

| W11               | GPI                                                        | A10                                    | IRQ5                 | GPOA10      | TO                              | RFS       |

| W12               | GP                                                         | IA7                                    | IRQ7                 | GPOA7       | T0                              | TFS       |

| W13               | GP                                                         | IA3                                    | IRQ8                 | GPOA3       | T1                              | RD        |

### Table 1. MSC7113 Signals by Ball Designator (continued)

|        | Signal Names     |                          |                      |             |              |            |  |  |

|--------|------------------|--------------------------|----------------------|-------------|--------------|------------|--|--|

| Number |                  | s                        | oftware Control      | ed          | Hardware     | Controlled |  |  |

|        | End of Reset     | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary      | Alternate  |  |  |

| W14    | GP               | 'IA1                     | IRQ10                | GPOA1       | T1           | TFS        |  |  |

| W15    |                  | GPID4                    |                      | GPOD4       | TXD2         | reserved   |  |  |

| W16    | GP               | A27                      | IRQ18                | GPOA27      | RXD3 reserve |            |  |  |

| W17    | GP               | A19                      | IRQ19                | GPOA19      | T>           | KD1        |  |  |

| W18    | GP               | A23                      | IRQ23                | GPOA23      | TXCLK o      | or REFCLK  |  |  |

| W19    | GP               | A26                      | IRQ26                | GPOA26      | RX           | _ER        |  |  |

| W20    | H8BIT            |                          | reserved             |             | М            | DC         |  |  |

| Y1     | V <sub>DDM</sub> |                          |                      |             |              |            |  |  |

| Y2     |                  |                          | C                    | GND         |              |            |  |  |

| Y3     | A9               |                          |                      |             |              |            |  |  |

| Y4     | A1               |                          |                      |             |              |            |  |  |

| Y5     | AO               |                          |                      |             |              |            |  |  |

| Y6     | A4               |                          |                      |             |              |            |  |  |

| Y7     |                  |                          | E                    | BA1         |              |            |  |  |

| Y8     | rese             | erved                    | NMI                  |             | reserved     |            |  |  |

| Y9     | BM1              | GPI                      | C15                  | GPOC15      | EV           | 'NT3       |  |  |

| Y10    | GP               | A11                      | IRQ4                 | GPOA11      | TO           | RCK        |  |  |

| Y11    |                  | GPIA9                    |                      | GPOA9       | тс           | )RD        |  |  |

| Y12    |                  | GPIA6                    |                      | GPOA6       | TC           | )TD        |  |  |

| Y13    | GF               | IA5                      | IRQ0                 | GPOA5       | T1           | RCK        |  |  |

| Y14    | GF               | IA2                      | IRQ9                 | GPOA2       | T1TCK        |            |  |  |

| Y15    | GP               | A29                      | IRQ16                | GPIA29      | TXD3         | reserved   |  |  |

| Y16    |                  | GPID5                    |                      | GPOD5       | RXCLK        | reserved   |  |  |

| Y17    | GP               | A20                      | IRQ20                | GPOA20      | T            | KD0        |  |  |

| Y18    | GP               | A21                      | IRQ21 GPOA21 RXD1    |             | XD1          |            |  |  |

| Y19    |                  |                          | C                    | GND         |              |            |  |  |

| Y20    | GP               | A25                      | IRQ25                | GPOA25      | RX_DV o      | or CRS_DV  |  |  |

### Table 1. MSC7113 Signals by Ball Designator (continued)

**Electrical Characteristics**

# 2 Electrical Characteristics

This document contains detailed information on power considerations, DC/AC electrical characteristics, and AC timing specifications. For additional information, see the *MSC711x Reference Manual*.

## 2.1 Maximum Ratings

### CAUTION

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, normal precautions should be taken to avoid exceeding maximum voltage ratings. Reliability is enhanced if unused inputs are tied to an appropriate logic voltage level (for example, either GND or  $V_{DD}$ ).

#### ww.DataSheet4U.com

In calculating timing requirements, adding a maximum value of one specification to a minimum value of another specification does not yield a reasonable sum. A maximum specification is calculated using a worst case variation of process parameter values in one direction. The minimum specification is calculated using the worst case for the same parameters in the opposite direction. Therefore, a "maximum" value for a specification never occurs in the same device with a "minimum" value for another specification; adding a maximum to a minimum represents a condition that can never exist.

Table 2 describes the maximum electrical ratings for the MSC7113.

| Rating                        | Symbol             | Value              | Unit |  |  |

|-------------------------------|--------------------|--------------------|------|--|--|

| Core supply voltage           | V <sub>DDC</sub>   | 1.5                | V    |  |  |

| Memory supply voltage         | V <sub>DDM</sub>   | 4.0                | V    |  |  |

| PLL supply voltage            | V <sub>DDPLL</sub> | 1.5                | V    |  |  |

| I/O supply voltage            | V <sub>DDIO</sub>  | -0.2 to 4.0        | V    |  |  |

| Input voltage                 | V <sub>IN</sub>    | (GND – 0.2) to 4.0 | V    |  |  |

| Reference voltage             | V <sub>REF</sub>   | 4.0                | V    |  |  |

| Maximum operating temperature | TJ                 | 105                | °C   |  |  |

| Minimum operating temperature | T <sub>A</sub>     | -40                | °C   |  |  |

| Storage temperature range     | T <sub>STG</sub>   | -55 to +150        | °C   |  |  |

#### **Table 2. Absolute Maximum Ratings**

Notes: 1. Functional operating conditions are given in Table 3.

- 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximum is not guaranteed. Stress beyond the listed limits may affect device reliability or cause permanent damage.

- 3. Section 3.1, Thermal Design Considerations includes a formula for computing the chip junction temperature (T<sub>J</sub>).

# 2.2 Recommended Operating Conditions

Table 3 lists recommended operating conditions. Proper device operation outside of these conditions is not guaranteed.

| Rating                      | Symbol                           | Value                        | Unit   |

|-----------------------------|----------------------------------|------------------------------|--------|

| Core supply voltage         | V <sub>DDC</sub>                 | 1.14 to 1.26                 | V      |

| Memory supply voltage       | V <sub>DDM</sub>                 | 2.38 to 2.63                 | V      |

| PLL supply voltage          | V <sub>DDPLL</sub>               | 1.14 to 1.26                 | V      |

| I/O supply voltage          | V <sub>DDIO</sub>                | 3.14 to 3.47                 | V      |

| Reference voltage           | V <sub>REF</sub>                 | 1.19 to 1.31                 | V      |

| Operating temperature range | T <sub>J</sub><br>T <sub>A</sub> | maximum: 105<br>minimum: –40 | ℃<br>℃ |

| Table 3. Recommended | <b>Operating Conditions</b> |

|----------------------|-----------------------------|

|----------------------|-----------------------------|

# 2.3 Thermal Characteristics

Table 4 describes thermal characteristics of the MSC7113 for the MAP-BGA package.

|                                                       | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                 |                      | MAP-BGA <sup>2</sup>  | $17 	imes 17 \text{ mm}^5$    |                    |  |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------|-----------------------|-------------------------------|--------------------|--|