# CS1180 用户手册

www.DataSheet4U.com

# 深圳市苍海科技有限公司

# 目 录

| 1 (                 | CS1180 功能说明                        | 4  |

|---------------------|------------------------------------|----|

| 1.1                 | CS1180 主要功能特性                      | 4  |

| 1.2                 | 应用场合                               | 4  |

| 1.3                 | 功能描述                               | 5  |

| 2 (                 | CS1180 特性说明                        | 6  |

| 2.1                 | 芯片绝对最大极限值                          | 6  |

| 2.2                 |                                    |    |

| 2.3                 |                                    |    |

| 2.4                 | CS1180 电气特性                        | 9  |

| 2.5                 | CS1180 时序                          | 11 |

| 3 (                 | CS1180 功能模块描述                      | 13 |

| 3.1.                | . 输入模拟缓冲器(Buffer)                  | 13 |

| 3.2.                | . 可编程增益放大器(PGA)                    | 13 |

| 3.3.                | . 调制器(Modulator)                   |    |

| 3.4.                | . 误差校正(Calibration)                |    |

| 3                   | 3.3.1 系统校正(System Calibration)     |    |

| 3.4                 | 外接参考电压(External Voltage Reference) | 14 |

| 3.5                 | 时钟单元(Clock Unit)                   | 14 |

| 3.6                 | 数字滤波器(FIR)                         | 14 |

| 3.7                 | 1 13 200 ( == )                    |    |

|                     | 3.7.1 片选信号( CS )                   |    |

| _                   | 3.7.2 串行时钟( SCLK )                 |    |

| _                   | 3.7.3 数据输入(SDI)和数据输出(SDO)          |    |

| _                   | 3.7.4 数据准备就绪 ( DRDY )              |    |

| 3.8                 |                                    |    |

| www.DataSheet44.con | CS1180 寄存器描述                       | 16 |

| 4.1                 | 寄存器列表                              | 16 |

| 4.2                 | 寄存器详细描述                            | 17 |

| 5 0                 | CS1180 指令描述                        | 21 |

| 5.1                 | CS1180 指令列表                        | 21 |

| 5.2                 | CS1180 指令详细描述                      | 22 |

| 6 (                 | CS1180 的封装                         | 24 |

# 图列表

| 图 1 CS1180 原理框图         | 5  |

|-------------------------|----|

| 图 2 CS1180 管脚图          |    |

| 图 3 CS1180 时序图          | 11 |

| 图 4 外部晶振连接图             | 14 |

|                         |    |

| 表 清 单                   |    |

| 表 1 CS1180 极限值          | 6  |

| 表 2 CS1180 数字逻辑特性       | 6  |

| 表 3 CS1180 管脚描述         |    |

| 表 4 CS1180 封装           | 8  |

| 表 5 AVDD=5V时CS1180 电气特性 | 9  |

| 表 6 AVDD=3V时CS1180 电气特性 | 10 |

| 表 7 CS1180 时序表          | 12 |

| 表 8 调制器采样频率表            |    |

| 表 9 外部参考电压和RAN的关系表      | 14 |

| 表 10 内部寄存器详细列表          | 16 |

| 表 11 CS1180 指令描述表       | 21 |

# 1 CS1180 功能说明

CS1180 是高精度、低功耗模数转换芯片。其分辨率为 24bit, 有效分辨率可达 19 位。可以广泛使用在工艺控制、量重、液体/气体化学分析、血液分析、智能发送器、便携测量仪器领域

### 1.1 CS1180 主要功能特性

- 24 位无失码、19 位有效精度模数转换器

- 集成 50Hz、60Hz 陷波(可达-90dB)

- INL 小于 0.0015%

- 可编程增益(1~128)

- 单时钟周期准备就绪

- 可编程模数转换(ADC)数据速率输出

- 外接参考电压范围可以为 0.1V~5V

- 芯片带有校正

- 集成兼容 SPI 总线接口

#### 1.2 应用场合

- 工业过程控制

- 重量计

- 液体/气体化学分析

- 血液计

- 智能变换器

- 便携式设备

# 1.3 功能描述

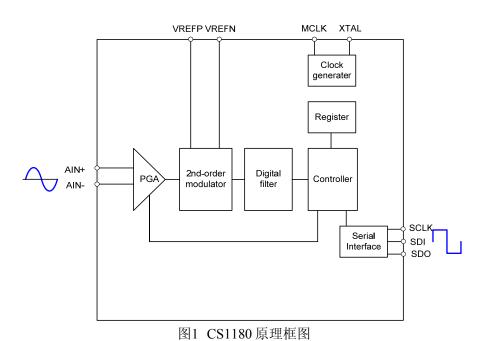

CS1180原理框图如图 1 所示。

CS1180 是 24 位高精度、低功耗 Sigma-Delta 模数转换芯片,有效分辨率可达 19 位。可以在  $2.7V\sim5.5V$  电源电压条件下工作.

CS1180 提供的  $1\sim$ 128 倍可编程增益放大器,在 128 倍时,CS1180 有效分辨率可达 18bit。调制器是一个二阶 Sigma-Delta 调制器,芯片的 FIR 滤波器提供 50Hz 和 60Hz 陷波滤波,有效提高芯片的抗干扰性能。

CS1180 提供 SPI 兼容的串行接口总线。

www.DataSheet4U.com

# CS1180 特性说明

# 2.1 芯片绝对最大极限值

表 1 示出了 CS1180 的极限值

表1 CS1180 极限值

| 名称       | 符号    | 最小   | 最大       | 单位 | 说明                                |  |

|----------|-------|------|----------|----|-----------------------------------|--|

| 模拟电源电压   | AVDD  | -0.3 | 6        | V  | AVDD to AGND                      |  |

| 数字电源电压   | DVDD  | -0.3 | 6        | V  | DVDD to DGND                      |  |

| 地之间压差    | DVGND | -0.3 | 0.3      | V  | DGND to AGND                      |  |

| 电源瞬间电流   |       |      | 100      | mA | Input Current momentary           |  |

| 电源恒定电流   |       |      | 10       | mA | Input Current continuous          |  |

| 数字管脚输入电压 |       | -0.3 | DVDD+0.3 | V  | Digital Output Voltage to DGND    |  |

| 数字输出管脚电压 |       | -0.3 | DVDD+0.3 | V  | Digital Output Voltage to DOND    |  |

| 节温       |       |      | 150      | °C | Max. Junction Temperature         |  |

| 工作温度     |       | -40  | 85       | °C | Operating Temperature             |  |

| 储存温度     |       | -60  | 150      | °C | Storage Temperature               |  |

| 芯片管脚焊接温度 |       |      | 240      | °C | Lead Temperature (Soldering, 10s) |  |

# 2.2 CS1180 数字逻辑特性

表 2 示出了 CS1180 的数字逻辑特性

表2 CS1180 数字逻辑特性

|                 | 参数     | 最小                | 典型 | 最大                | 单位  | 条件说明    |

|-----------------|--------|-------------------|----|-------------------|-----|---------|

|                 | VIH    | $0.8 \times DVDD$ |    | DVDD              | V   |         |

|                 | VIL    | DGND              |    | $0.2 \times DVDD$ | V   |         |

|                 | VOH    | DVDD-0.4          |    | DVDD+0.4          | V   | Ioh=1mA |

|                 | VOL    | DGND              |    | DGND+0.4          | V   | IoL=1mA |

| www.DataSheet4l | · 4414 |                   |    | 10                | uA  | VI=DVDD |

|                 | IIL    | -10               |    |                   | uA  | VI=DGND |

|                 | fosc   | 1                 |    | 5                 | MHz |         |

|                 | tosc   | 200               |    | 1000              | ns  |         |

|                 | 说明:    |                   |    |                   |     |         |

1、CS1180 数字接口为 CMOS 逻辑接口。

# 2.3 CS1180 的管脚和封装

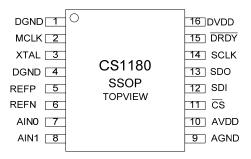

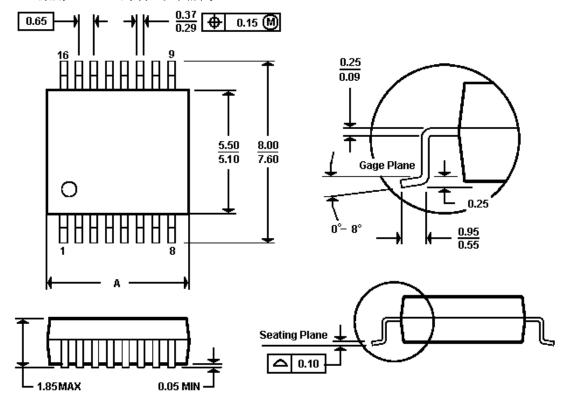

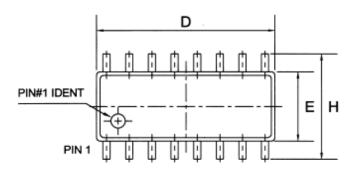

CS1180 管脚图如图 2 所示,管脚的详细描述则见表 3 和表 4

图2 CS1180 管脚图

表3 CS1180 管脚描述

|     | 管脚序号    | 符号                       | 管脚描述                  | 备注 |

|-----|---------|--------------------------|-----------------------|----|

| Ī   | 1       | DGND                     | 数字地                   |    |

|     | 2       | MCLK                     | 主时钟输入,1~10MHz         |    |

|     | 3       | XTAL                     | 晶振驱动管脚 2              |    |

|     | 4       | DGND                     | 数字地                   |    |

|     | 5       | REFP                     | 模拟(正)参考电压输入端          |    |

|     | 6       | REFN                     | 模拟(负)参考电压输入端          |    |

|     | 7       | AIN0                     | 模拟输入+                 |    |

|     | 8       | AIN1                     | 模拟输入 -                |    |

|     | 9       | AGND                     | 模拟地                   |    |

|     | 10      | AVDD                     | 模拟电源电压 2.7V~5.25V     |    |

|     | 11      | $\overline{\mathrm{CS}}$ | 芯片选择信号,低有效            |    |

| Lo  | 12      | SDI                      | 串口输入数据                |    |

| J.E | 13      | SDO                      | 串口输出数据                |    |

|     | 14 SCLK |                          | 串口工作时钟,采用 Schmitt 触发器 |    |

|     | 15      | DRDY                     | 数据准备就绪指示信号, 低有效       |    |

|     | 16      | DVDD                     | 数字电源电压, 2.7~5.25V     |    |

www.DataSheet4U

CS1180 使用的是 SSOP16 封装,工作温度范围为-40℃到+85℃,参见表 4

### 表4 CS1180 封装

| 产品名称   | 封装及管脚数 | 工作温度范围     |

|--------|--------|------------|

| CS1180 | SSOP16 | _40°C~85°C |

# 2.4 CS1180 电气特性

表5 AVDD=DVDD=5V 时 CS1180 电气特性

| 参数                                      |                    | 条件                                                             | 最小值       | 典型值       | 最大值                | 单位          |

|-----------------------------------------|--------------------|----------------------------------------------------------------|-----------|-----------|--------------------|-------------|

|                                         | HE LOCAL STREET    | Buffer 关闭                                                      | AGND-0.1  |           | AVDD+0.1           | V           |

|                                         | 模拟输入范围             | Buffer 打开                                                      | AGND+0.4  |           | AVDD-1.5           | V           |

|                                         | 满幅输入电压             | RAN=0                                                          |           |           | ±VREF/PGA          | V           |

|                                         | (AIN+) - (AIN-)    | RAN=1                                                          |           |           | $\pm$ VREF/(2×PGA) | V           |

|                                         | , , , ,            | Buffer 关闭                                                      |           | 5/PGA     | ,                  | ΜΩ          |

| 模拟输入                                    | 差分输入阻抗             | Buffer 打开                                                      |           | 5         |                    | GΩ          |

|                                         |                    | $f_{DATA} = 3.75Hz$                                            |           | 1.65      |                    | Hz          |

|                                         | 带宽(-3dB)           | $f_{DATA} = 7.50Hz$                                            |           | 3.44      |                    | Hz          |

|                                         |                    | $f_{DATA} = 15.0Hz$                                            |           | 3.7       |                    | Hz          |

|                                         | PGA                | 可选增益范围                                                         | 1         |           | 128                |             |

|                                         | 输入电容               |                                                                |           | 9         |                    | pF          |

|                                         | 输入泄漏电流             | 调制器关闭, T = 25℃                                                 |           | 5         |                    | pA          |

|                                         | 分辨率                | 无失码                                                            |           | 24        |                    | Bits        |

|                                         | 积分线性度              |                                                                |           |           | $\pm 0.0015$       | % of FS     |

|                                         | 失调误差               |                                                                |           | 8         |                    | ppm of FS   |

|                                         | 失调误差漂移             |                                                                |           | 0.02      |                    | ppm of FS/℃ |

|                                         | 增益误差               |                                                                |           | 0.005     |                    | %           |

| 系统性能                                    | 增益误差漂移             |                                                                |           | 1.0       |                    | ppm/°C      |

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 共模抑制比              | 直流                                                             | 100       |           |                    | dB          |

|                                         |                    | $f_{CM} = 60$ Hz, $f_{DATA} = 15$ Hz                           |           | 130       |                    | dB          |

|                                         |                    | $f_{\text{CM}} = 50 \text{Hz}, f_{\text{DATA}} = 15 \text{Hz}$ |           | 120       |                    | dB          |

|                                         | 陷波抑制比              | $f_{CM} = 60$ Hz, $f_{DATA} = 15$ Hz                           |           | 100       |                    | dB          |

|                                         |                    | $f_{SIG} = 50$ Hz, $f_{DATA} = 15$ Hz                          | 00        | 100       |                    | dB          |

|                                         | 电源抑制比              | 直流<br>RAN=0                                                    | 80<br>0.1 | 95<br>2.5 | 2.6                | dB<br>V     |

|                                         | VREF≡REFP          | RAN = 0 $RAN = 1$                                              | 0.1       | 2.5       | AVDD               | V           |

|                                         | -REFN              | RAN = 1 $RAN = 0$                                              | 0         | 2.3       | AVDD               | V           |

| 参考电压                                    | REFP,REFN<br>输入范围  | RAN = 0 $RAN = 1$                                              | 0.1       |           | AVDD               | V           |

| 输入                                      | <b>和</b> 八花田       | 直流                                                             | 0.1       | 120       | AVDD               | dB          |

| sheet4U.com                             | 共模抑制比              | 且.かに<br>f <sub>VREFCM</sub> = 60Hz                             |           | 120       |                    | dB          |

|                                         | 偏置电流               | IVREFCM — OUTIZ                                                |           | 1.3       |                    | uA          |

|                                         | 电源电压               | AVDD                                                           | 4.75      | 1.3       | 5.25               | V           |

|                                         |                    | PGA = 1, Buffer 关闭                                             | 1./3      | 350       | 5.25               | uA          |

|                                         |                    | PGA = 1, Buffer 打开                                             |           | 470       |                    | uA          |

| 电源                                      | 模拟部分电流             | PGA = 1, Buffer 关闭                                             |           | 370       |                    | uA          |

|                                         |                    | PGA = 128, Buffer 打开                                           |           | 630       |                    | uA          |

|                                         | 数字部分电流             | PGA = 128, Buffer 打开<br>普通模式                                   |           | 1.40      |                    | mA          |

|                                         | ※ 1 HP刀 <b>七</b> 加 | ロペピスと                                                          | <u> </u>  | 1.70      | 1                  | 111/1       |

www.DataS

## 表6 AVDD=DVDD=3V时 CS1180 电气特性

| 参数         |                 | 条件                                    | 最小值      | 典型值   | 最大值                | 单位          |

|------------|-----------------|---------------------------------------|----------|-------|--------------------|-------------|

|            | 提到tA ) 英国       | Buffer 关闭                             | AGND-0.1 |       | AVDD+0.1           | V           |

|            | 模拟输入范围          | Buffer 打开                             | AGND+0.3 |       | AVDD-1.5           | V           |

|            | 满幅输入电压          | RAN=0                                 |          |       | ± VREF/PGA         | V           |

|            | (AIN+) - (AIN-) | RAN=1                                 |          |       | $\pm$ VREF/(2×PGA) | V           |

|            |                 | Buffer 关闭                             |          | 5/PGA | , ,                | ΜΩ          |

| 模拟输入       | 差分输入阻抗          | Buffer 打开                             |          | 5     |                    | GΩ          |

| (美)外間/へ    |                 | $f_{DATA} = 3.75Hz$                   |          | 1.65  |                    | Hz          |

|            | 带宽(-3dB)        | $f_{DATA} = 7.50Hz$                   |          | 3.44  |                    | Hz          |

|            |                 | $f_{DATA} = 15.0Hz$                   |          | 14.6  |                    | Hz          |

|            | PGA             | 可选增益范围                                | 1        |       | 128                |             |

|            | 输入电容            |                                       |          | 9     |                    | pF          |

|            | 输入泄漏电流          | 调制器关闭, T = 25℃                        |          | 5     |                    | pA          |

|            | 分辨率             | 无失码                                   |          | 24    |                    | Bits        |

|            | 积分线性度           |                                       |          |       | $\pm 0.0015$       | % of FS     |

|            | 失调误差            |                                       |          | 15    |                    | ppm of FS   |

|            | 失调误差漂移          |                                       |          | 0.04  |                    | ppm of FS/℃ |

|            | 增益误差            |                                       |          | 0.01  |                    | %           |

| 系统性能       | 增益误差漂移          |                                       |          | 1.0   |                    | ppm/°C      |

| 71/2017/10 | 共模抑制比           | 直流                                    | 100      |       |                    | dB          |

|            |                 | $f_{CM}$ = 60Hz, $f_{DATA}$ = 15Hz    |          | 130   |                    | dB          |

|            |                 | $f_{CM} = 50$ Hz, $f_{DATA} = 15$ Hz  |          | 120   |                    | dB          |

|            | 陷波抑制比           | $f_{CM} = 60$ Hz, $f_{DATA} = 15$ Hz  |          | 100   |                    | dB          |

|            |                 | $f_{SIG} = 50$ Hz, $f_{DATA} = 15$ Hz |          | 100   |                    | dB          |

|            | 电源抑制比           | 直流                                    | 75       | 90    | 1.20               | dB          |

|            | VREF≡REFP       | RAN = 0                               | 0.1      | 1.25  | 1.30               | V           |

|            | -REFN           | RAN = 1                               | 0        | 2.5   | 2.6                | V           |

| 参考电压       | REFP, REFN      | RAN = 0                               | 0        |       | AVDD               | V           |

| 输入         | 输入范围            | RAN = 1                               | 0.1      | 120   | AVDD               | V           |

| 1124       | 共模抑制比           | 直流                                    |          | 120   |                    | dB          |

|            | 位出土法            | $f_{VREFCM} = 60Hz$                   |          | 120   |                    | dB          |

|            | 偏置电流            | AVDD                                  | 2.7      | 0.65  | 2.2                | uA          |

| heet4U.com | 电源电压            | AVDD                                  | 2.7      | 220   | 3.3                | V           |

|            |                 | PGA = 1, Buffer 关闭                    |          | 330   |                    | uA          |

| 电源         | 模拟部分电流          | PGA = 1, Buffer 打开                    |          | 450   |                    | uA          |

|            |                 | PGA = 128, Buffer 关闭                  |          | 350   |                    | uA          |

|            |                 | PGA = 128, Buffer 打开                  |          | 630   |                    | uA          |

|            | 数字部分电流          | 普通模式                                  |          | 1.1   |                    | mA          |

www.DataS

# 2.5 CS1180 时序

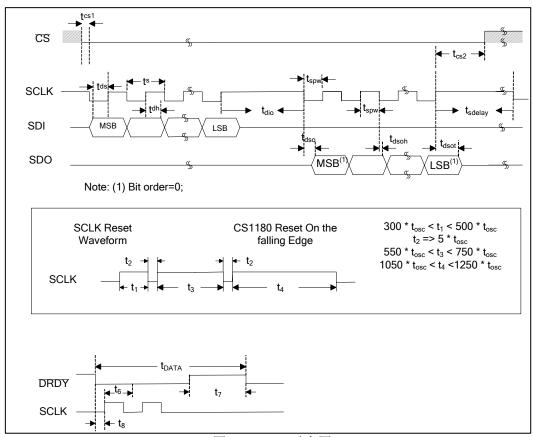

CS1180的时序图如图 3 所示,详细的时序说明见表 7

图3 CS1180 时序图

# 表7 CS1180 时序表

|                     |                                               | ***                                         |     |      |         |

|---------------------|-----------------------------------------------|---------------------------------------------|-----|------|---------|

| 参数                  | 描述                                            |                                             | 最小值 | 最大值  | 单位      |

| $t_{\rm s}$         | SCLK 时钟周期                                     |                                             | 4   |      | tosc 周期 |

| $t_{\mathrm{spw}}$  | SCLK 脉冲宽度,高                                   | 电平及低电平                                      | 200 |      | ns      |

| $t_{cs1}$           | 片选信号 CS 下降沿                                   | 与第一个 SCLK 沿的建立时间                            | 0   |      | ns      |

| t <sub>ds</sub>     | SDI数据的建立时间                                    | l(与 SCLK 的延迟)                               | 50  |      | ns      |

| t <sub>dh</sub>     | 有效 SDI 数据的保持                                  | <b>持时间</b>                                  | 50  |      | ns      |

| t <sub>dio</sub>    | 在发出下列指令时 S<br>的第一个 SCLK 时旬<br>RDATA, RREG, WR |                                             | 50  |      | tosc 周期 |

| $t_{ m dso}$        | SDO 输出数据与 SC                                  | LK 的延迟时间                                    |     | 50   | ns      |

| t <sub>dsoh</sub>   | SDO 数据的保持时间                                   | 1                                           | 0   |      |         |

| t <sub>dsot</sub>   | SDO 变为三态与 SC                                  | LK 时钟沿的延迟                                   | 6   | 10   | tosc 周期 |

| t <sub>cs2</sub>    | 片选信号 CS 保持低                                   | 电平时间与最后一个 SCLK 时钟沿                          | 0   |      | ns      |

|                     | 当前指令的最后一                                      | RREG, WREG, SYNC, RDATA,<br>STOPC           | 4   |      | tosc 周期 |

| $t_{\text{sdelay}}$ | 个 SCLK 时钟沿到                                   | OCALSYS, GCALSYS                            | 8   |      | DRDY 周期 |

| Sucius              | 下一个指令的第一<br>个 SCLK 时钟沿:                       | RESET(也可以是通过 SCLK 或者<br>RST 引脚发出的 RESET 指令) | 16  |      | tosc 周期 |

| $t_6$               | 允许的模拟输入信号                                     | 号的变化到下一次有效的转换                               |     | 5000 | tosc 周期 |

| t <sub>7</sub>      | DOR 更新,DOR 无                                  | · · · · · · · · · · · · · · · · · · ·       | 4   |      | tosc 周期 |

| t <sub>8</sub>      | DRDY 信号变低后的                                   | 的首个 SCLK 时钟                                 | 0   |      | tosc 周期 |

## 3 CS1180 功能模块描述

#### 3.1. 输入模拟缓冲器(Buffer)

在没有使能模拟输入缓冲器(Buffer)时,输入阻抗约  $5M\Omega/PGA$ 。当系统要求较高的输入阻抗时,可以使能模拟输入缓冲器,此时可以将输入阻抗提高约到  $5G\Omega$ 。

缓冲器的使能信号可以由内部寄存器 ACR 控制。当 ACR 寄存器的 BUF 为高时,输入缓冲器使能,有效提高输入阻抗。

如果使能缓冲器,芯片增加额外的功率消耗。消耗功率的大小与 PGA 的增益有关, PGA = 1 时,增加约 50uA 电流,而 PGA = 128 时,增加的电流则达 150uA。

当开启缓冲器后,对输入信号的范围有所要求,此时要求输入信号的范围为AGND+0.3V~AVDD-1.5V。

### 3.2. 可编程增益放大器 (PGA)

内部的电压增益放大器可以编程配置增益为 1, 2, 4, 8, 16, 32, 64, 128。通过使用 PGA 可以提高有效转换精度。例如,PGA=1, 5V 满幅模数转换,有效识别电压为 4.7uV,但 如果 PGA=128, 39mV 满幅模数转换时,可最小可以识别 75nV 输入电压。

#### 3.3. 调制器(Modulator)

CS1180 的调制器是单环回、2 阶 $\Sigma$ — $\Delta$ 调制器,调制器的采样频率可以通过 SPEED (ACR 寄存器的 bit 5) 控制,具体如下表所示:

| 晶振频率   | SPEED | ADC 采样频率 | 数据输出速率  | 陷波频率    |         |         |

|--------|-------|----------|---------|---------|---------|---------|

| (MHz)  | SPEED | (KHz)    | DR = 00 | DR = 01 | DR = 10 | (Hz)    |

| 2.4576 | 0     | 19.200   | 15      | 7.5     | 3.75    | 50/60   |

| 2.4370 | 1     | 9.600    | 7.5     | 3.75    | 1.875   | 25/30   |

| 4.9152 | 0     | 38.400   | 30      | 15      | 7.5     | 100/120 |

| 4.9132 | 1     | 19.200   | 15      | 7.5     | 3.75    | 50/60   |

表8 调制器采样频率表

www.DataSheet4U.com

#### 3.4. 误差校正(Calibration)

芯片校正是指芯片系统校正,校正包括模数转换器偏移误差校正(Offset calibration)、模数转换器增益校正(Gain calibration)。在进行纠正时,DRDY 维持为高,表示现在 AD 转换的结果不可用。

在芯片重新上电、外部环境温度改变、增益(PGA)改变后必须进行误差校正,以保证模数转换的正确。

完成校正后 DRDY 管脚变低,即 DRDY 输出低电平时表示芯片已经完成校正。校正完成后的第一个输出数据由于内部电路工作的延时导致不正确,不能作为正常模数转换数据。第二个转换输出数据是正常的,可以使用。

#### 3.3.1 系统校正 (System Calibration)

系统校正可以校正芯片内部及系统的偏移误差和增益误差,校正必须要求输入正确的输入信号后进行。系统校正指令包括 OCALSYS、GCALSYS,其中 OCALSYS 进行偏移误差校正,GCALSYS 进行增益误差校正,偏移误差校正、增益误差校正分别在 8 个 TDADA 数据周期内完成。

在进行偏移误差校正(OCALSYS)时,必须要求输入为差分电压为 0, 芯片计算出系统的偏移误差值并写入 OCC 寄存器中,在正常转换时予以抵消。

在进行增益误差校正(SYSGCAL)时,必须输入正满幅度(Full Scale)的电压,芯片计算出系统的增益误差并写入 GCC 寄存器中,在正常转换时予以抵消。

### 3.4 外接参考电压(External Voltage Reference)

CS1180 需要外接参考电压,具体值通过 ACR 寄存器配置。参考电压接在 REFP 与 REFN 管脚上,电压不能超过芯片的电源电压,具体电压值如下表:

| 次,并能多引起在16100000000000000000000000000000000000 |          |           |    |  |  |  |  |  |

|------------------------------------------------|----------|-----------|----|--|--|--|--|--|

| RAN (ACR.2)                                    | 电源电压 (V) | 参考差分电压(V) | 备注 |  |  |  |  |  |

| 0                                              | 5        | <=2.5     |    |  |  |  |  |  |

| 1                                              | 5        | <=5       |    |  |  |  |  |  |

| 0                                              | 3.0      | <=1.25    |    |  |  |  |  |  |

| 1                                              | 3.0      | <=2.5     |    |  |  |  |  |  |

表9 外部参考电压和 RAN 的关系表

### 3.5 时钟单元 (Clock Unit)

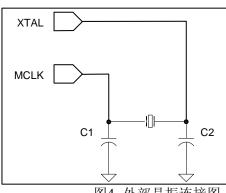

CS1180 可以外接晶体、振荡器或时钟。如果接外部时钟,则从 MCLK 管脚输入,此时 XTAL 悬空。如果外部接晶体,电路要求如下: (要求在 MCLK 及 XTAL 管脚上同时接 10~20pF 的电容)

www.DataSheet4U.com

图4 外部晶振连接图

#### 3.6 数字滤波器(FIR)

CS1180 带有一个可编程的 FIR 滤波器。FIR 滤波器可以被配置成不同的输出速率。当使用 2.4576M 的时钟时,CS1180 的输出数据的速率可以被配置成 15Hz, 7.5Hz 或者 3.75Hz。此时,FIR 滤波器可以同时对 50Hz 和 60Hz 的杂波信号进行陷波滤波。

如果希望得到其他的输出数据速率,则须使用其他的时钟频率。此时,陷波频率也同时跟着改变了。比如,当使用默认的寄存器配置,时钟频率为3.6864M时候,输出数据的频率为:

(3.6864MHz/2.4576MHz)×15Hz=22.5Hz 陷波频率为:

$(3.6864MHz/2.4576MHz) \times (50Hz 和 60Hz) = (75Hz 和 90Hz)$

### 3.7 串行总线接口(SPI)

CS1180 通过 SPI 总线与外部的控制器进行通讯。CS1180 只能用于从模式。总线接口是标准的四线 SPI 总线,包括 CS,SCLK,SDI 和 SDO。

#### 3.7.1 片选信号(CS)

在与 CS1180 进行通讯前,外部的控制器必须先发出 CS 片选信号。在整个通讯期间,CS 信号必须维持为低。当 CS 信号变高后,整个 SPI 总线会被复位。CS 信号也可以被接为常低。当 CS 信号被拉为常低时,SPI 总线可以工作在三线模式,这种情况比较适合于 CS1180 和外部的微控制器进行通讯。

#### 3.7.2 串行时钟(SCLK)

SCLK 为施密特触发,用来对 SDI 和 SDO 信号进行采样。为了防止错误的采样数据,SCLK 必须十分干净。如果在 3 个 DRDY 周期内都没有 SCLK 时钟出现,那么在下一个 SCLK 来临时,SPI 总线将被复位,进而开始下一个通讯周期。SCLK 上的一个特定的波形可以复位整个芯片。具体信息请参考 RESET 章节

#### 3.7.3 数据输入(SDI)和数据输出(SDO)

SDI和 SDO 引脚分别用来输入和输出数据。在没有使用时,SDO 为高阻态,这样就允许将 SDI和 SDO 接在一起然后通过一个双向的总线来驱动它。

#### 3.7.4 数据准备就绪(DRDY)

DRDY信号用来表示内部数据寄存器的状态。当内部数据寄存器 DOR 内新的数据准备就绪时,DRDY信号会变低。当执行完一个从内部数据寄存器 DOR 读取数据的读操作后,DRDY信号将变高。在 DOR 寄存器的数据准备更新时 DRDY信号也会变高,表示此时 DOR寄存器内的数据不可用,防止在 DOR 寄存器进行更新时从 DOR 寄存器内读取数据。DRDY的信号也可以从 ACR 寄存器的 bit 7 来获得。

#### 3.8 上电复位及芯片的复位(RESET)

# 4 CS1180 寄存器描述

CS1180 通过一系列控制寄存器来配置工作方式,控制寄存器包括数据格式、模数转换数据输出速率、校正控制等。

# 4.1 寄存器列表

内部寄存器详细列表如表 11 所示:

表10 内部寄存器详细列表

|   | 地址(H)           | 寄存器   | 第7位   | 第6位   | 第5位   | 第4位   | 第3位   | 第2位   | 第1位   | 第0位   |

|---|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|   | 00              | SETUP | ID3   | ID2   | ID1   | ID0   | 保留    | PGA2  | PGA1  | PGA0  |

|   | 01              | MUX   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     |

|   | 02              | ACR   | DRDY  | U/B   | SPEED | BUF   | BITOR | RAN   | DR1   | DR0   |

|   | 03              | ODAC  | 保留    | CHSEL | ISET1 | ISET0 | 保留    | 保留    | 保留    | 保留    |

|   | 04              | 保留    |       |       |       |       |       |       |       |       |

|   | 05              | 保留    |       |       |       |       |       |       |       |       |

|   | 06              | 保留    |       |       |       |       |       |       |       |       |

|   | 07              | OCC0  | OCC07 | OCC06 | OCC05 | OCC04 | OCC03 | OCC02 | OCC01 | OCC00 |

| h | 08<br>eet4U.com | OCC1  | OCC17 | OCC16 | OCC15 | OCC14 | OCC13 | OCC12 | OCC11 | OCC10 |

|   | 09              | OCC2  | OCC27 | OCC26 | OCC25 | OCC24 | OCC23 | OCC22 | OCC21 | OCC20 |

|   | 0A              | GCC0  | GCC07 | GCC06 | GCC05 | GCC04 | GCC03 | GCC02 | GCC01 | GCC00 |

|   | 0B              | GCC1  | GCC15 | GCC14 | GCC13 | GCC12 | GCC11 | GCC10 | GCC09 | GCC08 |

|   | 0C              | GCC2  | GCC23 | GCC22 | GCC21 | GCC20 | GCC19 | GCC18 | GCC17 | GCC16 |

|   | 0D              | DOR2  | DOR23 | DOR22 | DOR21 | DOR20 | DOR19 | DOR18 | DOR17 | DOR16 |

|   | 0E              | DOR1  | DOR15 | DOR14 | DOR13 | DOR12 | DOR11 | DOR10 | DOR09 | DOR08 |

|   | 0F              | DOR0  | DOR07 | DOR06 | DOR05 | DOR04 | DOR03 | DOR02 | DOR01 | DOR00 |

www.DataSl

### 4.2 寄存器详细描述

SETUP 寄存器(地址=00H, 复位值=xxxx0000) PGA 控制(SETUP REGISTER)

| MSB   |       |       |       |       |       |       |       |  |  |

|-------|-------|-------|-------|-------|-------|-------|-------|--|--|

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

| ID3   | ID2   | ID1   | ID0   | 保留    | PGA2  | PGA1  | PGA0  |  |  |

SETUP. 7-4: 芯片的 ID 编号, 供厂家使用

SETUP.3 :保留

SETU.2-0 : PGA2/PGA1/PGA0, 可编程增益放大器增益选择(Programmable Gain Amplifier Gain

Selection)

000=1 (默认值);

001 = 2

010 = 4

011 = 8

100 = 16

101 = 32

110 = 64

111 = 128

MUX 寄存器(地址=01H,复位值=01H)通道选择(SETUP REGISTER)

| MSB   | MSB   |                                     |   |   |   |   |   |  |  |

|-------|-------|-------------------------------------|---|---|---|---|---|--|--|

| Bit 7 | Bit 6 | Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 |   |   |   |   |   |  |  |

| 0     | 0     | 0                                   | 0 | 0 | 0 | 0 | 1 |  |  |

此寄存器配置为 00H 时,可将 ADC 的输入端从芯片内部短路,此时可以测量 ADC 自身的性能(此时 ADC 的输出即为其噪声),在正常使用时,必须将此寄存器配置为 01H。

ACR寄存器(地址=02H, 复位值=x0H) 模拟电路控制(Analog Control Register)

|       |       |       | **    |       |       |       |       |

|-------|-------|-------|-------|-------|-------|-------|-------|

| MSB   |       |       |       |       |       |       | LSB   |

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| DRDY  | U/B   | SPEED | BUF   | BITOR | RAN   | DR1   | DR0   |

ACR.7 : DRDY,数据准备就绪(Data Ready,只读),与输出管脚 DRDY 值相同;

ACR.6 : U/B, 数据格式 (Data Format)

0=双极性(默认值);

+FSR 输出7FFFFFH, ZERO=000000H, -FSR=800000H;

1=单极性:

+FSR 输出 FFFFFFH, ZERO =000000H, -FSR =000000H;

ACR.5 : SPEED,模数转换器采样频率控制(Modulator Clock Speed)

0=fosc/128 (默认值);

$1 = \frac{\text{fosc}}{256}$ ;

ACR.4 : BUF, 输入缓冲器使能(Buffer Enable);

ACR.3 : BITOR, 输出数据 bit 顺序

0=高位在前(默认值)

1=低位在前

ACR.2 : RAN, 转换范围选择(Select)

0=满幅输入(Full Scale)为+/-V<sub>REF</sub>(默认值);

1=满幅输入(Full Scale)为+/- V<sub>REF</sub>/2;

ACR.1-0 : DR1/DR0,数据输出速率(Data Rate)

00=15Hz(默认值);

01 = 7.5Hz;

10=3.75Hz; 11=保留(Reserved)

#### ODAC寄存器(地址=03<sub>H</sub>,复位值=00<sub>H</sub>)Offset DAC设置

| MSB   |       |       |       |       |       |       | LSB   |

|-------|-------|-------|-------|-------|-------|-------|-------|

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| 无效    | CHSEL | ISET1 | ISET0 | 无效    | 无效    | 无效    | 无效    |

ISET1-0: 模拟电路偏置电流选择,

00=偏置电流为 10uA (默认值)

01 或 10=偏置电流增加 25%,

11=偏置电流增加 50%,

当使用较高的时钟频率时,增加模拟电路偏置电流有助于提高 CS1180 的性能。

CHSEL: 斩波一调制方式选择。

0=斩波频率为调制器采样频率 1/2, PGA=1~128 时可用。(默认)

1=斩波频率等于调制器采样频率,PGA=2~128时可用。

在一般情况下 CHSEL 设置为 0 即可,但是在某些情况下(具体情况和外围应用电路有关)一些高频噪声可能会耦合到低频段,此时可以设置 CHSEL 为 1,注意此时会导致失调电压和噪声又一些增大。

#### OCC0 寄存器(地址=07<sub>H</sub>,复位值=00<sub>H</sub>),失调误差系数(Offset Calibration Coefficient)

| MSB                                                         |         |        |       |       |       |       |       |  |  |

|-------------------------------------------------------------|---------|--------|-------|-------|-------|-------|-------|--|--|

| Bit 7                                                       | Bit 6   | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

| OCC07                                                       | OCC06   | OCC05  | OCC04 | OCC03 | OCC02 | OCC01 | OCC00 |  |  |

| OCC0 与 OCC1 及 OCC2 组成偏移误差校正系数 OCC23~0 (共 24 位, OCC23 是 MSB, |         |        |       |       |       |       |       |  |  |

| OCC00 是 I                                                   | LSB),对偏 | 扇移误差进行 | 校正。   |       |       |       |       |  |  |

### OCC1 寄存器(地址=08<sub>H</sub>,复位值=00<sub>H</sub>)失调误差正系数(Offset Calibration Coefficient)

| MSB       |                                                             |       |       |       |       |       | LSB   |  |  |

|-----------|-------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--|--|

| Bit 7     | Bit 6                                                       | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

| OCC15     | OCC14                                                       | OCC13 | OCC12 | OCC11 | OCC10 | OCC09 | OCC08 |  |  |

| OCC0与O    | OCC0 与 OCC1 及 OCC2 组成偏移误差校正系数 OCC23~0 (共 24 位, OCC23 是 MSB, |       |       |       |       |       |       |  |  |

| OCC00 是 I | LSB),对偏                                                     | 移误差进行 | 校正。   |       |       |       |       |  |  |

### www.DataSheet4OCC2 寄存器(地址=09H,复位值=00H)失调误差校正系数(Offset Calibration Coefficient)

| MSB       |           |        |        |          |           |           | LSB   |

|-----------|-----------|--------|--------|----------|-----------|-----------|-------|

| Bit 7     | Bit 6     | Bit 5  | Bit 4  | Bit 3    | Bit 2     | Bit 1     | Bit 0 |

| OCC23     | OCC22     | OCC21  | OCC20  | OCC19    | OCC18     | OCC17     | OCC16 |

| OCC0与O    | CC1 及 OCC | 2组成偏移设 | 吴差校正系数 | COCC23~0 | (共 24 位,C | CC23 是 MS | SB,   |

| OCC00 是 1 | LSB),对偏   | 扇移误差进行 | 校正。    |          |           |           |       |

#### GCC0 寄存器(地址=0A<sub>H</sub>,复位值=59<sub>H</sub>)增益误差校正系数(Gain Calibration Coefficient)

| MSB       |                                                             |        |       |       |       |       |       |  |  |

|-----------|-------------------------------------------------------------|--------|-------|-------|-------|-------|-------|--|--|

| Bit 7     | Bit 6                                                       | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

| GCC07     | GCC06                                                       | GCC05  | GCC04 | GCC03 | GCC02 | GCC01 | GCC00 |  |  |

| GCC0与G    | GCC0 与 GCC1 及 GCC2 组成偏移误差校正系数 GCC23~0 (共 24 位, GCC23 是 MSB, |        |       |       |       |       |       |  |  |

| GCC00 是 I | LSB),对增                                                     | 曾益误差进行 | 校正。   |       |       |       |       |  |  |

# GCC1 寄存器(地址=0B<sub>H</sub>,复位值=55<sub>H</sub>)增益误差校正系数(Gain Calibration Coefficient)

| MSB                                                       |         |        |       |       |       |       |       |  |  |

|-----------------------------------------------------------|---------|--------|-------|-------|-------|-------|-------|--|--|

| Bit 7                                                     | Bit 6   | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

| GCC15                                                     | GCC14   | GCC13  | GCC12 | GCC11 | GCC10 | GCC09 | GCC08 |  |  |

| GCC0 与 GCC1 及 GCC2 组成偏移误差校正系数 GCC23~0(共 24位, GCC23 是 MSB, |         |        |       |       |       |       |       |  |  |

| GCC00 是 1                                                 | LSB),对增 | 曾益误差进行 | 校正。   |       |       |       |       |  |  |

### GCC2 寄存器(地址=0C<sub>H</sub>,复位值=55<sub>H</sub>)增益误差校正系数(Gain Calibration Coefficient)

| MSB       |                                                            |                                          |       |       |       |       |       |  |  |  |

|-----------|------------------------------------------------------------|------------------------------------------|-------|-------|-------|-------|-------|--|--|--|

| Bit 7     | Bit 6                                                      | Bit 5                                    | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |

| GCC23     | GCC22                                                      | CC22 GCC21 GCC20 GCC19 GCC18 GCC17 GCC16 |       |       |       |       |       |  |  |  |

| GCC0与G    | GCC0 与 GCC1 及 GCC2 组成偏移误差校正系数 GCC23~0(共 24 位, GCC23 是 MSB, |                                          |       |       |       |       |       |  |  |  |

| GCC00 是 1 | LSB),对增                                                    | 曾益误差进行                                   | 校正。   |       |       |       |       |  |  |  |

### DOR2 寄存器(地址=0D<sub>H</sub>,复位值=00<sub>H</sub>)模数转换数据(Data Output Register)

| MSB     |            |        |         |          |          |           |        |  |  |

|---------|------------|--------|---------|----------|----------|-----------|--------|--|--|

| Bit 7   | Bit 6      | Bit 5  | Bit 4   | Bit 3    | Bit 2    | Bit 1     | Bit 0  |  |  |

| DOR 23  | DOR22      | DOR 21 | DOR 20  | F DOR 19 | DOR 18   | DOR 17    | DOR 16 |  |  |

| DOR 0与I | OOR 1 及 DO | R2组成模数 | 女转换数据 D | OR23~0(共 | E 24位,DO | R23 是 MSB | DOR00  |  |  |

| 是 LSB)。 |            |        |         |          |          |           |        |  |  |

### DOR1 寄存器(地址=0E<sub>H</sub>,复位值=00<sub>H</sub>)模数转换数据(Data Output Register)

| MSB      |          |          |         |          |          |           | LSB     |

|----------|----------|----------|---------|----------|----------|-----------|---------|

| Bit 7    | Bit 6    | Bit 5    | Bit 4   | Bit 3    | Bit 2    | Bit 1     | Bit 0   |

| DOR15    | DOR14    | DOR13    | DOR12   | DOR11    | DOR10    | DOR09     | DOR08   |

| DOR 0与 I | OOR 1及DO | R 2 组成模数 | 女转换数据 D | OR23~0(共 | E 24位,DO | R23 是 MSB | , DOR00 |

| 是 LSB)。  |          |          |         |          |          |           |         |

### DOR0 寄存器(地址=0F<sub>H</sub>,复位值=00<sub>H</sub>)模数转换数据(Data Output Register)

|   | MSB                                                             |       |       |       |       |       |       | LSB   |

|---|-----------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|

|   | Bit 7                                                           | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| е | <sup>4</sup> DOR07                                              | DOR06 | DOR05 | DOR04 | DOR03 | DOR02 | DOR01 | DOR00 |

|   | DOR 0 与 DOR 1 及 DOR 2 组成模数转换数据 DOR23~0(共 24 位,DOR23 是 MSB,DOR00 |       |       |       |       |       |       |       |

|   | 是 LSB)。                                                         |       |       |       |       |       |       |       |

www.DataShee

# 5 CS1180 指令描述

CS1180 使用了一系列指令,指令完成对芯片的工作模式控制、工作速度控制、误差校正等。这些指令中有些是单条的(比如 RESET),有些则需要另外的操作数(比如 WREG等)。

操作数:

n=数量 (0到127)

r=寄存器(0到15)

x = 任意值

# 5.1 CS1180 指令列表

表 12 示出了 CS1180 的指令集

表11 CS1180 指令描述表

| 表刊 CSTTOV 用 V 固定化 |                   |                                     |           |  |  |  |

|-------------------|-------------------|-------------------------------------|-----------|--|--|--|

| 指令                | 描述                | 操作码                                 | 操作数       |  |  |  |

| RDATA             | 从 DOR 寄存器中读取数据    | 0000 0001<br>( 01 <sub>H</sub> )    | -         |  |  |  |

| RREG              | 读取寄存器 "rrrr" 的值   | 0001 r r r r<br>( 1X <sub>H</sub> ) | xxxx_nnnn |  |  |  |

| WREG              | 将数据写入到寄存器 "rrrr"中 | 0101 r r r r<br>( 5X <sub>H</sub> ) | xxxx_nnnn |  |  |  |

| OCALSYS           | 对系统的失调误差进行纠正      | 1111 0011 ( F3 <sub>H</sub> )       |           |  |  |  |

| GCALSYS           | 对系统的增益误差进行纠正      | 1111 0100<br>( F4 <sub>H</sub> )    |           |  |  |  |

| WAKEUP            | 将系统从睡眠模式模式中唤醒     | 1111 1011<br>( FB <sub>H</sub> )    |           |  |  |  |

| RESET<br>U.com    | 将芯片复位到上电后的状态      | 1111 1110<br>( FE <sub>H</sub> )    |           |  |  |  |

www.DataSheet4

注:接收数据时总是高位在前。发送数据的格式则由 ACR 寄存器的 BITORDER 位来决定

#### 5.2 CS1180 指令详细描述

RDATA一读取数据

描述: 从 DOR 寄存器中读取最新的一次 AD 转换的值,这个值为 24bit

操作数:无 字节: 1

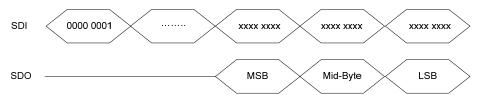

编码: 0000 0001 数据传输序列:

RREG一读取寄存器的值

描述: 输出最多 16 个寄存器的值。首个寄存器的地址由指令的首个操作数决定。读取的寄存器的数量由指令的第二个操作数的值加 1 决定。如果这个值超过了剩余的寄存器的数目,则寄存器的地址转到首个寄存器上。

操作数: r, n 字节: 2

编码: 0001 rrrr xxxx nnnn

数据传输序列:

读取两个寄存器的值,首个寄存器的地址为 01<sub>H</sub>(MUX)

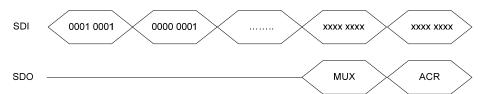

WREG-将数据写入寄存器中

www.DataSheet4描述: 将数据写入多个寄存器中。首个寄存器的地址由指令的首个操作数决定。读取的寄存器的数量由指令的第二个操作数的值加1决定。

操作数: r, n 字节: 2

编码: 0101 rrrr xxxx nnnn

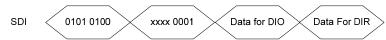

数据传输序列:

将数据写入到两个寄存器中,第一个寄存器的地址为04H(DIO)

OCALSYS一纠正系统的失调误差

描述: 对系统的失调误差进行纠正。这个时候,系统的输入信号应该为 0, CS1180 计算出 OCC 的值对失调误差进行补偿。进行完这个操作后,OCC 寄存器的值将被更新。用户必须在正确的模拟输入端输入 0 信号 OCC 寄存器会被自动更新。

操作数:无

字节: 1

编码: 1111 0011 数据传输序列:

SDI 1111 0011

#### GCALSYS一纠正系统的增益误差

描述: 对系统的增益误差进行纠正,此时,系统的输入信号应该为满幅电压,CS1180 计算出 GCC 的值对增益误差进行补偿。进行完这个操作后,OCC 寄存器的值将被更新。用户必须在正确的模拟输入端输入满幅信号。GCC 寄存器会被自动更新。

操作数:无

字节: 1

编码: 1111 0100 数据传输序列:

SDI 1111 0100

WAKEUP一将系统从睡眠模式中唤醒

描述: 将 CS1180 从睡眠模式中唤醒

操作数:无 字节: 1

编码: 1111 1011 数据传输序列:

SDI 1111 1100

RESET-将芯片复位到默认状态

描述: 将所有寄存器的值复位到上电后的状态。这个指令可以终止 RDATAC 指令

操作数:无 字节: 1

编码: 1111 1110 数据传输序列:

SDI 1111 1110

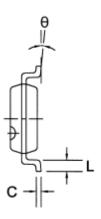

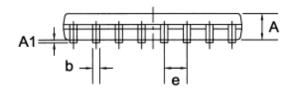

# 6 CS1180 的封装

CS1180采用 SSOP16 封装,如图所示。

#### NOTES:

A. All linear dimensions are in millimeters

www.DataSheet4U.com B. This drawing is subject to change without notice

- C. Body demensions do not include mold flash or protrusion nont to exceed 0.15

- D. Falls within JEDEC MO-150

| A MAX | 6.40 |

|-------|------|

| A MIN | 6.00 |

CS1180采用 SOP16 封装,如图所示:

| 0      | Dimensions In Millmeters |       |       | Dimensions In Inches |       |       |  |

|--------|--------------------------|-------|-------|----------------------|-------|-------|--|

| Symbol | Min                      | Nom   | Max   | Min                  | Nom   | Max   |  |

| Α      | 1.30                     | 1.50  | 1.70  | 0.051                | 0.059 | 0.067 |  |

| A1     | 0.06                     | 0.16  | 0.26  | 0.002                | 0.006 | 0.010 |  |

| b      | 0.30                     | 0.40  | 0.55  | 0.012                | 0.016 | 0.022 |  |

| С      | 0.15                     | 0.25  | 0.35  | 0.006                | 0.010 | 0.014 |  |

| D      | 9.70                     | 10.00 | 10.30 | 0.382                | 0.394 | 0.406 |  |

| E      | 3.75                     | 3.95  | 4.15  | 0.148                | 0.156 | 0.163 |  |

| е      | _                        | 1.27  |       | _                    | 0.050 |       |  |

| Н      | 5.70                     | 6.00  | 6.30  | 0.224                | 0.236 | 0.248 |  |

| L      | 0.45                     | 0.65  | 0.85  | 0.018                | 0.026 | 0.033 |  |

| θ      | 0.                       |       | 8'    | 0.                   | _     | 8-    |  |

www. Data Sheet 4U.com