Vishay Dale

# **Plasma Panel Display Module**

256 x 64 Graphics Display with Drive Electronics, + 5V CMOS Level Video Interface and Integrated DC Converter

The APD-256G064A has been designed to offer high brightness and superior viewing aesthetics in a package that is very affordable. This display is ideal for low to medium level information content messages and would be ideal for applications such as arcade games, process control, POS terminals, medical equipment, message centers and ATM machines.

| STANDARD ELECTRICAL SPECIFICATIONS* |                 |                      |                |                 |       |

|-------------------------------------|-----------------|----------------------|----------------|-----------------|-------|

| DESCRIPTION                         | SYMBOL          | MIN.                 | TYP.           | MAX.            | UNITS |

| Logic supply                        | V <sub>cc</sub> | + 4.5                | + 5.0          | + 5.5           | VDC   |

| DC converter input                  | VDC             | + 10                 | + 24.0         | + 28.0          | VDC   |

| DC converter power @ + 12V          | IDC             | Screen Clear<br>0.13 | 50% Lit<br>2.7 | 100% Lit<br>5.5 | ADC   |

| Logic 1 Input                       | V <sub>ih</sub> | 2/3Vcc               | _              | _               | VDC   |

| Logic 0 Input                       | Vil             | _                    | _              | 1/3Vcc          | VDC   |

<sup>\*</sup>Recommended operating voltages. All maximums are absolute maximum.

# with Drive Electronics

- + 5V CMOS level video interface (with 4.7k pull-up resistors).

- · On board DC converter.

- · Slim Profile.

**FEATURES**

- · Large, bright characters and graphics.

- · Highly visible for long distance viewing.

### **ELECTRICAL SPECIFICATIONS**

Voltages Required: VDC: + 12 to + 24VDC.

V<sub>cc</sub>: + 5VDC.

**Power Required:** Typical = 20 watts, Maximum = 65 watts.

### **OPTICAL SPECIFICATIONS**

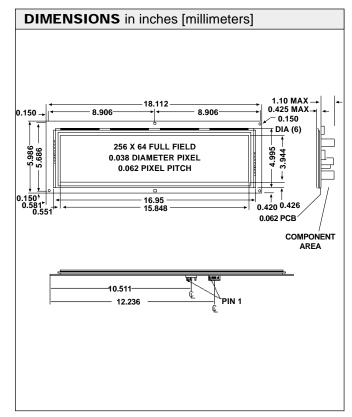

Viewing Area: 15.85" W x 5.00" H.

Pixel Pitch: 0.062".

Pixel Size: 0.038" diameter.

Color: Neon orange.

Text with typical 5x7 character matrix using 1 column

between characters and 1 row between lines. Maximum Number of Characters per Line: 42.

Maximum Number of Lines: 16. Luminance: 40 foot lamberts minimum.

## **ENVIRONMENTAL SPECIFICATIONS**

**Operating Temperature:** 0°C to + 70°C. **Storage Temperature:** - 20°C to + 85°C.

Relative Operating Humidity: To 95% non-condensing.

Mechanical Shock: 30G.

Vibration: 3G.

Operating Altitude: 10,000 feet.

# **GENERAL DESCRIPTION**

The APD-256G064A DC Plasma display offers viewing qualities designers seek such as high contrast, viewing angle of 150° minimum, and long distance readability. It is bright (40 foot lamberts minimum) with characters and graphics figures presented in a pleasing neon orange color against a black background. Plasma is much more readable and eye-pleasing than liquid crystal or vacuum fluorescent displays and is filterable to red, amber, or neutral density.

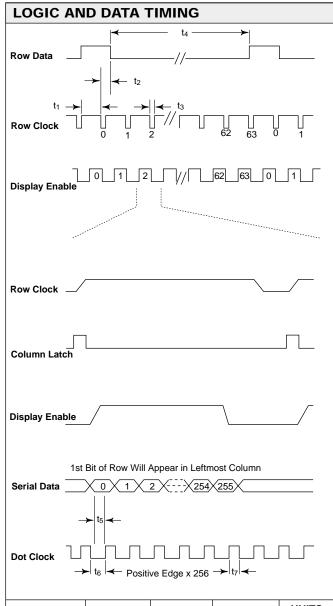

These plasma display panels are driven in a standard row-column refresh method much like a CRT display. The designer need only supply + 5V CMOS level signals for SERIAL DATA, DOT CLOCK, COLUMN LATCH, ROW DATA, ROW CLOCK and DISPLAY ENABLE. The SERIAL DATA is entered with the DOT CLOCK up to frequencies as high as 8mHz. After a row of 256 pixels is clocked in, the COLUMN LATCH signal is toggled and the data is latched. At the time the data is latched, the display is briefly disabled using the DISPLAY ENABLE signal, then the row pointer is advanced with the ROW CLOCK signal. Once each frame the ROW DATA must be asserted to synchronize the column serial data with the beginning row. The recommended scanning

frequency is approximately 70 Hz but may be as high as 200 Hz. The high clock rate on the data clock allows for rapid refresh and maximum access time to the refresh ram.

www.vishay.com Document Number: 37073 8 Revision 03-Aug-01

# PIN DESCRIPTION

# **P3, POWER CONNECTOR**

AMP #640445-5 or equivalent.

(Mates with AMP 640428-5, MOLEX 09-05-3051 or equivalent.)

| PIN | SIGNAL          | DESCRIPTION           |

|-----|-----------------|-----------------------|

| 1   | GND             | GROUND                |

| 2   | VDC             | DC Converter Supply   |

| 3   | V <sub>cc</sub> | Logic Supply          |

| 4   | KEY             | Used to key connector |

| 5   | GND             | GROUND                |

#### P2, DATA CONNECTOR

AMP #103309-2 or equivalent.

(Mates with AMP 746195-2, MOLEX 39-27-1146 or equivalent.)

| PIN | DESCRIPTION    | PIN | DESCRIPTION |

|-----|----------------|-----|-------------|

| 1   | DISPLAY ENABLE | 2   | GROUND      |

| 3   | ROW DATA       | 4   | GROUND      |

| 5   | ROW CLOCK      | 6   | GROUND      |

| 7   | COLUMN LATCH   | 8   | GROUND      |

| 9   | DOT CLOCK      | 10  | GROUND      |

| 11  | SERIAL DATA    | 12  | GROUND      |

| 13  | No connect     | 14  | GROUND      |

### **DESCRIPTION OF INPUT SIGNALS**

**DOT CLOCK** - This signal enters the SERIAL DATA on each low to high transition. A total of 256 DOT CLOCK transitions must be present for each line of column/anode data.

**SERIAL DATA** - This signal presents the pixel data in positive logic format. A logic one represents a lit pixel and a logic zero represents an extinguished pixel. Data is entered from right to left. The first pixel data entered will represent the leftmost pixel in the row.

COLUMN LATCH - This signal latches the pixel data into the driver outputs. When the COLUMN LATCH signal goes to logic one the data entered previously will fall through to the driver outputs. When the signal returns to a logic zero, the data is latched and the shift register is now ready to accept the next row of data. Must be held low while entering new SERIAL DATA.

**DISPLAY ENABLE -** This signal enables the output drivers. Using a duty cycle control, this signal may also be used for intensity control. The DISPLAY ENABLE <u>must be at logic zero</u> before the COLUMN LATCH signal transitions. To avoid display blurring, the ROW CLOCK signal should also transition while DISPLAY ENABLE is a logic zero. It is recommended that this signal remain low for  $10\mu S$  min.

**ROW DATA -** This signal is the first line marker for the scan. This input should be held high to correspond to the first row of pixel data.

**RÓW CLOCK** - This signal clocks ROW DATA on the falling edge. The ROW CLOCK signal is repetitive and must be present for proper scanning of the display module. The APD-256G064A has a unique input protection circuit that assures the column drivers stay blanked on power up. The protection circuit unblanks the column drivers when the ROW CLOCK signal begins (i.e. the display begins scanning).

| PARAMETER      | MINIMUM | TYPICAL | MAXIMUM | UNITS |

|----------------|---------|---------|---------|-------|

| t <sub>1</sub> | 100     | _       | _       | nS    |

| t <sub>2</sub> | 5       | _       | _       | uS    |

| t <sub>3</sub> | 1       | _       | _       | uS    |

| t <sub>4</sub> | _       | 70      | 200     | Hz    |

| t <sub>5</sub> | 25      | _       | _       | nS    |

| t <sub>6</sub> | 75      | _       | _       | nS    |

| t <sub>7</sub> | 75      | _       | _       | nS    |

| ORDERING INFORMATION                                                          |              |

|-------------------------------------------------------------------------------|--------------|

| Plasma Display Module with Drivers, CMOS Video Interface, and DC/DC Converter | APD-256G064A |

| Data Connector Kit                                                            | 280105-05    |

| Power Connector Kit                                                           | 280108-13    |

| Video Controller (+5V) Parallel and Serial Interface                          | PDS-500      |

| Video Controller (+12V) Parallel and Serial Interface                         | PDS-500-1    |