Preliminary

# **Programmable Peripheral PSD813FN/FH** Field-Programmable Microcontroller Peripherals with Flash Memory and Embedded Micro⇔Cells<sup>™</sup>

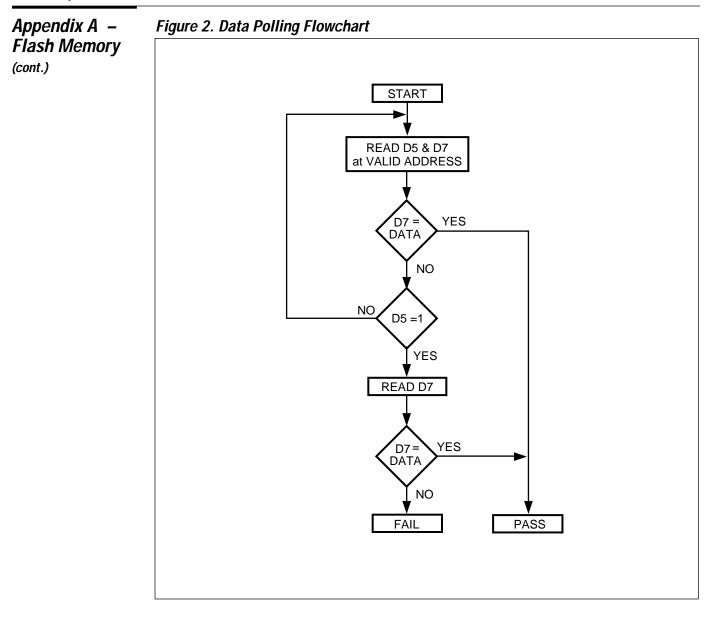

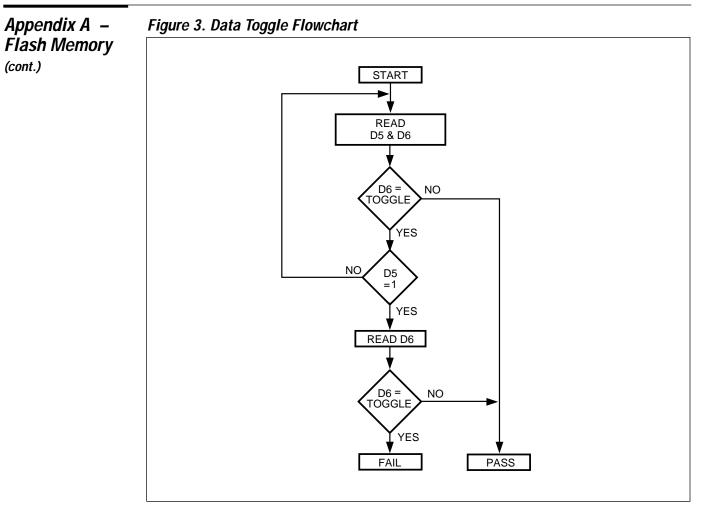

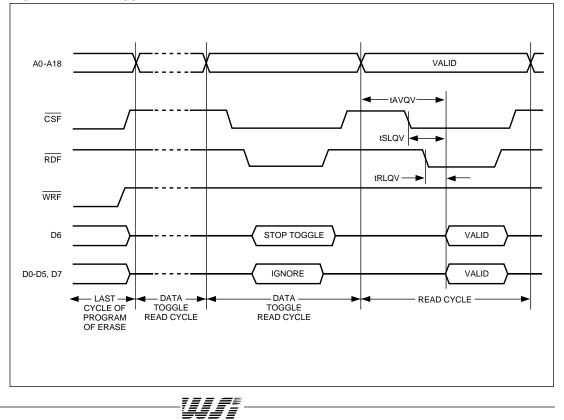

Introduction The PSD813FH and PSD813FN devices are field-programmable microcontroller (MCU) peripherals with Flash memory. These multi-chip modules (MCM) are the first two members of a complete family of in-system-programmable (ISP) peripherals from WSI that enhance any embedded microcontroller design. These devices will interface easily with most popular MCUs and enable a simple two-chip solution that addresses virtually all of the MCUs external needs. Major features provided by the PSD813FH/FN are large Flash memory, concurrent OTP boot memory, battery backed SRAM, programmable I/O, programmable logic, address space expansion, power management, code security, and small package size. A two-chip solution consisting of an MCU and a PSD813FN/FH reduces design and manufacturing cost, reduces board space, lowers power consumption, and shortens time-to-market while increasing design flexibility. In addition, in-system features such as concurrent Flash read and write capability, dynamically reconfigurable I/O ports, and low power management increases system performance and manufacturing flexibility. New innovative "microcontroller-macrocells", called Micro⇔Cells<sup>™</sup>, bring inexpensive programmable logic to MCU-based embedded system designs. Because the Micro⇔Cells are directly connected to the MCU address/data bus, their programmable logic is tightly coupled to the MCU software with no hardware overhead. The MCU's ability to communicate directly with the Micro⇔Cells at the flip-flop level makes PSD813FN/FH devices ideal for popular functions such as counters, serial channels, and mailboxes. When compared to industry standard CPLD implementation, this architecture can save 25% to 50% of the CPLD product term and macrocell resources. The PSD813FN/FH devices are the first of WSI's Flash PSD8XXF product family. Starting with the PSD813FN/FH, a pin-for-pin upgrade path exists for future lower cost monolithic PSD8XXF devices that will incorporate expanded Flash-based programmable logic, Flash and EEPROM memory types, larger SRAM, and serial ISP using the industry standard JTAG protocol. **Key Features** MCM 5-volt only Flash Programmable Peripheral for Microcontroller-based Applications Solves Problems of In-System Flash Erase and Programming Concurrently Operating Main Memory and Boot Memory Resolves Microcontroller Decoding Issues During Flash Update Two separate non-volatile memory arrays. Both 1 Mbit (128 Kbytes) of Flash memory and 256 Kbits (32 Kbytes) of Separate OTP Boot EPROM memory are available. The Boot memory allows continuous operation of the MCU while the Flash memory is being written or erased. The Flash memory is divided into eight 16 Kbyte sectors that can be mapped to different address spaces. Access time is 150 ns which includes address latching and DPLD decoding. Embedded On-Chip Erase and Program Algorithms for the Flash Memory. Automatically accommodates on-chip events for writing and erasing the Flash memory. The Flash memory is byte-programmable and can be erased sector by sector or by entire chip. The embedded algorithms indicate completion of program or erase cycles

by using two popular methods: data polling or bit toggling. PSD813FN/FH algorithms are compatible with the standard JEDEC single-power-supply Flash command set.

#### **Low** $V_{CC}$ write inhibit <= 3.2 V for the Flash Memory.

#### Guaranteed Minimum 10,000 Erase/Write Cycles.

□ A simple, programmable interface to 8-bit microcontrollers using either multiplexed or non-multiplexed busses. The bus interface logic directly decodes microcontroller control signals. Supports all popular microcontrollers.

#### □ Three Flexible OTP PLD Sections

One PLD is used for internal PSD address decoding, one is used for external device address decoding, and one is used as a general-purpose design resource. The general-purpose PLD may be used to efficiently implement a variety of logic functions commonly associated with MCUs such as state machines, address decoders, address generators, serial channels, multiprocessor mailboxes, and shift registers.

The general-purpose PLD also supports 12-Output Micro⇔Cells and 23-Input Micro⇔Cells. The MCM PSD813FN/FH dedicates seven Output and eight Input Micro⇔Cells to Flash memory usage and SRAM standby voltage control. Although the seven Output Micro⇔Cells are dedicated, an internal product term allocator redistributes any unused product terms if needed by the remaining Micro⇔Cells.

- □ Internal 4Kbit SRAM. The SRAM retains data if power is lost by automatically switching to an external standby power source.

- Nineteen individually configurable I/O Port Pins. The Ports may be used as microcontroller I/Os, PLD I/Os, latched microcontroller address outputs or special function I/Os.

- □ The programmable Power Management Unit (PMU) supports two separate, low-power modes allowing operations with as little as 25µA (at 5V V<sub>CC</sub>). The device can automatically detect a lack of microcontroller activity and put the PSD into power down mode.

#### Page Logic

Page Logic is connected to the ZPLDs and enables address space expansion for microcontrollers with limited address space capability. Up to 16 pages are available.

#### Security Bit

The security bit prevents reading the PSD configuration, ZPLD, EPROM Boot array, and Flash memory contents. This inhibits copying the device on a programmer.

#### Development Tools

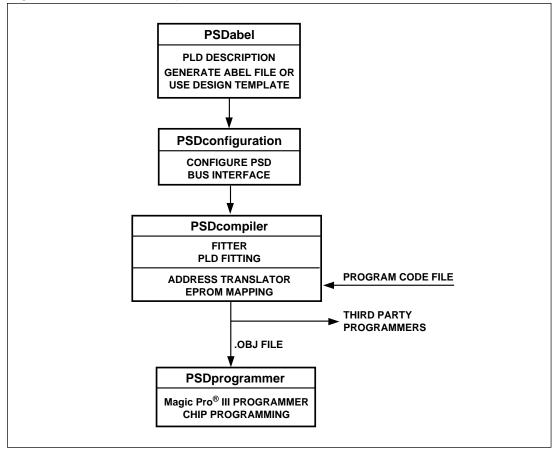

Supported by the PSDsoft<sup>™</sup> MS-Windows<sup>®</sup> compatible development tools. Includes PSDabel as the design entry method, an efficient Fitter, and an Address Translator (see Figure 2).

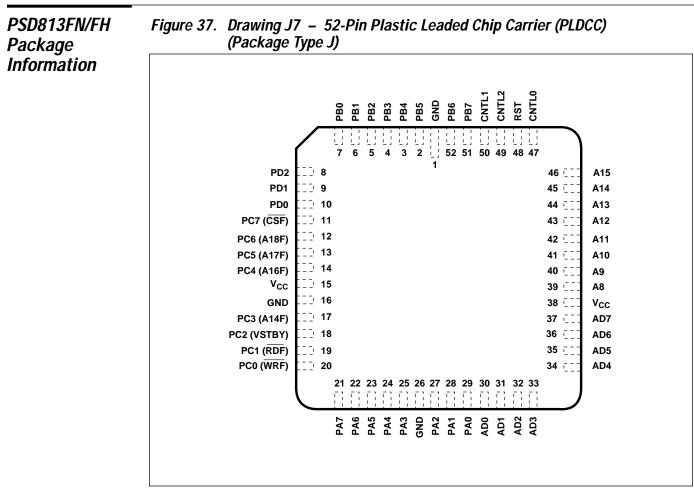

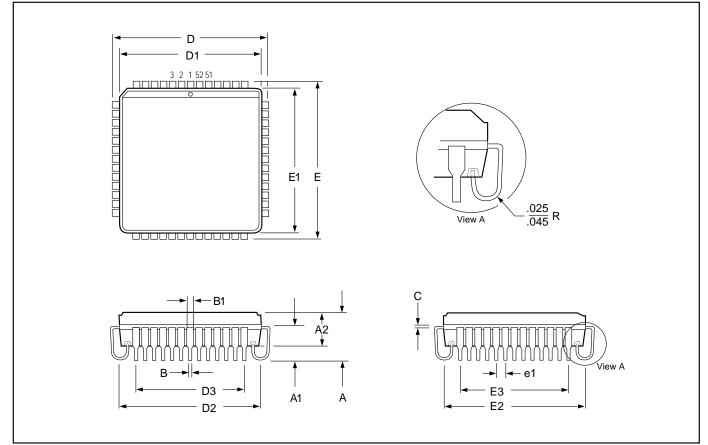

Packaging consists of a 52 pin plastic chip carrier.

Please refer to the revision block at the end of this document for updated information.

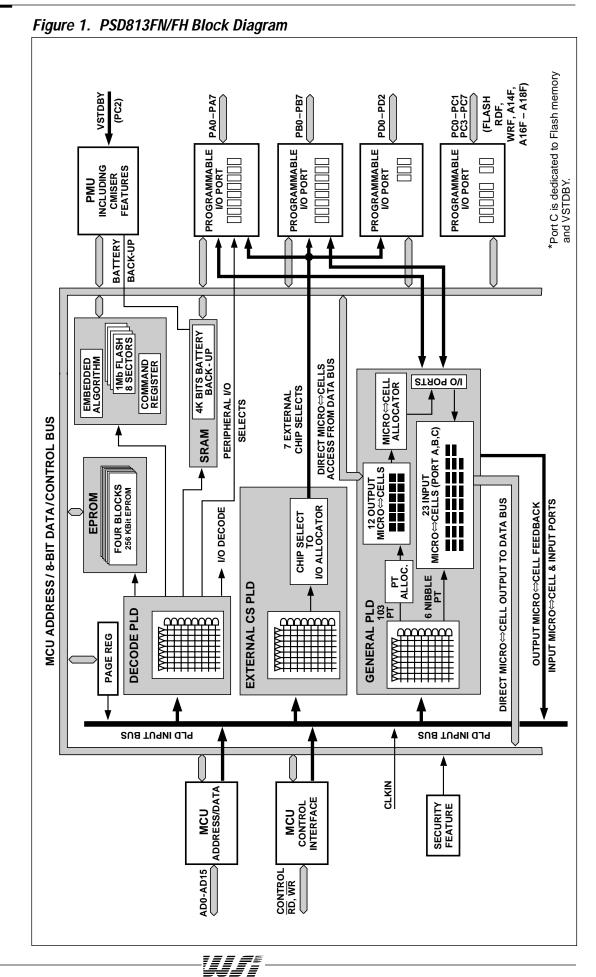

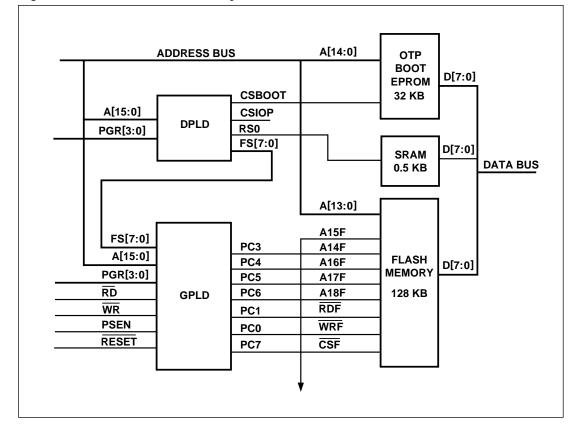

*PSD813FN/FH Architectural Overview*  PSD813FN/FH devices consist of several major functional blocks. Figure 1 shows the architecture of the PSD813FN/FH device. The functions of each block are described briefly in the following sections. Many of the blocks perform multiple functions, and are user configurable.

#### PLDs

The device contains three PLD blocks each optimized for a different function as shown in Table 1. The functional partitioning of the PLDs reduces power consumption, optimizes cost/performance and ease of design entry.

The Decode PLD (DPLD) is used to decode and generate chip selects for the PSD813FN/FH internal memory, registers, and peripheral I/O mode. The External Chip Select PLD (ECSPLD) is optimized to generate chip selects for devices external to the PSD813FN/FH. The General Purpose PLD (GPLD) can implement user defined logic functions. The DPLD and ECSPLD have combinatorial outputs while the GPLD has 12 Output Micro⇔Cells. Seven of the Port C Micro⇔Cells are dedicated to Flash memory control. The PSD813FN/FH also has 23 Input Micro⇔Cells that can be configured as inputs to the PLD. The PLDs receive their inputs from the PLD Input bus.

#### I/O Ports

The PSD813FN/FH has 19 I/O pins divided among three ports. Each I/O pin can be individually configured to provide many functions. Ports A, B and D can be configured as standard MCU I/O ports, PLD I/O, or latched address outputs for microcontrollers using multiplexed address/data busses.

#### Table 1.

| Name                     | Abbreviation | Inputs | Outputs | Product Terms |

|--------------------------|--------------|--------|---------|---------------|

| Decode PLD               | DPLD         | 63     | 12      | 13            |

| External Chip Select PLD | ECSPLD       | 24     | 7       | 7             |

| General PLD              | GPLD         | 63     | 12      | 109           |

# -415

#### PSD813FN/FH Architectural Overview

(cont.)

PSD813FN/FH Architectural Overview (cont.)

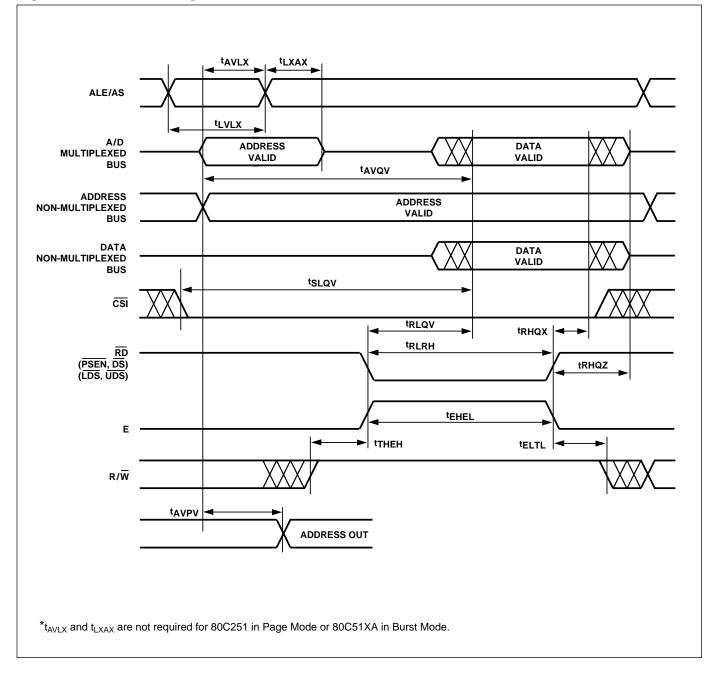

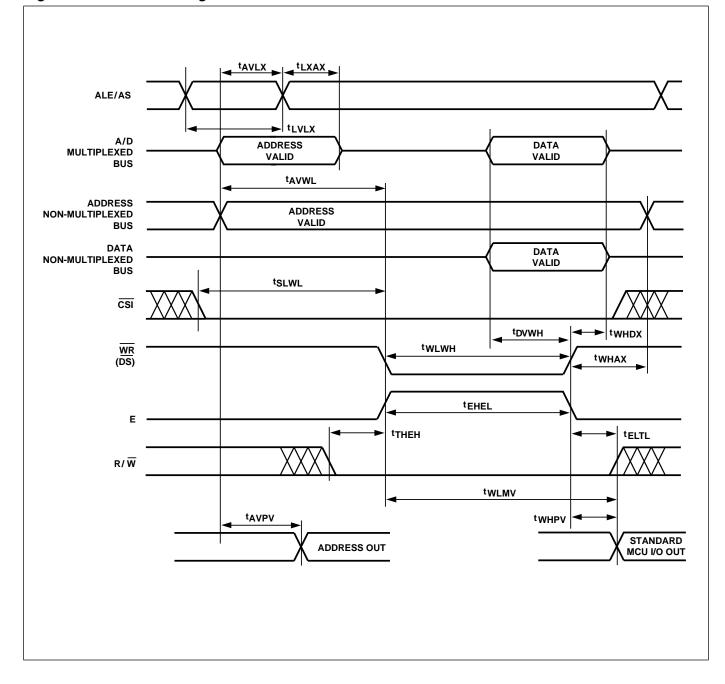

#### Microcontroller Bus Interface

The PSD813FN/FH easily interfaces with most popular eight and sixteen-bit microcontrollers with either multiplexed or non-multiplexed address/data busses. The PSD813FH is for multiplexed applications and the PSD813FN is for non-multiplexed applications. The PSD813FN/FH can operate with 16-bit MCUs if the MCU is configured for 8-bit external data path mode. The device is configured to respond to the microcontroller control signals which are also used as inputs to the PLDs

as inputs to the PLDs.

#### Memory

The PSD813FN/FH contains a 1 Mbit Flash memory, a 256 Kbit Boot EPROM and a 4 Kbit SRAM. The EPROM space and Flash memory space are divided into four and eight equally sized blocks, respectively. Each block can be located in a different address space defined by the user. The access time of either memory includes the address latching and DPLD decoding. The Flash memory is implemented using a 4 Mbit (29040) device configured as a 1 Mbit memory. All the commands for the 29040 are applicable for operating as a 1 Mbit Flash memory.

The 4 Kbit SRAM may be used as a scratch pad memory and an extension of the microcontroller SRAM. The SRAM data is retained in the event of a system power down, provided a backup battery is connected to the Vstby pin (PC2). Switching from the  $V_{CC}$  supply to standby power occurs automatically when  $V_{CC}$  drops below Vstby voltage.

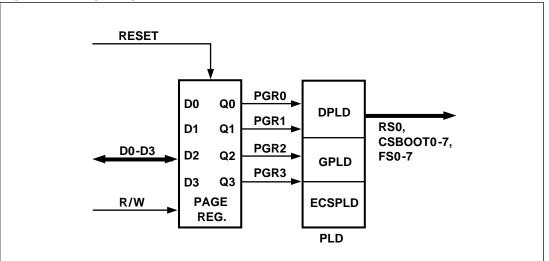

#### Page Register

The four-bit Page Register expands the address range of the microcontroller by sixteen times. The paged address can be used as part of the address space to access external memory and peripherals or internal EPROM, SRAM and I/O.

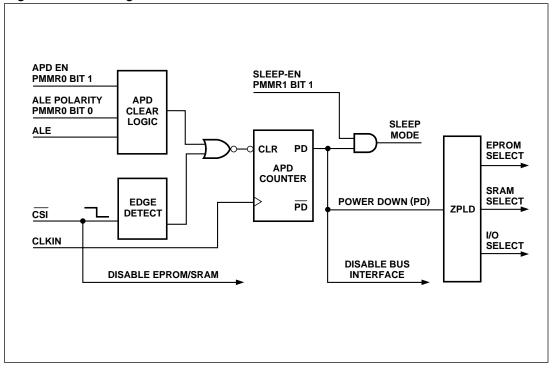

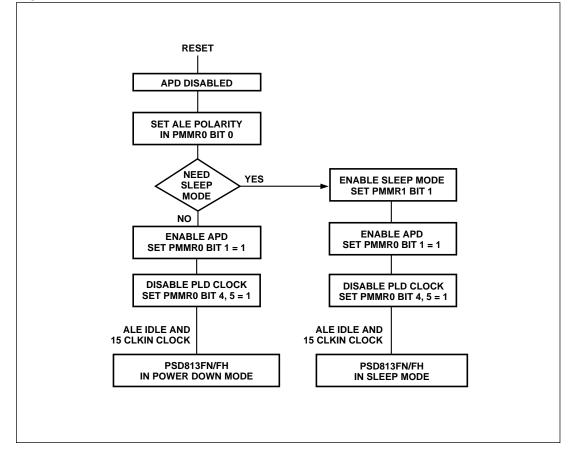

#### Power Management Unit

The Power Management Unit (PMU) in the PSD813FN/FH enables the user to control the power consumption on selected functional blocks based on system requirements. The PMU includes an Automatic Power Down unit (APD) that will turn off device functions due to microcontroller inactivity in one of two modes: the Power Down mode and Sleep mode.

Other power saving features, such as the CMiser in the PMU, allow the EPROM/SRAM to operate at a slower rate to conserve power.

# Development System

The PSD813FN/FH devices are supported by the Windows-based PSDsoft Development System. The PSDsoft design flow is shown in Figure 2. The PLD design entry is done using PSDabel, which creates a minimized logic implementation, and provides logic simulation of the PLDs. The PSD813FN/FH Bus Interface and I/O Port configuration are entered in PSDconfiguration.

The PSDcompiler, comprised of a fitter and address translator, generates an object file from the PSDabel, PSDconfiguration and MCU code files. The object file is then down loaded to a programmer (MagicPro III, Data I/O, or other third party programmer for device programming).

**PSD813FN/FH**The PSD813FN/FH are two unique devices. The part classifications are based on bus<br/>mode. The features of each part are listed in Table 2.

| <i>Table 2.<br/>PSD813FN/FH</i> |                      |                      | ZPLD<br>DPLD + GPLD + ECSPL |                           |                 |            | Flash        |               | Boot           |

|---------------------------------|----------------------|----------------------|-----------------------------|---------------------------|-----------------|------------|--------------|---------------|----------------|

| Product<br>Matrix               | Part Bus             |                      | Inputs                      | Registered<br>Micro⇔cells | I/O<br>Pins PMU |            |              | SRAM<br>K Bit | EPROM<br>K Bit |

|                                 | PSD813FH<br>PSD813FN | x8/MUX<br>x8/Non-MUX | 63<br>63                    | 12<br>12                  | 19<br>19        | Yes<br>Yes | 1024<br>1024 | 4<br>4        | 256<br>256     |

**NOTE:** PMU = Power Management Unit.

# *Table 3. PSD813FN/FH Pin Descriptions*

The following table describes the pin names and pin functions of the PSD813FN/FH. Pins that have multiple names and/or functions are defined by configuration.

| Pin Name                 | Pin                  | Туре | Function Description                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------|----------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADIO0-7                  | 30–37                | I/O  | <ul> <li>Address/Data Port, interface to Microcontroller Bus</li> <li>1. Input pins for multiplexed low order address/data byte.</li> <li>ALE or AS latches address A0-7 for input to PLDs.</li> <li>The PSD drives data out only if read is active and one of the internal PSD functional blocks is selected.</li> </ul>                                                                                                                 |

| A8–15                    | 39–46                | I/O  | Address Port, interface to Microcontroller Bus<br>1. Address A8-15 inputs.                                                                                                                                                                                                                                                                                                                                                                |

| CNTL0<br>(WR,<br>R_W)    | 47                   | Ι    | <ul> <li>Write Input pin with multiple configurations. Depending on the MCU interface selected, this pin can be:</li> <li>1. WR – active low write input</li> <li>2. R_W – read/write pin, low for write bus cycle</li> <li>3. Control signal (CNTL0) input to PLD</li> </ul>                                                                                                                                                             |

| CNTL1<br>(RD,<br>E, DS)  | 50                   | Ι    | <ul> <li>Read or Data Strobe Input pin with multiple configurations.</li> <li>Depending on the MCU interface selected, this pin can be:</li> <li>1. RD – active low read input</li> <li>2. E – E clock input.</li> <li>During a write bus cycle, E is high and R/W is low</li> <li>During a read bus cycle, E is high and R/W is high</li> <li>3. DS – Data Strobe, active low</li> <li>4. Control signal (CNTL1) input to PLD</li> </ul> |

| CNTL2<br>(PSEN)          | 49                   | I    | <ul> <li>Read or other Control input pin with multiple configurations.</li> <li>Depending on the MCU interface selected, this pin can be:</li> <li>1. PSEN – Program Select enable, active low in code fetch bus cycle</li> <li>2. Control signal (CNTL2) input or general input to PLD</li> </ul>                                                                                                                                        |

| Reset                    | 48                   | I    | Active low input. Resets I/O Ports, PLD Micro⇔Cells and some of the Configuration Registers. Must be active at power up.                                                                                                                                                                                                                                                                                                                  |

| PA0<br>PA1<br>PA2<br>PA3 | 29<br>28<br>27<br>25 | I/O  | <ul> <li>Port A, PA0 – 3. This port is pin configurable and has multiple functions:</li> <li>1. MCU I/O – standard output or input port</li> <li>2. External chip select (ECSPLD) output, or input to GPLD</li> <li>3. Latched address outputs (see Table 4)</li> <li>4. As Data Bus Port (D0–3) in non-multiplexed bus configuration</li> <li>5. Peripheral I/O mode</li> </ul>                                                          |

| <i>Table 3.<br/>PSD813FN/FH</i> | Pin Name                                                                                    | Pin                                    | Туре                               | Function Description                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>Descriptions<br>(cont.)  | PA4<br>PA5<br>PA6<br>PA7                                                                    | 24<br>23<br>22<br>21                   | I/O<br>CMOS<br>or<br>Open<br>Drain | <ul> <li>Port A, PA4–7. This port is pin configurable and has multiple functions:</li> <li>1. MCU I/O – standard output or input port</li> <li>2. GPLD Micro⇔Cell (McellAB) output or input</li> <li>3. Latched address outputs (see Table 4)</li> <li>4. As Data Bus Port (D4–7) in non-multiplexed bus configuration</li> <li>5. Peripheral I/O mode</li> </ul> |

|                                 | PB0<br>PB1<br>PB2<br>PB3                                                                    | 7<br>6<br>5<br>4                       | I/O                                | Port B, PB0–3. This port is pin configurable and has<br>multiple functions:<br>1. MCU I/O – standard output or input port<br>2. External chip select (ECSPLD) output, or input to GPLD<br>3. Latched address outputs (see Table 4)                                                                                                                                |

|                                 | PB4<br>PB5<br>PB6<br>PB7                                                                    | 3<br>2<br>52<br>51                     | I/O<br>CMOS<br>or<br>Open<br>Drain | Port B, PB4–7. This port is pin configurable and has multiple functions:<br>1. MCU I/O – standard output or input port<br>2. GPLD Micro⇔Cell (McellAB) output or input<br>3. Latched address outputs (see Table 4)                                                                                                                                                |

|                                 | PC0 (WRF)<br>PC1 (RDF)<br>PC3 (A14F)<br>PC4 (A16F)<br>PC5 (A17F)<br>PC6 (A18F)<br>PC7 (CFS) | 20<br>19<br>17<br>14<br>13<br>12<br>11 | *                                  | Flash Write<br>Flash Read<br>Flash Address A14<br>Flash Address A16<br>Flash Address A17<br>Flash Address A18<br>Flash Select                                                                                                                                                                                                                                     |

|                                 | PC2<br>(Vstby)                                                                              | 18                                     | I                                  | Port C pin PC2.<br>Dedicated SRAM Standby Voltage Input. Pin should be<br>grounded if Vstby is not required.                                                                                                                                                                                                                                                      |

|                                 | PD0<br>(ALE)                                                                                | 10                                     | I/O                                | Port D Pin PD0 can be configured as:<br>1. ALE input - latches addresses on ADIO0–15 pins<br>2. MCU I/O<br>3. GPLD input<br>4. ECSPLD output                                                                                                                                                                                                                      |

|                                 | PD1<br>(CLKIN)                                                                              | 9                                      | I/O                                | <ul> <li>Port D Pin PD1 can be configured as:</li> <li>1. MCU I/O</li> <li>2. GPLD input</li> <li>3. External chip select (ECSPLD) output</li> <li>4. CLKIN clock input – clock input to the GPLD Micro⇔Cells, the APD power down counter and GPLD AND Array</li> </ul>                                                                                           |

$^{\star}\mbox{These}$  pins are reserved for internal Flash memory control and should not be used as outputs.

| Table 3.<br>PSD813FN/FH        | Pin Name        | Pin           | Туре | Function Description                                                                                                                                                                                                                                                    |

|--------------------------------|-----------------|---------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>Descriptions<br>(cont.) | PD2<br>(CSI)    | 8             | I/O  | <ul> <li>Port D Pin PD2 can be configured as:</li> <li>1. MCU I/O</li> <li>2. GPLD input</li> <li>3. External (ECSPLD) output</li> <li>4. CSI input – When low, the CSI enables the PSD EPROM/SRAM. When high, the EPROM/SRAM are disabled to conserve power</li> </ul> |

|                                | V <sub>CC</sub> | 15<br>38      |      | Power pins                                                                                                                                                                                                                                                              |

|                                | GND             | 1<br>16<br>26 |      | Ground pins                                                                                                                                                                                                                                                             |

# Table 4. I/O Port Latched Address Output Assignments\*

| Microcontroller                 | Port A (3:0)  | Port A (7:4)  | Port B (3:0)  | Port B (7:4)  |

|---------------------------------|---------------|---------------|---------------|---------------|

| 8-Bit<br>Multiplexed Bus        | Address [3:0] | Address [7:4] | Address [3:0] | Address [7:4] |

| 8-bit<br>Non-Multiplexed<br>Bus | N/A           | N/A           | Address [3:0] | Address [7:4] |

N/A = Not Applicable

\*Refer to the I/O Port Section on how to enable the Latched Address Output function.

# *PSD813FN/FH Register Description and Address Offset*

Table 5 shows the offset address to the PSD813FN/FH registers relative to the CSIOP base address. The CSIOP space is the 256 bytes of address that is allocated by the user to the internal PSD813FN/FH registers.

Preliminary

| Table 5. Register Address Of | ffset |

|------------------------------|-------|

|------------------------------|-------|

| Register Name        | Port A | Port B | Port C | Port D | Other * | Description                                                                                          |

|----------------------|--------|--------|--------|--------|---------|------------------------------------------------------------------------------------------------------|

| Data In              | 00     | 01     | 10     | 11     |         | Reads Port pin as input,<br>MCU I/O input mode                                                       |

| Control              | 02     | 03     |        |        |         | Selects mode between<br>MCU I/O or Address Out                                                       |

| Data Out             | 04     | 05     | 12     | 13     |         | Stores data for output<br>to Port pins, MCU I/O<br>output mode                                       |

| Direction            | 06     | 07     | 14     | 15     |         | Configures Port pin as<br>input or output                                                            |

| Drive                | 08     | 09     | 16     | 17     |         | Configures Port pin<br>between CMOS,<br>Open Drain and<br>Slew rate                                  |

| Input Micro⇔Cell     | 0A     | 0B     | 18     |        |         | Reads Input Micro⇔Cell                                                                               |

| Enable Out           | 0C     | 0D     | 1A     |        |         | Reads the status of the output enable to the I/O Port driver                                         |

| Output<br>Micro⇔Cell | 20     | 20     | 21     |        |         | Read – reads output of<br>Micro⇔Cells<br>(McellC, McellAB)<br>Write – loads Micro⇔cell<br>Flip-Flops |

| PMMR0                |        |        |        |        | B0      | Power Management<br>Register 0                                                                       |

| PMMR1                |        |        |        |        | B2      | Power Management<br>Register 1                                                                       |

| Page                 |        |        |        |        | E0      | Page Register                                                                                        |

| VM                   |        |        |        |        | E2      | 8031/PIO Configuration<br>Register                                                                   |

\*Other registers that are not part of the I/O ports.

The<br/>PSD813FN/FH<br/>Functional<br/>BlocksThe PSD813FN/FH consists of five major functional blocks:□PLD Block□Bus Interface□I/0 Ports□Memory Block□Power Management Unit

The functions of each block are described in the following sections. Many of the blocks perform multiple functions, and are user configurable.

**PLDs**

The PLDs bring programmable logic functionality to the PSD813FN/FH. After specifying the logic for the PLDs by using the PSDabel tool in the PSDsoft suite, the logic configuration is programmed into the device and available when power is applied.

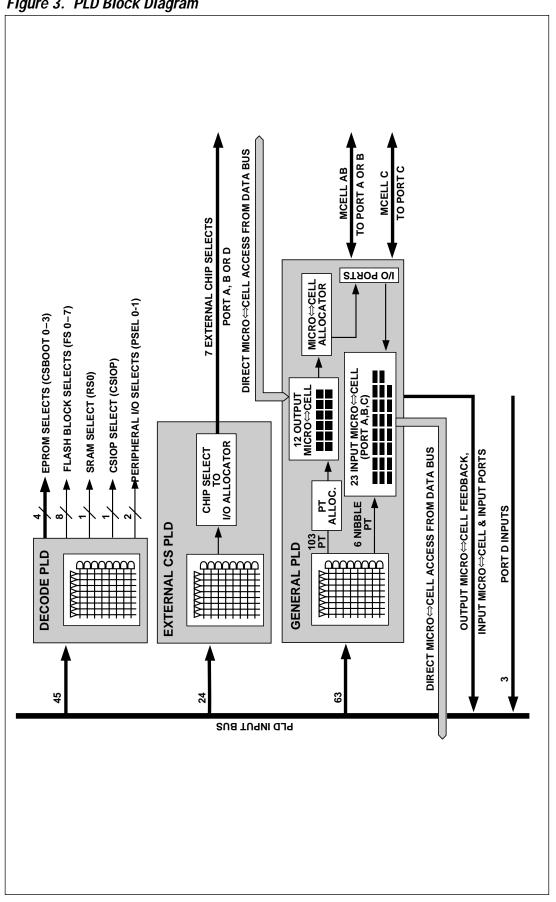

The PLDs (DPLD, ECSPLD and GPLD) consist of an AND array. The GPLD architecture includes 12 Output Micro⇔Cells in addition to the AND array. There are 23 Input Micro⇔Cells that can be configured as inputs to the PLD. Figure 3 shows the organization of the PLDs.

The AND array is used to form product terms specified using the PSDabel tool in the PSDsoft development system. When the inputs used in a term are true, the output is active. The GPLD Input Bus consists of 63 signals as shown in Table 6. Both the true and complement value of inputs are available to the AND array. The DPLD and ECSPLD Input Busses consists of fewer inputs and is a subset of the 63 inputs.

| Input Source                         | Input Name                           | Number of Signals |

|--------------------------------------|--------------------------------------|-------------------|

| MCU Address Bus                      | A [15:0]                             | 16                |

| MCU Control Signals                  | CNTL[2:0]                            | 3                 |

| Reset                                | RST                                  | 1                 |

| Power Down                           | PDN                                  | 1                 |

| I/O Ports Inputs (Input Micro⇔Cells) | PA[7:0], PB[7:0]<br>PC[7:3], PC[1:0] | 23                |

| Port D Inputs                        | PD[2:0]                              | 3                 |

| Page Register                        | PGR [3:0]                            | 4                 |

| Port A or B Micro⇔Cell Feedback      | MCELLAB.FB[7:4]                      | 4                 |

| Port C Micro⇔Cell Feedback           | MCELLC.FB[7:0]                       | 8                 |

Table 6. GPLD Inputs

(cont.)

Each of the three PLDs has unique characteristics suited for its applications. They are described in the following sections.

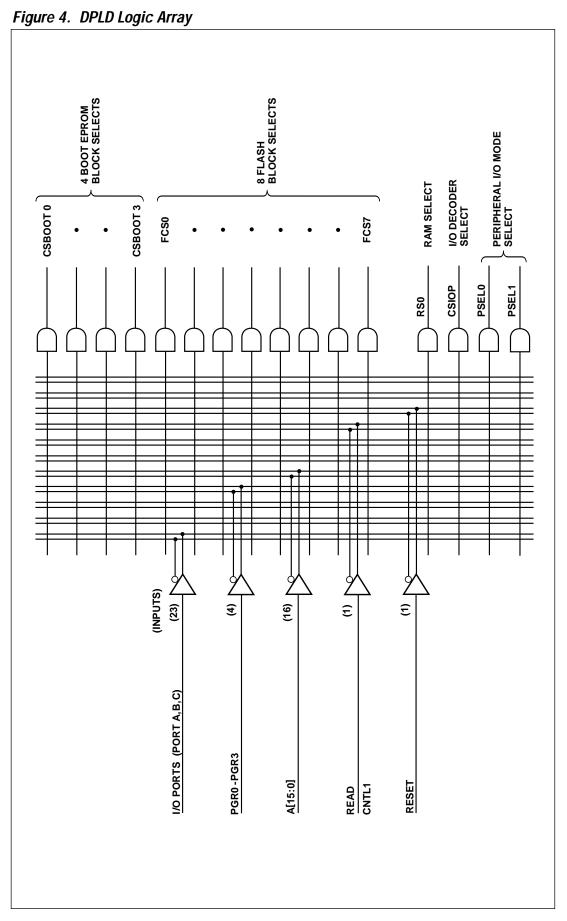

#### Decode PLD

The Decode PLD (DPLD), shown in Figure 4, is used to select the internal PSD813FN/FH functions: Flash blocks, EPROM blocks, SRAM, Registers (CSIOP) and the Port A Peripheral Mode. All the select signals are active high and have one product term.

The CSIOP is the select line for the PSD813FN/FH internal registers that occupies 256 bytes of memory space. A second level decoder selects a register based on the address inputs A[7-0]. Each Flash memory sector has its own chip select.

The 128 Kbyte Flash memory is partitioned into eight 16 Kbyte blocks, each with its own decoded select line (FS0-FS7). The 32 Kbyte OTP boot memory is partitioned into four 8 Kbyte blocks, each with its own decoded select line (CSBOOT0-CSBOOT7).

PSEL 0 & 1 are used as inputs to Port A to control the port's Peripheral I/O mode operation. Usually PSEL 0&1 are defined in term of the MCU address inputs. This mode is explained in the I/O Port section.

| Input Source              | Input Name                           | Number of Bits |

|---------------------------|--------------------------------------|----------------|

| MCU Address Bus           | A[15:0]                              | 16             |

| I/O Ports<br>Port A, B, C | PA[7:0], PB[7:0]<br>PC[7:3], PC[1:0] | 23             |

| Page Register             | PGR[3:0]                             | 4              |

| Control Signal            | CNTL1 (Read)                         | 1              |

| Reset Pin                 | RST                                  | 1              |

Table 7. DPLD Inputs

(cont.)

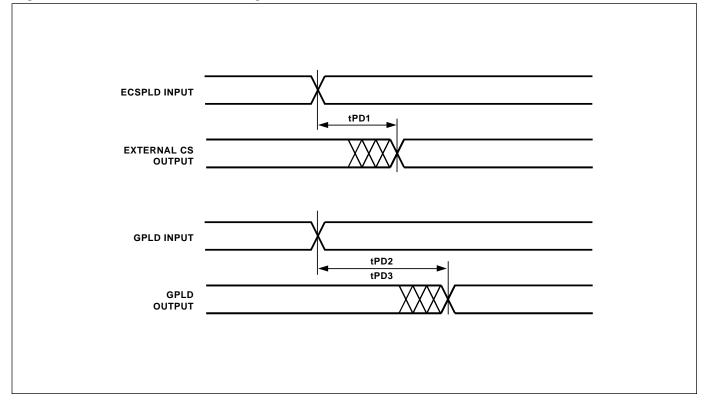

#### External Chip Select PLD

The External Chip Select PLD (ECSPLD) provides the means to select external devices. The output buffer of the ECSPLD can be configured to operate in high slew rate by writing a "1" to the corresponding bit in the Drive Register. The slew rate is a measurement of the rise and fall times of the output. A higher slew rate means a faster output response while a lower slew rate is a slower response. Refer to Table 25 in the I/O Section for setting up the Drive Register.

Faster transitions are more likely to cause line reflections and system noise than slower rates. Adjusting the slew rate allows a trade-off between greater speed and noise sensitivity. The selection should be based on the performance requirements of the system and its noise characteristics. Set the corresponding bits in the Drive Register to "0" (for normal speed) or "1" (for fast drive). The default value is zero.

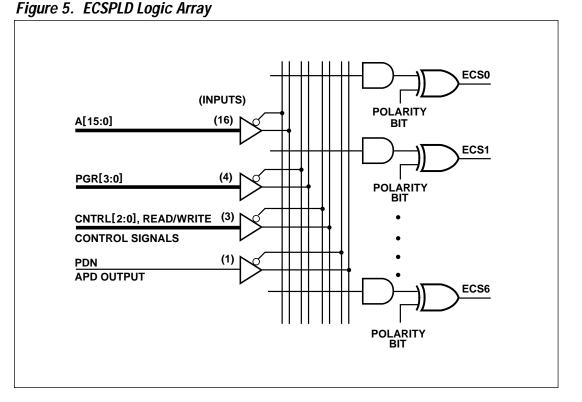

The ECSPLD has 24 inputs as shown in Table 8. Its outputs are combinatorial, of either polarity, and have one product term each as shown in Figure 5.

| Input Source        | Input Name | Number of Bits |

|---------------------|------------|----------------|

| MCU Address Bus     | A[15:0]    | 16             |

| MCU Control Signals | CNTL[2:0]  | 3              |

| Power Down Signal   | PDN*       | 1              |

| Page Register       | PGR[3:0]   | 4              |

#### Table 8. ECSPLD Inputs

\*APD output. When PDN is high, the PSD813FN/FH is in power down mode

The seven ECSPLD outputs may be driven off the device through Ports A, B, or D, as shown in Table 9, via the Micro⇔Cell Allocator. Port selection is specified in the PSDabel file or assigned by the PSDcompiler.

| ECSPLD Output | Port A, B, or D Assignments |

|---------------|-----------------------------|

| ECS0          | PA0, PB0                    |

| ECS1          | PA1, PB1                    |

| ECS2          | PA2, PB2                    |

| ECS3          | PA3, PB3                    |

| ECS4          | PD0*                        |

| ECS5          | PD1*                        |

| ECS6          | PD2*                        |

Table 9. ECSPLD Output Port Assignments

\*Port D has no output enable (.oe) product terms for ECS4-6 outputs.

ust

PSD813FN/FH

(cont.)

#### General PLD

The General PLD (GPLD) is used to implement system logic such as MCU loadable counters, system mailboxes or handshaking protocols. In addition, the GPLD can implement random logic and state machine functions.

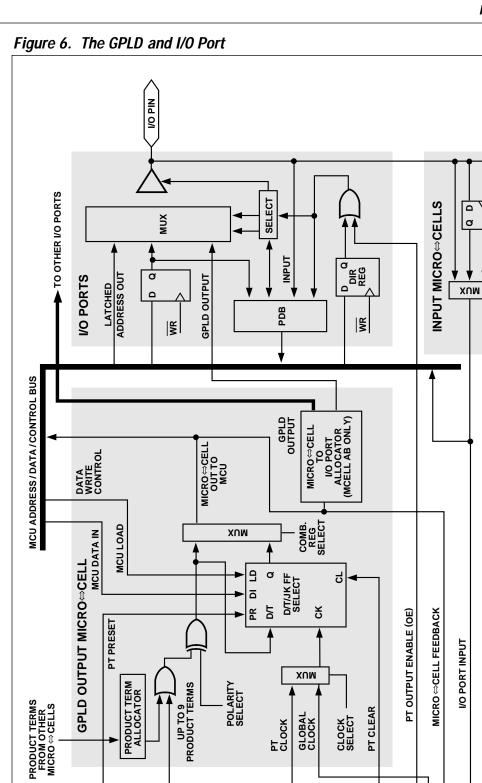

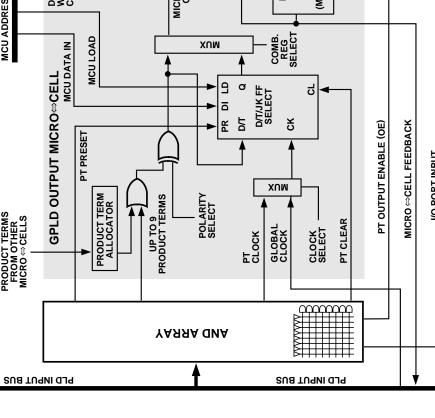

The GPLD has Output and Input Micro⇔Cells (see Figure 6). The Micro⇔Cells are configured using the PSDsoft development system. Like the other PLDs, the GPLD has an AND array which can generate up to 109 product terms, a maximum of nine product terms for each of the twelve Micro⇔Cells.

The Input and Output Micro⇔Cells are connected to the PSD813FN/FH internal data bus and can be directly accessed by the microcontroller. This enables the MCU software to load data into the Output Micro⇔Cells or read data from both the Input and Output Micro⇔Cells with no overhead visible to the user. This feature allows efficient implementation of system logic and eliminates the need to connect the data bus to the AND logic array as required in most standard PLD macrocell architectures.

Pins may also be driven as outputs by the MCU directly using MCU I/O Mode (see page 32). If the user drives pins with MCU I/O Mode, the underlying output Micro⇔Cell may be used for embedded nodes.

**PLDs** (cont.)

G

ø

х∩พ

ALE

PT INPUT LATCH GATE/CLOCK

(cont.)

#### Output Micro⇔Cell

Eight of the Output Micro⇔Cells are connected to Port C pins (except PC2) and are named as McellC0-7. The remaining four Micro⇔Cells can be connected to Port A or Port B and are named as McellAB4-7. If an McellAB output is not assigned to a specific pin in PSDabel, the Micro⇔Cell Allocator will assign it to either Port A or B. Table 10 shows the Micro⇔Cells and Port assignment. Seven of the 12 output Micro⇔Cells are dedicated to controlling the Flash memory in this multi-chip module.

| Output<br>Micro⇔Cell | Port<br>Assignment | Native<br>Product<br>Terms | Max<br>Borrowed<br>Product<br>Terms | Data Bit for<br>Loading or<br>Reading in<br>8-Bit Mode | PSD8XXF<br>Assignment |

|----------------------|--------------------|----------------------------|-------------------------------------|--------------------------------------------------------|-----------------------|

| McellC0              | Port C0            | 4                          | 5                                   | D0                                                     | WRF                   |

| McellC1              | Port C1            | 4                          | 5                                   | D1                                                     | RDF                   |

| McellC2              | *                  | 4                          | 5                                   | D2                                                     | **                    |

| McellC3              | Port C3            | 4                          | 5                                   | D3                                                     | A14F                  |

| McellC4              | Port C4            | 4                          | 5                                   | D4                                                     | A16F                  |

| McellC5              | Port C5            | 4                          | 5                                   | D5                                                     | A17F                  |

| McellC6              | Port C6            | 4                          | 5                                   | D6                                                     | A18F                  |

| McellC7              | Port C7            | 4                          | 5                                   | D7                                                     | CSF                   |

| McellAB4             | Port A4, B4        | 3                          | 6                                   | D4                                                     | **                    |

| McellAB5             | Port A5, B5        | 3                          | 6                                   | D5                                                     | **                    |

| McellAB6             | Port A6, B6        | 3                          | 6                                   | D6                                                     | **                    |

| McellAB7             | Port A7, B7        | 3                          | 6                                   | D7                                                     | **                    |

*Table 10. Output Micro⇔Cell Port and Data Bit Assignments*

\*Internal node only.

\*\*General purpose use.

# The Product Term Allocator

All Micro⇔Cells have the same cell architecture except McellC0-McellC7 have four native product terms and McellAB4-McellAB7 have three native product terms. The GPLD also has a Product Term Allocator with which the PSDcompiler can automatically borrow product terms from one Micro⇔Cell to another. The McellC may borrow up to five product terms from other Micro⇔Cells for a total of nine product terms. The McellAB has three native product terms and can borrow up to six product terms. Borrowing allows Micro⇔Cell outputs needing more product terms to use the unused product terms of others and is transparent to the user.

The architecture of the 12 Output Micro⇔Cells, as shown in Figure 6, consists of native product terms and borrowed product terms from other Micro⇔Cells. The polarity of the product term input is controlled by the XOR gate. The Micro⇔Cell can implement either sequential logic, using the Flip-Flop element, or combinatorial functions. The multiplexor selects the combinatorial or the sequential logic as the Micro⇔Cell output. The multiplexor output can drive a Port pin and has also a feedback path to the AND array inputs.

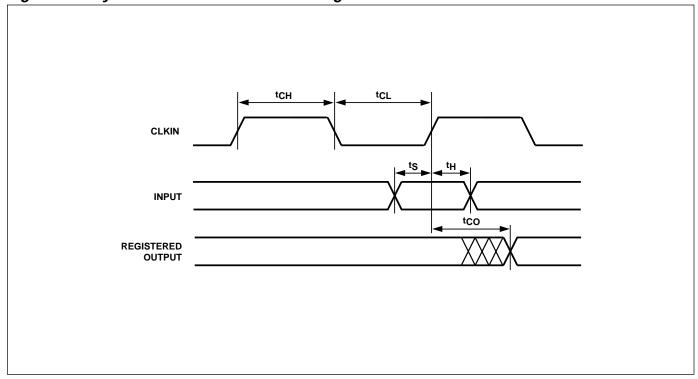

# Micro⇔Cell Flip-Flop Type

The Flip-Flop in the Micro⇔Cell can be configured as a D, Toggle, JK or SR type by using PSDabel in PSDsoft. The flip-flop Clock, Preset and Clear inputs are driven from a product term of the AND array. Alternatively, the device clock input (CLKIN) can be used for the flip-flop. The Preset and Clear are active high inputs; the Flip-Flop is clocked by the rising edge of the clock input.

#### Loading and Reading the Micro⇔Cells

PSD813FN/FH

The GPLD Micro $\Leftrightarrow$ Cells occupy a memory location in the MCU address space as defined by the CSIOP (refer to the I/O section). The Flip-Flops in each of the 12 Micro $\Leftrightarrow$ Cells can be loaded from the data bus by a microcontroller write bus cycle to the Micro $\Leftrightarrow$ Cell (see I/O Port section for Micro $\Leftrightarrow$ Cell Addresses). A "1" in the data bit that associates with the Micro $\Leftrightarrow$ Cell will load a "1" to the Flip-Flop, a "0" in the data bit will load a "0" to the Flip-Flop. The loading bus cycle takes priority over other Flip-Flop inputs that include the Preset, Clear and clock. See Table 11 for the data bits that are connected to the Micro $\Leftrightarrow$ Cells. The ability to load the flip-flops and read them back is useful in such applications as loadable counters, shift registers, mailboxes or handshaking protocols.

|    |     |                           |    | ·  |     |   |  |

|----|-----|---------------------------|----|----|-----|---|--|

| LD | Din | Clk                       | In | PR | CLR | Q |  |

| 1  | 1   | Х                         | Х  | Х  | Х   | 1 |  |

| 1  | 0   | Х                         | Х  | Х  | Х   | 0 |  |

| 0  | Х   | Normal Flip-Flop Function |    |    |     |   |  |

NOTE: LD is "1" when the MCU writes to the Micro⇔Cell address

### The Output Enable

The Micro⇔Cell can be connected to a PSD813FN/FH I/O pin as PLD output. The output enable of each of the Port pin output driver is controlled by a single product term (.oe) from the AND array ORed with the Direction Register output. Upon power up, if no output enable (.oe) equation is defined and the pin is declared as a PLD output in PSDsoft, the pin is enabled.

If the Micro⇔Cell output is declared as internal node and not as Port pin output in the PSDabel file, then the Port pin can be used for other I/O functions (such as MCU I/O mode). The internal node feedback can be routed as an input to the AND array.

#### Input Micro⇔Cell

The Input Micro⇔Cell as shown in Figure 6 is used to latch, register or pass incoming Port signals prior to driving them onto the PLD Input bus. The outputs of these Micro⇔Cells can also be read by the microcontroller through the internal Data Bus. The GPLD has 23 Input Micro⇔Cells, one for each pin of Ports A, B and C (except PC2). The Input Micro⇔Cells are individually configurable.

The enable/clock for the latch and flip-flop is driven by a multiplexor whose inputs are a product term from the GPLD AND array and the MCU address strobe (ALE). Each product term output is used to latch/clock four Input Micro⇔Cells. Port inputs [3:0] can be controlled by one product term and [7:4] can be controlled by another one.

The Input Micro $\Leftrightarrow$ Cell configurations are specified by equations written in PSDabel. Outputs of the Micro $\Leftrightarrow$ Cells can be read by the microcontroller via the "Input Micro $\Leftrightarrow$ Cell" buffer. See the I/O Port section on how to read the Micro $\Leftrightarrow$ Cells.

Input Micro $\Leftrightarrow$ Cells can use the ALE to latch the higher address bits (A31 – A16). The latched addresses are routed to the PLD as inputs.

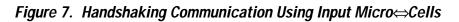

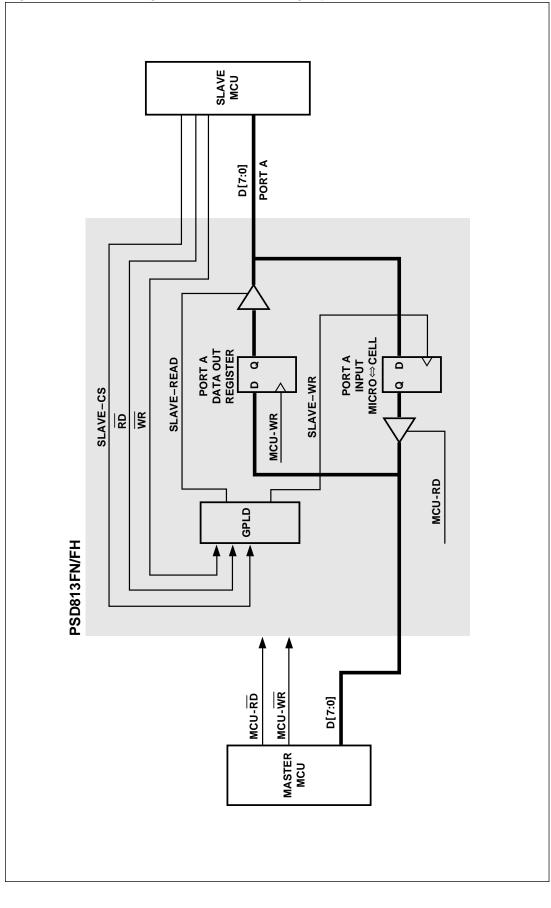

The Input Micro-Cell is particularly useful in handshaking communication applications where two processors wish to pass data between each other through a commonly accessible storage. Figure 7 shows a typical configuration where the Master MCU writes to the Port A Data Out Register that is read by the Slave MCU via the activation of the "Slave-Read" output enable product term. The Slave MCU can write to Port A Input Micro⇔Cells by activating the "Slave-Read" and "Slave-Wr" signals are product terms that are derived from the Slave MCU inputs of RD, WR, and Slave\_CS.

(cont.)

The "No-glue Logic" PSD813FN/FH Microcontroller Bus Interface can be directly connected to the most popular microcontrollers and their control signals. Some of these microcontrollers with their bus types and control signals are shown in Table 12. The interface type is specified using the PSDsoft tools.

| МСИ         | Data Bus | CNTLO | CNTL1 | CNTL2 | PD0** | ADIO0 |

|-------------|----------|-------|-------|-------|-------|-------|

| 8031        | 8        | WR    | RD    | PSEN  | ALE   | A0    |

| 68330       | 8        | R/W   | DS    | *     | ALE   | A0    |

| 80198       | 8        | WR    | RD    | *     | ALE   | A0    |

| 68HC11      | 8        | R/W   | E     | *     | AS    | A0    |

| 80C251***   | 8        | WR    | RD    | PSEN  | ALE   | A0    |

| Z8          | 8        | R/W   | DS    | *     | *     | A0    |

| Neuron 3150 | 8        | R/W   | DS    | *     | *     | A0    |

#### Table 12. Microcontroller Busses and Control Signals

\*Not used CNTL2 pin can be configured as GPLD input. Other not used pins (CNTL2, PD0) can be configured for other I/O functions.

\*\*ALE/AS input is optional for microcontrollers with a non-multiplexed bus.

\*\*\*8051 compatible mode only.

Table 12 shows the names of the PSD813FN/FH bus interface control pins and their functions. The control pins have multiple functions and can be configured to interface to many microcontrollers. Depending on the microcontroller, some of the control input pins are not required and may be used as GPLD input or other I/O functions. Specific examples of interfaces to different microcontrollers are provided in the following sections. For microcontrollers that have more than 16 address lines, Port A and B pins may be used as additional address inputs

(cont.)

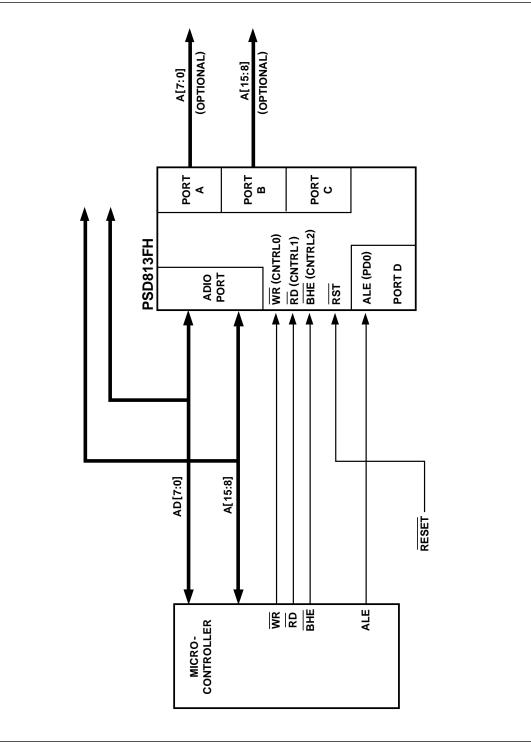

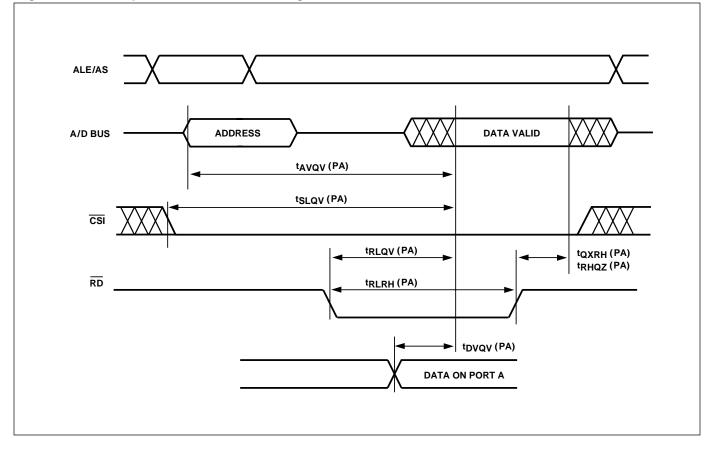

#### PSD813FH Interface To a Multiplexed Bus

Figure 8 shows an example of a system using a microcontroller with a multiplexed bus and a PSD813FH. The ADIO port on the PSD813FH is connected directly to the microcontroller address/data bus. The bus may be multiplexed only on one byte (eight-bit data) or on both bytes (sixteen-bit data). The ALE latches the address lines internally; latched addresses can be brought out to Port A or B. The PSD813FH drives the ADIO data bus only when one of its internal resources is accessed and the RD input is active.

us

(cont.)

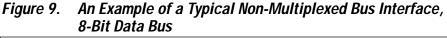

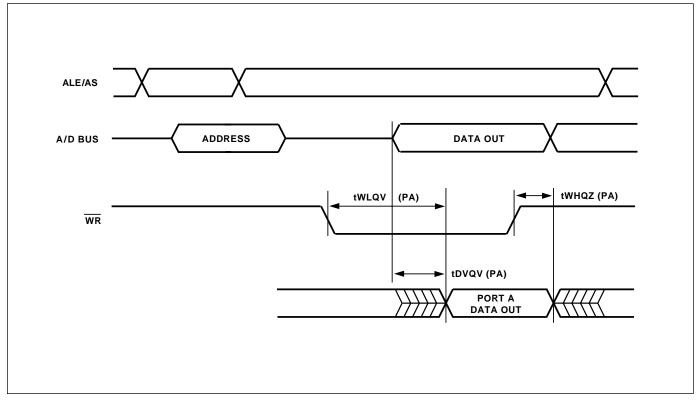

#### PSD813FN Interface To a Non-Multiplexed Bus

Figure 9 shows an example of a system using a microcontroller with a non-multiplexed bus and a PSD813FN. The address bus is connected to the ADIO Port, and the data bus is connected to Port A (D[7:0]). The data Ports are in tri-state mode when the PSD813FN is not accessed by the microcontroller. Should the system address bus exceed sixteen bits, Port B may be used as additional address inputs.

us

(cont.)

#### Microcontroller Interface Examples

Preliminary

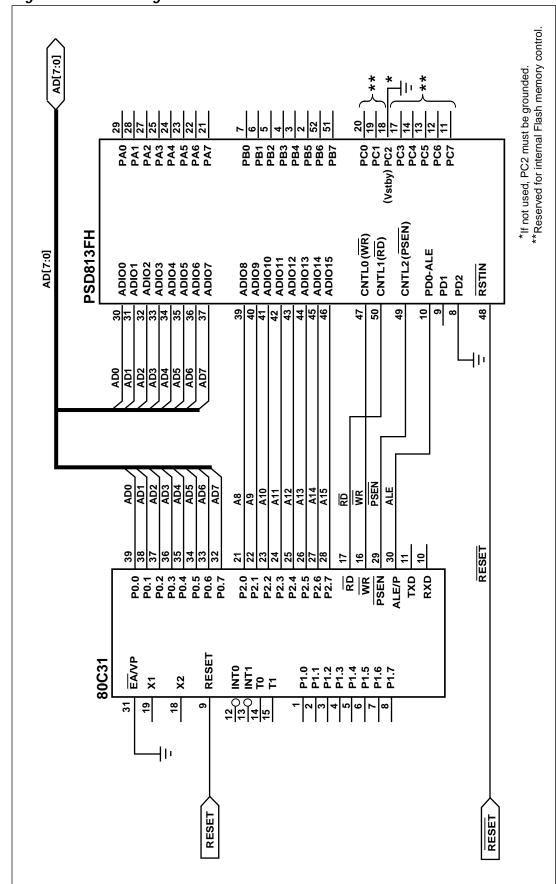

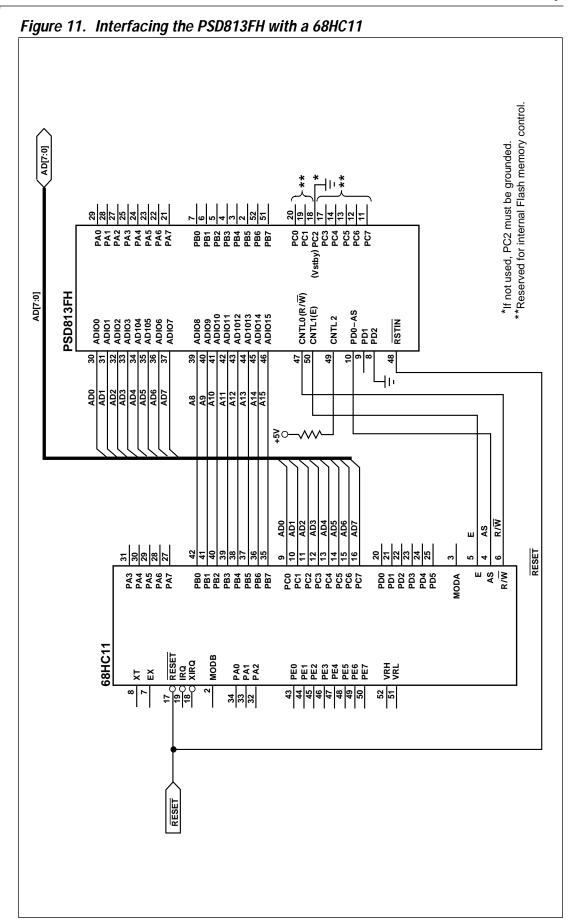

Figures 10 and 11 show examples of the basic connections between the PSD813FN/FH and some popular microcontrollers. The PSD813FN/FH control input pins are labeled as the microcontroller function for which they are configured. The MCU interface is specified using the PSDsoft tools. The PC2 pin should be grounded if Vstby is not used.

#### 80C31

Figure 10 shows the interface to the 80C31 which has an 8-bit multiplexed address/data bus. The lower address byte is multiplexed with the data bus. The microcontroller RD and WR signals may be used for accessing internal SRAM and I/O Ports while the PSEN signal is used to read the EPROM. The ALE input (Port D PD0) latches the address. Refer to the Memory Section for additional 80C31 operating modes.

#### 68HC11

Figure 11 shows an interface to an 68HC11 where the PSD813FH is configured in 8-bit multiplexed mode with E and R/W settings. The ECSPLD can generate the READ and WR signals for external on board devices. The CNTL2 pin is not used and can be used as a PLD input.

#### 80C251

The Intel 80C251 microcontroller features a user-configurable bus interface with two possible bus configurations as shown in Table 13.

| Configuration | 80C251<br>Read/Write<br>Pins | Connecting to<br>PSD813FN/FH<br>Pins | Page Mode                                                       |

|---------------|------------------------------|--------------------------------------|-----------------------------------------------------------------|

| 1             | WR<br>RD<br>PSEN             | CNTL0<br>CNTL1<br>CNTL2              | Non-Page Mode, 80C31 compatible<br>A[7:0] multiplex with D[7:0} |

| 2             | WR<br>PSEN only              | CNTL0<br>CNTL1                       | Non-Page Mode<br>A[7:0] multiplex with D[7:0}                   |

Table 13.

80C251 Configurations

Configuration 1 is 80C31 compatible. The bus interface to the PSD813FH is identical to that shown in Figure 10. There is only one read input (PSEN) connected to the CNTL1 pin on the PSD813FH. The A16 connection to the PA0 pin allows for a larger address input to the PSD813FH.

# Bus Interface (cont.)

us

25

(cont.)

There are four programmable I/O ports: Ports A, B are 8 bits, Port C is seven bits and Port D is three bits. The ports can be configured to function in different modes of operation.

Each port pin is individually configurable allowing a single port to perform multiple functions. The configuration is defined either using the PSDsoft tools or by the microcontroller writing to on-chip registers.

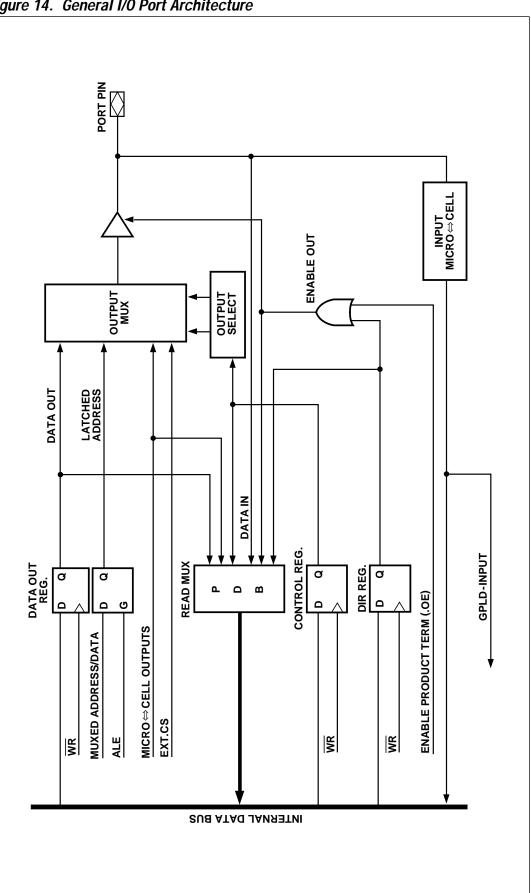

#### **General Port Architecture**

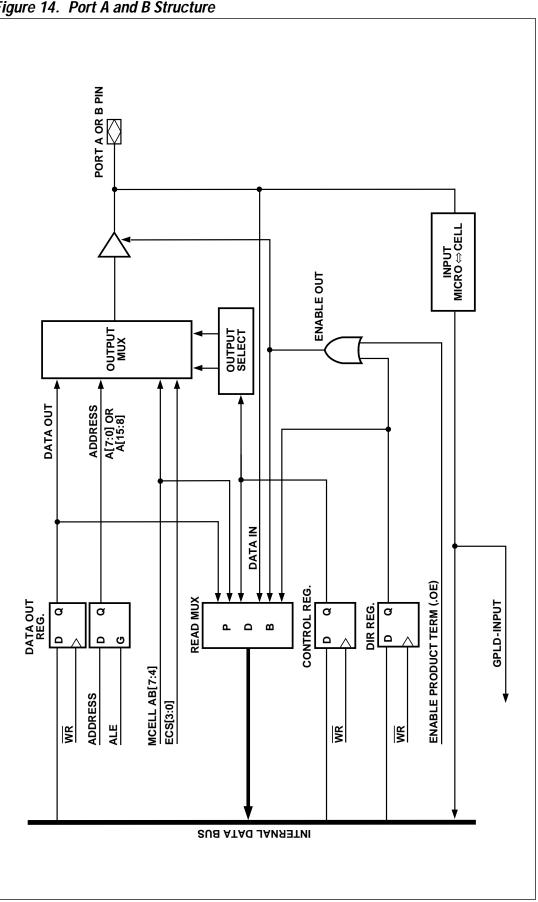

The general architecture of the I/O Port is shown in Figure 12. Individual Port diagrams are shown in Figures 14, 15 and 16, and will be discussed in the section below. If the PSD813FN/FH is configured to a non-multiplexed bus mode, Port A and/or Port B are connected to the MCU data bus and are not available as general purpose I/O ports.

As shown in Figure 12, the port pins contain an output multiplexer whose selects are driven by the configuration defined in PSDabel and the Control Registers. Inputs to the multiplexer include the following:

- Output data from the Data Out Register in the MCU I/O output mode

- □ Latched address outputs

- □ GPLD Micro⇔Cell output or ECSPLD external chip select output

- □ ECSPLD external chip select output

The above inputs are also connected to the Port Data Buffer (PDB) for feedback to the Internal Data Bus that can be read by the microcontroller. The PDB is a three-state buffer operating like a multiplexer that allows only one source to be read at a time. The PDB also has inputs from the Direction Register, Control Register and direct port pin input (Data In).

The Port pin's tri-state output driver enable is controlled by a two input OR gate whose inputs come from the GPLD AND array Enable product term (.oe) and the Direction Register. If the enable product term of the array output is not defined, then the Direction Register has sole control of the buffer. Refer to Tables 14 and 15 on how the direction of a port pin is configured.

Table 14. Port Pin Direction Control, Output Enable P.T. Not Defined

| Direction Register Bit | Port Pin Mode |

|------------------------|---------------|

| 0                      | Input         |

| 1                      | Output        |

| Direction Register Bit | Output Enable P.T.* | Port Pin Mode |

|------------------------|---------------------|---------------|

| 0                      | 0                   | Input         |

| 0                      | 1                   | Output        |

| 1                      | 0                   | Output        |

| 1                      | 1                   | Output        |

Table 15. Port Pin Direction Control, Output Enable P.T. Defined

\*Port D does not have an output enable P.T.

The register contents can be altered by the microcontroller. The PDB feedback path allows the microcontroller to check the contents of the registers.

The A, B and C Ports have embedded Input Micro⇔Cells which can be configured as a latch, a register or direct input to the GPLD. The latch and register are clocked by the address strobe or a product term from the GPLD AND array. The output from the Input Micro⇔Cell drives the PLD input bus and can be read by the microcontroller. Refer to the Input Micro⇔Cell description in the PLD section.

Port A has additional logic (not shown in Figure 12) that enables it to operate in Peripheral I/O mode when the PIO bit in the VM Register is set.

# I/O Ports

(cont.)

# I/O Ports

(cont.)

#### **Port Operating Modes**

The I/O Ports have several modes of operation as shown in Table 16. Some modes may be selected using the PSDabel tool and programmed into the device using Non-Volatile Memory (NVM) that is active when power is applied and cannot be altered unless the device is reprogrammed. If a mode is not defined in PSDsoft, then other modes can be set by the microcontroller writing to the Port configuration registers at Run-Time. The PLD I/O, Data Port and Address Input modes are NVM configurations. The other modes are initiated by the microcontroller.

If the NVM modes are not selected, the port can be altered dynamically between MCU I/O or Address Out modes by writing to the Control Register. Each bit of the eight-bit Control Register may store a "1", setting its respective bit in the port to MCU I/O, or to a "0", setting it to Address Out. The Direction Register or the output enable product term determine if the pin is input or output.

Table 16 summarizes the operating modes of the I/O ports. Not all the functions are available to every port. Table 17 shows how and where the different modes are configured.

| Port Mode                                                                     | Port A                      | Port B                      | Port C          | Port D                   | Configured<br>at Run-Time |

|-------------------------------------------------------------------------------|-----------------------------|-----------------------------|-----------------|--------------------------|---------------------------|

| MCU I/O                                                                       | Yes                         | Yes                         |                 | Yes                      | Yes                       |

| PLD I/O<br>McellAB Outputs<br>McellC Outputs<br>ECSPLD Outputs<br>ZPLD Inputs | PA7-4<br>No<br>PA3-0<br>Yes | PB7-4<br>No<br>PB3-0<br>Yes |                 | No<br>No<br>PD2-0<br>Yes | No                        |

| Address Out                                                                   | Yes<br>(A7-0)               | Yes (A7–0,<br>A15–8)        | Reserved<br>for | No                       | Yes                       |

| Address In                                                                    | Yes                         | Yes                         | Flash<br>Memory | No                       | No                        |

| Data Port                                                                     | Yes<br>(D7–0)               |                             | Control<br>Plus | No                       | No                        |

| Open Drain                                                                    | Yes<br>(PA7-4)              | Yes<br>(PB7-4)              | VSTBY           | No                       | Yes                       |

| Slew Rate                                                                     | Yes<br>(PA3-0)              | Yes<br>(PB3-0)              |                 | Yes                      | Yes                       |

| Peripheral I/O                                                                | Yes                         | No                          |                 | No                       | Yes                       |

Table 16. Port Operating Modes

#### I/O Ports (cont.)

Port Operating Modes (cont.)

# Table 17. Port Operating Mode Settings

| Mode                       | Defined In<br>PSDabel                   | Defined In<br>PSDconfiguration | Control<br>Register<br>Setting | Direction<br>Register<br>Setting     | VM<br>Register<br>Setting |

|----------------------------|-----------------------------------------|--------------------------------|--------------------------------|--------------------------------------|---------------------------|

| MCU I/O                    | Declare pins only                       | NA                             | 0                              | 1 = output,<br>0 = input<br>(Note 1) | NA                        |

| PLD I/O                    | Logic equations                         | NA                             | NA*                            | (Note 1)                             | NA                        |

| Data Port<br>(Port A,B)    | NA                                      | Specify bus type               | NA                             | NA                                   | NA                        |

| Address Out<br>(Port A,B)  | Declare pins only                       | NA                             | 1                              | 1 (Note 1)                           | NA                        |

| Address In<br>(Port A,B,C) | Logic equation for<br>Input Micro⇔Cells | NA                             | NA                             | NA                                   | NA                        |

| Peripheral I/O<br>(Port A) | Logic equations<br>(PSEL0 & 1)          | NA                             | NA                             | NA                                   | PIO bit =1                |

\*NA – Not Applicable

NOTE 1: The direction of the Port A, B, C pins are controlled by the Direction Register ORed with the individual output enable product term (.oe) from the GPLD AND array.

### PLD I/O Mode

The PLD I/O mode uses the port as an input to the GPLD Input Micro⇔Cell, and/or as an output from the GPLD, ECSPLD. The Port assignments are shown in Tables 9 and 10. The output can be tri-stated with a control signal defined by a product term (.oe) from the PLD, or, by setting a zero in the Direction Register. The Direction Register **must not** be set to "1" if the pin is defined as a PLD input pin. The PLD I/O mode is specified in PSDabel by declaring the port pins, then writing an equation assigning it to the port.

#### MCU I/O Mode

In the MCU I/O Mode the microcontroller uses the PSD813FN/FH ports to expand its own I/O ports. The ports on the PSD813FN/FH are mapped into the microcontroller address space. The addresses of the ports are listed in Table 22.

A port pin will be put into MCU I/O mode by writing a zero to the corresponding bit in the Control Register. The direction may be changed by writing to the Direction Register for the port where a "1" makes it an output and a "0" an input. The output enable product term also can change the direction of the pin (see Table 14 and 15). When the pin is configured as output, the content of the Data Out Register drives the pins. In input mode, the microcontroller reads the port input through the Data In buffer

Ports C and D do not have a Control Register and are in MCU I/O mode by default for pins that are not configured as PLD I/O.

#### Address Out Mode

For microcontrollers with a multiplexed address/data bus, the ports in Address Out mode drive latched addresses to external devices. Address [7:0] are always assigned to Port A. See Table 23 for the address output pin assignments on Ports A and B. The Direction Register and the Control Register must be set to a "1" for port pins using Address Out mode.

In non-multiplexed 8 bit bus mode, address[7:0] are available on Port B in Address Out Mode.

I/O Ports

(cont.)

#### Port Operating Modes (cont.)

#### Address In Mode

For microcontrollers that have more than 16 address lines, the higher addresses can be connected to Port A, B, or C. The address input can be latched in the Input Micro⇔Cell by ALE. Any input that is included in the DPLD equations for the PSD Flash, OTP Boot, or EPROM is considered as address input.

#### Data Port Mode

Port A can be used as a data bus port for a microcontroller with a non-multiplexed address/data bus. The Data Port is connected to the data bus of the microcontroller. The general I/O functions are disabled in Port A if the port is configured as Data Port. See Figure 9.

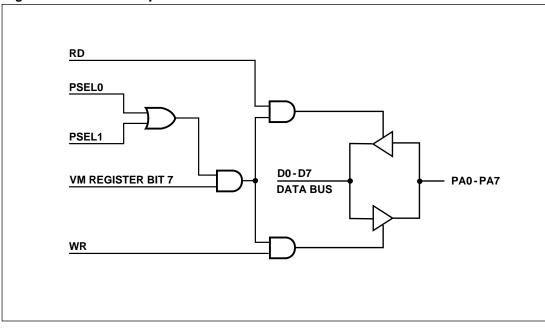

#### Peripheral I/O Mode

Only Port A supports the Peripheral I/O mode whereby all of Port A serves as a tri-stateable bi-directional data buffer of the microcontroller's data bus. Peripheral mode is enabled by setting Bit 7 of the VM Register to a "1". Figure 13 shows that when Peripheral mode is enabled and either PSEL0 and PSEL1 from the DPLD is active, Port A acts as a bi-directional buffer for the microcontroller D[7:0] data bus. The buffer is tri-stated when PSEL 0 or 1 is not active. The Peripheral I/O mode can be used to interface with external peripherals. Use PSDabel to write equations that contain the keyboards PSEL0 and PSEL1.

#### **Open Drain/Slew Rate Mode**

Ports A (pins PA7-4) and B (pins PB7-4) and C (except PC2) can be configured as open drain instead of CMOS outputs. The Open Drain configuration is useful for sinking large currents to operate LEDs, for example. The Open Drain mode is enabled by writing a "1" to the corresponding bit in the Drive Register.

Port A (PA3–0), Port B (PB3–0) and Port D can be configured as ECSPLD outputs that have a high slew rate. The high slew rate is enabled by writing a "1" to the corresponding bit in the Drive Register.

Figure 13. Port A Peripheral Mode

# I/O Ports

(cont.)

#### Port Registers

Each port has a set of registers used for configuration (PCR, Port Configuration Registers) and data transfers (PDR, Port Data Registers). The contents of the registers can be accessed by the microcontroller through normal read/write bus cycles at the addresses given in Table 22. The address of the registers is comprised by that of the CSIOP output from the DPLD plus an address offset as listed in the tables.

The pins of a port are individually configurable and each bit in the register controls its respective pin. For example, Bit 0 in a register refers to Bit 0 in its port. The three Port Configuration Registers, shown in Table 18, are used for setting the port configuration. Each register is set to zero at power up.

| Register Name | Port    | MCU Access |

|---------------|---------|------------|

| Control       | A,B     | Write/Read |

| Direction     | A,B,C,D | Write/Read |

| Drive*        | A,B,C,D | Write/Read |

\*Note: See Table 20 for Drive Register bit definition.

# **Control Register**

A "0" in the Control Register sets the Port pin to MCU I/O for Port A and B. A "1" sets the Port pin to Address Out mode. The default mode is MCU I/O.

#### **Direction Register**

Controls the direction of data flow in the I/O Ports. A "1" configures the port to be an output, and a "0" to an input. The I/O configuration can be read from the Direction Register. The default mode is input.

As shown in Figure 12, the direction of data flow in Port A,B and C pins are also controlled by the output enable (.oe) product term from the GPLD AND array. If the .oe product term is not active, the Direction Register has sole control of the pin direction.

An example of a configuration for a port with the three least significant bits set to output and the remainder set to input is shown in Table 19. The Port D register has only the three least significant bits active.

Table 19. Port Direction Assignment Example

| ſ | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|-------|-------|-------|-------|-------|-------|-------|-------|

|   | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 1     |

### I/O Ports (cont.)

#### Port Registers (cont.)

#### Drive Register

The Drive Register configures the pin driver as Open Drain, or in the case of ECSPLD outputs, sets the pin to operate in high slew rate. An external pull-up resistor is not required when the pin is in the slew rate mode.

For Ports A and B the register sets different functions for the lower and higher nibbles. The four upper bits set the corresponding bits the as CMOS ("0") or Open Drain ("1") driver. The four lower bits are used for slew rate control. The slew rate is a measurement of the rise and fall times of the output. A higher slew rate means a faster output response while a lower slew rate is a slower, lower slope, response. The pin operates in high slew rate when the corresponding bit in the Drive Register is set to "1".

Table 20 shows the Drive Registers of Port A, B, C and D and which pin has the Open Drain or Slew Rate configuration.

|                   |               |               | -             |               |               |              |               |               |

|-------------------|---------------|---------------|---------------|---------------|---------------|--------------|---------------|---------------|

| Drive<br>Register | Bit 7         | Bit 6         | Bit 5         | Bit 4         | Bit 3         | Bit 2        | Bit 1         | Bit 0         |

| Port A            | Open<br>Drain | Open<br>Drain | Open<br>Drain | Open<br>Drain | Slew<br>Rate  | Slew<br>Rate | Slew<br>Rate  | Slew<br>Rate  |

| Port B            | Open<br>Drain | Open<br>Drain | Open<br>Drain | Open<br>Drain | Slew<br>Rate  | Slew<br>Rate | Slew<br>Rate  | Slew<br>Rate  |

| Port C*           | Open<br>Drain | Open<br>Drain | Open<br>Drain | Open<br>Drain | Open<br>Drain | NA           | Open<br>Drain | Open<br>Drain |

| Port D            | NA            | NA            | NA            | NA            | NA            | Slew<br>Rate | Slew<br>Rate  | Slew<br>Rate  |

Table 20. Drive Register Pin Assignment

NOTE: NA = Not Applicable, bit should set to "0".

\*Port C pins are dedicated to Flash memory control in this multi-chip module product.

# I/O Ports

(cont.)

#### Port Data Registers

The Port Data Registers, shown in Table 21, are used by the microcontroller to write or read data to or from the ports. Table 21 shows the register name, the ports having each register type and microcontroller access for each register. The registers are described below.

| Register Name          | Port    | MCU Access                                                             |  |

|------------------------|---------|------------------------------------------------------------------------|--|

| Data In                | A,B,C,D | Read – the input on pin                                                |  |

| Data Out               | A,B,C,D | Write/Read Feedback                                                    |  |

| Output Micro⇔Cell      | A,B,C   | Read – outputs of Micro⇔Cells<br>Write – loading Micro⇔Cells Flip-Flop |  |

| Input Micro⇔Cell A,B,C |         | Read – outputs of the Input Micro⇔Cells                                |  |

| Enable Out A,B,C       |         | Read – the output enable control of the port driver                    |  |

#### Table 21. Port Data Registers

#### Data In

Port pins are connected directly to the Data In buffer. In MCU I/O input mode, the pin input is read through the Data In buffer. The MCU can always read the state of a Port pin using this method, regardless of what is driving the pin.

#### Data Out Register

Stores output data written by the MCU in the MCU I/O output mode. The contents of the Register are driven out to the pins if the Direction Register or the .oe product term is set to "1". The contents of the register can also be read back by the microcontroller.

#### Output Micro⇔Cell

The GPLD Output Micro $\Leftrightarrow$ Cells occupy a location in the microcontroller's address space. The microcontroller can read the output of the Micro $\Leftrightarrow$ Cells. Writing to the Micro $\Leftrightarrow$ Cell loads data to the Micro $\Leftrightarrow$ Cell Flip-Flops. Refer to the PLD section for more detail.

#### Input Micro⇔Cell

The Input Micro⇔Cells can be used to latch or store external inputs. The outputs of the Input Micro⇔Cells are routed to the PLD input bus and also can be read by the microcontroller. Refer to the PLD section for detail description.

#### Enable Out

The Enable Out buffer allows the microcontroller to read the outputs of the "OR" gate that is the enable input to the port output driver. A "1" indicates the driver is in output mode, a "0" indicates the driver is in tri-state and the pin is in input mode.

#### Port Data Registers (cont.)

# Register I/O Address Offset

The base address of the Registers is defined in the CSIOP equation that occupies 256 bytes of address space and is defined by the user in PSDsoft. The lower address byte A[7:0], or address offset, selects the register. Table 22 shows the address offset for all MCUs except those Motorola microcontrollers with a 16-bit data bus.

For example, when the CSIOP is defined to occupy the address range of 1000h to 10FFh in PSDabel, the address of the Port A Control Register is then 1002h.

| Register Name     | Port A | Port B | Port C | Port D |  |  |

|-------------------|--------|--------|--------|--------|--|--|

| Data In           | 00     | 01     | 10     | 11     |  |  |

| Control           | 02     | 03     |        |        |  |  |

| Data Out          | 04     | 05     | 12     | 13     |  |  |

| Direction         | 06     | 07     | 14     | 15     |  |  |

| Drive             | 08     | 09     | 16     | 17     |  |  |

| Input Micro⇔Cell  | 0A     | 0B     | 18     |        |  |  |

| Enable Out        | 0C     | 0D     | 1A     |        |  |  |

| Output Micro⇔Cell | 20     | 20     | 21     |        |  |  |

Table 22. I/O Register Address Offset (relative to CSIOP)

# Port A and B – Functionality and Structure

Port A and B have similar functionality and structure as shown in Figure 14. The two ports can be configured to perform one or more of the following functions:

- □ MCU I/O Mode

- □ GPLD Output Micro⇔Cells McellAB[7:4] can be connected to Port A PA[7:4} or Port B PB[7:4].

- ECSPLD Output External chip select output can be connected to either Port A PA[3:0] or Port PB[3:0].

- □ Latched Address output Provide latched address output per Table 23.

- □ Address In Additional high address inputs using the Input Micro⇔Cells.

- Open Drain/Slew Rate pins PA[3:0] and PB[3:0] can be configured to Open Drain Mode pins PA[7:4] and PB[7:4] can be configured to fast slew rate

- □ Data Port Port A to D[7:0} for 8 bit non-multiplexed bus

- □ Peripheral Mode Port A only

| Table 23. | I/O Port Latched Address Output Assignments |

|-----------|---------------------------------------------|

|-----------|---------------------------------------------|

| , 5                                        |               |               |               |               |  |

|--------------------------------------------|---------------|---------------|---------------|---------------|--|

| Microcontroller                            | Port A (3:0)  | Port A (7:4)  | Port B (3:0)  | Port B (7:4)  |  |

| 8-Bit<br>Multiplexed Bus<br>(PSD813FH)     | Address (3:0) | Address (7:4) | Address (3:0) | Address (7:4) |  |

| 8-Bit<br>Non-Multiplexed Bus<br>(PSD813FN) | N/A           | N/A           | Address (3:0) | Address (7:4) |  |

N/A = Not Applicable.

(cont.)

## I/O Ports

(cont.)

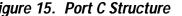

#### *Port C – Functionality and Structure*

All Port C pins are configured as PLD I/O mode for Flash memory controls (except PC2). The other Port C I/O functions are disabled (multi-chip module only).

| PC0<br>PC1 | WRF<br>RDF | Flash Memory Write Signal<br>Flash Memory Read Signal |

|------------|------------|-------------------------------------------------------|

| PC2        | Vstby      | SRAM Vstby                                            |

| PC3        | A14F       | Flash Address A14                                     |

| PC4        | A16F       | Flash Address A16                                     |

| PC5        | A17F       | Flash Address A17                                     |

| PC6        | A18F       | Flash Address A18                                     |

| PC7        | CSF        | Flash Chip Select                                     |

|            |            |                                                       |

Port C pin PC2 is dedicated as the Vstby pin for SRAM battery backup and can not be used for other functions.

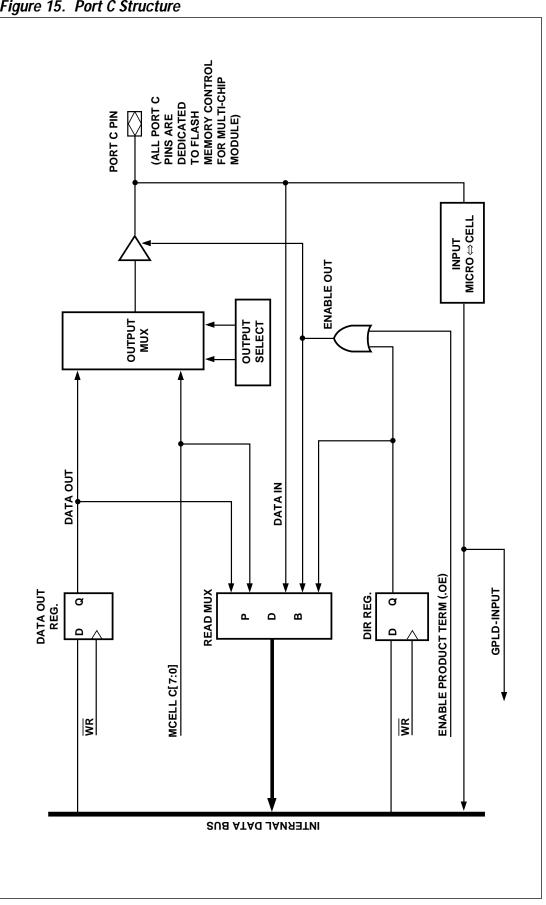

#### Port D – Functionality and Structure

Port D has only three I/O pins, does not support Address Out mode, and no Control Register is required. Port D can be configured to perform one or more of the following functions:

- □ MCU I/O Mode

- □ ECSPLD Output External chip select output

- □ PLD Input direct input to PLD, no Input Micro⇔Cells

- □ Slew rate pins can be set up for fast slew rate

Port D pins can be configured in PSDsoft as input pins for other dedicated functions:

- D PD0 ALE, as address strobe input

- □ PD1 CLKIN, as clock input to the Micro⇔Cells Flip-Flops and APD counter

- PD2 CSI, as active low chip select input. A high input will disable the PSD EPROM/SRAM.

I/O Ports

## Figure 15. Port C Structure

### (cont.)

Preliminary

**US**

38

**US**

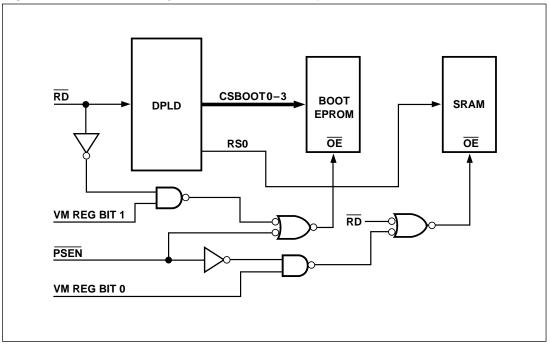

The PSD813FN/FH are a multi-chip module that includes a PSD6XX die and a 4 megabit Flash memory die configured to operate as a 1 Mb device. The PSD813FN/FH includes 32 Kbytes of OTP Boot EPROM; the Flash die provides 128 Kbytes of Flash memory. The OTP Boot EPROM is used for system boot up and for storing the Flash memory programming algorithm. The Flash erase and programming algorithms are compatible to the AMD and SGS-Thomson Embedded Erase and Programming Algorithm<sup>™</sup>. The Flash memory can be erased or programmed while the microcontroller is executing code from the Boot EPROM.

Chip selects for the memory blocks come from the DPLD and GPLD decoding logic and are defined by the user in the PSDsoft software. Figure 17 shows the organization of the Memory Block.

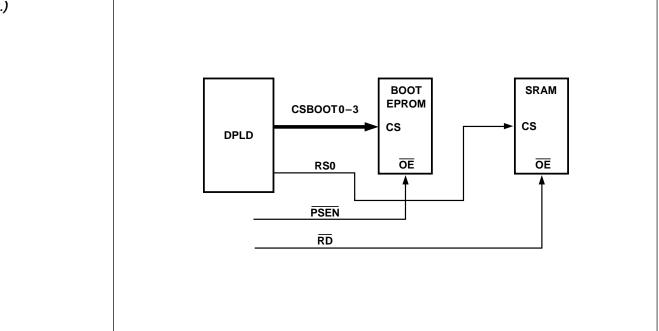

#### **Boot EPROM**

The chip selects (CSBOOT0–3) for the OTP Boot EPROM are generated from the DPLD address decoder. The CSBOOT0–3 are defined in 8 Kbyte boundaries and should not overlap the Flash memory address space.

#### Flash Memory

The Flash die that is used on this MCM is a 4 Mbit Flash device but only 1 Mbit will be addressed. Address lines A14 and A15 are inactive during Flash reads. This leaves address lines A16, A17, and A18 to page through eight 16 Kbyte sectors of Flash memory. Each 16 Kbyte sector of Flash is addressed by the address lines A0–A13. This Flash paging is simplified by the configuration of the DPLD and the GPLD. FS0–7 are the chip selects for each block that is defined in the DPLD at 16 Kbyte boundaries. The designer may custom configure Flash addressing schemes by the HDL equations developed in PSDsoft. The use of the internal PSD Page register is very effective in this application. See Figure 17 and Table 24.

**NOTE:** Unlike Flash reads, whenever the embedded Flash algorithms are exercised (write, erase, ID, etc), address line A14 to the Flash is enabled (as configured by the HDL) to pass commands from the MCU to the Flash die. Address line A15 to the Flash die is permanently grounded.

Seven of the pins and Micro⇔Cells on the PSD6XX die are reserved for generation of Flash memory control signals. The address lines A14F, A16F, A17F, A18F, and the chip select CSF are generated based on the FS0–7 inputs to the GPLD.

Refer to Appendix A for the operation and programming algorithm for the Flash memory.

#### SRAM

The SRAM has 4 Kbits of memory, organized as 512 x 8. The SRAM is enabled by the chip select signal RS0 from the DPLD. The SRAM has a battery back-up (STBY) mode. This back-up mode is automatically invoked when the  $V_{CC}$  voltage drops under the Vstdby voltage. The Vstdby voltage is connected only to the SRAM and cannot be lower than 2.0 volts.

#### Memory Select Map

The Boot EPROM, Flash memory, and SRAM chip select equations are defined in the ABEL file in terms of address and other DPLD inputs. The memory space for the Flash chip select (FS0–7) should not be larger than the 16K Flash block it is selecting. The Boot EPROM block should not be larger than 8 Kbytes.

The following rules govern how the PSD813F memory selects/space are defined:

- □ The Flash blocks address space cannot overlap among blocks.

- □ The Flash blocks address space cannot overlap the Boot EPROM, the SRAM and I/O address space.

- □ SRAM and internal I/O address space cannot overlap.

- □ SRAM and internal I/O space can overlap Boot EPROM space, with priority given to SRAM or I/O. The portion of Boot EPROM which is overlapped cannot be accessed.

## Memory Block (cont.)

### Figure 17. PSD813FN/FH Memory Block

| Signal<br>Name | Pin/Macrocell | Function                  | <i>Example Equations<br/>Based on the 8031 Bus</i>               |  |  |  |  |

|----------------|---------------|---------------------------|------------------------------------------------------------------|--|--|--|--|

| WRF            | Pin PC0       | Write input               | WRF = wr;                                                        |  |  |  |  |

| RDF            | Pin PC1       | Read input                | RDF = ! (!rd # !psen);                                           |  |  |  |  |

| A14F           | Pin PC3       | Flash memory<br>A14 input | A14F = A14 & PGR3                                                |  |  |  |  |

| A16F           | Pin PC4       | Flash memory<br>A16 input | A16F = FCS1 # FCS3 # FCS5 # FCS7;                                |  |  |  |  |

| A17F           | Pin PC5       | Flash memory<br>A17 input | A17F = FCS2 # FCS3 # FCS6 # FCS7;                                |  |  |  |  |

| A18F           | Pin PC6       | Flash memory<br>A18 input | A18F = FCS4 # FCS5 # FCS6 # FCS7;                                |  |  |  |  |

| CSF            | Pin PC7       | Flash memory select       | !CSF = FCS0 # FCS1 # FCS2 # FCS3 #<br>FCS4 # FCS5 # FCS6 # FCS7; |  |  |  |  |

**U**S

## Memory Blocks

(cont.)

### Memory Select for 8031 Microcontrollers

Preliminary