#### **Features**

- 2,097,152 word by 8 bit organization

- Single 3.3V  $\pm$  0.3V or 5.0V  $\pm$  0.5V power supply

- Standard Power (SP) and Low Power (LP)

- 2048 Refresh Cycles

- 32 ms Refresh Rate (SP version)

- 128 ms Refresh Rate (LP version)

- · High Performance:

|                  |                                     | -50 | -60 | -6R | -70 | Units |

|------------------|-------------------------------------|-----|-----|-----|-----|-------|

| t <sub>RAC</sub> | RAS Access Time                     | 50  | 60  | 60  | 70  | ns    |

| t <sub>CAC</sub> | CAS Access Time                     | 13  | 15  | 17  | 20  | ns    |

| t <sub>AA</sub>  | Column Address Access Time          | 25  | 30  | 30  | 35  | ns    |

| t <sub>RC</sub>  | Cycle Time                          | 84  | 104 | 104 | 124 | ns    |

| t <sub>HPC</sub> | EDO (Hyper Page) Mode<br>Cycle Time | 20  | 25  | 25  | 30  | ns    |

- · Low Power Dissipation

- Active (max) 100 mA / 90 mA / 80 mAStandby: TTL Inputs (max) 1.0 mA

- Standby: CMOS Inputs (max)

- 1.0 mA (SP version)

- 0.2 mA (LP version)

- Self Refresh (LP version only)

- 200μA (3.3 Volt)

- 300μA (5.0 Volt)

- Extended Data Out (Hyper Page) Mode

- · Read-Modify-Write

- RAS Only and CAS before RAS Refresh

- · Hidden Refresh

- Package: TSOP-II 28 (400milx725mil)

### **Description**

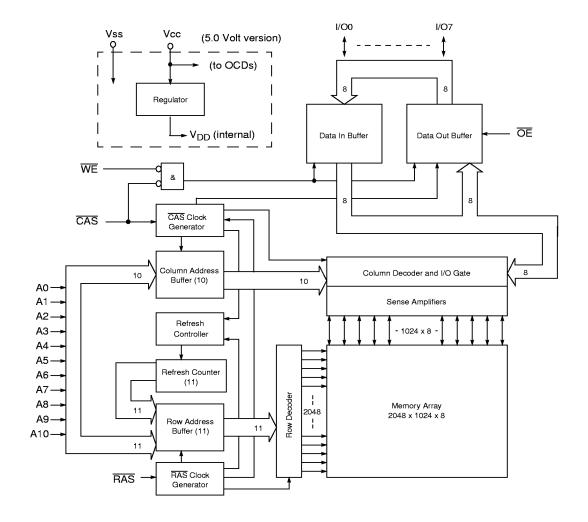

The IBM0117805 is a dynamic RAM organized 2,097,152 words by 8 bits, which has a very low "sleep mode" power consumption option. These devices are fabricated in IBM's advanced 0.5µm CMOS silicon gate process technology. The circuit and process have been carefully designed to pro-

vide high performance, low power dissipation, and high reliability. The devices operate with a single  $3.3V \pm 0.3V$  or  $5.0V \pm 0.5V$  power supply. The 21 addresses required to access any bit of data are multiplexed (11 are strobed with RAS, 10 are strobed with CAS).

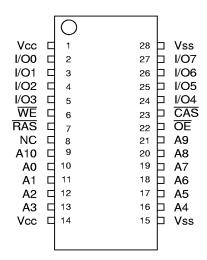

#### Pin Assignments (Top View)

#### **Pin Description**

| RAS             | Row Address Strobe     |

|-----------------|------------------------|

| CAS             | Column Address Strobe  |

| WE              | Read/Write Input       |

| A0 - A10        | Address Inputs         |

| ŌĒ              | Output Enable          |

| 1/00 - 1/07     | Data Input/Output      |

| V <sub>CC</sub> | Power (+3.3V or +5.0V) |

| V <sub>SS</sub> | Ground                 |

28H4724 SA14-4221-04 Revised 11/96

## **Ordering Information**

| Part Number       | SP/LP | Self Refresh | Power Supply | Speed | Package           | Notes |

|-------------------|-------|--------------|--------------|-------|-------------------|-------|

| IBM0117805T3 -50  | SP    | No           | 5.0V         | 50ns  | 400mil TSOP-II 28 | 1     |

| IBM0117805T3 -60  | SP    | No           | 5.0V         | 60ns  | 400mil TSOP-II 28 | 1     |

| IBM0117805T3 -6R  | SP    | No           | 5.0V         | 60ns  | 400mil TSOP-II 28 | 1     |

| IBM0117805T3 -70  | SP    | No           | 5.0V         | 70ns  | 400mil TSOP-II 28 | 1     |

| IBM0117805BT3 -50 | SP    | No           | 3.3V         | 50ns  | 400mil TSOP-II 28 | 1     |

| IBM0117805BT3 -60 | SP    | No           | 3.3V         | 60ns  | 400mil TSOP-II 28 | 1     |

| IBM0117805BT3 -6R | SP    | No           | 3.3V         | 60ns  | 400mil TSOP-II 28 | 1     |

| IBM0117805BT3 -70 | SP    | No           | 3.3V         | 70ns  | 400mil TSOP-II 28 | 1     |

| IBM0117805MT3 -50 | LP    | Yes          | 5.0V         | 50ns  | 400mil TSOP-II 28 | 1     |

| IBM0117805MT3 -60 | LP    | Yes          | 5.0V         | 60ns  | 400mil TSOP-II 28 | 1     |

| IBM0117805MT3 -70 | LP    | Yes          | 5.0V         | 70ns  | 400mil TSOP-II 28 | 1     |

| IBM0117805PT3 -50 | LP    | Yes          | 3.3V         | 50ns  | 400mil TSOP-II 28 | 1     |

| IBM0117805PT3 -60 | LP    | Yes          | 3.3V         | 60ns  | 400mil TSOP-II 28 | 1     |

| IBM0117805PT3 -6R | LP    | Yes          | 3.3V         | 60ns  | 400mil TSOP-II 28 | 1     |

| IBM0117805PT3 -70 | LP    | Yes          | 3.3V         | 70ns  | 400mil TSOP-II 28 | 1     |

<sup>1.</sup> SP = Standard Power version (IBM0117805 and IBM0117805B); LP = Low Power version (IBM0117805M and IBM00117805P)

# **Block Diagram**

## **Truth Table**

| Function                       |                                        | RAS   | CAS | WE  | ŌĒ  | Row<br>Address | Col<br>Address | 1/00 - 1/07       |

|--------------------------------|----------------------------------------|-------|-----|-----|-----|----------------|----------------|-------------------|

| Standby                        |                                        | Н     | Н→Х | Χ   | Х   | Х              | Х              | High Impedance    |

| Read                           |                                        | L     | L   | Н   | L   | Row            | Col            | Data Out          |

| Early-Write                    |                                        | L     | L   | L   | Х   | Row            | Col            | Data In           |

| Delayed-Write                  |                                        | L     | L   | H→L | Н   | Row            | Col            | Data In           |

| ead-Modify-Write               |                                        | L     | L   | H→L | L→H | Row            | Col            | Data Out, Data In |

| EDO (Hyper Page) Mode          | 1st Cycle                              | L     | H→L | Н   | L   | Row            | Col            | Data Out          |

| Read                           |                                        |       | H→L | Н   | L   | N/A            | Col            | Data Out          |

| EDO (Hyper Page) Mode          | 1st Cycle                              | L     | H→L | L   | Х   | Row            | Col            | Data In           |

| Write                          | 2nd Cycle                              | L     | H→L | L   | Х   | N/A            | Col            | Data In           |

| EDO (Hyper Page) Mode          | 1st Cycle                              | L     | H→L | H→L | L→H | Row            | Col            | Data Out, Data In |

| Read-Modify-Write              | 2nd Cycle                              | L     | H→L | H→L | L→H | N/A            | Col            | Data Out, Data In |

| RAS-Only Refresh               |                                        | L     | Н   | Х   | Х   | Row            | N/A            | High Impedance    |

| CAS-Before-RAS Refresh         |                                        | H→L   | L   | Н   | Х   | Х              | N/A            | High Impedance    |

| IIIddaa Dafaada                | Read                                   | L→H→L | L   | Н   | L   | Row            | Col            | Data Out          |

| Hidden Refresh                 | Write                                  | L→H→L | L   | Н   | Х   | Row            | Col            | Data In           |

| Self Refresh (LP version only) | ······································ | H→L   | L   | L   | Н   | Х              | Х              | X                 |

### **Absolute Maximum Ratings**

| C b - l          | D                            | Ra                                      | ting                                    | 11    | NI-4  |

|------------------|------------------------------|-----------------------------------------|-----------------------------------------|-------|-------|

| Symbol           | Parameter                    | 3.3 Volt Device                         | 5.0 Volt Device                         | Units | Notes |

| V <sub>CC</sub>  | Power Supply Voltage         | -0.5 to +4.6                            | -1.0 to +7.0                            | ٧     | 1     |

| V <sub>IN</sub>  | Input Voltage                | -0.5 to min (V <sub>CC</sub> +0.5, 4.6) | -0.5 to min (V <sub>CC</sub> +0.5, 7.0) | ٧     | 1     |

| V <sub>OUT</sub> | Output Voltage               | -0.5 to min (V <sub>CC</sub> +0.5, 4.6) | -0.5 to min (V <sub>CC</sub> +0.5, 7.0) | ٧     | 1     |

| T <sub>OPR</sub> | Operating Temperature        | 0 to +70                                | 0 to +70                                | °C    | 1     |

| T <sub>STG</sub> | Storage Temperature          | -55 to +150                             | -55 to +150                             | °C    | 1     |

| P <sub>D</sub>   | Power Dissipation            | 1.0                                     | 1.0                                     | W     | 1     |

| I <sub>OUT</sub> | Short Circuit Output Current | 50                                      | 50                                      | mA    | 1     |

Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a

stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **Recommended DC Operating Conditions** (T<sub>A</sub>= 0 to 70°C)

| C               | D                  | 3    | .3 Volt Devi | се                    | 5    | .0 Volt Devic | е                     | 11-4- | N1-4  |

|-----------------|--------------------|------|--------------|-----------------------|------|---------------|-----------------------|-------|-------|

| Symbol          | Parameter          | Min. | Тур.         | Max.                  | Min. | Typ.          | Max.                  | Units | Notes |

| V <sub>cc</sub> | Supply Voltage     | 3.0  | 3.3          | 3.6                   | 4.5  | 5.0           | 5.5                   | V     | 1     |

| V <sub>IH</sub> | Input High Voltage | 2.0  | _            | V <sub>CC</sub> + 0.5 | 2.4  | _             | V <sub>CC</sub> + 0.5 | ٧     | 1, 2  |

| V <sub>IL</sub> | Input Low Voltage  | -0.5 | —            | 0.8                   | -0.5 | —             | 0.8                   | ٧     | 1, 2  |

<sup>1.</sup> All voltages referenced to  $V_{\text{SS}}$ .

## **Capacitance** (T<sub>A</sub>= 25°C, V<sub>CC</sub>= $3.3V \pm 0.3V$ or V<sub>CC</sub>= $5.0V \pm 0.5V$ )

| Symbol          | Parameter                            | Min.        | Max. | Units | Notes |

|-----------------|--------------------------------------|-------------|------|-------|-------|

| C <sub>I1</sub> | Input Capacitance (A0 - A10)         | _           | 5    | pF    | 1     |

| C <sub>I2</sub> | Input Capacitance (RAS, CAS, WE, OE) | _           | 7    | pF    | 1     |

| Co              | Output Capacitance (I/O0 - I/O7)     | <del></del> | 7    | pF    | 1     |

|                 |                                      | . 545       |      |       |       |

<sup>1.</sup> Input capacitance measurements made with rise time shift method with  $\overline{CAS}$  &  $\overline{RAS}$  =  $V_{IH}$  to disable output.

28H4724 SA14-4221-04 Revised 11/96

<sup>2.</sup> V<sub>IH</sub> may overshoot to V<sub>CC</sub> + 1.2V for pulse widths of ≤ 4.0ns with 3.3 Volt, or V<sub>CC</sub> + 2.0V for pulse widths of ≤ 4.0ns (or V<sub>CC</sub> + 1.0V for ≤ 8.0ns) with 5.0 Volt. Additionally, V<sub>IL</sub> may undershoot to -2.0V for pulse widths ≤ 4.0ns with 3.3 Volt, or to -2.0V for pulse widths ≤ 4.0ns (or -1.0V for ≤ 8.0ns) with 5.0 Volt. Pulse widths measured at 50% points with amplitude measured peak to DC reference.

## **DC Electrical Characteristics** (T<sub>A</sub>= 0 to +70 °C, V<sub>CC</sub>= $3.3V \pm 0.3V$ or V<sub>CC</sub>= $5.0V \pm 0.5V$ )

| Symbol                                  | Parameter                                                                                                                                                                                                        |            | Min.     | Max.            | Units                                   | Notes                                   |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|-----------------|-----------------------------------------|-----------------------------------------|

| ••••••                                  | Operating Current                                                                                                                                                                                                | -50        | _        | 100             |                                         |                                         |

| I <sub>CC1</sub>                        | Average Power Supply Operating Current (RAS, CAS, Address Cycling: t <sub>RC</sub> = t <sub>RC</sub> min.)                                                                                                       | -60 / 6R   | _        | 90              | mA                                      | 1, 2, 3                                 |

|                                         | (RAS, CAS, Address Cycling: t <sub>RC</sub> = t <sub>RC</sub> min.)                                                                                                                                              | -70        | —        | 80              |                                         |                                         |

| I <sub>CC2</sub>                        | Standby Current (TTL)  Power Supply Standby Current  (RAS = CAS = V <sub>IH</sub> )                                                                                                                              |            | _        | 1               | mA                                      |                                         |

|                                         | RAS Only Refresh Current                                                                                                                                                                                         | -50        | —        | 100             |                                         |                                         |

| I <sub>CC3</sub>                        | Average Power Supply Current, RAS Only Mode                                                                                                                                                                      | -60 / 6R   | _        | 90              | mA                                      | 1, 3                                    |

|                                         | (RAS Cycling, $\overline{CAS} = V_{IH}$ : $t_{RC} = t_{RC} \min$ )                                                                                                                                               | -70        | _        | 80              |                                         |                                         |

|                                         | EDO (Hyper Page) Mode Current                                                                                                                                                                                    | -50        | _        | 60              |                                         |                                         |

| I <sub>CC4</sub>                        | Average Power Supply Current                                                                                                                                                                                     | -60 / 6R   | _        | 50              | mA                                      | 1, 2, 3                                 |

|                                         | $(\overline{RAS} = V_{IL}, \overline{CAS}, Address Cycling: t_{PC} = t_{PC} min)$                                                                                                                                | -70        | —        | 40              |                                         |                                         |

|                                         | Standby Current (CMOS)                                                                                                                                                                                           | SP version | _        | 1               |                                         | <u> </u>                                |

| I <sub>CC5</sub>                        | Power Supply Standby Current (RAS = CAS = V <sub>CC</sub> - 0.2V)                                                                                                                                                | LP version | _        | 0.2             | mA                                      |                                         |

| ***************                         | CAS Before RAS Refresh Current                                                                                                                                                                                   | -50        | <u> </u> | 100             | *************************************** | *************************************** |

| I <sub>CC6</sub>                        | Average Power Supply Current, CAS Before RAS Mode                                                                                                                                                                | -60 / 6R   | —        | 90              | mA                                      | 1, 3                                    |

|                                         | (RAS, CAS, Cycling: t <sub>RC</sub> = t <sub>RC</sub> min)                                                                                                                                                       | -70        | <u> </u> | 80              |                                         |                                         |

| *************************************** | Self Refresh Current, LP version only                                                                                                                                                                            | 3.3V       | _        | 200             |                                         |                                         |

| I <sub>CC7</sub>                        | Average Power Supply Current during Self Refresh CBR cycle with $\overline{RAS} \ge t_{RASS}$ (min); $\overline{CAS}$ held low; $\overline{WE} = V_{CC}$ - 0.2V; Addresses and $D_{IN} = V_{CC}$ - 0.2V or 0.2V. | 5.0V       | _        | 300             | μА                                      |                                         |

| I <sub>I(L)</sub>                       | Input Leakage Current Input Leakage Current, any input $(0.0 \le V_{IN} \le (V_{CC} + 0.3V))$ , All Other Pins Not Under Test = 0V                                                                               |            | -5       | +5              | μΑ                                      |                                         |

| I <sub>O(L)</sub>                       | Output Leakage Current $(D_{OUT}$ is disabled, $0.0 \le V_{OUT} \le V_{CC})$                                                                                                                                     |            | -5       | +5              | μА                                      |                                         |

| V <sub>OH</sub>                         | Output Level (TTL) Output "H" Level Voltage (I <sub>OUT</sub> = -2.0mA for 3.3V, or I <sub>OUT</sub> = -5mA for 5.0V)                                                                                            |            | 2.4      | V <sub>cc</sub> | V                                       |                                         |

| V <sub>OL</sub>                         | Output Level (TTL) Output "L" Level Voltage (I <sub>OUT</sub> = +2.0mA for 3.3V, or I <sub>OUT</sub> = +4.2mA for 5.0V)                                                                                          |            | 0.0      | 0.4             | ٧                                       |                                         |

<sup>1.</sup>  $I_{CC1},\,I_{CC3},\,I_{CC4}$  and  $I_{CC6}$  depend on cycle rate.

<sup>2.</sup>  $I_{CC1}$  and  $I_{CC4}$  depend on output loading. Specified values are obtained with the output open.

<sup>3.</sup> Address can be changed once or less while  $\overline{RAS} = V_{IL}$ . In the case of  $I_{CC4}$ , it can be changed once or less when  $\overline{CAS} = V_{IH}$ .

#### **AC Characteristics** ( $T_A$ = 0 to +70°C, $V_{CC}$ = 3.3V $\pm$ 0.3V or $V_{CC}$ = 5.0V $\pm$ 0.5V)

- 1. An initial pause of 200µs is required after power-up followed by 8 RAS only refresh cycles before proper device operation is achieved. In case of using the internal refresh counter, a minimum of 8 CAS before RAS refresh cycles instead of 8 RAS only refresh cycles is required.

- 2. AC measurements assume  $t_T$ =2ns.

- 3.  $V_{IH}(min.)$  and  $V_{IL}(max.)$  are reference levels for measuring timing of input signals. Also, transition times are measured between  $V_{IH}$  and  $V_{II}$ .

- 4. Valid column addresses are A0 through A9.

#### Read, Write, Read-Modify-Write and Refresh Cycles (Common Parameters)

| Cumbal           | Devemater                           |      | -50          |      | 60   | -6R  |      |      | -70      | l luita | Nietes                                  |

|------------------|-------------------------------------|------|--------------|------|------|------|------|------|----------|---------|-----------------------------------------|

| Symbol           | Parameter                           | Min. | Max.         | Min. | Max. | Min. | Max. | Min. | Max.     | Units   | Notes                                   |

| t <sub>RC</sub>  | Random Read or Write Cycle Time     | 84   | _            | 104  | —    | 104  | _    | 124  | <u> </u> | ns      | •••••                                   |

| t <sub>RP</sub>  | RAS Precharge Time                  | 30   |              | 40   |      | 40   |      | 50   | _        | ns      |                                         |

| t <sub>CP</sub>  | CAS Precharge Time                  | 8    | _            | 10   | _    | 10   | _    | 10   | _        | ns      |                                         |

| t <sub>RAS</sub> | RAS Pulse Width                     | 50   | 10K          | 60   | 10K  | 60   | 10K  | 70   | 10K      | ns      | *************************************** |

| t <sub>CAS</sub> | CAS Pulse Width                     | 8    | 10K          | 10   | 10K  | 10   | 10K  | 12   | 10K      | ns      |                                         |

| t <sub>ASR</sub> | Row Address Setup Time              | 0    | <u> </u>     | 0    | —    | 0    | _    | 0    | _        | ns      |                                         |

| t <sub>RAH</sub> | Row Address Hold Time               | 10   |              | 10   | —    | 10   | _    | 10   | _        | ns      |                                         |

| t <sub>ASC</sub> | Column Address Setup Time           | 0    | _            | 0    | _    | 0    | _    | 0    | _        | ns      |                                         |

| t <sub>CAH</sub> | Column Address Hold Time            | 8    | _            | 10   | _    | 10   | _    | 10   | _        | ns      |                                         |

| t <sub>RCD</sub> | RAS to CAS Delay Time               | 14   | 37           | 14   | 45   | 14   | 43   | 14   | 50       | ns      | 1                                       |

| t <sub>RAD</sub> | RAS to Column Address Delay Time    | 12   | 25           | 12   | 30   | 12   | 30   | 12   | 35       | ns      | 2                                       |

| t <sub>RSH</sub> | RAS Hold Time                       | 8    | <u> </u>     | 10   | _    | 10   | _    | 12   | _        | ns      |                                         |

| t <sub>CSH</sub> | CAS Hold Time                       | 38   | _            | 45   | —    | 45   | _    | 50   | _        | ns      |                                         |

| t <sub>CRP</sub> | CAS to RAS Precharge Time           | 5    | <u> </u>     | 5    | —    | 5    | _    | 5    | _        | ns      | ••••••••••                              |

| t <sub>OED</sub> | OE to D <sub>IN</sub> Delay Time    | 13   | <del>-</del> | 15   |      | 15   | _    | 15   | _        | ns      | 3                                       |

| t <sub>DZO</sub> | OE Delay Time from D <sub>IN</sub>  | 0    | _            | 0    | _    | 0    | _    | 0    | _        | ns      | 4                                       |

| t <sub>DZC</sub> | CAS Delay Time from D <sub>IN</sub> | 0    |              | 0    |      | 0    |      | 0    |          | ns      | 4                                       |

| t⊤               | Transition Time (Rise and Fall)     | 2    | 50           | 2    | 50   | 2    | 50   | 2    | 50       | ns      | 5                                       |

Operation within the t<sub>RCD</sub>(max.) limit ensures that t<sub>RAC</sub>(max.) can be met. t<sub>RCD</sub>(max.) is specified as a reference point only. If t<sub>RCD</sub> is greater than the specified t<sub>RCD</sub>(max.) limit, then access time is controlled by t<sub>CAC</sub>.

- 3. Either t<sub>CDD</sub> or t<sub>OED</sub> must be satisfied.

- Either t<sub>DZC</sub> or t<sub>DZO</sub> must be satisfied.

- 5. AC measurements assume t<sub>T</sub>=2ns.

28H4724 SA14-4221-04 Revised 11/96

Operation within the t<sub>RAD</sub>(max.) limit ensures that t<sub>RAD</sub>(max.) can be met. t<sub>RAD</sub>(max.) is specified as a reference point only. If t<sub>RAD</sub> is greater than the specified t<sub>RAD</sub>(max.) limit, then access time is controlled by t<sub>AA</sub>.

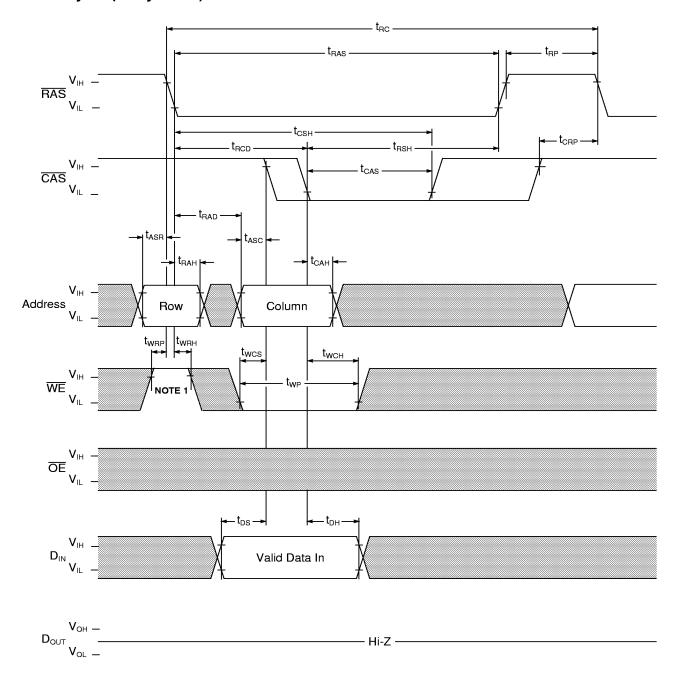

### **Write Cycle**

|                  | Parameter                      |      | -50  |      | /-6R | į.   | -70          |       |                                         |

|------------------|--------------------------------|------|------|------|------|------|--------------|-------|-----------------------------------------|

| Symbol           | Parameter                      | Min. | Max. | Min. | Max. | Min. | Max.         | Units | Notes                                   |

| t <sub>wcs</sub> | Write Command Set Up Time      | 0    | _    | 0    | _    | 0    | _            | ns    | 1                                       |

| t <sub>wch</sub> | Write Command Hold Time        | 7    | _    | 10   | _    | 12   | _            | ns    |                                         |

| t <sub>WP</sub>  | Write Command Pulse Width      | 7    | _    | 10   | _    | 12   |              | ns    |                                         |

| t <sub>RWL</sub> | Write Command to RAS Lead Time | 7    | _    | 10   | _    | 12   |              | ns    |                                         |

| t <sub>CWL</sub> | Write Command to CAS Lead Time | 7    | _    | 10   |      | 12   |              | ns    | *************************************** |

| t <sub>DS</sub>  | D <sub>IN</sub> Setup Time     | 0    | _    | 0    | _    | 0    | <del>-</del> | ns    | 2                                       |

| t <sub>DH</sub>  | D <sub>IN</sub> Hold Time      | 7    | _    | 10   | _    | 12   | _            | ns    | 2                                       |

<sup>1.</sup> t<sub>WCS</sub>, t<sub>RWD</sub>, t<sub>CWD</sub> and t<sub>AWD</sub> are not restrictive operating parameters. They are included in the data sheet as electrical characteristics only. If t<sub>WCS</sub> ≥ t<sub>WCS</sub> (min), the cycle is an early write cycle and the data pin will remain open circuit (high impedance) through the entire cycle. If t<sub>RWD</sub> ≥ t<sub>RWD</sub> (min), t<sub>CWD</sub> ≥ t<sub>CWD</sub> (min) and t<sub>AWD</sub> ≥ t<sub>AWD</sub> (min), the cycle is a Read-Modify-Write cycle and the data out will contain data read from the selected cell. If neither of the above sets of conditions are satisfied, the condition of the data out (at access time) is indeterminate.

<sup>2.</sup> These parameters are referenced to CAS leading edge in early write cycles and to WE leading edge in Read-Modify-Write cycles.

#### **Read Cycle**

| C. mahal         | Parameter                                   | -        | 50   | -        | 60   | -        | 6R   | -    | 70   | Units | Notes   |

|------------------|---------------------------------------------|----------|------|----------|------|----------|------|------|------|-------|---------|

| Symbol           | raiametei                                   | Min.     | Max. | Min.     | Max. | Min.     | Max. | Min. | Max. | Units | notes   |

| t <sub>RAC</sub> | Access Time from RAS                        | <u> </u> | 50   | <u> </u> | 60   | <u> </u> | 60   | _    | 70   | ns    | 1, 2, 3 |

| t <sub>CAC</sub> | Access Time from CAS                        | _        | 13   | _        | 15   | <u> </u> | 17   | —    | 20   | ns    | 1, 3    |

| t <sub>AA</sub>  | Access Time from Address                    | _        | 25   | _        | 30   | _        | 30   | _    | 35   | ns    | 2, 3    |

| t <sub>OEA</sub> | Access Time from OE                         | _        | 13   | _        | 15   | <u> </u> | 17   | —    | 20   | ns    | 3       |

| t <sub>RCS</sub> | Read Command Setup Time                     | 0        | _    | 0        |      | 0        | _    | 0    |      | ns    |         |

| t <sub>RCH</sub> | Read Command Hold Time to CAS               | 0        | _    | 0        | _    | 0        | _    | 0    | _    | ns    | 4       |

| t <sub>RRH</sub> | Read Command Hold Time to RAS               | 0        | _    | 0        | _    | 0        | _    | 0    | _    | ns    | 4       |

| t <sub>RAL</sub> | Column Address to RAS Lead Time             | 25       | _    | 30       | _    | 30       | —    | 35   | _    | ns    |         |

| t <sub>CLZ</sub> | CAS to Output in Low-Z                      | 0        | _    | 0        | _    | 0        | _    | 0    | _    | ns    | 3       |

| t <sub>OFF</sub> | Output Buffer Turn-Off Delay                | _        | 13   | _        | 15   | <u> </u> | 15   | _    | 15   | ns    | 5, 6    |

| t <sub>CDD</sub> | CAS to D <sub>IN</sub> Delay Time           | 13       | _    | 15       | _    | 15       | _    | 15   | _    | ns    | 7       |

| t <sub>OEZ</sub> | Output Buffer Turn-Off Delay from OE        | _        | 13   | _        | 15   | _        | 15   | —    | 15   | ns    | 5       |

| t <sub>OES</sub> | OE Setup Time Prior to CAS                  | 5        | _    | 5        |      | 5        | _    | 5    |      | ns    |         |

| t <sub>ORD</sub> | OE Setup Time Prior to RAS (Hidden Refresh) | 0        | _    | 0        | _    | 0        | _    | 0    |      | ns    |         |

- Operation within the t<sub>RCD</sub>(max.) limit ensures that t<sub>RAC</sub>(max.) can be met. t<sub>RCD</sub>(max.) is specified as a reference point only. If t<sub>RCD</sub> is greater than the specified t<sub>RCD</sub>(max.) limit, then access time is controlled by t<sub>CAC</sub>.

- Operation within the t<sub>RAD</sub>(max.) limit ensures that t<sub>RAD</sub>(max.) can be met. t<sub>RAD</sub>(max.) is specified as a reference point only. If t<sub>RAD</sub> is greater than the specified t<sub>RAD</sub>(max.) limit, then access time is controlled by t<sub>AA</sub>.

- 3. Measured with the specified current load and 100pF at  $V_{OL}$  = 0.8V and  $V_{OH}$  = 2.0V.

- 4. Either t<sub>RCH</sub> or t<sub>RRH</sub> must be satisfied for a read cycle.

- 5. t<sub>OFF</sub> (max) and t<sub>OEZ</sub> (max) define the time at which the output achieves the open circuit condition and are not referenced to output voltage levels.

- 6.  $t_{OFF}$  is referenced from the rising edge of  $\overline{RAS}$  or  $\overline{CAS}$ , which ever is last.

- 7. Either t<sub>CDD</sub> or t<sub>OED</sub> must be satisfied.

### **Read-Modify-Write Cycle**

| Cymphal          | Parameter                       | -50  |      | -60  |      | -6R  |      | -70  |      | Units | Notes |

|------------------|---------------------------------|------|------|------|------|------|------|------|------|-------|-------|

| Symbol           | rarameter                       | Min. | Max. | Min. | Max. | Min. | Max. | Min. | Max. | Units | Notes |

| t <sub>RWC</sub> | Read-Modify-Write Cycle Time    | 115  | _    | 135  | _    | 135  |      | 162  |      | ns    |       |

| t <sub>RWD</sub> | RAS to WE Delay Time            | 67   | _    | 79   |      | 79   | _    | 94   |      | ns    | 1     |

| t <sub>CWD</sub> | CAS to WE Delay Time            | 30   | _    | 34   | _    | 36   | _    | 44   | _    | ns    | 1     |

| t <sub>AWD</sub> | Column Address to WE Delay Time | 42   | _    | 49   |      | 49   |      | 59   |      | ns    | 1     |

| t <sub>OEH</sub> | OE Command Hold Time            | 7    | _    | 10   |      | 10   |      | 12   |      | ns    |       |

<sup>1.</sup> t<sub>WCS</sub>, t<sub>RWD</sub>, t<sub>CWD</sub> and t<sub>AWD</sub> are not restrictive operating parameters. They are included in the data sheet as electrical characteristics only. If t<sub>WCS</sub> ≥ t<sub>WCS</sub> (min), the cycle is an early write cycle and the data pin will remain open circuit (high impedance) through the entire cycle. If t<sub>RWD</sub> ≥ t<sub>RWD</sub> (min), t<sub>CWD</sub> ≥ t<sub>CWD</sub> (min) and t<sub>AWD</sub> ≥ t<sub>AWD</sub> (min), the cycle is a Read-Modify-Write cycle and the data out will contain data read from the selected cell. If neither of the above sets of conditions are satisfied, the condition of the data out (at access time) is indeterminate.

### **Extended Data Out (Hyper Page) Mode Cycle**

| Symbol             | Parameter                                             | -50  |      | -60 / -6R |      | -70  |          | 1111  | NI-4  |

|--------------------|-------------------------------------------------------|------|------|-----------|------|------|----------|-------|-------|

|                    |                                                       | Min. | Max. | Min.      | Мах. | Min. | Max.     | Units | Notes |

| t <sub>HCAS</sub>  | EDO (Hyper Page) Mode CAS Pulse Width                 | 8    | 10K  | 10        | 10K  | 12   | 10K      | ns    |       |

| t <sub>HPC</sub>   | EDO (Hyper Page) Mode Cycle Time (Read/Write)         | 20   | _    | 25        | _    | 30   | _        | ns    |       |

| t <sub>HPRWC</sub> | EDO (Hyper Page) Mode Read Modify Write Cycle<br>Time | 51   | _    | 60        | _    | 72   | _        | ns    |       |

| t <sub>DOH</sub>   | Data-out Hold Time from CAS                           | 5    | _    | 5         | _    | 5    | _        | ns    |       |

| t <sub>WHZ</sub>   | Output buffer Turn-Off Delay from WE                  | 0    | 10   | 0         | 10   | 0    | 15       | ns    |       |

| t <sub>WPZ</sub>   | WE Pulse Width to Output Disable at CAS High          | 7    | _    | 10        | _    | 10   | _        | ns    |       |

| t <sub>CPRH</sub>  | RAS Hold Time from CAS Precharge                      | 30   | _    | 35        | _    | 40   | _        | ns    |       |

| t <sub>CPA</sub>   | Access Time from CAS Precharge                        | _    | 28   | _         | 35   | _    | 40       | ns    | 1     |

| t <sub>RASP</sub>  | EDO (Hyper Page) Mode RAS Pulse Width                 | 50   | 200K | 60        | 200K | 70   | 200K     | ns    |       |

| t <sub>OEP</sub>   | OE Precharge                                          | 5    | _    | 5         | _    | 5    | _        | ns    |       |

| t <sub>OEHC</sub>  | OE High Hold Time from CAS High                       | 5    | _    | 5         | _    | 5    | <b>—</b> | ns    |       |

<sup>1.</sup> Measured with the specified current load and 100pF at  $V_{OL} = 0.8V$  and  $V_{OH} = 2.0V$ .

### Refresh Cycle

| C                | Parameter                                        | -50  |      | -60 / -6R |      | -70  |      |       |       |

|------------------|--------------------------------------------------|------|------|-----------|------|------|------|-------|-------|

| Symbol           |                                                  | Min. | Max. | Min.      | Max. | Min. | Max. | Units | Notes |

| t <sub>CSR</sub> | CAS Setup Time<br>(CAS before RAS Refresh Cycle) | 5    | _    | 5         | _    | 5    | _    | ns    |       |

| t <sub>CHR</sub> | CAS Hold Time<br>(CAS before RAS Refresh Cycle)  | 10   |      | 10        | _    | 10   | —    | ns    |       |

| twap             | WE Setup Time<br>(CAS before RAS Refresh Cycle)  | 10   | _    | 10        | _    | 10   | _    | ns    |       |

| t <sub>wa</sub>  | WE Hold Time<br>(CAS before RAS Cycle)           | 10   | _    | 10        | _    | 10   | _    | ns    |       |

| t <sub>RPC</sub> | RAS Precharge to CAS Hold Time                   | 5    |      | 5         |      | 5    | _    | ns    |       |

### Self Refresh Cycle - Low Power version only

| C. makal          | Parameter                                                   | -50  |      | -60  |      | -70  |      | 11-:1- | NI-1  |

|-------------------|-------------------------------------------------------------|------|------|------|------|------|------|--------|-------|

| Symbol            |                                                             | Min. | Max. | Min. | Max. | Min. | Max. | Units  | Notes |

| t <sub>RASS</sub> | RAS Pulse Width<br>During Self Refresh Cycle                | 100  | —    | 100  | _    | 100  | _    | μs     | 1     |

| t <sub>RPS</sub>  | RAS Precharge Time<br>During Self Refresh Cycle             | 89   | —    | 104  | _    | 124  | _    | ns     | 1     |

| t <sub>CHS</sub>  | CAS Hold Time From RAS Rising<br>During Self Refresh Cycle  | -50  |      | -50  |      | -50  | _    | ns     | 1, 2  |

| t <sub>CHD</sub>  | CAS Hold Time From RAS Falling<br>During Self Refresh Cycle | 350  | _    | 350  | _    | 350  | _    | μs     | 1, 2  |

<sup>1.</sup> When using Self Refresh mode, the following refresh operations must be performed to ensure proper DRAM operation:

If row addresses are being refreshed in an EVENLY DISTRIBUTED manner over the refresh interval using CBR refresh cycles, then only one CBR cycle must be performed immediately after exit from Self Refresh.

If row addresses are being refreshed in any other manner (ROR- Distributed/Burst: or CBR-Burst) over the refresh interval, then

If row addresses are being refreshed in any other manner (ROR- Distributed/Burst; or CBR-Burst) over the refresh interval, then a full set of row refreshes must be performed immediately before entry to and immediately after exit from Self Refresh.

#### Refresh

| SYMBOL          | Parameter      |            | -50  |      | -60 / -6R |      | -70  |      | Units  | Notes |

|-----------------|----------------|------------|------|------|-----------|------|------|------|--------|-------|

| STIVIBOL        |                |            | Min. | Max. | Min.      | Max. | Min. | Max. | UIIIIS | Mores |

|                 | Refresh Period | SP version | _    | 32   | _         | 32   | _    | 32   | ms     | 1     |

| ₹REF            |                | LP version | _    | 128  | <u>—</u>  | 128  |      | 128  |        |       |

| 1. 2048 cycles. |                |            |      |      |           |      |      |      |        |       |

<sup>2.</sup> If  $t_{RASS} > t_{CHD}$  (min) then  $t_{CHD}$  applies. If  $t_{RASS} \le t_{CHD}$  (min) then  $t_{CHS}$  applies.

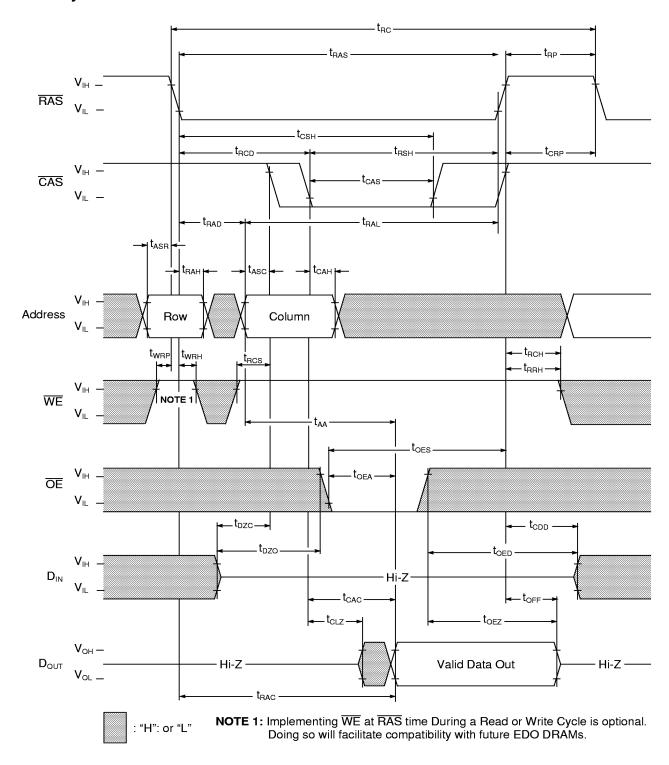

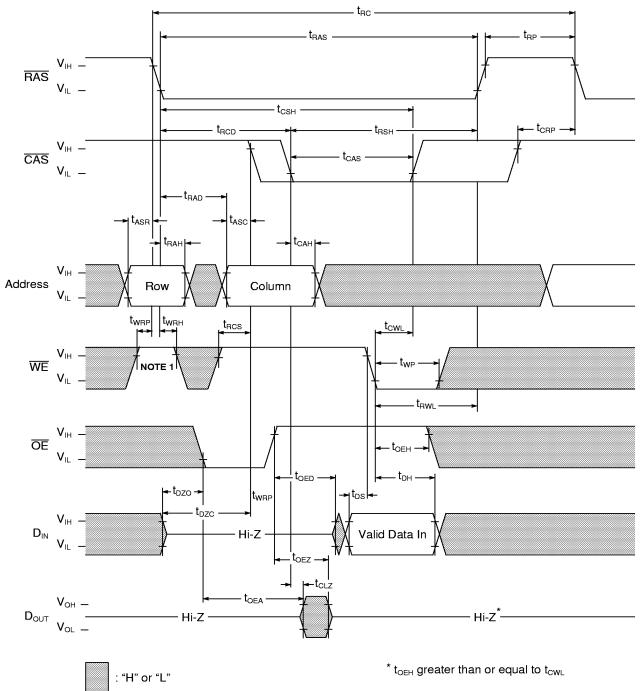

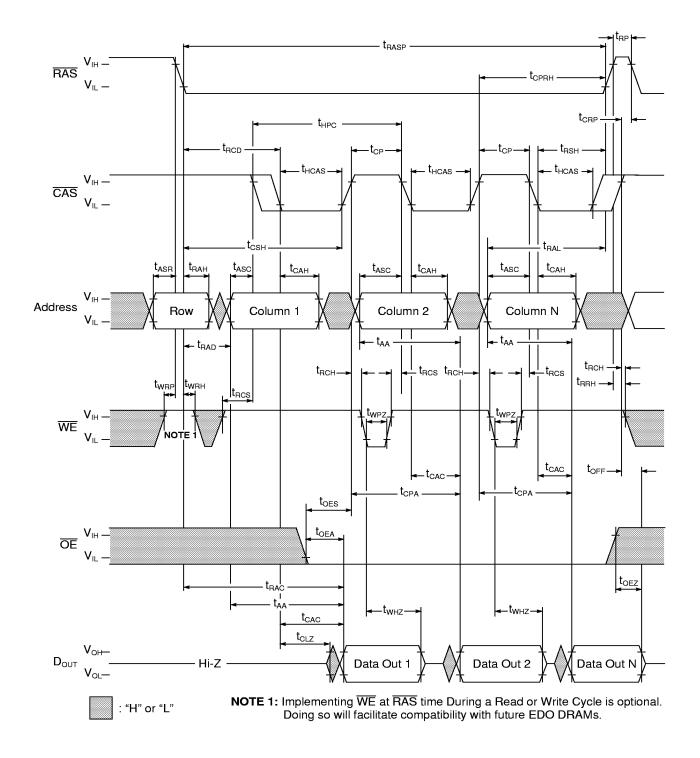

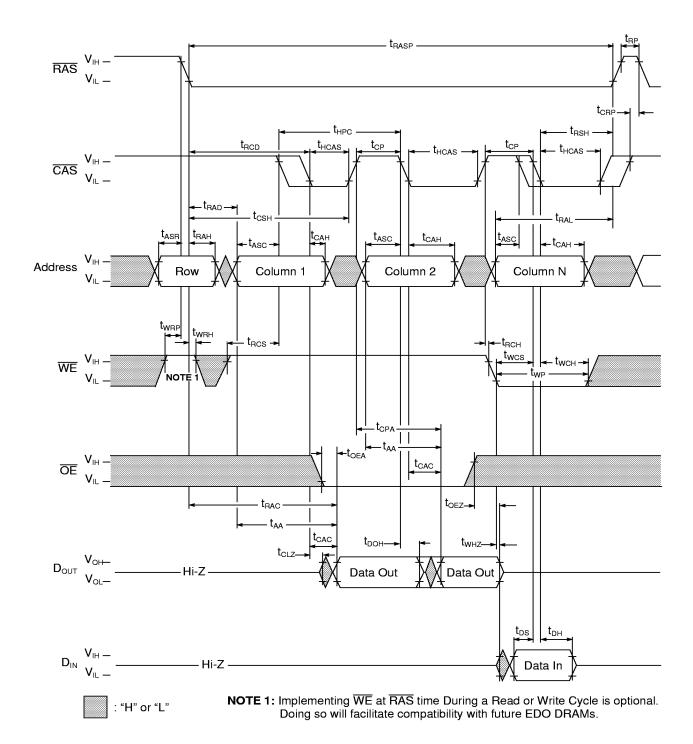

# **Read Cycle**

©IBM Corporation. All rights reserved.

Use is further subject to the provisions at the end of this document.

28H4724 SA14-4221-04 Revised 11/96

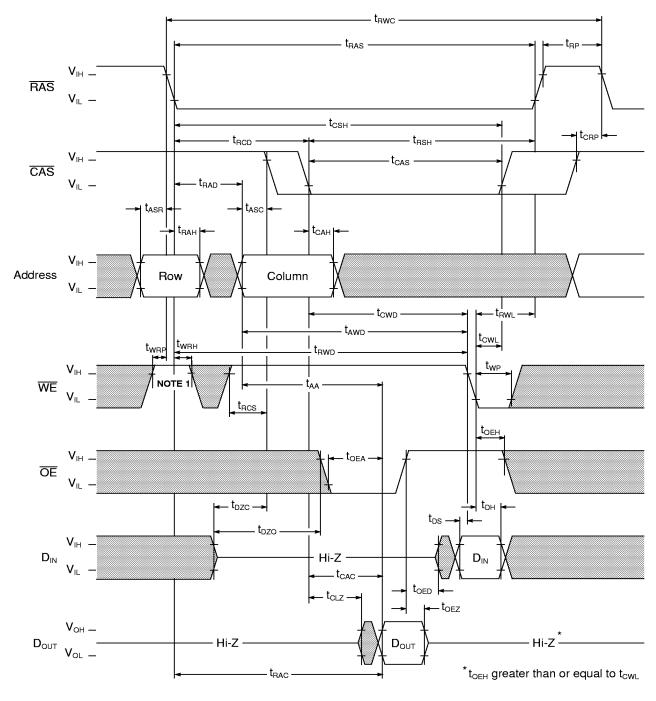

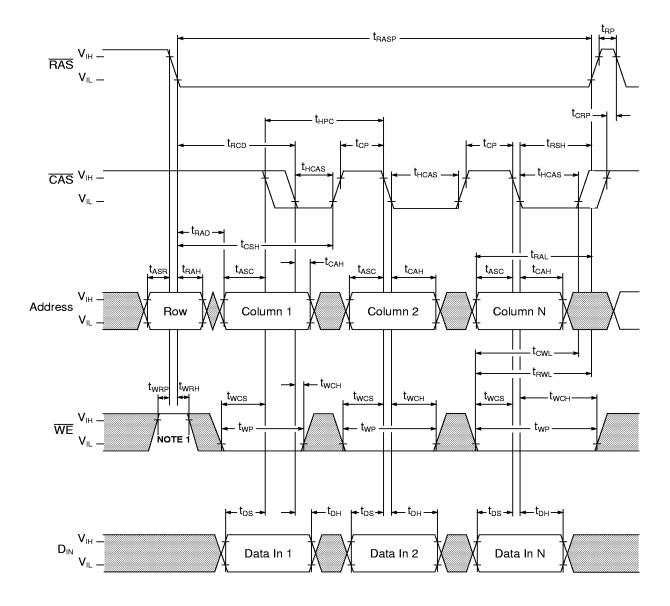

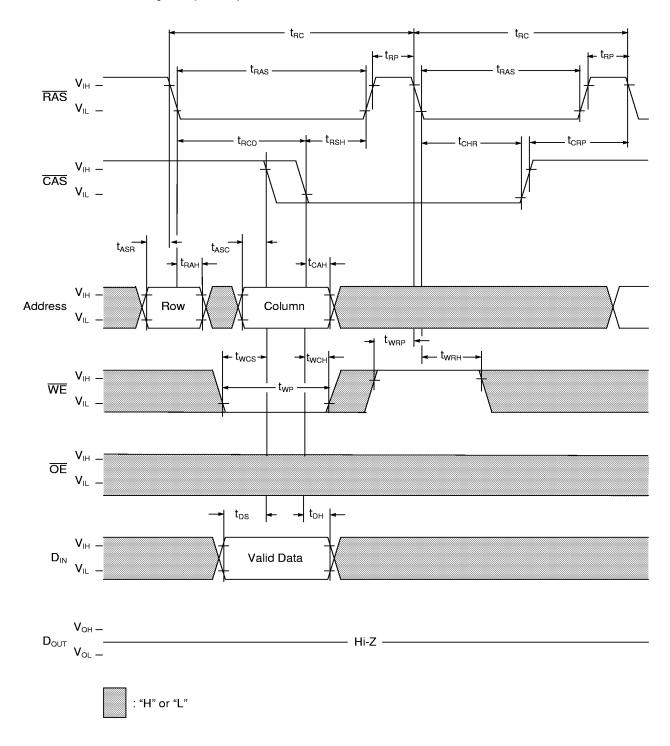

# Write Cycle (Early Write)

: "H" or "L"

**NOTE 1:** Implementing  $\overline{\text{WE}}$  at  $\overline{\text{RAS}}$  time During a Read or Write Cycle is optional. Doing so will facilitate compatibility with future EDO DRAMs.

28H4724 SA14-4221-04 Revised 11/96

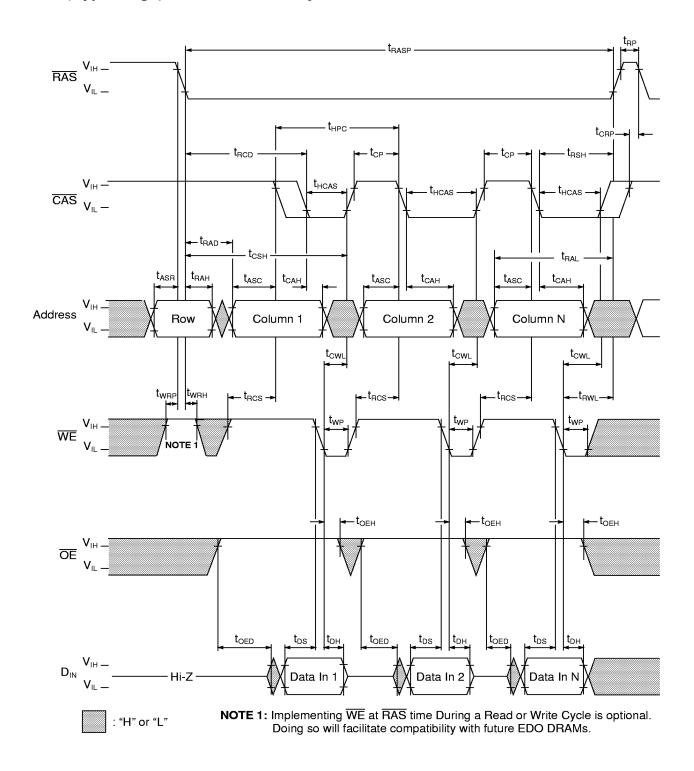

# Write Cycle (Delayed Write)

**NOTE 1:** Implementing WE at RAS time During a Read or Write Cycle is optional. Doing so will facilitate compatibility with future EDO DRAMs.

©IBM Corporation. All rights reserved.

Use is further subject to the provisions at the end of this document.

28H4724 SA14-4221-04 Revised 11/96

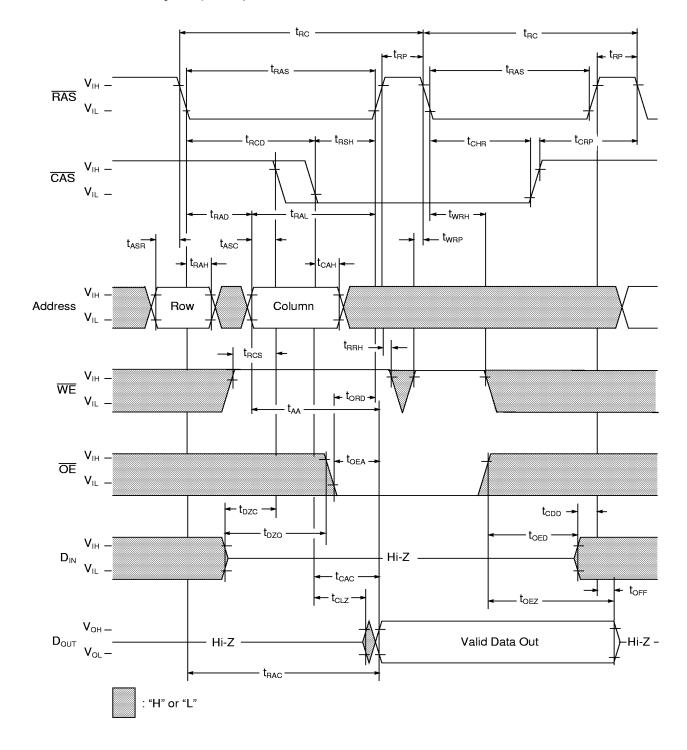

## **Read-Modify-Write Cycle**

: "H" or "L"

NOTE 1: Implementing WE at RAS time During a Read or Write Cycle is optional.

Doing so will facilitate compatibility with future EDO DRAMs.

28H4724 SA14-4221-04 Revised 11/96

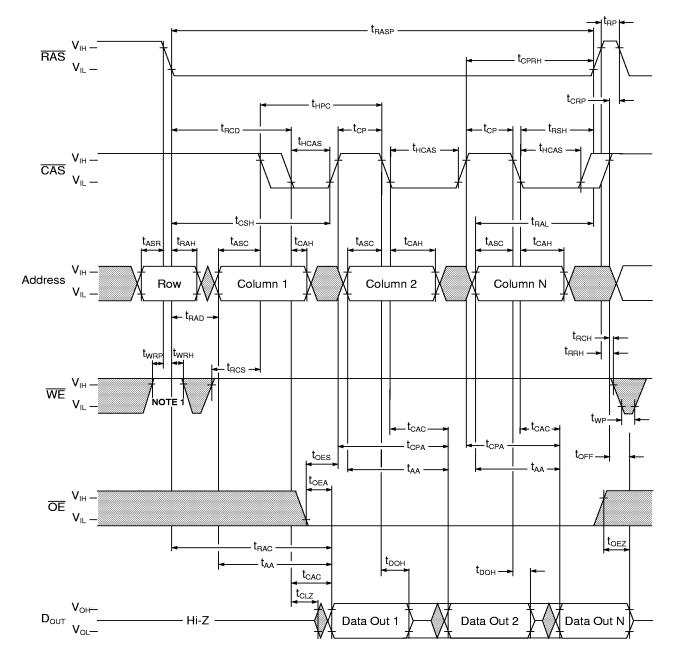

# **EDO (Hyper Page) Mode Read Cycle**

: "H" or "L"

NOTE 1: Implementing WE at RAS time During a Read or Write Cycle is optional.

Doing so will facilitate compatibility with future EDO DRAMs.

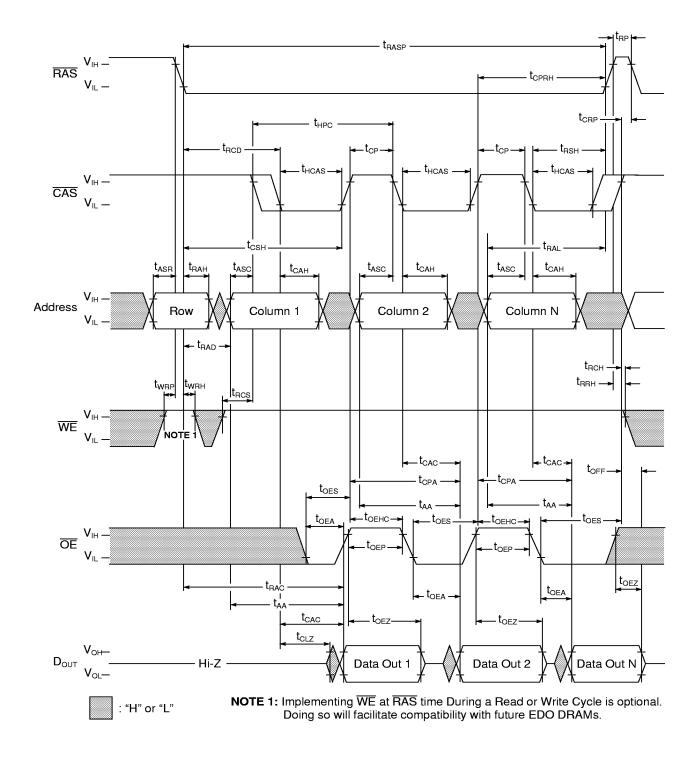

## **EDO (Hyper Page) Mode Read Cycle (OE Control)**

28H4724 SA14-4221-04 Revised 11/96

# **EDO (Hyper Page) Mode Read Cycle (WE Control)**

©IBM Corporation. All rights reserved.

Use is further subject to the provisions at the end of this document.

28H4724 SA14-4221-04 Revised 11/96

## **EDO (Hyper Page) Mode Early Write Cycle**

**NOTE 1:** Implementing WE at RAS time During a Read or Write Cycle is optional. Doing so will facilitate compatibility with future EDO DRAMs.

OE = Don't care

28H4724 SA14-4221-04 Revised 11/96

# **EDO (Hyper Page) Mode Late Write Cycle**

©IBM Corporation. All rights reserved.

Use is further subject to the provisions at the end of this document.

28H4724 SA14-4221-04 Revised 11/96

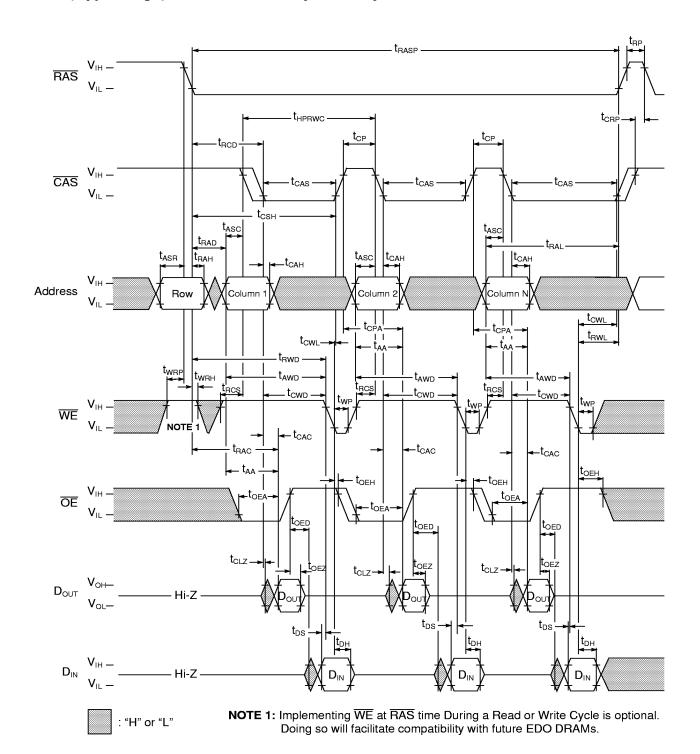

## **EDO (Hyper Page) Mode Read Modify Write Cycle**

28H4724 SA14-4221-04 Revised 11/96

## **EDO (Hyper Page) Mode Read and Write Cycle**

©IBM Corporation. All rights reserved.

Use is further subject to the provisions at the end of this document.

SA14-4221-04 Revised 11/96

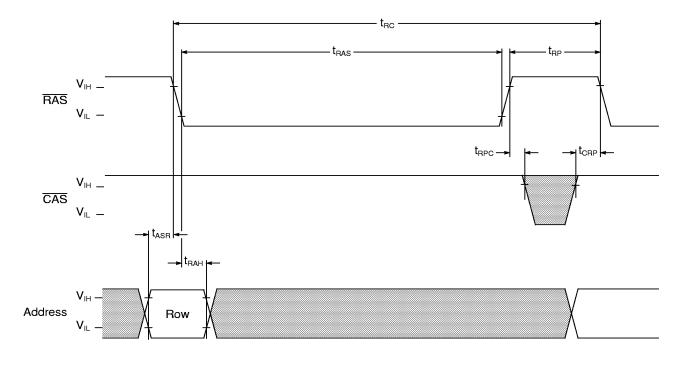

# **RAS** Only Refresh Cycle

: "H" or "L"

NOTE :  $\overline{\text{WE}}$ ,  $\overline{\text{OE}}$  and  $D_{\text{IN}}$  are "H" or "L"

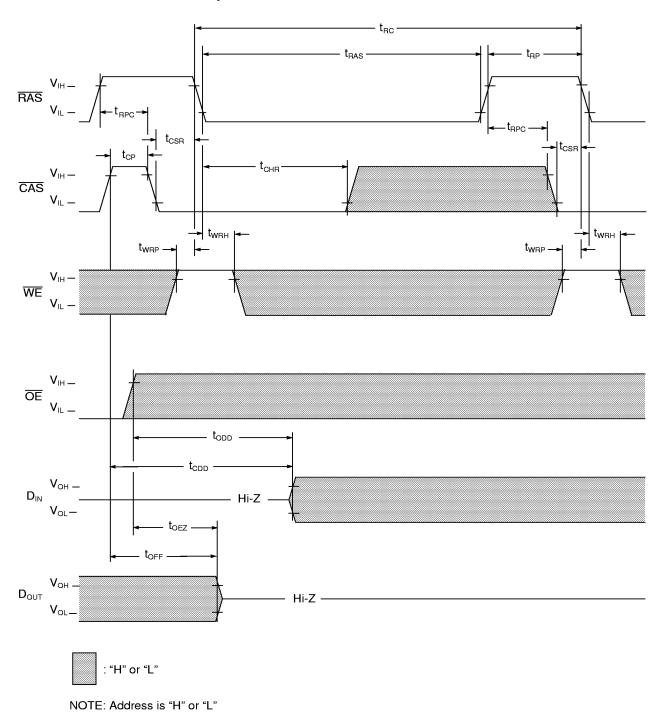

# **CAS** Before **RAS** Refresh Cycle

©IBM Corporation. All rights reserved.

Use is further subject to the provisions at the end of this document.

28H4724 SA14-4221-04 Revised 11/96

# Hidden Refresh Cycle (Read)

28H4724 SA14-4221-04 Revised 11/96

# **Hidden Refresh Cycle (Write)**

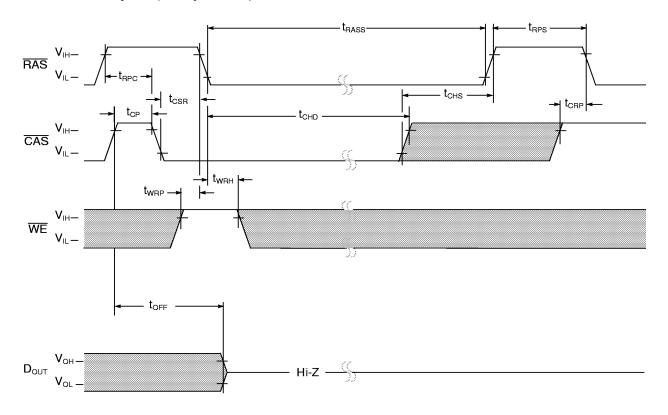

## Self Refresh Cycle (Sleep Mode) - Low Power version only

#### NOTES:

- 1. Address and  $\overline{OE}$  are "H" or "L"

- 2. Once RAS (min) is provided and RAS remains low, the DRAM will be in Self Refresh, commonly known as "Sleep Mode."

- $\begin{array}{ll} 3. \ \ \mbox{If} \ t_{\mbox{\tiny RASS}} > t_{\mbox{\tiny CHD}} \ \mbox{(min) then} \ t_{\mbox{\tiny CHD}} \ \mbox{applies}. \\ \ \mbox{If} \ t_{\mbox{\tiny RASS}} \leq t_{\mbox{\tiny CHD}} \ \mbox{(min) then} \ t_{\mbox{\tiny CHS}} \ \mbox{applies}. \\ \end{array}$

28H4724 SA14-4221-04 Revised 11/96

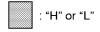

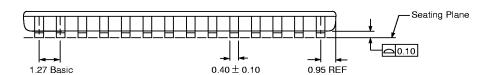

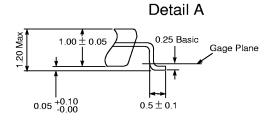

### Package Dimensions (400 mil; 28/28 lead; Thin Small Outline Package)

NOTE: All dimensions are in millimeters; Package diagrams are not drawn to scale

## **Revision Log**

| Revision | Contents Of Modification                                                                                                                                     |  |  |  |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 11/15/95 | Initial Release                                                                                                                                              |  |  |  |  |  |  |

|          | <ol> <li>The Low Power and Standard Power Specifications were combined. ES# 43G9060 and ES# 28H4724 were<br/>combined into ES# 28H4724.</li> </ol>           |  |  |  |  |  |  |

|          | 2. Added Die Rev E part numbers.                                                                                                                             |  |  |  |  |  |  |

|          | 3. A -6R speed sort was added, with the following differences over the -60 speed sort:                                                                       |  |  |  |  |  |  |

|          | <ul> <li>t<sub>CAC</sub> was increased from 15ns to 17ns for the -6R speed sort</li> </ul>                                                                   |  |  |  |  |  |  |

|          | <ul> <li>t<sub>RCD</sub> (max) was decreased from 45ns to 43ns for the -6R speed sort.</li> </ul>                                                            |  |  |  |  |  |  |

| 12/10/95 | <ul> <li>t<sub>CWD</sub> was increased from 34ns to 36ns for the -6R speed sort.</li> </ul>                                                                  |  |  |  |  |  |  |

|          | - t <sub>OEA</sub> was increased from 15ns to 17ns for the -6R speed sort.                                                                                   |  |  |  |  |  |  |

|          | 4. t <sub>CHD</sub> was added to the Self Refresh Cycle with a value of 350μs for all speed sorts.                                                           |  |  |  |  |  |  |

|          | <ol> <li>The Self Refresh timing diagram was changed to allow CAS to go high t<sub>CHD</sub> (350μs) after RAS falls entering a<br/>Self Refresh.</li> </ol> |  |  |  |  |  |  |

|          | 6. The CBR timing diagram was changed to allow CAS to remain low for back-to-back CBR cycles.                                                                |  |  |  |  |  |  |

|          | 7. WE for the Hidden Refresh Write cycle in the Truth Table was changed from "L" to "H".                                                                     |  |  |  |  |  |  |

|          | 1. I <sub>CC2</sub> was changed from 2mA to 1mA.                                                                                                             |  |  |  |  |  |  |

|          | 2. $I_{I(L)}$ and $I_{O(L)}$ were altered from +/- 10uA to +/- 5uA.                                                                                          |  |  |  |  |  |  |

|          | 3. $t_{RC}$ was changed from 89ns to 84ns for the -50 speed sort.                                                                                            |  |  |  |  |  |  |

|          | 4. t <sub>CSH</sub> changed from 45ns to 38ns, 50ns to 45ns, and 55ns to 50ns for the -50, -60, and -70 speed sorts, respectively.                           |  |  |  |  |  |  |

| 09/01/96 | 5. $t_T$ was initially at a max of 30ns. It has been modified to 50ns for all speed sorts.                                                                   |  |  |  |  |  |  |

|          | 6. t <sub>CPA</sub> was decreased from 30ns to 28ns for the -50 speed sort.                                                                                  |  |  |  |  |  |  |

|          | 7. t <sub>RASP</sub> max of 125K was raised to 200K for all speed sorts.                                                                                     |  |  |  |  |  |  |

|          | 8. t <sub>OEP</sub> was changed from 10ns to 5ns for all speed sorts.                                                                                        |  |  |  |  |  |  |

|          | 9. t <sub>OEHC</sub> was also lowered from 10ns to 5ns for all speed sorts.                                                                                  |  |  |  |  |  |  |

|          | 10. $t_{RP}$ was changed from 35ns to 30ns for the -50 speed sort.                                                                                           |  |  |  |  |  |  |