# **Document Title**

## Multi-Chip Package MEMORY

64M Bit (8Mx8/4Mx16) Dual Bank NOR Flash / 128M Bit (8Mx16) NAND Flash / 32M Bit (2Mx16) UtRAM

# **Revision History**

| <u>Revision No.</u> | History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Draft Date       | <u>Remark</u> |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|

| 0.0                 | Initial Draft                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | March 20, 2002   | Preliminary   |

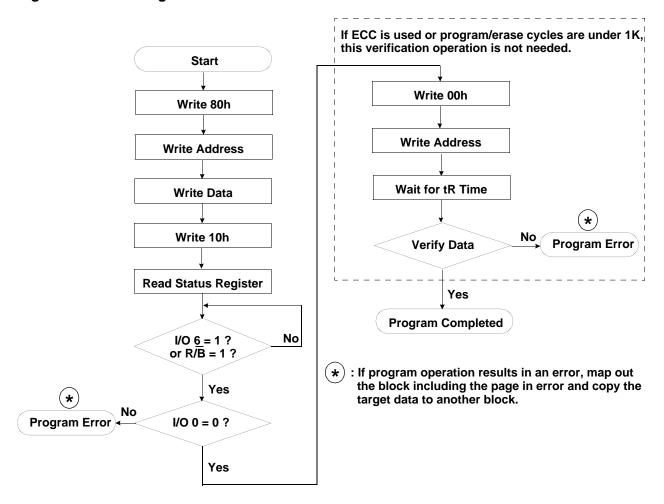

| 0.1                 | Inserted No ECC condition in NAND Flash<br>• Endurance (1page)<br>: 1,000 Program/Erase Cycles Maximum without ECC<br>• Program Flow (39page)<br>: Excluded "Read Verify" step after programming in this condition                                                                                                                                                                                                                                                                                                                                                                                                                              | March 28, 2002   | Preliminary   |

| 0.2                 | <common><br/>Revised TBIAS(43page)<br/>• from "-25 to 85" to "-40 to 125"<br/>Revised VIL(43page)<br/>• from max. 0.6V to max. 0.5V<br/>Revised VOH(43page)<br/>• from min. 2.4V to min. 2.3V<br/>Revised IOL(43page)<br/>• from 0.1mA to max. 2.1mA<br/>Revised IOH(43page)<br/>• from -0.1mA to max1.0mA</common>                                                                                                                                                                                                                                                                                                                             | March 28, 2002   | Preliminary   |

| 0.3                 | <nand><br/>Revised the internal voltage that disables all functions(37page)<br/>• from 2V to 1.3V<br/>Revised power-up and power-down recovery time(37page)<br/>• from min. 1µs to min. 10µs<br/>Revised write cycle time(tWC)(59page)<br/>• from 50ns to min. 45ns<br/>Combined ALE to RE Delay in ID read and in Read cycle(59page)<br/>• from min. 20ns and 50ns to min. 10ns<br/>Revised RE Access Time(tREA)(59page)<br/>• from max. 35ns to max. 30ns<br/>Excluded min. value of RE High to Output Hi-Z(tREH)(59page)<br/>Inserted RE or CE<sub>F</sub> High to Output Hold(toH) with min. 15ns(59page)<br/>Revised timing diagram</nand> | June 17, 2002    | Final         |

| 1.0                 | Finalize                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | October 15, 2002 | Final         |

| 1.1                 | Revised <nor><br/>- Release the stand-by current from typ. 5uA(max. 18uA) to typ.<br/>10uA(max. 30uA).</nor>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | June 18, 2003    | Final         |

| 1.11                | Revised <nand><br/>- Corrected Some typos in the timing diagram</nand>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | August 14, 2003  | Final         |

Note : For more detailed features and specifications including FAQ, please refer to Samsung's web site. http://samsungelectronics.com/semiconductors/products/products\_index.html

The attached datasheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the right to change the specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions about device. If you have any questions, please contact the SAMSUNG branch office near you.

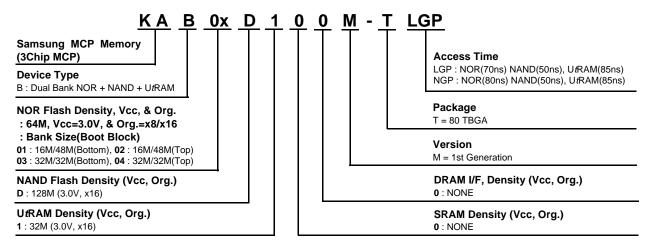

# KAB0xD100M - TxGP

# Multi-Chip Package MEMORY

#### 64M Bit (8Mx8/4Mx16) Dual Bank NOR Flash / 128M Bit (8Mx16) NAND Flash / 32M Bit (2Mx16) UtRAM **GENERAL DESCRIPTION FEATURES**

- Power Supply Voltage : 2.7V~3.1V

- Organization

- NOR Flash : 8.388.608 x 8 bit / 4.194.304 x 16 bit

- NAND Flash : (8M + 256K)bit x 16bit

- UtRAM : 2Mbit x 16 bit

- Access Time

- NOR Flash : 70ns(Max.)

- NAND Flash : Random : 10us(Max.), Serial : 50ns(Min.)

- UtRAM : 85ns

- Power Consumption (typical value)

- NOR Flash Read Current : 14mA (@5MHz) Program/Erase Current: 15mA Read while Program or Read while Erase : 35mA Standby Mode/Autosleep Mode : 10µA

- NAND Flash Read Current : 10mA(@20MHz) Program/Erase Current : 10mA Standby Current : 10µA

- UtRAM Operating Current : 30mA Standby Current : 80µA

- NOR Flash Secode(Security Code) Block : Extra 64KB Block

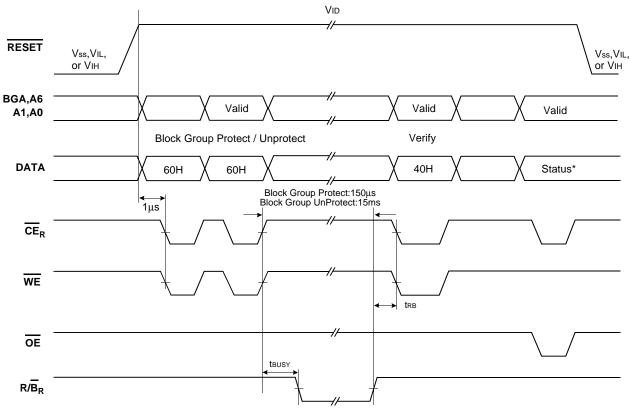

- NOR Flash Block Group Protection / Unprotection

- NOR Flash Bank Size: 16Mb / 48Mb, 32Mb / 32Mb

- NAND Flash Automatic Program and Erase

- Page Program: (256 + 8)Word, Block Erase: (8K + 256)Word NAND Flash Fast Write Cycle Time

- Program time : 200µs(Typ.) Block Erase Time : 2ms(Typ.)

- Endurance NOR: 100,000 Program/Erase Cycles Minimum NAND : 100,000 Program/Erase Cycles Minimum with ECC : 1,000 Program/Erase Cycles Maximum without ECC

- Data Retention : 10 years

- Operating Temperature : -25°C ~ 85°C

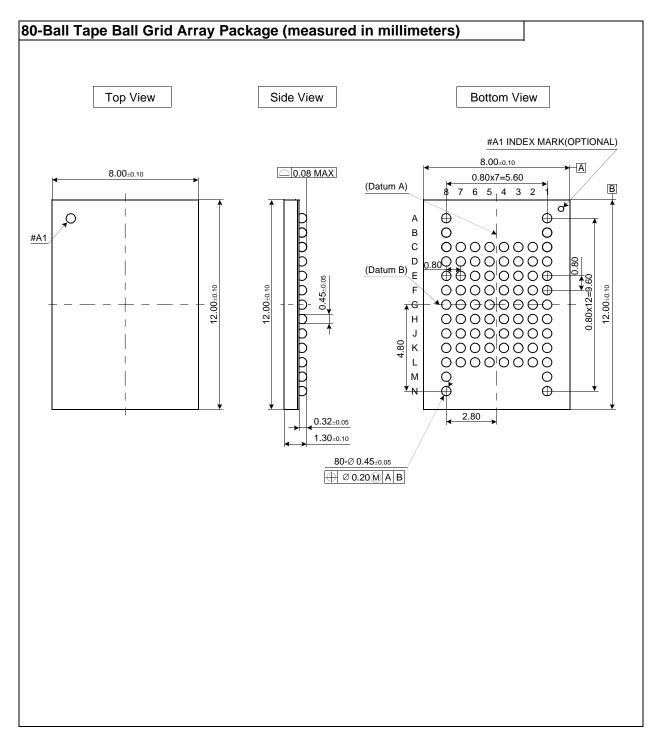

- Package : 80 Ball TBGA Type 8 x 12mm, 0.8 mm pitch

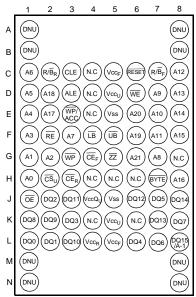

#### **BALL CONFIGURATION**

80 Ball TBGA, 0.8mm Pitch Top View (Ball Down)

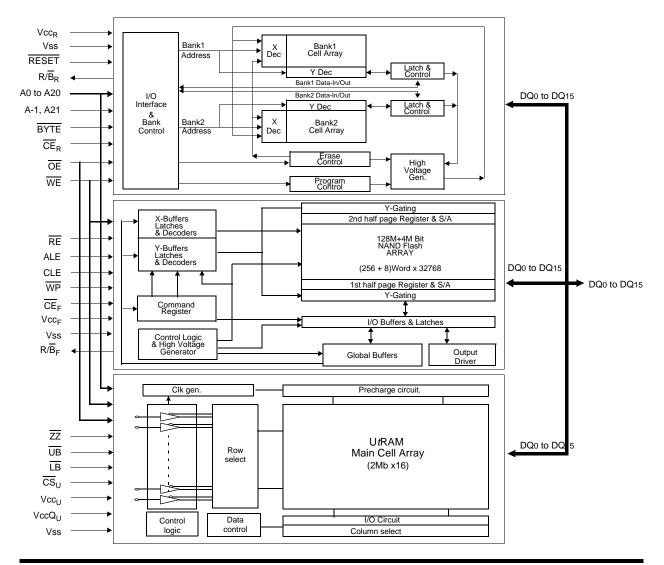

The KAB0xD100M featuring single 3.0V power supply is a Multi Chip Package Memory which combines 64Mbit NOR Flash, 128Mbit NAND Flash and 32Mbit Unit Transistor CMOS RAM. 64Mbit NOR Flash memory is organized as 8M x8 or 4M x16 bit, 128Mbit NAND Flash memory is organized as 8M x16 bit and 32Mbit UtRAM is organized as 2M x16 bit. The memory architecture of NOR Flash memory is designed to divide its memory arrays into 135 blocks and this provides highly flexible erase and program capability. This device is capable of reading data from one bank while programming or erasing in the other bank with dual bank organization. NOR Flash memory performs a program operation in units of 8 bits (Byte) or 16 bits (Word) and erases in units of a block. Single or multiple blocks can be erased. The block erase operation is completed for typically 0.7sec.

In 128Mbit NAND Flash a 256-word page program can be typically achieved within 200µs and an 8K-word block erase can be typically achieved within 2ms. In serial read operation, a byte can be read by 50ns. DQ pins serve as the ports for address and data input/output as well as command inputs. The KAB0xD100M is suitable for the memory of mobile communication system to reduce not only mount area but also power consumption. This device is available in 80-ball TBGA package.

#### BALL DESCRIPTION

| Ball Name        | Description                                             |

|------------------|---------------------------------------------------------|

| A0 to A20        | Address Input Balls (NOR, U <i>t</i> RAM)               |

| A-1, A21         | Address Input Balls (NOR)                               |

| DQ0 to DQ7       | Data Input/Output Balls (Common)                        |

| DQ8 to DQ15      | Data Input/Output Balls (Common)                        |

| Vcc <sub>R</sub> | Power Supply (NOR)                                      |

| Vcc <sub>F</sub> | Power Supply (NAND)                                     |

| Vcc <sub>U</sub> | Power Supply (UtRAM)                                    |

| VccQU            | Data Output Buffer Power (UtRAM)                        |

| Vss              | Ground (Common)                                         |

| WE               | Write Enable (Common)                                   |

| OE               | Output Enable (NOR,UtRAM)                               |

| CER              | Chip Enable (NOR)                                       |

| CEF              | Chip Enable (NAND)                                      |

| CSU              | Chip Enable (UtRAM)                                     |

| RESET            | Hardware Reset (NOR)                                    |

| WP/ACC           | Hardware Write Protection/Program<br>Acceleration (NOR) |

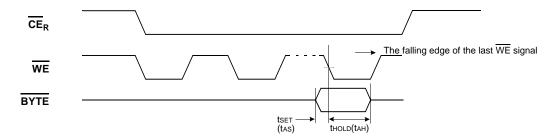

| BYTE             | Byte Control (NOR)                                      |

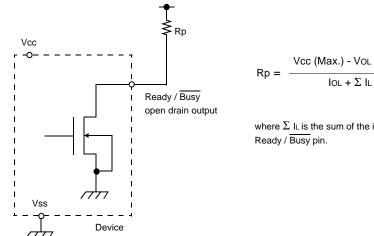

| R/B <sub>R</sub> | Read/Busy (NOR)                                         |

| WP               | Write Protection (NAND)                                 |

| CLE              | Command Latch Enable(NAND)                              |

| ALE              | Address Latch Enable(NAND)                              |

| R/B <sub>F</sub> | Read/Busy (NAND)                                        |

| RE               | Output Enable (NAND)                                    |

| ZZ               | Deep Power Down (UtRAM)                                 |

| UB               | Upper Byte Enable (UtRAM)                               |

| LB               | Lower Byte Enable (UtRAM)                               |

| N.C              | No Connection                                           |

| DNU              | Do Not Use                                              |

SAMSUNG ELECTRONICS CO., LTD. reserves the right to change products and specifications without notice.

# **ORDERING INFORMATION**

# Figure 1. FUNCTIONAL BLOCK DIAGRAM

ELECTRONICS

SAMSUNG

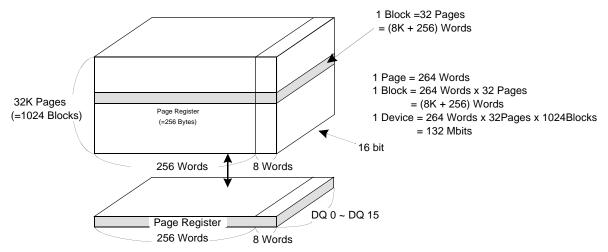

# Figure 2. NAND Flash ARRAY ORGANIZATION

|           | DQ 0 | DQ 1 | DQ 2 | DQ 3 | DQ 4 | DQ 5 | DQ 6 | DQ 7 | DQ8 to 15 |                |

|-----------|------|------|------|------|------|------|------|------|-----------|----------------|

| 1st Cycle | Ao   | A1   | A2   | Аз   | A4   | A5   | A6   | A7   | *L        | Column Address |

| 2nd Cycle | A9   | A10  | A11  | A12  | A13  | A14  | A15  | A16  | *L        | Row Address    |

| 3rd Cycle | A17  | A18  | A19  | A20  | A21  | A22  | A23  | *L   | *L        | (Page Address) |

NOTE: Column Address : Starting Address of the Register.

\* L must be set to "Low"

| KAB        | KAB        |       |     |     |     | E   | Block A | ddress | 5   |     |     |     | Block Size | Addres          | s Range         |

|------------|------------|-------|-----|-----|-----|-----|---------|--------|-----|-----|-----|-----|------------|-----------------|-----------------|

| 02D1<br>00 | 04D1<br>00 | Block | A21 | A20 | A19 | A18 | A17     | A16    | A15 | A14 | A13 | A12 | (KB/KW)    | Byte Mode       | Word Mode       |

|            |            | BA134 | 1   | 1   | 1   | 1   | 1       | 1      | 1   | 1   | 1   | 1   | 8/4        | 7FE000H-7FFFFFH | 3FF000H-3FFFFFH |

|            |            | BA133 | 1   | 1   | 1   | 1   | 1       | 1      | 1   | 1   | 1   | 0   | 8/4        | 7FC000H-7FDFFFH | 3FE000H-3FEFFFH |

|            |            | BA132 | 1   | 1   | 1   | 1   | 1       | 1      | 1   | 1   | 0   | 1   | 8/4        | 7FA000H-7FBFFFH | 3FD000H-3FDFFFH |

|            |            | BA131 | 1   | 1   | 1   | 1   | 1       | 1      | 1   | 1   | 0   | 0   | 8/4        | 7F8000H-7F9FFFH | 3FC000H-3FCFFFH |

|            |            | BA130 | 1   | 1   | 1   | 1   | 1       | 1      | 1   | 0   | 1   | 1   | 8/4        | 7F6000H-7F7FFFH | 3FB000H-3FBFFFH |

|            |            | BA129 | 1   | 1   | 1   | 1   | 1       | 1      | 1   | 0   | 1   | 0   | 8/4        | 7F4000H-7F5FFFH | 3FA000H-3FAFFFH |

|            |            | BA128 | 1   | 1   | 1   | 1   | 1       | 1      | 1   | 0   | 0   | 1   | 8/4        | 7F2000H-7F3FFFH | 3F9000H-3F9FFFH |

|            |            | BA127 | 1   | 1   | 1   | 1   | 1       | 1      | 1   | 0   | 0   | 0   | 8/4        | 7F0000H-7F1FFFH | 3F8000H-3F8FFFH |

|            |            | BA126 | 1   | 1   | 1   | 1   | 1       | 1      | 0   | Х   | Х   | Х   | 64/32      | 7E0000H-7EFFFFH | 3F0000H-3F7FFFH |

|            |            | BA125 | 1   | 1   | 1   | 1   | 1       | 0      | 1   | Х   | Х   | Х   | 64/32      | 7D0000H-7DFFFFH | 3E8000H-3EFFFFH |

|            |            | BA124 | 1   | 1   | 1   | 1   | 1       | 0      | 0   | Х   | Х   | Х   | 64/32      | 7C0000H-7CFFFFH | 3E0000H-3E7FFFH |

|            |            | BA123 | 1   | 1   | 1   | 1   | 0       | 1      | 1   | Х   | Х   | Х   | 64/32      | 7B0000H-7BFFFFH | 3D8000H-3DFFFFH |

|            |            | BA122 | 1   | 1   | 1   | 1   | 0       | 1      | 0   | Х   | Х   | Х   | 64/32      | 7A0000H-7AFFFH  | 3D0000H-3D7FFFH |

|            |            | BA121 | 1   | 1   | 1   | 1   | 0       | 0      | 1   | Х   | Х   | Х   | 64/32      | 790000H-79FFFFH | 3C8000H-3CFFFFH |

|            |            | BA120 | 1   | 1   | 1   | 1   | 0       | 0      | 0   | Х   | Х   | Х   | 64/32      | 780000H-78FFFFH | 3C0000H-3C7FFFH |

|            |            | BA119 | 1   | 1   | 1   | 0   | 1       | 1      | 1   | Х   | Х   | Х   | 64/32      | 770000H-77FFFFH | 3B8000H-3BFFFFH |

|            |            | BA118 | 1   | 1   | 1   | 0   | 1       | 1      | 0   | Х   | Х   | Х   | 64/32      | 760000H-76FFFFH | 3B0000H-3B7FFFH |

| Bank1      | Bank1      | BA117 | 1   | 1   | 1   | 0   | 1       | 0      | 1   | Х   | Х   | Х   | 64/32      | 750000H-75FFFFH | 3A8000H-3AFFFFH |

| Danki      | Danki      | BA116 | 1   | 1   | 1   | 0   | 1       | 0      | 0   | Х   | Х   | Х   | 64/32      | 740000H-74FFFFH | 3A0000H-3A7FFFH |

|            |            | BA115 | 1   | 1   | 1   | 0   | 0       | 1      | 1   | Х   | Х   | Х   | 64/32      | 730000H-73FFFFH | 398000H-39FFFFH |

|            |            | BA114 | 1   | 1   | 1   | 0   | 0       | 1      | 0   | х   | Х   | х   | 64/32      | 720000H-72FFFFH | 390000H-397FFFH |

|            |            | BA113 | 1   | 1   | 1   | 0   | 0       | 0      | 1   | х   | Х   | х   | 64/32      | 710000H-71FFFFH | 388000H-38FFFFH |

|            |            | BA112 | 1   | 1   | 1   | 0   | 0       | 0      | 0   | Х   | Х   | Х   | 64/32      | 700000H-70FFFFH | 380000H-387FFFH |

|            |            | BA111 | 1   | 1   | 0   | 1   | 1       | 1      | 1   | х   | Х   | х   | 64/32      | 6F0000H-6FFFFFH | 378000H-37FFFFH |

|            |            | BA110 | 1   | 1   | 0   | 1   | 1       | 1      | 0   | х   | Х   | х   | 64/32      | 6E0000H-6EFFFFH | 370000H-377FFFH |

|            |            | BA109 | 1   | 1   | 0   | 1   | 1       | 0      | 1   | Х   | х   | Х   | 64/32      | 6D0000H-6DFFFFH | 368000H-36FFFFH |

|            |            | BA108 | 1   | 1   | 0   | 1   | 1       | 0      | 0   | х   | Х   | х   | 64/32      | 6C0000H-6CFFFFH | 360000H-367FFFH |

|            |            | BA107 | 1   | 1   | 0   | 1   | 0       | 1      | 1   | х   | Х   | х   | 64/32      | 6B0000H-6BFFFFH | 358000H-35FFFFH |

|            |            | BA106 | 1   | 1   | 0   | 1   | 0       | 1      | 0   | Х   | х   | Х   | 64/32      | 6A0000H-6AFFFH  | 350000H-357FFFH |

|            |            | BA105 | 1   | 1   | 0   | 1   | 0       | 0      | 1   | х   | Х   | х   | 64/32      | 690000H-69FFFFH | 348000H-34FFFFH |

|            |            | BA104 | 1   | 1   | 0   | 1   | 0       | 0      | 0   | Х   | Х   | Х   | 64/32      | 680000H-68FFFFH | 340000H-347FFFH |

|            |            | BA103 | 1   | 1   | 0   | 0   | 1       | 1      | 1   | Х   | Х   | Х   | 64/32      | 670000H-67FFFH  | 338000H-33FFFFH |

|            |            | BA102 | 1   | 1   | 0   | 0   | 1       | 1      | 0   | Х   | Х   | Х   | 64/32      | 660000H-66FFFFH | 330000H-337FFFH |

|            |            | BA101 | 1   | 1   | 0   | 0   | 1       | 0      | 1   | Х   | Х   | Х   | 64/32      | 650000H-65FFFFH | 328000H-32FFFFH |

|            |            | BA100 | 1   | 1   | 0   | 0   | 1       | 0      | 0   | Х   | Х   | Х   | 64/32      | 640000H-64FFFFH | 320000H-327FFFH |

|            |            | BA99  | 1   | 1   | 0   | 0   | 0       | 1      | 1   | Х   | Х   | Х   | 64/32      | 630000H-63FFFFH | 318000H-31FFFFH |

| KAB        | KAB        |       |     |     |     | E   | Block A | ddress | ;   |     |     |     | Block Size | Addres          | s Range         |

|------------|------------|-------|-----|-----|-----|-----|---------|--------|-----|-----|-----|-----|------------|-----------------|-----------------|

| 02D1<br>00 | 04D1<br>00 | Block | A21 | A20 | A19 | A18 | A17     | A16    | A15 | A14 | A13 | A12 | (KB/KW)    | Byte Mode       | Word Mode       |

|            |            | BA98  | 1   | 1   | 0   | 0   | 0       | 1      | 0   | Х   | Х   | Х   | 64/32      | 620000H-62FFFFH | 310000H-317FFFH |

| Bank1      |            | BA97  | 1   | 1   | 0   | 0   | 0       | 0      | 1   | Х   | Х   | Х   | 64/32      | 610000H-61FFFFH | 308000H-30FFFFH |

|            |            | BA96  | 1   | 1   | 0   | 0   | 0       | 0      | 0   | Х   | Х   | Х   | 64/32      | 600000H-60FFFFH | 300000H-307FFFH |

|            |            | BA95  | 1   | 0   | 1   | 1   | 1       | 1      | 1   | х   | х   | Х   | 64/32      | 5F0000H-5FFFFFH | 2F8000H-2FFFFFH |

|            |            | BA94  | 1   | 0   | 1   | 1   | 1       | 1      | 0   | Х   | Х   | Х   | 64/32      | 5E0000H-5EFFFFH | 2F0000H-2F7FFFH |

|            |            | BA93  | 1   | 0   | 1   | 1   | 1       | 0      | 1   | х   | х   | Х   | 64/32      | 5D0000H-5DFFFFH | 2E8000H-2EFFFFH |

|            |            | BA92  | 1   | 0   | 1   | 1   | 1       | 0      | 0   | х   | х   | Х   | 64/32      | 5C0000H-5CFFFFH | 2E0000H-2E7FFFH |

|            |            | BA91  | 1   | 0   | 1   | 1   | 0       | 1      | 1   | Х   | Х   | Х   | 64/32      | 5B0000H-5BFFFFH | 2D8000H-2DFFFFH |

|            |            | BA90  | 1   | 0   | 1   | 1   | 0       | 1      | 0   | х   | х   | Х   | 64/32      | 5A0000H-5AFFFFH | 2D0000H-2D7FFFH |

|            |            | BA89  | 1   | 0   | 1   | 1   | 0       | 0      | 1   | х   | х   | Х   | 64/32      | 590000H-59FFFFH | 2C8000H20CFFFFH |

|            |            | BA88  | 1   | 0   | 1   | 1   | 0       | 0      | 0   | Х   | Х   | Х   | 64/32      | 580000H-58FFFFH | 2C0000H-2C7FFFH |

|            |            | BA87  | 1   | 0   | 1   | 0   | 1       | 1      | 1   | х   | х   | Х   | 64/32      | 570000H-57FFFFH | 2B8000H-2BFFFFH |

|            |            | BA86  | 1   | 0   | 1   | 0   | 1       | 1      | 0   | Х   | Х   | Х   | 64/32      | 560000H-56FFFFH | 2B0000H-2B7FFFH |

|            | Bank1      | BA85  | 1   | 0   | 1   | 0   | 1       | 0      | 1   | Х   | Х   | Х   | 64/32      | 550000H-55FFFFH | 2A8000H-2AFFFFH |

|            | Daliki     | BA84  | 1   | 0   | 1   | 0   | 1       | 0      | 0   | х   | х   | Х   | 64/32      | 540000H-54FFFFH | 2A0000H-2A7FFFH |

| Bank2      |            | BA83  | 1   | 0   | 1   | 0   | 0       | 1      | 1   | Х   | Х   | Х   | 64/32      | 530000H-53FFFFH | 298000H-29FFFFH |

|            |            | BA82  | 1   | 0   | 1   | 0   | 0       | 1      | 0   | Х   | Х   | Х   | 64/32      | 520000H-52FFFFH | 290000H-297FFFH |

|            |            | BA81  | 1   | 0   | 1   | 0   | 0       | 0      | 1   | Х   | Х   | Х   | 64/32      | 510000H-51FFFFH | 288000H-28FFFFH |

|            |            | BA80  | 1   | 0   | 1   | 0   | 0       | 0      | 0   | Х   | Х   | Х   | 64/32      | 500000H-50FFFFH | 280000H-287FFFH |

|            |            | BA79  | 1   | 0   | 0   | 1   | 1       | 1      | 1   | Х   | Х   | Х   | 64/32      | 4F0000H-4FFFFFH | 278000H-27FFFFH |

|            |            | BA78  | 1   | 0   | 0   | 1   | 1       | 1      | 0   | х   | х   | Х   | 64/32      | 4E0000H-4EFFFFH | 270000H-277FFFH |

|            |            | BA77  | 1   | 0   | 0   | 1   | 1       | 0      | 1   | Х   | Х   | Х   | 64/32      | 4D0000H-4DFFFFH | 268000H-26FFFFH |

|            |            | BA76  | 1   | 0   | 0   | 1   | 1       | 0      | 0   | Х   | Х   | Х   | 64/32      | 4C0000H-4CFFFFH | 260000H-267FFFH |

|            |            | BA75  | 1   | 0   | 0   | 1   | 0       | 1      | 1   | Х   | Х   | Х   | 64/32      | 4B0000H-4BFFFFH | 258000H-25FFFFH |

|            |            | BA74  | 1   | 0   | 0   | 1   | 0       | 1      | 0   | Х   | х   | х   | 64/32      | 4A0000H-4AFFFFH | 250000H-257FFFH |

|            |            | BA73  | 1   | 0   | 0   | 1   | 0       | 0      | 1   | Х   | Х   | Х   | 64/32      | 490000H-49FFFFH | 248000H-24FFFFH |

|            |            | BA72  | 1   | 0   | 0   | 1   | 0       | 0      | 0   | Х   | Х   | Х   | 64/32      | 480000H-48FFFFH | 240000H-247FFFH |

|            |            | BA71  | 1   | 0   | 0   | 0   | 1       | 1      | 1   | Х   | Х   | Х   | 64/32      | 470000H-47FFFFH | 238000H-23FFFFH |

| KAB        | KAB        |       |     |     |     | E   | Block A | ddress | 5   |     |     |     | Block Size | Addres          | s Range         |

|------------|------------|-------|-----|-----|-----|-----|---------|--------|-----|-----|-----|-----|------------|-----------------|-----------------|

| 02D1<br>00 | 04D1<br>00 | Block | A21 | A20 | A19 | A18 | A17     | A16    | A15 | A14 | A13 | A12 | (KB/KW)    | Byte Mode       | Word Mode       |

|            |            | BA70  | 1   | 0   | 0   | 0   | 1       | 1      | 0   | Х   | х   | Х   | 64/32      | 460000H-46FFFFH | 230000H-237FFFH |

|            |            | BA69  | 1   | 0   | 0   | 0   | 1       | 0      | 1   | Х   | Х   | Х   | 64/32      | 450000H-45FFFFH | 228000H-22FFFFH |

|            |            | BA68  | 1   | 0   | 0   | 0   | 1       | 0      | 0   | Х   | Х   | Х   | 64/32      | 440000H-44FFFFH | 220000H-227FFFH |

|            | Bank1      | BA67  | 1   | 0   | 0   | 0   | 0       | 1      | 1   | Х   | Х   | Х   | 64/32      | 430000H-43FFFFH | 218000H-21FFFFH |

|            |            | BA66  | 1   | 0   | 0   | 0   | 0       | 1      | 0   | Х   | Х   | Х   | 64/32      | 420000H-42FFFFH | 210000H-217FFFH |

|            |            | BA65  | 1   | 0   | 0   | 0   | 0       | 0      | 1   | Х   | Х   | Х   | 64/32      | 410000H-41FFFFH | 208000H-20FFFFH |

|            |            | BA64  | 1   | 0   | 0   | 0   | 0       | 0      | 0   | Х   | Х   | Х   | 64/32      | 400000H-3FFFFFH | 200000H-207FFFH |

|            |            | BA63  | 0   | 1   | 1   | 1   | 1       | 1      | 1   | Х   | Х   | Х   | 64/32      | 3F0000H-3FFFFFH | 1F8000H-1FFFFFH |

|            |            | BA62  | 0   | 1   | 1   | 1   | 1       | 1      | 0   | Х   | Х   | Х   | 64/32      | 3E0000H-3EFFFFH | 1F0000H-1F7FFFH |

|            |            | BA61  | 0   | 1   | 1   | 1   | 1       | 0      | 1   | Х   | Х   | Х   | 64/32      | 3D0000H-3DFFFFH | 1E8000H-1EFFFFH |

|            |            | BA60  | 0   | 1   | 1   | 1   | 1       | 0      | 0   | Х   | Х   | Х   | 64/32      | 3C0000H-3CFFFFH | 1E0000H-1E7FFFH |

|            |            | BA59  | 0   | 1   | 1   | 1   | 0       | 1      | 1   | Х   | Х   | Х   | 64/32      | 3B0000H-3BFFFFH | 1D8000H-1DFFFFH |

|            |            | BA58  | 0   | 1   | 1   | 1   | 0       | 1      | 0   | Х   | Х   | Х   | 64/32      | 3A0000H-3AFFFFH | 1D0000H-1D7FFFH |

|            |            | BA57  | 0   | 1   | 1   | 1   | 0       | 0      | 1   | Х   | Х   | Х   | 64/32      | 390000H-39FFFFH | 1C8000H-1CFFFFH |

|            |            | BA56  | 0   | 1   | 1   | 1   | 0       | 0      | 0   | Х   | Х   | Х   | 64/32      | 380000H-38FFFFH | 1C0000H-1C7FFFH |

|            |            | BA55  | 0   | 1   | 1   | 0   | 1       | 1      | 1   | Х   | Х   | Х   | 64/32      | 370000H-37FFFFH | 1B8000H-1BFFFFH |

|            |            | BA54  | 0   | 1   | 1   | 0   | 1       | 1      | 0   | Х   | Х   | Х   | 64/32      | 360000H-36FFFFH | 1B0000H-1B7FFFH |

| Bank2      |            | BA53  | 0   | 1   | 1   | 0   | 1       | 0      | 1   | Х   | Х   | Х   | 64/32      | 350000H-35FFFFH | 1A8000H-1AFFFFH |

| Dalikz     |            | BA52  | 0   | 1   | 1   | 0   | 1       | 0      | 0   | Х   | Х   | Х   | 64/32      | 340000H-34FFFFH | 1A0000H-1A7FFFH |

|            |            | BA51  | 0   | 1   | 1   | 0   | 0       | 1      | 1   | Х   | Х   | Х   | 64/32      | 330000H-33FFFFH | 198000H-19FFFFH |

|            |            | BA50  | 0   | 1   | 1   | 0   | 0       | 1      | 0   | Х   | Х   | Х   | 64/32      | 320000H-32FFFFH | 190000H-197FFFH |

|            | Bank2      | BA49  | 0   | 1   | 1   | 0   | 0       | 0      | 1   | Х   | Х   | Х   | 64/32      | 310000H-31FFFFH | 188000H-18FFFFH |

|            |            | BA48  | 0   | 1   | 1   | 0   | 0       | 0      | 0   | Х   | Х   | Х   | 64/32      | 300000H-30FFFFH | 180000H-187FFFH |

|            |            | BA47  | 0   | 1   | 0   | 1   | 1       | 1      | 1   | Х   | Х   | Х   | 64/32      | 2F0000H-2FFFFFH | 178000H-17FFFFH |

|            |            | BA46  | 0   | 1   | 0   | 1   | 1       | 1      | 0   | Х   | Х   | Х   | 64/32      | 2E0000H-2EFFFFH | 170000H-177FFFH |

|            |            | BA45  | 0   | 1   | 0   | 1   | 1       | 0      | 1   | Х   | Х   | Х   | 64/32      | 2D0000H-2DFFFFH | 168000H-16FFFFH |

|            |            | BA44  | 0   | 1   | 0   | 1   | 1       | 0      | 0   | Х   | Х   | Х   | 64/32      | 2C0000H-2CFFFFH | 160000H-167FFFH |

|            |            | BA43  | 0   | 1   | 0   | 1   | 0       | 1      | 1   | Х   | Х   | Х   | 64/32      | 2B0000H-2BFFFFH | 158000H-15FFFFH |

|            |            | BA42  | 0   | 1   | 0   | 1   | 0       | 1      | 0   | Х   | Х   | Х   | 64/32      | 2A0000H-2AFFFFH | 150000H-157FFFH |

|            |            | BA41  | 0   | 1   | 0   | 1   | 0       | 0      | 1   | Х   | Х   | Х   | 64/32      | 290000H-29FFFFH | 148000H-14FFFFH |

|            |            | BA40  | 0   | 1   | 0   | 1   | 0       | 0      | 0   | Х   | Х   | Х   | 64/32      | 280000H-28FFFFH | 140000H-147FFFH |

|            |            | BA39  | 0   | 1   | 0   | 0   | 1       | 1      | 1   | Х   | Х   | Х   | 64/32      | 270000H-27FFFFH | 138000H-13FFFFH |

|            |            | BA38  | 0   | 1   | 0   | 0   | 1       | 1      | 0   | Х   | Х   | Х   | 64/32      | 260000H-26FFFFH | 130000H-137FFFH |

|            |            | BA37  | 0   | 1   | 0   | 0   | 1       | 0      | 1   | Х   | Х   | Х   | 64/32      | 250000H-25FFFFH | 128000H-12FFFFH |

|            |            | BA36  | 0   | 1   | 0   | 0   | 1       | 0      | 0   | Х   | Х   | Х   | 64/32      | 240000H-24FFFFH | 120000H-127FFFH |

|            |            | BA35  | 0   | 1   | 0   | 0   | 0       | 1      | 1   | Х   | Х   | Х   | 64/32      | 230000H-23FFFFH | 118000H-11FFFFH |

| KAB        | KAB        | Disala |     |     |     | E   | Block A | ddress | 6   |     |     |     | Block Size | Addres          | s Range         |

|------------|------------|--------|-----|-----|-----|-----|---------|--------|-----|-----|-----|-----|------------|-----------------|-----------------|

| 02D1<br>00 | 04D1<br>00 | Block  | A21 | A20 | A19 | A18 | A17     | A16    | A15 | A14 | A13 | A12 | (KB/KW)    | Byte Mode       | Word Mode       |

|            |            | BA34   | 0   | 1   | 0   | 0   | 0       | 1      | 0   | Х   | Х   | Х   | 64/32      | 220000H-22FFFFH | 110000H-117FFFH |

|            |            | BA33   | 0   | 1   | 0   | 0   | 0       | 0      | 1   | х   | Х   | Х   | 64/32      | 210000H-21FFFFH | 108000H-10FFFFH |

|            |            | BA32   | 0   | 1   | 0   | 0   | 0       | 0      | 0   | Х   | Х   | Х   | 64/32      | 200000H-20FFFFH | 100000H-107FFFH |

|            |            | BA31   | 0   | 0   | 1   | 1   | 1       | 1      | 1   | Х   | Х   | Х   | 64/32      | 1F0000H-1FFFFFH | 0F8000H-0FFFFH  |

|            |            | BA30   | 0   | 0   | 1   | 1   | 1       | 1      | 0   | Х   | Х   | Х   | 64/32      | 1E0000H-1EFFFFH | 0F0000H-0F7FFFH |

|            |            | BA29   | 0   | 0   | 1   | 1   | 1       | 0      | 1   | х   | Х   | Х   | 64/32      | 1D0000H-1DFFFFH | 0E8000H-0EFFFH  |

|            |            | BA28   | 0   | 0   | 1   | 1   | 1       | 0      | 0   | Х   | Х   | Х   | 64/32      | 1C0000H-1CFFFFH | 0E0000H-0E7FFH  |

|            |            | BA27   | 0   | 0   | 1   | 1   | 0       | 1      | 1   | Х   | Х   | Х   | 64/32      | 1B0000H-1BFFFFH | 0D8000H-0DFFFFH |

|            |            | BA26   | 0   | 0   | 1   | 1   | 0       | 1      | 0   | х   | Х   | Х   | 64/32      | 1A0000H-1AFFFFH | 0D0000H-0D7FFFH |

|            |            | BA25   | 0   | 0   | 1   | 1   | 0       | 0      | 1   | Х   | Х   | Х   | 64/32      | 190000H-19FFFFH | 0C8000H-0CFFFFH |

|            |            | BA24   | 0   | 0   | 1   | 1   | 0       | 0      | 0   | х   | Х   | Х   | 64/32      | 180000H-18FFFFH | 0C0000H-0C7FFFH |

|            |            | BA23   | 0   | 0   | 1   | 0   | 1       | 1      | 1   | х   | Х   | Х   | 64/32      | 170000H-17FFFFH | 0B8000H-0BFFFFH |

|            |            | BA22   | 0   | 0   | 1   | 0   | 1       | 1      | 0   | х   | Х   | Х   | 64/32      | 160000H-16FFFFH | 0B0000H-0B7FFFH |

|            |            | BA21   | 0   | 0   | 1   | 0   | 1       | 0      | 1   | Х   | Х   | Х   | 64/32      | 150000H-15FFFFH | 0A8000H-0AFFFFH |

|            |            | BA20   | 0   | 0   | 1   | 0   | 1       | 0      | 0   | х   | х   | Х   | 64/32      | 140000H-14FFFFH | 0A0000H-0A7FFF  |

|            |            | BA19   | 0   | 0   | 1   | 0   | 0       | 1      | 1   | х   | Х   | Х   | 64/32      | 130000H-13FFFFH | 098000H-09FFFFH |

|            |            | BA18   | 0   | 0   | 1   | 0   | 0       | 1      | 0   | Х   | Х   | Х   | 64/32      | 120000H-12FFFFH | 090000H-097FFFH |

| Bank2      | Bank2      | BA17   | 0   | 0   | 1   | 0   | 0       | 0      | 1   | х   | х   | Х   | 64/32      | 110000H-11FFFFH | 088000H-08FFFFH |

|            |            | BA16   | 0   | 0   | 1   | 0   | 0       | 0      | 0   | х   | х   | Х   | 64/32      | 100000H-10FFFFH | 080000H-087FFFH |

|            |            | BA15   | 0   | 0   | 0   | 1   | 1       | 1      | 1   | Х   | Х   | Х   | 64/32      | 0F0000H-0FFFFH  | 078000H-07FFFH  |

|            |            | BA14   | 0   | 0   | 0   | 1   | 1       | 1      | 0   | х   | х   | Х   | 64/32      | 0E0000H-0EFFFFH | 070000H-077FFFH |

|            |            | BA13   | 0   | 0   | 0   | 1   | 1       | 0      | 1   | х   | Х   | Х   | 64/32      | 0D0000H-0DFFFFH | 068000H-06FFFH  |

|            |            | BA12   | 0   | 0   | 0   | 1   | 1       | 0      | 0   | Х   | Х   | Х   | 64/32      | 0C0000H-0CFFFFH | 060000H-067FFH  |

|            |            | BA11   | 0   | 0   | 0   | 1   | 0       | 1      | 1   | х   | Х   | Х   | 64/32      | 0B0000H-0BFFFFH | 058000H-05FFFFH |

|            |            | BA10   | 0   | 0   | 0   | 1   | 0       | 1      | 0   | Х   | Х   | Х   | 64/32      | 0A0000H-0AFFFFH | 050000H-057FFFH |

|            |            | BA9    | 0   | 0   | 0   | 1   | 0       | 0      | 1   | Х   | Х   | Х   | 64/32      | 090000H-09FFFFH | 048000H-04FFFFH |

|            |            | BA8    | 0   | 0   | 0   | 1   | 0       | 0      | 0   | х   | х   | Х   | 64/32      | 080000H-08FFFFH | 040000H-047FFFH |

|            |            | BA7    | 0   | 0   | 0   | 0   | 1       | 1      | 1   | х   | Х   | Х   | 64/32      | 070000H-07FFFFH | 038000H-03FFFFH |

|            |            | BA6    | 0   | 0   | 0   | 0   | 1       | 1      | 0   | Х   | Х   | Х   | 64/32      | 060000H-06FFFFH | 030000H-037FFFH |

|            |            | BA5    | 0   | 0   | 0   | 0   | 1       | 0      | 1   | Х   | Х   | Х   | 64/32      | 050000H-05FFFFH | 028000H-02FFFFH |

|            |            | BA4    | 0   | 0   | 0   | 0   | 1       | 0      | 0   | Х   | Х   | Х   | 64/32      | 040000H-04FFFFH | 020000H-027FFFH |

|            |            | BA3    | 0   | 0   | 0   | 0   | 0       | 1      | 1   | Х   | Х   | Х   | 64/32      | 030000H-03FFFFH | 018000H-01FFFFH |

|            |            | BA2    | 0   | 0   | 0   | 0   | 0       | 1      | 0   | Х   | Х   | Х   | 64/32      | 020000H-02FFFFH | 010000H-017FFFH |

|            |            | BA1    | 0   | 0   | 0   | 0   | 0       | 0      | 1   | Х   | Х   | Х   | 64/32      | 010000H-01FFFFH | 008000H-00FFFF  |

|            |            | BA0    | 0   | 0   | 0   | 0   | 0       | 0      | 0   | Х   | Х   | Х   | 64/32      | 000000H-00FFFFH | 000000H-007FFFH |

NOTE: The bank address bits are A21 ~ A20 for KAB02D100, A21 for KAB04D100.

# Table 2. Secode Block Addresses for Top Boot Devices

| Device              | Block Address | Block | (X8)            | (X16)           |

|---------------------|---------------|-------|-----------------|-----------------|

|                     | A21-A12       | Size  | Address Range   | Address Range   |

| KAB02D100/KAB04D100 | 1111111xxx    | 64/32 | 7F0000H-7FFFFFH | 3F8000H-3FFFFFH |

| KAB        | KAB        |       |     |     |     | E   | Block A | ddress | 5   |     |     |     | Block Size | Addres          | s Range         |

|------------|------------|-------|-----|-----|-----|-----|---------|--------|-----|-----|-----|-----|------------|-----------------|-----------------|

| 01D1<br>00 | 03D1<br>00 | Block | A21 | A20 | A19 | A18 | A17     | A16    | A15 | A14 | A13 | A12 | (KB/KW)    | Byte Mode       | Word Mode       |

|            |            | BA134 | 1   | 1   | 1   | 1   | 1       | 1      | 1   | Х   | Х   | Х   | 64/32      | 7F0000H-7FFFFH  | 3F8000H-3FFFFFH |

|            |            | BA133 | 1   | 1   | 1   | 1   | 1       | 1      | 0   | Х   | Х   | Х   | 64/32      | 7E0000H-7EFFFFH | 3F0000H-3F7FFFH |

|            |            | BA132 | 1   | 1   | 1   | 1   | 1       | 0      | 1   | х   | Х   | Х   | 64/32      | 7D0000H-7DFFFFH | 3E8000H-3EFFFFH |

|            |            | BA131 | 1   | 1   | 1   | 1   | 1       | 0      | 0   | Х   | Х   | Х   | 64/32      | 7C0000H-7CFFFFH | 3E0000H-3E7FFFH |

|            |            | BA130 | 1   | 1   | 1   | 1   | 0       | 1      | 1   | х   | Х   | Х   | 64/32      | 7B0000H-7BFFFFH | 3D8000H-3DFFFFH |

|            |            | BA129 | 1   | 1   | 1   | 1   | 0       | 1      | 0   | х   | Х   | Х   | 64/32      | 7A0000H-7AFFFFH | 3D0000H-3D7FFFH |

|            |            | BA128 | 1   | 1   | 1   | 1   | 0       | 0      | 1   | х   | Х   | Х   | 64/32      | 790000H-79FFFFH | 3C8000H-3CFFFFH |

|            |            | BA127 | 1   | 1   | 1   | 1   | 0       | 0      | 0   | Х   | Х   | Х   | 64/32      | 780000H-78FFFFH | 3C0000H-3C7FFFH |

|            |            | BA126 | 1   | 1   | 1   | 0   | 1       | 1      | 1   | Х   | Х   | Х   | 64/32      | 770000H-77FFFFH | 3B8000H-3BFFFFH |

|            |            | BA125 | 1   | 1   | 1   | 0   | 1       | 1      | 0   | х   | Х   | Х   | 64/32      | 760000H-76FFFH  | 3B0000H-3B7FFFH |

|            |            | BA124 | 1   | 1   | 1   | 0   | 1       | 0      | 1   | х   | х   | Х   | 64/32      | 750000H-75FFFFH | 3A8000H-3AFFFFH |

|            |            | BA123 | 1   | 1   | 1   | 0   | 1       | 0      | 0   | х   | х   | х   | 64/32      | 740000H-74FFFH  | 3A0000H-3A7FFFH |

|            |            | BA122 | 1   | 1   | 1   | 0   | 0       | 1      | 1   | х   | х   | х   | 64/32      | 730000H-73FFFFH | 398000H-39FFFFH |

|            |            | BA121 | 1   | 1   | 1   | 0   | 0       | 1      | 0   | х   | х   | Х   | 64/32      | 720000H-72FFFFH | 390000H-397FFFH |

|            |            | BA120 | 1   | 1   | 1   | 0   | 0       | 0      | 1   | х   | х   | х   | 64/32      | 710000H-71FFFFH | 388000H-38FFFFH |

|            |            | BA119 | 1   | 1   | 1   | 0   | 0       | 0      | 0   | х   | х   | х   | 64/32      | 700000H-70FFFH  | 380000H-387FFFH |

|            |            | BA118 | 1   | 1   | 0   | 1   | 1       | 1      | 1   | х   | х   | Х   | 64/32      | 6F0000H-6F1FFFH | 378000H-37FFFFH |

|            |            | BA117 | 1   | 1   | 0   | 1   | 1       | 1      | 0   | х   | х   | Х   | 64/32      | 6E0000H-6EFFFH  | 370000H-377FFFH |

| Bank2      | Bank2      | BA116 | 1   | 1   | 0   | 1   | 1       | 0      | 1   | х   | х   | х   | 64/32      | 6D0000H-6DFFFFH | 368000H-36FFFFH |

|            |            | BA115 | 1   | 1   | 0   | 1   | 1       | 0      | 0   | х   | Х   | х   | 64/32      | 6C0000H-6CFFFFH | 360000H-367FFFH |

|            |            | BA114 | 1   | 1   | 0   | 1   | 0       | 1      | 1   | х   | Х   | х   | 64/32      | 6B0000H-6BFFFFH | 358000H-35FFFFH |

|            |            | BA113 | 1   | 1   | 0   | 1   | 0       | 1      | 0   | х   | х   | х   | 64/32      | 6A0000H-6AFFFH  | 350000H-357FFFH |

|            |            | BA112 | 1   | 1   | 0   | 1   | 0       | 0      | 1   | х   | Х   | х   | 64/32      | 690000H-69FFFFH | 348000H-34FFFFH |

|            |            | BA111 | 1   | 1   | 0   | 1   | 0       | 0      | 0   | х   | Х   | х   | 64/32      | 680000H-68FFFFH | 340000H-347FFFH |

|            |            | BA110 | 1   | 1   | 0   | 0   | 1       | 1      | 1   | х   | х   | х   | 64/32      | 670000H-67FFFH  | 338000H-33FFFFH |

|            |            | BA109 | 1   | 1   | 0   | 0   | 1       | 1      | 0   | х   | х   | х   | 64/32      | 660000H-66FFFFH | 330000H-337FFFH |

|            |            | BA108 | 1   | 1   | 0   | 0   | 1       | 0      | 1   | х   | Х   | х   | 64/32      | 650000H-65FFFFH | 328000H-32FFFFH |

|            |            | BA107 | 1   | 1   | 0   | 0   | 1       | 0      | 0   | х   | Х   | х   | 64/32      | 640000H-64FFFFH | 320000H-327FFFH |

|            |            | BA106 | 1   | 1   | 0   | 0   | 0       | 1      | 1   | Х   | Х   | х   | 64/32      | 630000H-63FFFFH | 318000H-31FFFFH |

|            |            | BA105 | 1   | 1   | 0   | 0   | 0       | 1      | 0   | Х   | Х   | Х   | 64/32      | 620000H-62FFFFH | 310000H-317FFFH |

|            |            | BA104 | 1   | 1   | 0   | 0   | 0       | 0      | 1   | х   | х   | х   | 64/32      | 610000H-61FFFH  | 308000H-30FFFFH |

|            |            | BA103 | 1   | 1   | 0   | 0   | 0       | 0      | 0   | х   | х   | х   | 64/32      | 600000H-60FFFH  | 300000H-307FFFH |

|            |            | BA102 | 1   | 0   | 1   | 1   | 1       | 1      | 1   | х   | х   | х   | 64/32      | 5F0000H-5FFFFFH | 2F8000H-2FFFFFH |

|            |            | BA101 | 1   | 0   | 1   | 1   | 1       | 1      | 0   | х   | х   | х   | 64/32      | 5E0000H-5EFFFFH | 2F0000H-2F7FFFH |

|            |            | BA100 | 1   | 0   | 1   | 1   | 1       | 0      | 1   | х   | х   | х   | 64/32      | 5D0000H-5DFFFFH | 2E8000H-2EFFFFH |

|            |            | BA99  | 1   | 0   | 1   | 1   | 1       | 0      | 0   | Х   | Х   | Х   | 64/32      | 5C0000H-5CFFFFH | 2E0000H-2E7FFFH |

# Table 3. NOR Flash Memory Bottom Block Address (KAB01D100/KAB03D100)

| KAB        | KAB        |       |     |     |     |     | Bloc | ck Add | ress |     |     |     | Block Size | Addres          | s Range         |

|------------|------------|-------|-----|-----|-----|-----|------|--------|------|-----|-----|-----|------------|-----------------|-----------------|

| 01D1<br>00 | 03D1<br>00 | Block | A21 | A20 | A19 | A18 | A17  | A16    | A15  | A14 | A13 | A12 | (KB/KW)    | Byte Mode       | Word Mode       |

|            |            | BA98  | 1   | 0   | 1   | 1   | 0    | 1      | 1    | Х   | х   | Х   | 64/32      | 5B0000H-5BFFFFH | 2D8000H-2DFFFFH |

|            |            | BA97  | 1   | 0   | 1   | 1   | 0    | 1      | 0    | Х   | Х   | Х   | 64/32      | 5A0000H-5AFFFFH | 2D0000H-2D7FFFH |

|            |            | BA96  | 1   | 0   | 1   | 1   | 0    | 0      | 1    | Х   | Х   | Х   | 64/32      | 590000H-59FFFFH | 2C8000H-2CFFFFH |

|            |            | BA95  | 1   | 0   | 1   | 1   | 0    | 0      | 0    | Х   | Х   | Х   | 64/32      | 580000H-58FFFFH | 2C0000H-2C7FFFH |

|            |            | BA94  | 1   | 0   | 1   | 0   | 1    | 1      | 1    | Х   | Х   | Х   | 64/32      | 570000H-57FFFFH | 2B8000H-2BFFFFH |

|            |            | BA93  | 1   | 0   | 1   | 0   | 1    | 1      | 0    | Х   | Х   | х   | 64/32      | 560000H-56FFFFH | 2B0000H-2B7FFFH |

|            |            | BA92  | 1   | 0   | 1   | 0   | 1    | 0      | 1    | Х   | Х   | Х   | 64/32      | 550000H-55FFFFH | 2A8000H-2AFFFFH |

|            |            | BA91  | 1   | 0   | 1   | 0   | 1    | 0      | 0    | Х   | Х   | Х   | 64/32      | 540000H-54FFFFH | 2A0000H-2A7FFFH |

|            |            | BA90  | 1   | 0   | 1   | 0   | 0    | 1      | 1    | Х   | Х   | Х   | 64/32      | 530000H-53FFFFH | 298000H-29FFFFH |

|            |            | BA89  | 1   | 0   | 1   | 0   | 0    | 1      | 0    | Х   | Х   | Х   | 64/32      | 520000H-52FFFFH | 290000H-297FFFH |

|            |            | BA88  | 1   | 0   | 1   | 0   | 0    | 0      | 1    | Х   | Х   | Х   | 64/32      | 510000H-51FFFFH | 288000H-28FFFFH |

|            |            | BA87  | 1   | 0   | 1   | 0   | 0    | 0      | 0    | Х   | Х   | Х   | 64/32      | 500000H-50FFFFH | 280000H-287FFFH |

|            |            | BA86  | 1   | 0   | 0   | 1   | 1    | 1      | 1    | Х   | Х   | Х   | 64/32      | 4F0000H-4FFFFFH | 278000H-27FFFFH |

| Bank2      | Bank2      | BA85  | 1   | 0   | 0   | 1   | 1    | 1      | 0    | Х   | Х   | Х   | 64/32      | 4E0000H-4EFFFFH | 270000H-277FFFH |

|            |            | BA84  | 1   | 0   | 0   | 1   | 1    | 0      | 1    | Х   | Х   | х   | 64/32      | 4D0000H-4DFFFFH | 268000H-26FFFFH |

|            |            | BA83  | 1   | 0   | 0   | 1   | 1    | 0      | 0    | Х   | Х   | х   | 64/32      | 4C0000H-4CFFFFH | 260000H-267FFFH |

|            |            | BA82  | 1   | 0   | 0   | 1   | 0    | 1      | 1    | Х   | Х   | Х   | 64/32      | 4B0000H-4BFFFFH | 258000H-25FFFFH |

|            |            | BA81  | 1   | 0   | 0   | 1   | 0    | 1      | 0    | Х   | х   | х   | 64/32      | 4A0000H-4AFFFFH | 250000H-257FFFH |

|            |            | BA80  | 1   | 0   | 0   | 1   | 0    | 0      | 1    | Х   | Х   | Х   | 64/32      | 490000H-49FFFFH | 248000H-24FFFFH |

|            |            | BA79  | 1   | 0   | 0   | 1   | 0    | 0      | 0    | Х   | Х   | Х   | 64/32      | 480000H-48FFFFH | 240000H-247FFFH |

|            |            | BA78  | 1   | 0   | 0   | 0   | 1    | 1      | 1    | Х   | Х   | Х   | 64/32      | 470000H-47FFFFH | 238000H-23FFFFH |

|            |            | BA77  | 1   | 0   | 0   | 0   | 1    | 1      | 0    | Х   | Х   | Х   | 64/32      | 460000H-46FFFFH | 230000H-237FFFH |

|            |            | BA76  | 1   | 0   | 0   | 0   | 1    | 0      | 1    | Х   | Х   | Х   | 64/32      | 450000H-45FFFFH | 228000H-22FFFFH |

|            |            | BA75  | 1   | 0   | 0   | 0   | 1    | 0      | 0    | Х   | Х   | Х   | 64/32      | 440000H-44FFFFH | 220000H-227FFFH |

|            |            | BA74  | 1   | 0   | 0   | 0   | 0    | 1      | 1    | Х   | Х   | Х   | 64/32      | 430000H-43FFFFH | 218000H-21FFFFH |

|            |            | BA73  | 1   | 0   | 0   | 0   | 0    | 1      | 0    | Х   | Х   | Х   | 64/32      | 420000H-42FFFFH | 210000H-217FFFH |

|            |            | BA72  | 1   | 0   | 0   | 0   | 0    | 0      | 1    | Х   | Х   | Х   | 64/32      | 410000H-41FFFFH | 208000H-20FFFFH |

|            |            | BA71  | 1   | 0   | 0   | 0   | 0    | 0      | 0    | Х   | Х   | Х   | 64/32      | 400000H-40FFFFH | 200000H-207FFFH |

| KAB        | KAB        |       |     |     | -   | E   | Block A | ddress | 5   |     |     |     | Block Size | Addres          | s Range         |

|------------|------------|-------|-----|-----|-----|-----|---------|--------|-----|-----|-----|-----|------------|-----------------|-----------------|

| 01D1<br>00 | 03D1<br>00 | Block | A21 | A20 | A19 | A18 | A17     | A16    | A15 | A14 | A13 | A12 | (KB/KW)    | Byte Mode       | Word Mode       |

|            |            | BA70  | 0   | 1   | 1   | 1   | 1       | 1      | 1   | Х   | Х   | Х   | 64/32      | 3F0000H-3FFFFFH | 1F8000H-1FFFFFH |

|            |            | BA69  | 0   | 1   | 1   | 1   | 1       | 1      | 0   | Х   | Х   | Х   | 64/32      | 3E0000H-3EFFFFH | 1F0000H-1F7FFFH |

|            |            | BA68  | 0   | 1   | 1   | 1   | 1       | 0      | 1   | Х   | Х   | Х   | 64/32      | 3D0000H-3DFFFFH | 1E8000H-1EFFFFH |

|            |            | BA67  | 0   | 1   | 1   | 1   | 1       | 0      | 0   | Х   | Х   | Х   | 64/32      | 3C0000H-3CFFFFH | 1E0000H-1E7FFFH |

|            |            | BA66  | 0   | 1   | 1   | 1   | 0       | 1      | 1   | Х   | Х   | Х   | 64/32      | 3B0000H-3BFFFFH | 1D8000H-1DFFFFH |

|            |            | BA65  | 0   | 1   | 1   | 1   | 0       | 1      | 0   | Х   | Х   | Х   | 64/32      | 3A0000H-3AFFFFH | 1D0000H-1D7FFFH |

|            |            | BA64  | 0   | 1   | 1   | 1   | 0       | 0      | 1   | х   | х   | х   | 64/32      | 390000H-39FFFFH | 1C8000H-1CFFFFH |

|            |            | BA63  | 0   | 1   | 1   | 1   | 0       | 0      | 0   | Х   | Х   | Х   | 64/32      | 380000H-38FFFFH | 1C0000H-1C7FFFH |

|            |            | BA62  | 0   | 1   | 1   | 0   | 1       | 1      | 1   | х   | х   | Х   | 64/32      | 370000H-37FFFFH | 1B8000H-1BFFFFH |

|            |            | BA61  | 0   | 1   | 1   | 0   | 1       | 1      | 0   | х   | х   | х   | 64/32      | 360000H-36FFFFH | 1B0000H-1B7FFFH |

|            |            | BA60  | 0   | 1   | 1   | 0   | 1       | 0      | 1   | Х   | Х   | Х   | 64/32      | 350000H-35FFFFH | 1A8000H-1AFFFFH |

|            |            | BA59  | 0   | 1   | 1   | 0   | 1       | 0      | 0   | Х   | Х   | Х   | 64/32      | 340000H-34FFFFH | 1A0000H-1A7FFFH |

|            |            | BA58  | 0   | 1   | 1   | 0   | 0       | 1      | 1   | х   | х   | Х   | 64/32      | 330000H-33FFFFH | 198000H-19FFFFH |

|            |            | BA57  | 0   | 1   | 1   | 0   | 0       | 1      | 0   | Х   | Х   | Х   | 64/32      | 320000H-32FFFFH | 190000H-197FFFH |

|            |            | BA56  | 0   | 1   | 1   | 0   | 0       | 0      | 1   | Х   | Х   | Х   | 64/32      | 310000H-31FFFFH | 188000H-18FFFFH |

|            |            | BA55  | 0   | 1   | 1   | 0   | 0       | 0      | 0   | Х   | Х   | Х   | 64/32      | 300000H-30FFFFH | 180000H-187FFFH |

| Bank2      | Bank2      | BA54  | 0   | 1   | 0   | 1   | 1       | 1      | 1   | Х   | Х   | Х   | 64/32      | 2F0000H-2F1FFFH | 178000H-17FFFFH |

|            |            | BA53  | 0   | 1   | 0   | 1   | 1       | 1      | 0   | Х   | Х   | Х   | 64/32      | 2E0000H-2EFFFFH | 170000H-177FFFH |

|            | Bank1      | BA52  | 0   | 1   | 0   | 1   | 1       | 0      | 1   | Х   | Х   | Х   | 64/32      | 2D0000H-2DFFFFH | 168000H-16FFFFH |

|            |            | BA51  | 0   | 1   | 0   | 1   | 1       | 0      | 0   | Х   | Х   | Х   | 64/32      | 2C0000H-2CFFFFH | 160000H-167FFFH |

|            |            | BA50  | 0   | 1   | 0   | 1   | 0       | 1      | 1   | Х   | Х   | Х   | 64/32      | 2B0000H-2BFFFFH | 158000H-15FFFFH |

|            |            | BA49  | 0   | 1   | 0   | 1   | 0       | 1      | 0   | Х   | Х   | Х   | 64/32      | 2A0000H-2AFFFFH | 150000H-157FFFH |

|            |            | BA48  | 0   | 1   | 0   | 1   | 0       | 0      | 1   | Х   | Х   | Х   | 64/32      | 290000H-29FFFFH | 148000H-14FFFFH |

|            |            | BA47  | 0   | 1   | 0   | 1   | 0       | 0      | 0   | Х   | Х   | Х   | 64/32      | 280000H-28FFFFH | 140000H-147FFFH |

|            |            | BA46  | 0   | 1   | 0   | 0   | 1       | 1      | 1   | Х   | Х   | Х   | 64/32      | 270000H-27FFFFH | 138000H-13FFFFH |

|            |            | BA45  | 0   | 1   | 0   | 0   | 1       | 1      | 0   | Х   | Х   | Х   | 64/32      | 260000H-26FFFFH | 130000H-137FFFH |

|            |            | BA44  | 0   | 1   | 0   | 0   | 1       | 0      | 1   | Х   | Х   | Х   | 64/32      | 250000H-25FFFFH | 128000H-12FFFFH |

|            |            | BA43  | 0   | 1   | 0   | 0   | 1       | 0      | 0   | Х   | Х   | Х   | 64/32      | 240000H-24FFFFH | 120000H-127FFFH |

|            |            | BA42  | 0   | 1   | 0   | 0   | 0       | 1      | 1   | х   | х   | х   | 64/32      | 230000H-23FFFFH | 118000H-11FFFFH |

|            |            | BA41  | 0   | 1   | 0   | 0   | 0       | 1      | 0   | Х   | х   | Х   | 64/32      | 220000H-22FFFFH | 110000H-117FFFH |

|            |            | BA40  | 0   | 1   | 0   | 0   | 0       | 0      | 1   | х   | х   | Х   | 64/32      | 210000H-21FFFFH | 108000H-10FFFFH |

|            |            | BA39  | 0   | 1   | 0   | 0   | 0       | 0      | 0   | Х   | Х   | Х   | 64/32      | 200000H-20FFFH  | 100000H-107FFFH |

|            |            | BA38  | 0   | 0   | 1   | 1   | 1       | 1      | 1   | Х   | Х   | Х   | 64/32      | 1F0000H-1FFFFH  | 0F8000H-0FFFFH  |

| Bank1      |            | BA37  | 0   | 0   | 1   | 1   | 1       | 1      | 0   | Х   | х   | Х   | 64/32      | 1E0000H-1EFFFFH | 0F0000H-0F7FFH  |

|            |            | BA36  | 0   | 0   | 1   | 1   | 1       | 0      | 1   | Х   | Х   | Х   | 64/32      | 1D0000H-1DFFFFH | 0E8000H-0EFFFFH |

|            |            | BA35  | 0   | 0   | 1   | 1   | 1       | 0      | 0   | Х   | Х   | Х   | 64/32      | 1C0000H-1CFFFFH | 0E0000H-0E7FFFH |

# Table 3. NOR Flash Memory Bottom Block Address (KAB01D100/KAB03D100)

| KAB        | KAB        | Black |     |     |     | l   | Block A | ddress | 5   | -   |     | -   | Block Size | Addres          | s Range         |

|------------|------------|-------|-----|-----|-----|-----|---------|--------|-----|-----|-----|-----|------------|-----------------|-----------------|

| 01D1<br>00 | 03D1<br>00 | Block | A21 | A20 | A19 | A18 | A17     | A16    | A15 | A14 | A13 | A12 | (KB/KW)    | Byte Mode       | Word Mode       |

|            |            | BA34  | 0   | 0   | 1   | 1   | 0       | 1      | 1   | Х   | Х   | Х   | 64/32      | 1B0000H-1BFFFFH | 0D8000H-0DFFFFH |

|            |            | BA33  | 0   | 0   | 1   | 1   | 0       | 1      | 0   | Х   | Х   | Х   | 64/32      | 1A0000H-1AFFFFH | 0D0000H-0D7FFFH |

|            |            | BA32  | 0   | 0   | 1   | 1   | 0       | 0      | 1   | Х   | Х   | Х   | 64/32      | 190000H-19FFFFH | 0C8000H-0CFFFFH |

|            |            | BA31  | 0   | 0   | 1   | 1   | 0       | 0      | 0   | Х   | Х   | Х   | 64/32      | 180000H-18FFFFH | 0C0000H-0C7FFFH |

|            |            | BA30  | 0   | 0   | 1   | 0   | 1       | 1      | 1   | Х   | Х   | Х   | 64/32      | 170000H-17FFFFH | 0B8000H-0BFFFFH |

|            |            | BA29  | 0   | 0   | 1   | 0   | 1       | 1      | 0   | Х   | Х   | Х   | 64/32      | 160000H-16FFFH  | 0B0000H-0B7FFFH |

|            |            | BA28  | 0   | 0   | 1   | 0   | 1       | 0      | 1   | Х   | Х   | Х   | 64/32      | 150000H-15FFFFH | 0A8000H-0AFFFFH |

|            |            | BA27  | 0   | 0   | 1   | 0   | 1       | 0      | 0   | Х   | Х   | Х   | 64/32      | 140000H-14FFFFH | 0A0000H-0A7FFFH |

|            |            | BA26  | 0   | 0   | 1   | 0   | 0       | 1      | 1   | Х   | Х   | Х   | 64/32      | 130000H-13FFFFH | 098000H-09FFFFH |

|            |            | BA25  | 0   | 0   | 1   | 0   | 0       | 1      | 0   | Х   | Х   | Х   | 64/32      | 120000H-12FFFFH | 090000H-097FFFH |

|            |            | BA24  | 0   | 0   | 1   | 0   | 0       | 0      | 1   | Х   | Х   | Х   | 64/32      | 110000H-11FFFFH | 088000H-08FFFFH |

|            |            | BA23  | 0   | 0   | 1   | 0   | 0       | 0      | 0   | Х   | Х   | Х   | 64/32      | 100000H-10FFFFH | 080000H-087FFFH |

|            |            | BA22  | 0   | 0   | 0   | 1   | 1       | 1      | 1   | Х   | Х   | Х   | 64/32      | 0F0000H-0FFFFFH | 078000H-07FFFFH |

|            |            | BA21  | 0   | 0   | 0   | 1   | 1       | 1      | 0   | Х   | Х   | Х   | 64/32      | 0E0000H-0EFFFFH | 070000H-077FFFH |

|            |            | BA20  | 0   | 0   | 0   | 1   | 1       | 0      | 1   | Х   | Х   | Х   | 64/32      | 0D0000H-0DFFFFH | 068000H-06FFFFH |

|            |            | BA19  | 0   | 0   | 0   | 1   | 1       | 0      | 0   | Х   | Х   | Х   | 64/32      | 0C0000H-0CFFFFH | 060000H-067FFFH |

|            |            | BA18  | 0   | 0   | 0   | 1   | 0       | 1      | 1   | Х   | х   | Х   | 64/32      | 0B0000H-0BFFFFH | 058000H-05FFFFH |

| Bank1      | Bank1      | BA17  | 0   | 0   | 0   | 1   | 0       | 1      | 0   | Х   | Х   | Х   | 64/32      | 0A0000H-0AFFFFH | 050000H-057FFFH |

|            |            | BA16  | 0   | 0   | 0   | 1   | 0       | 0      | 1   | Х   | Х   | Х   | 64/32      | 090000H-09FFFFH | 048000H-04FFFFH |

|            |            | BA15  | 0   | 0   | 0   | 1   | 0       | 0      | 0   | Х   | Х   | Х   | 64/32      | 080000H-08FFFFH | 040000H-047FFFH |

|            |            | BA14  | 0   | 0   | 0   | 0   | 1       | 1      | 1   | Х   | Х   | Х   | 64/32      | 070000H-07FFFH  | 038000H-03FFFFH |

|            |            | BA13  | 0   | 0   | 0   | 0   | 1       | 1      | 0   | Х   | Х   | Х   | 64/32      | 060000H-06FFFFH | 030000H-037FFFH |

|            |            | BA12  | 0   | 0   | 0   | 0   | 1       | 0      | 1   | Х   | х   | Х   | 64/32      | 050000H-05FFFFH | 028000H-02FFFFH |

|            |            | BA11  | 0   | 0   | 0   | 0   | 1       | 0      | 0   | Х   | х   | Х   | 64/32      | 040000H-04FFFFH | 020000H-027FFFH |

|            |            | BA10  | 0   | 0   | 0   | 0   | 0       | 1      | 1   | Х   | Х   | Х   | 64/32      | 030000H-03FFFFH | 018000H-01FFFFH |

|            |            | BA9   | 0   | 0   | 0   | 0   | 0       | 1      | 0   | Х   | х   | Х   | 64/32      | 020000H-02FFFFH | 010000H-017FFFH |

|            |            | BA8   | 0   | 0   | 0   | 0   | 0       | 0      | 1   | Х   | х   | Х   | 64/32      | 010000H-01FFFFH | 008000H-00FFFFH |

|            |            | BA7   | 0   | 0   | 0   | 0   | 0       | 0      | 0   | 1   | 1   | 1   | 8/4        | 00E000H-00FFFFH | 007000H-007FFFH |

|            |            | BA6   | 0   | 0   | 0   | 0   | 0       | 0      | 0   | 1   | 1   | 0   | 8/4        | 00C000H-00DFFFH | 006000H-006FFFH |

|            |            | BA5   | 0   | 0   | 0   | 0   | 0       | 0      | 0   | 1   | 0   | 1   | 8/4        | 00A000H-00BFFFH | 005000H-005FFFH |

|            |            | BA4   | 0   | 0   | 0   | 0   | 0       | 0      | 0   | 1   | 0   | 0   | 8/4        | 008000H-009FFFH | 004000H-004FFFH |

|            |            | BA3   | 0   | 0   | 0   | 0   | 0       | 0      | 0   | 0   | 1   | 1   | 8/4        | 006000H-007FFFH | 003000H-003FFFH |

|            |            | BA2   | 0   | 0   | 0   | 0   | 0       | 0      | 0   | 0   | 1   | 0   | 8/4        | 004000H-005FFFH | 002000H-002FFFH |

|            |            | BA1   | 0   | 0   | 0   | 0   | 0       | 0      | 0   | 0   | 0   | 1   | 8/4        | 002000H-003FFFH | 001000H-001FFFH |

|            |            | BA0   | 0   | 0   | 0   | 0   | 0       | 0      | 0   | 0   | 0   | 0   | 8/4        | 000000H-001FFFH | 000000H-000FFFH |

NOTE: The bank address bits are A21 ~ A20 for KAB01D100, A21 for KAB04D100.

### Table 4. Secode Block Addresses for Bottom Boot Devices

| Device              | Block Address | Block | (X8)            | (X16)           |

|---------------------|---------------|-------|-----------------|-----------------|

|                     | A21-A12       | Size  | Address Range   | Address Range   |

| KAB01D100/KAB03D100 | 000000xxx     | 64/32 | 000000H-00FFFFH | 000000H-007FFFH |

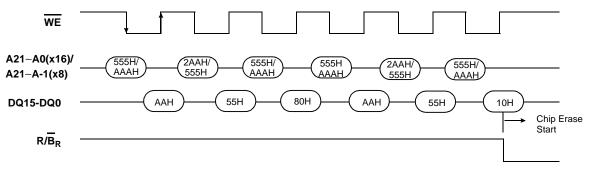

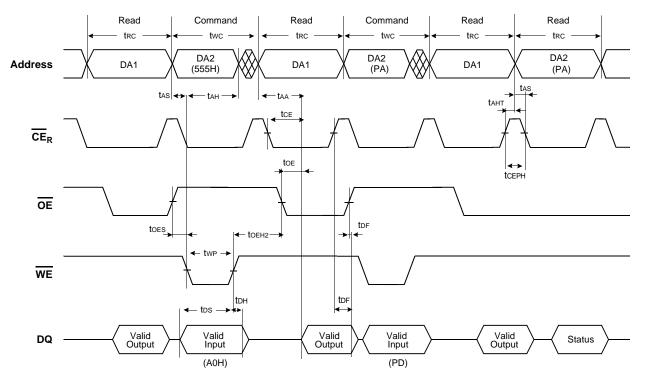

# NOR FLASH MEMORY COMMAND DEFINITIONS

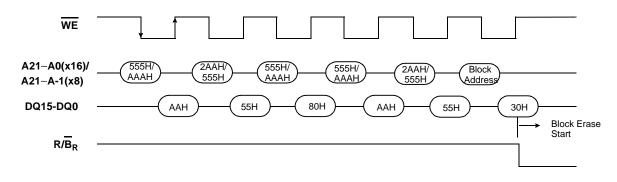

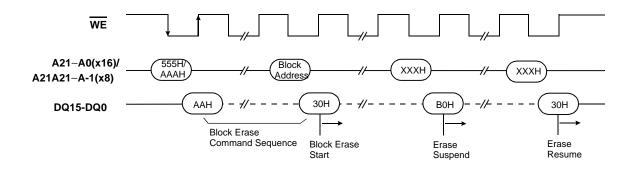

The NOR Flash Memory operates by selecting and executing its operational modes. Each operational mode has its own command set. In order to select a certain mode, a proper command with specific address and data sequences must be written into the command register. Writing incorrect information which include address and data or writing an improper command will reset the device to the read mode. The defined valid register command sequences are stated in Table 5. Note that Erase Suspend (B0H) and Erase Resume (30H) commands are valid only while the Block Erase Operation is in progress.

### **Table 5. Command Sequences**

|                                 |       | Cuala | 1st C | ycle | 2nd ( | Cycle | 3rd C       | Cycle       | 4th C        | Cycle       | 5th C | Cycle | 6th C | Cycle |

|---------------------------------|-------|-------|-------|------|-------|-------|-------------|-------------|--------------|-------------|-------|-------|-------|-------|

| Command Seq                     | uence | Cycle | Word  | Byte | Word  | Byte  | Word        | Byte        | Word         | Byte        | Word  | Byte  | Word  | Byte  |

|                                 | Addr  |       | R     | A    |       |       |             |             |              |             |       |       |       |       |

| Read                            | Data  | 1     | R     | D    |       |       |             |             |              |             |       |       |       |       |

|                                 | Addr  |       | XX    | хн   |       |       |             |             |              |             |       |       |       |       |

| Reset                           | Data  | 1     | F     | H    |       |       |             |             |              |             |       |       |       |       |

| Autoselect<br>Manufacturer      | Addr  | 4     | 555H  | AAAH | 2AAH  | 555H  | DA/<br>555H | DA/<br>AAAH | DA/<br>X00H  | DA/<br>X00H |       |       |       |       |

| ID (2,3)                        | Data  |       | AA    | λH   | 55    | БН    | 90          | ЭН          | EC           | СН          |       |       |       |       |

| Autoselect<br>Device Code       | Addr  | 4     | 555H  | AAAH | 2AAH  | 555H  | DA/<br>555H | DA/<br>AAAH | DA/<br>X01H  | DA/<br>X02H |       |       |       |       |

| (2,3)                           | Data  |       | AA    | λH   | 55    | 5H    | 90          | H           | (See T       | able 9)     |       |       |       |       |

| Autoselect<br>Block Group       | Addr  | 4     | 555H  | AAAH | 2AAH  | 555H  | DA/<br>555H | DA/<br>AAAH | BA /<br>X02H | BA/<br>X04H |       |       |       |       |

| Protect Verify<br>(2,3)         | Data  |       | AA    | λH   | 55    | БН    | 90          | ЭН          | (See T       | able 9)     |       |       |       |       |

| Auto Select<br>Secode Block     | Addr  | 4     | 555H  | AAAH | 2AAH  | 555H  | DA/<br>555H | DA/<br>AAAH | DA /<br>X03H | DA/<br>X06H |       |       |       |       |

| Factory Protect<br>Verify (2,3) | Data  |       | AA    | λH   | 55    | 5H    | 90          | ЭH          | (See T       | able 9)     |       |       |       |       |

| Enter Secode                    | Addr  |       | 555H  | AAAH | 2AAH  | 555H  | 555H        | AAAH        |              |             |       |       |       |       |

| BlockRegion                     | Data  | 3     | AA    | λH   | 55    | 5H    | 88          | 3H          |              |             |       |       |       |       |

| Exit Secode                     | Addr  |       | 555H  | AAAH | 2AAH  | 555H  | 555H        | AAAH        | XX           | хн          |       |       |       |       |

| BlockRegion                     | Data  | 4     | AA    | λH   | 55    | 5H    | 90          | )H          | 00           | ЭН          |       |       |       |       |

| 2                               | Addr  |       | 555H  | AAAH | 2AAH  | 555H  | 555H        | AAAH        | Р            | A           |       |       |       |       |

| Program                         | Data  | 4     | AA    | λH   | 55    | БH    | A           | ЭH          | P            | D           |       |       |       |       |

| Lista els Diverses              | Addr  | 0     | 555H  | AAAH | 2AAH  | 555H  | 555H        | AAAH        |              |             |       |       |       |       |

| Unlock Bypass                   | Data  | 3     | AA    | λH   | 55    | БН    | 20          | ЭН          |              |             |       |       |       |       |

| Unlock Bypass                   | Addr  |       | XX    | ХН   | Р     | A     |             |             |              |             |       |       |       |       |

| Program                         | Data  | 2     | A     | )H   | Р     | D     |             |             |              |             |       |       |       |       |

| Unlock Bypass                   | Addr  |       | XX    | ХН   | XX    | ХН    |             |             |              |             |       |       |       |       |

| Reset                           | Data  | 2     | 90    | )H   | 00    | )H    |             |             |              |             |       |       |       |       |

|                                 | Addr  |       | 555H  | AAAH | 2AAH  | 555H  | 555H        | AAAH        | 555H         | AAAH        | 2AAH  | 555H  | 555H  | AAAH  |

| Chip Erase                      | Data  | 6     | AA    | λH   | 55    | 5H    | 80          | )H          | AA           | λH          | 55    | 5H    | 10    | ЭН    |

|                                 | Addr  |       | 555H  | AAAH | 2AAH  | 555H  | 555H        | AAAH        | 555H         | AAAH        | 2AAH  | 555H  | В     | A     |

| Block Erase                     | Data  | 6     | AA    | λH   | 55    | 5H    | 80          | )H          | AA           | λΗ          | 55    | 5H    | 30    | ЭН    |

| Block Erase                     | Addr  | -     | XX    | XH   |       |       |             |             |              |             |       |       |       |       |

| Suspend (4, 5)                  | Data  | 1     | B     | )H   |       |       |             |             |              |             |       |       |       |       |

| Block Erase                     | Addr  |       | ХХ    | ХН   |       |       |             |             |              |             |       |       |       |       |

| Resume                          | Data  | 1     | 30    | )H   |       |       |             |             |              |             |       |       |       |       |

|                                 | Addr  |       | 55H   | AAH  |       |       |             |             |              |             |       |       |       |       |

| CFI Query (6)                   | Data  | 1     | 98    | 3H   |       |       |             |             |              |             |       |       |       |       |

NOTES: 1. RA : Read Address, PA : Program Address, RD : Read Data, PD : Program Data DA : Dual Bank Address (A20 - A21), BA : Block Address (A12 - A21), X = Don't care .

- 2. To terminate the Autoselect Mode, it is necessary to write Reset command to the register.

- 3. The 4th cycle data of Autoselect mode is output data.

- The 3rd and 4th cycle bank addresses of Autoselect mode must be same.

- 4. The Read / Program operations at non-erasing blocks and the autoselect mode are allowed in the Erase Suspend mode.

- 5. The Erase Suspend command is applicable only to the Block Erase operation.

- 6. Command is valid when the device is in read mode or Autoselect mode. 7. DQ8 - DQ15 are don't care in command sequence, but RD and PD is excluded.

- 8. A11 A21 are also don't care, except for the case of special notice.

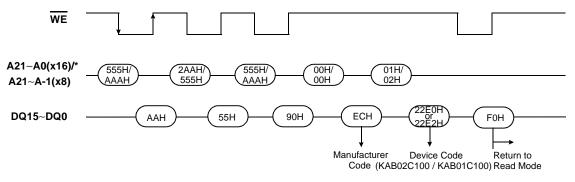

### Table 6. NOR Flash Memory Autoselect Codes

| Description                               | DQ8 to     | DQ15       | DQ7 to DQ0                                        |

|-------------------------------------------|------------|------------|---------------------------------------------------|

| Description                               | BYTE = VIH | BYTE = VIL |                                                   |

| Manufacturer ID                           | Х          | Х          | ECH                                               |

| Device Code KAB02D100 (Top Boot Block)    | 22H        | х          | ЕОН                                               |

| Device Code KAB01D100 (Bottom Boot Block) | 22H        | Х          | E2H                                               |

| Device Code KAB04D100 (Top Boot Block)    | 22H        | Х          | E1H                                               |

| Device Code KAB03D100 (Bottom Boot Block) | 22H        | Х          | E3H                                               |

| Block Protection Verification             | x          | х          | 01H (Protected),<br>00H (Unprotected)             |

| Secode Block Indicator Bit (DQ7)          | х          | Х          | 80H (Factory locked),<br>00H (Not factory locked) |

NOTES: 1. L=Logic Low=VIL, H=Logic High=VIH, DA=Dual Bank Address, BA=Block Address, X=Don't care. 2. Secode Block : Security Code Block.

# NAND FLASH PRODUCT INTRODUCTION

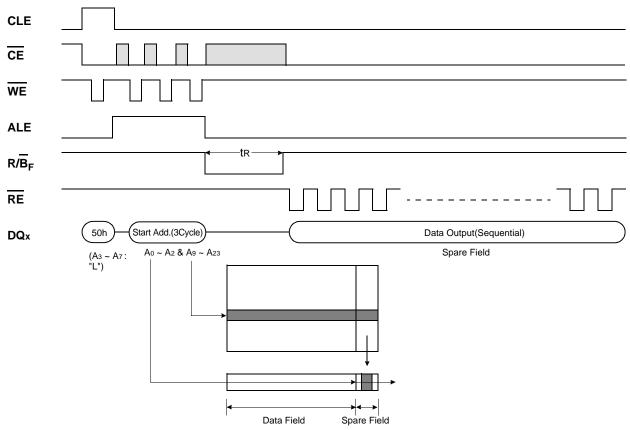

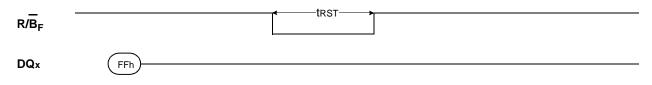

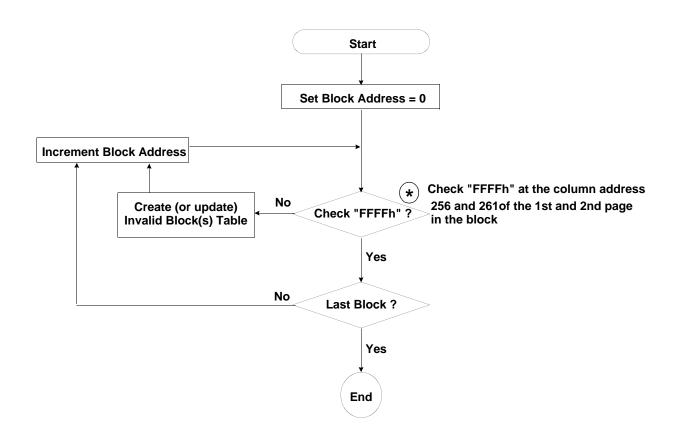

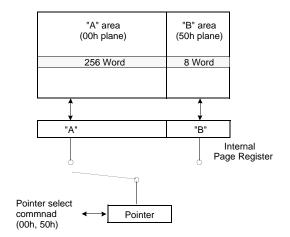

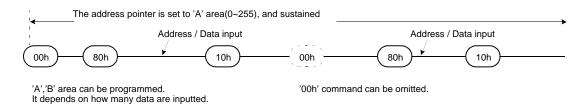

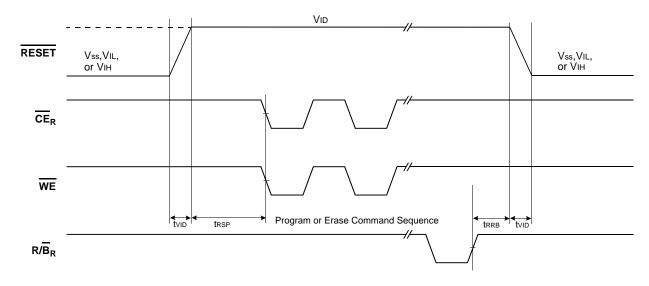

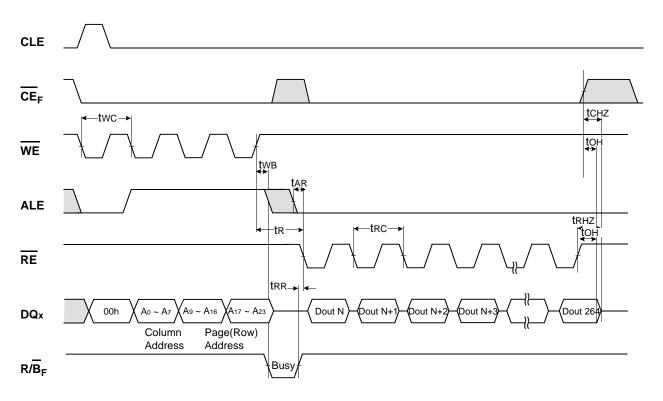

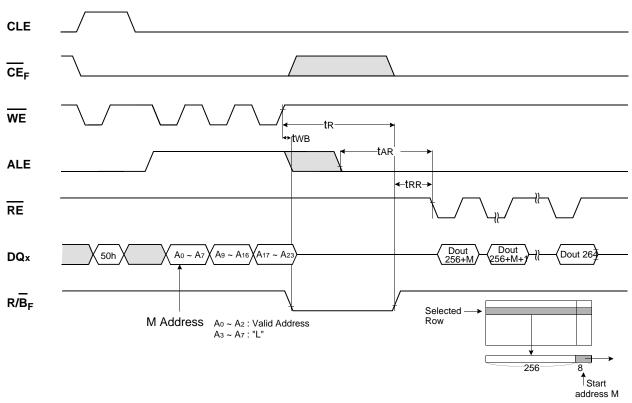

The NAND Flash Memory is a 132Mbit(138,412,032 bit) memory organized as 32,768 rows(pages) by 264 columns. Spare 8 columns are located in 256 to 263 column address. A 264-word data register is connected to memory cell arrays accommodating data transfer between the I/O buffers and memory during page read and page program operations. The memory array is made up of 16 cells that are serially connected like NAND structure. Each of the 16 cells resides in a different page. A block consists of the 32 pages formed by one NAND structures, totaling 8,448 NAND structures of 16 cells. The array organization is shown in Figure 2. Program and read operations are executed on a page basis, while erase operation is executed on a block basis. The memory array consists of 1024 blocks, and a block is separately erasable by 8K-word unit. It indicates that the bit by bit erase operation is prohibited on the NAND Flash Memory.

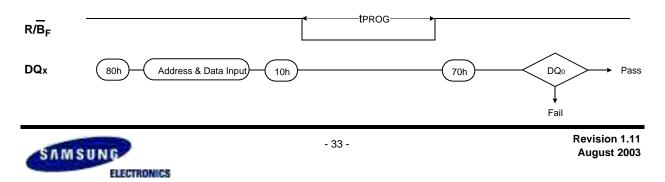

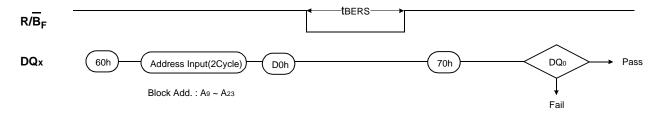

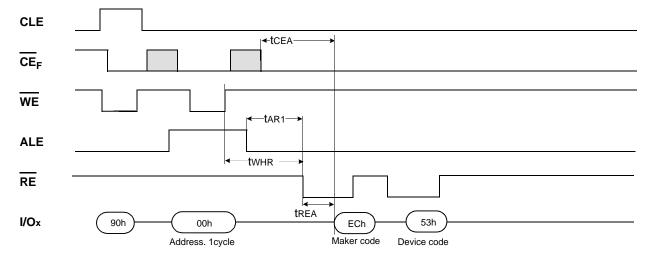

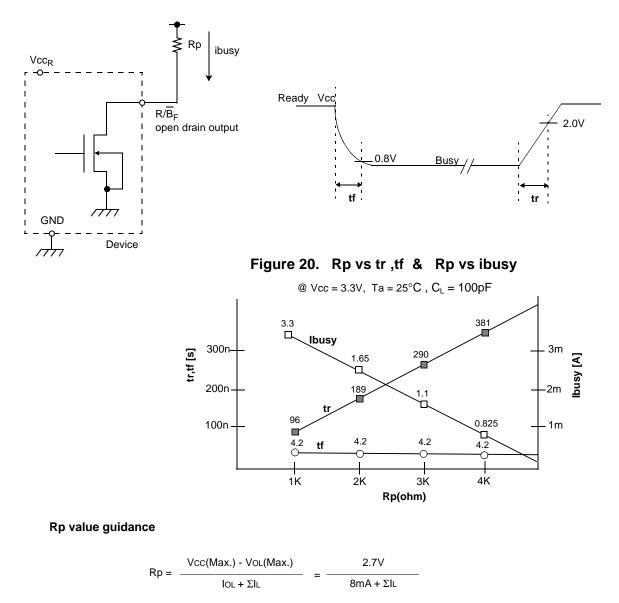

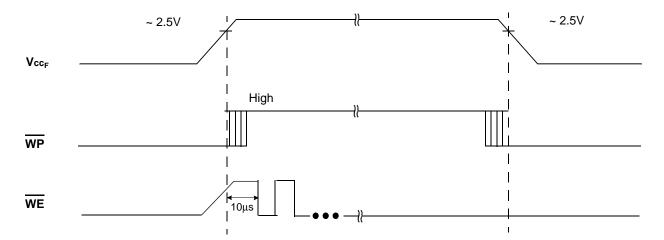

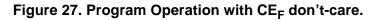

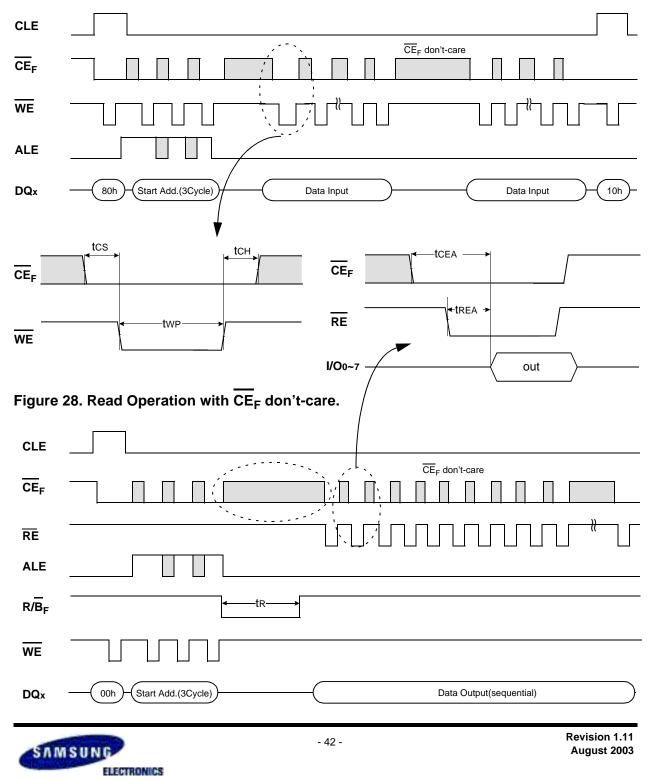

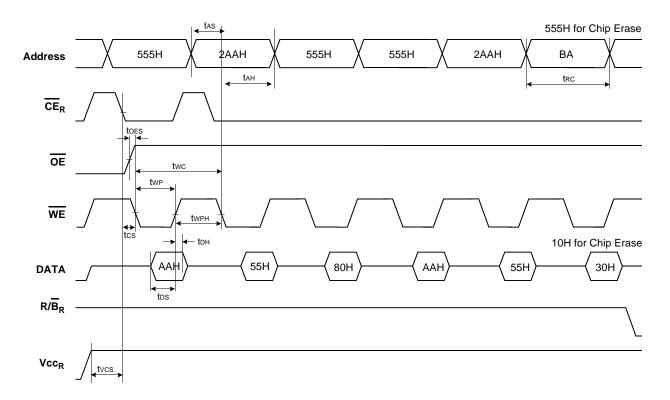

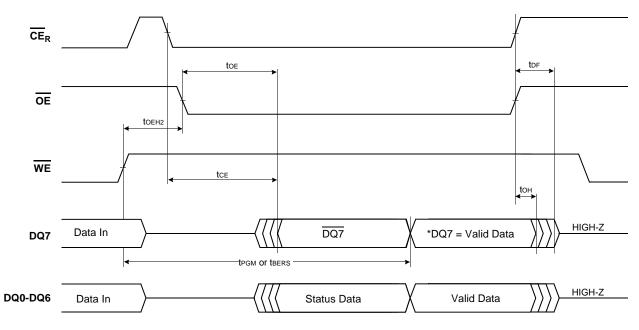

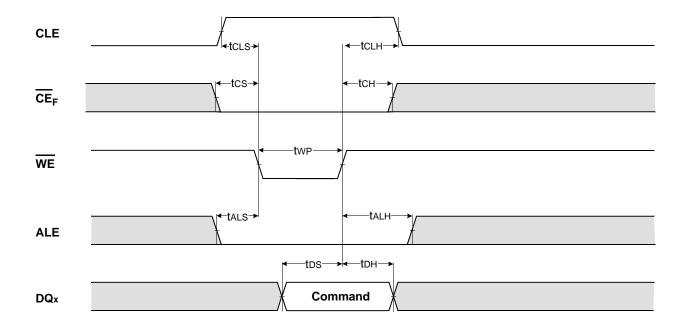

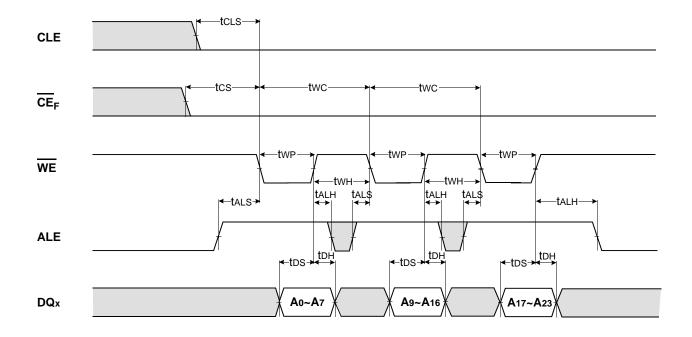

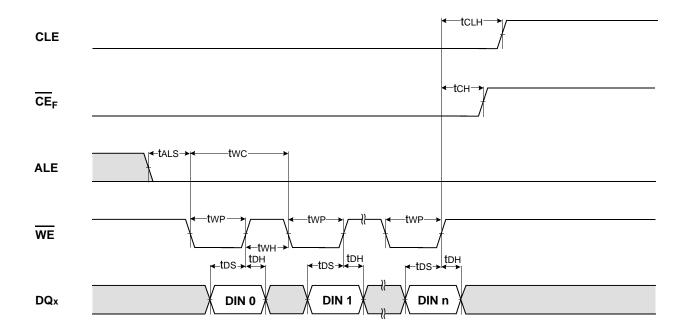

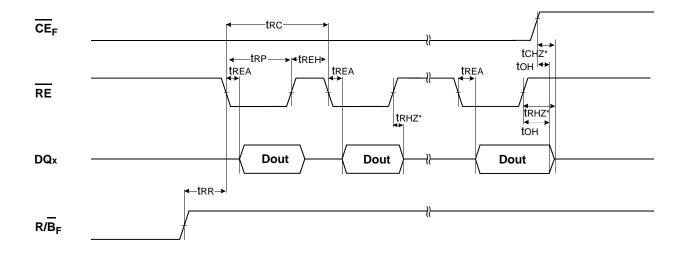

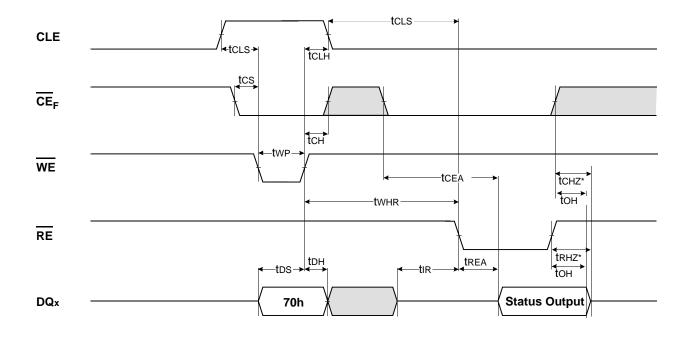

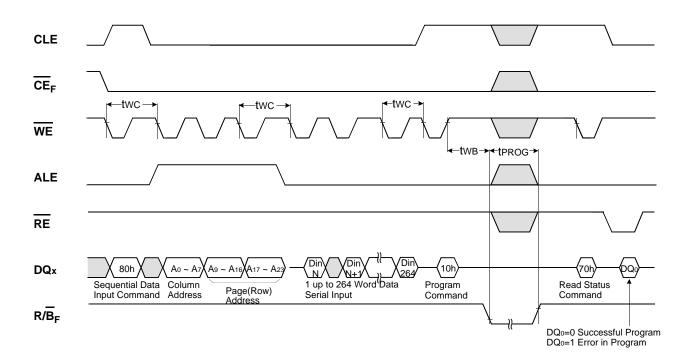

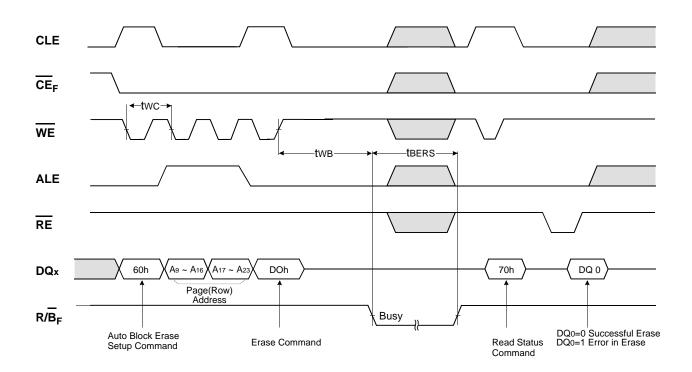

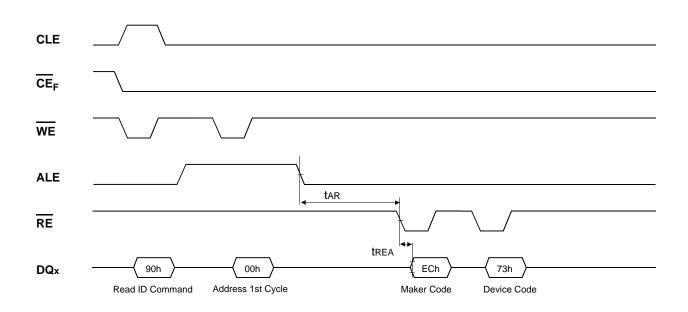

The NAND Flash Memory has addresses multiplexed with lower 8 I/O's. The NAND Flash Memory allows sixteen bit wide data transfer into and out of page registers. This scheme dramatically reduces pin counts and allows systems upgrades to future densities by maintaining consistency in system board design. Command, address and data are all written through I/O's by bringing WE to low while CE is low. Data is latched on the rising edge of WE. Command Latch Enable(CLE) and Address Latch Enable(ALE) are used to multiplex command and address respectively, via the I/O pins. All commands require one bus cycle except Page Program command and Block Erase command which require two cycles: one cycle for setup and another for execution. The 8M word physical space requires 24 addresses, thereby requiring three cycles for byte-level addressing: column address, low row address and high row address, in that order. Page Read and Page Program need the same three address cycles following required command input. In Block Erase operation, however, only two row address cycles are used. Device operations are selected by writing specific commands into command register. Table 7 defines the specific commands of the NAND Flash Memory.

| Function     | 1st. Cycle | 2nd. Cycle | Acceptable Command during Busy |

|--------------|------------|------------|--------------------------------|

| Read 1       | 00h        | -          |                                |

| Read 2       | 50h        | -          |                                |

| Read ID      | 90h        | -          |                                |

| Reset        | FFh        | -          | 0                              |

| Page Program | 80h        | 10h        |                                |

| Block Erase  | 60h        | D0h        |                                |

| Read Status  | 70h        | -          | 0                              |

## Table 7. Command Sets

# Table 8. NOR Flash Operations Table

| Opera                     | ation |                            | OE | WE | BYTE | WP/<br>ACC | A9 | A6 | A1 | A0 | DQ15/<br>A-1 | DQ8/<br>DQ14 | DQ0/<br>DQ7 | RESET |

|---------------------------|-------|----------------------------|----|----|------|------------|----|----|----|----|--------------|--------------|-------------|-------|

| Read                      | word  | L                          | L  | н  | н    | L/H        | A9 | A6 | A1 | A0 | DQ15         | Dout         | Dout        | н     |

| Read                      | byte  | L                          | L  | н  | L    | L/H        | A9 | A6 | A1 | A0 | A-1          | High-Z       | Dout        | н     |

| Stand-by                  |       | Vcc <sub>R</sub> ±<br>0.3V | х  | х  | х    | (2)        | х  | х  | х  | х  | High-Z       | High-Z       | High-Z      | (2)   |

| Output Dis                | able  | L                          | н  | н  | х    | L/H        | Х  | Х  | Х  | Х  | High-Z       | High-Z       | High-Z      | н     |

| Reset                     |       | Х                          | Х  | Х  | х    | L/H        | Х  | Х  | Х  | Х  | High-Z       | High-Z       | High-Z      | L     |

| Write                     | word  | L                          | н  | L  | н    |            | A9 | A6 | A1 | A0 | Din          | Din          | Din         | н     |

| white                     | byte  | L                          | н  | L  | L    | (4)        | A9 | A6 | A1 | A0 | A-1          | High-Z       | Din         | н     |

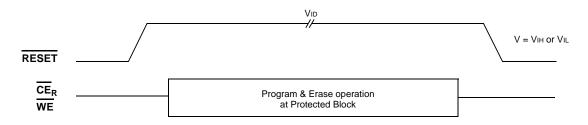

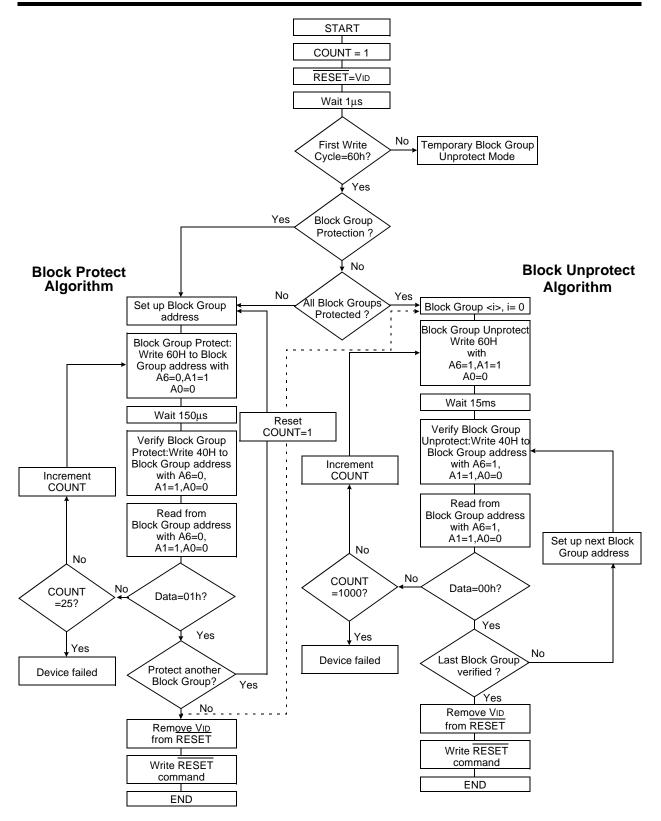

| Enable Blo<br>Protect (3) |       | L                          | н  | L  | х    | L/H        | х  | L  | н  | L  | х            | х            | DIN         | Vid   |

| Enable Blo<br>Unprotect   |       | L                          | н  | L  | х    | (4)        | х  | Н  | н  | L  | х            | х            | DIN         | Vid   |

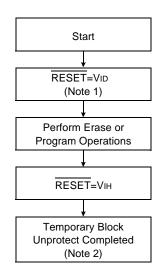

| Temporary<br>Group        | Block | х                          | х  | х  | х    | (4)        | х  | х  | х  | х  | х            | х            | х           | Vid   |

#### NOTES:

- 1. L = VIL (Low), H = VIH (High), VID =  $8.5V \sim 12.5V$ , DIN = Data in, DOUT = Data out, X = Don't care.

- 2.  $\overline{\text{WP}}/\text{ACC}$  and  $\overline{\text{RESET}}$  pin are asserted at  $\text{Vcc}_{\text{R}}\pm0.3$  V or  $\text{Vss}\pm0.3$  V in the Stand-by mode.

- 3. Addresses must be composed of the Block address (A12 A21). The Block Protect and Unprotect operations may be implemented via programming equipment too. Refer to the "Block Group Protection and Unprotection".

- 4. If WP/ACC=VII, the two outermost boot blocks is protected. If WP/ACC=VIH, the two outermost boot block protection depends on whether those blocks were last protected or unprotected using the method described in "Block Group Protection and Unprotection". If WP/ACC=VHH, all blocks will be temporarily unprotected.

| CLE | ALE              | CER | WE | RE | WP                                 |                      | Mode                  |

|-----|------------------|-----|----|----|------------------------------------|----------------------|-----------------------|

| Н   | L                | L   |    | Н  | Х                                  | Read Mode            | Command Input         |

| L   | Н                | L   |    | Н  | Х                                  | Read Mode            | Address Input(3clock) |

| Н   | L                | L   |    | Н  | Н                                  | Write Mode           | Command Input         |

| L   | Н                | L   |    | Н  | Н                                  |                      | Address Input(3clock) |

| L   | L                | L   |    | Н  | Н                                  | Data Input           |                       |

| L   | L                | L   | Н  | ₹  | Х                                  | Data Output          |                       |

| Х   | Х                | Х   | Х  | Н  | Х                                  | During Read(Busy)    |                       |

| Х   | Х                | Х   | Х  | Х  | Н                                  | During Program(Busy) |                       |

| Х   | Х                | Х   | Х  | Х  | Н                                  | During Erase(Busy)   |                       |

| Х   | X <sup>(1)</sup> | Х   | Х  | Х  | L                                  | Write Protect        |                       |

| Х   | Х                | Н   | Х  | Х  | 0V/Vcc <sub>F</sub> <sup>(2)</sup> | Stand-by             |                       |

# **Table 9. NAND Flash Operations Table**

NOTE: 1. X can be VIL or VIH.

2. WP should be biased to CMOS high or CMOS low for standby.

|                 | 01 0 1 1 / |                 | uliono          | Table           |                 |        |                 |                  |            |

|-----------------|------------|-----------------|-----------------|-----------------|-----------------|--------|-----------------|------------------|------------|

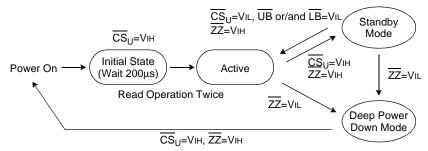

| <b>CS</b> u     | ZZ         | OE              | WE              | LB              | UB              | I/O0~7 | <b>I/O</b> 8~15 | Mode             | Power      |

| Н               | Н          | X <sup>1)</sup> | X <sup>1)</sup> | X <sup>1)</sup> | X <sup>1)</sup> | High-Z | High-Z          | Deselected       | Standby    |

| X <sup>1)</sup> | L          | X <sup>1)</sup> | X <sup>1)</sup> | X <sup>1)</sup> | X <sup>1)</sup> | High-Z | High-Z          | Deselected       | Deep Power |

| L               | Н          | X <sup>1)</sup> | X <sup>1)</sup> | н               | Н               | High-Z | High-Z          | Deselected       | Standby    |

| L               | Н          | Н               | н               | L               | X <sup>1)</sup> | High-Z | High-Z          | Output Disabled  | Active     |

| L               | н          | н               | Н               | X <sup>1)</sup> | L               | High-Z | High-Z          | Output Disabled  | Active     |

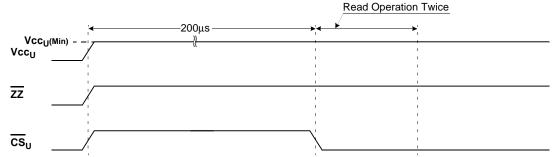

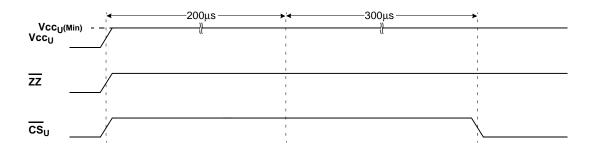

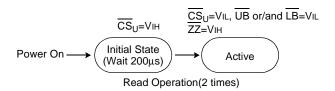

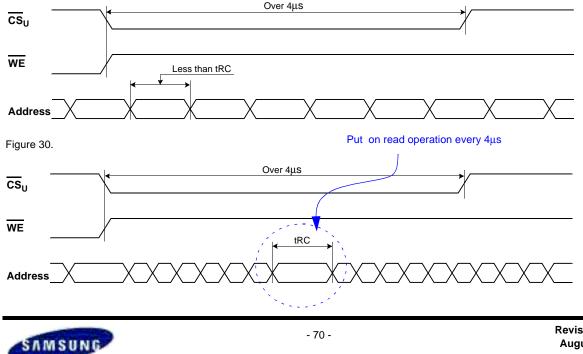

| L               | Н          | L               | Н               | L               | н               | Dout   | High-Z          | Lower Byte Read  | Active     |