# 24-Pin XOR AmPAL20XRP10 Family

24-Pin IMOX™ Programmable Array Logic (PAL) Elements

#### **Distinctive Characteristics**

- AND-OR-XOR logic structure

- AMD's superior IMOX technology

- Guarantees tpD = 20 ns max

- Individually programmable output polarity on each output

- Eight logical product terms per output

- Programming yields > 98% are realized via platinumsilicide fuse technology and the use of added test words

- Post Programming Functional Yield (PPFY) of 99.9%

- PRELOAD feature permits full logical verification

- Reliability assured through more than 70 billion fuse hours of life testing with no failures

- AC and DC parametric testing at the factory through on-board testing circuitry

- > 3000V ESD protection per pin

- JEDEC-Standard LCC and PLCC pinout

### **General Description**

AMD 24-pin XOR PAL devices are high-speed, electrically programmable array logic elements. They utilize the familiar sum-of-products (AND-OR-XOR) structure allowing users to program custom logic functions to fit most applications precisely. Typically they are a replacement for low-power Schottky SSI/MSI logic circuits that require an exclusive-OR function, reducing chip count by more than 5 to 1 and greatly simplifying prototyping and board layout.

Five different devices are available, including both registered and combinatorial devices. All devices have user-programmable output polarity on all outputs. A variety of speed options allow the designer maximum flexibility in matching precise system requirements. The Product Selector Guide below shows the available speed options. The second table gives details about the functionality of the five available devices.

Please see the following pages for Block Diagrams.

#### **Product Selector Guide**

AMD PAL Speed/Power Families

|                                                        | tpp<br>ns (Max.) |           | ts<br>ns (Min.) |           | t <sub>CO</sub><br>ns (Max.) |           | icc<br>mA (Max.) | I <sub>OL</sub><br>mA (Min.) |           |

|--------------------------------------------------------|------------------|-----------|-----------------|-----------|------------------------------|-----------|------------------|------------------------------|-----------|

| Family                                                 | C Devices        | M Devices | C Devices       | M Devices | C Devices                    | M Devices | C/M Devices      | C Devices                    | M Devices |

| Very High-Speed<br>(-20 & -25) Versions                | 20               | 25        | 20              | 25        | 13                           | 15        | 210              | 24                           | 12        |

| High-Speed<br>(-30 & -35) Versions                     | 30               | 35        | 30              | 35        | 15                           | 25        | 180              | 24                           | 12        |

| High-Speed,<br>Half-Power<br>(-30L & -35L)<br>Versions | 30               | 35        | 30              | 35        | 15                           | 25        | 105              | 24                           | 12        |

| Half-Power<br>(-40L & -45L)<br>Versions                | 40               | 45        | 40              | 45        | 30                           | 35        | 105              | 24                           | 12        |

| Part<br>Number | Array<br>Inputs                   | Logic                       | Output<br>Enable | Outputs/Polarity                       | Package<br>Pins |

|----------------|-----------------------------------|-----------------------------|------------------|----------------------------------------|-----------------|

| 22XP10         | 12 Dedicated,<br>10 Bidirectional | Ten (2-6)-Wide AND-OR-XOR   | Programmable     | Bidirectional/Programmable             | 24              |

|                | 10 Dedicated,                     | Four (2-6)-Wide AND-OR-XOR  | Dedicated        | Registered/Programmable                | 24              |

| 20XRP4         | 4 Feedback,<br>6 Bidirectional    | Six 8-Wide AND-OR           | Programmable     | rogrammable Bidirectional/Programmable |                 |

|                | 10 Dedicated,                     | Six (2-6)-Wide AND-OR-XOR   | Dedicated        | Registered/Programmable                | 24              |

| 20XRP6         | 6 Feedback,<br>4 Bidirectional    | Four 8-Wide AND-OR          | Programmable     | Bidirectional/Programmable             |                 |

|                | 10 Dedicated,                     | Eight (2-6)-Wide AND-OR-XOR | Dedicated        | Registered/Programmable                | 24              |

| 20XRP8         | 8 Feedback,<br>2 Bidirectional    | Two 8-Wide AND-OR           | Programmable     | Bidirectional/Programmable             |                 |

| 20XRP10        | 10 Dedicated,<br>10 Feedback      | Ten (2-6)-Wide AND-OR-XOR   | Dedicated        | Registered/Programmable                | 24              |

08655C/0 JANUARY 1988

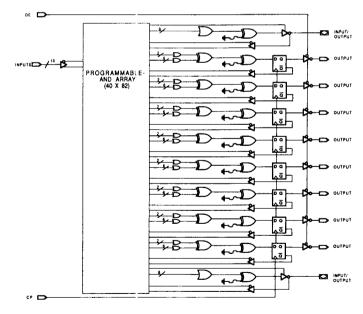

### **Block Diagrams**

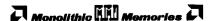

### AmPAL22XP10

LD000900

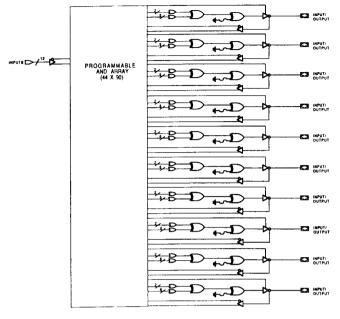

#### AmPAL20XRP4

LD000940

5-272

Monolithic Mil Memories

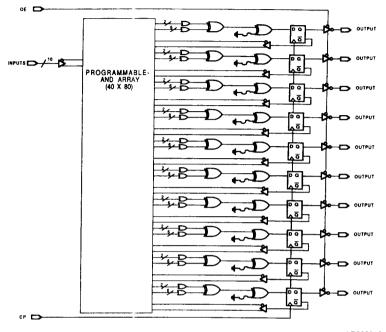

### **Block Diagrams** (Cont'd.)

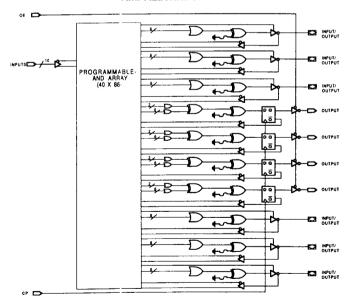

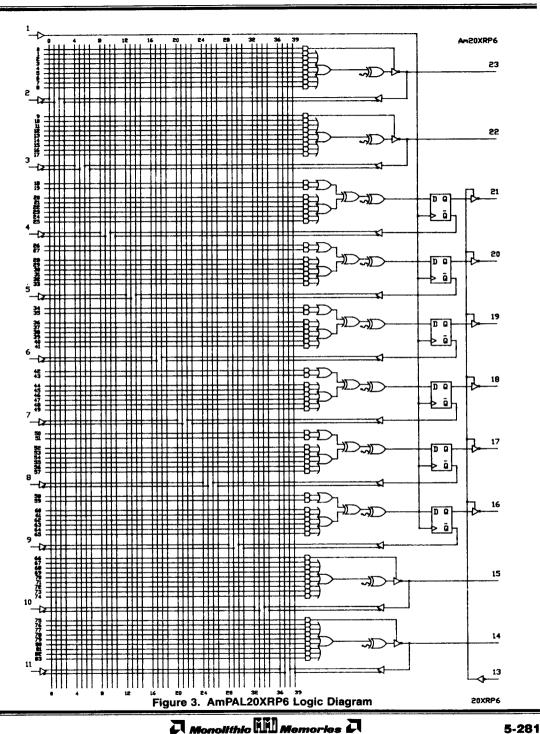

#### AmPAL20XRP6

LD000920

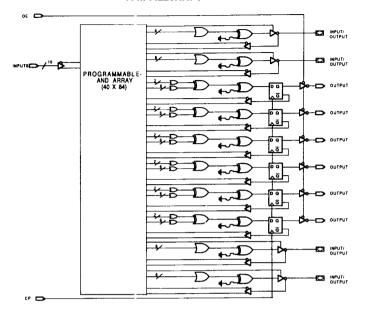

#### AmPAL20XRP8

LD000930

7 Monolithic MM Memories 7

### **Block Diagrams** (Cont'd.)

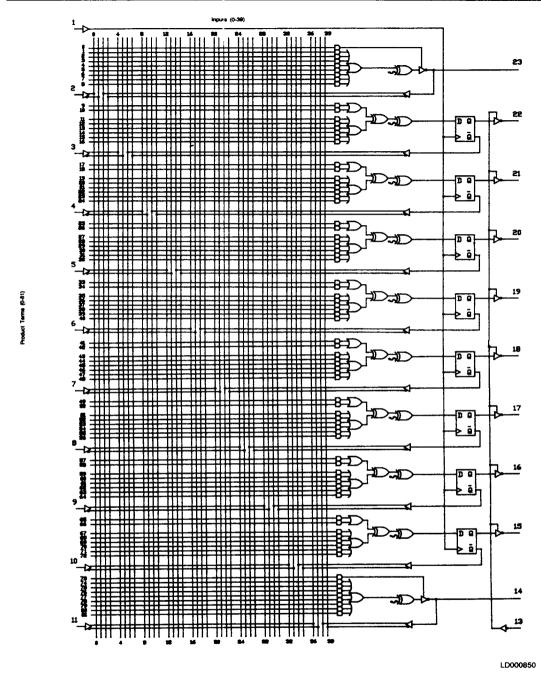

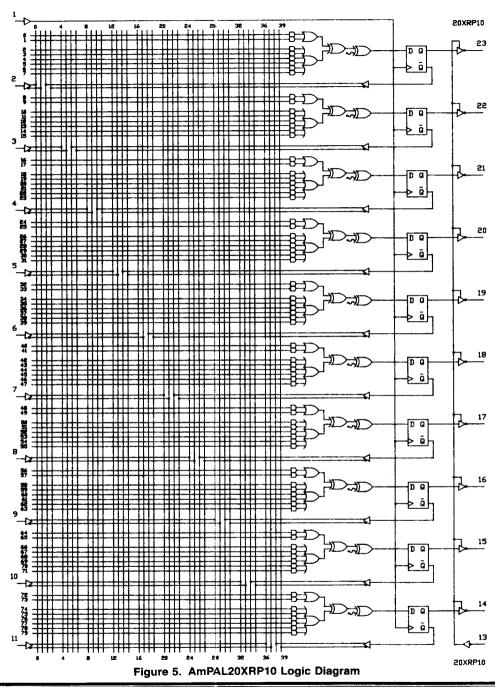

### AmPAL20XRP10

LD000910

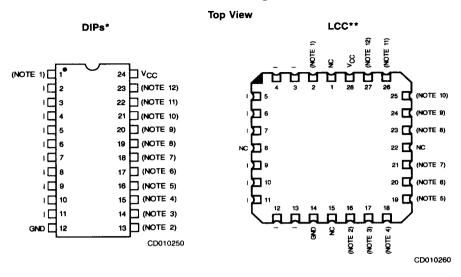

#### **Connection Diagrams**

Note: Pin 1 is marked for orientation.

Notes:

|    | 22XP10 | 20XRP4 | 20XRP6 | 20XRP8 | 20XRP10 |

|----|--------|--------|--------|--------|---------|

| 1  | ı      | CLK    | CLK    | CLK    | CLK     |

| 2  | ı      | OE     | OE     | OE     | OE      |

| 3  | 1/0    | 1/0    | 1/0    | 1/0    | 0       |

| 4  | 1/0    | 1/0    | 1/0    | 0      | 0       |

| 5  | 1/0    | 1/0    | 0      | 0      | 0       |

| 6  | 1/0    | 0      | 0      | 0      | 0       |

| 7  | 1/0    | 0      | 0      | 0      | 0       |

| 8  | 1/0    | 0      | 0      | 0      | 0       |

| 9  | 1/0    | 0      | 0      | 0      | 0       |

| 10 | 1/0    | 1/0    | 0      | 0      | 0       |

| 11 | 1/0    | 1/0    | 1/0    | 0      | 0       |

| 12 | 1/0    | 1/0    | 1/0    | 1/0    | 0       |

<sup>\*</sup>Also available in 24-Pin Ceramic Flatpack. Pinouts identical to DIPs.

### **Pin Designations**

i ≕ Input

I/O == Input/Output

O == Output

V<sub>CC</sub> = Supply Voltage

GND = Ground

CLK = Clock

OE = Output Enable

NC = No Connect

<sup>\*\*</sup>Also available in 28-Pin Plastic Leaded Chip Carrier. Pinouts identical to LCC.

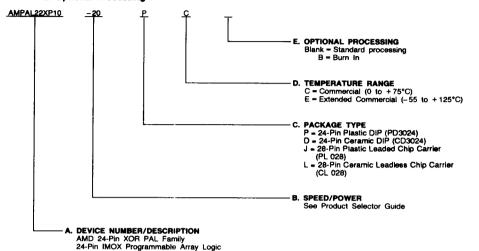

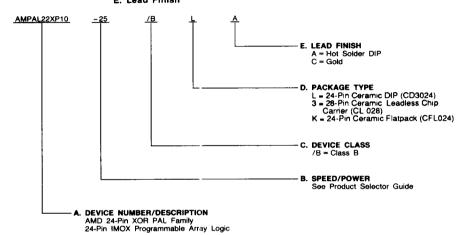

### **Ordering Information**

#### **Standard Products**

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: A. Device Number

- B. Speed Option (if applicable)

- C. Package Type

- D. Temperature Range

- E. Optional Processing

| Valid Combinations            | 3                   |

|-------------------------------|---------------------|

| AMPAL22XP10-20/-30/-30L/-40L  |                     |

| AMPAL20XRP4-20/-30/-30L/-40L  | 7 20 20             |

| AMPAL20XRP6-20/-30/-30L/-40L  | PC, DC,<br>DCB, DE, |

| AMPAL20XRP8-20/-30/-30L/-40L  | JC, LC, LE          |

| AMPAL20XRP10-20/-30/-30L/-40L |                     |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

### Ordering Information (Cont'd.)

#### **APL Products**

AMD products for Aereospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) for APL products is formed by a combination of:

- A. Device Number

- B. Speed Option (if applicable)

- C. Device Class

- D. Package Type

- E. Lead Finish

| Valid Combinations            |       |

|-------------------------------|-------|

| AMPAL22XP10-25/-35/-35L/-45L  |       |

| AMPAL20XRP4-25/-35/-35L/-45L  | /BLA. |

| AMPAL20XRP6-25/-35/-35L/-45L  | /B3A, |

| AMPAL20XRP8-25/-35/-35L/-45L  | /BKA  |

| AMPAL20XRP10-25/-35/-35L/-45L |       |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

#### **Group A Tests**

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, & 11

### **Functional Description**

# AMD 24-PIN XOR PAL20XRP10 Family Characteristics

All members of the AMD 24-Pin XOR PAL Family have common electrical characteristics and programming procedures. All parts are produced with a fusible link at each input to the AND gate array, and connections may be selectively removed by applying appropriate voltages to the circuit.

Initially the AND gates are connected, via fuses, to both the true and complement of each input. By selective programming of fuses the AND gates may be "connected" to only the true input (by blowing the complement fuse), to only the complement input (by blowing the true fuse), or to neither type of input (by blowing both fuses) establishing a logical "don't care." When both the true and complement fuses are left intact a logical false results on the output of the AND gate, while all fuses blown results in a logical true state. On the AmPAL22XP10 device, the AND gates are connected to fixed (2-6) OR-XOR structures whose outputs become device outputs. The remaining four (registered) devices function as follows: for combinatorial outputs, the AND gates are connected to fixed-OR gates whose outputs become device outputs. For registered outputs, the AND gates are connected to fixed (2-6) OR-XOR structures whose outputs become output register inputs.

All parts are fabricated with AMD's fast programming, highly reliable Platinum-Silicide Fuse technology. Utilizing an easily implemented programming algorithm, these products can be

rapidly programmed to any customized pattern. Extra test words are pre-programmed during manufacturing to insure extremely high field programming yields (> 98%), and provide extra test paths to achieve excellent parametric correlation.

#### Power-Up Reset

The registered devices in the AMD PAL family have been designed to reset during system power-up. Following power-up, all registers will be initialized to zero, setting all the outputs to a logic 1. This feature provides extra flexibility to the designer and is especially valuable in simplifying state machine initialization.

#### **PRELOAD**

AMD PAL devices are designed with unique PRELOAD circuitry that provides an easy method of testing registered devices for logical functionality. PRELOAD allows any arbitrary state value to be loaded into the registered output of an AMD PAL device.

A typical functional test sequence would be to verify all possible state transitions for the device being tested. This requires the ability to set the state registers into an arbitrary "present state" value and to set the device inputs to any arbitrary "present input" value. Once this is done, the state machine is clocked into a new state or "next state." The next state is then checked to validate the transition from the present state. In this way any state transition can be checked.

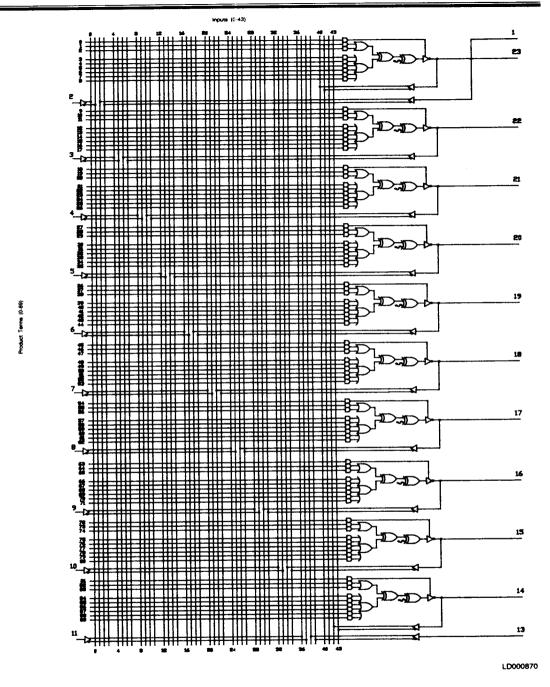

Figure 1. AmPAL22XP10 Logic Diagram

Monolithic IIII Memories

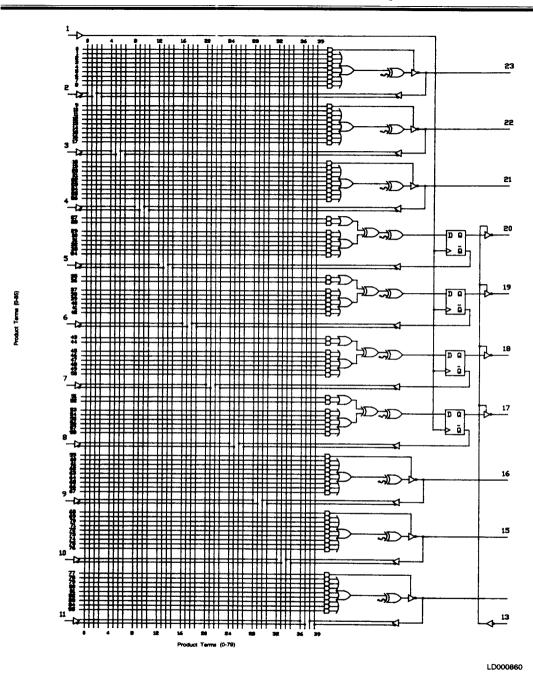

Figure 2. AmPAL20XRP4 Logic Diagram

Monolithic Memories

Powered by ICminer.com Electronic-Library Service CopyRight 2003

Figure 4. AmPAL20XRP8 Logic Diagram

Monolithia Memories 7

Monolithia Mil Memories

### 24-Pin XOR AmPAL20XRP10 Family

### **PRELOAD of Registered Outputs**

The AMD 24-pin XOR PAL devices incorporate circuitry to allow loading each register synchronously to either a HIGH or

LOW state. This feature simplifies testing since any initial state for the registers can be set to optimize test sequencing.

The pin levels and timing necessary to perform the PRELOAD function are detailed below:

| Par.            | Min. | Max. |

|-----------------|------|------|

| V <sub>HH</sub> | 10   | 12   |

| VILP            | 0    | 0.5  |

| VIHP            | 2.4  | 5.5  |

| Level forced on registered output<br>pin during PRELOAD cycle | Register Q output state after cycle |

|---------------------------------------------------------------|-------------------------------------|

| V <sub>IHP</sub>                                              | HIGH                                |

| VILP                                                          | LOW                                 |

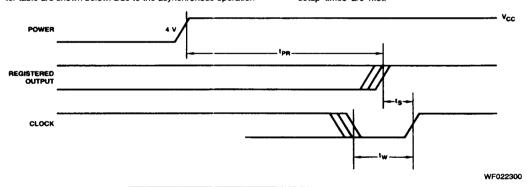

### **Power-Up Reset**

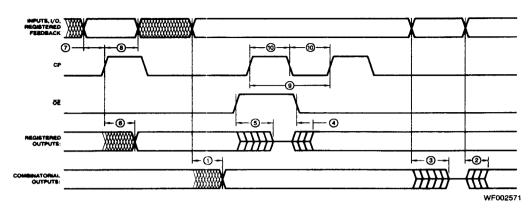

The registered devices in the AMD 24-Pin XOR PAL Family have been designed with the capability to reset during system power-up. Following power-up, all registers will be reset to LOW. The output state will be HIGH. This feature provides flexibility to the designer and is especially valuable in simplifying state-machine initialization. A timing diagram and parameter table are shown below. Due to the asynchronous operation

of the power-up RESET and the wide range of ways V<sub>CC</sub> can rise to its steady state, two conditions are required to ensure a valid power-up RESET. These conditions are:

- 1. The V<sub>CC</sub> rise must be monotonic.

- Following reset, the clock input must not be driven from LOW to HIGH until all applicable input and feedback setup times are met.

| Parameters | Description                     | Min. | Тур.                             | Max. | Units |

|------------|---------------------------------|------|----------------------------------|------|-------|

| tpR        | Power-Up<br>Reset Time          |      | 600                              | 1000 | ns    |

| ts         | Input or Feedback<br>Setup Time |      | See Switching<br>Characteristics |      |       |

| tw         | Clock Width                     |      |                                  |      |       |

Monolithic III Memories

#### **Absolute Maximum Ratings**

| Storage Temperature65 to +150°C                           |

|-----------------------------------------------------------|

| Supply Voltage to Ground Potential                        |

| (Pin 24 to Pin 12) Continuous0.5 to +7.0 V                |

| DC Voltage Applied to Outputs                             |

| (Except During Programming)0.5 V to +V <sub>CC</sub> Max. |

| DC Voltage Applied to Outputs                             |

| During Programming 16 V                                   |

| Output Current Into Outputs During                        |

| Programming (Max Duration of 1 sec) 200 mA                |

| DC Input Voltage0.5 to +5.5 V                             |

| DC Input Current30 to +5 mA                               |

|                                                           |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

### **Operating Ranges**

|                                   | •                |

|-----------------------------------|------------------|

| Commercial (C) Devices            |                  |

| Temperature (TA)                  | 0 to +75°C       |

| Supply Voltage (V <sub>CC</sub> ) |                  |

| Extended Commercial (E) Devices   |                  |

| Temperature (TA)                  | 55°C Min.        |

| Temperature (T <sub>C</sub> )     | + 125°C Max      |

| Supply Voltage (VCC)              | +4.50 to +5.50 V |

| Military (M) Devices*             |                  |

| Temperature (T <sub>A</sub> )     | 55°C Min.        |

| Temperature (T <sub>C</sub> )     | + 125°C Max      |

| Supply Voltage (Vcc)              |                  |

Operating ranges define those limits between which the functionality of the device is guaranteed.

\*Military product 100% tested at T<sub>C</sub> = +25°C, +125°C, and -55°C.

DC Characteristics over operating range unless otherwise specified; included in Group A, Subgroup 1, 2, 3 tests unless otherwise noted

| Parameter<br>Symbol         | Parameter<br>Description     |                                                        | Test Co                                                 | nditions                |       | Min.          | Typ.<br>(Note 1) | Max. | Unite |

|-----------------------------|------------------------------|--------------------------------------------------------|---------------------------------------------------------|-------------------------|-------|---------------|------------------|------|-------|

|                             | 0.4-4.11014.14-14            | V <sub>CC</sub> = Min.,                                | CC = Min., IOH = -3.2 mA COM'L                          |                         | 2.4   | 3.5           |                  | V    |       |

| VOH                         | Output HIGH Voltage          | VIN = VIH or \                                         | /IL                                                     | I <sub>OH</sub> = -2 mA | MIL   | ] *· <b>-</b> | 3.5              |      |       |

|                             | Outside LOW Values           | V <sub>CC</sub> = Min.,                                |                                                         | IOL = 24 mA             | COM'L | ľ             |                  | 0.5  | V     |

| VOL                         | Output LOW Voltage           | VIN = VIH or                                           | /IL                                                     | IOL = 12 mA             | MIL   |               |                  | 0.5  | •     |

| V <sub>IH</sub><br>(Note 2) | Input HIGH Level             |                                                        | Guaranteed Input Logical HIGH<br>Voltage for All Inputs |                         | 2.0   |               | 5.5              | >    |       |

| V <sub>IL</sub><br>(Note 2) | input LOW Level              | Guaranteed Input Logical LOW<br>Voltage for All Inputs |                                                         |                         |       |               | 0.8              | >    |       |

| l <sub>IL</sub>             | Input LOW Current            | V <sub>CC</sub> = Max., V <sub>IN</sub> = 0.40 V       |                                                         |                         |       | -20           | - 100            | μΑ   |       |

| IIH                         | Input HIGH Current           | V <sub>CC</sub> = Max., \                              | V <sub>CC</sub> = Max., V <sub>IN</sub> = 2.7 V         |                         |       |               | 25               | μΑ   |       |

| l <sub>l</sub>              | Input HiGH Current           | V <sub>CC</sub> = Max., \                              | 'IN = 5.5 V                                             |                         |       |               |                  | 1.0  | mA    |

| Isc                         | Output Short-Circuit Current | V <sub>CC</sub> = Max., \                              | OUT = 0.5 V (No                                         | ote 3)                  |       | -30           | -60              | - 90 | mA    |

|                             |                              |                                                        | COMIL                                                   |                         | MIL.  |               |                  |      |       |

|                             |                              |                                                        | -20                                                     | -25                     |       |               |                  | 210  |       |

| łcc                         | Power Supply Current         | V <sub>CC</sub> = Max.                                 | -30,                                                    | -35,                    |       |               |                  | 180  | mA    |

|                             | -30L, -40                    |                                                        | -30L, -40L                                              | -35L, -45L              |       |               |                  | 105  |       |

| VI                          | input Clamp Voltage          | V <sub>CC</sub> = Min., I <sub>IN</sub> = -18 mA       |                                                         |                         | -0.9  | -1.2          | ٧                |      |       |

| lozh                        | Output Leakage Current       | VCC = Max., V                                          | IN = VIH                                                | V <sub>O</sub> = 2.7 V  |       |               |                  | 100  | μА    |

| lozu                        | (Note 4)                     | or VIL                                                 |                                                         | Vo = 0.4 V              |       | 1             |                  | -100 | μ.    |

Notes: 1. Typical limits are at V<sub>CC</sub> = 5.0 V and T<sub>A</sub> = 25°C.

2. These are absolute values with respect to device ground and all overshoots due to system or tester noise are included.

3. Not more than one output should be tested at a time. Duration of the short circuit should not be more than one second.

Volt = 0.5V has been chosen to avoid test problems caused by tester ground degradation. 4. I/O pin leakage is the worst case of  $l_{OZX}$  or  $l_{IX}$  (where X = H or L).

Capacitance\*

| Parameter<br>Symbol | Parameter<br>Description | Test                             | Conditions | Тур. | Units |

|---------------------|--------------------------|----------------------------------|------------|------|-------|

|                     |                          | V <sub>IN</sub> = 2.0 V          | Pins 1, 13 | 11   |       |

| CIN                 | Input Capacitance        | @ f = 1 MHz                      | Others     | 6    | pF    |

| Соит                | Output Capacitance       | V <sub>OUT</sub> = 2.0 V @ f = 1 | 1 MHz      | 9    | 1     |

<sup>\*</sup>These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where capacitance may be affected.

### 24-Pin XOR AmPAL20XRP10 Family

Switching Characteristics over operating range unless otherwise specified; included in Group A, Subgroup 9, 10. 11 tests unless otherwise noted

#### Commercial Range

| No. | Parameter<br>Symbol | Parameter<br>Description                                                        | -20 Version |                  |      | -30 & -30L<br>Version |                  |      | -40L<br>Version |                  |      |       |

|-----|---------------------|---------------------------------------------------------------------------------|-------------|------------------|------|-----------------------|------------------|------|-----------------|------------------|------|-------|

|     |                     |                                                                                 | Min.        | Typ.<br>(Note 1) | Max. | Min.                  | Typ.<br>(Note 1) | Max. | Min.            | Typ.<br>(Note 1) | Max. | Units |

| 1   | <b>t</b> ₽D         | input or Feedback to Non-Registered<br>Output 22XP10, 20XRP4, 20XRP6.<br>20XRP8 |             |                  | 20   |                       |                  | 30   |                 |                  | 40   | ns    |

| 2   | <sup>1</sup> EA     | Input to Output Enable 22XP10, 20XRP4, 20XRP6, 20XRP8                           |             |                  | 20   |                       |                  | 30   |                 |                  | 40   | ns    |

| 3   | ten .               | Input to Output Disable 22XP10, 20XRP4, 20XRP6, 20XRP8                          |             |                  | 20   |                       |                  | 30   |                 |                  | 40   | ns    |

| 4   | †PZX                | Pin 13 to Output Enable 20XRP4,<br>20XRP6, 20XRP8, 20XRP10                      |             |                  | 15   |                       |                  | 20   |                 |                  | 35   | ns    |

| 5   | texz                | Pin 13 to Output Disable 20XRP4.<br>20XRP6, 20XRP8, 20XRP10                     |             |                  | 15   |                       |                  | 20   |                 |                  | 35   | ns    |

| 6   | tco                 | Clock to Output 20XRP4, 20XRP6, 20XRP8, 20XRP10                                 |             |                  | 13   |                       |                  | 15   |                 |                  | 30   | ns    |

| 7   | ts                  | Input or Feedback Setup Time 20XRP4,<br>20XRP6, 20XRP8, 20XRP10                 | 20          |                  |      | 30                    |                  |      | 40              |                  |      | ns    |

| 8   | t <sub>H</sub>      | Hold Time 20XRP4, 20XRP6, 20XRP8, 20XRP10                                       | 0           |                  |      | 0                     |                  |      | 0               |                  |      | ns    |

| 9   | tp                  | Clock Period (ts + tco)                                                         | 33          |                  |      | 45                    |                  |      | 70              |                  |      | ns    |

| 10  | tw                  | Clock Width                                                                     | 10          |                  |      | 15                    |                  |      | 25              |                  |      | ns    |

| 11  | fMAX.               | Maximum Frequency                                                               |             |                  | 30.3 |                       |                  | 22.2 |                 |                  | 14.3 | MHz   |

Notes: 1. Typical limits are at V<sub>CC</sub> = 5.0 V and T<sub>A</sub> = 25°C.

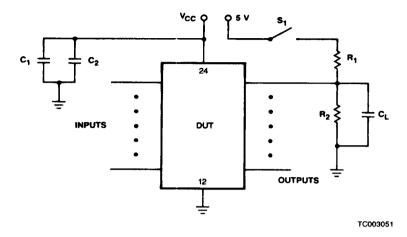

2. tp<sub>D</sub> is tested with switch S<sub>1</sub> closed and C<sub>L</sub> = 50 pF.

3. For three-state outputs, output enable times are tested with C<sub>L</sub> = 50 pF to the 1.5 V level; S<sub>1</sub> is open for high impedance to HIGH tests and closed for high impedance to LOW tests. Output disable times are tested with C<sub>L</sub> = 5 pF. HIGH to high impedance tests are made to an output voltage of V<sub>OH</sub> - 0.5 V with S<sub>1</sub> open; LOW to high impedance tests are made to the V<sub>OL</sub> + 0.5 V level with S<sub>1</sub> closed.

#### Military Range

| No. | Parameter<br>Symbol | Parameter<br>Description                                                        | -25 Version |                  | -35 & -35L<br>Version |      |                  | -45L<br>Version |      |                  |      |       |

|-----|---------------------|---------------------------------------------------------------------------------|-------------|------------------|-----------------------|------|------------------|-----------------|------|------------------|------|-------|

|     |                     |                                                                                 | Min.        | Typ.<br>(Note 1) | Max.                  | Min. | Typ.<br>(Note 1) | Max.            | Min. | Typ.<br>(Note 1) | Max. | Units |

| 1   | t <sub>PD</sub>     | Input or Feedback to Non-Registered<br>Output 22XP10, 20XRP4, 20XRP6.<br>20XRP8 |             |                  | 25                    |      |                  | 35              |      |                  | 45   | ns    |

| 2   | t <sub>EA</sub>     | Input to Output Enable 22XP10, 20XRP4, 20XRP6, 20XRP8                           |             |                  | 25                    |      |                  | 35              |      |                  | 45   | ns    |

| 3   | t <sub>ER</sub>     | Input to Output Disable 22XP10, 20XRP4, 20XRP6, 20XRP8                          |             |                  | 25                    |      |                  | 35              |      |                  | 45   | ns    |

| 4   | ФZX                 | Pin 13 to Output Enable 20XRP4,<br>20XRP6, 20XRP8, 20XRP10                      |             |                  | 20                    |      |                  | 25              |      |                  | 40   | ns    |

| 5   | †PXZ                | Pin 13 to Output Disable 20XRP4<br>20XRP6, 20XRP8, 20XRP10                      |             |                  | 20                    |      |                  | 25              |      |                  | 40   | ns    |

| 6   | tco                 | Clock to Output 20XRP4, 20XRP6, 20XRP8, 20XRP10                                 |             |                  | 15                    |      |                  | 25              |      |                  | 35   | ns    |

| 7   | ts                  | Input or Feedback Setup Time 20XRP4,<br>20XRP6, 20XRP8, 20XRP10                 | 25          |                  |                       | 35   |                  |                 | 45   |                  |      | ns    |

| 8   | ч                   | Hold Time 20XRP4, 20XRP6, 20XRP8, 20XRP10                                       | 0           |                  |                       | 0    |                  |                 | 0    |                  |      | ns    |

| 9   | tр                  | Clock Period (ts + tco)                                                         | 40          | 1                |                       | 60   |                  |                 | 80   |                  |      | ns    |

| 10  | tw                  | Clock Width                                                                     | 12          |                  |                       | 20   |                  |                 | 30   | ĺ                |      | ns    |

| 11  | fMAX.               | Maximum Frequency                                                               |             |                  | 25                    |      |                  | 16.7            |      |                  | 12.5 | MHz   |

A Manalithia Mill Memories

JANUARY 1988

Notes: 1. Typical limits are at V<sub>CC</sub> = 5.0 V and T<sub>A</sub> = 25°C.

2. typ is tested with switch S<sub>1</sub> closed and C<sub>L</sub> = 50 pF.

3. For three-state outputs, output enable times are tested with C<sub>L</sub> = 50 pF to the 1.5 V level; S<sub>1</sub> is open for high impedance to HIGH tests and closed for high impedance to LOW tests. Output disable times are tested with C<sub>L</sub> = 5 pF. HIGH to high impedance tests are made to an output voltage of V<sub>OH</sub> - 0.5 V with S<sub>1</sub> open; LOW to high impedance tests are made to the V<sub>OL</sub> + 0.5 V level with S<sub>1</sub> closed.

## **Switching Test Circuit**

Note: C<sub>1</sub> and C<sub>2</sub> are to bypass V<sub>CC</sub> to ground.

| TEST OUTPUT LOADS |            |          |  |  |  |  |

|-------------------|------------|----------|--|--|--|--|

| Pin Name          | Commercial | Military |  |  |  |  |

| R <sub>1</sub>    | 200 Ω      | 390 Ω    |  |  |  |  |

| R <sub>2</sub>    | 390 Ω      | 750 Ω    |  |  |  |  |

| C <sub>1</sub>    | 1 μF       | 1 μF     |  |  |  |  |

| C <sub>2</sub>    | 0.1 μF     | 0.1 μF   |  |  |  |  |

| CL                | 50 pF      | 50 pF    |  |  |  |  |

### **Switching Waveforms**

### **Key to Timing Diagram**

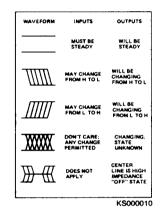

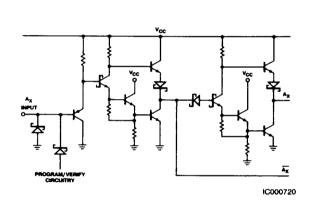

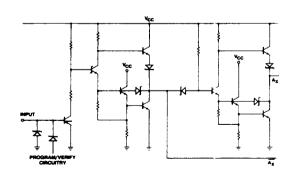

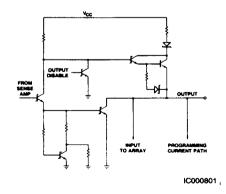

**Input Circuitry**

### **Output Circuitry**

5-288

Monolithic III Memories

#### Security Fuse Programming

A single fuse is provided on each device to prevent unauthorized copying of PAL fuse patterns. Once blown, the circuitry enabling fuse verification and registered output PRELOAD is permanently disabled.

Programming of the security fuse is the same as an array fuse. Verification of a blown security fuse is accomplished by verifying the whole fuse array as if every fuse is blown.

# Programmers/Development Systems (refer to Programmer Reference Guide, page 3-81)

Monolithia Memories