### **DESCRIPTION**

The NE592 is a monolithic, two-stage, differential output, wideband video amplifier. It offers fixed gains of 100 and 400 without external components and adjustable gains from 400 to 0 with one external resistor. The input stage has been designed so that with the addition of a few external reactive elements between the gain select terminals. the circuit can function as a high-pass. low-pass, or band-pass filter. This feature makes the circuit ideal for use as a video or pulse amplifier in communications, magnetic memories, display, video recorder systems, and floppy disk head amplifiers. Now available in an 8-pin version with fixed gain of 400 without external components and adjustable gain from 400 to 0 with one external resistor.

### **FEATURES**

- 120MHz unity gain bandwidth

- Adjustable gains from 0 to 400

- Adjustable pass band

- No frequency compensation required

- Wave shaping with minimal external components

- MIL-STD processing available

#### **APPLICATIONS**

- Floppy disk head amplifier

- Video amplifier

- Pulse amplifier in communications

- Magnetic memory

- Video recorder systems

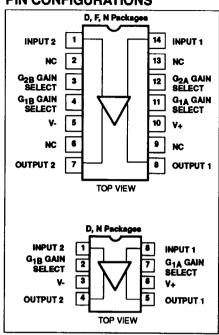

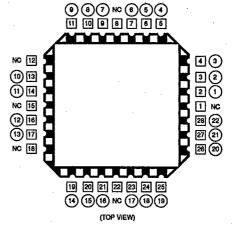

### **PIN CONFIGURATIONS**

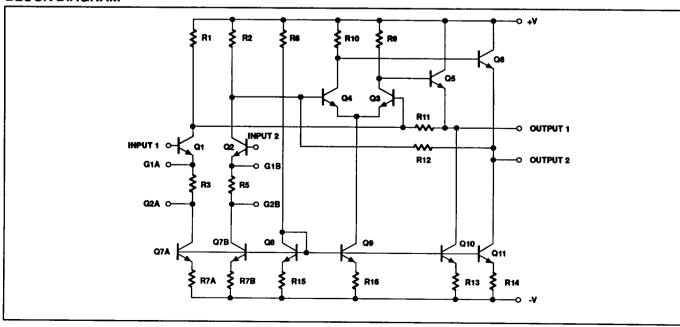

### **BLOCK DIAGRAM**

### **ORDERING INFORMATION**

| DESCRIPTION        | TEMPERATURE RANGE | ORDER CODE | DWG# |

|--------------------|-------------------|------------|------|

| 14-Pin Plastic DIP | 0 to +70°C        | NE592N14   | 0405 |

| 14-Pin Cerdip      | 0 to +70°C        | NE592F14   | 0581 |

| 14-Pin SO          | 0 to +70°C        | NE592D14   | 0175 |

| 8-Pin Plastic DIP  | 0 to +70°C        | NE592N8    | 0404 |

| 8-Pin SO           | 0 to +70°C        | NE592D8    | 0174 |

NOTES:

N8, N14, D8 and D14 package parts also available in "High" gain version by adding "H" before package designation, i.e., NE592HDB

### **ABSOLUTE MAXIMUM RATINGS**

T<sub>A</sub>=+25°C, unless otherwise specified.

| SYMBOL             | PARAMETER                           | RATING      | UNIT |

|--------------------|-------------------------------------|-------------|------|

| Vcc                | Supply voltage                      | ±8          | ٧    |

| V <sub>IN</sub>    | Differential input voltage          | ±5          | ٧    |

| V <sub>CM</sub>    | Common-mode input voltage           | ±6          | ٧    |

| lout               | Output current                      | 10          | mA   |

| TA                 | Operating ambient temperature range | 0 to +70    | °C   |

| TSTG               | Storage temperature range           | -65 to +150 | °C   |

| P <sub>D MAX</sub> | Maximum power dissipation,          |             |      |

|                    | TA=25°C (still air)1                |             |      |

|                    | F-14 package                        | 1.17        | w    |

|                    | D-14 package                        | 0.98        | w    |

|                    | D-8 package                         | 0.79        | w    |

|                    | N-14 package                        | 1.44        | w    |

|                    | N-8 package                         | 1.17        | w    |

### NOTES:

2. Derate above 25°C at the following rates:

F-14 package at 9.3mW/°C D-14 package at 7.8mW/°C

D-8 package at 6.3mW/°C N-14 package at 11.5mW/°C N-8 package at 9.3mW/°C

April 15, 1992

NE592

### DC ELECTRICAL CHARACTERISTICS

$T_A=+25^{\circ}C$   $V_{SS}=+6V$ ,  $V_{CM}=0$ , unless otherwise specified. Recommended operating supply voltages  $V_S=+6.0V$ . All specifications apply to both standard and high gain parts unless noted differently.

| SYMBOL             | PARAMETER                      | TEST CONDITIONS                                          | NE/SA592 |      |      | UNIT              |

|--------------------|--------------------------------|----------------------------------------------------------|----------|------|------|-------------------|

|                    |                                |                                                          | Min      | Тур  | Max  | 1                 |

| A <sub>VOL</sub>   | Differential voltage gain,     |                                                          |          |      |      |                   |

|                    | standard part                  |                                                          |          |      |      |                   |

|                    | Gain 1 <sup>1</sup>            | R <sub>L</sub> =2kΩ, V <sub>OUT</sub> =3V <sub>P-P</sub> | 250      | 400  | 600  | V/V               |

|                    | Gain 2 <sup>2, 4</sup>         |                                                          | 80       | 100  | 120  | V/V               |

|                    | High gain part                 |                                                          | 400      | 500  | 600  | V/V               |

| R <sub>IN</sub>    | Input resistance               |                                                          |          | Ì    |      |                   |

|                    | Gain 1 <sup>1</sup>            |                                                          |          | 4.0  |      | kΩ                |

|                    | Gain 2 <sup>2, 4</sup>         |                                                          | 10       | 30   |      | kΩ                |

| C <sub>IN</sub>    | Input capacitance <sup>2</sup> | Gain 2 <sup>4</sup>                                      |          | 2.0  |      | pF                |

| los                | Input offset current           |                                                          |          | 0.4  | 5.0  | μА                |

| BIAS               | Input bias current             |                                                          |          | 9.0  | 30   | μА                |

| V <sub>NOISE</sub> | Input noise voltage            | BW 1kHz to 10MHz                                         |          | 12   |      | μV <sub>RMS</sub> |

| V <sub>IN</sub>    | Input voltage range            |                                                          | ±1.0     |      |      | V                 |

| CMRR               | Common-mode rejection ratio    |                                                          |          |      |      |                   |

|                    | Gain 2 <sup>4</sup>            | V <sub>CM</sub> ±1V, f<100kHz                            | 60       | 86   |      | dB                |

|                    | Gain 2 <sup>4</sup>            | V <sub>CM</sub> ±1V, f=5MHz                              |          | 60   |      | dB                |

| PSRR               | Supply voltage rejection ratio |                                                          |          |      |      |                   |

|                    | Gain 2 <sup>4</sup>            | ΔV <sub>S</sub> =±0.5V                                   | 50       | 70   |      | dB                |

| Vos                | Output offset voltage          |                                                          |          |      |      |                   |

|                    | Gain 1                         | R <sub>L≂∞</sub>                                         |          |      | 1.5  | l v               |

|                    | Gain 2 <sup>4</sup>            | Rլ⇒∞                                                     |          |      | 1.5  | V                 |

|                    | Gain 3 <sup>3</sup>            | R <sub>L</sub> =∞                                        |          | 0.35 | 0.75 | V                 |

| V <sub>CM</sub>    | Output common-mode voltage     | R <sub>L</sub> =∞                                        | 2.4      | 2.9  | 3.4  | V                 |

| Vout               | Output voltage swing           | R <sub>L</sub> =2kΩ                                      | 3.0      | 4.0  |      | v                 |

|                    | differential                   |                                                          |          |      |      |                   |

| R <sub>out</sub>   | Output resistance              |                                                          |          | 20   |      | Ω                 |

| lcc                | Power supply current           | R∟∞∞                                                     |          | 18   | 24   | mA                |

#### NOTES:

- Gain select Pins G<sub>1A</sub> and G<sub>1B</sub> connected together.

Gain select Pins G<sub>2A</sub> and G<sub>2B</sub> connected together.

All gain select pins open.

- 4. Applies to 14-pin version only.

April 15, 1992 95

NE592

### DC ELECTRICAL CHARACTERISTICS

DC Electrical CharacteristicsV<sub>SS</sub>=±6V, V<sub>CM</sub>=0, 0°C ≤T<sub>A</sub>≤70°C, unless otherwise specified. Recommended operating supply voltages V<sub>S</sub>=+6.0V. All specifications apply to both standard and high gain parts unless noted differently.

| SYMBOL           | PARAMETER                         | TEST CONDITIONS                     | NE/SA592 |     |            | UNIT                   |

|------------------|-----------------------------------|-------------------------------------|----------|-----|------------|------------------------|

|                  |                                   |                                     | Min      | Тур | Max        | 1                      |

| Avol             | Differential voltage gain,        |                                     |          |     |            |                        |

|                  | standard part                     |                                     |          |     |            |                        |

|                  | Gain 1 <sup>1</sup>               | $R_L=2k\Omega$ , $V_{OUT}=3V_{P-P}$ | 250      |     | 600        | \ v <sub>\(\nu\)</sub> |

|                  | Gain 2 <sup>2, 4</sup>            |                                     | 80       |     | 120        | \ v <sub>\(\nu\)</sub> |

|                  | High gain part                    |                                     | 400      | 500 | 600        | V/V                    |

| R <sub>IN</sub>  | Input resistance                  |                                     |          |     |            |                        |

|                  | Gain 2 <sup>2, 4</sup>            |                                     | 8.0      |     |            | kΩ                     |

| los              | Input offset current              |                                     |          |     | 6.0        | μА                     |

| BIAS             | Input bias current                |                                     |          |     | 40         | μА                     |

| V <sub>IN</sub>  | Input voltage range               |                                     | ±1.0     |     |            | V                      |

| CMRR             | Common-mode rejection ratio       |                                     |          |     |            |                        |

|                  | Gain 2 <sup>4</sup>               | V <sub>CM</sub> ±1V, f<100kHz       | 50       |     |            | dB                     |

| PSRR             | Supply voltage rejection ratio    |                                     |          |     |            |                        |

|                  | Gain 2 <sup>4</sup>               | ΔV <sub>S</sub> =±0.5V              | 50       |     |            | dB                     |

|                  | Output offset voltage             |                                     |          |     |            |                        |

| Vos              | Gain 1<br>Gain 2 <sup>4</sup>     | R <sub>L</sub> ≕∞                   |          |     | 1.5        | l v                    |

| -                | Gain 3 <sup>3</sup>               | -                                   |          |     | 1.5<br>1.0 |                        |

| V <sub>out</sub> | Output voltage swing differential | R <sub>L</sub> =2kΩ                 | 2.8      |     |            | V                      |

| lcc              | Power supply current              | R <sub>L=∞</sub>                    | -        |     | 27         | mA                     |

#### NOTES:

- 1. Gain select Pins G<sub>1A</sub> and G<sub>1B</sub> connected together.

- 2. Gain select Pins G2A and G2B connected together.

- 3. All gain select pins open.

- 4. Applies to 10- and 14-pin versions only.

### **AC ELECTRICAL CHARACTERISTICS**

$T_{A}=+25$ °C  $V_{SS}=+6V$ ,  $V_{CM}=0$ , unless otherwise specified. Recommended operating supply voltages  $V_{S}=\pm6.0V$ . All specifications apply to both standard and high gain parts unless noted differently.

| SYMBOL         | PARAMETER              | TEST CONDITIONS                     | NE/SA592 |      |     | UNIT |

|----------------|------------------------|-------------------------------------|----------|------|-----|------|

|                |                        |                                     | Min      | Тур  | Max | 7    |

|                | Bandwidth              |                                     |          |      |     |      |

| BW             | Gain 1 <sup>1</sup>    |                                     |          | 40   |     | MHz  |

|                | Gain 2 <sup>2, 4</sup> |                                     |          | 90   |     | MHz  |

|                | Rise time              |                                     |          |      |     |      |

| t <sub>R</sub> | Gain 1 <sup>1</sup>    | V <sub>OUT</sub> =1V <sub>P-P</sub> |          | 10.5 | 12  | ns   |

|                | Gain 2 <sup>2, 4</sup> | <u> </u>                            |          | 4.5  |     | ns   |

|                | Propagation delay      |                                     |          |      |     |      |

| <b>t</b> PD    | Gain 1 <sup>1</sup>    | V <sub>OUT</sub> =1V <sub>P-P</sub> |          | 7.5  | 10  | ns   |

|                | Gain 2 <sup>2, 4</sup> |                                     |          | 6.0  |     | ns   |

### NOTES:

- 1. Gain select Pins G<sub>1A</sub> and G<sub>1B</sub> connected together.

- 2. Gain select Pins G2A and G2B connected together.

- 3. All gain select pins open.

- 4. Applies to 10- and 14-pin versions only.

April 15, 1992 96

NE592

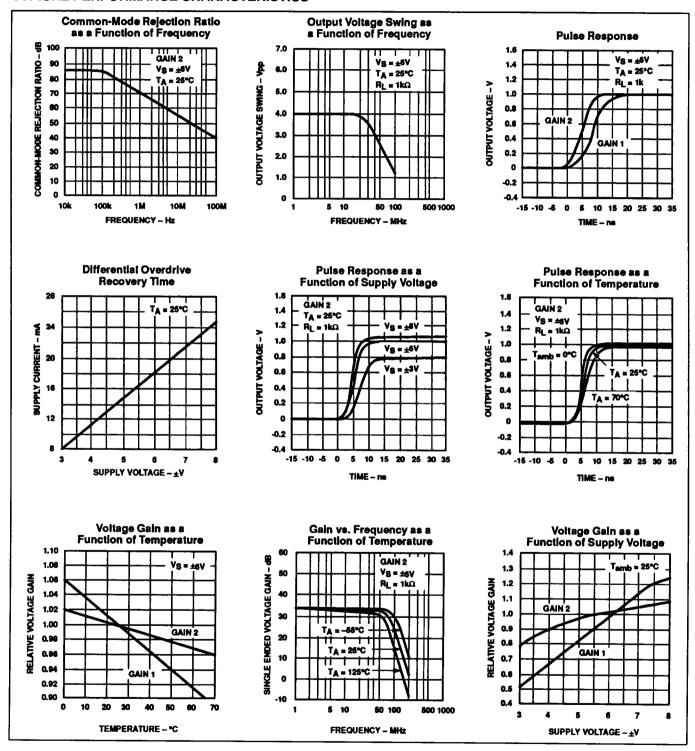

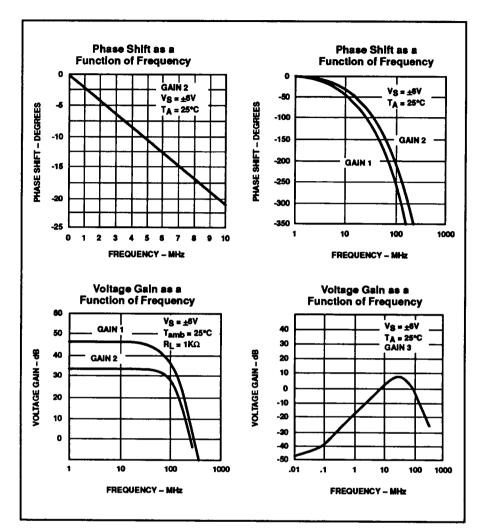

### TYPICAL PERFORMANCE CHARACTERISTICS

97

April 15, 1992

NE592

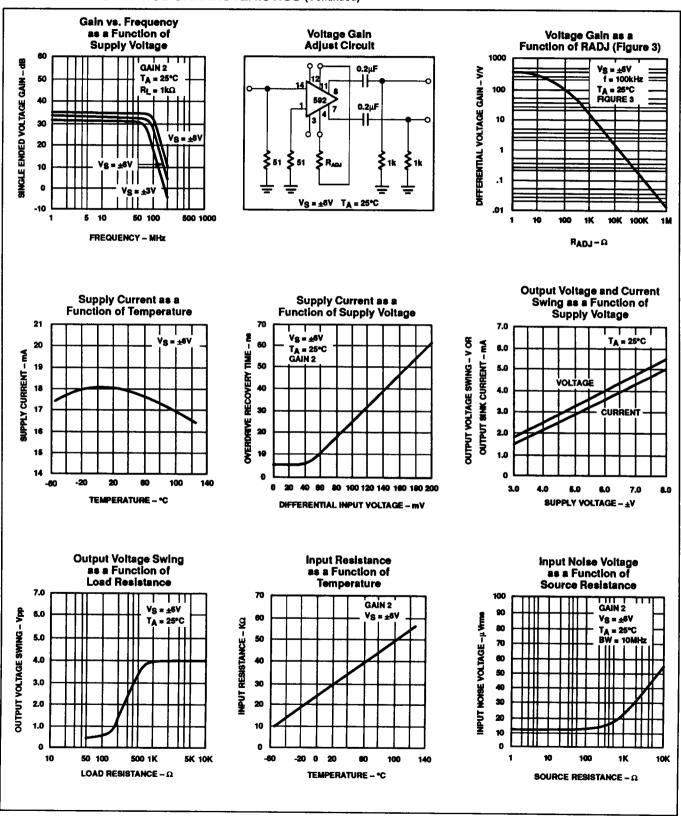

### TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

NE592

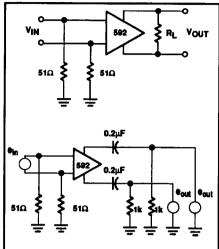

TEST CIRCUITS  $T_A = 25$ °C, unless otherwise specified.

April 15, 1992

99

NE592

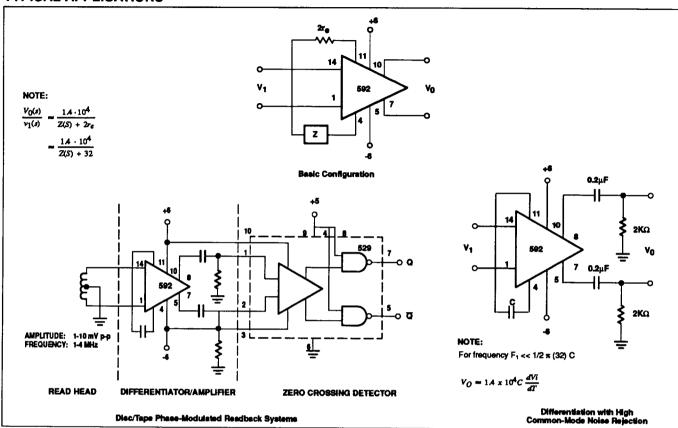

### **TYPICAL APPLICATIONS**

### **FILTER NETWORKS**

| Z NETWORK FILTER TYPE |             | V <sub>0</sub> (s) TRANSFER<br>V <sub>1</sub> (s) FUNCTION                             |

|-----------------------|-------------|----------------------------------------------------------------------------------------|

| o————————o            | LOW PASS    | $\frac{1.4 \times 10^4}{L} \qquad \left[ \frac{1}{s + R/L} \right]$                    |

| ∘RC                   | HIGH PASS   | $\frac{1.4 \times 10^4}{R} \qquad \left[\frac{s}{s+1/RC}\right]$                       |

|                       | BAND PASS   | $\frac{1.4 \times 10^4}{L} \qquad \left[ \frac{s}{s^2 + R/Ls + 1/LC} \right]$          |

| 0                     | BAND REJECT | $\frac{1.4 \times 10^4}{R} \qquad \left[ \frac{s^2 + 1/LC}{s^2 + 1/LC + s/RC} \right]$ |

# Signetics

# Packaging Information

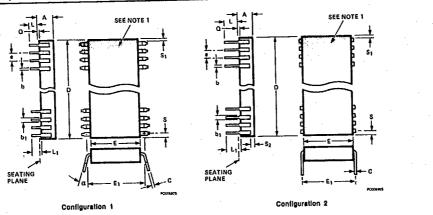

T.90-20

### **Military Products**

### SIGNETICS STANDARD PACKAGE DESCRIPTIONS

All Military package case outlines and physical dimensions conform with the current revision MIL-M-38510, Appendix C, except for package types which are not included in that specifica-

The physical dimensions for standard package types which are not included in Appendix C are included herein in Appendix C format. Case outline letters are assigned to these packages according to JEDEC Publication 101 as follows:

- Leadless chip carriers Dual-in-line packages U;

- Flat packages

- All other configurations

A case outline suffix number is assigned herein for identification purposes only, and is not marked on the product.

Signetics Military products are offered in a wide range of package configurations to optimally fit our customer needs.

- Dual-in-line Packages; Frit glass sealed CERDIP (F package family) with 8-40 leads, and skie-brazed ceramic (I package family) with 48-64 leads.

- Flat Packages; Frit glass sealed alumina CERPAC (W package family) with 14-28 leads, and brazed leaded ceramic (Q package family) with 52 leads.

- · Ceramic Chip Carriers; triple laminated, metal-lidded LCC (G package family) with 20-68 terminals.

- Pin Grid Array; metal-lidded ceramic pin grid (P package family) with 68-100 leads.

- Shown in Table 1 are the case outline letters assigned according to Appendix C of MIL-M-38510 and JEDEC publication 101. Unless otherwise noted, all package types are Configuration 1 and all lead finishes are hot solder dip Finish "A".

Table 1

| Package Description                   | Type Designation  | Case Outline                                                 | Theta-JC °C/Watt4    |

|---------------------------------------|-------------------|--------------------------------------------------------------|----------------------|

| · · · · · · · · · · · · · · · · · · · | D-4               | Р                                                            | 28<br>28<br>28<br>28 |

| 8DIP3                                 | D-1               | C                                                            | 28                   |

| 14DIP3                                | D-2               | Ě                                                            | 28                   |

| 16DIP3                                | D-6               | Ě                                                            | 28 '                 |

| 18DIP3                                | D-8               | Ř                                                            | i 28                 |

| 20DIP3                                |                   | ŵ                                                            | 28                   |

| 22DIP4                                | D-7               |                                                              | 28                   |

| 24DIP3                                | D-9               | X <sub>5</sub>                                               | 28<br>28             |

| 24DIP4                                | D-11              | ĵ                                                            | 28                   |

| 24DIP6                                | D-3               | <b>5</b>                                                     | 28                   |

| 28DIP6                                | D-10              | X²<br>Q<br>X²<br>X²<br>X²                                    | 28                   |

| 40DIP6                                | D-5               | Q <sub>3</sub>                                               | 20                   |

| 48DIP6                                | D-14 <sup>1</sup> | ,                                                            | 28<br>28<br>28       |

| 50DIP9                                | D-12 <sup>1</sup> |                                                              | 20                   |

| 64DIP9                                | D-13 <sup>1</sup> | X²                                                           |                      |

| 14FLAT                                | F-2               | D<br>F                                                       | 22                   |

| 16FLAT                                | F-5               | F ·                                                          | 22<br>22             |

| 18FLAT                                | F-10              | Υ <sup>2</sup>                                               | 22                   |

| 20FLAT                                | F-9               | Y2<br>S<br>K<br>Y2<br>Y2                                     | 22                   |

| 24FLAT                                | F-6               | l K                                                          | 22                   |

| 28FLAT                                | F-11              | Y <sup>2</sup>                                               | 22                   |

| 52FLAT                                | Yii               | Y2                                                           | 22                   |

| 18LLCC                                | C-9               | U <sup>2</sup>                                               | 20                   |

| 20LLCC                                | Č-23              | 2                                                            | 20                   |

| 28LLCC                                | C-43              | 2<br>3<br>U <sup>2</sup><br>U <sup>2</sup><br>U <sup>2</sup> | 20                   |

| 32LLCC                                | C-12              | l Ú2                                                         | 20                   |

|                                       |                   | Ū2 ·                                                         | 20<br>20             |

| 44LLCC                                | C-5<br>C-7        | U2 -                                                         | 20                   |

| 68LLCC                                | l                 |                                                              | 20                   |

| 68PGA                                 | P-AB              | Z <sup>2</sup><br>Z <sup>2</sup>                             | 20 20                |

| 84PGA                                 | P-AB              | Z <sup>2</sup>                                               | 20                   |

### NOTES:

NOTES:

1. Configuration 2.

2. Per JEDEC publication 101.

3. Dimension A (LLCC thickness) is 75mils maximum.

4. See RADC test report RADC-TR-86-97 for thermal resistance confidence and derating.

January 1990

# T-90-20

### **Packaging Information**

### **CASE OUTLINES Y (FLAT PACKAGES)**

### NOTES:

- A lead tab (enlargement) or index dot is located within the shaded area shown at Pin 1. Other pin numbers proceed sequentially from Pin 1 counterclockwise (as viewed from the top of the device).

- 2. This dimension allows for off-center lid, meniscus, and glass overrun.

- 3. The reference pin spacing is 0.050 between centerlines. Each pin centerline is located within ± 0.005 of its logitudinal position relative to the first and last pin numbers.

4. This dimension is measured at the point of exit of the lead

- body.

5. This dimension applied to all four comer pins.

6. Lead dimensions include 0.003 inch allowance for hot solder dip lead finish.

| OUTLINE       |           | Y1     |       |   |       |   |

|---------------|-----------|--------|-------|---|-------|---|

| CONFIGURATION | 2         |        | 2     |   | 1     | l |

| NO. LEADS     | 52        |        | 52    |   | NOTES | l |

| SIG. PKG.     | QP        |        | HOIES | l |       |   |

| SYMBOL        | INC       | INCHES |       |   |       |   |

| STMBUL        | Min       | Max    |       | l |       |   |

| A             | 0.045     | 0.100  |       | ĺ |       |   |

| b             | 0.015     | 0.026  | 6     | ı |       |   |

| C             | 0.008     | 0.015  | 6     | l |       |   |

| D             | • • •     | 1.330  | 2     |   |       |   |

| E             | 0.620     | 0.660  |       |   |       |   |

|               | 0.050 BSC |        | 3     |   |       |   |

| L,            | 0.250     | 0.370  | -     |   |       |   |

| Q             | 0.054     | 0.0666 | 4     |   |       |   |

| S             | -         | 0.045  | 5     |   |       |   |

| <b>S</b> 1    | 0.005     |        | 5     |   |       |   |

## T-90-20

### **Packaging Information**

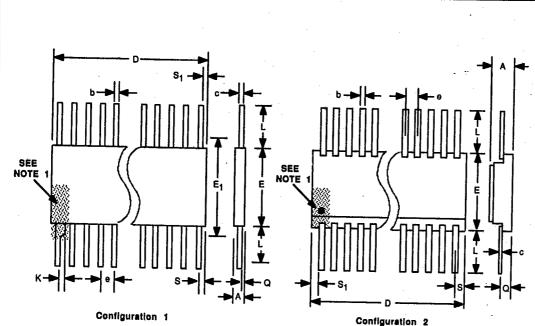

CASE OUTLINES X (DUAL IN-LINE PACKAGES)

- 1. An index notch is located within the shaded area shown. Pin 1 is adjacent to the notch to the immediate left (as viewed from the top of the device) and other pin numbers proceed sequentially from Pin 1 counterclockwise.

2. The minimum limit for Dimension b1 is 0.023 inches for all four corner pins.

- This dimension allows for off-center lid, meniscus, and glass overrun.

- 4. This dimension is measured at the centerline of the leads for Configuration 2.

- 5. The reference pin spacing is 0.100 between centerlines. Each pin centerline is located within ±0.010 of its longitudinal position relative to the first and last pin numbers.

- 6. This dimension is measured from the seating plane to the base plane.

- 7. This dimension applies to all four corner pins.

- 8. Lead dimensions include 0.003 inch allowance for hot solder dip lead finish.

D

### **Packaging Information**

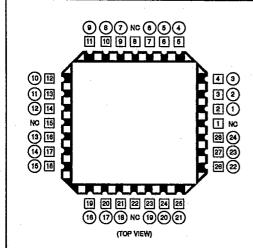

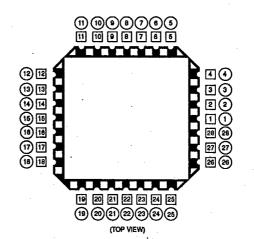

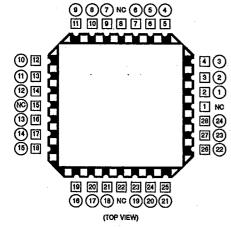

### LEADLESS CHIP CARRIER (LLCC) PINOUTS

24-Lead Logic Pinout for 28 Terminal Chip Carrier

28-Lead Pinout for 28 Terminal Chip Carrier for all Device Types

24-Lead Memory Pinout for 28 Terminal Chip Carrier

- ☐ = Chip Carrier Terminal Number

- O = Dual In-Line Lead Number NC = No Connect

22-Lead Memory Pinout for 28 Terminal Chip Carrier