Inc

#### 8,388,608 bit CMOS UV Eraseable PROM

#### **Features**

Access times of 100/120/150/170/200/250 ns.

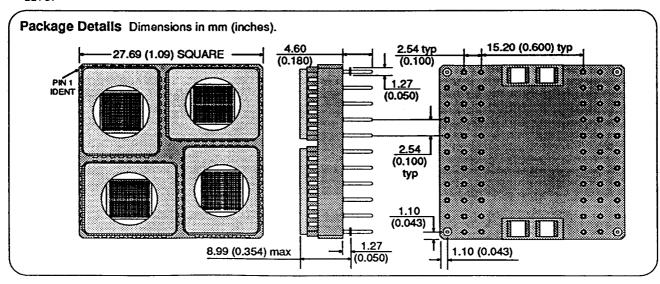

Pin grid array gives 2:1 improvement over DIL.

Package Suitable for Thermal Ladder Applications.

On board decoupling capacitors.

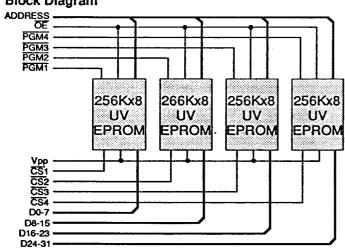

Configurable as 8 / 16 / 32 bit wide.

Operating Power 100 / 200 / 400 mW (typ)

Standby Power 1 mW (typ)

V<sub>pp</sub> Voltage of 12.5V.

Complete Module Programming in 30 sec. (typ)

May be screened in accordance with MIL-STD-883D (not 100ns or 120ns modules - see ordering information)

Block Diagram

# PUMA 2U8002

### PUMA 2U8002-10/12/15/17/20/25

Issue 1.0 : March 1992

### ADVANCE PRODUCT INFORMATION

| Pin Definition                                    |                       |                                         |

|---------------------------------------------------|-----------------------|-----------------------------------------|

| 1 12 23                                           |                       | 34 45 56                                |

| O 55 O 54 O 53 O 52 O 55 O 55 O 55 O 55 O 55 O 55 | VIEW<br>FROM<br>ABOVE | O 25 |

| 11 22 33                                          |                       | <del></del>                             |

#### **Pin Functions**

| A0 - A17        | Address Inputs      |

|-----------------|---------------------|

| D0 - D31        | Data Inputs/Outputs |

| CS1-4           | Chip Select         |

| ŌĒ              | Output Enable       |

| PGM1-4          | Program Enable      |

| NC              | No Connect          |

| $V_{pp}$        | Programming Voltage |

| V <sub>cc</sub> | Power (+5V)         |

| GND             | Ground              |

## Absolute Maximum Ratings (1)

| Voltage on pins V <sub>pp</sub> and A <sub>s</sub> (5) | V <sub>TPP</sub> -0.6V to +13.5 V                  |    |

|--------------------------------------------------------|----------------------------------------------------|----|

| Voltage on pin V                                       | $V_{TCC}^{(r)}$ -0.6V to + 7.0 V                   |    |

| Voltage on any other pins (2)                          | $V_{\tau}^{(0)} = -0.6V \text{ to } +V_{cc} + 0.5$ | V  |

| Power Dissipation                                      | P <sub>t</sub> 2                                   | W  |

| Storage Temperature                                    | T <sub>srg</sub> -65 to +150                       | .c |

Notes: (1) Stresses above those listed may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

|                       |                 | min  | typ            | max                 |                  |

|-----------------------|-----------------|------|----------------|---------------------|------------------|

| Supply Voltage        | V <sub>cc</sub> | 4.5  | 5.0            | 5.5                 | V                |

| Input High Voltage    | V <sub>IH</sub> | 2.0  | -              | V <sub>∞</sub> +0.5 | V                |

| Input Low Voltage     | ٧ <u>"</u>      | -0.5 | , <del>-</del> | 8.0                 | V                |

| Operating Temperature | T,              | 0    | -              | 70                  | *C (2U8002)      |

|                       | т               | -40  | -              | 85                  | °C (2U8002I)     |

|                       | T <sub>AM</sub> | -55  | •              | 125                 | °C (2U8002M, MB) |

# DC Electrical Characteristics (T<sub>A</sub>=-55°C to +125°C, V<sub>CC</sub>=5V ± 10%)

| Parameter                                      | Symbol            | Test Condition                                                            | min | typ(4) | max                 | Unit |

|------------------------------------------------|-------------------|---------------------------------------------------------------------------|-----|--------|---------------------|------|

| Input Leakage Current Address, OE              | I <sub>LI1</sub>  | V <sub>IN</sub> =0V or V <sub>CCI</sub> V <sub>pp</sub> =V <sub>ppt</sub> | -   | -      | 4                   | μΑ   |

| Other Pins                                     |                   | V <sub>IN</sub> =0V or V <sub>cc</sub>                                    | -   | -      | 1                   | μΑ   |

| Output Leakage Current                         | Ι <mark>ω</mark>  | V <sub>our</sub> =0V or V <sub>cc</sub> , 8 bit                           | -   | -      | 20                  | μΑ   |

| V <sub>pp</sub> Read Current                   | l <sub>pp1</sub>  | V <sub>PP</sub> =V <sub>PPH</sub>                                         | -   | -      | 400                 | μΑ   |

| V <sub>∞</sub> Operating Supply Current 32 bit | l <sub>cc32</sub> | $\overline{CS}=V_{a}^{(1)}$ , $I_{OUT}=0$ mA, $f=5$ MHz <sup>(2)</sup>    | -   | 80     | 240                 | mΑ   |

| 16 bit                                         |                   | As above                                                                  | -   | 42     | 122                 | mΑ   |

| 8 bit                                          |                   | As above                                                                  | -   | 23     | 63                  | mΑ   |

| Standby Supply Current TTL levels              |                   | CS=V <sub>14</sub> (1)                                                    | -   | -      | 4                   | mΑ   |

| CMOS levels                                    |                   | CS=V <sub>∞</sub> ±0.3V <sup>(1)</sup>                                    | -   | 80     | 400                 | μΑ   |

| V <sub>pp</sub> Voltage During Read Only       | $V_{ppl}$         |                                                                           | 0   | -      | V <sub>∞</sub> +0.5 | V    |

| Output Low Voltage                             | Val               | I <sub>ot</sub> =2.1mA.                                                   | -   | -      | 0.45                | ٧    |

| Output High Voltage                            | V <sub>OH</sub>   | I <sub>oн</sub> =-400μA.                                                  | 2.4 | -      | -                   | V    |

- Notes (1) CS above are accessed through CS1-4. These inputs must be operated simultaneously for 32 bit operation, in pairs in 16 bit mode and singly for 8 bit mode.

- (2) Maximum active current is the sum of Icc and Ipp.

- (3) CAUTION: the PUMA 2U8002 must not be removed from or inserted into a socket when  $V_{cc}$  or  $V_{pp}$  is applied.

- (4) Typical values are measured at 25°C and nominal supply voltage.

| Capacitance (V <sub>cc</sub> = | Capacitance (V <sub>cc</sub> =5V±10%,T <sub>x</sub> =25°C) |                  |                     |     |     |      |  |  |  |  |

|--------------------------------|------------------------------------------------------------|------------------|---------------------|-----|-----|------|--|--|--|--|

| Parameter                      |                                                            | Symbol           | Test Condition      | typ | max | Unit |  |  |  |  |

| Input Capacitance              | Address                                                    | C <sub>IN1</sub> | V <sub>IN</sub> =0V | 38  | 51  | pF   |  |  |  |  |

| • •                            | ŌĒ                                                         | C <sub>IN3</sub> | V <sub>#N</sub> =0V | 33  | 46  | рF   |  |  |  |  |

| Ĩ                              | PGM1-4, CS1-4                                              | Cina             | V <sub>IN</sub> =0V | 12  | 19  | pF   |  |  |  |  |

| I/O Capacitance                | 32 Bit Mode                                                | Cio              | V <sub>vo</sub> =0V | 11  | 19  | pF   |  |  |  |  |

| Note: This param               | eter is calculated a                                       | and not meas     | sured.              |     |     |      |  |  |  |  |

#### **AC Test Conditions**

- \*Input pulse levels: GND to 3.0V

- \*Output load: 1 TTL gate + 100pF

\*Input rise and fall times: 5 ns

- \*V\_=5V±10%

- \*Input and Output timing reference levels: 1.5V

# **Electrical Characteristics & Recommended AC Operating Conditions**

| Rea | d | Cv | cle | (1 |

|-----|---|----|-----|----|

|     |   |    |     |    |

|                              |                  | -   | 10  | -   | 12  | -   | 15  |      |

|------------------------------|------------------|-----|-----|-----|-----|-----|-----|------|

| Parameter                    | Symbol           | min | max | min | max | min | max | Unit |

| dress to Output Delay        | t <sub>ACC</sub> | -   | 100 | -   | 120 | -   | 150 | ns   |

| Select Access Time           | t <sub>ce</sub>  | -   | 100 | -   | 120 | -   | 150 | ns   |

| out Enable to Output Valid   | to∈              | -   | 50  | -   | 50  | -   | 65  | ns   |

| p Deselect to O/P high Z (2) | t <sub>DF</sub>  | 0   | 50  | 0   | 50  | 0   | 50  | ns   |

| put Hold from Address Char   |                  | 0   | -   | 0   | -   | 0   | -   | ns   |

|                                 | <del></del>      | -   | 17  | -   | 20  | -,  | 25  |      |  |

|---------------------------------|------------------|-----|-----|-----|-----|-----|-----|------|--|

| Parameter                       | Symbol           | min | max | min | max | min | max | Unit |  |

| Address to Output Delay         | t <sub>ACC</sub> | -   | 170 | -   | 200 | •   | 250 | ns   |  |

| Chip Select Access Time         | t <sub>ce</sub>  | -   | 170 | -   | 200 | -   | 250 | ns   |  |

| Output Enable to Output Valid   | to∈              | -   | 65  | -   | 75  | -   | 100 | ns   |  |

| Chip Deselect to O/P high Z (2) | t <sub>oe</sub>  | 0   | 50  | 0   | 60  | 0   | 60  | ns   |  |

| Output Hold from Address Chan   |                  | 0   | -   | 0   | -   | 0   | -   | ns   |  |

Notes (1)  $V_{cc}$  must be applied simultaneously or before  $V_{pp}$  and removed simultaneously or after  $V_{pp}$ .

- (2) This parameter is sampled, not 100% tested.

- (3) See ordering information for speed and temperature restrictions.

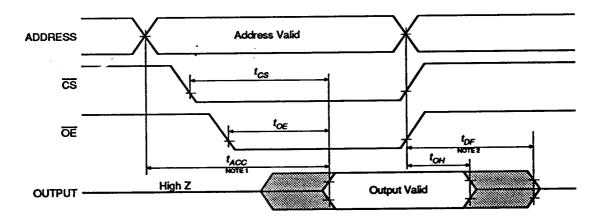

# **Read Cycle Timing Waveform**

Notes: (1)  $\overline{OE}$  may be delayed up to  $t_{acc}$ - $t_{oe}$  after the falling edge of  $\overline{CS}$  without impact on  $t_{acc}$ .

(2)  $t_{oe}$  is specified from  $\overline{OE}$  or  $\overline{CS}$  whichever occurs first.

#### PROGRAMMING OPERATION

The following information is provided for design purposes only.

| DC Electrical Character             | ristics (V <sub>cc</sub> =6.2 | 5V±0.2            | 5V,V <sub>pp</sub> =12.5V±0.5V,T <sub>A</sub> =25°C±5°C)                                                       |      |      |      |

|-------------------------------------|-------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------|------|------|------|

| Parameter                           | S                             | ymbol             | Test Condition                                                                                                 | min  | max  | Unit |

| Input Leakage Current               | Address, OE                   | l <sub>u1</sub>   | V <sub>cc</sub> =V <sub>cc</sub> max, V <sub>m</sub> =0V or V <sub>cc</sub> ,V <sub>pp</sub> =V <sub>ppH</sub> | -    | 4    | μА   |

|                                     | Other Pins                    | l <sub>uz</sub>   | $V_{cc} = V_{cc} \max_{s} V_{se} = 0 \text{V or } V_{cc}, V_{pp} = V_{ppH}$                                    | -    | 1    | μΑ   |

| V <sub>pp</sub> Program Current     | 32 bit                        | I <sub>PP32</sub> | Program, CS=V <sub>a</sub> , OE=V <sub>a</sub> ,                                                               | -    | 120  | mΑ   |

| FF -                                | 16 bit                        | I <sub>PP16</sub> | As above                                                                                                       | -    | 60   | mΑ   |

|                                     | 8 bit                         | I <sub>PP8</sub>  | As above                                                                                                       | -    | 30   | mA   |

| V <sub>∞</sub> Operating Supply Cu  | rrent 32 bit                  | I <sub>CC32</sub> | Program and Verify                                                                                             | -    | 200  | mA   |

| <b>&amp;</b> . • • · · · ·          | 16 bit                        | I <sub>CC16</sub> | As above                                                                                                       | -    | 102  | mA   |

|                                     | 8 bit                         | I <sub>CC8</sub>  | As above                                                                                                       | -    | 53   | mA   |

| Standby Supply Current              | TTL levels                    | I <sub>SB1</sub>  | V <sub>cc</sub> =V <sub>cc</sub> max, CS=V <sub>H</sub> <sup>(1)</sup>                                         | -    | 4    | mA   |

|                                     | CMOS levels                   | I <sub>SB2</sub>  | V <sub>cc</sub> =V <sub>cc</sub> max, CS=V <sub>cc</sub> -0.2V <sup>(1)</sup>                                  | -    | 400  | μΑ   |

| V <sub>∞</sub> Supply Voltage Durin | ng Program                    | V <sub>cc1</sub>  |                                                                                                                | 6.0  | 6.5  | ٧    |

| V <sub>PP</sub> Voltage During Prog |                               | V <sub>PPH</sub>  |                                                                                                                | 12.5 | 13.0 | ٧    |

| Identifier Select Voltage           |                               | V <sub>H</sub>    |                                                                                                                | 11.5 | 12.5 | V    |

| Output Low Voltage                  |                               | V <sub>OL</sub>   | I <sub>ot</sub> =2.1mA.                                                                                        | -    | 0.45 | V    |

| Output High Voltage                 |                               | V <sub>OH</sub>   | I <sub>οн</sub> ≖-400μA.                                                                                       | 2.4  | -    | V    |

Notes (1) CS above are accessed through CS1-4. These inputs must be operated simultaneoulsy for 32 bit operation, in pairs in 16 bit mode and singly for 8 bit mode.

- (2)  $V_{cc}$  must be applied simultaneously or before  $V_{pp}$ , and removed simultaneously or after  $V_{pp}$ .

- (3) A 0.1μF or greater capacitor is required between V<sub>PP</sub> and GND to suppress voltage transients.

- (4) CAUTION: the PUMA 2U8002 must not be removed from or inserted into a socket when  $V_{cc}$  or  $V_{pp}$  is applied.

- (3) Programming characteristics are sampled but not 100% tested at worst case conditions.

#### **Operating Modes**

This table shows the inputs required to control the operating modes of the EPROMs on the PUMA 2U8002.

| MODE       |              | <del>cs</del>   | ŌĒ              | PGM             | <b>A</b> o      | A <sub>9</sub> | V <sub>PP</sub> | OUTPUTS          |

|------------|--------------|-----------------|-----------------|-----------------|-----------------|----------------|-----------------|------------------|

| Read       |              | V <sub>IL</sub> | V <sub>IL</sub> | X               | X               | Х              | X               | D <sub>OUT</sub> |

| Output Di  | sable        | V <sub>EL</sub> | V <sub>IH</sub> | Х               | Х               | Х              | X               | High Z           |

| Standby    |              | VIH             | Х               | Х               | Х               | Х              | X               | High Z           |

| Program    |              | VIL             | V <sub>8H</sub> | VL              | Х               | Х              | V <sub>PP</sub> | D <sub>IN</sub>  |

| Program '  | Verify       | VIL             | VIL             | V <sub>IH</sub> | X               | Х              | V <sub>PP</sub> | D <sub>OUT</sub> |

| Program    | Inhibit      | V               | ×               | X               | ×               | Х              | V <sub>PP</sub> | High Z           |

| Identifier | Manufacturer | V <sub>IL</sub> | V <sub>IL</sub> | Х               | V <sub>IL</sub> | V <sub>H</sub> | Х               | 01 <sub>H</sub>  |

| (NOTE 1)   | Device Code  | V <sub>IL</sub> | V <sub>IL</sub> | Х               | V <sub>M</sub>  | V <sub>H</sub> | Х               | 97 <sub>H</sub>  |

V<sub>4</sub>=12.0V±0.5V X=V<sub>H</sub> or V<sub>L</sub> A1-A8=A10-A16=VIL

Notes (1) A1 - A8 = A10 - A17 = V<sub>II</sub>

(2) CS is accessed through CS1-4, and PGM is accessed through PGM1-4. For correct operation, CS1-4 must operate simultaneously for 32 bit operation, in pairs for 16 bit operation, or singly for 8 bit operation. PGM1-4 must also be operated in the same manner.

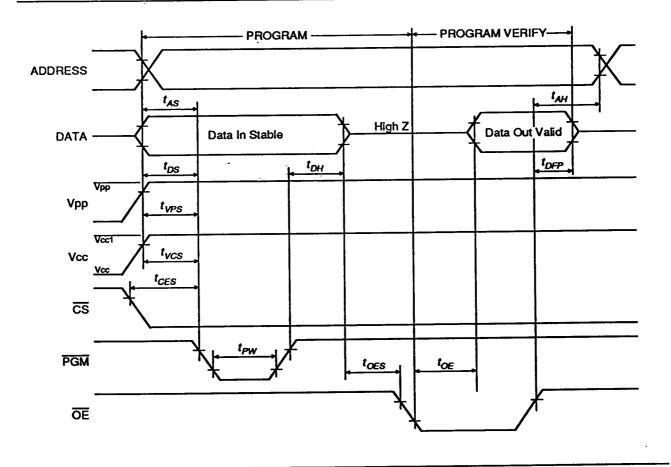

| Programming    | n Timina                                | Characteristics |

|----------------|-----------------------------------------|-----------------|

| i ivgiailiilii | 4 1 11111111111111111111111111111111111 | Olivi dotoliono |

| Parameter                    | Symbol           | min_ | typ | max | Unit |

|------------------------------|------------------|------|-----|-----|------|

| ddress Setup Time            | t <sub>AS</sub>  | 2    | -   | -   | μs   |

| DE Setup Time                | t <sub>oes</sub> | 2    | -   | -   | μs   |

| ata Setup Time               | t <sub>os</sub>  | 2    | -   | -   | μs   |

| ddress Hold Time             | t <sub>AH</sub>  | 0    | -   | -   | μs   |

| ata Hold Time                | t <sub>DH</sub>  | 2    | -   | -   | μs   |

| E High to Output Float Delay | t <sub>DFP</sub> | 0    | -   | 130 | ns   |

| Setup Time                   | t <sub>vps</sub> | 2    | -   | -   | μs   |

| M Initial Pulse Width        | t <sub>pw</sub>  | 95   | -   | 105 | μs   |

| <sub>c</sub> Setup Time      | t <sub>vcs</sub> | 2    | -   | -   | μs   |

| Setup Time                   | t <sub>ces</sub> | 2    | -   | -   | μs   |

| ta Valid from OE             | t <sub>o∈</sub>  | -    | -   | 150 | ns   |

# **Programming Cycle Timing Waveform**

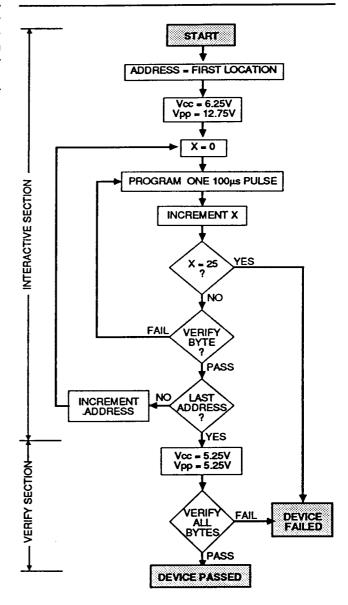

#### **High Performance Programming Algorithm**

The PUMA2U8002 can be programmed using the alogorithm shown here. This allows faster programming times without stressing the device or causing deterioration in Data Retention Time. Each of the four devices used on this module is an AMD Am27C020; this information, together with the device identifier code, should allow the correct programming alogorithm to be selected automatically.

Although the flow chart specifically refers to a single EPROM, all four devices on the PUMA tile can be programmed simultaneously in 32 bit mode, in pairs in 16 bit mode or singly in 8 bit mode. Obviously 32 bit mode is potentially the fastest programming time, but this makes greater demands on the  $V_{\rm pp}$  Supply Current as shown on the Programming Operation DC Characteristics on page 4.

#### **Programming**

Upon delivery, or after each erasure, the PUMA 2U8002 has all 8,388,608 bits in the ONE or HIGH state. ZEROs are loaded into the devices through the procedure of programming.

This mode is entered when 12.75V $\pm$ 0.25V is applied to the  $V_{pp}$  pin, CS and PGM are at  $V_{IL}$  and  $\overline{OE}$  is at  $V_{HI}$ , as shown on the Table on page 2. Data may be applied in 8, 16 or 32 bits in parallel depending on how CS1-4 and PGM1-4 are controlled.

The algorithm reduces programming time by using 100µs pulses followed by byte verification to determine if the byte has been successfully programmed. If the data does not verify, up to 25 such pulses can be applied, after which, if verification fails, programming stops. This process is repeated for each memory location within the PUMA 2U8002.

This algorithm programs at  $V_{\infty}$ =6.25V in order to ensure that each EPROM bit is programmed to a sufficiently high threshold voltage. After programming is complete, all bytes are compared with the original data with  $V_{\infty}$ =5.25V.

In order to overcome the voltage drop caused by the inductive effects of the printed circuit board on which the PUMA 2U8002 module is used, it is recommended that a 4.7 $\mu$ F electrolytic capacitor is used between V $_{\infty}$  and GND for every two PUMA modules. This capacitor should be placed close to the point where the power supply is routed to the UV EPROM array.

#### PROGRAMMING ALGORITHM

NOTE: THE ALGORITHM SHOWN HERE MUST BE USED TO ENSURE CORRECT PROGRAMMING OF THE PUMA 2U8002. THIS MAXIMIZES THE DATA RETENTION TIME OF THE UV EPROMS AND DOES NOT STRESS THE MEMORY CELL.

#### **DEVICE IDENTIFIER MODE**

The device identifier mode allows the reading out of a binary code from an EPROM which identify its manufacturer and specific type. It is intended to be used to automatically match the device to be programmed with the correct algorithm. This mode operates over the 25°C±5°C temperature range.

In order to activate this mode 12.0V $\pm$ 0.5V must be placed onto address line A9, after which two identifier bytes may be read by toggling A0 from V<sub>IL</sub> to V<sub>IH</sub>. All other address lines are held at V<sub>IL</sub> during this sequence.

The manufacturer code is accessed with  $A0=V_{\rm L}$  and the device code with  $A0=V_{\rm H}$ ; the values for these codes are given in the Operating Mode Table on page 2. Note that all identifiers for manufacturer and device codes will possess odd parity, with D7 defined as the parity bit.

#### **ERASE**

Complete erasure of the devices used on the PUMA 2U8002 is performed by exposure to an ultraviolet light source giving a dosage of 15WS/cm². This dosage can be obtained by using an ultraviolet lamp with a wavelength of 2537 Å at a minimum intensity of 12,000 $\mu$ W/cm², for approximately 15 - 20 minutes. The PUMA 2U8002 should be directly under and about 1 inch from the light source.

Note that sunlight and fluorescent light may contain sufficient ultraviolet light to erase the programmed information. Although erasure times will be much longer at these levels, the transparent lids on this module should be covered with an opaque label to realise maximum system reliability.

### **Military Screening Procedure**

Module Screening Flow for high reliability non-compliant product processed to MIL-STD-883D, Method 5004 is detailed below:

| MB MODULE SCREENING FLOW             |                                                                                                                            |              |  |  |  |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------|--|--|--|

| SCREEN                               | TEST METHOD                                                                                                                |              |  |  |  |

| Visual and Mechanical                |                                                                                                                            |              |  |  |  |

| External visual<br>Temperature cycle | 2017 Condition B (or manufacturers equivalent)<br>1010 Condition C (10 Cycles,-65°C to +150°C)                             | 100%<br>100% |  |  |  |

| Burn-In                              |                                                                                                                            |              |  |  |  |

| Pre Burn-in Electrical<br>Burn-In    | Per Applicable device Specifications at $T_A = +25^{\circ}C$ (optional)<br>Method 1015, Condition D, $T_A = +125^{\circ}C$ | 100%<br>100% |  |  |  |

| Final Electrical Tests               | Per applicable Device Specification                                                                                        |              |  |  |  |

| Static (dc)                          | a) @ T <sub>A</sub> =+25°C and power supply extremes<br>b) @ temperature and power supply extremes                         |              |  |  |  |

| Functional                           | <ul> <li>a) @ T<sub>x</sub>=+25°C and power supply extremes</li> <li>b) @ temperature and power supply extremes</li> </ul> | 100%<br>100% |  |  |  |

| Switching (ac)                       | <ul> <li>a) @ T<sub>A</sub>=+25°C and power supply extremes</li> <li>b) @ temperature and power supply extremes</li> </ul> | 100%<br>100% |  |  |  |

| Percent Defective Allowable (PDA)    | Calculated at Post Burn-in at T <sub>x</sub> =+25°C                                                                        |              |  |  |  |

| Quality Conformance                  | Per applicable Device Specification                                                                                        | Sample       |  |  |  |

| External Visual                      | 2009 Per MSI or customer specification                                                                                     |              |  |  |  |

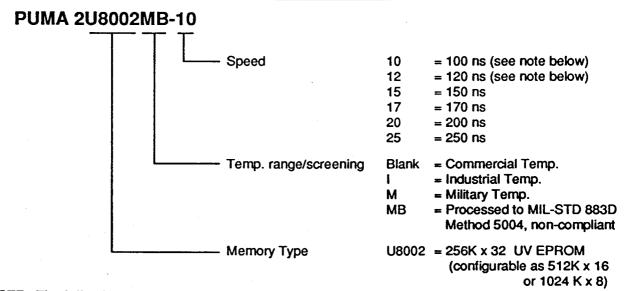

### Ordering Information

NOTE - The following devices are not available at present:

PUMA 2U8002I-10, M-10, MB-10, M-12, MB-12

mofaic

Mosaic

Semiconductor

The policy of the company is one of continuous development and while the information presented in this data sheet is believed to be accurate, no liability is assumed for any data contained within. The company reserves the right to make changes without notice at any time.

© 1988 This design is the property of Mosaic Semiconductor, Inc.

7420 Carroll Road San Diego, CA 92121 Tel: (619) 271 4565 FAX: (619) 271 6058

029450