PRELIMINARY

# SERIES 2 FLASH MEMORY CARDS iMC002FLSA, iMC004FLSA, iMC010FLSA, iMC020FLSA

Extended Temperature Specifications Included

- 2, 4, 10 and 20 Megabyte Capacities

- PCMCIA 2.1/JEIDA 4.1 68-Pin Standard

- Hardwired Card Information

Structure

- Byte- or Word-Wide Selectable

- Component Management Registers for Card Status/Control and Flexible System Interface

- Automatic Erase/WriteMonitored with Ready/Busy Output

- Card Power-Down Modes— Deep-Sleep for Low Power

- Mechanical Write Protect Switch

- Solid-State Reliability

**Applications**

■ Intel FlashFile™ Architecture

- High-Performance Read Access — 150 ns Maximum

- High-Performance Random Writes

6 μs Typical Word Write

- Erase Suspend to Read Command— Keeps Erase as Background Task

- Nonvolatility (Zero Retention Power)

No Batteries Required for Back-up

- ETOX<sup>™</sup> V 0.4*µ* Flash Memory Technology

- 5V Read, 12V Erase/Write

- High-Volume Manufacturing Experience

- Extended Temperature Version — -40°C to +85°C

Intel's Series 2 Flash Memory Card facilitates high-performance disk emulation in mobile PCs and dedicated equipment. Manufactured with Intel's ETOX<sup>TM</sup> III  $0.8\mu$ , FlashFile Memory devices, the Series 2 Card allows code and data retention while erasing and/or writing other blocks. Additionally, the Series 2 Flash Memory Card features low power modes, flexible system interfacing and a 150 ns read access time. When coupled with Intel's low-power microprocessors, these cards enable high-performance implementations of mobile computers and systems.

Series 2 Cards conform to the Personal Computer Memory Card International Association (PCMCIA 2.1)/Japanese Electronics Industry Development Association (JEIDA 4.1) 68-pin standard, providing electrical and physical compatibility.

Data file management software, Flash Translation Layer (FTL), provides data file storage and memory management, much like a disk operating system. Intel's Series 2 Flash Memory Cards, coupled with flash file management software, effectively provide a removable, all-silicon mass storage solution with higher performance and reliability than disk-based memory architectures.

Designing with Intel's FlashFile Architecture enables OEM system manufacturers to design and manufacture a new generation of mobile PCs and dedicated equipment where high performance, ruggedness, long battery life and lighter weight are a requirement. For large user groups in workstation environments, the Series 2 Cards provide a means to securely store user data and backup system configuration/status information.

December 1996 Order Number: 290434-006

Table 1. Series 2 Flash Memory Card Pinout

| Pin | Signal            | 1/0 | Function       | Active |

|-----|-------------------|-----|----------------|--------|

| 1   | GND               |     | Ground         |        |

| 2   | DQ <sub>3</sub>   | 1/0 | Data Bit 3     |        |

| 3   | DQ <sub>4</sub>   | 1/0 | Data Bit 4     |        |

| 4   | DQ <sub>5</sub>   | 1/0 | Data Bit 5     |        |

| 5   | DQ <sub>6</sub>   | 1/0 | Data Bit 6     |        |

| 6   | DQ <sub>7</sub>   | 1/0 | Data Bit 7     |        |

| 7   | CE <sub>1</sub> # | - 1 | Card Enable 1  | O      |

| 8   | A <sub>10</sub>   | - 1 | Address Bit 10 |        |

| 9   | OE#               | - 1 | Output Enable  | LO     |

| 10  | A <sub>11</sub>   | - 1 | Address Bit 11 |        |

| 11  | A <sub>9</sub>    | I   | Address Bit 9  |        |

| 12  | A <sub>8</sub>    | I   | Address Bit 8  |        |

| 13  | A <sub>13</sub>   | I   | Address Bit 13 |        |

| 14  | A <sub>14</sub>   | I   | Address Bit 14 |        |

| 15  | WE#               | 1   | Write Enable   | LO     |

| 16  | RDY/BSY#          |     | Ready-Busy     | HI/LO  |

| 17  | V <sub>CC</sub>   |     | Supply Voltage |        |

| 18  | V <sub>PP1</sub>  |     | Supply Voltage |        |

| 19  | A <sub>16</sub>   | I   | Address Bit 16 |        |

| 20  | A <sub>15</sub>   | I   | Address Bit 15 |        |

| 21  | A <sub>12</sub>   | ı   | Address Bit 12 |        |

| 22  | A <sub>7</sub>    | I   | Address Bit 7  |        |

| 23  | A <sub>6</sub>    | ı   | Address Bit 6  |        |

| 24  | A <sub>5</sub>    | I   | Address Bit 5  |        |

| 25  | A <sub>4</sub>    | I   | Address Bit 4  |        |

| 26  | A <sub>3</sub>    | ı   | Address Bit 3  |        |

| 27  | A <sub>2</sub>    | I   | Address Bit 2  |        |

| 28  | A <sub>1</sub>    | I   | Address Bit 1  |        |

| 29  | A <sub>0</sub>    | I   | Address Bit 0  |        |

| 30  | DQ <sub>0</sub>   | 1/0 | Data Bit 0     |        |

| 31  | DQ <sub>1</sub>   | 1/0 | Data Bit 1     |        |

| 32  | DQ <sub>2</sub>   | 1/0 | Data Bit 2     |        |

| 33  | WP                | 0   | Write Protect  | HI     |

| 34  | GND               |     | Ground         |        |

2

| ve | Pin | Signal            | 1/0 | Function         | Active |

|----|-----|-------------------|-----|------------------|--------|

|    | 35  | GND               |     | Ground           |        |

|    | 36  | CD <sub>1</sub> # | 0   | Card Detect 1    | LO     |

|    | 37  | DQ <sub>11</sub>  | 1/0 | Data Bit 11      |        |

|    | 38  | DQ <sub>12</sub>  | 1/0 | Data Bit 12      |        |

|    | 39  | DQ <sub>13</sub>  | 1/0 | Data Bit 13      |        |

|    | 40  | DQ <sub>14</sub>  | 1/0 | Data Bit 14      |        |

| )  | 41  | DQ <sub>15</sub>  | 1/0 | Data Bit 15      |        |

|    | 42  | CE <sub>2</sub> # | ı   | Card Enable 2    | LO     |

| )  | 43  | VS <sub>1</sub>   | 0   | Voltage Sense 1  | N.C.   |

|    | 44  | RFU               |     | Reserved         |        |

|    | 45  | RFU               |     | Reserved         |        |

|    | 46  | A <sub>17</sub>   | ı   | Address Bit 17   |        |

|    | 47  | A <sub>18</sub>   | I   | Address Bit 18   |        |

|    | 48  | A <sub>19</sub>   | ı   | Address Bit 19   |        |

|    | 49  | A <sub>20</sub>   | ı   | Address Bit 20   |        |

| .0 | 50  | A <sub>21</sub>   | ı   | Address Bit 21   |        |

|    | 51  | V <sub>CC</sub>   |     | Supply Voltage   |        |

|    | 52  | V <sub>PP2</sub>  |     | Supply Voltage   |        |

|    | 53  | A <sub>22</sub>   | I   | Address Bit 22   |        |

|    | 54  | A <sub>23</sub>   | ı   | Address Bit 23   |        |

|    | 55  | A <sub>24</sub>   | I   | Address Bit 24   |        |

|    | 56  | A <sub>25</sub>   |     | No Connect       |        |

|    | 57  | VS <sub>2</sub>   | 0   | Voltage Sense 2  | N.C.   |

|    | 58  | RST               | I   | Reset            | HI     |

|    | 59  | WAIT#             | 0   | Extend Bus Cycle | LO     |

|    | 60  | RFU               |     | Reserved         |        |

|    | 61  | REG#              | ı   | Register Select  | LO     |

|    | 62  | BVD <sub>2</sub>  | 0   | Batt. Volt Det 2 |        |

|    | 63  | BVD <sub>1</sub>  | 0   | Batt. Volt Det 1 |        |

|    | 64  | DQ <sub>8</sub>   | 1/0 | Data Bit 8       |        |

|    | 65  | DQ <sub>9</sub>   | 1/0 | Data Bit 9       |        |

|    | 66  | DQ <sub>10</sub>  | 1/0 | Data Bit 10      |        |

|    | 67  | CD <sub>2</sub> # | 0   | Card Detect 2    | LO     |

|    | 68  | GND               |     | Ground           |        |

Table 2. Series 2 Flash Memory Card Pin Descriptions

| Symbol                                | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub> -A <sub>25</sub>       | I    | <b>ADDRESS INPUTS:</b> $A_0$ through $A_{25}$ are address bus lines which enable direct addressing of 64 megabytes of memory on a card. $A_0$ is not used in word access mode. $A_{24}$ is the most significant address bit. Note: $A_{25}$ is a no-connect but should be provided on host side.                                                                                                    |

| DQ <sub>0</sub> -DQ <sub>15</sub>     | 1/0  | <b>DATA INPUT/OUTPUT:</b> $DQ_0$ through $DQ_{15}$ constitute the bidirectional data bus. $DQ_{15}$ is the most significant bit.                                                                                                                                                                                                                                                                    |

| CE <sub>1</sub> #, CE <sub>2</sub> #  | I    | <b>CARD ENABLE 1, 2:</b> $CE_1\#$ enables even bytes, $CE_2\#$ enables odd bytes. Multiplexing $A_0$ , $CE_1\#$ and $CE_2\#$ allows 8-bit hosts to access all data on $DQ_0$ through $DQ_1$ . (See Table 3 for a more detailed description.)                                                                                                                                                        |

| OE#                                   | I    | OUTPUT ENABLE: Active low signal gating read data from the memory card.                                                                                                                                                                                                                                                                                                                             |

| WE#                                   | I    | WRITE ENABLE: Active low signal gating write data to the memory card.                                                                                                                                                                                                                                                                                                                               |

| RDY/BSY#                              | 0    | READY/BUSY OUTPUT: Indicates status of internally timed erase or write activities. A high output indicates the memory card is ready to accept accesses. A low output indicates that a device(s) in the memory card is(are) busy with internally timed activities. See text for an alternate function (READY-BUSY MODE REGISTER).                                                                    |

| CD <sub>1</sub> # & CD <sub>2</sub> # | 0    | CARD DETECT 1, 2: These signals provide for correct card insertion detection. They are positioned at opposite ends of the card to detect proper alignment. The signals are connected to ground internally on the memory card and will be forced low whenever a card is placed in the socket. The host socket interface circuitry shall supply 10K or larger pull-up resistors on these signal pins. |

| WP                                    | 0    | <b>WRITE PROTECT:</b> Write Protect reflects the status of the Write-Protect switch on the memory card. WP set high = write protected, providing internal hardware write lockout to the flash array.                                                                                                                                                                                                |

| V <sub>PP1</sub> , V <sub>PP2</sub>   |      | WRITE/ERASE POWER SUPPLY: (12V nominal) for erasing memory array blocks or writing data in the array. They must be 12V to perform an erase/write operation.                                                                                                                                                                                                                                         |

| V <sub>CC</sub>                       |      | CARD POWER SUPPLY (5V nominal) for all internal circuitry.                                                                                                                                                                                                                                                                                                                                          |

| GND                                   | I    | GROUND for all internal circuitry.                                                                                                                                                                                                                                                                                                                                                                  |

| REG#                                  | I    | <b>REGISTER SELECT</b> provides access to Series 2 Flash Memory Card registers and Card Information Structure in the Attribute Memory Plane.                                                                                                                                                                                                                                                        |

| RST                                   | I    | <b>RESET</b> from system, active high. Places card in Power-On Default State. RESET pulse width must be $\geq$ 200 ns.                                                                                                                                                                                                                                                                              |

| WAIT#                                 | 0    | WAIT (Extend Bus Cycle) is used by Intel's I/O cards and is driven high.                                                                                                                                                                                                                                                                                                                            |

| BVD <sub>1</sub> , BVD <sub>2</sub>   | 0    | <b>BATTERY VOLTAGE DETECT:</b> Upon completion of the power on reset cycle, these signals are driven high to maintain SRAM-card compatibility.                                                                                                                                                                                                                                                      |

| RFU                                   |      | RESERVED FOR FUTURE USE                                                                                                                                                                                                                                                                                                                                                                             |

| NC                                    |      | NO INTERNAL CONNECTION. Pin may be driven or left floating.                                                                                                                                                                                                                                                                                                                                         |

| VS <sub>1</sub> , VS <sub>2</sub>     |      | <b>VOLTAGE SENSE:</b> Notifies the host Socket of the card's $V_{CC}$ requirements. $VS_1$ and $VS_2$ are both open, indicating a 5V $V_{CC}$ card.                                                                                                                                                                                                                                                 |

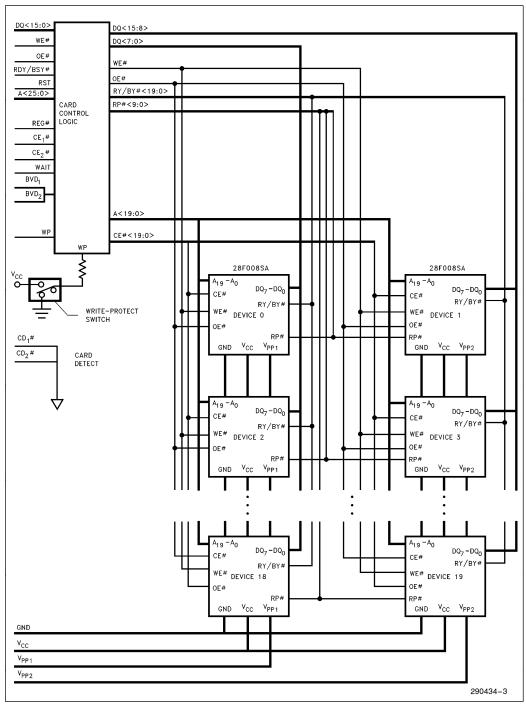

Figure 1. Detailed Block Diagram. The Card Control Logic Provides

Decoding Buffering and Control Signals.

### **APPLICATIONS**

Intel's second generation Series 2 Flash Memory Cards facilitate high performance disk emulation for the storage of data files and application programs on a purely solid-state removable medium. File management software, Flash Translation Layer (FTL), in conjunction with the Series 2 Flash Memory Cards, enable the design of high-performance light-weight notebook, palmtop, and pen-based PCs that have the processing power of today's desktop computers.

Application software stored on the flash memory card substantially reduces the slow disk-to-DRAM download process. Replacing the mechanical disk results in a dramatic enhancement of read performance and substantial reduction of power consumption, size and weight-considerations particularly important in portable PCs and equipment. The Series 2 Card's high performance read access time allows the use of Series 2 Cards in an "execute-inplace" (XIP) architecture. XIP eliminates redundancy associated with DRAM/Disk memory system architectures. Operating systems stored in Flash Memory decreases system boot or program load times, enabling the design of PCs that boot, operate, store data files and execute application programs from/to nonvolatile memory without losing the ability to perform an update.

File management systems modify and store data files by allocating flash memory space intelligently. Wear leveling algorithms, employed to equally distribute the number of rewrite cycles, ensure that no particular block is cycled excessively relative to other blocks. This provides hundreds of thousands of hours of power on usage.

This file management software enables the user to interact with the flash memory card in precisely the same way as a magnetic disk.

Series 2 Flash Memory Cards provide durable nonvolatile memory storage for mobile PCs on the road, facilitating simple transfer back into the desktop environment For systems currently using a static RAM/battery configuration for data acquisition, the Series 2 Flash Memory Card's nonvolatility eliminates the need for battery backup. The concern for battery failure no longer exists, an important consideration for portable computers and medical instruments, both requiring continuous operation. Series 2 Cards consume no power when the system is off, and only 60  $\mu A$  in Deep-Sleep mode (2 Megabyte card). Furthermore, Flash Memory Cards offer a considerable cost and density advantage over memory cards based on static RAM with battery backup.

Besides disk emulation, the Series 2 Card's electrical block-erasure, data writability, and inherent nonvolatility fit well with data accumulation and recording needs. Electrical block-erasure provides design flexibility to selectively rewrite blocks of data, while saving other blocks for infrequently updated parameters and lookup tables. For example, networks and systems that utilize large banks of battery-backed DRAM to store configuration and status benefit from the Series 2 Flash Card's nonvolatility and reliability.

# SERIES 2 ARCHITECTURE OVERVIEW

The Series 2 Flash Memory Card contains a 2 to 20 Megabyte Flash Memory array consisting of 2 to 20 28F008SA FlashFile Memory devices. Each 28F008SA contains sixteen individually-erasable, 64 Kbyte blocks; therefore, the Flash Memory Card contains from 32 to 320 device blocks. It also contains two Card Control Logic devices that manage the external interface, address decoding, and component management logic. (Refer to Figure 1 for a block diagram.)

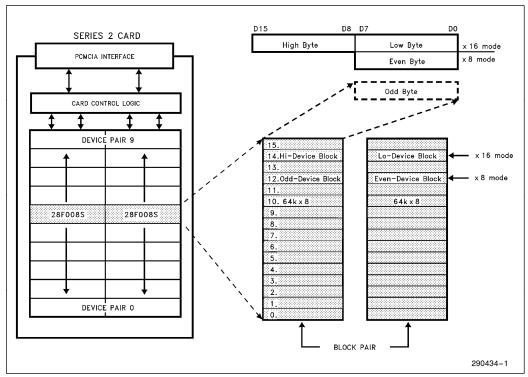

To support PCMCIA-compatible word-wide access, devices are paired so that each accessible memory block is 64 KWords (see Figure 2). Card logic allows the system to write or read one word at a time, or one byte at a time by referencing the high or low byte. Erasure can be performed on the entire block pair (high and low device blocks simultaneously), or on the high or low byte portion separately.

Also in accordance with PCMCIA specifications this product supports byte-wide operation, in which the flash array is divided into 128K x 8 bit device blocks. In this configuration, odd bytes are multiplexed onto the low byte data bus.

Figure 2. Memory Architecture. Each Device Pair Consists of Sixteen 64 KWord Blocks.

Series 2 Flash Memory Cards offer additional features over the Bulk Erase Flash Card product family (refer to iMC001FLKA, iMC002FLKA and iMC004FLKA data sheets). Some of the more notable enhancements include: high density capability, erase blocking, internal write/erase automation, erase suspension to read, Component Management Registers that provide software control of device-level functions and a deep-sleep mode.

Erase blocking facilitates solid-state storage applications by allowing selective memory reclamation. Multiple 64 Kbyte blocks may be simultaneously erased within the memory card as long as not more than one block per device is erasing. This shortens the total time required for erasure, but requires additional supply current. A block typically requires 1.6 seconds to erase. Each memory block can be erased and completely written 100,000 times.

Erase suspend allows the system to temporarily interrupt a block erase operation. This mode permits reads from alternate device blocks while that same device contains an erasing block. Upon completion of the read operation, erasure of the suspended block must be resumed.

Write/erase automation simplifies the system software interface to the card. A two-step command sequence initiates write or erase operations and provides additional data security. Internal device circuits automatically execute the algorithms and timings necessary for data-write or block-erase operations, including verifications for long-term data integrity. While performing either data-write or block-erase, the memory card interface reflects this by bringing its RDY/BSY# (Ready/Busy) pin low. This output goes high when the operation completes. This feature reduces CPU overhead and allows software polling or hardware interrupt mechanisms. Writing memory data is achieved in single byte or word increments, typically in 6 μs.

Read access time is 150 ns or less over the entire operating temperature range.

The Reset-PowerDown mode reduces power consumption to less than 60  $\mu$ A to help extend battery life of portable host systems. Activated through software control, this mode optionally affects the entire flash array (Global Reset-PowerDown Register) or specific device pairs (Sleep Control Register).

#### PCMCIA/JEIDA INTERFACE

The Series 2 Flash Memory Card interface supports the PCMCIA 2.1 and JEIDA 4.1 68-pin card format (see Tables 1 and 2). Detailed specifications are described in the PC Card Standard, Release 2.1, July, 1993, published by PCMCIA. The Series 2 Card conforms to the requirements of both Release 1 and Release 2 of the PC Card Standard.

Series 2 Card pin definitions are equivalent to the Bulk-Erase Flash Card except that certain No Connects are now used. A<sub>22</sub> through A<sub>24</sub>, RST (Reset), and RDY/BSY# (Ready/Busy) have pin assignments as set by the PCMCIA standard.

NOTE: The READY/BUSY signal is abbreviated as RDY/BSY# by PCMCIA (card level) and as RY/BY# by JEDEC (component level).

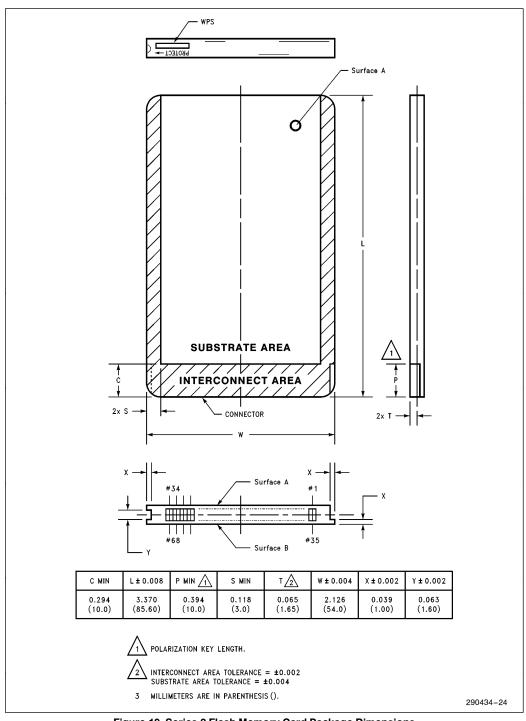

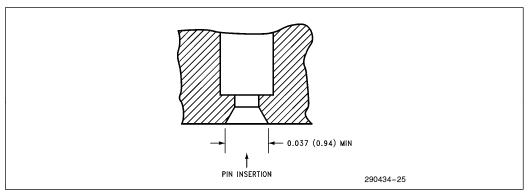

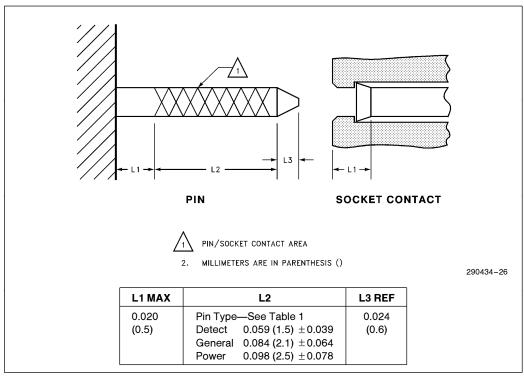

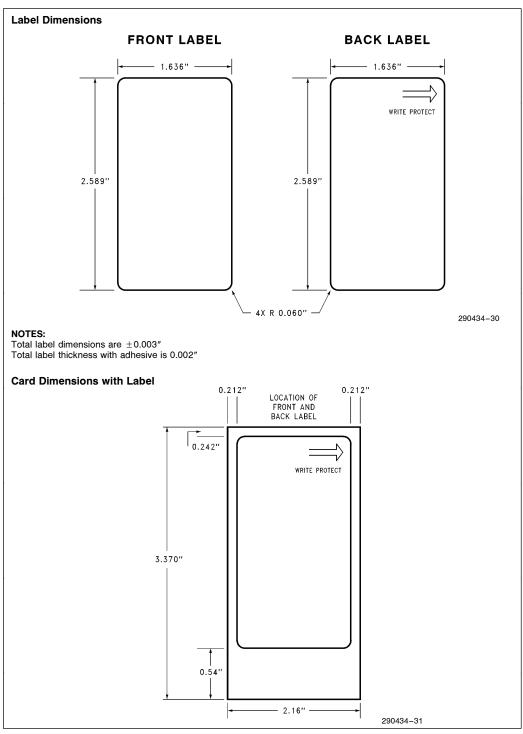

The outer shell of the Series 2 card meets all PCMCIA/JEIDA Type 1 mechanical specifications. See Figure 19 for mechanical dimensions.

## WRITE PROTECT SWITCH

A mechanical write protect switch provides the card's memory array with internal write lockout. The Write-Protect (WP) output pin reflects the status of this mechanical switch. It outputs a high signal ( $V_{OH}$ ) when writes are disabled. This switch does not lock out writes to the Component Management Registers.

#### **BATTERY VOLTAGE DETECT**

PCMCIA requires two signals,  $BVD_1$  and  $BVD_2$ , be supplied at the interface to reflect card battery condition. Flash Memory Cards do not require batteries. When the power on reset cycle is complete,  $BVD_1$  and  $BVD_2$  are driven high to maintain compatibility.

#### CARD DETECT

Two signals,  $CD_1\#$  and  $CD_2\#$ , allow the host to determine proper socket seating. They reside at opposite ends of the connector and are tied to ground within the memory card.

#### **DESIGN CONSIDERATIONS**

The Series 2 Card consists of two separate memory planes: the Common Memory Plane (or Main Memory) and the Attribute Memory Plane. The Common Memory Plane resides in the banks of device pairs and represents the user-alterable memory space.

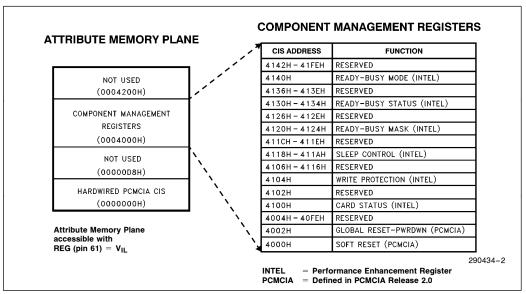

The Component Management Registers (CMR) and the hardwired Card Information Structure (CIS) reside in the Attribute Memory Plane within the Card Control Logic, as shown in Figure 3. The Card Control Logic interfaces the PCMCIA connector and the internal flash memory array and performs address decoding and data control.

Figure 3. Component Management Registers Allow S/W Control of Components within Card

### **ADDRESS DECODE**

Address decoding provides the decoding logic for the 2 to 20 Device Chip Enables and the elements of the Attribute Memory Plane. REG# selects between the Common Memory Plane (REG# =  $V_{IH}$ ) and the Attribute Memory Plane (REG# =  $V_{IL}$ ).

#### NOTE:

The Series 2 Card has *active* address inputs  $A_0$  to  $A_{24}$  implying that reading and writing to addresses beyond 32 Megabytes causes wraparound. Furthermore, reads to illegal addresses (for example, between 20 and 32 Meg on a 20 Megabyte card) returns Default data (00FFH or FFFFH).

The 28F008SA devices, storing data, applications or firmware, form the Common Memory Plane accessed individually or as device pairs. Memory is linearly mapped in the Common Memory Plane. Three memory access modes are available when accessing the Common Memory Plane: Byte-Wide, Word Wide, and Odd-Byte modes.

Additional decoding selects the hardwired PCMCIA CIS and Component Management Registers mapped in the Attribute Memory Plane beginning at address 000000H.

The 512 memory-mapped even-byte CMRs are linearly mapped beginning at address 4000H in the Attribute Memory Plane.

#### **DATA CONTROL**

Data Control Logic selects the path and direction for accessing the Common or Attribute Memory Plane. It controls any of the PCMCIA-defined Word-Wide, Byte-Wide or Odd-Byte modes for either reads or writes to these areas. As shown in Table 3, input pins which determine these selections are REG#, A<sub>0</sub> through A<sub>24</sub>, WE#, OE#, CE<sub>1</sub>#, and CE<sub>2</sub>#. PCMCIA specifications allow only even-byte access to the Attribute Memory Plane.

In Byte-Wide mode, bytes contiguous in software actually alternate between two device blocks of a device pair. Therefore, erasure of one device block erases every other contiguous byte. In accordance with the PCMCIA standard for memory configuration, the Series 2 Card does not support confining contiguous bytes within one flash device when in by-8 mode.

**Table 3. Data Access Mode Truth Table**

| Function Mode  | REG#   | CE#2 | CE# <sub>1</sub> | A <sub>0</sub> | OE# | WE# | V <sub>PP2</sub>     | V <sub>PP1</sub>     | D <sub>15</sub> -D <sub>8</sub> | D <sub>7</sub> -D <sub>0</sub>      |

|----------------|--------|------|------------------|----------------|-----|-----|----------------------|----------------------|---------------------------------|-------------------------------------|

| COMMON MEMOR   | Y PLAN | E    |                  |                |     |     |                      |                      |                                 |                                     |

| STANDBY(1)     | Х      | Η    | Н                | Х              | Х   | Х   | V <sub>PPL</sub> (2) | V <sub>PPL</sub> (2) | HIGH-Z                          | HIGH-Z                              |

| BYTE READ      | Н      | Ι    | ┙                | L              | L   | Н   | V <sub>PPL</sub> (2) | V <sub>PPL</sub> (2) | HIGH-Z                          | EVEN-BYTE                           |

|                | Н      | Η    | ┙                | Н              | L   | Н   | V <sub>PPL</sub> (2) | V <sub>PPL</sub> (2) | HIGH-Z                          | ODD-BYTE                            |

| WORD READ      | Н      | L    | L                | Х              | L   | Н   | V <sub>PPL</sub> (2) | V <sub>PPL</sub> (2) | ODD-BYTE                        | EVEN-BYTE                           |

| ODD-BYTE READ  | Н      | L    | Н                | Х              | L   | Н   | V <sub>PPL</sub> (2) | V <sub>PPL</sub> (2) | ODD-BYTE                        | HIGH-Z                              |

| BYTE WRITE     | Н      | Н    | L                | L              | Н   | L   | V <sub>PPH</sub>     | V <sub>PPH</sub>     | X                               | EVEN-BYTE                           |

|                | Н      | Η    | ┙                | Н              | Н   | L   | V <sub>PPH</sub>     | V <sub>PPH</sub>     | X                               | ODD-BYTE                            |

| WORD WRITE     | Н      | لــ  | ┙                | Х              | Н   | L   | V <sub>PPH</sub>     | V <sub>PPH</sub>     | ODD-BYTE                        | EVEN-BYTE                           |

| ODD-BYTE WRITE | Н      | ┙    | Η                | Х              | Н   | L   | V <sub>PPH</sub>     | V <sub>PPL</sub> (2) | ODD-BYTE                        | X                                   |

| ATTRIBUTE MEMO | RY PLA | NE   |                  |                |     |     |                      |                      |                                 |                                     |

| BYTE READ      | L      | Н    | L                | L              | L   | Н   | χ(2)                 | χ(2)                 | HIGH-Z                          | EVEN-BYTE                           |

|                | L      | Η    | L                | Н              | L   | Н   | χ(2)                 | χ(2)                 | HIGH-Z                          | INVALID                             |

| WORD READ      | L      | L    | L                | х              | L   | Н   | χ(2)                 | χ(2)                 | INVALID<br>DATA <sup>(3)</sup>  | EVEN-BYTE                           |

| ODD-BYTE READ  | L      | L    | Н                | Х              | L   | Н   | χ(2)                 | χ(2)                 | INVALID<br>DATA <sup>(3)</sup>  | HIGH-Z                              |

| BYTE WRITE     | L      | Η    | L                | L              | Н   | L   | χ(2)                 | χ(2)                 | X                               | EVEN-BYTE                           |

|                | L      | Н    | L                | Н              | Н   | L   | χ(2)                 | χ(2)                 | Х                               | INVALID<br>OPERATION <sup>(3)</sup> |

| WORD WRITE     | L      | _ا   | L                | Х              | Н   | L   | χ(2)                 | χ(2)                 | INVALID<br>OPERATION(3)         | EVEN-BYTE                           |

| ODD-BYTE WRITE | L      | L    | Н                | Х              | Н   | L   | χ(2)                 | χ(2)                 | INVALID<br>OPERATION(3)         | Х                                   |

- **NOTES:**1. Standby mode is valid in Common Memory or Attribute Memory access.

2. To meet the low power specifications,  $V_{PP} = V_{PPL}$ ; however  $V_{PPH}$  presents no reliability problems.

3. Odd-Byte data are not valid during access to the Attribute Memory Plane.

4.  $H = V_{IH}$ ,  $L = V_{IL}$ , X = Don't Care.

### PRINCIPLES OF OPERATION

Intel's Series 2 Flash Memory Card provides electrically-alterable, non-volatile, random-access storage. Individual 28F008SA devices utilize a Command User Interface (CUI) and Write State Machine (WSM) to simplify block-erasure and data write operations.

#### COMMON MEMORY ARRAY

Figure 4 shows the Common Memory Plane's organization. The first block pair (64 KWords) of Common Memory, referred to as the Common Memory Card Information Structure Block, optionally extends the hardwired CIS in the Attribute Memory Plane for additional card information. This may be written during initial card formatting for OEM customization. Since this CIS Block is part of Common Memory, its data can be altered. Write access to the Common Memory CIS Block is controlled by the Write Protect Control Register which may be activated by system software after power-up. Additionally, the entire Common Memory plane (minus the Common Memory CIS Block) may be software write protected. Note that the Common Memory CIS Block is not part of the Attribute Memory Plane. Do not assert REG # to access the Common Memory CIS Block.

| 13FFFFFH | Device Pair 9 |

|----------|---------------|

| 1200000H | Device Pail 9 |

| 1000000H | Device Pair 8 |

| 0E00000H | Device Pair 7 |

| 0C00000H | Device Pair 6 |

| 0A00000H | Device Pair 5 |

| 0800000H | Device Pair 4 |

| 0600000H | Device Pair 3 |

| 0400000H | Device Pair 2 |

| 0200000H | Device Pair 1 |

| 0020000H | Device Pair 0 |

| 0000000H | Optional CIS  |

Figure 4. Common Memory Plane. Use the Optional Common Memory Plane CIS for Custom Card Format Information.

#### HARDWIRED CIS

The card's structure description resides in the evenbyte locations starting at 0000H and going to the CIS ending tuple (FNULL) within the Attribute Memory Plane. Data included in the hardwired CIS consists of tuples. Tuples are a variable-length list of data blocks describing details such as manufacturer's name, the size of each memory device and the number of flash devices within the card.

# COMPONENT MANAGEMENT REGISTERS (CMRs)

The CMRs in the Attribute Memory Plane provide special, software-controlled functionality. Card Control Logic includes circuitry to access the CMRs. REG (PCMCIA, pin 61) selects the Attribute Memory Plane (and therefore the CMRs) when equal to V<sub>IL</sub>.

CMRs are classified into two categories: those defined by PCMCIA R2.1 and those included by Intel (referred to as Performance Enhancement Registers) to enhance the interface between the host system and the card's flash memory array. CMRs (See Figure 3) provide seven control functions—Ready-Busy Interrupt Mode, Device Ready-Busy Status, Device Ready-Busy Mask, Reset-PowerDown Control, Software-controlled Write Protection, Card Status and Soft Reset.

# **SOFT RESET REGISTER (PCMCIA)**

(CONFIGURATION OPTION)

The SOFT RESET REGISTER (Attribute Memory Plane Address 4000H, Figure 5) is defined in the PCMCIA Release 2.0 specification as the Configuration Option Register.

Bit 7 is the soft reset bit (SRESET). Writing a 1 to this bit initiates card reset to the power-on default state (see Side Bar page 11). This bit must be cleared to use the CMRs or to access the devices.

SRESET implements in software what the reset pin implements in hardware. On power-up, the card automatically assumes default conditions. Similar to the reset pin (pin 58), this bit clears at the end of a power-on reset cycle or a system reset cycle.

Bits 0 through 6 are not used by this memory card, but power up as zeroes for PCMCIA compatibility.

#### SOFT RESET REGISTER

#### (CONFIGURATION OPTION REGISTER)

(Read/Write Register)

| ADDRESS | BIT 7  | BIT 6 | BIT 5 | BIT 4 | BIT 4                  | BIT 2                  | BIT 1 | BIT 0 |

|---------|--------|-------|-------|-------|------------------------|------------------------|-------|-------|

| 4000H   | SRESET |       |       |       | ONFIGURAT<br>O ZERO ON | TION INDEX<br>POWER UP |       |       |

1 = RESET, CLEAR TO ACCESS CARD

Figure 5. SOFT RESET REGISTER (PCMCIA). Sets the Memory Card in the Power-On Default State.

#### **POWER-ON DEFAULT CONDITIONS**

- All Devices Powered Up In Standby Mode

- Common Memory Available For Writes

- All Device Ready/Busy Outputs Unmasked

- PCMCIA Ready/Busy Mode Enabled

- · Ready/Busy Output Goes To Ready

# Global PowerDown Register (PCMCIA)

(Configuration and Status)

The Global Reset-PowerDown Register (Attribute Memory Plane Address 4002H, Figure 6) is referred to as the Configuration and Status Register in the PCMCIA Release 2.0 specification.

Bit 2 (RP) controls global card power-down. Writing a 1 to this bit places each device within the card into "Deep-Sleep" mode. *Devices in Deep-Sleep are not accessible.* Recovery from power-down requires 500 ns for reads and 1  $\mu$ s for writes.

The RP bit defaults to 0 on card power-up or reset. Setting or clearing this bit has no affect on the bit settings of the Sleep Control Register.

The remaining Global Reset-PwrDwn Register bits are defined for Intel's family of I/O cards and are driven low for compatibility.

## **GLOBAL RESET-POWER-DOWN REGISTER**

(CONFIGURATION AND STATUS REGISTER)

(Read/Write Register)

Figure 6. GLOBAL RESET-PWRDWN REGISTER (PCMCIA). The RP Bit Enables Reset PowerDown of All Flash Memory Devices.

#### **CARD STATUS REGISTER**

(Read Only Register)

| ADDRESS | BIT 7 | BIT 6 | BIT 5  | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0    |

|---------|-------|-------|--------|-------|-------|-------|-------|----------|

| 4100H   | ADM   | ADS   | SRESET | CMWP  | RP    | CISWP | WP    | RDY/BSY# |

Figure 7. CARD STATUS REGISTER (Intel) Provides a Quick Review of the Card's Status

# **CARD STATUS REGISTER (INTEL)**

The Read-Only, CARD STATUS REGISTER (Attribute Memory Plane Address 4100H, Figure 7) returns generalized status of the Series 2 Card and its CMRs.

Bit 0 (RDY/BSY#) reflects the card's RDY/BSY# (Ready-Busy) output. Software polling of this bit provides data-write or block-erase operation status. A zero indicates a busy device(s) in the card.

Bit 1 (WP) reports the position of the card's Write Protection switch with 1 indicating write protected. It reports the status of the WP pin.

Bit 2 (CISWP) reflects whether the Common Memory CIS is write protected using the WRITE PROTECT REGISTER, with 1 indicating write protected.

Bit 3 (RP) reports whether the entire flash memory array is in "Deep-Sleep" (Reset-PwrDwn) mode, with 1 indicating "Deep-Sleep". This bit reflects the RP bit of the GLOBAL RESET-POWERDOWN REGISTER. Powering down *all* device pairs individually (using the Sleep Control Register), also sets this bit.

Bit 4 (CMWP) reports whether the Common Memory Plane (minus Common Memory CIS) is write protected via the WRITE PROTECT REGISTER with 1 indicating write protected.

Bit 5 (SRESET) reflects the SRESET bit of the SOFT RESET REGISTER. It reports that the card is in Soft

Reset with 1 indicating reset. When this bit is zero, the flash memory array and CMRs may be accessed, otherwise clear it via the SRESET REGISTER

Bit 6 (ADS, ANY DEVICE SLEEP) is the "ORed" value of the SLEEP CONTROL REGISTER. Powering down any device pair sets this bit.

Bit 7 (ADM, ANY DEVICE MASKED) is the "ORed" value of the READY/BUSY MASK REGISTER. Masking any device sets this bit.

# WRITE PROTECTION REGISTER (INTEL)

The WRITE PROTECTION REGISTER (Attribute Memory Plane Address 4104H, Figure 8) selects whether the optional Common Memory CIS and the remaining Common Memory blocks are write protected (see Figure 4).

Enable Common Memory CIS write protection by writing a 1 to the CISWP Bit (bit 0).

Enable write protection of the remaining Common Memory blocks by writing a 1 to the CMWP Bit (bit 1).

In the power-on default state, both bits are 0, and therefore not write protected.

Reserved bits (2-7) have undefined values and should be written as zeroes for future compatibility.

#### WRITE PROTECTION REGISTER (Read/Write Register) ADDRESS BIT 1 BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 0 4104H RESERVED FOR FUTURE USE CMWP CISWP 1 = WRITE PROTECT

Figure 8. WRITE PROTECTION REGISTER (Intel) Eliminates Accidental Data Corruption

# **SLEEP CONTROL REGISTER (INTEL)**

Unlike the GLOBAL RESET-POWERDOWN REGISTER, which simultaneously resets and places all flash memory devices into a Deep-Sleep mode, the SLEEP CONTROL REGISTER (Attribute Memory Plane Address 4118H–411AH, Figure 9) allows selective power-down control of individual device pairs.

Writing a 1 to a specific bit of the SLEEP CONTROL REGISTER places the corresponding device pair into the "Deep-Sleep" mode. *Devices in Deep-Sleep are not accessible*. On cards with fewer than 20 Megabytes (10 device pairs), writing a one to an absent device pair has no affect and reads back as zero.

This register contains all zeroes (i.e., not in Deep-Sleep mode) when the card powers up or after a hard or soft reset. Furthermore, the Global Reset-PowerDown Register has no affect on the contents of this register. Therefore, any bit settings of the

Sleep Control Register will remain unchanged after returning from a global reset and power down (writing a zero to the RP bit of the Global Reset-Power-Down Register).

# READY-BUSY STATUS REGISTER (INTEL)

The bits in the Read-only, READY-BUSY Status Register (Attribute Memory Plane Address 4130H-4134H, Figure 10) reflect the status (READY=1, BUSY=0) of each device's RY/BY# output. A busy condition indicates that a device is currently processing a data-write or block-erase operation.

These bits are logically "AND-ed" to form the Ready/Busy output (RDY/BSY#, pin 16) of the PCMCIA interface. On memory cards with fewer than 20 devices, unused Device RY/BY# Status Register bits appear as ready.

# SLEEP CONTROL REGISTER

(Read/Write Register)

| ADDRESS | BIT 7            | BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 |                  |                  |                  |                |                |                |  |

|---------|------------------|-------------------------------------|------------------|------------------|------------------|----------------|----------------|----------------|--|

| 411AH   |                  |                                     |                  | DEVICES<br>18/19 | DEVICES<br>16/17 |                |                |                |  |

| 4118H   | DEVICES<br>14/15 | DEVICES<br>12/13                    | DEVICES<br>10/11 | DEVICES<br>8/9   | DEVICES<br>6/7   | DEVICES<br>4/5 | DEVICES<br>2/3 | DEVICES<br>0/1 |  |

### 1 = SELECTED DEVICE PAIR IN POWER-DOWN MODE AND RESET

Figure 9. SLEEP CONTROL REGISTER (Intel) Allows Specific Devices to be Reset and Put into Power-Down Mode

## **READY-BUSY STATUS REGISTER**

(Read/Write Register)

| ADDRESS | BIT 7  | BIT 6 BIT |        | BIT 7 BIT 6 BIT 5 BIT |              | BIT 4        | BIT 3        | BIT 2        | BIT 1 | BIT 0 |

|---------|--------|-----------|--------|-----------------------|--------------|--------------|--------------|--------------|-------|-------|

| 4134H   |        | RESE      | RVED   |                       | DEVICE<br>19 | DEVICE<br>18 | DEVICE<br>17 | DEVICE<br>16 |       |       |

| 4132H   | DEVICE | DEVICE    | DEVICE | DEVICE                | DEVICE       | DEVICE       | DEVICE       | DEVICE       |       |       |

|         | 15     | 14        | 13     | 12                    | 11           | 10           | 9            | 8            |       |       |

| 4130H   |        | DEVICE    | DEVICE | DEVICE                | DEVICE       | DEVICE       | DEVICE       |              |       |       |

|         |        | 5         | 4      | 3                     | 2            | 1            | 0            |              |       |       |

1 = DEVICE READY, 0 = DEVICE BUSY

Figure 10. READY-BUSY STATUS REGISTER (Intel) Provides

Operation Status of All Flash Memory Devices

# READY-BUSY MASK REGISTER (INTEL)

The bits of the Read/Write READY-BUSY MASK REGISTER (Attribute Memory Plane Address 4120H-4124H, Figure 11) mask out the corresponding "AND-ed" READY-BUSY STATUS REGISTER bits from the PCMCIA data bus (RDY/BSY#, pin 16) and the CARD STATUS REGISTER RDY/BSY# Bit (bit 0).

In an unmasked condition (MASK REGISTER bits = 0), any device RY/BY# output going low pulls the card's RDY/BSY# output to V<sub>IL</sub> (BUSY). In this case, all devices must be READY to allow the card's RDY/BSY# output to be ready (V<sub>IH</sub>). This is referred to as the PCMCIA READY-BUSY MODE. An alternate type of READY-BUSY function is described in the next section, READY-BUSY MODE REGISTER.

## **READY-BUSY MASK**

(Read/Write Register)

| ADDRESS               | BIT 7  | BIT 6  | BIT 5  | BIT 4  | BIT 3        | BIT 2        | BIT 1        | BIT 0        |

|-----------------------|--------|--------|--------|--------|--------------|--------------|--------------|--------------|

| 4124H                 |        | RESE   | RVED   |        | DEVICE<br>19 | DEVICE<br>18 | DEVICE<br>17 | DEVICE<br>16 |

| 4122H                 | DEVICE | DEVICE | DEVICE | DEVICE | DEVICE       | DEVICE       | DEVICE       | DEVICE       |

|                       | 15     | 14     | 13     | 12     | 11           | 10           | 9            | 8            |

| 4120H DEVICE DEVICE C |        | DEVICE | DEVICE | DEVICE | DEVICE       | DEVICE       | DEVICE       |              |

|                       |        | 5      | 4      | 3      | 2            | 1            | 0            |              |

1 = MASK ENABLED

Figure 11. READY-BUSY MASK REGISTER (Intel) Essential for Write Optimization

# intel®

#### **SERIES 2 FLASH MEMORY CARDS**

If the READY-BUSY MASK REGISTER bits are set to ones (masked condition), the RDY/BSY# output and the CARD STATUS REGISTER RDY/BSY# bit will reflect a READY condition regardless of the state of the corresponding devices. The READY-BUSY MASK REGISTER does not affect the READY-BUSY STATUS REGISTER allowing software polling to determine operation status.

Unmasked is the default condition for the bits in this register. On memory cards with fewer than 20 devices, unused device mask bits appear as masked.

# READY-BUSY MODE REGISTER (INTEL)

The READY-BUSY MODE REGISTER (Attribute Memory Plane Address 4140H, Figure 12) provides the selection of two types of system interfacing for the busy-to-ready transition of the card's RDY/BSY# pin:

- The standard PCMCIA READY-BUSY MODE, in which the card's RDY/BSY# signal generates a low-to-high transition (from busy to ready) only after all busy devices (not including masked devices) have completed their data-write or blockerase operations. This may result in a long interrupt latency.

- A High-Performance mode that generates a lowto-high (from busy-to-ready) transition after each device becomes ready. This provides the host

system with immediate notification that a specific device's operation has completed and that device may now be used. This is particularly useful in a file management application where a block pair, containing only deleted files, is being erased to free up space so new file data may be written.

Enabling the HIGH-PERFORMANCE READY-BUSY MODE requires a three step sequence:

- Set all bits in the READY/BUSY MASK REGIS-TER. This prevents ready devices from triggering an unwanted interrupt when step 3 is performed.

- Write 01H to the READY-BUSY MODE REGIS-TER. This sets the MODE bit.

- Write 01H to the READY-BUSY MODE REGIS-TER. This clears the RACK bit.

The MODE and RACK bits *must* be written in the prescribed sequence, *not* simultaneously. The card's circuitry is designed purposely in this manner to prevent an initial, unwanted busy-to-ready transition. Note that in Step 2, writing to the RACK bit is a Don't Care.

When the High-Performance Mode is enabled, specific READY-BUSY MASK bits must be cleared after an operation is initiated on the respective devices. After each device becomes ready, the RDY/BSY# pin makes a low-to-high transition. To catch the next device's completion of an operation, the RACK bit must be cleared by writing "01H" to the Ready/Busy Mode Register.

# **READY-BUSY MODE REGISTER**

(Read/Write Register)

| ADDRESS | BIT 7 | BIT 6 | BIT 5      | BIT 4       | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---------|-------|-------|------------|-------------|-------|-------|-------|-------|

| 4140H   |       | R     | ESERVED FO | R FUTURE US | SE    |       | RACK  | MODE  |

MODE = READY-BUSY MODE 0 = PCMCIA MODE 1 = HIGH PERFORMANCE

RACK = READY ACKNOWLEDGE CLEAR TO SET UP RDY/BSY# PIN, THEN CLEAR AFTER EACH DEVICE BECOMES READY TO ACKNOWL-EDGE TRANSITION.

Figure 12. High Performance Ready-Busy Mode REGISTER (Intel)

Used to Trigger a Ready Interrupt for Each Device

#### PRINCIPLES OF DEVICE OPERATION

Individual 28F008SA devices include a Command User Interface (CUI) and a Write State Machine (WSM) to manage write and erase functions in each device block.

The CUI serves as the device's interface to the Card Control Logic by directing commands to the appropriate device circuitry (Table 4). It allows for fixed power supplies during block erasure and data writes. The CUI handles the WE# interface into the device data and address latches, as well as system software requests for status while the WSM is operating.

The CUI itself does not occupy an addressable memory location. The CUI provides a latch used to store the command and address and data information needed to execute the command. Erase Setup and Erase Confirm commands require both appropriate command data and an address within the block to be erased. The Data Write Setup command requires both appropriate command data and the address of the location to be written, while the Data Write command consists of the data to be written and the address of the location to be written.

The CUI initiates flash memory writing and erasing operations only when VPP is at 12V. Depending on the application, the system designer may choose to make the V<sub>PP</sub> power supply switchable (available when writes and erases are required) or hardwired to  $V_{PPH}$ . When  $V_{PP} = V_{PPI}$ , power savings are incurred and memory contents cannot be altered. The CUI architecture provides protection from unwanted write and erase operations even when high voltage is applied to VPP. Additionally, all functions are disabled whenever V<sub>CC</sub> is below the write lockout voltage V<sub>LKO</sub>, or when the card's Deep-Sleep modes are enabled. The WSM automates the writing and erasure of blocks within a device. This on-chip state machine controls block erase and data-write, freeing the host processor for other tasks. After receiving the Erase Setup and Erase Confirm commands from the CUI, the WSM controls block-erase. Progress is monitored via the device's status register, the card's control logic, and the RDY/BSY# pin of the PCMCIA interface. Data-write is similarly controlled, after destination address and expected data are supplied.

**Table 4. Device Command Set**

|                                 | Bus             |           | First B             | us Ccyle |          | Second Bus Cycle |          |         |          |  |  |

|---------------------------------|-----------------|-----------|---------------------|----------|----------|------------------|----------|---------|----------|--|--|

| 28F008SA Command <sup>(1)</sup> | Cycles<br>Req'd | Operation | Addr <sup>(2)</sup> | D        | ata      | Operation        | V 44*(5) | Data    |          |  |  |

|                                 |                 | Operation |                     | x8 Mode  | x16 Mode |                  | Auui (-) | x8 Mode | x16 Mode |  |  |

| Read Array/Reset                | 1               | Write     | DA                  | FFH      | FFFFH    |                  |          |         |          |  |  |

| Intelligent Identifer           | 3               | Write     | DA                  | 90H      | 9090H    | Read             | IA       | IID(3)  | IID(3)   |  |  |

| Read Device Status Register     | 2               | Write     | DA                  | 70H      | 7070H    | Read             | DA       | SRD(4)  | SRD(4)   |  |  |

| Clear Device Status Register    | 1               | Write     | DA                  | 50H      | 5050H    |                  |          |         |          |  |  |

| Erase Setup/Erase Confirm       | 2               | Write     | ВА                  | 20H      | 2020H    | Write            | ВА       | D0H     | D0D0H    |  |  |

| Erase Suspend/<br>Erase Resume  | 2               | Write     | DA                  | вон      | Вовон    | Write            | DA       | D0H     | D0D0H    |  |  |

| Write Setup/Write               | 2               | Write     | WA                  | 40H      | 4040H    | Write            | WA       | WD(5)   | WD(5)    |  |  |

| Alternate Write Setup/Write(6)  | 2               | Write     | WA                  | 10H      | 1010H    | Write            | WA       | WD(5)   | WD(5)    |  |  |

# NOTES:

- Commands other than those shown above are reserved by Intel for future device implementations and should not be used.

- 2. DA = A device-level (or device pair) address within the card.

- BA = Address within the block of a specific device (device pair) being erased.

- WA = Address of memory location to be written.

- IA = A device-level address; 00H for manufacturer code, 01 for device code.

- 3. Following the intelligent identifier command, two read operations access manufacturer (89H) and device codes (A2H).

- 4. SRD = Data read from Device Status Register.

- 5. WD = Data to be written at location WA. Data is latched on the rising edge of WE#.

- 6. Either 40H or 10H are recognized by the WSM as the Write Setup command.

#### **COMMAND DEFINITIONS**

# Read Array (FFH) —

Upon initial card power-up, after exit from the Deep-Sleep modes, and whenever illegal commands are given, individual devices default to the Read Array mode. This mode is also entered by writing FFH into the CUI. In this mode, microprocessor read cycles retrieve array data. Devices remain enabled for reads until the CUI receives an alternate command. Once the internal WSM has started a block-erase or data-write operation within a device, that device will not recognize the Read Array command until the WSM has completed its operation (or the Erase Suspend command is issued during erase).

# Intelligent Identifier (90H) —

After executing this command, the intelligent identifier values can be read. Only address  $A_0$  of each device is used in this mode, all other address inputs are reserved and should be cleared to 0. [[Manufacturer code = 89H for  $A_0=0$ ), (Device code = A2H for  $A_0=1$ )]. The device will remain in this mode until the CUI receives another command.

This information is useful by system software in determining what type of flash memory device is contained within the card and allows the correct matching of device to write and erase algorithms. System software that fully uitilizes the PCMCIA specification will not use the intelligent identifier mode, as this data is available within the Card Information Structure (refer to section on PCMCIA Card Information Structure).

# Read Status Register (70H)

After writing this command, a device read outputs the contents of its Status Register, regardless of the address presented to that device. The contents of this register are latched on the falling edge of OE#, CE\_1# (and/or CE\_2#), whichever occurs last in the read cycle. This prevents possible bus errors which might occur if the contents of the Status Register changed while reading its contents. CE\_1# (and CE\_2# for odd-byte or word access) or OE# must be toggled with each subsequent status read, or the completion of a write or erase operation will not be evident. This command is executable while the WSM is operating, however, during a block-erase or data-write operation, reads from the device will auto-

matically return status register data. Upon completion of that operation, the device remains in the Status Register read mode until the CUI receives another command.

The read Status Register command functions when  $V_{PP} = V_{PPL}$  or  $V_{PPH}$ .

# Clear Status Register (50H)

The Erase Status and Write Status bits may be set to "1"s by the WSM and can only be reset by the Clear Status Register Command. These bits indicate various failure conditions. By allowing system software to control the resetting of these bits, several operations may be performed (such as cumulatively writing several bytes or erasing multiple blocks in sequence). The device's Status Register may then be polled to determine if an error occurred during that sequence. This adds flexibility to the way the device may be used.

Additionally, the  $V_{PP}$  Status bit (SR.3) MUST be reset by system software (Clear Status Register command) before further block-erases are attempted (after an error).

The Clear Status Register command functions when  $V_{PP} = V_{PPL}$  or  $V_{PPH}$ . This command puts the device in the Read Array mode.

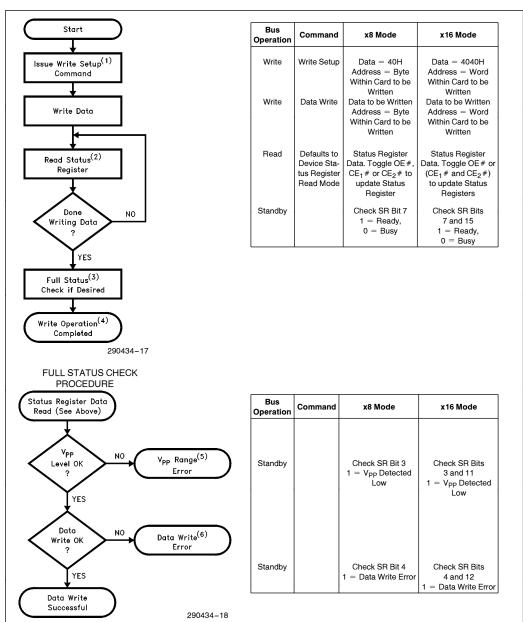

## Write Setup/Write

A two-command sequence executes a data-write operation. After the system switches VPP to VPPH, the write setup command (40H) is written to the CUI of the appropriate device, followed by a second write specifying the address and write data (latched on the rising edge of WE#). The device's WSM controls the data-write and write verify algorithms internally. After receiving the two-command write sequence, the device automatically outputs Status Register data when read (see Figure 13). The CPU detects the completion of the write operation by analvzing card-level or device-level indicators. Cardlevel indicators include the RDY/BSY# pin and the READY-BUSY STATUS REGISTER; while devicelevel indicators include the specific device's Status Register. Only the Read Status Register command is valid while the write operation is active. Upon completion of the data-write sequence (see section on Status Register) the device's Status Register reflects the result of the write operation. The device remains in the Read Status Register mode until the CUI receives an alternate command.

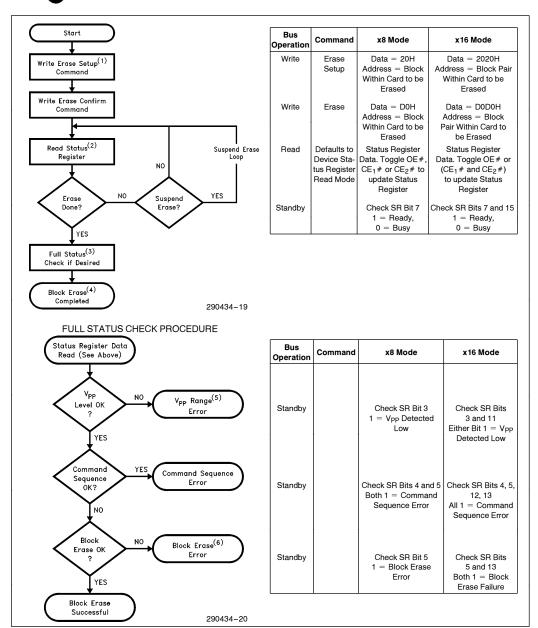

# Erase Setup/Erase Confirm Commands (20H)

Within a device, a two-command sequence initiates an erase operation on one device block at a time. After the system switches V<sub>PP</sub> to V<sub>PPH</sub>, an Erase Setup command (20H) prepares the CUI for the Erase Confirm command (D0H). The device's WSM controls the erase algorithms internally. After receiving the two-command erase sequence, the device automatically outputs Status Register data when read (see Figure 14). If the command after erase setup is not an Erase Confirm command, the CR sets the Write Failure and Erase Failure bits of the Status Register, places the device into the Read Status Register mode, and waits for another command. The Erase Confirm command enables the WSM for erase (simultaneously closing the address latches for that device's block (A<sub>16</sub>-A<sub>19</sub>). The CPU detects the completion of the erase operation by analyzing card-level or device-level indicators. Cardlevel indicators include the RDY/BSY pin and the READY-BUSY STATUS REGISTER; while devicelevel indicators include the specific device's Status Register. Only the Read Status Register and Erase Suspend command is valid during an active erase operation. Upon completion of the erase sequence (see section on Status Register) the device's Status Register reflects the result of the erase operation. The device remains in the Read Status Register mode until the CUI receives an alternate command.

The two-step block-erase sequence ensures that memory contents are not accidentally erased. Erase attempts while  $V_{PPL} < V_{PP} < V_{PPH}$  produce spurious results and are not recommended. Reliable block erasure only occurs when  $V_{PP} = V_{PPH}$ . In the absence of this voltage, memory contents are protected against erasure. If block erase is attempted while  $V_{PP} = V_{PPL}$ , the  $V_{PP}$  Status bit will be set to "1".

When erase completes, the Erase Status bit should be checked. If an erase error is detected, the device's Status Register should be cleared. The CUI remains in Read Status Register mode until receiving an alternate command.

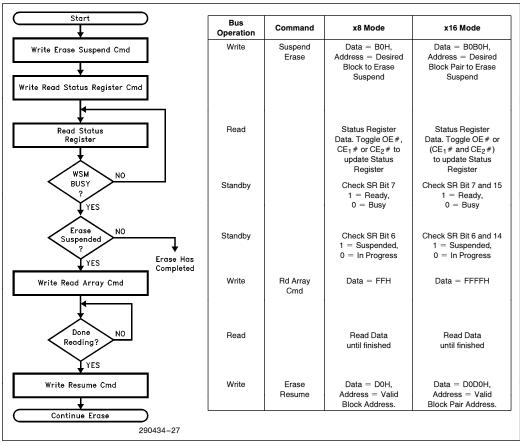

# Erase Suspend (B0H)/Erase Resume (D0H)

Erase Suspend allows block erase interruption to read data from another block of the device or to temporarily conserve power for another system operation. Once the erase process starts, writing the Erase Suspend command to the CUI (see Figure 15) requests the WSM to suspend the erase sequence at a predetermined point in the erase algorithm. In the erase suspend state, the device continues to output Status Register data when read.

Polling the device's RY/BY# and Erase Suspend Status bits (Status Register) will determine when the erase suspend mode is valid. It is important to note that the card's RDY/BSY# pin will also transition to VOH and will generate an interrupt if this pin is connected to a system-level interrupt. At this point, a Read Array command can be written to the device's CUI to read data from blocks other than those which are suspended. The only other valid commands at this time are Read Status Register (70H) and Erase Resume (D0H). If Vpp goes low during Erase Suspend, the Vpp Status bit is set in the Status Register and the erase operation is aborted.

The Erase Resume command clears the Erase Suspend state and allows the WSM to continue with the erase operation. The device's RY/BY # Status and Erase Suspend Status bits and the card's READY-BUSY Status Register are automatically updated to reflect the erase resume condition. The card's RDY/BSY # pin also returns to  $V_{OL}$ .

### Invalid/Reserved

These are unassigned commands having the same effect as the Read Array command. Do not issue any command other than the valid commands specified above. Intel reserves the right to redefine these codes for future functions.

### **DEVICE STATUS REGISTER**

Each 28F008SA device in the Series 2 Card contains a Status Register which displays the condition of its Write State Machine. The Status Register is read at any time by writing the Read Status command to the CUI. After writing this command, all subsequent Read operations output data from the Status Register, until another command is written to the CUI.

### Bit 7—WSM Status

This bit reflects the Ready/Busy condition of the WSM. A "1" indicates that read, block-erase or data- write operations are available. A "0" indicates that write or erase operations are in progress.

### Bit 6—Erase Suspend Status

If an Erase Suspend command is issued during the erase operation, the WSM halts execution and sets the WSM Status bit and the Erase Suspend Status bit to a "1". This bit remains set until the device receives an Erase Resume command, at which point the CUI resets the WSM Status bit and the Erase Suspend Status bit.

#### Bit 5—Erase Status

This bit will be cleared to 0 to indicate a successful block-erasure. When set to a "1", the WSM has been unsuccessful at performing an erase verification. The device's CUI only resets this bit to a "0" in response to a Clear Status Register command.

#### Bit 4—Write Status

This bit will be cleared to a 0 to indicate a successful data-write operation. When the WSM fails to write data after receiving a write command, the bit is set to a "1" and can only be reset by the CUI in response to a Clear Status Register command.

# Bit 3-V<sub>PP</sub> Status

During block-erase and data-write operations, the WSM monitors the output of the device's internal Vpp detector. In the event of low Vpp, the WSM sets ("1") the Vpp Status bit, the status bit for the operation in progress (either write or erase). The CUI resets these bits in response to a Clear Status Register command. Also, the WSM RY/BY# bit will be set to indicate a device ready condition. This bit MUST be reset by system software (Clear Status Register command) before further data writes or block erases are attempted.

#### **Device Status Register (Read Only Register)**

| Bit 7         | Bit 6                      | Bit 5           | Bit 4           | Bit 3                     | Bit 2 | Bit 1    | Bit 0 |

|---------------|----------------------------|-----------------|-----------------|---------------------------|-------|----------|-------|

| WSM<br>Status | Erase<br>Suspend<br>Status | Erase<br>Status | Write<br>Status | V <sub>PP</sub><br>Status |       | Reserved |       |

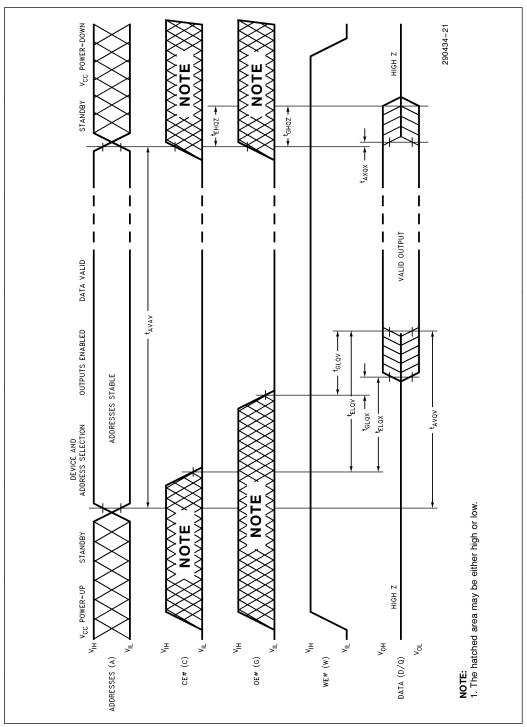

Figure 13. Device-Level Automated Write Algorithm

# NOTES:

- 1. Repeat for subsequent data writes.

- 2. In addition, the card's READY-BUSY STATUS REGISTER or the RDY/BSY# pin may be used.

- 3. Full device-level status check can be done after each data write or after a sequence of data writes.

- 4. Write FFH (or FFFFH) after the last data write operation to reset the device(s) to Read Array Mode.

- 5. If a data write operation fails due to a low  $V_{PP}$  (setting SR Bit 3), the Clear Status Register command MUST be issued before further attempts are allowed by the Write State Machine.

- 6. If a data write operation fails during a multiple write sequence, SR Bit 4 (Write Status) will not be cleared until the Command User Interface receives the Clear Status Register command.

# inta

#### **SERIES 2 FLASH MEMORY CARDS**

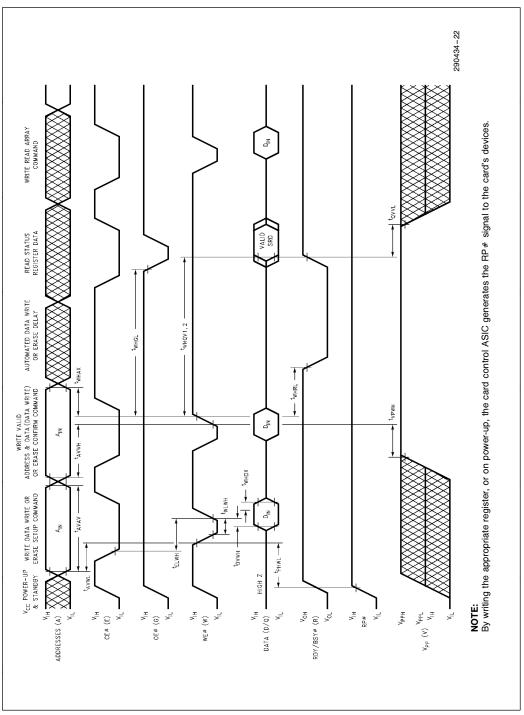

Figure 14. Device-Level Automated Erase Algorithm

#### NOTES:

- 1. Repeat for subsequent data writes.

- 2. In addition, the card's READY-BUSY STATUS REGISTER or the RDY/BSY# pin may be used.

- 3. Full device-level status check can be done after each block erase or after a sequence of block erases.

- 4. Write FFH (or FFFFH) after the last block erase operation to reset the device(s) to Ready Array Mode.

- 5. If a block erase operation fails due to a low V<sub>PP</sub> (setting SR Bit 3), the Clear Status Register command MUST be issued before further attempts are allowed by the Write State Machine.

- 6. If a block erase operation fails during a multiple block erase sequence, SR Bit 4 (Write Status) will not be cleared until the Command User Interface receives the Clear Status Register command.

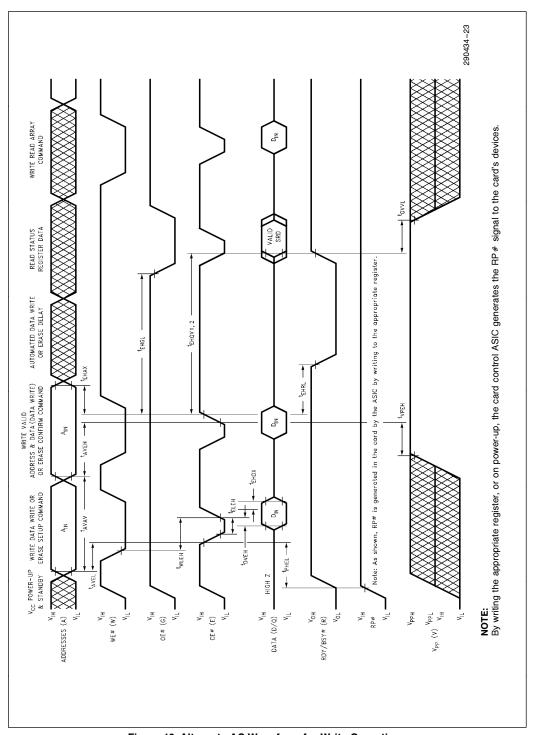

Figure 15. Erase Suspend/Resume Algorithm. Allows Reads to Interrupt Erases.

# **POWER CONSUMPTION**

### STANDBY MODE

In most applications, software will only be accessing one device pair at a time. The Series 2 Card is defined to be in the standby mode when one device pair is in the Read Array Mode while the remaining devices are in the Deep-Sleep Mode. The Series 2 Card's CE $_1\#$  and CE $_2\#$  input signals must also be at VIH. In standby mode, much of the card's circuitry is shut off, substantially reducing power consumption. Typical power consumption for a 20 Megabyte Series 2 card in standby mode is 65  $\mu A$ .

### SLEEP MODE

Writing a "1" to the PWRDWN bit of the GLOBAL POWERDOWN REGISTER places all FlashFile Memory devices into a Deep-Sleep mode. This disables most of the 28F008SA's circuitry and reduces current consumption to 0.2  $\mu$ A per device. Additionally, when the host system pulls ASIC control logic high and latches all address and data lines (i.e., not toggling), the card's total current draw is reduced to approximately 5  $\mu$ A (CMOS input levels) for a 20 Megabyte card. On writing a "0" to the PWRDWN bit (Global PowerDown Register) or any individual device pair (Sleep Control Register), a Deep-Sleep mode recovery period must be allowed for 28F008SA device circuitry to power back on.

# intel®

#### SERIES 2 FLASH MEMORY CARDS

#### SYSTEM DESIGN CONSIDERATIONS

#### **POWER SUPPLY DECOUPLING**

Flash memory power-switching characteristics require careful device decoupling. System designers are interested in three supply current issues—standby, active and transient current peaks, produced by rising and falling edges of CE<sub>1</sub># and CE<sub>2</sub>#. The capacitive and inductive loads on the card and internal flash memory device pairs determine the magnitudes of these peaks.

The Flash Memory Card features on-card ceramic decoupling capacitors connected between  $V_{CC}$  and GND, and between  $V_{PP1}/V_{PP2}$  and GND to help transient voltage peaks.

On the host side, the card connector should also have a 4.7  $\mu\text{F}$  electrolytic capacitor between V<sub>CC</sub> and GND, as well as between V<sub>PP1</sub>/V<sub>PP2</sub> and GND. The bulk capacitors will overcome voltage slumps caused by printed-circuit-board trace inductance, and will supply charge to the smaller capacitors as needed.

## **POWER UP/DOWN PROTECTION**

Each device in the Flash Memory Card is designed to offer protection against accidental erasure or writing, caused by spurious system-level signals that may exist during power transitions. The card will power-up into the Read Array Mode.

A system designer must guard against active writes for  $V_{CC}$  voltages above  $V_{LKO}$  when  $V_{PP}$  is active. Since both WE# and CE<sub>1</sub># (and/or CE<sub>2</sub>#) must be low for a command write, driving either to  $V_{IH}$  will inhibit writes. With its Command User Interface, alteration of device contents only occurs after successful completion of the two-step command sequences.

While these precautions are sufficient for most applications, an alternative approach would allow  $V_{CC}$  to reach its steady state value before raising  $V_{PP1}/V_{PP2}$  above  $V_{CC}\ +\ 2.0V.$  In addition, upon powering-down,  $V_{PP1}/V_{PP2}$  should be below  $V_{CC}\ +\ 2.0V,$  before lowering  $V_{CC}.$

#### HOT INSERTION/REMOVAL

The capability to remove or insert PC cards while the system is powered on (i.e., hot insertion/removal) requires careful design approaches on the system and card levels. To design for this capability consider card overvoltage stress, system power droop and control line stability.

A PCMCIA/JEIDA specified socket properly sequences the power supplies to the flash memory card via shorter and longer pins. This assures that hot insertion and removal will not result in card damage or data loss.

# PCMCIA CARD INFORMATION STRUCTURE

The Card Information Structure (CIS) starts at address zero of the card's Attribute Memory Plane. It contains a variable-length chain of data blocks (tuples) that conform to a basic format as shown in Table 5. This section describes each tuple contained within the Series 2 Flash Memory Card.

# **The Device Information Tuple**

This tuple (CISTPL\_DEV = 01H) contains information pertaining to the card's speed and size. The Series 2 Card is offered with a 150 nanosecond access time. Card sizes range between 2 and 20 Megabytes.

#### **Table 5. Tuple Format**

| Bytes | Data                                                                                                                                                                                                                                                                        |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | Tuple Code: CISTPL_xxx. The tuple code 0FFH indicates no more tuples in the list.                                                                                                                                                                                           |

| 1     | Tuple Link: TPLLINK. Link to the next tuple in the list. This can be viewed as the number of additional bytes in tuple, excluding this byte. If the link field is zero, the tuple body is empty. If the link field contains 0FFH, this tuple is the last tuple in the list. |

| 2-n   | Bytes specific to this tuple.                                                                                                                                                                                                                                               |

# **The Device Geometry Tuple**

This tuple (CISTPL\_DEVICEGEO = 1EH) is conceptually similar to a DOS disk geometry tuple (CISTPL\_GEOMETRY), except it is not a format-dependent property; this deals with the fixed architecture of the memory device(s).

Fields are defined as follows:

**DGTPL BUS**—Value = n, where system bus width =  $2^{(n-1)}$  bytes. N = 2 for standard PCMCIA Release 1.0/2.0 cards.

**DGTPL EBS.**—Value = n, where the memory array's physical memory segments have a minimum erase block size of  $2^{(n-1)}$  address increments of DGTPL\_BUS-wide accesses.

**DGTPL RBS**—Value = n, where the memory array's physical memory segments have a minimum read block size of  $2^{(n-1)}$  address increments of DGTPL\_BUS-wide accesses.

**DGTPL WBS**—Value = n, where the memory array's physical memory segments have a minimum write block size of  $2^{(n-1)}$  address increments of DGTPL\_BUS-wide accesses.

**DGTPL PART**—Value = n, where the memory array's physical memory segments can have partitions subdividing the arrays in minimum granularity of  $2^{(n-1)}$  number of erase blocks.

**FL DEVICE INTERLEAVE**—Value = n, where card architectures employ a multiple of  $2^{(n-1)}$  times interleaving of the entire memory arrays with the above characteristics. Non-interleaved cards have values n=1.

# Jedec Programming Information Tuple

This tuple (CISTPL\_\_JEDEC = 18H) contains the Intel manufacturing identifier (89H) and the 28F008SA device ID (A2H).

# Level 1 Version/Product Information Tuple

This tuple (CISTPL\_VERI = 15H) contains Level-1-version compliance and card-manufacturer information. Fields are described as follows:

**TPLLV1 MAJOR**—Major version number = 04H.

**TPLLV1 MINOR**—Minor version number = 01H for release 2.0.

#### TPLLV1 INFO-

Name of manufacturer = intel;

Name of product = SERIES2-"Card size";

Card type = 2;

Speed = 150 ns or 200 ns

Register Base = REGBASE 4000H

Test Codes = DBBDRELP

Legalities = COPYRIGHT intel

Corporation 1991

## The Configurable Card Tuple

This tuple (CISTPL\_\_CONF = 1AH) describes the interface supported by the card and the locations of the Card Configuration Registers and the Card Configuration Table.

Fields are described as follows:

**TPCC SZ**—Size of fields byte = 01H.

**TPCC LAST**—Index number of the last entry in the Card Configuration Table = 00H.

**TPCC RADR**—Configuration Registers Base Address in Reg Space = 4000H.

**TPCC RMSK**—Configuration Registers Present Mask = 03H.

## The End-Of-List Tuple

The end-of-list tuple (CISTPL\_END = FFH) marks the end of a tuple chain. Upon encountering this tuple, continue tuple processing as if a long-link to address 0 of common memory space were encountered.

| Tuple<br>Address | Value                    | Description                                           |

|------------------|--------------------------|-------------------------------------------------------|

| 00H              | 01H                      | CISTPL_DEV                                            |

| 02H              | 03H                      | TPL_LINK                                              |

| 04H              | 53H<br>52H               | DEVICE_INFO = FLASH 150 ns DEVICE_INFO = FLASH 200 ns |

| 06Н              | 06H<br>0EH<br>26H<br>4EH | CARD SIZE<br>2M<br>4M<br>10M<br>20M                   |

| 08H              | FFH                      | END OF<br>DEVICE                                      |

| 0AH              | 1EH                      | CISTPL<br>DEVICEGEO                                   |

| 0CH              | 06H                      | TPL_LINK                                              |

| 0EH              | 02H                      | DGTPL_BUS                                             |

| 10H              | 11H                      | DGTPL_EBS                                             |

| 12H              | 01H                      | DGTPL_RBS                                             |

| 14H              | 01H                      | DGPL_WBS                                              |

| 16H              | 03H                      | DGTPL_PART                                            |

| 18H              | 01H                      | FL_DEVICE<br>INTERLEAVE                               |

| 1AH              | 18H                      | CISTPL_JEDEC                                          |

| 1CH              | 02H                      | TPL_LINK                                              |

| 1EH              | 89H                      | INTEL J-ID                                            |

| 20H              | A2H                      | 28F008 J-ID                                           |

| 22H              | 15H                      | CISTPL_VER1                                           |

| 24H              | 50H                      | TPL_LINK                                              |

| 26H              | 04H                      | TPLLV1<br>MAJOR                                       |

| 28H              | 01H                      | TPLLV1<br>MINOR                                       |

| 2AH              | 69H                      | TPLLV1 INFO<br>i                                      |

| 2CH              | 6EH                      | n                                                     |

| 2EH              | 74H                      | t                                                     |