# V048F060T040 V048F060M040 Rohs

## VTM<sup>™</sup> Current Multiplier

- 48 V to 6 V V•I Chip<sup>™</sup> Converter

- 40 A (60.0 A for 1 ms)

- High density 813 W/in<sup>3</sup>

- Small footprint 210 W/in<sup>2</sup>

- Low weight 0.5 oz (15 g)

- Pick & Place / SMD or Through hole

- 125°C operation (T<sub>J</sub>)

- 1 µs transient response

- 3.5 million hours MTBF

- Typical efficiency 95%

- . No output filtering required

Vf = 26 - 55 V  $V_{OUT} = 3.25 - 6.87 V$   $I_{OUT} = 40 A$  K = 1/8 $R_{OUT} = 7.09 mΩ max$

## **Product Description**

The V048F060T040 V•I Chip Voltage Transformation Module excels at speed, density and efficiency to meet the demands of advanced power applications while providing isolation from input to output. It achieves a response time of less than 1 µs and delivers up to 40 A in a volume of less than 0.295 in<sup>3</sup> with unprecedented efficiency. It may be paralleled to deliver higher power levels at an output voltage settable from 3.25 to 6.87 Vdc.

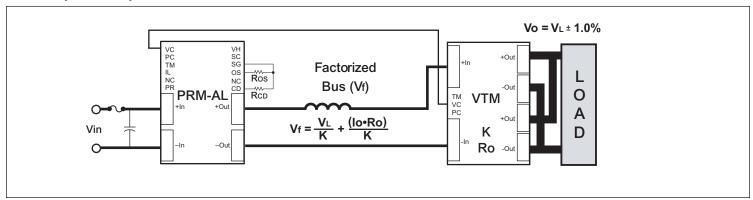

The VTM V048F060T040's nominal output voltage is 6 Vdc from a 48 Vdc input Factorized Bus, Vf, and is controllable from 3.25 to 6.87 Vdc at no load, and from 2.97 to 6.61 Vdc at full load, over a Vf input range of 26 to 55 Vdc. It can be operated either open- or closed-loop depending on the output regulation needs of the application. Operating open-loop, the output voltage tracks its Vf input voltage with a transformation ratio, K = 1/8, for applications requiring an isolated output voltage with high efficiency. Closing the loop back to an input PRM<sup>TM</sup> regulator or DC-DC converter enables tight load regulation.

The 6 V VTM achieves a power density of 813 W/in<sup>3</sup> in a V•I Chip package compatible with standard pick-and-place and surface mount assembly processes. The VTM's fast dynamic response and low noise eliminate the need for bulk capacitance at the load, substantially increasing system density while improving reliability and decreasing cost.

## **Absolute Maximum Ratings**

| Parameter                           | Values       | Unit | Notes               |

|-------------------------------------|--------------|------|---------------------|

| +In to -In                          | -1.0 to 60   | Vdc  |                     |

| +In to -In                          | 100          | Vdc  | For 100 ms          |

| PC to -In                           | -0.3 to 7.0  | Vdc  |                     |

| VC to -In                           | -0.3 to 19.0 | Vdc  |                     |

| +Out to -Out                        | -0.5 to 12   | Vdc  |                     |

| Isolation voltage                   | 2,250        | Vdc  | Input to output     |

| Output current                      | 40           | А    | Continuous          |

| Peak output current                 | 60.0         | А    | For 1 ms            |

| Output power                        | 264          | W    | Continuous          |

| Peak output power                   | 397          | W    | For 1 ms            |

| Case temperature                    | 225          | °C   | During reflow MSL 5 |

| Operating in action temperature (1) | -40 to 125   | °C   | T-Grade             |

| Operating junction temperature (1)  | -55 to 125   | °C   | M-Grade             |

| Storage temperature                 | -40 to 125   | °C   | T-Grade             |

| Storage temperature                 | -65 to 125   | °C   | M-Grade             |

#### Note:

(1) The referenced junction is defined as the semiconductor having the highest temperature. This temperature is monitored by a shutdown comparator.

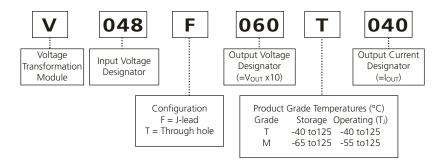

#### **Part Numbering**

vicorpower.com 800-735-6200

V•I Chip Voltage Transformation Module

V048F060T040

## **Input Specs** (Conditions are at 48 Vin, full load, and 25°C ambient unless otherwise specified)

| Parameter                      | Min  | Тур | Max  | Unit   | Note                                          |

|--------------------------------|------|-----|------|--------|-----------------------------------------------|

| Input voltage range            | 26   | 48  | 55   | Vdc    | Max Vin = 53 V, operating from -55°C to -40°C |

| Input dV/dt                    |      |     | 1    | V/µs   |                                               |

| Input overvoltage turn-on      | 55.0 |     |      | Vdc    |                                               |

| Input overvoltage turn-off     |      |     | 59.3 | Vdc    |                                               |

| Input current                  |      |     | 5.5  | Adc    |                                               |

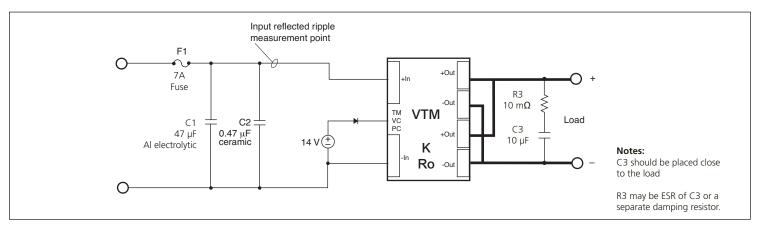

| Input reflected ripple current |      | 275 |      | mA p-p | Using test circuit in Figure 15; See Figure 1 |

| No load power dissipation      |      | 2.7 | 3.50 | W      |                                               |

| Internal input capacitance     |      | 1.9 |      | μF     |                                               |

| Internal input inductance      |      |     | 5    | nΗ     |                                               |

## Output Specs (Conditions are at 48 Vin, full load, and 25°C ambient unless otherwise specified)

| Parameter                          | Min    | Тур  | Max    | Unit               | Note                                                                  |

|------------------------------------|--------|------|--------|--------------------|-----------------------------------------------------------------------|

| Output voltage                     | 3.25   |      | 6.87   | Vdc                | No load                                                               |

| Output voltage<br>                 | 2.97   |      | 6.61   | 5.61 Vdc           | Full load                                                             |

| Rated DC current                   | 0      |      | 40     | Adc                | 26 - 55 V <sub>IN</sub>                                               |

| Peak repetitive current            |        |      | 60.0   | А                  | Max pulse width 1ms, max duty cycle 10%,                              |

|                                    |        |      |        | baseline power 50% |                                                                       |

| Short circuit protection set point | 47.4   |      |        | Adc                | Module will shut down                                                 |

| Current share accuracy             |        | 5    | 10     | %                  | See Parallel Operation on Page 9                                      |

| Efficiency                         |        |      |        |                    |                                                                       |

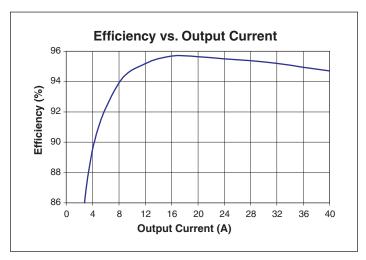

| Half load                          | 94.8   | 95.6 |        | %                  | See Figure 3                                                          |

| Full load                          | 94.0   | 94.6 |        | %                  | See Figure 3                                                          |

| Internal output inductance         |        | 1.1  |        | nH                 |                                                                       |

| Internal output capacitance        |        | 35.6 |        | μF                 | Effective value                                                       |

| Output overvoltage setpoint        | 6.9    |      |        | Vdc                | Module will shut down                                                 |

| Output ripple voltage              |        |      |        |                    |                                                                       |

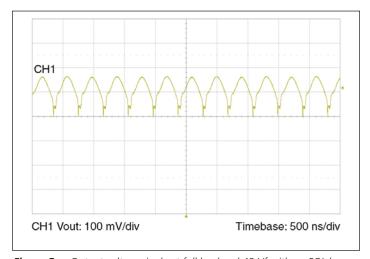

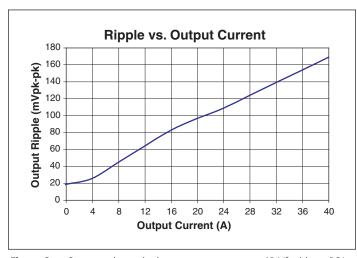

| No external bypass                 |        | 145  | 275    | mVp-p              | See Figures 2 and 5                                                   |

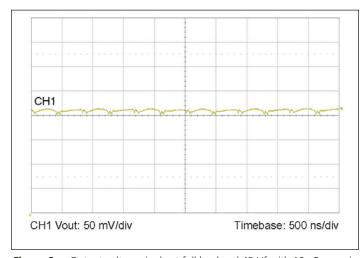

| 10 μF bypass capacitor             |        | 13   |        | mVp-p              | See Figure 6                                                          |

| Effective switching frequency      | 2.1    | 2.5  | 3.1    | MHz                | Fixed, 1.3 MHz per phase                                              |

| Line regulation                    |        |      |        |                    |                                                                       |

| K                                  | 0.1238 | 1/8  | 0.1263 |                    | V <sub>OUT</sub> = K•V <sub>IN</sub> at no load                       |

| Load regulation                    |        |      |        |                    |                                                                       |

| R <sub>OUT</sub>                   |        | 6.0  | 7.09   | mΩ                 | See Figure 16                                                         |

| Transient response                 |        |      |        |                    |                                                                       |

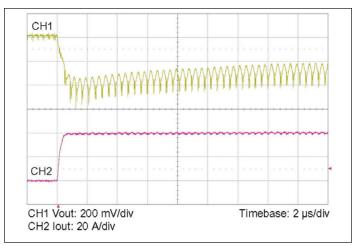

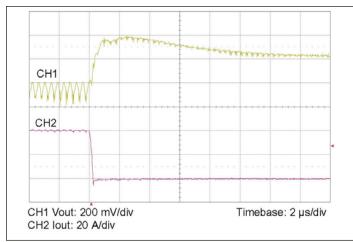

| Voltage overshoot                  |        | 180  |        | mV                 | 40 A load step with 100 $\mu$ F C <sub>IN</sub> ; See Figures 7 and 8 |

| Response time                      |        | 200  |        | ns                 | See Figures 7 and 8                                                   |

| Recovery time                      |        | 1    |        | μs                 | See Figures 7 and 8                                                   |

V•I Chip Voltage Transformation Module 800-735-6200

V048F060T040

## **Electrical Specifications** (continued)

#### **Waveforms**

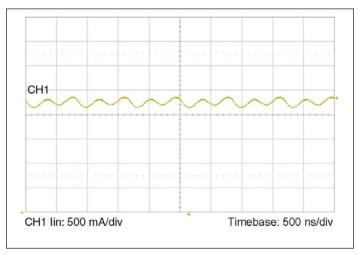

Figure 1 — Input reflected ripple current at full load and 48 Vf.

Figure 3 — Efficiency vs. output current.

Figure 5 — Output voltage ripple at full load and 48 Vf with no POL bypass capacitance.

Figure 2 — Output voltage ripple vs. output current at 48 Vf with no POL bypass capacitance.

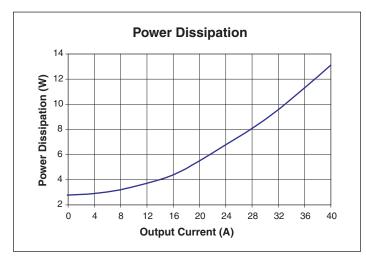

Figure 4 — Power dissipation vs. output current.

**Figure 6** — Output voltage ripple at full load and 48 Vf with 10  $\mu$ F ceramic POL bypass capacitance and 20 nH distribution inductance.

800-735-6200

Figure 7 — 0-40 A load step with 100 μF input capacitance and no output capacitance.

**Figure 8** — 40-0 A load step with 100  $\mu$ F input capacitance and no output capacitance.

#### General

| Parameter                                               | Min   | Тур        | Max | Unit  | Note                                     |

|---------------------------------------------------------|-------|------------|-----|-------|------------------------------------------|

| MTBF                                                    |       |            |     |       |                                          |

| MIL-HDBK-217F                                           |       | 3.5        |     | Mhrs  | 25°C, GB                                 |

| Isolation specifications                                |       |            |     |       |                                          |

| Voltage                                                 | 2,250 |            |     | Vdc   | Input to output                          |

| Capacitance                                             |       | 3,000      |     | pF    | Input to output                          |

| Resistance                                              | 10    |            |     | МΩ    | Input to output                          |

|                                                         |       | cTÜVus     |     |       | UL/CSA 60950-1, EN 60950-1               |

| Agency approvals                                        |       | CE Mark    |     |       | Low voltage directive                    |

|                                                         |       | RoHS       |     |       |                                          |

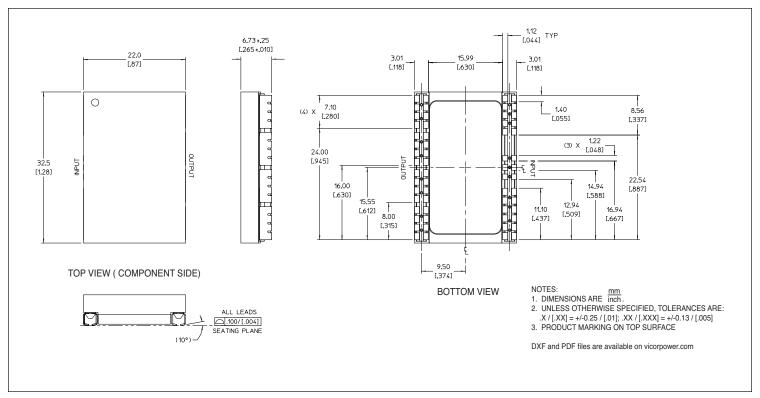

| Mechanical                                              |       |            |     |       | See Mechanical Drawings, Figures 10 – 13 |

| Weight                                                  |       | 0.53/15    |     | oz/g  |                                          |

| Dimensions                                              |       |            |     |       |                                          |

| Length                                                  |       | 1.28/32,5  |     | in/mm |                                          |

| Width                                                   |       | 0.87/22    |     | in/mm |                                          |

| Height                                                  |       | 0.265/6,73 |     | in/mm |                                          |

| Peak compressive force applied to case (Z axis)         |       | 5          | 6   | lbs.  | Supported by J-leads only                |

| Thermal                                                 |       |            |     |       |                                          |

| Over temperature shutdown                               | 125   | 130        | 135 | °C    | Junction temperature                     |

| Thermal capacity                                        |       | 9.3        |     | Ws/°C |                                          |

| Junction-to-case thermal impedance (R <sub>0JC</sub> )  |       | 1.1        |     | °C/W  |                                          |

| Junction-to-board thermal impedance (R <sub>0JB</sub> ) |       | 2.1        |     | °C/W  |                                          |

## **Auxiliary Pins** (Conditions are at 48 Vin, full load, and 25°C ambient unless otherwise specified)

| Parameter               | Min | Тур | Max | Unit | Note                                                       |

|-------------------------|-----|-----|-----|------|------------------------------------------------------------|

| Primary Control (PC)    |     |     |     |      |                                                            |

| DC voltage              | 4.8 | 5.0 | 5.2 | Vdc  |                                                            |

| Module disable voltage  | 2.4 | 2.5 |     | Vdc  |                                                            |

| Module enable voltage   |     | 2.5 | 2.6 | Vdc  | VC voltage must be applied when module is enabled using PC |

| Current limit           | 2.4 | 2.5 | 2.9 | mA   | Source only                                                |

| Disable delay time      |     | 10  |     | μs   | PC low to Vout low                                         |

| VTM Control (VC)        |     |     |     |      |                                                            |

| External boost voltage  | 12  | 14  | 19  | Vdc  | Required for VTM start up without PRM                      |

| External boost duration |     | 10  | ·   | ms   | Vin > 26 Vdc. VC must be applied continuously              |

|                         |     |     |     |      | if Vin < 26 Vdc.                                           |

**V•I Chip Voltage Transformation Module** 800-735-6200

V048F060T040

Rev. 2.8

vicorpower.com

#### **Pin / Control Functions**

#### +In / -In DC Voltage Ports

The VTM input should not exceed the maximum specified. Be aware of this limit in applications where the VTM is being driven above its nominal output voltage. If less than 26 Vdc is present at the +In and -In ports, a continuous VC voltage must be applied for the VTM to process power. Otherwise VC voltage need only be applied for 10 ms after the voltage at the +In and -In ports has reached or exceeded 26 Vdc. If the input voltage exceeds the overvoltage turn-off, the VTM will shutdown. The VTM does not have internal input reverse polarity protection. Adding a properly sized diode in series with the positive input or a fused reverse-shunt diode will provide reverse polarity protection.

#### TM - For Factory Use Only

#### VC - VTM Control

The VC port is multiplexed. It receives the initial  $V_{CC}$  voltage from an upstream PRM, synchronizing the output rise of the VTM with the output rise of the PRM. Additionally, the VC port provides feedback to the PRM to compensate for the VTM output resistance. In typical applications using VTMs powered from PRMs, the PRM's VC port should be connected to the VTM VC port.

In applications where a VTM is being used without a PRM, 14 V must be supplied to the VC port for as long as the input voltage is below 26 V and for 10 ms after the input voltage has reached or exceeded 26 V. The VTM is not designed for extended operation below 26 V. The VC port should only be used to provide V<sub>CC</sub> voltage to the VTM during startup.

#### PC - Primary Control

The Primary Control (PC) port is a multifunction port for controlling the VTM as follows:

Disable – If PC is left floating, the VTM output is enabled. To disable the output, the PC port must be pulled lower than 2.4 V, referenced to -In. Optocouplers, open collector transistors or relays can be used to control the PC port. Once disabled, 14 V must be re-applied to the VC port to restart the VTM.

Primary Auxiliary Supply – The PC port can source up to 2.4 mA at 5 Vdc.

#### +Out / -Out DC Voltage Output Ports

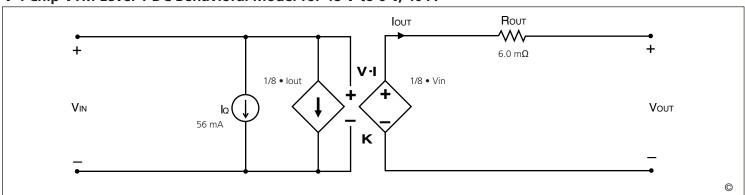

The output and output return are through two sets of contact locations. The respective +Out and -Out groups must be connected in parallel with as low an interconnect resistance as possible. Within the specified input voltage range, the Level 1 DC behavioral model shown in Figure 16 defines the output voltage of the VTM. The current source capability of the VTM is shown in the specification table.

To take full advantage of the VTM, the user should note the low output impedance of the device. The low output impedance provides fast transient response without the need for bulk POL capacitance. Limitedlife electrolytic capacitors required with conventional converters can be reduced or even eliminated, saving cost and valuable board real estate.

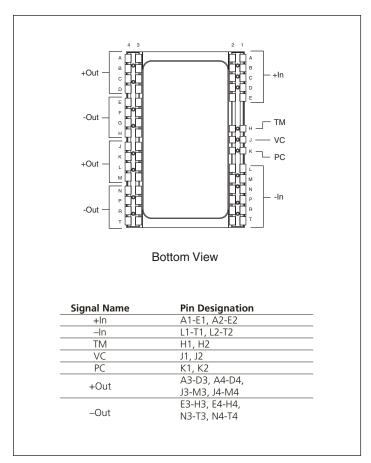

Figure 9 — VTM pin configuration

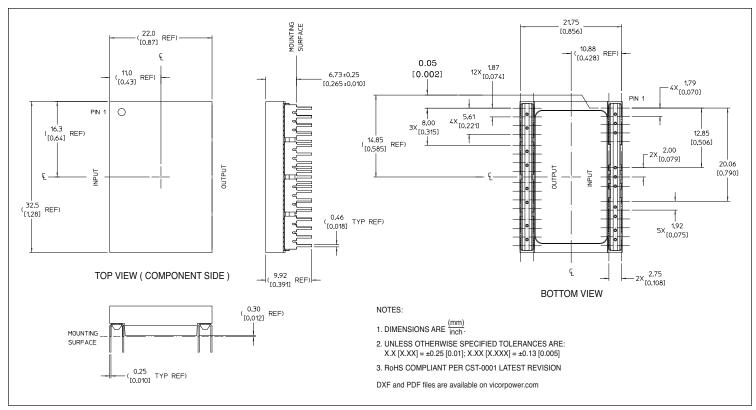

Figure 10 — VTM J-Lead mechanical outline; Onboard mounting

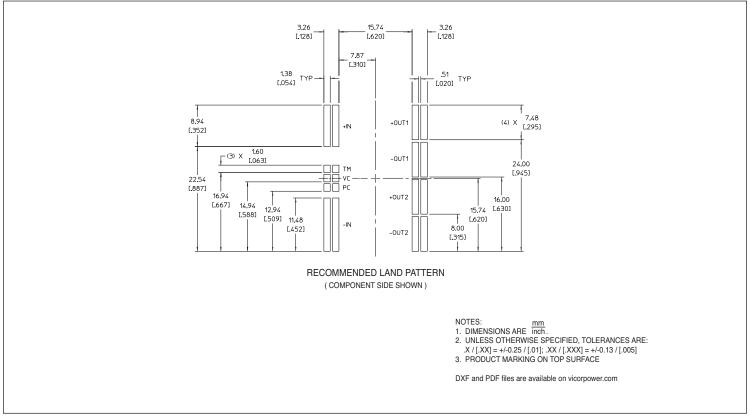

Figure 11 — VTM J-Lead PCB land layout information; Onboard mounting

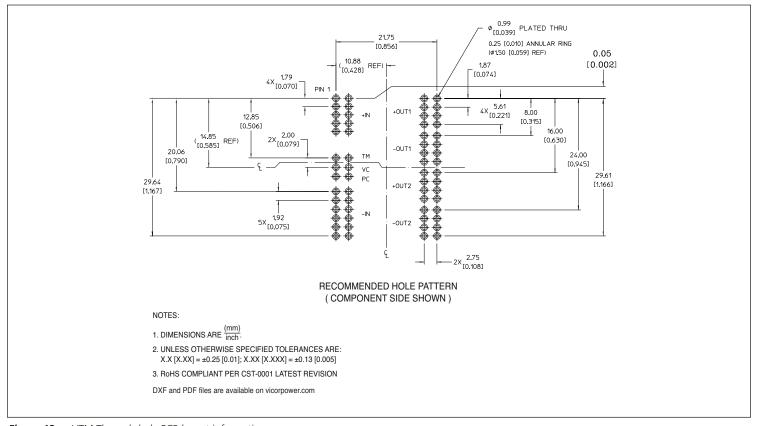

Figure 12 —VTM Through-hole mechanical outline

Figure 13 — VTM Through-hole PCB layout information

vicorpower.com 800-735-6200

V•I Chip Voltage Transformation Module

V048F060T040

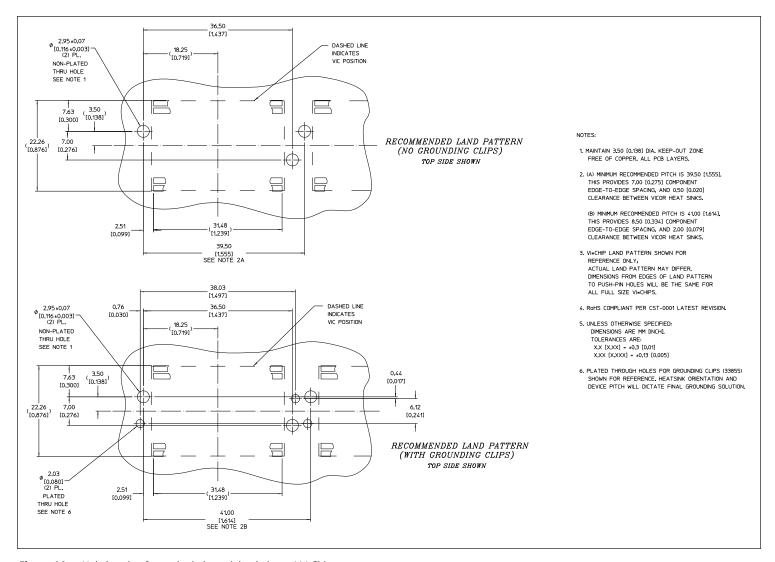

Figure 14 — Hole location for push pin heat sink relative to V•I Chip

## **Application Note**

#### **Parallel Operation**

In applications requiring higher current or redundancy. VTMs can be operated in parallel without adding control circuitry or signal lines. To maximize current sharing accuracy, it is imperative that the source and load impedance on each VTM in a parallel array be equal. If VTMs are being fed by an upstream PRM, the VC nodes of all VTMs must be connected to the PRM VC.

To achieve matched impedances, dedicated power planes within the PC board should be used for the output and output return paths to the array of paralleled VTMs. This technique is preferable to using traces of varying size and length.

The VTM power train and control architecture allow bi-directional power transfer when the VTM is operating within its specified ranges. Bi-directional power processing improves transient response in the event of an output load dump. The VTM may operate in reverse, returning output power back to the input source. It does so efficiently.

#### **Input Impedance Recommendations**

To take full advantage of the VTM's capabilities, the impedance of the source (input source plus the PC board impedance) must be low over a range from DC to 5 MHz. The input of the VTM (factorized bus) should be locally bypassed with a 8 µF low Q aluminum electrolytic capacitor. Additional input capacitance may be added to improve transient

performance or compensate for high source impedance. The VTM has extremely wide bandwidth so the source response to transients is usually the limiting factor in overall output response of the VTM.

Anomalies in the response of the source will appear at the output of the VTM, multiplied by its K factor of 1/8. The DC resistance of the source should be kept as low as possible to minimize voltage deviations on the input to the VTM. If the VTM is going to be operating close to the high limit of its input range, make sure input voltage deviations will not trigger the input overvoltage turn-off threshold.

#### **Input Fuse Recommendations**

V•I Chips are not internally fused in order to provide flexibility in configuring power systems. However, input line fusing of V•I Chips must always be incorporated within the power system. A fast acting fuse is required to meet safety agency Conditions of Acceptability. The input line fuse should be placed in series with the +In port.

#### **Application Notes**

For VTM and V•I Chip application notes on soldering, thermal management, board layout, and system design click on the link below: http://www.vicorpower.com/technical\_library/application\_information/chips/

Figure 15 — VTM test circuit

#### VI Chip VTM Level 1 DC Behavioral Model for 48 V to 6 V, 40 A

Figure 16 — This model characterizes the DC operation of the V•I Chip VTM, including the converter transfer function and its losses. The model enables estimates or simulations of output voltage as a function of input voltage and output load, as well as total converter power dissipation or heat generation.

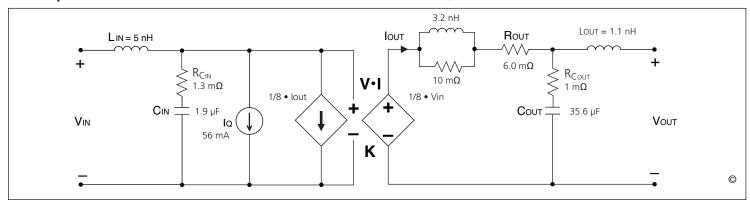

## V•I Chip VTM Level 2 Transient Behavioral Model for 48 V to 6 V, 40 A

**Figure 17** — This model characterizes the AC operation of the  $V \bullet I$  Chip VTM including response to output load or input voltage transients or steady state modulations. The model enables estimates or simulations of input and output voltages under transient conditions, including response to a stepped load with or without external filtering elements.

In figures below;

K = VTM transformation ratio

$R_O = VTM$  output resistance

$V_f$  = PRM output (Factorized Bus Voltage)

$V_0 = VTM$  output

$V_L$  = Desired load voltage

## **FPA Adaptive Loop**

**Figure 18** — The PRM controls the factorized bus voltage,  $V_f$ , in proportion to output current to compensate for the output resistance, Ro, of the VTM. The VTM output voltage is typically within 1% of the desired load voltage ( $V_D$ ) over all line and load conditions.

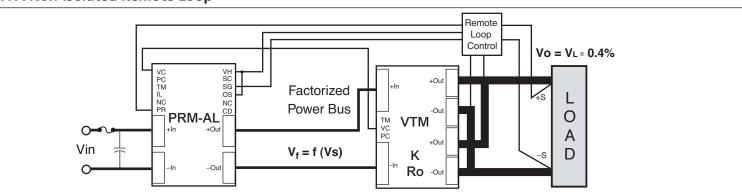

#### **FPA Non-isolated Remote Loop**

**Figure 19** — An external error amplifier or Point-of-Load IC (POLIC) senses the load voltage and controls the PRM output – the Factorized Bus – as a function of output current, compensating for the output resistance of the VTM and for distribution resistance.

VICOR

vicorpower.com

800-735-6200

V•I Chip Voltage Transformation Module

V048F060T040

#### Warranty

Vicor products are guaranteed for two years from date of shipment against defects in material or workmanship when in normal use and service. This warranty does not extend to products subjected to misuse, accident, or improper application or maintenance. Vicor shall not be liable for collateral or consequential damage. This warranty is extended to the original purchaser only.

EXCEPT FOR THE FOREGOING EXPRESS WARRANTY, VICOR MAKES NO WARRANTY, EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE.

Vicor will repair or replace defective products in accordance with its own best judgement. For service under this warranty, the buyer must contact Vicor to obtain a Return Material Authorization (RMA) number and shipping instructions. Products returned without prior authorization will be returned to the buyer. The buyer will pay all charges incurred in returning the product to the factory. Vicor will pay all reshipment charges if the product was defective within the terms of this warranty.

Information published by Vicor has been carefully checked and is believed to be accurate; however, no responsibility is assumed for inaccuracies. Vicor reserves the right to make changes to any products without further notice to improve reliability, function, or design. Vicor does not assume any liability arising out of the application or use of any product or circuit; neither does it convey any license under its patent rights nor the rights of others. Vicor general policy does not recommend the use of its components in life support applications wherein a failure or malfunction may directly threaten life or injury. Per Vicor Terms and Conditions of Sale, the user of Vicor components in life support applications assumes all risks of such use and indemnifies Vicor against all damages.

## Vicor's comprehensive line of power solutions includes high density AC-DC and DC-DC modules and accessory components, fully configurable AC-DC and DC-DC power supplies, and complete custom power systems.

Information furnished by Vicor is believed to be accurate and reliable. However, no responsibility is assumed by Vicor for its use. Vicor components are not designed to be used in applications, such as life support systems, wherein a failure or malfunction could result in injury or death. All sales are subject to Vicor's Terms and Conditions of Sale, which are available upon request.

## Specifications are subject to change without notice.

#### **Intellectual Property Notice**

Vicor and its subsidiaries own Intellectual Property (including issued U.S. and Foreign Patents and pending patent applications) relating to the products described in this data sheet. Interested parties should contact Vicor's Intellectual Property Department.

The products described on this data sheet are protected by the following U.S. Patents Numbers: 5,945,130; 6,403,009; 6,710,257; 6,911,848; 6,930,893; 6,934,166; 6,940,013; 6,969,909; 7,038,917; 7,145,186; 7,166,898; 7,187,263; 7,202,646; 7,361,844; D496,906; D505,114; D506,438; D509,472; and for use under 6,975,098 and 6,984,965

## **Vicor Corporation**

25 Frontage Road Andover, MA, USA 01810 Tel: 800-735-6200 Fax: 978-475-6715

#### email

Customer Service: custserv@vicorpower.com Technical Support: apps@vicorpower.com