Secondary Variable Output LDO Regulator Series for Local Power Supplies

# 300mA Secondary Variable Output LDO Regulators for Local Power Supplies

BD00GA3WEFJ No.10026EAT05

#### Description

BD00GA3WEFJ is a LDO regulator with output current 0.3A. The output accuracy is ±1% of output voltage. With external resistance, it is available to set the output voltage at random (from 1.5V to 13.0V) and also provides output voltage fixed type without external resistance. It is used for the wide applications of digital appliances. It has package type: HTSOP-J8. Over current protection (for protecting the IC destruction by output short circuit), circuit current ON/OFF switch (for setting the circuit 0µA at shutdown mode), and thermal shutdown circuit (for protecting IC from heat destruction by over load condition) are all built in. It is usable for ceramic capacitor and enables to improve smaller set and long-life.

#### Features

- 1) Output current 0.3A

- 2) High accuracy reference voltage circuit

- 3) Built-in Over Current Protection circuit (OCP)

- 4) Built-in Thermal Shut Down circuit (TSD)

- 5) With shut down switch

- 6) Output voltage variable type (1.5V to 13.0V)

- 7) Package: HTSOP-J8

# Output voltage differential Line up

| Product name | Variable | Package  |

|--------------|----------|----------|

| BD00GA3WEFJ  | 0        | HTSOP-J8 |

Product name : BD00GA3WEFJ

| Signal | Description        |            |                                 |          |  |  |

|--------|--------------------|------------|---------------------------------|----------|--|--|

|        | Output voltage (V) |            |                                 |          |  |  |

| а      | 0                  | 0          | Vari                            | Variable |  |  |

|        |                    | Voltage re | sistance(V)                     |          |  |  |

| h      | E                  | 24V        | Н                               | 10V      |  |  |

| b      | F                  | 20V        | I                               | 7V       |  |  |

|        | G                  | 15V        |                                 |          |  |  |

|        | Output current (A) |            |                                 |          |  |  |

|        | A1                 | 0.1A       | C0                              | 1.0A     |  |  |

| С      | A3                 | 0.3A       | C5                              | 1.5A     |  |  |

|        | A5 0.5A            |            | D0                              | 2.0A     |  |  |

|        | Shutdown switch    |            |                                 |          |  |  |

| d      | "W"                |            | Shutdown switch is built in     |          |  |  |

|        | u n                |            | Shutdown switch is not built in |          |  |  |

|        | Package            |            |                                 |          |  |  |

| е      | EFJ                |            | HTSOP-J8                        |          |  |  |

# ● Absolute Maximum Ratings (Ta=25°C)

| Parame                      | Parameter            |                  | Limits              | Unit |

|-----------------------------|----------------------|------------------|---------------------|------|

| Power supply voltage        | Power supply voltage |                  | 15.0 * <sup>1</sup> | V    |

| EN voltage                  |                      | $V_{EN}$         | 15.0                | V    |

| Output voltage              |                      | V <sub>OUT</sub> | 15.0                | V    |

| Feedback voltage            |                      | $V_{FB}$         | 15.0                | V    |

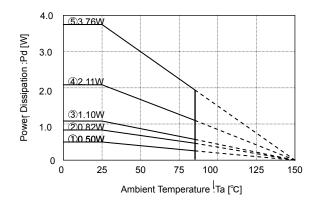

| Power dissipation HTSOP-J8  |                      | Pd <sup>*2</sup> | 2110 <sup>*2</sup>  | mW   |

| Operating Temperature Range |                      | Topr             | -25~+85             | °C   |

| Storage Temperature Range   |                      | Tstg             | -55 <b>~</b> +150   | °C   |

| Junction Temperature        |                      | Tjmax            | +150                | °C   |

<sup>\*1</sup> Not to exceed Pd

# ●Operating conditions (Ta=25°C)

| Parameter                    | Symbol   | Min. | Max. | Unit |

|------------------------------|----------|------|------|------|

| Input power supply voltage   | Vcc      | 4.5  | 14.0 | V    |

| EN voltage                   | $V_{EN}$ | 0.0  | 14.0 | V    |

| Output voltage setting range | Vo       | 1.5  | 13.0 | V    |

| Output current               | lo       | 0.0  | 0.3  | Α    |

This product should not be used in a radioactive environment.

#### Electrical Characteristics

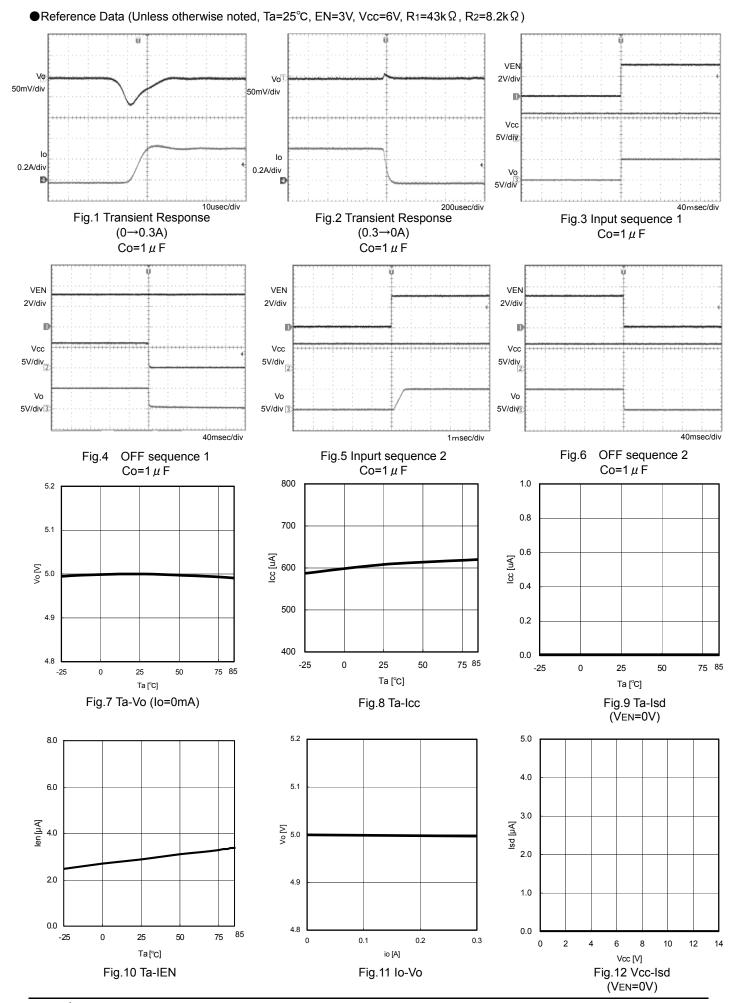

(Unless otherwise noted, Ta=25°C, EN=3V, Vcc=6V, R1=43k  $\Omega$  , R2=8.2k  $\Omega$  )

| Parameter                        | Symbol     | Min.  | Тур.  | Max.  | Unit | Conditions            |

|----------------------------------|------------|-------|-------|-------|------|-----------------------|

| Circuit current at shutdown mode | Isd        | -     | 0     | 5     | μΑ   | EN=0V, OFF mode       |

| Bias current                     | lcc        | -     | 600   | 900   | μΑ   |                       |

| Line regulation                  | Reg.I      | -     | 25    | 50    | mV   | Vcc=( Vo+0.9V )→14.0V |

| Load regulation                  | Reg Io     | -     | 25    | 75    | mV   | lo=0→0.3A             |

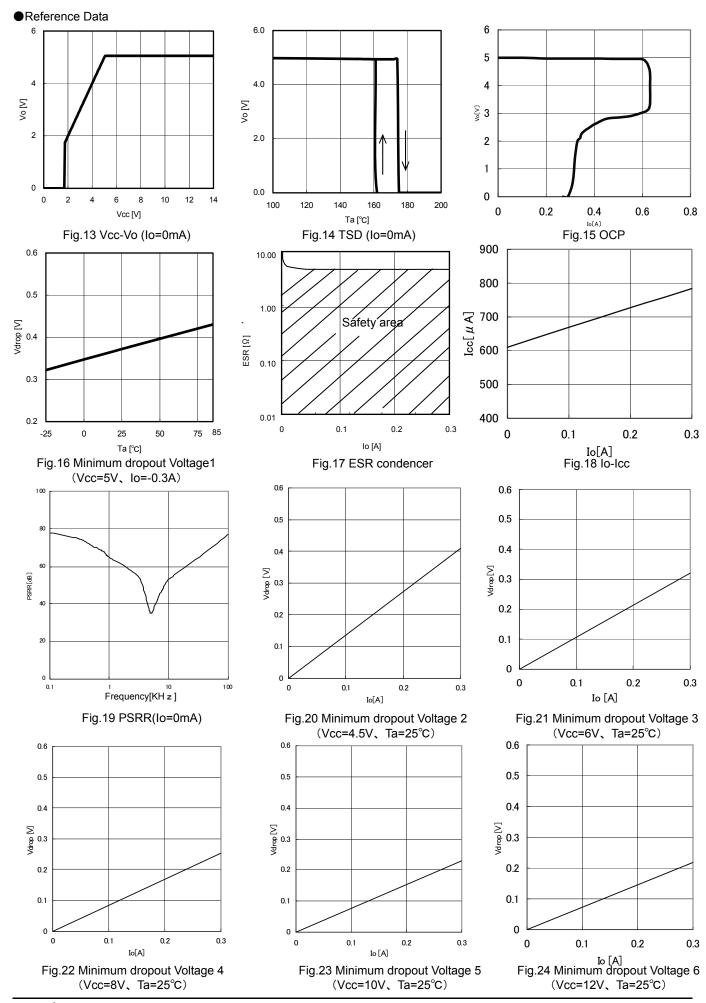

| Minimun dropout Voltage          | Vco        | -     | 0.6   | 0.9   | V    | Vcc=5V,Io=0.3A        |

| Output reference voltage         | $V_{FB}$   | 0.792 | 0.800 | 0.808 | V    | Io=0mA                |

| EN Low voltage                   | VEN (Low)  | 0     | -     | 0.8   | V    |                       |

| EN High voltage                  | VEN (High) | 2.4   | -     | 14.0  | V    |                       |

| EN Bias current                  | IEN        | 1     | 3     | 9     | μΑ   |                       |

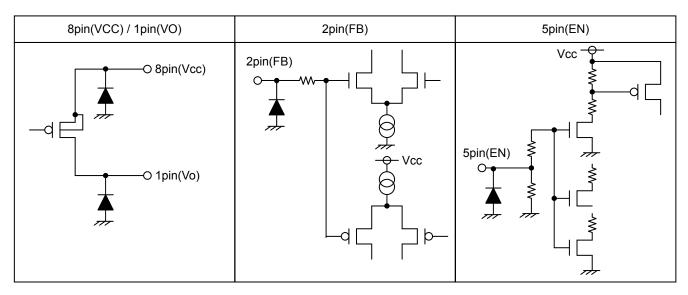

# ●I/O Equivalent circuits

<sup>\*2</sup> Reduced by 16.9mW/°C for each increase in Ta of 1°C over 25°C. (when mounted on a board 70mm×70mm×1.6mm glass-epoxy board, two layer)

Technical Note

# Heat Dissipation CharacteristicsØHTSOP-J8

Measure condition: mounted on a ROHM board, and IC

Substrate size: 70mm × 70mm × 1.6mm (Substrate with thermal via)

- Solder the substrate and package reverse exposure heat radiation part

- ① IC only  $\theta$  j-a=249.5°C/W

- ② 1-layer (copper foil are :0mm × 0mm)  $\theta$  j-a=153.2°C/W

- ③ 2-layer (copper foil are :15mm × 15mm)  $\theta$  j-a=113.6°C/W

- (a) 2-layer (copper foil are :70mm × 70mm)  $\theta$  j-a=59.2°C/W

- (5) 4-layer (copper foil are :70mm × 70mm)  $\theta$  j-a=33.3°C/W

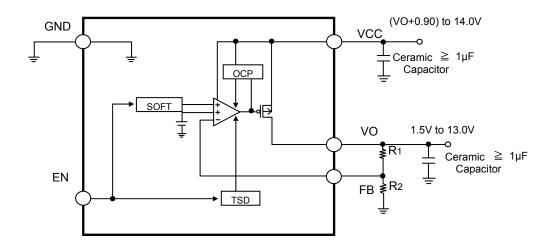

### About Input-to-output capacitor

It is recommended that a capacitor is placed nearby pin between Input pin and GND, output pin and GND.

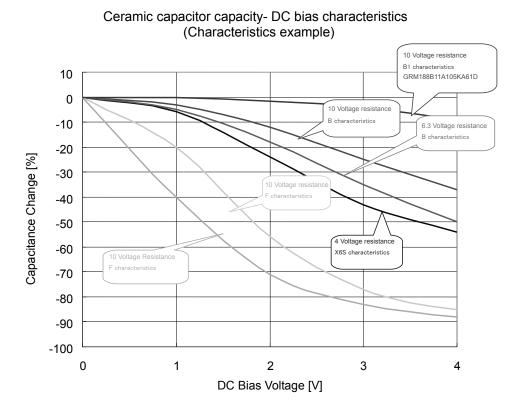

A capacitor, between input pin and GND, is valid when the power supply impedance is high or drawing is long. Also as for a capacitor, between output pin and GND, the greater the capacity, more sustainable the line regulation and it makes improvement of characteristics by load change. However, please check by mounted on a board for the actual application. Ceramic capacitor usually has difference, thermal characteristics and series bias characteristics, and moreover capacity decreases gradually by using conditions.

For more detail, please be sure to inquire the manufacturer, and select the best ceramic capacitor.

#### Heat Loss

Thermal design should allow operation within the following conditions. Note that the temperatures listed are the allowed temperature limits, and thermal design should allow sufficient margin from the limits.

- 1. Ambient temperature Ta can be no higher than 85°C.

- 2. Chip junction temperature (Tj) can be no higher than 150°C.

Chip junction temperature can be determined as follows:

① Calculation based on ambient temperature (Ta)  $T_i=Ta+\theta i-a\times W$

<Reference values>

$\theta$  j-a: HTSOP-J8 153.2°C/W 1-layer substrate (copper foil density 0mm × 0mm) 113.6°C/W 2-layer substrate (copper foil density 15mm × 15mm) 59.2°C/W 2-layer substrate (copper foil density 70mm × 70mm) 33.3°C/W 4-layer substrate (copper foil density 70mm × 70mm) Substrate size:  $70 \times 70 \times 1.6$ mm³ (substrate with thermal via)

Most of the heat loss that occurs in the BD00GA3WEFJ is generated from the output Pch FET. Power loss is determined by the total  $V_{\text{CC}}$ -Vo voltage and output current. Be sure to confirm the system input and output voltage and the output current conditions in relation to the heat dissipation characteristics of the VIN and Vo in the design. Bearing in mind that heat dissipation may vary substantially depending on the substrate employed (due to the power package incorporated in the BD00GA3WEFJ make certain to factor conditions such as substrate size into the thermal design.

Power consumption (W) =

$$\left\{ \text{Input voltage (VCC)- Output voltage (Vo)} \right\} \times \text{Io(Ave)}$$

Example) Where VCC=5.0V, VO=3.3V, Io(Ave) = 0.1A,

Power consumption (W) =  $\left\{ 5.0(\text{V}) - 3.3(\text{V}) \right\} \times 0.1(\text{A})$

=0.17(W)

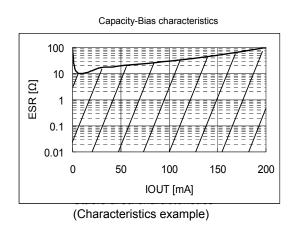

● About equivalent series resistance ESR (ceramic capacitor etc.)

Capacitor usually has ESR (Equivalent Series Resistance), and operates stable in ESR-OUT range, showed right. Generally, ESR of ceramic, tantalum and electronic capacitor etc. is different for each, so please be sure to check a capacitor which is going to use, and use it inside the stable range, showed right. Then, please evaluate for the actual application.

# ●Block Diagram BD00GA3WEFJ

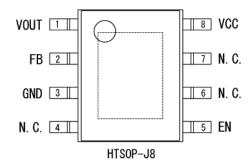

# ●Pin number • Pin name

| Pin No. | Pin name | Pin Function       |  |

|---------|----------|--------------------|--|

| 1       | VOUT     | Output voltage pin |  |

| 2       | FB       | Feedback pin       |  |

| 3       | GND      | GND pin            |  |

| 4       | N.C.     | Non Connection     |  |

| 5       | EN       | Enable pin         |  |

| 6       | N.C.     | Non Connection     |  |

| 7       | N.C.     | Non Connection     |  |

| 8       | VCC      | Input voltage pin  |  |

| Reverse | FIN      | Substrate(GND pin) |  |

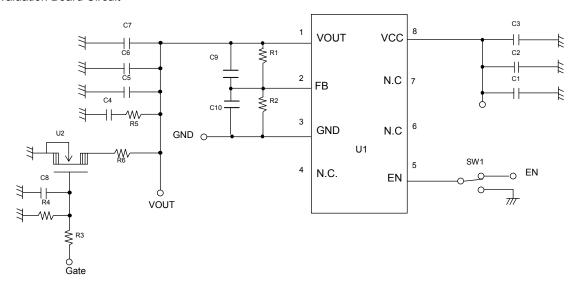

#### ●Evaluation Board Circuit

#### ●Evaluation Board Parts List

|             |       | 1              |         |             |       |               |         |

|-------------|-------|----------------|---------|-------------|-------|---------------|---------|

| Designation | Value | Part No.       | Company | Designation | Value | Part No.      | Company |

| R1          | 43kΩ  | MCR01PZPZF4302 | ROHM    | C4          | -     | •             | -       |

| R2          | 8.2kΩ | MCR01PZPZF8201 | ROHM    | C5          | 1uF   | CM105B105K16A | KYOCERA |

| R3          | •     | -              | -       | C6          |       |               |         |

| R4          | •     | -              | -       | C7          | -     | •             | -       |

| R5          |       | -              | -       | C8          | -     | -             | -       |

| R6          | •     | -              | -       | C9          | -     | •             | -       |

| C1          | 1uF   | CM105B105K16A  | KYOCERA | C10         | -     | •             | -       |

| C2          | ı     | -              |         | U1          | -     | BD00GA3WEFJ   | ROHM    |

| C3          | -     | -              |         | U2          | -     | -             | -       |

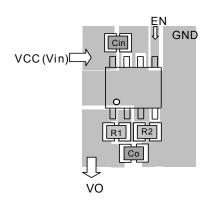

#### ●About Board Layout

- Input capacitor Cin of VCC (Vin) should be placed very close to VCC(Vin) pin as possible, and used broad wiring pattern.

Output capacitor Co also should be placed close to IC pin as possible. In case connected to inner layer GND plane, please use several through hole.

- VFB pin has comparatively high impedance, and is apt to be effected by noise, so floating capacity should be minimum as

possible. Please be careful in wiring drawing

- Please take GND pattern space widely, and design layout to be able to increase radiation efficiency.

- · For output voltage setting

Output voltage can be set by FB pin voltage (0.800V typ.) and external resistance R1, R2.

$$VO = V_{FB} \times \frac{R_1 + R_2}{R_2}$$

(The use of resistors with R1+R2=5k to 90k is recommended)

#### Operation Notes

#### (1). Absolute maximum ratings

An excess in the absolute maximum ratings, such as supply voltage, temperature range of operating conditions, etc., can break down the devices, thus making impossible to identify breaking mode, such as a short circuit or an open circuit. If any over rated values will expect to exceed the absolute maximum ratings, consider adding circuit protection devices, such as fuses.

#### (2). Connecting the power supply connector backward

Connecting of the power supply in reverse polarity can damage IC. Take precautions when connecting the power supply lines. An external direction diode can be added.

#### (3). Power supply lines

Design PCB layout pattern to provide low impedance GND and supply lines. To obtain a low noise ground and supply line, separate the ground section and supply lines of the digital and analog blocks. Furthermore, for all power supply terminals to ICs, connect a capacitor between the power supply and the GND terminal. When applying electrolytic capacitors in the circuit, not that capacitance characteristic values are reduced at low temperatures.

#### (4). GND voltage

The potential of GND pin must be minimum potential in all operating conditions.

#### (5). Thermal design

Use a thermal design that allows for a sufficient margin in light of the power dissipation (Pd) in actual operating conditions.

#### (6). Inter-pin shorts and mounting errors

Use caution when positioning the IC for mounting on printed circuit boards. The IC may be damaged if there is any connection error or if pins are shorted together.

#### (7). Actions in strong electromagnetic field

Use caution when using the IC in the presence of a strong electromagnetic field as doing so may cause the IC to malfunction.

# (8). ASO

When using the IC, set the output transistor so that it does not exceed absolute maximum ratings or ASO.

#### (9). Thermal shutdown circuit

The IC incorporates a built-in thermal shutdown circuit (TSD circuit). The thermal shutdown circuit (TSD circuit) is designed only to shut the IC off to prevent thermal runaway. It is not designed to protect the IC or guarantee its operation. Do not continue to use the IC after operating this circuit or use the IC in an environment where the operation of this circuit is assumed.

|             | TSD ON Temperature[°C] (typ.) | Hysteresis Temperature [°C] (typ.) |

|-------------|-------------------------------|------------------------------------|

| BD00GA3WEFJ | 175                           | 15                                 |

#### (10). Testing on application boards

When testing the IC on an application board, connecting a capacitor to a pin with low impedance subjects the IC to stress. Always discharge capacitors after each process or step. Always turn the IC's power supply off before connecting it to or removing it from a jig or fixture during the inspection process. Ground the IC during assembly steps as an antistatic measure. Use similar precaution when transporting or storing the IC.

BD00GA3WEFJ Technical Note

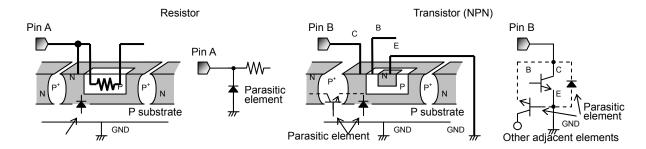

#### (11). Regarding input pin of the IC

This monolithic IC contains P+ isolation and P substrate layers between adjacent elements in order to keep them isolated. P-N junctions are formed at the intersection of these P layers with the N layers of other elements, creating a parasitic diode or transistor. For example, the relation between each potential is as follows:

When GND > Pin A and GND > Pin B, the P-N junction operates as a parasitic diode.

When GND > Pin B, the P-N junction operates as a parasitic transistor.

Parasitic diodes can occur inevitable in the structure of the IC.

The operation of parasitic diodes can result in mutual interference among circuits, operational faults, or physical damage. Accordingly, methods by which parasitic diodes operate, such as applying a voltage that is lower than the GND (P substrate) voltage to an input pin, should not be used.

## (12). Ground Wiring Pattern.

When using both small signal and large current GND patterns, it is recommended to isolate the two ground patterns, placing a single ground point at the ground potential of application so that the pattern wiring resistance and voltage variations caused by large currents do not cause variations in the small signal ground voltage. Be careful not to change the GND wiring pattern of any external components, either.

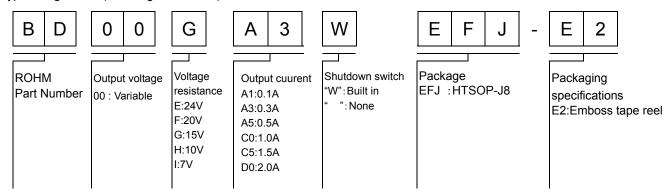

■Type Designations (Ordering Information)

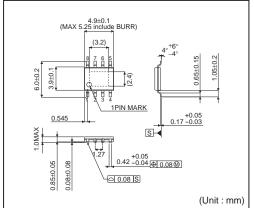

# HTSOP-J8

#### Notes

No copying or reproduction of this document, in part or in whole, is permitted without the consent of ROHM Co.,Ltd.

The content specified herein is subject to change for improvement without notice.

The content specified herein is for the purpose of introducing ROHM's products (hereinafter "Products"). If you wish to use any such Product, please be sure to refer to the specifications, which can be obtained from ROHM upon request.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, ROHM shall bear no responsibility for such damage.

The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. ROHM does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by ROHM and other parties. ROHM shall bear no responsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio visual equipment, office-automation equipment, communication devices, electronic appliances and amusement devices).

The Products specified in this document are not designed to be radiation tolerant.

While ROHM always makes efforts to enhance the quality and reliability of its Products, a Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe designs. ROHM shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). ROHM shall bear no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intended to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Thank you for your accessing to ROHM product informations. More detail product informations and catalogs are available, please contact us.

# ROHM Customer Support System

http://www.rohm.com/contact/