# Features

- High-performance, Low-power 8/16-bit AVR XMEGA Microcontroller

- Non-volatile Program and Data Memories

- 16 KB 128 KB of In-System Self-Programmable Flash

- 4 KB 8 KB Boot Code Section with Independent Lock Bits

- 1 KB 2 KB EEPROM

- 2 KB 8 KB Internal SRAM

- Peripheral Features

- Four-channel DMA Controller with support for external requests

- Eight-channel Event System

- Five 16-bit Timer/Counters

Three Timer/Counters with 4 Output Compare or Input Capture channels Two Timer/Counters with 2 Output Compare or Input Capture channels High-Resolution Extensions on all Timer/Counters Advanced Waveform Extension on one Timer/Counter

- Five USARTs

- IrDA Extension on one USART

- Two Two-Wire Interfaces with dual address match (I<sup>2</sup>C and SMBus compatible)

- Two SPIs (Serial Peripheral Interfaces) peripherals

- AES and DES Crypto Engine

- 16-bit Real Time Counter with Separate Oscillator

- One Twelve-channel, 12-bit, 2 Msps Analog to Digital Converter

- One Two-channel, 12-bit, 1 Msps Digital to Analog Converter

- Two Analog Comparators with Window compare function

- External Interrupts on all General Purpose I/O pins

- Programmable Watchdog Timer with Separate On-chip Ultra Low Power Oscillator

- Special Microcontroller Features

- Power-on Reset and Programmable Brown-out Detection

- Internal and External Clock Options with PLL

- Programmable Multi-level Interrupt Controller

- Sleep Modes: Idle, Power-down, Standby, Power-save, Extended Standby

- Advanced Programming, Test and Debugging Interfaces

- PDI (Program and Debug Interface) for programming, test and debugging

- I/O and Packages

- 34 Programmable I/O Lines

- 44 lead TQFP

- 44 pad VQFN/QFN

- 49 ball VFBGA

- Operating Voltage

- 1.6 3.6V

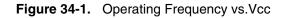

- Speed performance

- 0 12 MHz @ 1.6 3.6V

- 0 32 MHz @ 2.7 3.6V

# **Typical Applications**

- Industrial control

- Factory automation

- Building control

- Board control

- White Goods

- NetworkingOptical

• ZigBee

Climate control

Motor control

- Hand-held battery applications

- Power tools

- HVAC

- Metering

- Medical Applications

8/16-bit **AVR**<sup>®</sup> XMEGA A4 Microcontroller

ATxmega128A4 ATxmega64A4 ATxmega32A4 ATxmega16A4

# Preliminary

8069L-AVR-11/09

# 1. Ordering Information

| Ordering Code   | Flash         | E <sup>2</sup> | SRAM | Speed (MHz) | Power Supply | Package <sup>(1)(2)(3)</sup> | Temp         |

|-----------------|---------------|----------------|------|-------------|--------------|------------------------------|--------------|

| ATxmega128A4-AU | 128 KB + 8 KB | 2 KB           | 8 KB | 32          | 1.6 - 3.6V   |                              |              |

| ATxmega64A4-AU  | 64 KB + 4 KB  | 2 KB           | 4 KB | 32          | 1.6 - 3.6V   | 44.6                         |              |

| ATxmega32A4-AU  | 32 KB + 4 KB  | 1 KB           | 4 KB | 32          | 1.6 - 3.6V   | 44A                          |              |

| ATxmega16A4-AU  | 16 KB + 4 KB  | 1 KB           | 2 KB | 32          | 1.6 - 3.6V   |                              |              |

| ATxmega128A4-MH | 128 KB + 8 KB | 2 KB           | 8 KB | 32          | 1.6 - 3.6V   |                              | -40°C - 85°C |

| ATxmega64A4-MH  | 64 KB + 4 KB  | 2 KB           | 4 KB | 32          | 1.6 - 3.6V   | 44M1                         | -40°C - 85°C |

| ATxmega32A4-MH  | 32 KB + 4 KB  | 1 KB           | 4 KB | 32          | 1.6 - 3.6V   | 441/11                       |              |

| ATxmega16A4-MH  | 16 KB + 4 KB  | 1 KB           | 2 KB | 32          | 1.6 - 3.6V   |                              |              |

| ATxmega32A4-CU  | 32 KB + 4K    | 1 KB           | 4 KB | 32          | 1.6 - 3.6V   | 4000                         |              |

| ATxmega16A4-CU  | 16 KB + 4 KB  | 1 KB           | 2 KB | 32          | 1.6 - 3.6V   | 49C2                         |              |

Notes: 1. This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering information.

2. Pb-free packaging, complies to the European Directive for Restriction of Hazardous Substances (RoHS directive). Also Halide free and fully Green.

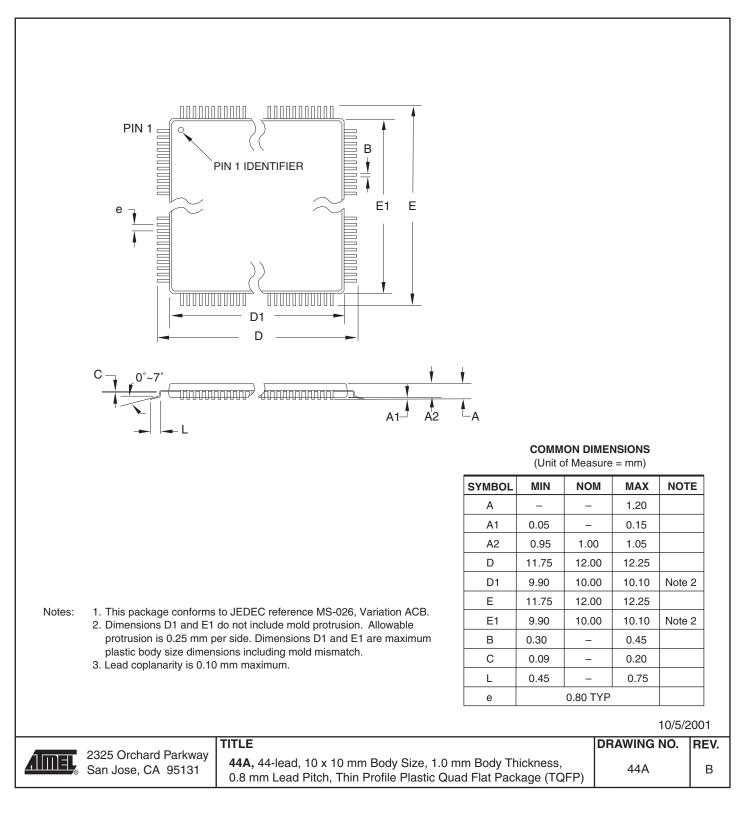

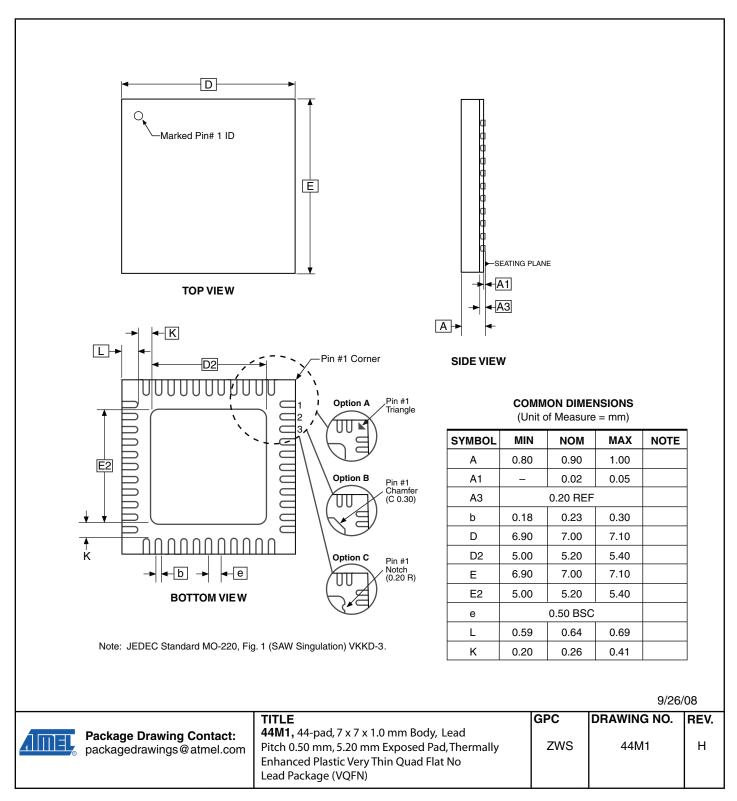

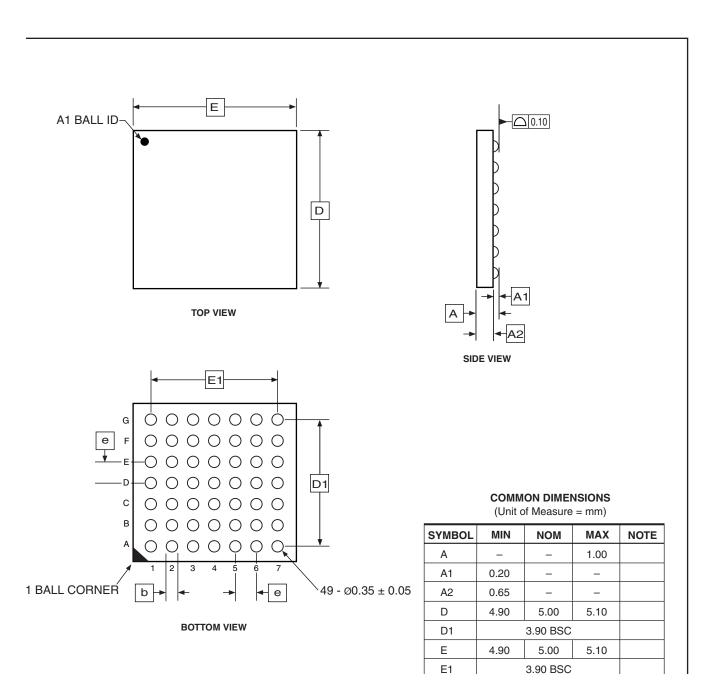

3. For packaging information see "Packaging information" on page 58.

|      | Package Type                                                                                                                     |

|------|----------------------------------------------------------------------------------------------------------------------------------|

| 44A  | 44-Lead, 10 x 10 mm Body Size, 1.0 mm Body Thickness, 0.8 mm Lead Pitch, Thin Profile Plastic Quad Flat Package (TQFP)           |

| 44M1 | 44-Pad, 7x7x1 mm Body, Lead Pitch 0.50 mm, 5.20 mm Exposed Pad, Thermally Enhanced Plastic Very Thin Quad No Lead Package (VQFN) |

| 49C2 | 49-Ball (7 x 7 Array), 0.65 mm Pitch, 5.0 x 5.0 x 1.0 mm, Very Thin, Fine-Pitch Ball Grid Array Package (VFBGA)                  |

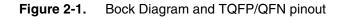

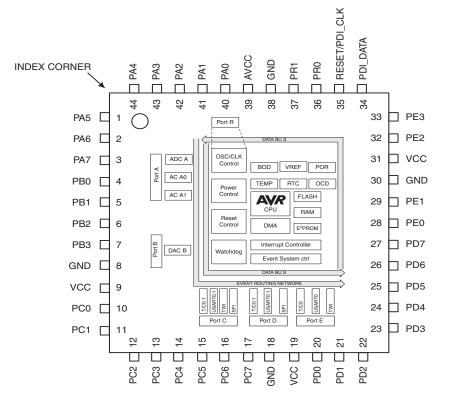

# 2. Pinout/Block Diagram

Note: For full details on pinout and pin functions refer to "Pinout and Pin Functions" on page 49.

# XMEGA A4

Table 2-1.VFBGA pinout

|   | 1   | 2    | 3   | 4   | 5                 | 6        |     |

|---|-----|------|-----|-----|-------------------|----------|-----|

| Α | PA3 | AVCC | GND | PR1 | PR0               | PDI_DATA | PE3 |

| в | PA4 | PA1  | PA0 | GND | RESET/<br>PDI_CLK | PE2      | VCC |

| С | PA5 | PA2  | PA6 | PA7 | GND               | PE1      | GND |

| D | PB1 | PB2  | PB3 | PB0 | GND               | PD7      | PE0 |

| Е | GND | GND  | PC3 | GND | PD4               | PD5      | PD6 |

| F | VCC | PC0  | PC4 | PC6 | PD0               | PD1      | PD3 |

| G | PC1 | PC2  | PC5 | PC7 | GND               | VCC      | PD2 |

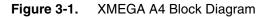

# 3. Overview

The XMEGA<sup>™</sup>A4 is a family of low power, high performance and peripheral rich CMOS 8/16-bit microcontrollers based on the AVR<sup>®</sup> enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the XMEGA A4 achieves throughputs approaching 1 Million Instructions Per Second (MIPS) per MHz allowing the system designer to optimize power consumption versus processing speed.

The AVR CPU combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction, executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs many times faster than conventional single-accumulator or CISC based microcontrollers.

The XMEGA A4 devices provide the following features: In-System Programmable Flash with Read-While-Write capabilities, Internal EEPROM and SRAM, four-channel DMA Controller, eight-channel Event System, Programmable Multi-level Interrupt Controller, 34 general purpose I/O lines, 16-bit Real Time Counter (RTC), five flexible 16-bit Timer/Counters with compare modes and PWM, five USARTs, two Two Wire Serial Interfaces (TWIs), two Serial Peripheral Interfaces (SPIs), AES and DES crypto engine, one Twelve-channel, 12-bit ADC with optional differential input with programmable gain, one Two-channel 12-bit DAC, two analog comparators with window mode, programmable Watchdog Timer with separate Internal Oscillator, accurate internal oscillators with PLL and prescaler and programmable Brown-Out Detection.

The Program and Debug Interface (PDI), a fast 2-pin interface for programming and debugging, is available.

The XMEGA A4 devices have five software selectable power saving modes. The Idle mode stops the CPU while allowing the SRAM, DMA Controller, Event System, Interrupt Controller and all peripherals to continue functioning. The Power-down mode saves the SRAM and register contents but stops the oscillators, disabling all other functions until the next TWI or pin-change interrupt, or Reset. In Power-save mode, the asynchronous Real Time Counter continues to run, allowing the application to maintain a timer base while the rest of the device is sleeping. In Standby mode, the Crystal/Resonator Oscillator is kept running while the rest of the device is sleeping. This allows very fast start-up from external crystal combined with low power consumption. In Extended Standby mode, both the main Oscillator and the Asynchronous Timer continue to run. To further reduce power consumption, the peripheral clock to each individual peripheral can optionally be stopped in Active mode and in Idle sleep mode.

The device is manufactured using Atmel's high-density nonvolatile memory technology. The program Flash memory can be reprogrammed in-system through the PDI. A Bootloader running in the device can use any interface to download the application program to the Flash memory. The Bootloader software in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation. By combining an 8/16-bit RISC CPU with In-System Self-Programmable Flash, the Atmel XMEGA A4 is a powerful microcontroller family that provides a highly flexible and cost effective solution for many embedded applications.

The XMEGA A4 devices are supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, programmers, and evaluation kits.

# 3.1 Block Diagram

# 4. Resources

A comprehensive set of development tools, application notes and datasheets are available for download on http://www.atmel.com/avr.

# 4.1 Recommended reading

- XMEGA A Manual

- XMEGA A Application Notes

This device data sheet only contains part specific information and a short description of each peripheral and module. The XMEGA A Manual describes the modules and peripherals in depth. The XMEGA A application notes contain example code and show applied use of the modules and peripherals.

The XMEGA A Manual and Application Notes are available from http://www.atmel.com/avr.

# 5. Disclaimer

For devices that are not available yet, typical values contained in this datasheet are based on simulations and characterization of other AVR XMEGA microcontrollers manufactured on the same process technology. Min. and Max values will be available after the device is characterized.

# 6. AVR CPU

# 6.1 Features

- 8/16-bit high performance AVR RISC Architecture

- 138 instructions

- Hardware multiplier

- 32x8-bit registers directly connected to the ALU

- Stack in RAM

- Stack Pointer accessible in I/O memory space

- Direct addressing of up to 16M Bytes of program and data memory

- True 16/24-bit access to 16/24-bit I/O registers

- Support for 8-, 16- and 32-bit Arithmetic

- · Configuration Change Protection of system critical features

#### 6.2 Overview

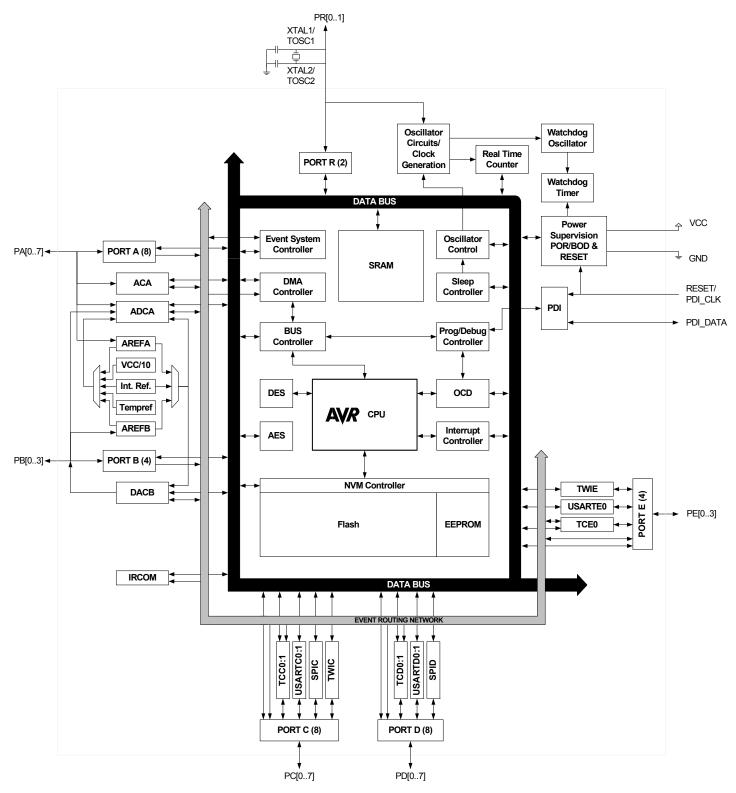

The XMEGA A4 uses the 8/16-bit AVR CPU. The main function of the CPU is program execution. The CPU must therefore be able to access memories, perform calculations and control peripherals. Interrupt handling is described in a separate section. Figure 6-1 on page 8 shows the CPU block diagram.

The AVR uses a Harvard architecture - with separate memories and buses for program and data. Instructions in the program memory are executed with a single level pipeline. While one instruction is being executed, the next instruction is pre-fetched from the program memory. This

concept enables instructions to be executed in every clock cycle. The program memory is In-System Re-programmable Flash memory.

### 6.3 Register File

The fast-access Register File contains 32 x 8-bit general purpose working registers with single clock cycle access time. This allows single-cycle Arithmetic Logic Unit (ALU) operation. In a typical ALU cycle, the operation is performed on two Register File operands, and the result is stored back in the Register File.

Six of the 32 registers can be used as three 16-bit address register pointers for data space addressing - enabling efficient address calculations. One of these address pointers can also be used as an address pointer for look up tables in Flash program memory.

#### 6.4 ALU - Arithmetic Logic Unit

The high performance Arithmetic Logic Unit (ALU) supports arithmetic and logic operations between registers or between a constant and a register. Single register operations can also be executed. Within a single clock cycle, arithmetic operations between general purpose registers or between a register and an immediate are executed. After an arithmetic or logic operation, the Status Register is updated to reflect information about the result of the operation.

The ALU operations are divided into three main categories – arithmetic, logical, and bit-functions. Both 8- and 16-bit arithmetic is supported, and the instruction set allows for efficient implementation of 32-bit arithmetic. The ALU also provides a powerful multiplier supporting both signed and unsigned multiplication and fractional format.

#### 6.5 Program Flow

When the device is powered on, the CPU starts to execute instructions from the lowest address in the Flash Program Memory '0'. The Program Counter (PC) addresses the next instruction to be fetched. After a reset, the PC is set to location '0'.

Program flow is provided by conditional and unconditional jump and call instructions, capable of addressing the whole address space directly. Most AVR instructions use a 16-bit word format, while a limited number uses a 32-bit format.

During interrupts and subroutine calls, the return address PC is stored on the Stack. The Stack is effectively allocated in the general data SRAM, and consequently the Stack size is only limited by the total SRAM size and the usage of the SRAM. After reset the Stack Pointer (SP) points to the highest address in the internal SRAM. The SP is read/write accessible in the I/O memory space, enabling easy implementation of multiple stacks or stack areas. The data SRAM can easily be accessed through the five different addressing modes supported in the AVR CPU.

# 7. Memories

# 7.1 Features

- Flash Program Memory

- One linear address space

- In-System Programmable

- Self-Programming and Bootloader support

- Application Section for application code

- Application Table Section for application code or data storage

- Boot Section for application code or bootloader code

- Separate lock bits and protection for all sections

- Built in fast CRC check of a selectable flash program memory section

- Data Memory

- One linear address space

- Single cycle access from CPU

- SRAM

- EEPROM

- Byte and page accessible

- Optional memory mapping for direct load and store

- I/O Memory

- Configuration and Status registers for all peripherals and modules 16 bit-accessible General Purpose Register for global variables or flags

- Bus arbitration

- Safe and deterministic handling of CPU and DMA Controller priority

- Separate buses for SRAM, EEPROM, I/O Memory and External Memory access Simultaneous bus access for CPU and DMA Controller

- Production Signature Row Memory for factory programmed data

- Device ID for each microcontroller device type

- Serial number for each device

- Oscillator calibration bytes

- ADC, DAC and temperature sensor calibration data

- User Signature Row

- One flash page in size Can be read and written from software Content is kept after chip erase

# 7.2 Overview

The AVR architecture has two main memory spaces, the Program Memory and the Data Memory. In addition, the XMEGA A4 features an EEPROM Memory for non-volatile data storage. All three memory spaces are linear and require no paging. The available memory size configurations are shown in "Ordering Information" on page 2. In addition each device has a Flash memory signature row for calibration data, device identification, serial number etc.

Non-volatile memory spaces can be locked for further write or read/write operations. This prevents unrestricted access to the application software.

# 7.3 In-System Programmable Flash Program Memory

The XMEGA A4 devices contain On-chip In-System Programmable Flash memory for program storage, see Figure 7-1 on page 11. Since all AVR instructions are 16- or 32-bits wide, each Flash address location is 16 bits.

The Program Flash memory space is divided into Application and Boot sections. Both sections have dedicated Lock Bits for setting restrictions on write or read/write operations. The Store Program Memory (SPM) instruction must reside in the Boot Section when used to write to the Flash memory.

A third section inside the Application section is referred to as the Application Table section which has separate Lock bits for storage of write or read/write protection. The Application Table section can be used for storing non-volatile data or application software.

#### Figure 7-1. Flash Program Memory (Hexadecimal address)

|       |   |      | Word | d Addres | S |      |                                                   |

|-------|---|------|------|----------|---|------|---------------------------------------------------|

|       |   |      |      |          |   | 0    | Application Section<br>(128 KB/64 KB/32 KB/16 KB) |

|       |   |      |      |          |   |      |                                                   |

| EFFF  | / | 77FF | /    | 37FF     | / | 17FF |                                                   |

| F000  | / | 7800 | /    | 3800     | / | 1800 | Application Table Section                         |

| FFFF  | / | 7FFF | /    | 3FFF     | / | 1FFF | (4 KB/4 KB/4 KB/4 KB)                             |

| 10000 | / | 8000 | /    | 4000     | / | 2000 | Boot Section                                      |

| 10FFF | / | 87FF | /    | 47FF     | / | 27FF | (8 KB/4 KB/4 KB/4 KB)                             |

The Application Table Section and Boot Section can also be used for general application software.

# 7.4 Data Memory

The Data Memory consist of the I/O Memory, EEPROM and SRAM memories, all within one linear address space, see Figure 7-2 on page 12. To simplify development, the memory map for all devices in the family is identical and with empty, reserved memory space for smaller devices.

Figure 7-2. Data Memory Map (Hexadecimal address)

| Byte Address | ATxmega64A4   | Byte Address | ATxmega32A4   | Byte Address | ATxmega16A4   |

|--------------|---------------|--------------|---------------|--------------|---------------|

| 0            | I/O Registers | 0            | I/O Registers | 0            | I/O Registers |

| FFF          | (4 KB)        | FFF          | (4 KB)        | FFF          | (4 KB)        |

| 1000         | EEPROM        | 1000         | EEPROM        | 1000         | EEPROM        |

| 17FF         | (2 KB)        | 13FF         | (1 KB)        | 13FF         | (1 KB)        |

|              | RESERVED      |              | RESERVED      |              | RESERVED      |

| 2000         | Internal SRAM | 2000         | Internal SRAM | 2000         | Internal SRAM |

| 2FFF         | (4 KB)        | 2FFF         | (4 KB)        | 27FF         | (2 KB)        |

| Byte Address | ATxmega128A4  |

|--------------|---------------|

| 0            | I/O Registers |

| FFF          | (4 KB)        |

| 1000         | EEPROM        |

| 17FF         | (2 KB)        |

|              | RESERVED      |

| 2000         | Internal SRAM |

| 3FFF         | (8 KB)        |

#### 7.4.1 I/O Memory

All peripherals and modules are addressable through I/O memory locations in the data memory space. All I/O memory locations can be accessed by the Load (LD/LDS/LDD) and Store (ST/STS/STD) instructions, transferring data between the 32 general purpose registers in the CPU and the I/O Memory.

The IN and OUT instructions can address I/O memory locations in the range 0x00 - 0x3F directly.

I/O registers within the address range 0x00 - 0x1F are directly bit-accessible using the SBI and CBI instructions. The value of single bits can be checked by using the SBIS and SBIC instructions on these registers.

The I/O memory address for all peripherals and modules in XMEGA A4 is shown in the "Peripheral Module Address Map" on page 53.

#### 7.4.2 SRAM Data Memory

The XMEGA A4 devices have internal SRAM memory for data storage.

#### 7.4.3 EEPROM Data Memory

The XMEGA A4 devices have internal EEPROM memory for non-volatile data storage. It is addressable either in a separate data space or it can be memory mapped into the normal data memory space. The EEPROM memory supports both byte and page access.

### 7.5 Production Signature Row

The Production Signature Row is a separate memory section for factory programmed data. It contains calibration data for functions such as oscillators and analog modules.

The production signature row also contains a device ID that identify each microcontroller device type, and a serial number that is unique for each manufactured device. The device ID for the available XMEGA A4 devices is shown in Table 7-1 on page 13. The serial number consist of the production LOT number, wafer number, and wafer coordinates for the device.

The production signature row can not be written or erased, but it can be read from both application software and external programming.

| Device       | Device ID bytes |        |        |  |  |

|--------------|-----------------|--------|--------|--|--|

|              | Byte 2          | Byte 1 | Byte 0 |  |  |

| ATxmega16A4  | 41              | 94     | 1E     |  |  |

| ATxmega32A4  | 41              | 95     | 1E     |  |  |

| ATxmega64A4  | 46              | 96     | 1E     |  |  |

| ATxmega128A4 | 46              | 97     | 1E     |  |  |

Table 7-1.

Device ID bytes for XMEGA A4 devices.

### 7.6 User Signature Row

The User Signature Row is a separate memory section that is fully accessible (read and write) from application software and external programming. The user signature row is one flash page in size, and is meant for static user parameter storage, such as calibration data, custom serial numbers or identification numbers, random number seeds etc. This section is not erased by Chip Erase commands that erase the Flash, and requires a dedicated erase command. This ensures parameter storage during multiple program/erase session and on-chip debug sessions.

# 7.7 Flash and EEPROM Page Size

The Flash Program Memory and EEPROM data memory are organized in pages. The pages are word accessible for the Flash and byte accessible for the EEPROM.

Table 7-2 on page 14 shows the Flash Program Memory organization. Flash write and erase operations are performed on one page at a time, while reading the Flash is done one byte at a time. For Flash access the Z-pointer (Z[m:n]) is used for addressing. The most significant bits in the address (FPAGE) give the page number and the least significant address bits (FWORD) give the word in the page.

| Devices      | Flash         | Page Size | FWORD  | FPAGE   | Appli  | cation      | Bo   | oot         |

|--------------|---------------|-----------|--------|---------|--------|-------------|------|-------------|

|              | Size          | (words)   |        |         | Size   | No of Pages | Size | No of Pages |

| ATxmega16A4  | 16 KB + 4 KB  | 128       | Z[6:0] | Z[13:7] | 16 KB  | 64          | 4 KB | 16          |

| ATxmega32A4  | 32 KB + 4 KB  | 128       | Z[6:0] | Z[14:7] | 32 KB  | 128         | 4 KB | 16          |

| ATxmega64A4  | 64 KB + 4 KB  | 128       | Z[6:0] | Z[15:7] | 64 KB  | 128         | 4 KB | 16          |

| ATxmega128A4 | 128 KB + 8 KB | 256       | Z[7:0] | Z[16:8] | 128 KB | 256         | 8 KB | 16          |

| Table 7-2. | Number of words and Pages in the Flash. |

|------------|-----------------------------------------|

|------------|-----------------------------------------|

Table 7-3 on page 14 shows EEPROM memory organization for the XMEGA A4 devices. EEPROM write and erase operations can be performed one page or one byte at a time, while reading the EEPROM is done one byte at a time. For EEPROM access the NVM Address Register (ADDR[m:n]) is used for addressing. The most significant bits in the address (E2PAGE) give the page number and the least significant address bits (E2BYTE) give the byte in the page.

| Devices      | EEPROM | Page Size | E2BYTE    | E2PAGE     | No of Pages |

|--------------|--------|-----------|-----------|------------|-------------|

|              | Size   | (Bytes)   |           |            |             |

| ATxmega16A4  | 1 KB   | 32        | ADDR[4:0] | ADDR[10:5] | 32          |

| ATxmega32A4  | 1 KB   | 32        | ADDR[4:0] | ADDR[10:5] | 32          |

| ATxmega64A4  | 2 KB   | 32        | ADDR[4:0] | ADDR[10:5] | 64          |

| ATxmega128A4 | 2 KB   | 32        | ADDR[4:0] | ADDR[10:5] | 64          |

#### **Table 7-3.**Number of Bytes and Pages in the EEPROM.

# 8. DMAC - Direct Memory Access Controller

### 8.1 Features

- Allows High-speed data transfer

- From memory to peripheral

- From memory to memory

- From peripheral to memory

- From peripheral to peripheral

- 4 Channels

- From 1 byte and up to 16 M bytes transfers in a single transaction

- Multiple addressing modes for source and destination address

- Increment

- Decrement

- Static

- 1, 2, 4, or 8 bytes Burst Transfers

- Programmable priority between channels

### 8.2 Overview

The XMEGA A4 has a Direct Memory Access (DMA) Controller to move data between memories and peripherals in the data space. The DMA controller uses the same data bus as the CPU to transfer data.

It has 4 channels that can be configured independently. Each DMA channel can perform data transfers in blocks of configurable size from 1 to 64K bytes. A repeat counter can be used to repeat each block transfer for single transactions up to 16M bytes. Each DMA channel can be configured to access the source and destination memory address with incrementing, decrementing or static addressing. The addressing is independent for source and destination address. When the transaction is complete the original source and destination address can automatically be reloaded to be ready for the next transaction.

The DMAC can access all the peripherals through their I/O memory registers, and the DMA may be used for automatic transfer of data to/from communication modules, as well as automatic data retrieval from ADC conversions, data transfer to DAC conversions, or data transfer to or from port pins. A wide range of transfer triggers is available from the peripherals, Event System and software. Each DMA channel has different transfer triggers.

To allow for continuous transfer, two channels can be interlinked so that the second takes over the transfer when the first is finished and vice versa.

The DMA controller can read from memory mapped EEPROM, but it cannot write to the EEPROM or access the Flash.

# 9. Event System

#### 9.1 Features

- Inter-peripheral communication and signalling with minimum latency

- CPU and DMA independent operation

- 8 Event Channels allow for up to 8 signals to be routed at the same time

- Events can be generated by

- TImer/Counters (TCxn)

- Real Time Counter (RTC)

- Analog to Digital Converters (ADCx)

- Analog Comparators (ACx)

- Ports (PORTx)

- System Clock (Clk<sub>SYS</sub>)

- Software (CPU)

- Events can be used by

- TImer/Counters (TCxn)

- Analog to Digital Converters (ADCx)

- Digital to Analog Converters (DACx)

- Ports (PORTx)

- DMA Controller (DMAC)

- IR Communication Module (IRCOM)

- The same event can be used by multiple peripherals for synchronized timing

- Advanced Features

- Manual Event Generation from software (CPU)

- Quadrature Decoding

- Digital Filtering

- Functions in Active and Idle mode

#### 9.2 Overview

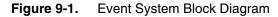

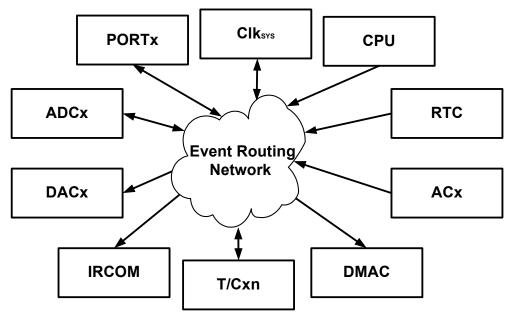

The Event System is a set of features for inter-peripheral communication. It enables the possibility for a change of state in one peripheral to automatically trigger actions in one or more peripherals. Whose changes in a peripheral that will trigger actions in other peripherals are configurable by software. It is a simple, but powerful system as it allows for autonomous control of peripherals without any use of interrupts, CPU or DMA resources.

The indication of a change in a peripheral is referred to as an event, and is usually the same as the interrupt conditions for that peripheral. Events are passed between peripherals using a dedicated routing network called the Event Routing Network. Figure 9-1 on page 17 shows a basic block diagram of the Event System with the Event Routing Network and the peripherals to which it is connected. This highly flexible system can be used for simple routing of signals, pin functions or for sequencing of events.

The maximum latency is two CPU clock cycles from when an event is generated in one peripheral, until the actions are triggered in one or more other peripherals.

The Event System is functional in both Active and Idle modes.

The Event Routing Network can directly connect together ADCs, DACs, Analog Comparators (ACx), I/O ports (PORTx), the Real-time Counter (RTC), Timer/Counters (T/C) and the IR Communication Module (IRCOM). Events can also be generated from software (CPU).

All events from all peripherals are always routed into the Event Routing Network. This consist of eight multiplexers where each can be configured in software to select which event to be routed into that event channel. All eight event channels are connected to the peripherals that can use events, and each of these peripherals can be configured to use events from one or more event channels to automatically trigger a software selectable action.

# 10. System Clock and Clock options

# 10.1 Features

- Fast start-up time

- Safe run-time clock switching

- Internal Oscillators:

- 32 MHz run-time calibrated RC oscillator

- 2 MHz run-time calibrated RC oscillator

- 32.768 kHz calibrated RC oscillator

- 32 kHz Ultra Low Power (ULP) oscillator with 1 kHz ouput

- External clock options

- 0.4 16 MHz Crystal Oscillator

- 32 kHz Crystal Oscillator

- External clock

- PLL with internal and external clock options with 1 to 31x multiplication

- Clock Prescalers with 1 to 2048x division

- Fast peripheral clock running at 2 and 4 times the CPU clock speed

- Automatic Run-Time Calibration of internal oscillators

- Crystal Oscillator failure detection

### 10.2 Overview

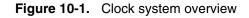

XMEGA A4 has an advanced clock system, supporting a large number of clock sources. It incorporates both integrated oscillators, external crystal oscillators and resonators. A high frequency Phase Locked Loop (PLL) and clock prescalers can be controlled from software to generate a wide range of clock frequencies from the clock source input.

It is possible to switch between clock sources from software during run-time. After reset the device will always start up running from the 2 Mhz internal oscillator.

A calibration feature is available, and can be used for automatic run-time calibration of the internal 2 MHz and 32 MHz oscillators. This reduce frequency drift over voltage and temperature.

A Crystal Oscillator Failure Monitor can be enabled to issue a Non-Maskable Interrupt and switch to internal oscillator if the external oscillator fails. Figure 10-1 on page 19 shows the principal clock system in XMEGA A4.

Each clock source is briefly described in the following sub-sections.

# 10.3 Clock Options

#### 10.3.1 32 kHz Ultra Low Power Internal Oscillator

The 32 kHz Ultra Low Power (ULP) Internal Oscillator is a very low power consumption clock source. It is used for the Watchdog Timer, Brown-Out Detection and as an asynchronous clock source for the Real Time Counter. This oscillator cannot be used as the system clock source, and it cannot be directly controlled from software.

#### 10.3.2 32.768 kHz Calibrated Internal Oscillator

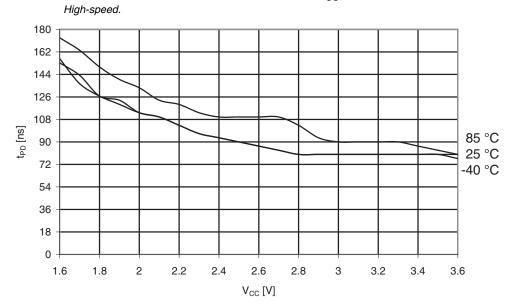

The 32.768 kHz Calibrated Internal Oscillator is a high accuracy clock source that can be used as the system clock source or as an asynchronous clock source for the Real Time Counter. It is calibrated during production to provide a default frequency which is close to its nominal frequency.

#### 10.3.3 32.768 kHz Crystal Oscillator

The 32.768 kHz Crystal Oscillator is a low power driver for an external watch crystal. It can be used as system clock source or as asynchronous clock source for the Real Time Counter.

#### 10.3.4 0.4 - 16 MHz Crystal Oscillator

The 0.4 - 16 MHz Crystal Oscillator is a driver intended for driving both external resonators and crystals ranging from 400 kHz to 16 MHz.

#### 10.3.5 2 MHz Run-time Calibrated Internal Oscillator

The 2 MHz Run-time Calibrated Internal Oscillator is a high frequency oscillator. It is calibrated during production to provide a default frequency which is close to its nominal frequency. The oscillator can use the 32 kHz Calibrated Internal Oscillator or the 32 kHz Crystal Oscillator as a source for calibrating the frequency run-time to compensate for temperature and voltage drift hereby optimizing the accuracy of the oscillator.

#### 10.3.6 32 MHz Run-time Calibrated Internal Oscillator

The 32 MHz Run-time Calibrated Internal Oscillator is a high frequency oscillator. It is calibrated during production to provide a default frequency which is close to its nominal frequency. The oscillator can use the 32 kHz Calibrated Internal Oscillator or the 32 kHz Crystal Oscillator as a source for calibrating the frequency run-time to compensate for temperature and voltage drift hereby optimizing the accuracy of the oscillator.

#### 10.3.7 External Clock input

The external clock input gives the possibility to connect a clock from an external source.

#### 10.3.8 PLL with Multiplication factor 1 - 31x

The PLL provides the possibility of multiplying a frequency by any number from 1 to 31. In combination with the prescalers, this gives a wide range of output frequencies from all clock sources.

# **11. Power Management and Sleep Modes**

# 11.1 Features

- 5 sleep modes

- Idle

- Power-down

- Power-save

- Standby

- Extended standby

- Power Reduction registers to disable clocks to unused peripherals

### 11.2 Overview

The XMEGA A4 provides various sleep modes tailored to reduce power consumption to a minimum. All sleep modes are available and can be entered from Active mode. In Active mode the CPU is executing application code. The application code decides when and what sleep mode to enter. Interrupts from enabled peripherals and all enabled reset sources can restore the microcontroller from sleep to Active mode.

In addition, Power Reduction registers provide a method to stop the clock to individual peripherals from software. When this is done, the current state of the peripheral is frozen and there is no power consumption from that peripheral. This reduces the power consumption in Active mode and Idle sleep mode.

# 11.3 Sleep Modes

#### 11.3.1 Idle Mode

In Idle mode the CPU and Non-Volatile Memory are stopped, but all peripherals including the Interrupt Controller, Event System and DMA Controller are kept running. Interrupt requests from all enabled interrupts will wake the device.

#### 11.3.2 Power-down Mode

In Power-down mode all system clock sources, and the asynchronous Real Time Counter (RTC) clock source, are stopped. This allows operation of asynchronous modules only. The only interrupts that can wake up the MCU are the Two Wire Interface address match interrupts, and asynchronous port interrupts, e.g pin change.

#### 11.3.3 Power-save Mode

Power-save mode is identical to Power-down, with one exception: If the RTC is enabled, it will keep running during sleep and the device can also wake up from RTC interrupts.

#### 11.3.4 Standby Mode

Standby mode is identical to Power-down with the exception that all enabled system clock sources are kept running, while the CPU, Peripheral and RTC clocks are stopped. This reduces the wake-up time when external crystals or resonators are used.

#### 11.3.5 Extended Standby Mode

Extended Standby mode is identical to Power-save mode with the exception that all enabled system clock sources are kept running while the CPU and Peripheral clocks are stopped. This reduces the wake-up time when external crystals or resonators are used.

# 12. System Control and Reset

# 12.1 Features

- Multiple reset sources for safe operation and device reset

- Power-On Reset

- External Reset

- Watchdog Reset

- The Watchdog Timer runs from separate, dedicated oscillator

- Brown-Out Reset

- Accurate, programmable Brown-Out levels

- PDI reset

- Software reset

- Asynchronous reset

- No running clock in the device is required for reset

- Reset status register

# 12.2 Resetting the AVR

During reset, all I/O registers are set to their initial values. The SRAM content is not reset. Application execution starts from the Reset Vector. The instruction placed at the Reset Vector should be an Absolute Jump (JMP) instruction to the reset handling routine. By default the Reset Vector address is the lowest Flash program memory address, '0', but it is possible to move the Reset Vector to the first address in the Boot Section.

The I/O ports of the AVR are immediately tri-stated when a reset source goes active.

The reset functionality is asynchronous, so no running clock is required to reset the device.

After the device is reset, the reset source can be determined by the application by reading the Reset Status Register.

# 12.3 Reset Sources

12.3.1 Power-On Reset

The MCU is reset when the supply voltage VCC is below the Power-on Reset threshold voltage.

#### 12.3.2 External Reset

The MCU is reset when a low level is present on the RESET pin.

#### 12.3.3 Watchdog Reset

The MCU is reset when the Watchdog Timer period expires and the Watchdog Reset is enabled. The Watchdog Timer runs from a dedicated oscillator independent of the System Clock. For more details see "WDT - Watchdog Timer" on page 24.

#### 12.3.4 Brown-Out Reset

The MCU is reset when the supply voltage VCC is below the Brown-Out Reset threshold voltage and the Brown-out Detector is enabled. The Brown-out threshold voltage is programmable.

#### 12.3.5 PDI reset

The MCU can be reset through the Program and Debug Interface (PDI).

#### 12.3.6 Software reset

The MCU can be reset by the CPU writing to a special I/O register through a timed sequence.

# 13. WDT - Watchdog Timer

#### 13.1 Features

- 11 selectable timeout periods, from 8 ms to 8s.

- Two operation modes

- Standard mode

- Window mode

- Runs from the 1 kHz output of the 32 kHz Ultra Low Power oscillator

- Configuration lock to prevent unwanted changes

#### 13.2 Overview

The XMEGA A4 has a Watchdog Timer (WDT). The WDT will run continuously when turned on and if the Watchdog Timer is not reset within a software configurable time-out period, the micro-controller will be reset. The Watchdog Reset (WDR) instruction must be run by software to reset the WDT, and prevent microcontroller reset.

The WDT has a Window mode. In this mode the WDR instruction must be run within a specified period called a window. Application software can set the minimum and maximum limits for this window. If the WDR instruction is not executed inside the window limits, the microcontroller will be reset.

A protection mechanism using a timed write sequence is implemented in order to prevent unwanted enabling, disabling or change of WDT settings.

For maximum safety, the WDT also has an Always-on mode. This mode is enabled by programming a fuse. In Always-on mode, application software can not disable the WDT.

# 14. PMIC - Programmable Multi-level Interrupt Controller

### 14.1 Features

- Separate interrupt vector for each interrupt

- Short, predictable interrupt response time

- Programmable Multi-level Interrupt Controller

- 3 programmable interrupt levels

- Selectable priority scheme within low level interrupts (round-robin or fixed)

- Non-Maskable Interrupts (NMI)

- Interrupt vectors can be moved to the start of the Boot Section

#### 14.2 Overview

XMEGA A4 has a Programmable Multi-level Interrupt Controller (PMIC). All peripherals can define three different priority levels for interrupts; high, medium or low. Medium level interrupts may interrupt low level interrupt service routines. High level interrupts may interrupt both lowand medium level interrupt service routines. Low level interrupts have an optional round robin scheme to make sure all interrupts are serviced within a certain amount of time.

The built in oscillator failure detection mechanism can issue a Non-Maskable Interrupt (NMI).

### 14.3 Interrupt vectors

When an interrupt is serviced, the program counter will jump to the interrupt vector address. The interrupt vector is the sum of the peripheral's base interrupt address and the offset address for specific interrupts in each peripheral. The base addresses for the XMEGA A4 devices are shown in Table 14-1. Offset addresses for each interrupt available in the peripheral are described for each peripheral in the XMEGA A manual. For peripherals or modules that have only one interrupt, the interrupt vector is shown in Table 14-1. The program address is the word address.

| Program Address<br>(Base Address) | Source           | Interrupt Description                             |

|-----------------------------------|------------------|---------------------------------------------------|

| 0x000                             | RESET            |                                                   |

| 0x002                             | OSCF_INT_vect    | Crystal Oscillator Failure Interrupt vector (NMI) |

| 0x004                             | PORTC_INT_base   | Port C Interrupt base                             |

| 0x008                             | PORTR_INT_base   | Port R Interrupt base                             |

| 0x00C                             | DMA_INT_base     | DMA Controller Interrupt base                     |

| 0x014                             | RTC_INT_base     | Real Time Counter Interrupt base                  |

| 0x018                             | TWIC_INT_base    | Two-Wire Interface on Port C Interrupt base       |

| 0x01C                             | TCC0_INT_base    | Timer/Counter 0 on port C Interrupt base          |

| 0x028                             | TCC1_INT_base    | Timer/Counter 1 on port C Interrupt base          |

| 0x030                             | SPIC_INT_vect    | SPI on port C Interrupt vector                    |

| 0x032                             | USARTC0_INT_base | USART 0 on port C Interrupt base                  |

| 0x038                             | USARTC1_INT_base | USART 1 on port C Interrupt base                  |

| 0x03E                             | AES_INT_vect     | AES Interrupt vector                              |

Table 14-1.

Reset and Interrupt Vectors

| Program Address<br>(Base Address) | Source           | Interrupt Description                                |

|-----------------------------------|------------------|------------------------------------------------------|

| 0x040                             | NVM_INT_base     | Non-Volatile Memory Interrupt base                   |

| 0x044                             | PORTB_INT_base   | Port B Interrupt base                                |

| 0x056                             | PORTE_INT_base   | Port E Interrupt base                                |

| 0x05A                             | TWIE_INT_base    | Two-Wire Interface on Port E Interrupt base          |

| 0x05E                             | TCE0_INT_base    | Timer/Counter 0 on port E Interrupt base             |

| 0x06A                             | TCE1_INT_base    | Timer/Counter 1 on port E Interrupt base             |

| 0x074                             | USARTE0_INT_base | USART 0 on port E Interrupt base                     |

| 0x080                             | PORTD_INT_base   | Port D Interrupt base                                |

| 0x084                             | PORTA_INT_base   | Port A Interrupt base                                |

| 0x088                             | ACA_INT_base     | Analog Comparator on Port A Interrupt base           |

| 0x08E                             | ADCA_INT_base    | Analog to Digital Converter on Port A Interrupt base |

| 0x09A                             | TCD0_INT_base    | Timer/Counter 0 on port D Interrupt base             |

| 0x0A6                             | TCD1_INT_base    | Timer/Counter 1 on port D Interrupt base             |

| 0x0AE                             | SPID_INT_vector  | SPI on port D Interrupt vector                       |

| 0x0B0                             | USARTD0_INT_base | USART 0 on port D Interrupt base                     |

| 0x0B6                             | USARTD1_INT_base | USART 1 on port D Interrupt base                     |

# Table 14-1. Reset and Interrupt Vectors (Continued)

# 15. I/O Ports

# 15.1 Features

- Selectable input and output configuration for each pin individually

- Flexible pin configuration through dedicated Pin Configuration Register

- · Synchronous and/or asynchronous input sensing with port interrupts and events

- Sense both edges

- Sense rising edges

- Sense falling edges

- Sense low level

- · Asynchronous wake-up from all input sensing configurations

- Two port interrupts with flexible pin masking

- Highly configurable output driver and pull settings:

- Totem-pole

- Pull-up/-down

- Wired-AND

- Wired-OR

- Bus-keeper

- Inverted I/O

- Optional Slew rate control

- Configuration of multiple pins in a single operation

- Read-Modify-Write (RMW) support

- Toggle/clear/set registers for Output and Direction registers

- Clock output on port pin

- Event Channel 7 output on port pin

- Mapping of port registers (virtual ports) into bit accessible I/O memory space

# 15.2 Overview

The XMEGA A4 devices have flexible General Purpose I/O Ports. A port consists of up to 8 pins, ranging from pin 0 to pin 7. The ports implement several functions, including synchronous/asynchronous input sensing, pin change interrupts and configurable output settings. All functions are individual per pin, but several pins may be configured in a single operation.

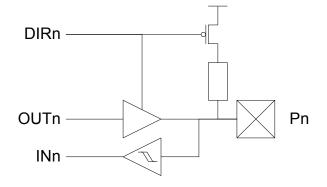

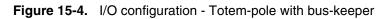

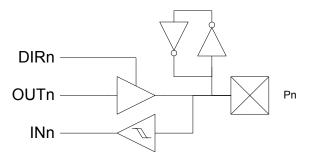

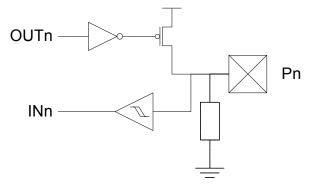

# 15.3 I/O configuration

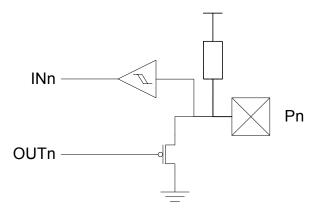

All port pins (Pn) have programmable output configuration. In addition, all port pins have an inverted I/O function. For an input, this means inverting the signal between the port pin and the pin register. For an output, this means inverting the output signal between the port register and the port pin. The inverted I/O function can be used also when the pin is used for alternate functions.

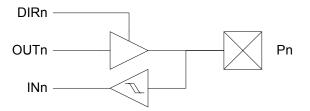

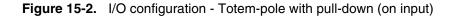

#### 15.3.1 Push-pull

#### 15.3.2 Pull-down

#### 15.3.3 Pull-up

#### 15.3.4 Bus-keeper

The bus-keeper's weak output produces the same logical level as the last output level. It acts as a pull-up if the last level was '1', and pull-down if the last level was '0'.

15.3.5 Others

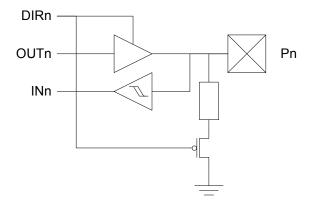

Figure 15-5. Output configuration - Wired-OR with optional pull-down

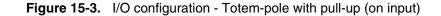

Figure 15-6. I/O configuration - Wired-AND with optional pull-up

# 15.4 Input sensing

- Sense both edges

- Sense rising edges

- Sense falling edges

- Sense low level

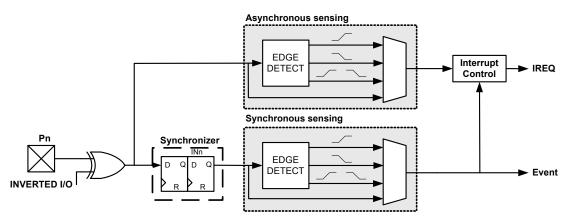

Input sensing is synchronous or asynchronous depending on the enabled clock for the ports, and the configuration is shown in Figure 15-7 on page 30.

Figure 15-7. Input sensing system overview

When a pin is configured with inverted I/O, the pin value is inverted before the input sensing.

#### 15.5 Port Interrupt

Each port has two interrupts with separate priority and interrupt vector. All pins on the port can be individually selected as source for each of the interrupts. The interrupts are then triggered according to the input sense configuration for each pin configured as source for the interrupt.

#### **15.6 Alternate Port Functions**

In addition to the input/output functions on all port pins, most pins have alternate functions. This means that other modules or peripherals connected to the port can use the port pins for their functions, such as communication or pulse-width modulation. "Pinout and Pin Functions" on page 49 shows which modules on peripherals that enable alternate functions on a pin, and which alternate function is available on a pin.

# 16. T/C - 16-bit Timer/Counter

# 16.1 Features

- Five 16-bit Timer/Counters

- Three Timer/Counters of type 0

- Two Timer/Counters of type 1

- Three Compare or Capture (CC) Channels in Timer/Counter 0

- Two Compare or Capture (CC) Channels in Timer/Counter 1

- Double Buffered Timer Period Setting

- Double Buffered Compare or Capture Channels

- Waveform Generation:

- Single Slope Pulse Width Modulation

- Dual Slope Pulse Width Modulation

- Frequency Generation

- Input Capture:

- Input Capture with Noise Cancelling

- Frequency capture

- Pulse width capture

- 32-bit input capture

- Event Counter with Direction Control

- Timer Overflow and Timer Error Interrupts and Events

- One Compare Match or Capture Interrupt and Event per CC Channel

- Supports DMA Operation

- Hi-Resolution Extension (Hi-Res)

- Advanced Waveform Extension (AWEX)

### 16.2 Overview

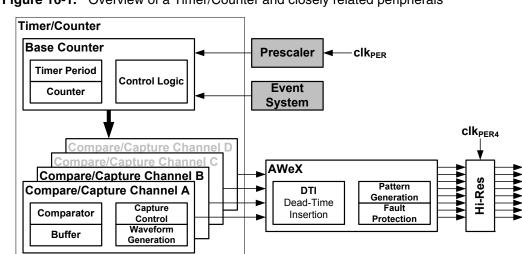

XMEGA A4 has five Timer/Counters, three Timer/Counter 0 and two Timer/Counter 1. The difference between them is that Timer/Counter 0 has four Compare/Capture channels, while Timer/Counter 1 has two Compare/Capture channels.

The Timer/Counters (T/C) are 16-bit and can count any clock, event or external input in the microcontroller. A programmable prescaler is available to get a useful T/C resolution. Updates of Timer and Compare registers are double buffered to ensure glitch free operation. Single slope PWM, dual slope PWM and frequency generation waveforms can be generated using the Compare Channels.

Through the Event System, any input pin or event in the microcontroller can be used to trigger input capture, hence no dedicated pins are required for this. The input capture has a noise canceller to avoid incorrect capture of the T/C, and can be used to do frequency and pulse width measurements.

A wide range of interrupt or event sources are available, including T/C Overflow, Compare match and Capture for each Compare/Capture channel in the T/C.

PORTC and PORTD each has one Timer/Counter 0 and one Timer/Counter1. PORTE has one Timer/Conter0. Notation of these are TCC0 (Time/Counter C0), TCC1, TCD0, TCD1 and TCE0, respectively.

PORT

Figure 16-1. Overview of a Timer/Counter and closely related peripherals

The Hi-Resolution Extension can be enabled to increase the waveform generation resolution by 2 bits (4x). This is available for all Timer/Counters. See "Hi-Res - High Resolution Extension" on page 34 for more details.

The Advanced Waveform Extension can be enabled to provide extra and more advanced feature for the Timer/Counter. This is only available for Timer/Counter 0. See "AWEX - Advanced Waveform Extension" on page 33 for more details.

# 17. AWEX - Advanced Waveform Extension

# 17.1 Features

- Output with complementary output from each Capture channel

- Four Dead Time Insertion (DTI) Units, one for each Capture channel

- 8-bit DTI Resolution

- Separate High and Low Side Dead-Time Setting

- Double Buffered Dead-Time

- Event Controlled Fault Protection

- Single Channel Multiple Output Operation (for BLDC motor control)

- Double Buffered Pattern Generation

# 17.2 Overview

The Advanced Waveform Extension (AWEX) provides extra features to the Timer/Counter in Waveform Generation (WG) modes. The AWEX enables easy and safe implementation of for example, advanced motor control (AC, BLDC, SR, and Stepper) and power control applications.

Any WG output from a Timer/Counter 0 is split into a complimentary pair of outputs when any AWEX feature is enabled. These output pairs go through a Dead-Time Insertion (DTI) unit that enables generation of the non-inverted Low Side (LS) and inverted High Side (HS) of the WG output with dead time insertion between LS and HS switching. The DTI output will override the normal port value according to the port override setting. Optionally the final output can be inverted by using the invert I/O setting for the port pin.

The Pattern Generation unit can be used to generate a synchronized bit pattern on the port it is connected to. In addition, the waveform generator output from Compare Channel A can be distributed to, and override all port pins. When the Pattern Generator unit is enabled, the DTI unit is bypassed.

The Fault Protection unit is connected to the Event System. This enables any event to trigger a fault condition that will disable the AWEX output. Several event channels can be used to trigger fault on several different conditions.

The AWEX is available for TCC0. The notation of this is AWEXC.

# 18. Hi-Res - High Resolution Extension

### 18.1 Features

- Increases Waveform Generator resolution by 2-bits (4x)

- Supports Frequency, single- and dual-slope PWM operation

- Supports the AWEX when this is enabled and used for the same Timer/Counter

#### 18.2 Overview

The Hi-Resolution (Hi-Res) Extension is able to increase the resolution of the waveform generation output by a factor of 4. When enabled for a Timer/Counter, the Fast Peripheral clock running at four times the CPU clock speed will be as input to the Timer/Counter.

The High Resolution Extension can also be used when an AWEX is enabled and used with a Timer/Counter.

XMEGA A4 devices have three Hi-Res Extensions that each can be enabled for each Timer/Counters pair on PORTC, PORTD and PORTE. The notation of these are HIRESC, HIRESD and HIRESE, respectively.

# 19. RTC - 16-bit Real-Time Counter

# 19.1 Features

- 16-bit Timer

- Flexible Tick resolution ranging from 1 Hz to 32.768 kHz

- One Compare register

- One Period register

- Clear timer on Overflow or Compare Match

- Overflow or Compare Match event and interrupt generation

# 19.2 Overview

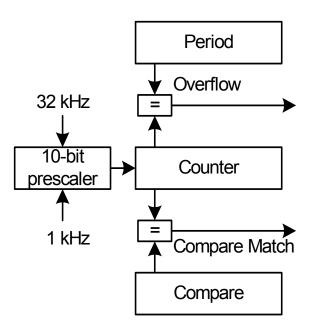

The XMEGA A4 includes a 16-bit Real-time Counter (RTC). The RTC can be clocked from an accurate 32.768 kHz Crystal Oscillator, the 32.768 kHz Calibrated Internal Oscillator, or from the 32 kHz Ultra Low Power Internal Oscillator. The RTC includes both a Period and a Compare register. For details, see Figure 19-1.

A wide range of Resolution and Time-out periods can be configured using the RTC. With a maximum resolution of  $30.5 \ \mu$ s, time-out periods range up to 2000 seconds. With a resolution of 1 second, the maximum time-out period is over 18 hours (65536 seconds).

Figure 19-1. Real Time Counter overview

# 20. TWI - Two-Wire Interface

### 20.1 Features

- Two Identical TWI peripherals

- Simple yet Powerful and Flexible Communication Interface

- Both Master and Slave Operation Supported

- Device can Operate as Transmitter or Receiver

- 7-bit Address Space Allows up to 128 Different Slave Addresses

- Multi-master Arbitration Support

- Up to 400 kHz Data Transfer Speed

- Slew-rate Limited Output Drivers

- Noise Suppression Circuitry Rejects Spikes on Bus Lines

- Fully Programmable Slave Address with General Call Support

- Address Recognition Causes Wake-up when in Sleep Mode

- I<sup>2</sup>C and System Management Bus (SMBus) compatible

### 20.2 Overview

The Two-Wire Interface (TWI) is a bi-directional wired-AND bus with only two lines, the clock (SCL) line and the data (SDA) line. The protocol makes it possible to interconnect up to 128 individually addressable devices. Since it is a multi-master bus, one or more devices capable of taking control of the bus can be connected.

The only external hardware needed to implement the bus is a single pull-up resistor for each of the TWI bus lines. Mechanisms for resolving bus contention are inherent in the TWI protocol.

PORTC and PORTE each has one TWI. Notation of these peripherals are TWIC and TWIE, respectively.

# 21. SPI - Serial Peripheral Interface

### 21.1 Features

- Two Identical SPI peripherals

- Full-duplex, Three-wire Synchronous Data Transfer

- Master or Slave Operation

- LSB First or MSB First Data Transfer

- Seven Programmable Bit Rates

- End of Transmission Interrupt Flag

- Write Collision Flag Protection

- Wake-up from Idle Mode

- Double Speed (CK/2) Master SPI Mode

# 21.2 Overview

The Serial Peripheral Interface (SPI) allows high-speed full-duplex, synchronous data transfer between different devices. Devices can communicate using a master-slave scheme, and data is transferred both to and from the devices simultaneously.

PORTC and PORTD each has one SPI. Notation of these peripherals are SPIC and SPID, respectively.

# 22. USART

## 22.1 Features

- Five Identical USART peripherals

- Full Duplex Operation (Independent Serial Receive and Transmit Registers)

- Asynchronous or Synchronous Operation

- Master or Slave Clocked Synchronous Operation

- High-resolution Arithmetic Baud Rate Generator

- Supports Serial Frames with 5, 6, 7, 8, or 9 Data Bits and 1 or 2 Stop Bits

- Odd or Even Parity Generation and Parity Check Supported by Hardware

- Data OverRun Detection

- Framing Error Detection

- Noise Filtering Includes False Start Bit Detection and Digital Low Pass Filter

- Three Separate Interrupts on TX Complete, TX Data Register Empty and RX Complete

- Multi-processor Communication Mode

- Double Speed Asynchronous Communication Mode

- Master SPI mode for SPI communication

- IrDA support through the IRCOM module

# 22.2 Overview

The Universal Synchronous and Asynchronous serial Receiver and Transmitter (USART) is a highly flexible serial communication module. The USART supports full duplex communication, and both asynchronous and clocked synchronous operation. The USART can also be set in Master SPI mode to be used for SPI communication.

Communication is frame based, and the frame format can be customized to support a wide range of standards. The USART is buffered in both direction, enabling continued data transmission without any delay between frames. There are separate interrupt vectors for receive and transmit complete, enabling fully interrupt driven communication. Frame error and buffer overflow are detected in hardware and indicated with separate status flags. Even or odd parity generation and parity check can also be enabled.

One USART can use the IRCOM module to support IrDA 1.4 physical compliant pulse modulation and demodulation for baud rates up to 115.2 kbps.

PORTC and PORTD each has two USARTs. PORTE has one USART. Notation of these peripherals are USARTC0, USARTC1, USARTD0, USARTD1 and USARTE0, respectively.

# 23. IRCOM - IR Communication Module

### 23.1 Features

- Pulse modulation/demodulation for infrared communication

- Compatible to IrDA 1.4 physical for baud rates up to 115.2 kbps

- Selectable pulse modulation scheme

- 3/16 of baud rate period

- Fixed pulse period, 8-bit programmable

- Pulse modulation disabled

- Built in filtering

- · Can be connected to and used by one USART at a time

### 23.2 Overview

XMEGA contains an Infrared Communication Module (IRCOM) for IrDA communication with baud rates up to 115.2 kbps. This supports three modulation schemes: 3/16 of baud rate period, fixed programmable pulse time based on the Peripheral Clock speed, or pulse modulation disabled. There is one IRCOM available which can be connected to any USART to enable infrared pulse coding/decoding for that USART.

# 24. Crypto Engine

## 24.1 Features

- Data Encryption Standard (DES) CPU instruction

- Advanced Encryption Standard (AES) Crypto module

- DES Instruction

- Encryption and Decryption

- Single-cycle DES instruction

- Encryption/Decryption in 16 clock cycles per 8-byte block

- AES Crypto Module

- Encryption and Decryption

- Support 128-bit keys

- Support XOR data load mode to the State memory for Cipher Block Chaining

- Encryption/Decryption in 375 clock cycles per 16-byte block

### 24.2 Overview

The Advanced Encryption Standard (AES) and Data Encryption Standard (DES) are two commonly used encryption standards. These are supported through an AES peripheral module and a DES CPU instruction. All communication interfaces and the CPU can optionally use AES and DES encrypted communication and data storage.

DES is supported by a DES instruction in the AVR XMEGA CPU. The 8-byte key and 8-byte data blocks must be loaded into the Register file, and then DES must be executed 16 times to encrypt/decrypt the data block.

The AES Crypto Module encrypts and decrypts 128-bit data blocks with the use of a 128-bit key. The key and data must be loaded into the key and state memory in the module before encryption/decryption is started. It takes 375 peripheral clock cycles before the encryption/decryption is done and decrypted/encrypted data can be read out, and an optional interrupt can be generated. The AES Crypto Module also has DMA support with transfer triggers when encryption/decryption is done and optional auto-start of encryption/decryption when the state memory is fully loaded.

# 25. ADC - 12-bit Analog to Digital Converter

### 25.1 Features

- One ADC with 12-bit resolution

- 2 Msps sample rate

- Signed and Unsigned conversions

- 4 result registers with individual input channel control

- 12 single ended inputs

- 8x4 differential inputs

- 4 internal inputs:

- Integrated Temperature Sensor

- DAC Output

- VCC voltage divided by 10

- Bandgap voltage

- Software selectable gain of 2, 4, 8, 16, 32 or 64

- Selectable accuracy of 8- or 12-bit.

- Internal or External Reference selection

- Event triggered conversion for accurate timing

- DMA transfer of conversion results

- Interrupt/Event on compare result

### 25.2 Overview

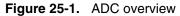

XMEGA A4 devices have one Analog to Digital Converter (ADC), see Figure 25-1 on page 42.

The ADC converts analog voltages to digital values. The ADC has 12-bit resolution and is capable of converting up to 2 million samples per second. The input selection is flexible, and both single-ended and differential measurements can be done. For differential measurements an optional gain stage is available to increase the dynamic range. In addition several internal signal inputs are available. The ADC can provide both signed and unsigned results.

This is a pipeline ADC. A pipeline ADC consists of several consecutive stages, where each stage convert one part of the result. The pipeline design enables high sample rate at low clock speeds, and remove limitations on samples speed versus propagation delay. This also means that a new analog voltage can be sampled and a new ADC measurement started while other ADC measurements are ongoing.

ADC measurements can either be started by application software or an incoming event from another peripheral in the device. Four different result registers with individual input selection (MUX selection) are provided to make it easier for the application to keep track of the data. Each result register and MUX selection pair is referred to as an ADC Channel. It is possible to use DMA to move ADC results directly to memory or peripherals when conversions are done.

Both internal and external analog reference voltages can be used. An accurate internal 1.0V reference is available.

An integrated temperature sensor is available and the output from this can be measured with the ADC. The output from the DAC, VCC/10 and the Bandgap voltage can also be measured by the ADC.

Each ADC has four MUX selection registers with a corresponding result register. This means that four channels can be sampled within 1.5  $\mu$ s without any intervention by the application other than starting the conversion. The results will be available in the result registers.

The ADC may be configured for 8- or 12-bit resolution, reducing the minimum conversion time (propagation delay) from 3.5 µs for 12-bit to 2.5 µs for 8-bit resolution.

ADC conversion results are provided left- or right adjusted with optional '1' or '0' padding. This eases calculation when the result is represented as a signed integer (signed 16-bit number).

PORTA has one ADC. Notation of this peripheral is ADCA.

# 26. DAC - 12-bit Digital to Analog Converter

### 26.1 Features

- One DAC with 12-bit resolution

- Up to 1 Msps conversion rate

- Flexible conversion range

- Multiple trigger sources

- 1 continuous output or 2 Sample and Hold (S/H) outputs

- Built-in offset and gain calibration

- High drive capabilities

- Low Power Mode

### 26.2 Overview

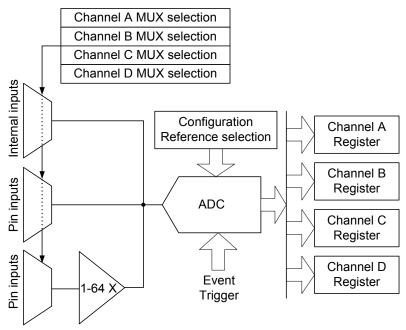

The XMEGA A4 devices feature one 12-bit, 1 Msps DAC with built-in offset and gain calibration, see Figure 26-1 on page 43.

A DAC converts a digital value into an analog signal. The DAC may use an internal 1.1 voltage as the upper limit for conversion, but it is also possible to use the supply voltage or any applied voltage in-between. The external reference input is shared with the ADC reference input.

#### Figure 26-1. DAC overview

The DAC has one continuous output with high drive capabilities for both resistive and capacitive loads. It is also possible to split the continuous time channel into two Sample and Hold (S/H) channels, each with separate data conversion registers.

A DAC conversion may be started from the application software by writing the data conversion registers. The DAC can also be configured to do conversions triggered by the Event System to have regular timing, independent of the application software. DMA may be used for transferring data from memory locations to DAC data registers.

The DAC has a built-in calibration system to reduce offset and gain error when loading with a calibration value from software.

PORTB has one DAC. Notation of this peripheral is DACB.

# 27. AC - Analog Comparator

### 27.1 Features

- Two Analog Comparators

- Selectable Power vs. Speed

- Selectable hysteresis

- 0, 20 mV, 50 mV

- Analog Comparator output available on pin

- Flexible Input Selection

- All pins on the port

- Output from the DAC

- Bandgap reference voltage.

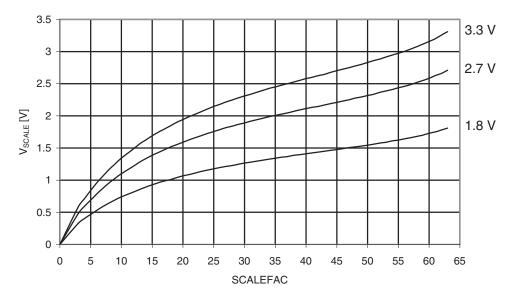

- Voltage scaler that can perform a 64-level scaling of the internal VCC voltage.

- Interrupt and event generation on

- Rising edge

- Falling edge

- Toggle

- Window function interrupt and event generation on

- Signal above window

- Signal inside window

- Signal below window

## 27.2 Overview

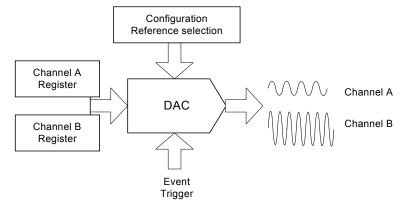

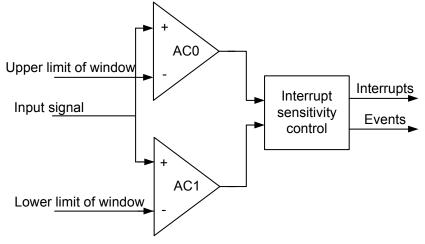

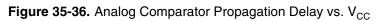

XMEGA A4 features two Analog Comparators (AC). An Analog Comparator compares two voltages, and the output indicates which input is largest. The Analog Comparator may be configured to give interrupt requests and/or events upon several different combinations of input change.

Both hysteresis and propagation delays may be adjusted in order to find the optimal operation for each application.

A wide range of input selection is available, both external pins and several internal signals can be used.

The Analog Comparators are always grouped in pairs (AC0 and AC1) on each analog port. They have identical behavior but separate control registers.

Optionally, the state of the comparator is directly available on a pin.

PORTA has one AC pair. Notation of this peripheral is ACA.

Figure 27-1. Analog comparator overview

### 27.3 Input Selection

The Analog comparators have a very flexible input selection and the two comparators grouped in a pair may be used to realize a window function. One pair of analog comparators is shown in Figure 27-1 on page 45.

- Input selection from pin

- Pin 0, 1, 2, 3, 4, 5, 6 selectable to positive input of analog comparator

- Pin 0, 1, 3, 5, 7 selectable to negative input of analog comparator

- Internal signals available on positive analog comparator inputs

Output from 12-bit DAC

- Output nom 12-bit DAC

- Internal signals available on negative analog comparator inputs

64-level scaler of the VCC, available on negative analog comparator input

- Bandgap voltage reference

- Output from 12-bit DAC

### 27.4 Window Function

The window function is realized by connecting the external inputs of the two analog comparators in a pair as shown in Figure 27-2.

# 28. OCD - On-chip Debug

### 28.1 Features

- Complete Program Flow Control

- Go, Stop, Reset, Step into, Step over, Step out, Run-to-Cursor

- Debugging on C and high-level language source code level

- Debugging on Assembler and disassembler level

- 1 dedicated program address or source level breakpoint for AVR Studio / debugger

- 4 Hardware Breakpoints

- Unlimited Number of User Program Breakpoints

- Unlimited Number of User Data Breakpoints, with break on:

- Data location read, write or both read and write

- Data location content equal or not equal to a value

- Data location content is greater or less than a value

- Data location content is within or outside a range

- Bits of a data location are equal or not equal to a value

- Non-Intrusive Operation

- No hardware or software resources in the device are used

- High Speed Operation

- No limitation on debug/programming clock frequency versus system clock frequency

### 28.2 Overview

The XMEGA A4 has a powerful On-Chip Debug (OCD) system that - in combination with Atmel's development tools - provides all the necessary functions to debug an application. It has support for program and data breakpoints, and can debug an application from C and high level language source code level, as well as assembler and disassembler level. It has full Non-Intrusive Operation and no hardware or software resources in the device are used. The ODC system is accessed through an external debugging tool which connects to the PDI physical interface. Refer to "Program and Debug Interfaces" on page 48.

# 29. Program and Debug Interfaces

### 29.1 Features

- PDI Program and Debug Interface (Atmel proprietary 2-pin interface)

- Access to the OCD system

- Programming of Flash, EEPROM, Fuses and Lock Bits

#### 29.2 Overview

The programming and debug facilities are accessed through PDI physical interface. The PDI physical interface uses one dedicated pin together with the Reset pin, and no general purpose pins are used.

### 29.3 PDI - Program and Debug Interface

The PDI is an Atmel proprietary protocol for communication between the microcontroller and Atmel's development tools.

# **30. Pinout and Pin Functions**

The pinout of XMEGA A4 is shown in "Pinout/Block Diagram" on page 3. In addition to general I/O functionality, each pin may have several functions. This will depend on which peripheral is enabled and connected to the actual pin. Only one of the alternate pin functions can be used at time.

# 30.1 Alternate Pin Functions Description

The tables below shows the notation for all pin functions available and describe their functions.

#### 30.1.1 Operation/Power Supply

| VCC  | Digital supply voltage |

|------|------------------------|

| AVCC | Analog supply voltage  |

| GND  | Ground                 |

#### 30.1.2 Port Interrupt functions

| SYNC  | Port pin with full synchronous and limited asynchronous interrupt function |

|-------|----------------------------------------------------------------------------|

| ASYNC | Port pin with full synchronous and full asynchronous interrupt function    |

#### 30.1.3 Analog functions

| ACn    | Analog Comparator input pin n            |

|--------|------------------------------------------|

| AC0OUT | Analog Comparator 0 Output               |

| ADCn   | Analog to Digital Converter input pin n  |

| DACn   | Digital to Analog Converter output pin n |

| AREF   | Analog Reference input pin               |

#### 30.1.4 Timer/Counter and AWEX functions

| OCnx | Output Compare Channel x for Timer/Counter n          |

|------|-------------------------------------------------------|

| OCnx | Inverted Output Compare Channel x for Timer/Counter n |

#### **Communication functions** 30.1.5

| SCL  | Serial Clock for TWI         |

|------|------------------------------|

| SDA  | Serial Data for TWI          |

| XCKn | Transfer Clock for USART n   |

| RXDn | Receiver Data for USART n    |

| TXDn | Transmitter Data for USART n |

| SS   | Slave Select for SPI         |

| MOSI | Master Out Slave In for SPI  |

| MISO | Master In Slave Out for SPI  |

| SCK  | Serial Clock for SPI         |

#### **Oscillators, Clock and Event** 30.1.6

30.1.7

| TOSCn                  | Timer Oscillator pin n                      |

|------------------------|---------------------------------------------|

| XTALn                  | Input/Output for inverting Oscillator pin n |

| Debug/System functions |                                             |

| RESET                  | Reset pin                                   |

| PDI_CLK                | Program and Debug Interface Clock pin       |

| HEOLI    | neset pin                             |

|----------|---------------------------------------|

| PDI_CLK  | Program and Debug Interface Clock pin |

| PDI_DATA | Program and Debug Interface Data pin  |

### 30.2 Alternate Pin Functions

The tables below shows the main and alternate pin functions for all pins on each port. It also shows which peripheral which make use of or enable the alternate pin function.

Table 30-1.

Port A - Alternate functions

| PORTA | PIN # | INTERRUPT  | ADCA POS | ADCA NEG | ADCA<br>GAINPOS | ADCA<br>GAINNEG | ACA POS | ACA NEG | ACA OUT | REF  |

|-------|-------|------------|----------|----------|-----------------|-----------------|---------|---------|---------|------|

| GND   | 38    |            |          |          |                 |                 |         |         |         |      |

| AVCC  | 39    |            |          |          |                 |                 |         |         |         |      |

| PA0   | 40    | SYNC       | ADC0     | ADC0     | ADC0            |                 | AC0     | AC0     |         | AREF |

| PA1   | 41    | SYNC       | ADC1     | ADC1     | ADC1            |                 | AC1     | AC1     |         |      |

| PA2   | 42    | SYNC/ASYNC | ADC2     | ADC2     | ADC2            |                 | AC2     |         |         |      |

| PA3   | 43    | SYNC       | ADC3     | ADC3     | ADC3            |                 | AC3     | AC3     |         |      |

| PA4   | 44    | SYNC       | ADC4     |          | ADC4            | ADC4            | AC4     |         |         |      |

| PA5   | 1     | SYNC       | ADC5     |          | ADC5            | ADC5            | AC5     | AC5     |         |      |

| PA6   | 2     | SYNC       | ADC6     |          | ADC6            | ADC6            | AC6     |         |         |      |

| PA7   | 3     | SYNC       | ADC7     |          | ADC7            | ADC7            |         | AC7     | AC0 OUT |      |

Table 30-2.

Port B - Alternate functions

| PORTB | PIN # | INTERRUPT  | ADCA POS | DACB | REF  |

|-------|-------|------------|----------|------|------|

| PB0   | 4     | SYNC       | ADC8     |      | AREF |

| PB1   | 5     | SYNC       | ADC9     |      |      |

| PB2   | 6     | SYNC/ASYNC | ADC10    | DAC0 |      |

| PB3   | 7     | SYNC       | ADC11    | DAC1 |      |

#### Table 30-3. Port C - Alternate functions

| PORTC | PIN # | INTERRUPT  | TCC0 | AWEXC | TCC1 | USARTC0 | USARTC1 | SPI  | TWIC | CLOCKOUT | EVENTOUT |

|-------|-------|------------|------|-------|------|---------|---------|------|------|----------|----------|

| GND   | 8     |            |      |       |      |         |         |      |      |          |          |

| vcc   | 9     |            |      |       |      |         |         |      |      |          |          |

| PC0   | 10    | SYNC       | OC0A | OC0A  |      |         |         |      | SDA  |          |          |

| PC1   | 11    | SYNC       | OC0B | OC0A  |      | XCK0    |         |      | SCL  |          |          |