The revision list can be viewed directly by clicking the title page. The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

# SH7101

Hardware Manual

Renesas 32-Bit RISC Microcomputer SuperH<sup>™</sup> RISC engine Family/SH7100 Series

SH7101 HD6437101

Rev.2.00

Revision date: Sep. 27, 2007

#### Notes regarding these materials

- This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com)

- Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below:

- (1) artificial life support devices or systems

- (2) surgical implantations

Rev.2.00 Sep. 27, 2007 Page ii of xxxiv

REJ09B0394-0200

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

- Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

### General Precautions in the Handling of MPU/MCU Products

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each other, the description in the body of the manual takes precedence.

#### 1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions may occur due to the false recognition of the pin state as an input signal. Unused pins should be handled as described under Handling of Unused Pins in the manual.

#### 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

- The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the

- states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

#### 3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

The reserved addresses are provided for the possible future expansion of functions. Do not access these addresses; the correct operation of LSI is not guaranteed if they are accessed.

#### 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

— When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

#### 5. Differences between Products

Before changing from one product to another, i.e. to one with a different type number, confirm that the change will not lead to problems.

— The characteristics of MPU/MCU in the same group but having different type numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different type numbers, implement a system-evaluation test for each of the products.

## Configuration of This Manual

This manual comprises the following items:

- 1. General Precautions on Handling of Product

- 2. Configuration of This Manual

- 3. Preface

- 4. Contents

- 5. Overview

- 6. Description of Functional Modules

- CPU and System-Control Modules

- On-Chip Peripheral Modules

The configuration of the functional description of each module differs according to the module. However, the generic style includes the following items:

- i) Feature

- ii) Input/Output Pin

- iii) Register Description

- iv) Operation

- v) Usage Note

When designing an application system that includes this LSI, take notes into account. Each section includes notes in relation to the descriptions given, and usage notes are given, as required, as the final part of each section.

- 7. List of Registers

- 8. Electrical Characteristics

- 9. Appendix

- 10. Index

### **Preface**

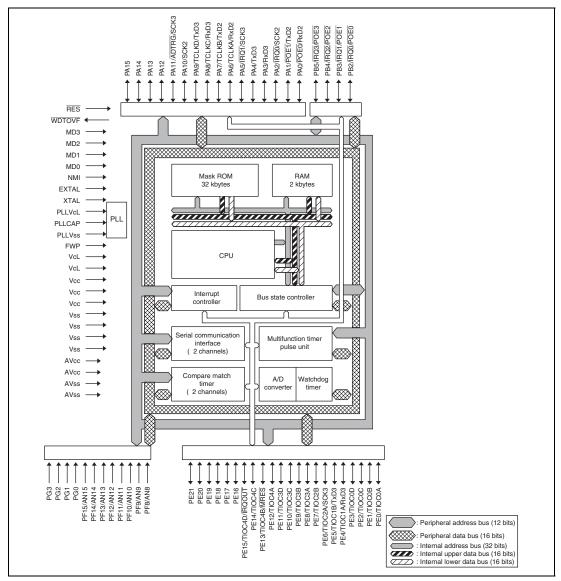

The SH7101 single-chip RISC (Reduced Instruction Set Computer) microcomputer includes a Renesas Technology-original RISC CPU as its core, and the peripheral functions required to configure a system.

Target Users: This manual was written for users who will be using this LSI in the design of

application systems. Users of this manual are expected to understand the fundamentals of electrical circuits, logical circuits, and microcomputers.

Objective: This manual was written to explain the hardware functions and electrical

characteristics of this LSI to the above users.

Refer to the SH-1/SH-2/SH-DSP Software Manual for a detailed description of the

instruction set.

#### Notes on reading this manual:

Product names

The following products are covered in this manual.

#### **Product Classifications and Abbreviations**

| Basic Classification    | On-Chip ROM Classification        | Part No.  |

|-------------------------|-----------------------------------|-----------|

| SH7101 (80-pin version) | Mask ROM version (ROM: 32 kbytes) | HD6437101 |

In this manual, the product abbreviations are used to distinguish products. For example, products are collectively referred to as the SH7101.

- In order to understand the overall functions of the chip

Read the manual according to the contents. This manual can be roughly categorized into parts

on the CPU, system control functions, peripheral functions and electrical characteristics.

- In order to understand the details of the CPU's functions Read the SH-1/SH-2/SH-DSP Software Manual.

- In order to understand the details of a register when the user knows its name Read the index that is the final part of the manual to find the page number of the entry on the register. The addresses, bit names, and initial values of the registers are summarized in section 18, List of Registers.

Rules: Register name: The following notation is used for cases when the same or a

similar function, e.g. serial communication, is implemented

on more than one channel:

XXX\_N (XXX is the register name and N is the channel

number)

Bit order: The MSB (most significant bit) is on the left and the LSB

(least significant bit) is on the right.

Related Manuals: The latest versions of all related manuals are available from our web site.

Please ensure you have the latest versions of all documents you require.

http://www.renesas.com/

#### SH7101 manuals:

| Document Title                   | Document No.    |

|----------------------------------|-----------------|

| SH7101 Hardware Manual           | This manual     |

| SH-1/SH-2/SH-DSP Software Manual | REJ09B0171-0500 |

#### Users manuals for development tools:

| Document Title                                                            | Document No.    |

|---------------------------------------------------------------------------|-----------------|

| SuperH C/C++ Compiler, Assembler, Optimizing Linkage Editor User's Manual | REJ10B0047-0100 |

| SuperH RISC engine Simulator/Debugger (for Windows) User's Manual         | REJ10B0210-0300 |

| High-performance Embedded Workshop User's Manual                          | REJ10J1554-0100 |

#### **Application Notes:**

| Document Title                                             | Document No.    |

|------------------------------------------------------------|-----------------|

| SuperH RISC engine C/C++ Compiler Package Application Note | REJ05B0463-0400 |

# Main Revisions for This Edition

| Item                                     | Page | Revision (See Manual for Details)                                                    |

|------------------------------------------|------|--------------------------------------------------------------------------------------|

| All                                      | _    | Company name and brand names amended                                                 |

|                                          |      | (Before) Hitachi, Ltd. $\rightarrow$ (After) Renesas Technology Corp.                |

| 6.5 Interrupt Exception                  | 79   | Table amended                                                                        |

| Processing Vectors                       |      | Interrupt                                                                            |

| Table C.O.Intermed                       |      | Source Name                                                                          |

| Table 6.2 Interrupt Exception Processing |      | MTU channel 3 TGIA_3                                                                 |

| Vectors and Priorities                   |      | TGIB_3                                                                               |

|                                          |      | TGIC_3                                                                               |

|                                          |      | TGID_3                                                                               |

|                                          |      | TCIV_3                                                                               |

| 7.5.1 Bus Control<br>Register 1 (BCR1)   | 89   | Bit table amended                                                                    |

| negister i (boni)                        |      | Initial<br>Bit Bit Name Value R/W Description                                        |

|                                          |      | 14 — 1 R Reserved These bits are always read as 1 and should always be written to 1. |

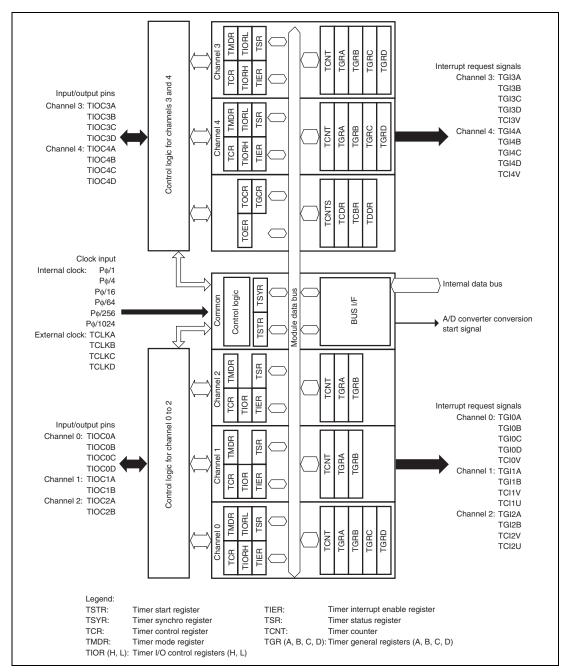

| 8.1 Features                             | 94   | Title and figure amended                                                             |

| Figure 8.1 Block<br>Diagram of MTU       |      | Interrupt request signals                                                            |

| Diagram of Wife                          |      | Channel 3: TGI3A<br>TGI3B                                                            |

|                                          |      | TGI3C                                                                                |

|                                          |      | TGI3D<br>TCI3V                                                                       |

|                                          |      | Channel 4: TGI4A                                                                     |

|                                          |      | TGI4B                                                                                |

|                                          |      | TGI4C                                                                                |

|                                          |      | TGI4D                                                                                |

|                                          |      | TCI4V                                                                                |

| 8.3.3 Timer I/O Control Register (TIOR)  | 109  | Table amended                                                                        |

| · · ·                                    |      | Description                                                                          |

| Table 8.13 TIORL_0 (channel 0)           |      | Bit 3                                                                                |

| (Chariner o)                             |      | 0 0 0 Output Output disable                                                          |

|                                          |      | 1 compare register* Initial output is 0 0 output at compare match                    |

| 8.4.4 Cascaded                           | 149  | Note amended                                                                         |

| Operation                                |      | Note: When phase counting mode is set for channel 1 or 2, the                        |

| Table 8.30 Cascaded                      |      | counter clock setting is invalid and the counters operates                           |

|                                          |      |                                                                                      |

| Item                                                                                             | Page | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

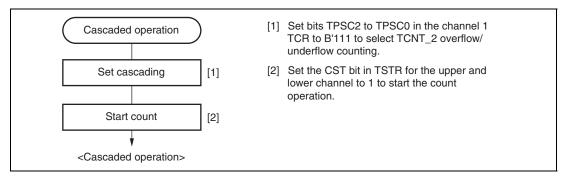

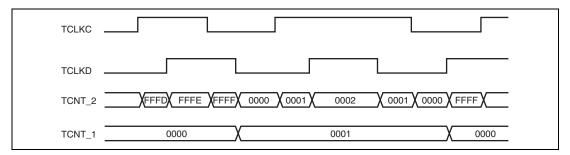

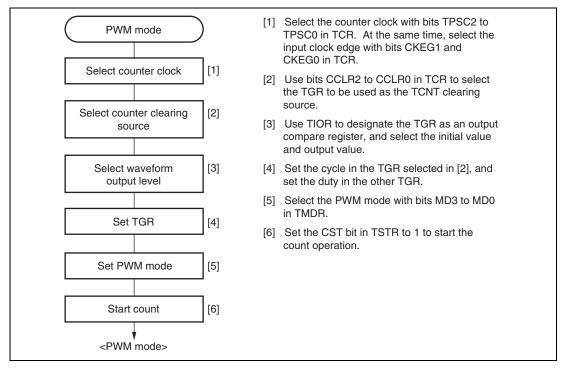

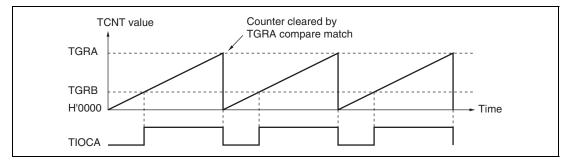

| 8.4.4 Cascaded Operation Figure 8.18 Cascaded Operation Setting Procedure                        | 149  | Figure amended [1] Set bits TPSC2 to TPSC0 in the channel 1 TCR to B'111 to select TCNT_2 overflow/ underflow counting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

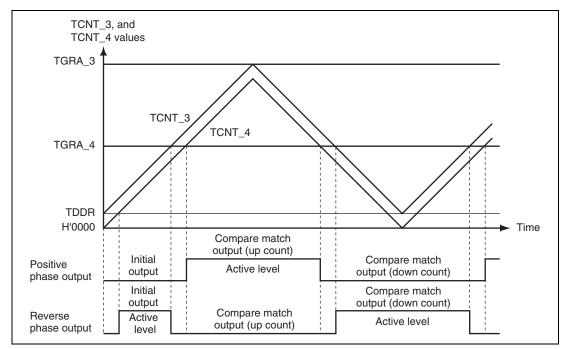

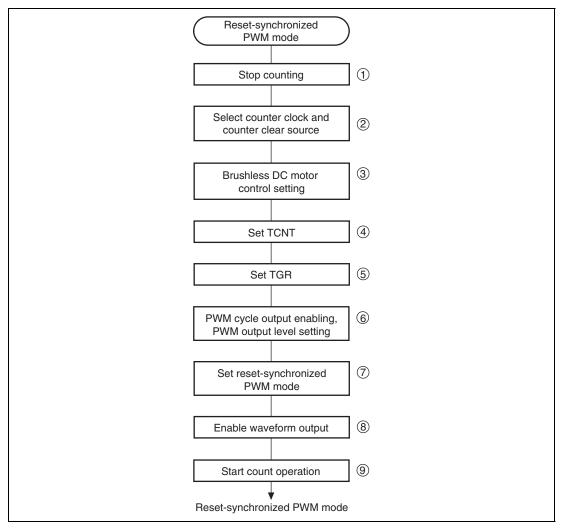

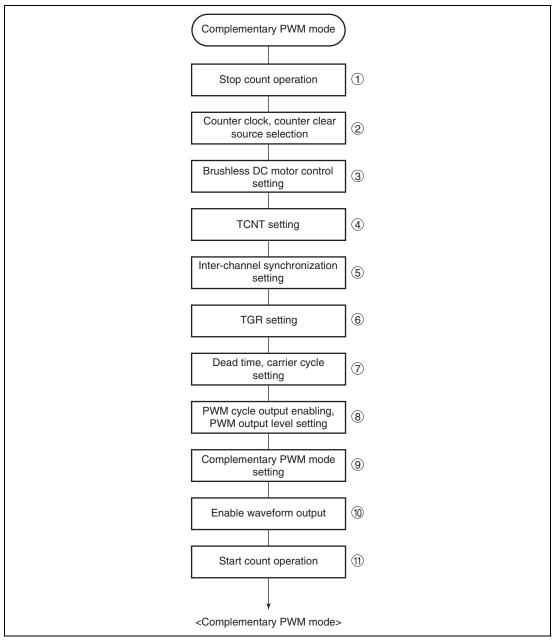

| 8.4.8 Complementary<br>PWM Mode<br>Example of<br>Complementary PWM<br>Mode Setting<br>Procedure: | 170  | Description amended  10. Set enabling/disabling of PWM waveform output pin output in the timer output master enable register (TOER).  11. Set bits CST3 and CST4 in TSTR to 1 simultaneously to start the count operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

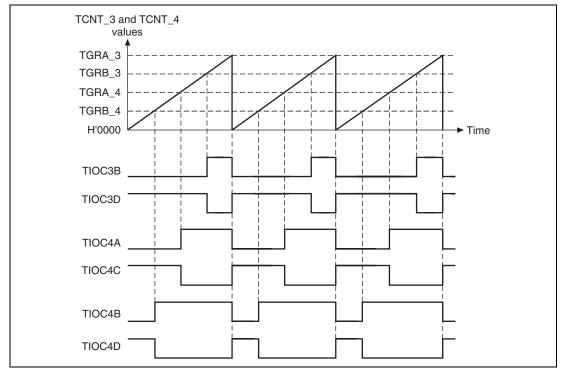

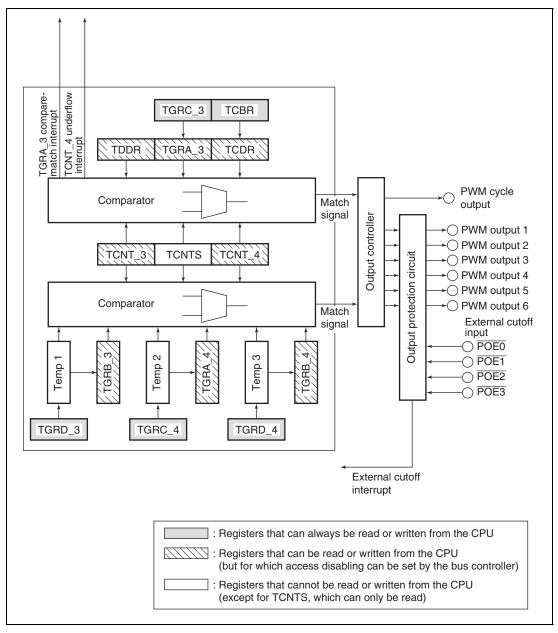

| Complementary PWM Mode Output Protection Function:                                               | 192  | <ul> <li>Register and counter miswrite prevention function</li> <li>With the exception of the buffer registers, which can be rewritten at any time, access by the CPU can be enabled or disabled for the mode registers, control registers, compare registers, and counters used in complementary PWM mode by means of bit 13 in the bus controller's bus control register 1 (BCR1). Some registers in channels 3 and 4 concerned are listed below: total 21 registers of TCR_3 and TCR_4; TMDR_3 and TMDR_4; TIORH_3 and TIORH_4; TIORL_3 and TIORL_4; TIER_3 and TIER_4; TCNT_3 and TCNT_4; TGRA_3 and TGRA_4; TGRB_3 and TGRB_4; TOER; TOCR; TGCR; TCDR; and TDDR. This function enables the CPU to prevent miswriting due to the CPU runaway by disabling CPU access to the mode registers, control registers, and counters. In access disabled state, an undefined value is read from the registers concerned, and cannot be modified.</li> </ul> |

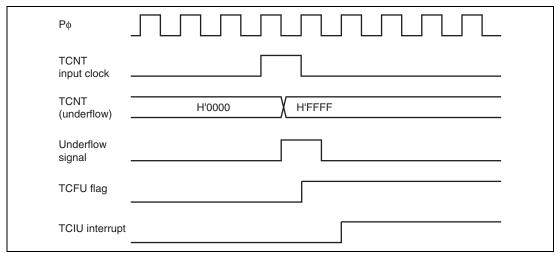

| 8.5.1 Interrupts and Priorities Underflow Interrupt:                                             | 194  | Description amended  An interrupt is requested if the TCIEU bit in TIER is set to 1 when the TCFU flag in TSR is set to 1 by the occurrence of TCNT underflow on a channel. The interrupt request is cleared by clearing the TCFU flag to 0. The MTU has two underflow interrupts, one each for channels 1 and 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Page

#### **Revision (See Manual for Details)**

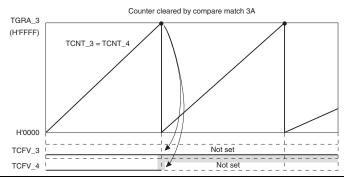

8.7.15 Overflow Flags in 216 Reset Sync PWM Mode Figure 8.81 Reset Sync PWM Mode Overflow Flag

8.7.21 Simultaneous 219

Input Capture of

TCNT\_1 and TCNT\_2 in

Cascade Connection

Description amended

When timer counters 1 and 2 (TCNT\_1 and TCNT\_2) are operated as a 32-bit counter in cascade connection, the cascade counter value cannot be captured successfully even if input-capture input is simultaneously done to TIOC1A and TIOC2A or to TIOC1B and TIOC2B. This is because the input timing of TIOC1A and TIOC2A or of TIOC1B and TIOC2B may not be the same when external input-capture signals to be input into TCNT 1 and TCNT 2 are taken in synchronization with the internal clock. For example, TCNT\_1 (the counter for upper 16 bits) does not capture the count-up value by overflow from TCNT\_2 (the counter for lower 16 bits) but captures the count value before the count-up. In this case, the values of TCNT\_1 = H'FFF1 and TCNT\_2 = H'0000 should be transferred to TGRA 1 and TGRA 2 or to TGRB 1 and TGRB 2, but the values of TCNT 1 = H'FFF0 and TCNT 2 = H'0000 are erroneously transferred.

| Item                 | Page | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                                              |

|----------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8.9.5 Usage Note     | 262  | Description added                                                                                                                                                                                                                                                                                                                                                              |

|                      |      | (1) Symptom                                                                                                                                                                                                                                                                                                                                                                    |

|                      |      | (a) Regarding the POEnF*1 bits                                                                                                                                                                                                                                                                                                                                                 |

|                      |      | If setting of the POEnF bits in the input level control/status registers (ICSR1 and ICSR2) by the hardware*2 and reading from these bits occur simultaneously, "0" will be read, where "1" should be read.                                                                                                                                                                     |

|                      |      | Furthermore, if clearing of these bits is attempted subsequent to the above condition, the clearing should be ignored*3 but it will be carried out.                                                                                                                                                                                                                            |

|                      |      | Notes: *1 For the SH7046-Series and SH7047-Series, $n=0$ to 6; for the SH7144-Series, $n=0$ to 3.                                                                                                                                                                                                                                                                              |

|                      |      | *2 The POEnF bits are set when the signals input to the<br>respective POEn pins satisfy the conditions that are<br>specified by the POEnM1 and POEnM0 of the<br>ICSR1 and ICSR2.                                                                                                                                                                                               |

|                      |      | *3 The correct operation is that clearing of the POEnF<br>bits is only possible after "1" is read from them in<br>order to prevent accidental clearing.                                                                                                                                                                                                                        |

|                      |      | (b) Regarding the OSF bit                                                                                                                                                                                                                                                                                                                                                      |

|                      |      | The same symptom applies to the OSF bits of the output level control/status register (OCSR).                                                                                                                                                                                                                                                                                   |

|                      |      | (2) To Avoid This Problem                                                                                                                                                                                                                                                                                                                                                      |

|                      |      | Please clear the POEnF bits or the OSF bit in these steps: first execute a read for ICSR1, ICSR2, or OCSR, then write "0" to the bits that had a read value of "1" to clear them while writing "1" to other bits. If this procedure is not followed, the POEnF bits and the OSF bit may be cleared unexpectedly if their setting by hardware and reading occur simultaneously. |

| 10.3.2 Receive Data  | 280  | Description added                                                                                                                                                                                                                                                                                                                                                              |

| Register (RDR)       |      | $\dots$ RDR cannot be written to by the CPU. The initial value of RDR is H'00.                                                                                                                                                                                                                                                                                                 |

| 10.3.4 Transmit Data | 280  | Description added                                                                                                                                                                                                                                                                                                                                                              |

| Register (TDR)       |      | Although TDR can be read or written to by the CPU at all times, to achieve reliable serial transmission, write transmit data to TDR for only once after confirming that the TDRE bit in SSR is set to 1. The initial value of TDR is H'FF.                                                                                                                                     |

|                      |      |                                                                                                                                                                                                                                                                                                                                                                                |

| Item                       | Page | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11.1 Features              | 325  | Description added                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                            |      | • Conversion time: 6.7 $\mu s$ per channel (at P $\varphi$ = 20-MHz operation)                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                            |      | 5.4 $\mu s$ per channel (at P $\varphi$ = 25-MHz operation)                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

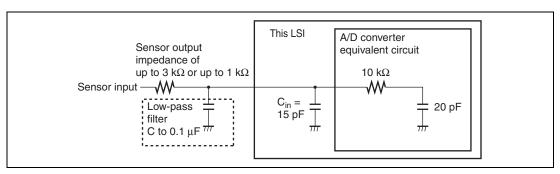

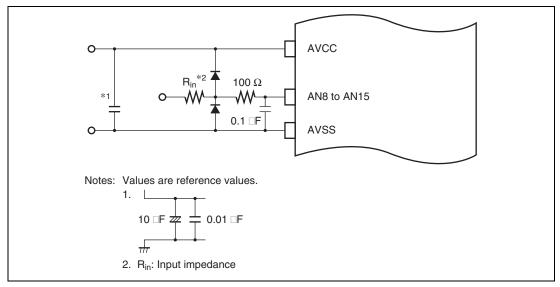

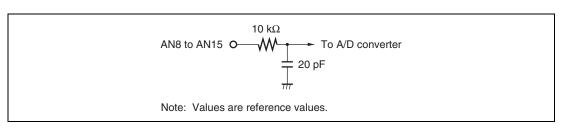

| 11.7.2 Permissible         | 340  | Description amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Signal Source<br>Impedance |      | This LSI's analog input is designed such that conversion accuracy is guaranteed for an input signal for which the signal source impedance is 1 k $\Omega$ or less, or 3 k $\Omega$ or less. This specification is provided to enable the A/D converter's sample-and-hold circuit input capacitance to be charged within the sampling time; if the sensor output impedance exceeds 1 k $\Omega$ or 3 k $\Omega$ , charging may be insufficient and it may not be possible to guarantee A/D conversion accuracy |

| 17.3.1 Sleep Mode          | 395  | Description added                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Notes on Using Sleep       |      | <ul> <li>There are 4 conditions to clear sleep mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Mode                       |      | (1) Clearing by an interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                            |      | (2) Clearing by DTC address error                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                            |      | (3) Clearing by the power-on reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                            |      | (4) Clearing by the manual reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                            |      | When clearing sleep mode by (1) or (2), CPU may run out of control. Please clear sleep mode by (3) or (4), don't use (1) or (2).                                                                                                                                                                                                                                                                                                                                                                              |

|                            |      | Do not use DTC module or AUD module during sleep mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

# Contents

| Section 1 Overview                      | 1 |  |  |  |  |

|-----------------------------------------|---|--|--|--|--|

| 1.1 Features                            | 1 |  |  |  |  |

| 1.2 Internal Block Diagram              | 3 |  |  |  |  |

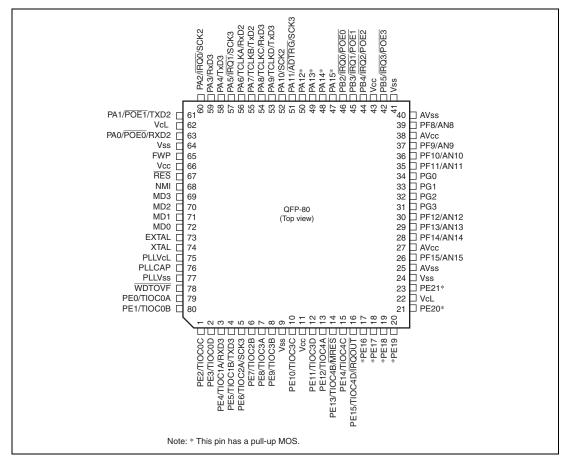

| Pin Arrangement                         |   |  |  |  |  |

| 1.4 Pin Functions                       |   |  |  |  |  |

| 1.5 Differences from SH7046 Group       | 9 |  |  |  |  |

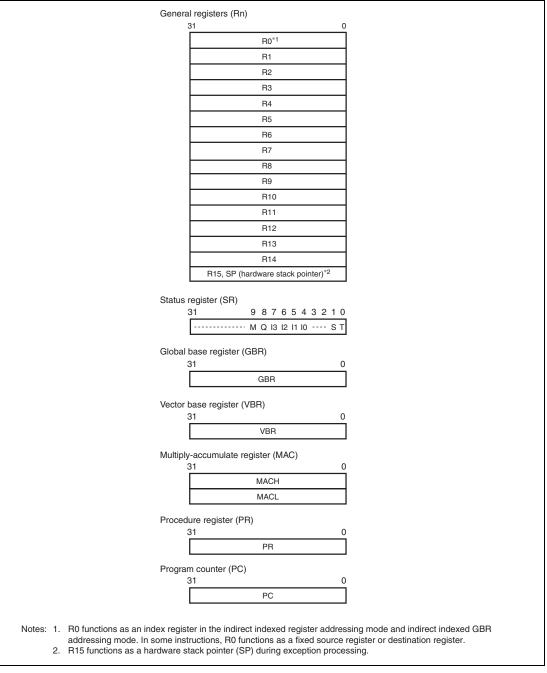

| Section 2 CPU                           | 1 |  |  |  |  |

| 2.1 Features                            | 1 |  |  |  |  |

| 2.2 Register Configuration              | 1 |  |  |  |  |

| 2.2.1 General Registers (Rn)            | 3 |  |  |  |  |

| 2.2.2 Control Registers                 | 3 |  |  |  |  |

| 2.2.3 System Registers                  | 4 |  |  |  |  |

| 2.2.4 Initial Values of Registers       | 5 |  |  |  |  |

| 2.3 Data Formats                        | 5 |  |  |  |  |

| 2.3.1 Data Format in Registers          | 5 |  |  |  |  |

| 2.3.2 Data Formats in Memory            | 6 |  |  |  |  |

| 2.3.3 Immediate Data Format             | 6 |  |  |  |  |

| 2.4 Instruction Features1               | 7 |  |  |  |  |

| 2.4.1 RISC-Type Instruction Set         | 7 |  |  |  |  |

| 2.4.2 Addressing Modes                  | 0 |  |  |  |  |

| 2.4.3 Instruction Format                | 4 |  |  |  |  |

| 2.5 Instruction Set                     | 6 |  |  |  |  |

| 2.5.1 Instruction Set by Classification | 6 |  |  |  |  |

| 2.6 Processing States 4                 | 1 |  |  |  |  |

| 2.6.1 State Transitions                 | 1 |  |  |  |  |

| Section 3 MCU Operating Modes           | 3 |  |  |  |  |

| 3.1 Selection of Operating Modes        | 3 |  |  |  |  |

| 3.2 Input/Output Pins                   | 4 |  |  |  |  |

| 3.3 Explanation of Operating Modes      | 4 |  |  |  |  |

| 3.3.1 Mode 3 (Single chip mode)4        | 4 |  |  |  |  |

| 3.3.2 Clock Mode                        | 4 |  |  |  |  |

| 3.4 Address Map                         | 5 |  |  |  |  |

| 3.5 Initial State of This LSI           | 6 |  |  |  |  |

| Section 4 Clock Pulse Generator         | 7 |  |  |  |  |

| 4.1 Oscillator                          | 7 |  |  |  |  |

|      | 4.1.1      | Connecting Crystal Resonator                                            | 47 |  |  |

|------|------------|-------------------------------------------------------------------------|----|--|--|

|      | 4.1.2      | External Clock Input Method                                             | 49 |  |  |

| 4.2  | Function   | on for Detecting Oscillator Halt                                        | 49 |  |  |

| 4.3  | Usage      | Notes                                                                   | 50 |  |  |

|      | 4.3.1      | Note on Crystal Resonator                                               | 50 |  |  |

|      | 4.3.2      | Notes on Board Design                                                   | 50 |  |  |

| Sect | ion 5      | Exception Processing                                                    | 53 |  |  |

| 5.1  | Overvi     | ew                                                                      | 53 |  |  |

|      | 5.1.1      | Types of Exception Processing and Priority                              | 53 |  |  |

|      | 5.1.2      | Exception Processing Operations                                         | 54 |  |  |

|      | 5.1.3      | Exception Processing Vector Table                                       | 55 |  |  |

| 5.2  | Resets     |                                                                         | 57 |  |  |

|      | 5.2.1      | Types of Reset                                                          | 57 |  |  |

|      | 5.2.2      | Power-On Reset                                                          | 57 |  |  |

|      | 5.2.3      | Manual Reset                                                            | 58 |  |  |

| 5.3  | Addres     | ss Errors                                                               | 59 |  |  |

|      | 5.3.1      | Cause of Address Error Exception                                        | 59 |  |  |

|      | 5.3.2      | Address Error Exception Processing                                      | 60 |  |  |

| 5.4  | Interrupts |                                                                         |    |  |  |

|      | 5.4.1      | Interrupt Sources                                                       | 60 |  |  |

|      | 5.4.2      | Interrupt Priority Level                                                | 61 |  |  |

|      | 5.4.3      | Interrupt Exception Processing                                          | 61 |  |  |

| 5.5  | Except     | ions Triggered by Instructions                                          |    |  |  |

|      | 5.5.1      | Types of Exceptions Triggered by Instructions                           | 62 |  |  |

|      | 5.5.2      | Trap Instructions                                                       | 62 |  |  |

|      | 5.5.3      | Illegal Slot Instructions                                               | 63 |  |  |

|      | 5.5.4      | General Illegal Instructions                                            | 63 |  |  |

| 5.6  | Cases      | when Exception Sources are Not Accepted                                 | 64 |  |  |

|      | 5.6.1      | Immediately after Delayed Branch Instruction                            | 64 |  |  |

|      | 5.6.2      | Immediately after Interrupt-Disabled Instruction                        | 64 |  |  |

| 5.7  | Stack S    | Status after Exception Processing Ends                                  | 65 |  |  |

| 5.8  | Usage      | Notes                                                                   | 66 |  |  |

|      | 5.8.1      | Value of Stack Pointer (SP)                                             | 66 |  |  |

|      | 5.8.2      | Value of Vector Base Register (VBR)                                     | 66 |  |  |

|      | 5.8.3      | Address Errors Caused by Stacking of Address Error Exception Processing | 66 |  |  |

| Sect | tion 6     | Interrupt Controller (INTC)                                             | 67 |  |  |

| 6.1  | Feature    | es                                                                      | 67 |  |  |

| 6.2  | Input/C    | Output Pins                                                             | 68 |  |  |

| 6.3  | Registe | er Descriptions                                             | 68  |

|------|---------|-------------------------------------------------------------|-----|

|      | 6.3.1   | Interrupt Control Register 1 (ICR1)                         | 69  |

|      | 6.3.2   | Interrupt Control Register 2 (ICR2)                         | 70  |

|      | 6.3.3   | IRQ Status Register (ISR)                                   | 72  |

|      | 6.3.4   | Interrupt Priority Registers A, D to I (IPRA, IPRD to IPRI) | 73  |

| 6.4  | Interru | pt Sources                                                  | 75  |

|      | 6.4.1   | External Interrupts                                         | 75  |

|      | 6.4.2   | On-Chip Peripheral Module Interrupts                        | 77  |

| 6.5  | Interru | pt Exception Processing Vectors Table                       | 77  |

| 6.6  | Operat  | ion                                                         | 81  |

|      | 6.6.1   | Interrupt Sequence                                          | 81  |

|      | 6.6.2   | Stack after Interrupt Exception Processing                  | 83  |

| 6.7  | Interru | pt Response Time                                            | 84  |

| Sect | ion 7   | Bus State Controller (BSC)                                  | 87  |

| 7.1  |         | es                                                          |     |

| 7.2  | Input/c | output Pin                                                  | 87  |

| 7.3  | Registe | er                                                          | 87  |

| 7.4  | Addres  | ss Map                                                      | 88  |

| 7.5  | Registe | er Description                                              | 89  |

|      | 7.5.1   | Bus Control Register 1 (BCR1)                               |     |

| 7.6  | On-chi  | p Peripheral I/O Register Access                            | 90  |

| Sect | ion 8   | Multi-Function Timer Pulse Unit (MTU)                       | 91  |

| 8.1  |         | es                                                          |     |

| 8.2  |         | Output Pins                                                 |     |

| 8.3  |         | er Descriptions                                             |     |

|      | 8.3.1   | Timer Control Register (TCR)                                | 98  |

|      | 8.3.2   | Timer Mode Register (TMDR)                                  |     |

|      | 8.3.3   | Timer I/O Control Register (TIOR)                           |     |

|      | 8.3.4   | Timer Interrupt Enable Register (TIER)                      | 122 |

|      | 8.3.5   | Timer Status Register (TSR)                                 | 124 |

|      | 8.3.6   | Timer Counter (TCNT)                                        | 126 |

|      | 8.3.7   | Timer General Register (TGR)                                | 127 |

|      | 8.3.8   | Timer Start Register (TSTR)                                 | 127 |

|      | 8.3.9   | Timer Synchro Register (TSYR)                               | 128 |

|      | 8.3.10  | Timer Output Master Enable Register (TOER)                  | 130 |

|      | 8.3.11  | Timer Output Control Register (TOCR)                        | 131 |

|      | 8.3.12  |                                                             |     |

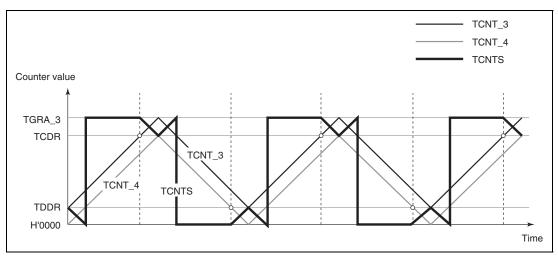

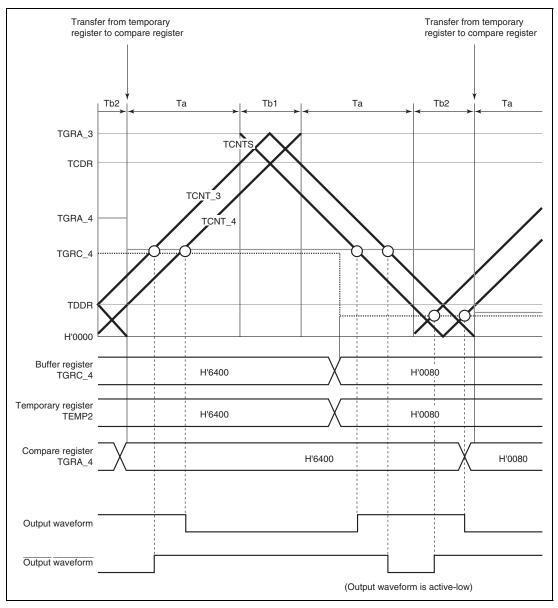

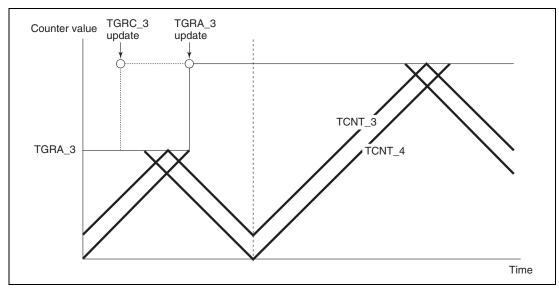

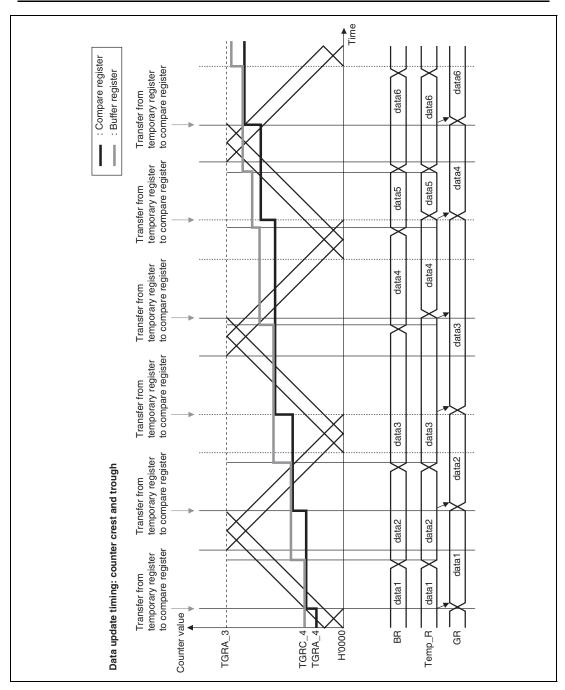

|      | 8.3.13  | Timer Subcounter (TCNTS)                                    | 135 |

|     | 8.3.14  | Timer Dead Time Data Register (TDDR)                                 | 135 |

|-----|---------|----------------------------------------------------------------------|-----|

|     |         | Timer Period Data Register (TCDR)                                    |     |

|     | 8.3.16  | Timer Period Buffer Register (TCBR)                                  | 135 |

|     | 8.3.17  | Bus Master Interface                                                 | 136 |

| 8.4 | Operati | on                                                                   | 137 |

|     | 8.4.1   | Basic Functions                                                      | 137 |

|     | 8.4.2   | Synchronous Operation                                                | 142 |

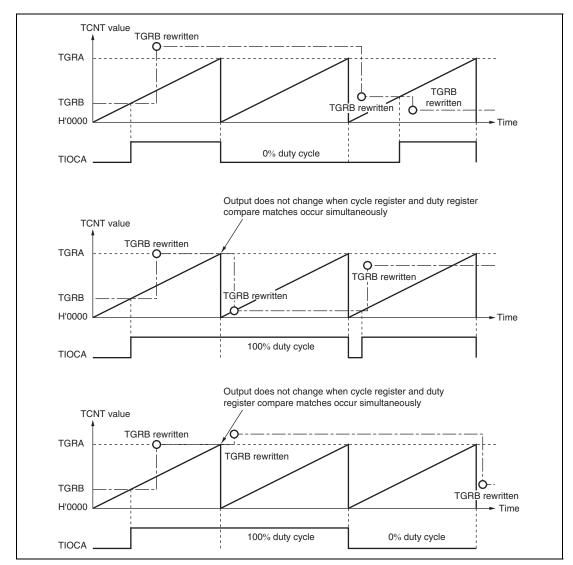

|     | 8.4.3   | Buffer Operation                                                     | 145 |

|     | 8.4.4   | Cascaded Operation                                                   | 149 |

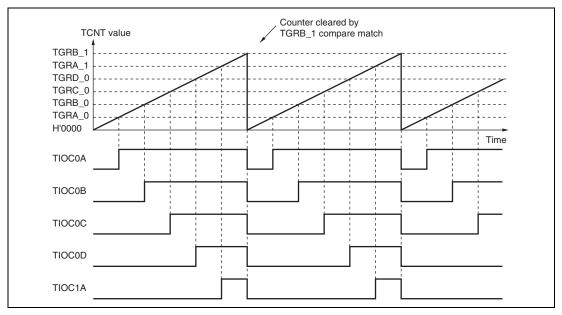

|     | 8.4.5   | PWM Modes                                                            | 150 |

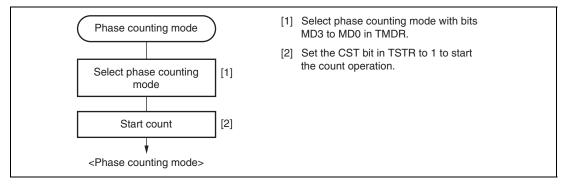

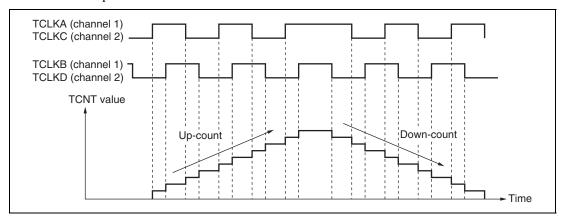

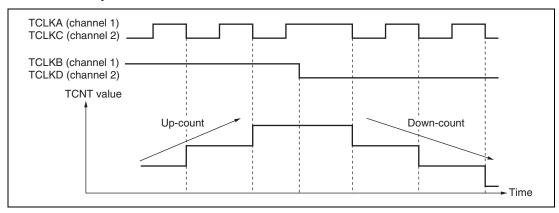

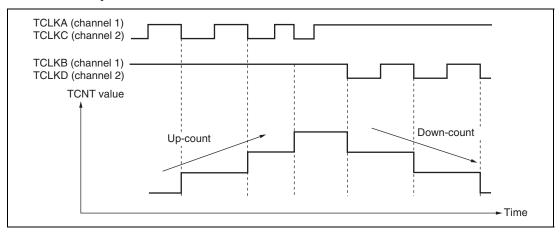

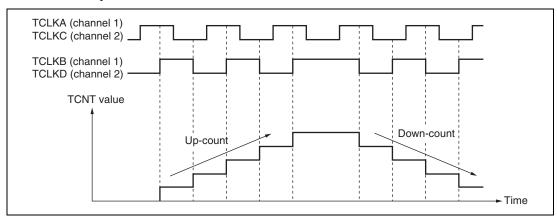

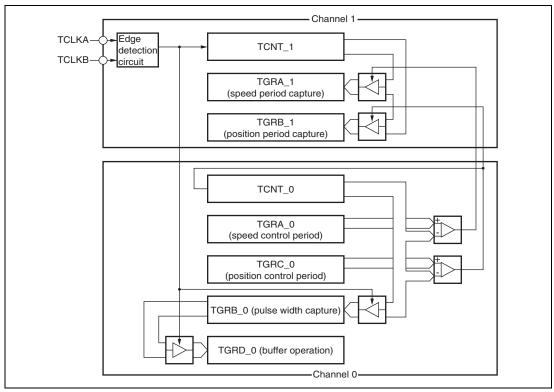

|     | 8.4.6   | Phase Counting Mode                                                  | 156 |

|     | 8.4.7   | Reset-Synchronized PWM Mode                                          | 163 |

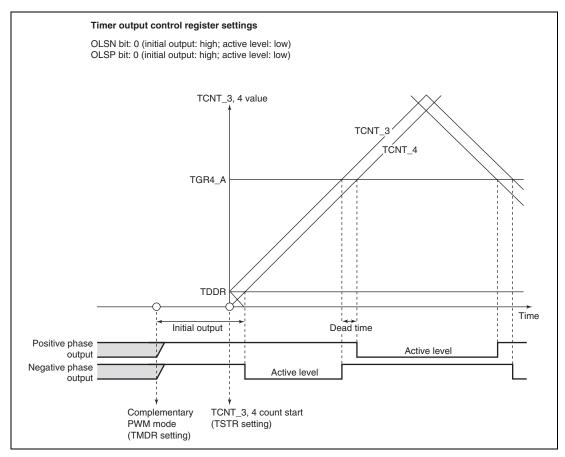

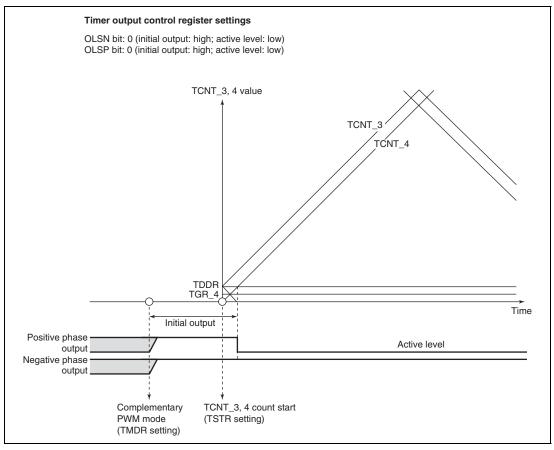

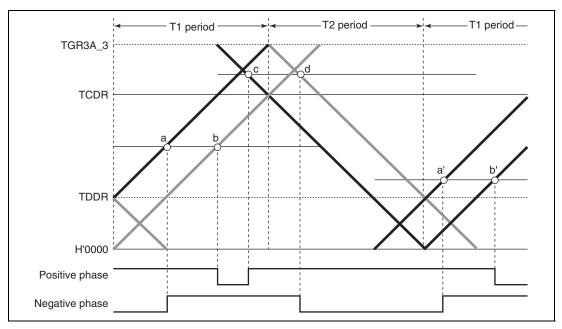

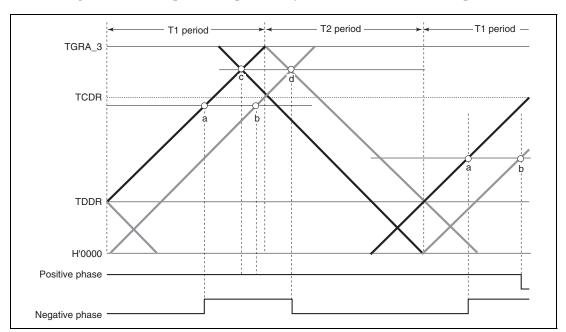

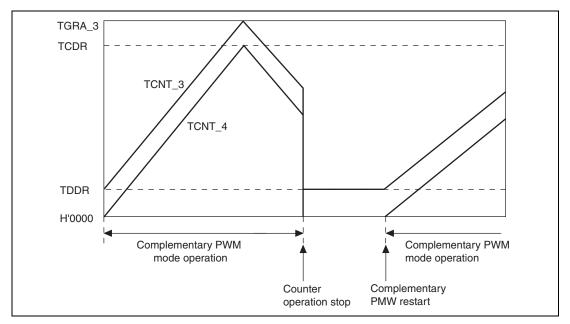

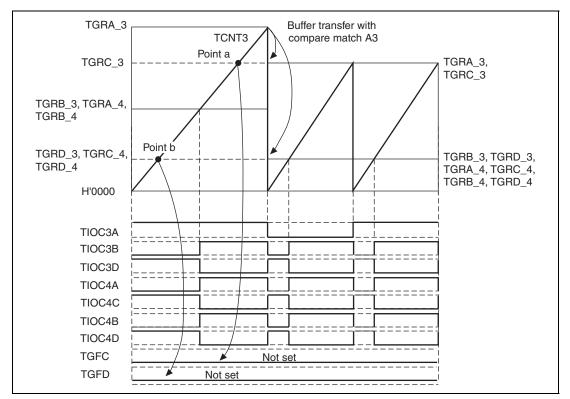

|     | 8.4.8   | Complementary PWM Mode                                               | 167 |

| 8.5 | Interru | pt Sources                                                           | 192 |

|     | 8.5.1   | Interrupts and Priorities                                            | 192 |

|     | 8.5.2   | A/D Converter Activation                                             | 194 |

| 8.6 | Operati | on Timing                                                            | 195 |

|     | 8.6.1   | Input/Output Timing                                                  | 195 |

|     | 8.6.2   | Interrupt Signal Timing                                              | 200 |

| 8.7 | Usage 1 | Notes                                                                | 204 |

|     | 8.7.1   | Module Standby Mode Setting                                          | 204 |

|     | 8.7.2   | Input Clock Restrictions                                             | 204 |

|     | 8.7.3   | Caution on Period Setting                                            | 205 |

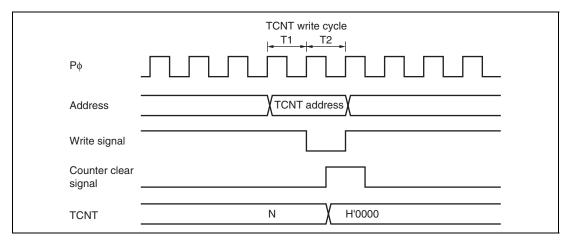

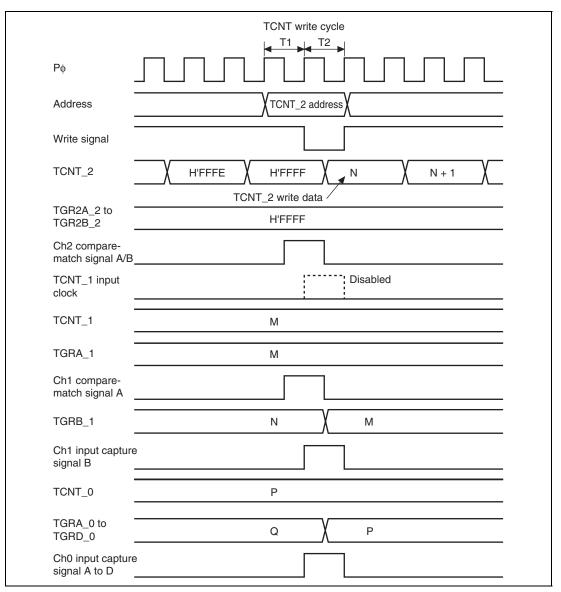

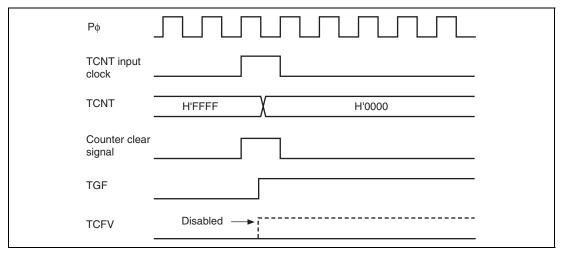

|     | 8.7.4   | Contention between TCNT Write and Clear Operations                   | 205 |

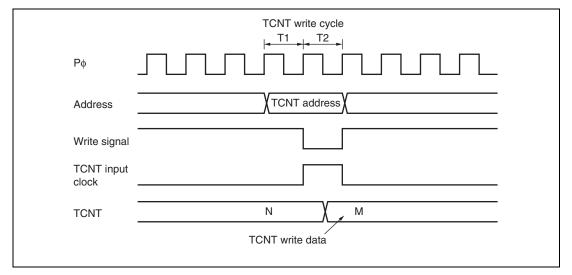

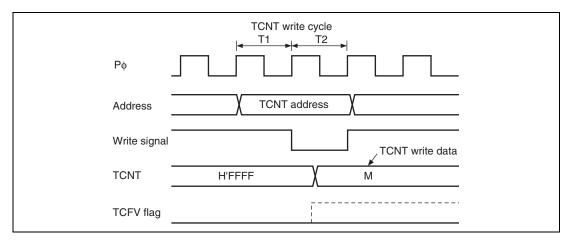

|     | 8.7.5   | Contention between TCNT Write and Increment Operations               | 206 |

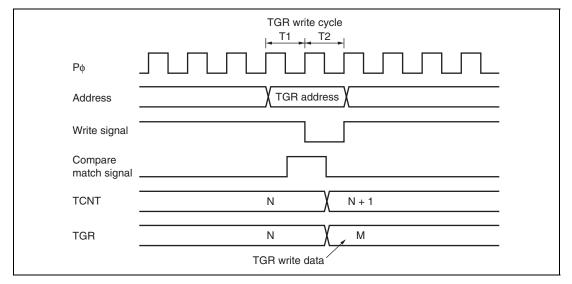

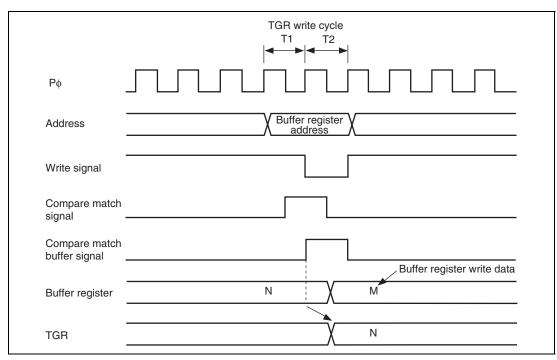

|     | 8.7.6   | Contention between TGR Write and Compare Match                       | 207 |

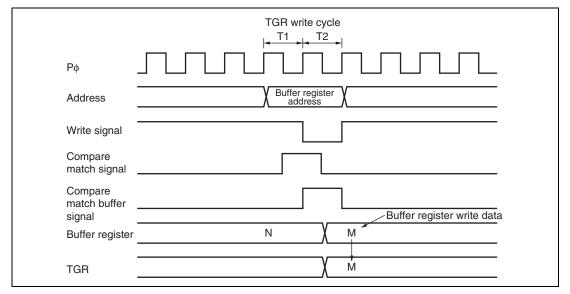

|     | 8.7.7   | Contention between Buffer Register Write and Compare Match           |     |

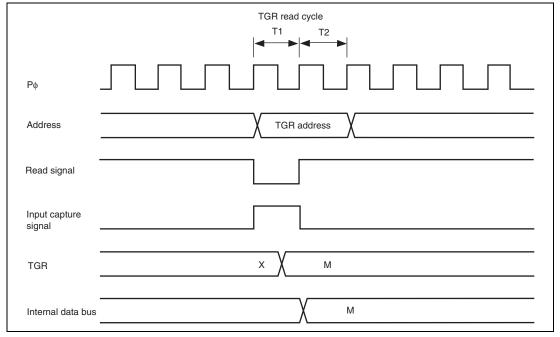

|     | 8.7.8   | Contention between TGR Read and Input Capture                        | 210 |

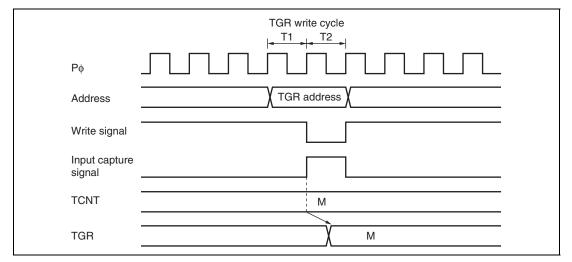

|     | 8.7.9   | Contention between TGR Write and Input Capture                       | 211 |

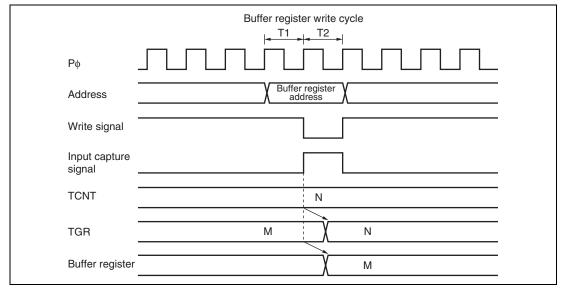

|     | 8.7.10  | Contention between Buffer Register Write and Input Capture           | 212 |

|     | 8.7.11  | TCNT_2 Write and Overflow/Underflow Contention in Cascade Connection | 212 |

|     | 8.7.12  | Counter Value during Complementary PWM Mode Stop                     | 214 |

|     | 8.7.13  | Buffer Operation Setting in Complementary PWM Mode                   | 214 |

|     | 8.7.14  | Reset Sync PWM Mode Buffer Operation and Compare Match Flag          | 215 |

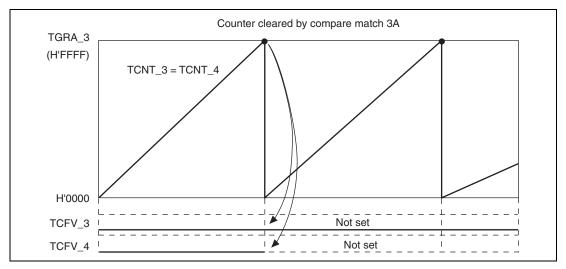

|     | 8.7.15  | Overflow Flags in Reset Sync PWM Mode                                | 216 |

|     | 8.7.16  | Contention between Overflow/Underflow and Counter Clearing           | 217 |

|     | 8.7.17  | Contention between TCNT Write and Overflow/Underflow                 | 218 |

|     | 8.7.18  | Cautions on Transition from Normal Operation or PWM Mode 1 to        |     |

|     |         | Reset-Synchronous PWM Mode                                           | 218 |

|            | 8.7.19         | Output Level in Complementary PWM Mode and                             |     |

|------------|----------------|------------------------------------------------------------------------|-----|

|            |                | Reset-Synchronous PWM Mode                                             | 219 |

|            | 8.7.20         | Interrupts in Module Standby Mode                                      | 219 |

|            | 8.7.21         | Simultaneous Input Capture of TCNT_1 and TCNT_2 in Cascade Connection. | 219 |

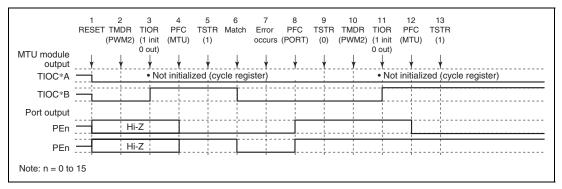

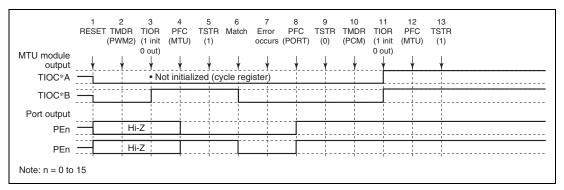

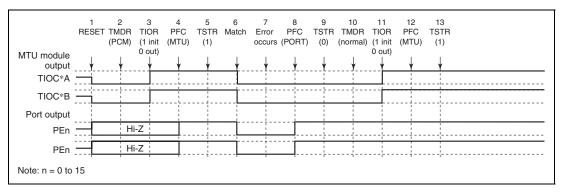

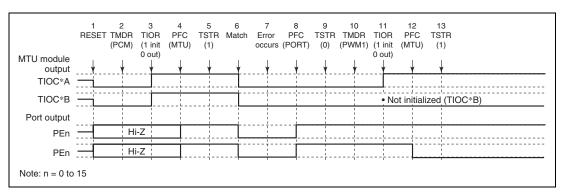

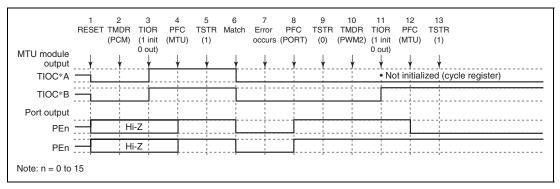

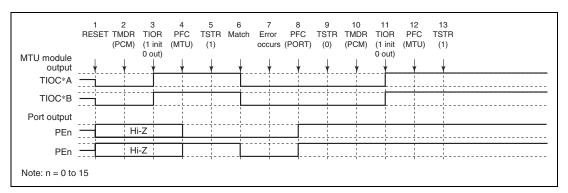

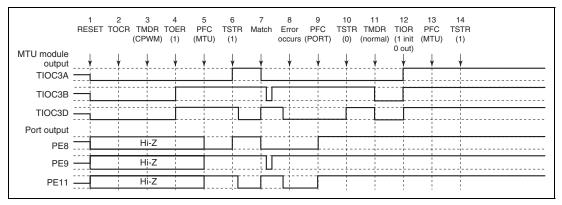

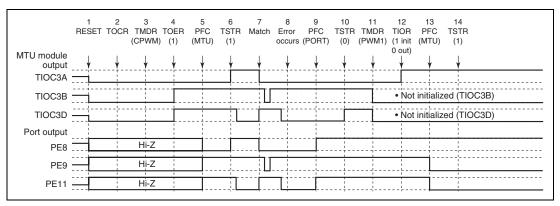

| 8.8        | MTU (          | Output Pin Initialization                                              | 220 |

|            | 8.8.1          | Operating Modes                                                        | 220 |

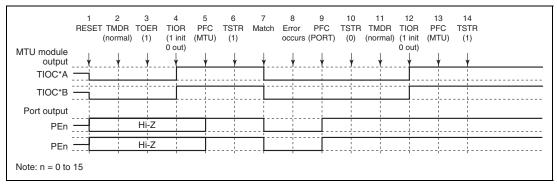

|            | 8.8.2          | Reset Start Operation                                                  | 220 |

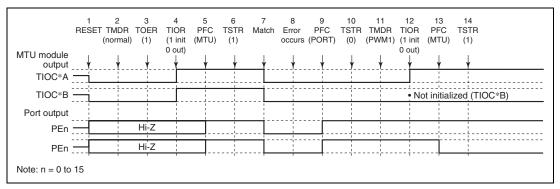

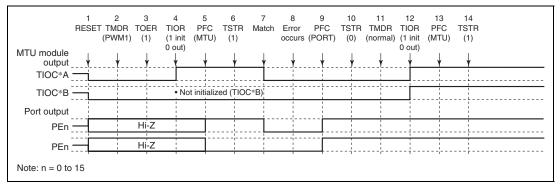

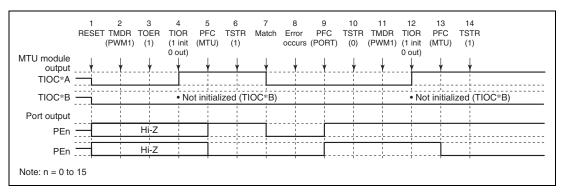

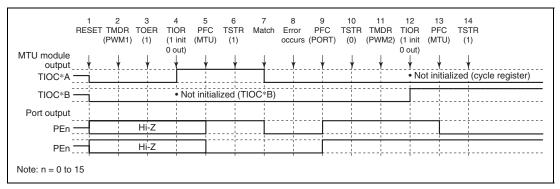

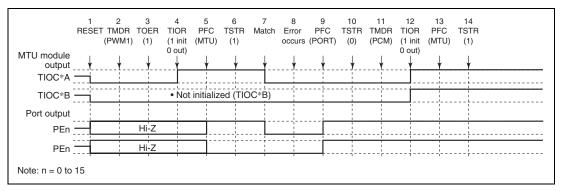

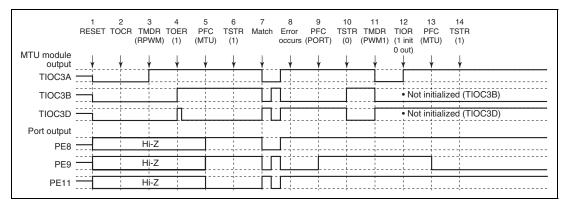

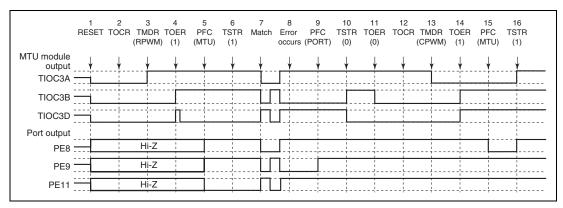

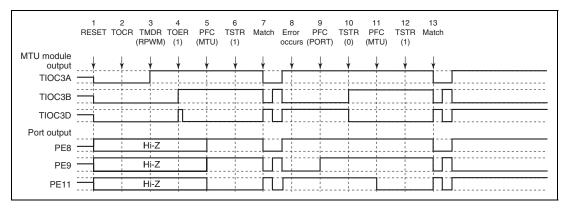

|            | 8.8.3          | Operation in Case of Re-Setting Due to Error During Operation, Etc     |     |

|            | 8.8.4          | Overview of Initialization Procedures and Mode Transitions             |     |

|            |                | in Case of Error during Operation, Etc.                                | 222 |

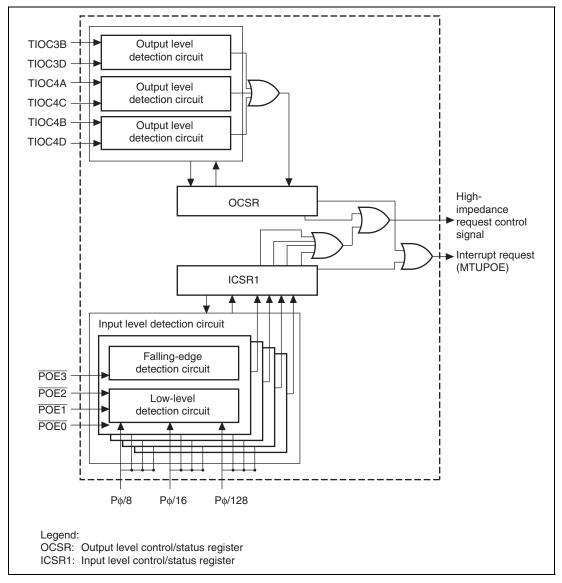

| 8.9        | Port O         | utput Enable (POE)                                                     |     |

|            | 8.9.1          | Features                                                               | 252 |

|            | 8.9.2          | Pin Configuration                                                      |     |

|            | 8.9.3          | Register Configuration                                                 |     |

|            | 8.9.4          | Operation                                                              | 259 |

|            | 8.9.5          | Usage Note                                                             |     |

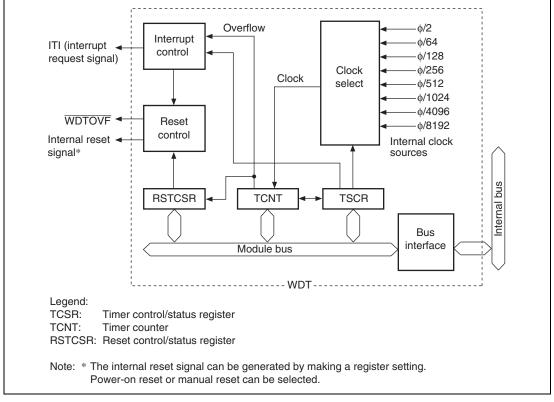

| Saci       | tion 9         | Watchdog Timer                                                         | 263 |

| 9.1        |                | es                                                                     |     |

| 9.1        |                | Output Pin                                                             |     |

| 9.2        |                | er Descriptions                                                        |     |

| 9.3        | 9.3.1          | Timer Counter (TCNT)                                                   |     |

|            | 9.3.1          | Timer Counter (TCN1)                                                   |     |

|            | 9.3.2          | Reset Control/Status Register (RSTCSR)                                 |     |

| 9.4        |                | ion                                                                    |     |

| 9.4        | -              |                                                                        |     |

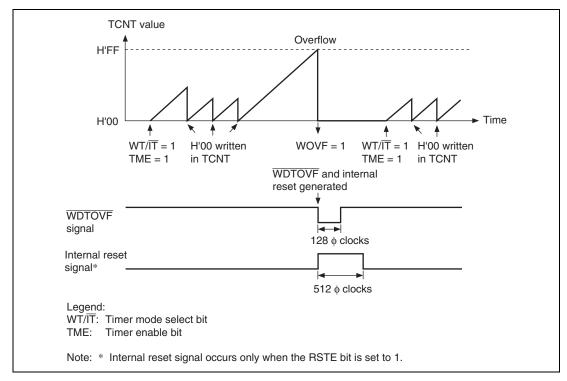

|            | 9.4.1          | Watchdog Timer Mode                                                    |     |

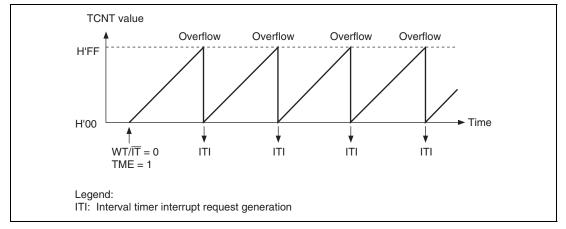

|            | 9.4.2          | Interval Timer Mode                                                    |     |

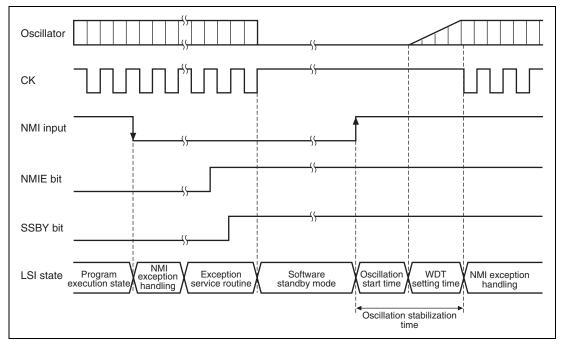

|            | 9.4.3          | Clearing Software Standby Mode                                         |     |

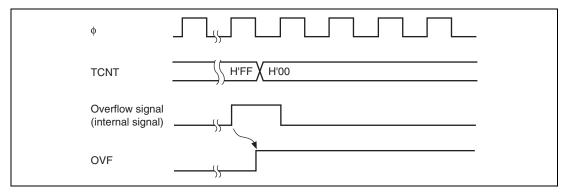

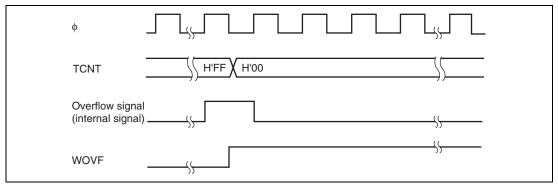

|            | 9.4.4<br>9.4.5 | Timing of Setting the Overflow Flag (OVF)                              |     |

| 0.5        |                |                                                                        |     |

| 9.5<br>9.6 |                | pt Source                                                              |     |

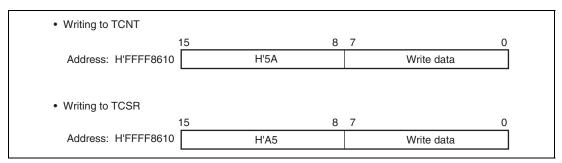

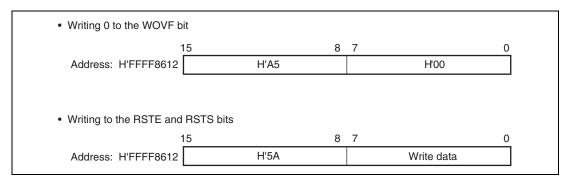

| 9.6        | _              | Notes on Posiston Access                                               |     |

|            | 9.6.1<br>9.6.2 | Notes on Register Access                                               |     |

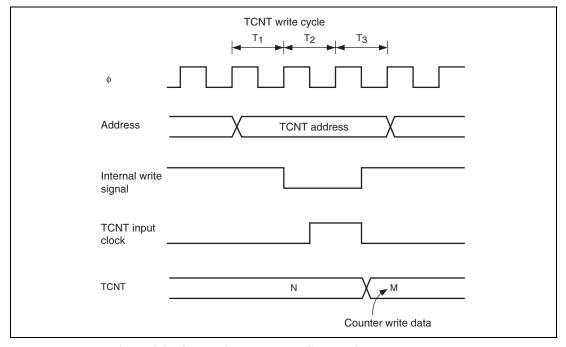

|            |                | TCNT Write and Increment Contention.                                   |     |

|            | 9.6.3          | Changing CKS2 to CKS0 Bit Values                                       |     |

|            | 9.6.4          | Changing between Watchdog Timer/Interval Timer Modes                   |     |

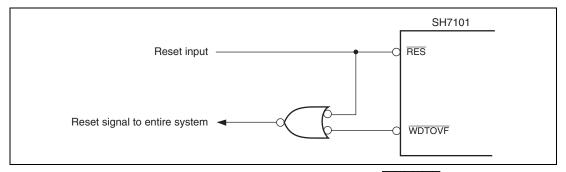

|            | 9.6.5          | System Reset by WDTOVF Signal                                          |     |

|            | 9.6.6          | Internal Reset in Watchdog Timer Mode                                  |     |

|            | 9.6.7          | Manual Reset in Watchdog Timer Mode                                    |     |

|            | 9.6.8          | Notes on Using WDTOVF pin                                              | 276 |

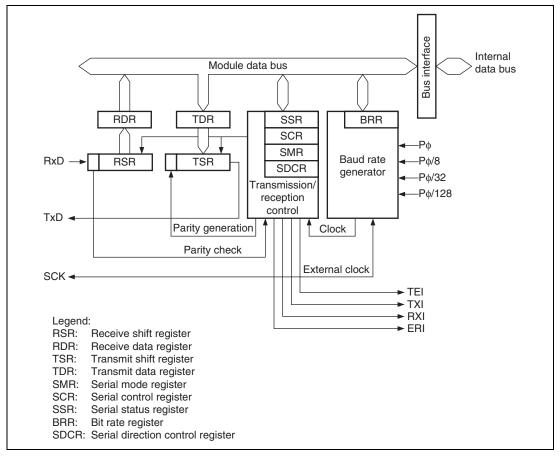

| Secti | ion 10  | Serial Communication Interface (SCI)                     | 277 |

|-------|---------|----------------------------------------------------------|-----|

| 10.1  | Feature | es                                                       | 277 |

| 10.2  | Input/C | Output Pins                                              | 279 |

| 10.3  | Registe | er Descriptions                                          | 279 |

|       | 10.3.1  | Receive Shift Register (RSR)                             | 280 |

|       | 10.3.2  | Receive Data Register (RDR)                              | 280 |

|       | 10.3.3  | Transmit Shift Register (TSR)                            | 280 |

|       | 10.3.4  | Transmit Data Register (TDR)                             | 280 |

|       | 10.3.5  | Serial Mode Register (SMR)                               | 281 |

|       | 10.3.6  | Serial Control Register (SCR)                            | 283 |

|       | 10.3.7  | Serial Status Register (SSR)                             | 285 |

|       | 10.3.8  | Serial Direction Control Register (SDCR)                 | 287 |

|       |         | Bit Rate Register (BRR)                                  |     |

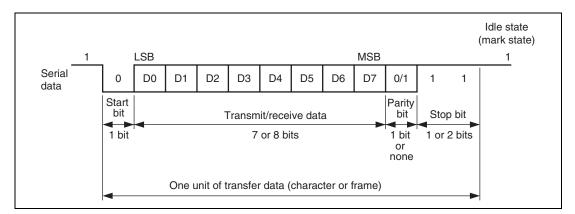

| 10.4  | _       | ion in Asynchronous Mode                                 |     |

|       | 10.4.1  | Data Transfer Format                                     | 296 |

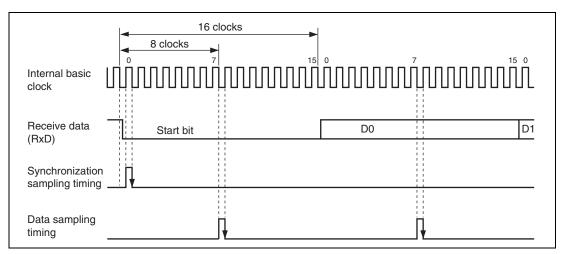

|       | 10.4.2  | Receive Data Sampling Timing and Reception Margin        |     |

|       |         | in Asynchronous Mode                                     | 298 |

|       | 10.4.3  | Clock                                                    | 299 |

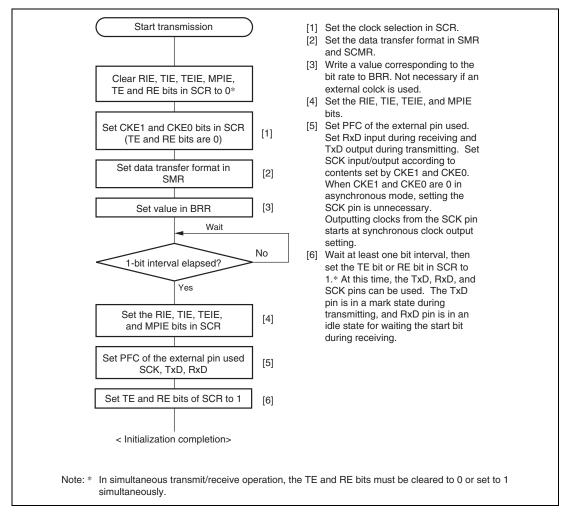

|       | 10.4.4  | SCI Initialization (Asynchronous Mode)                   | 300 |

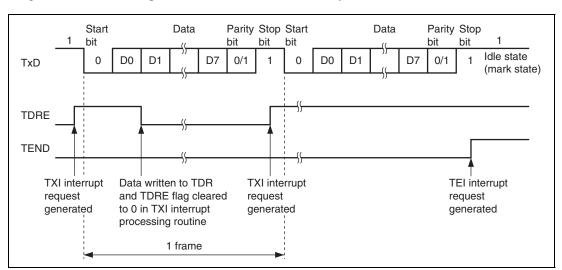

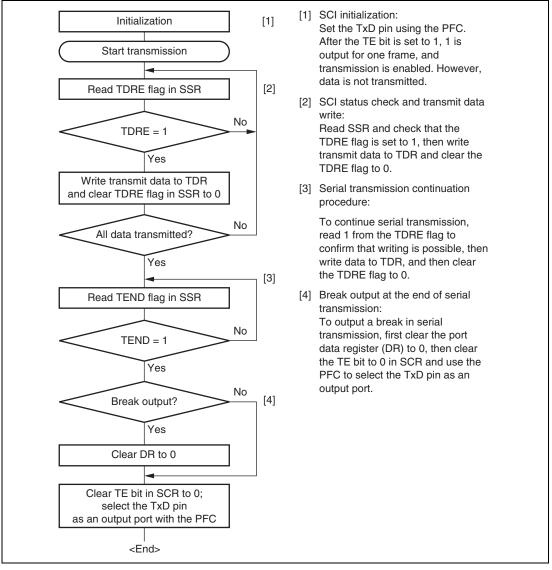

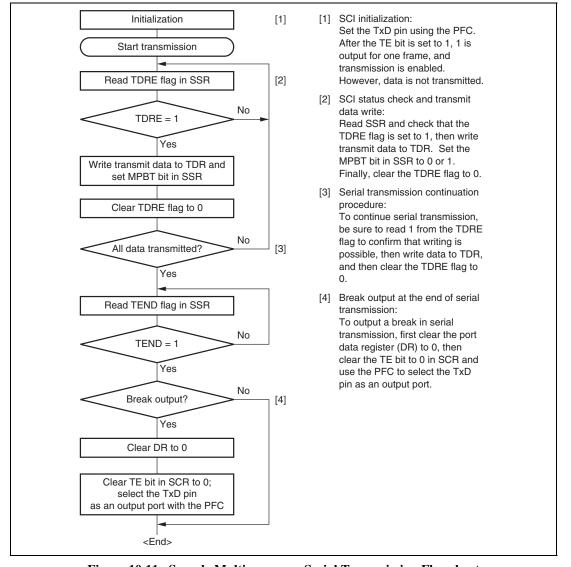

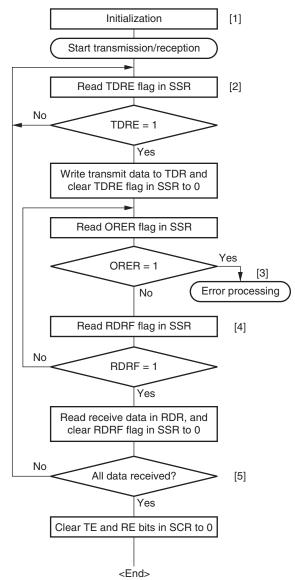

|       | 10.4.5  | Data Transmission (Asynchronous Mode)                    | 301 |

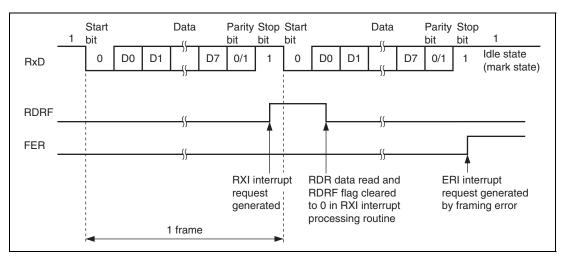

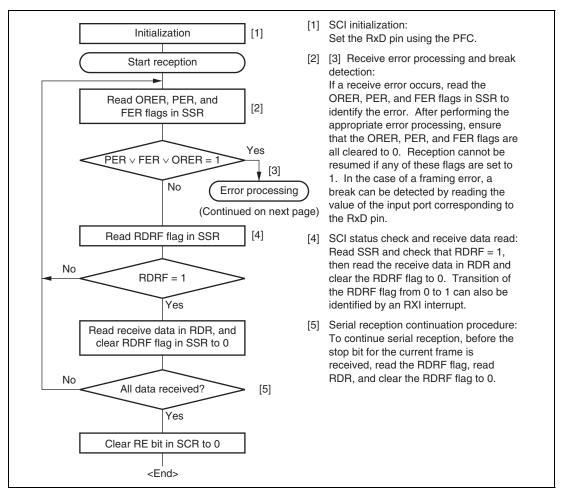

|       | 10.4.6  | Serial Data Reception (Asynchronous Mode)                | 303 |

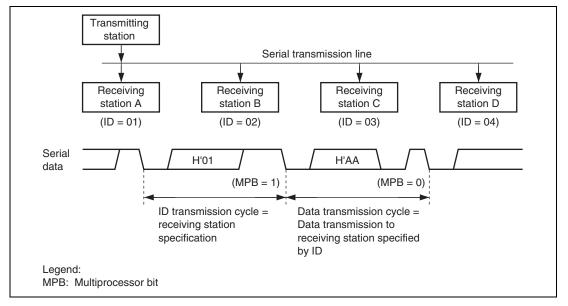

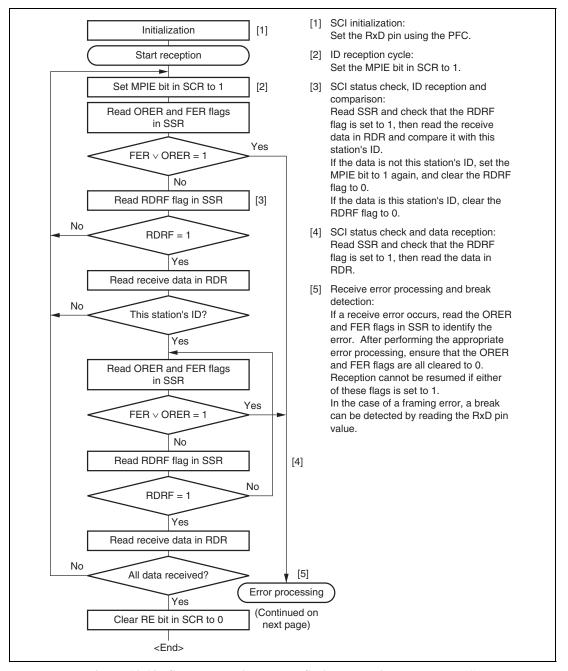

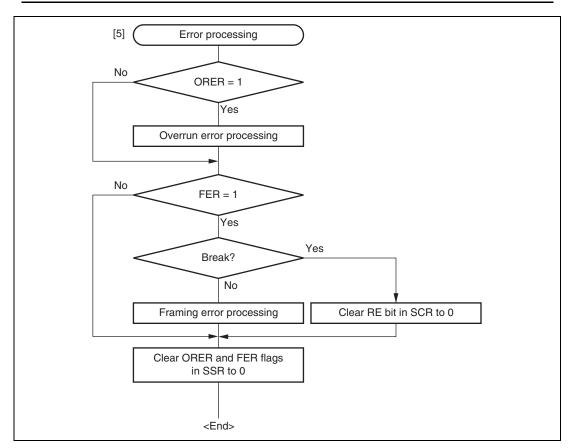

| 10.5  | Multip  | rocessor Communication Function.                         | 307 |

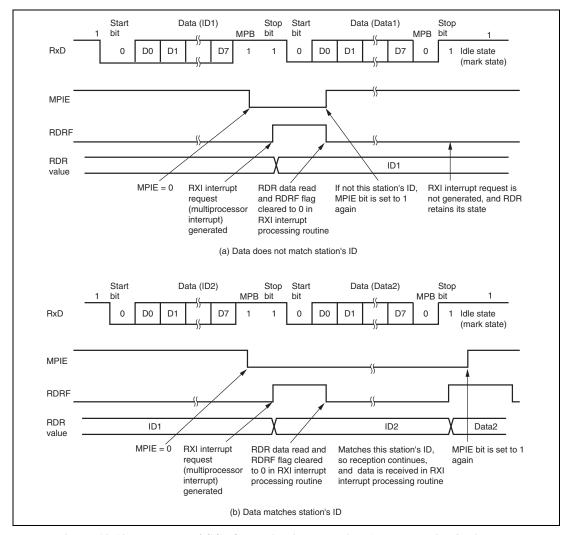

|       |         | Multiprocessor Serial Data Transmission                  |     |

|       |         | Multiprocessor Serial Data Reception                     |     |

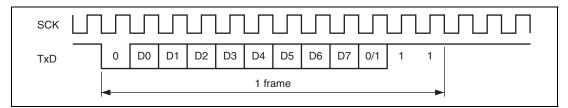

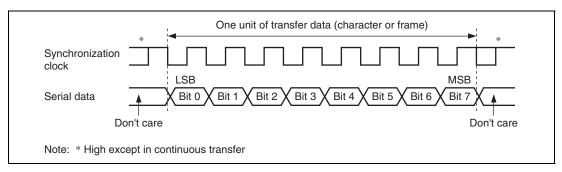

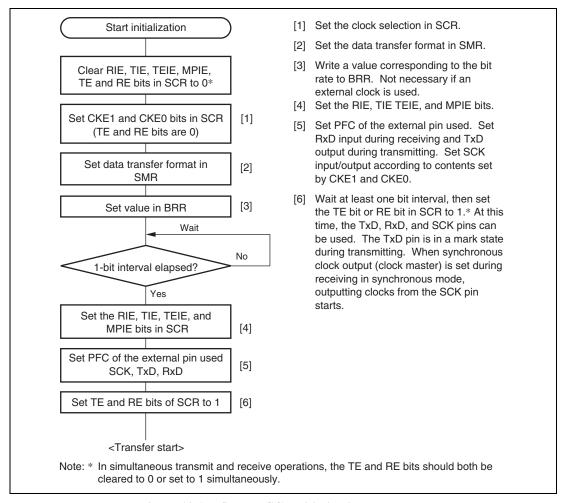

| 10.6  | Operat  | ion in Clocked Synchronous Mode                          | 313 |

|       | 10.6.1  | Clock                                                    | 313 |

|       | 10.6.2  | SCI Initialization (Clocked Synchronous Mode)            | 314 |

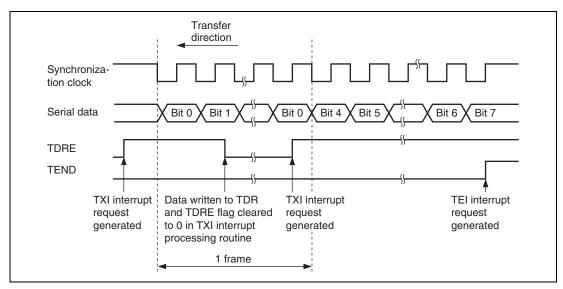

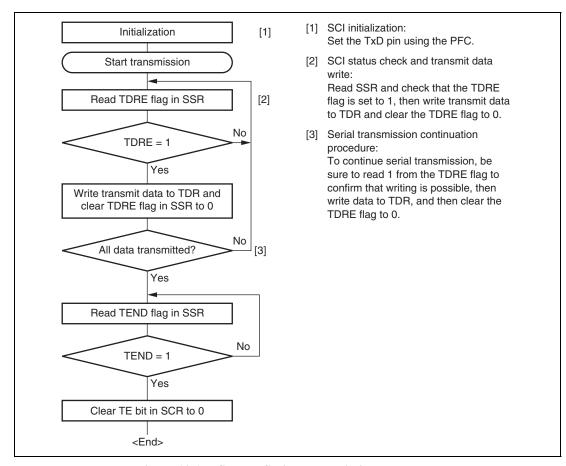

|       |         | Serial Data Transmission (Clocked Synchronous Mode)      |     |

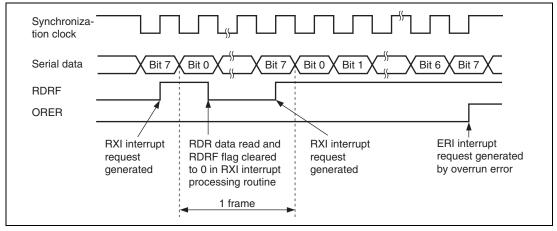

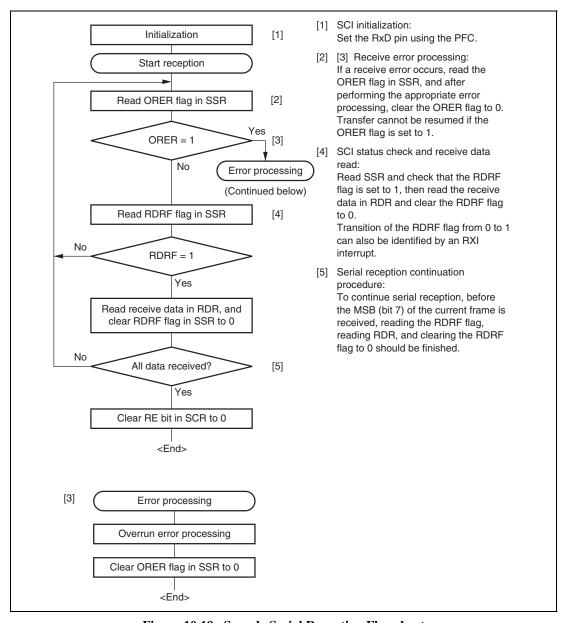

|       | 10.6.4  | Serial Data Reception (Clocked Synchronous Mode)         | 318 |

|       | 10.6.5  |                                                          |     |

|       |         | (Clocked Synchronous Mode)                               |     |

| 10.7  |         | pts Sources                                              |     |

|       | 10.7.1  | Interrupts in Normal Serial Communication Interface Mode | 322 |

| 10.8  | Usage   | Notes                                                    |     |

|       | 10.8.1  | TDR Write and TDRE Flag                                  | 323 |

|       |         | Module Standby Mode Setting                              |     |

|       | 10.8.3  | Break Detection and Processing (Asynchronous Mode Only)  |     |

|       | 10.8.4  |                                                          | 323 |

|       | 10.8.5  | Receive Error Flags and Transmit Operations              |     |

|       |         | (Clocked Synchronous Mode Only)                          | 324 |

|       |         |                                                          |     |

|      | 10.8.6   | Cautions on Clocked Synchronous External Clock Mode         | 324  |

|------|----------|-------------------------------------------------------------|------|

|      | 10.8.7   | Caution on Clocked Synchronous Internal Clock Mode          | 324  |

|      |          |                                                             |      |

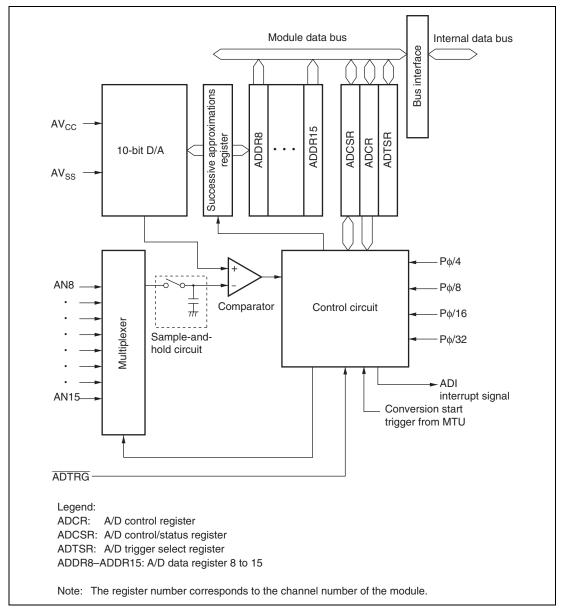

| Sect | ion 11   | A/D Converter                                               | 325  |

| 11.1 |          | S                                                           |      |

| 11.2 | Input/C  | Output Pins                                                 | 327  |

| 11.3 |          | r Descriptions                                              |      |

|      | 11.3.1   | A/D Data Registers 8 to 15 (ADDR8 to ADDR15)                | 328  |

|      | 11.3.2   | A/D Control/Status Registers_0 and _1 (ADCSR_0 and ADCSR_1) | 329  |

|      |          | A/D Control Registers_0 and _1 (ADCR_0 and ADCR_1)          |      |

|      | 11.3.4   | A/D Trigger Select Register (ADTSR)                         | 332  |

| 11.4 | Operati  | ion                                                         | 333  |

|      | 11.4.1   | Single Mode                                                 | 333  |

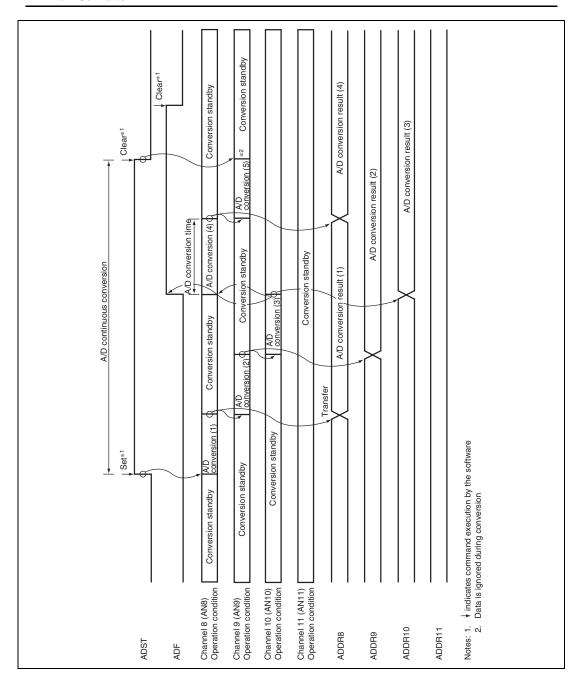

|      | 11.4.2   | Continuous Scan Mode                                        | 333  |

|      | 11.4.3   | Single-Cycle Scan Mode                                      | 335  |

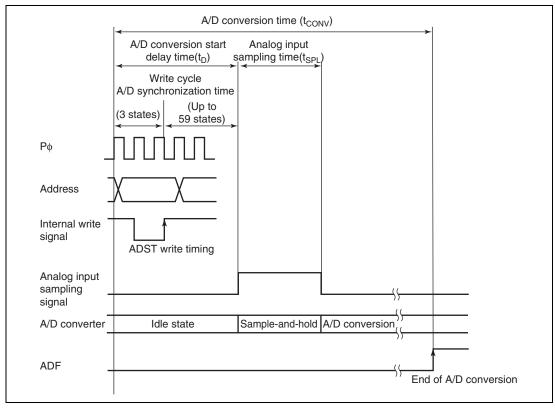

|      | 11.4.4   | Input Sampling and A/D Conversion Time                      | 335  |

|      | 11.4.5   | A/D Converter Activation by MTU                             | 337  |

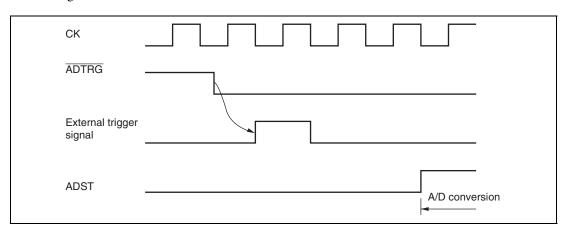

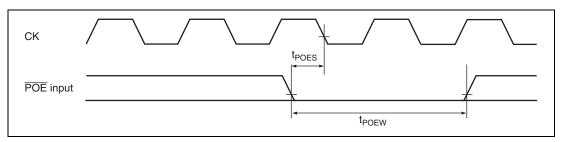

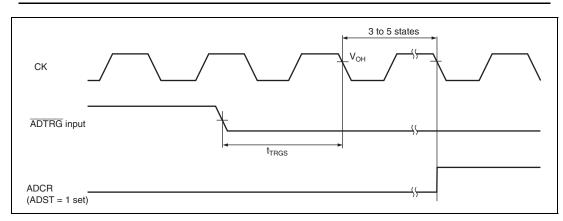

|      | 11.4.6   | External Trigger Input Timing                               | 337  |

| 11.5 | Interruj | pt Sources                                                  | 338  |

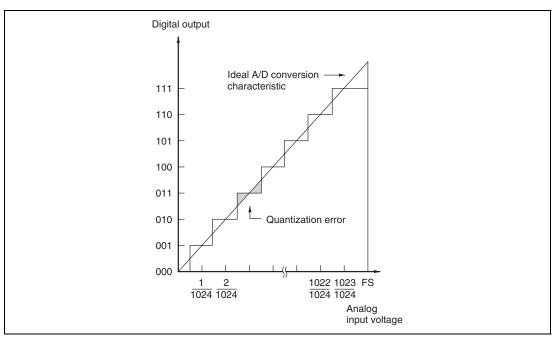

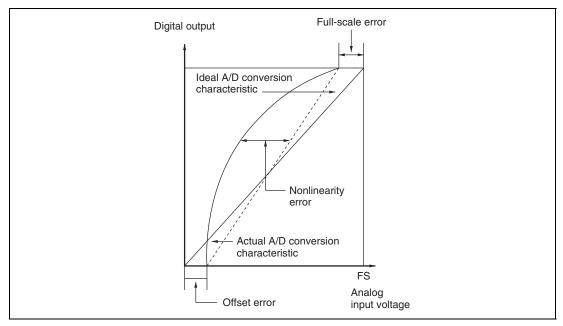

| 11.6 | Definit  | ions of A/D Conversion Accuracy                             | 338  |

| 11.7 | Usage 1  | Notes                                                       | 340  |

|      | 11.7.1   | Module Standby Mode Setting                                 | 340  |

|      | 11.7.2   | Permissible Signal Source Impedance                         | 340  |

|      | 11.7.3   | Influences on Absolute Accuracy                             | 340  |

|      | 11.7.4   | Range of Analog Power Supply and Other Pin Settings         | 341  |

|      | 11.7.5   | Notes on Board Design                                       | 341  |

|      | 11.7.6   | Notes on Noise Countermeasures                              | 341  |

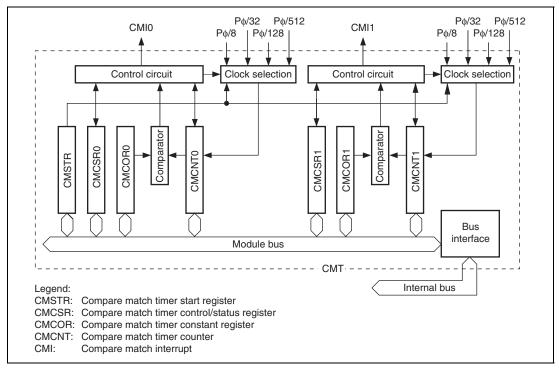

| Sect | ion 12   | Compare Match Timer (CMT)                                   | 343  |

| 12.1 |          | es                                                          |      |

| 12.2 |          | er Descriptions                                             |      |

| 12.2 | _        | Compare Match Timer Start Register (CMSTR)                  |      |

|      |          | Compare Match Timer Start Register (CMSTR)                  |      |

|      | 12,2,2   | (CMCSR_0, CMCSR_1)                                          | 3/15 |

|      | 1223     | Compare Match Timer Counter_0 and _1 (CMCNT_0, CMCNT_1)     |      |

|      |          | Compare Match Timer Counter_0 and _1 (CMCOR_0, CMCOR_       |      |

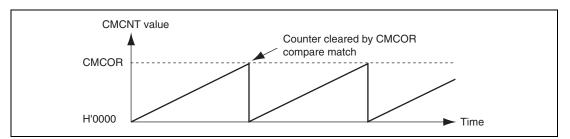

| 12.3 |          | ion                                                         |      |

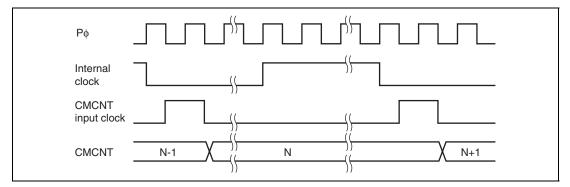

| 14.5 | -        | Cyclic Count Operation                                      |      |

|      |          | CMCNT Count Timing                                          |      |

| 12.4 |          | pts                                                         |      |

| 14.4 | mumu     | μιο                                                         | 5+1  |

|      | 12.4.1  | Interrupt Sources                                                  | 347 |

|------|---------|--------------------------------------------------------------------|-----|

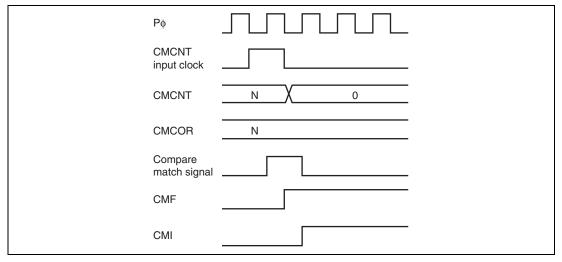

|      | 12.4.2  | Compare Match Flag Set Timing                                      | 347 |

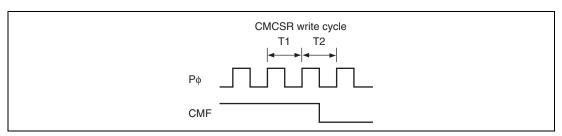

|      | 12.4.3  | Compare Match Flag Clear Timing                                    | 348 |

| 12.5 | Usage 1 | Notes                                                              | 349 |

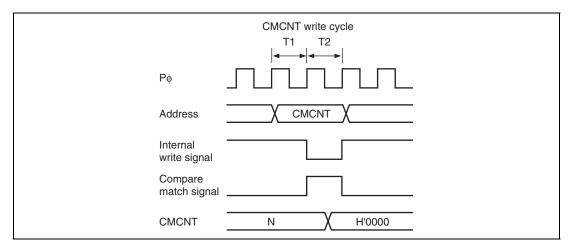

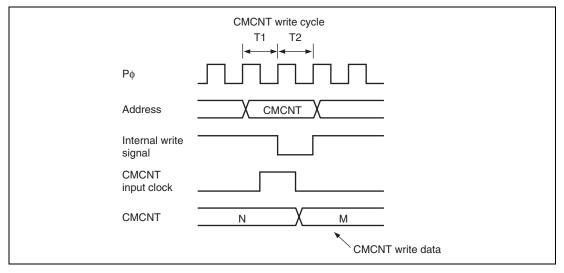

|      | 12.5.1  | Contention between CMCNT Write and Compare Match                   | 349 |

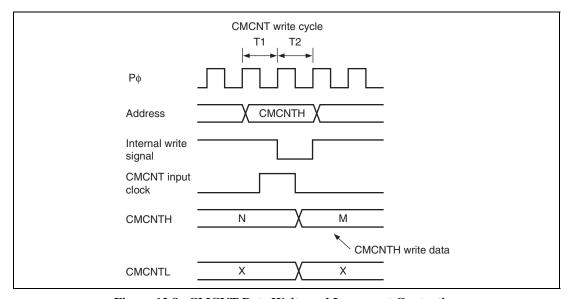

|      |         | Contention between CMCNT Word Write and Incrementation             |     |

|      | 12.5.3  | Contention between CMCNT Byte Write and Incrementation             | 351 |

| Sect | ion 13  | Pin Function Controller (PFC)                                      | 353 |

| 13.1 | Registe | er Descriptions                                                    | 360 |

|      | 13.1.1  | Port A I/O Register L (PAIORL)                                     | 360 |

|      | 13.1.2  | Port A Control Registers L3 to L1 (PACRL3 to PACRL1)               | 361 |

|      | 13.1.3  | Port B I/O Register (PBIOR)                                        | 364 |

|      | 13.1.4  | Port B Control Registers 1 and 2 (PBCR1 and PBCR2)                 | 365 |

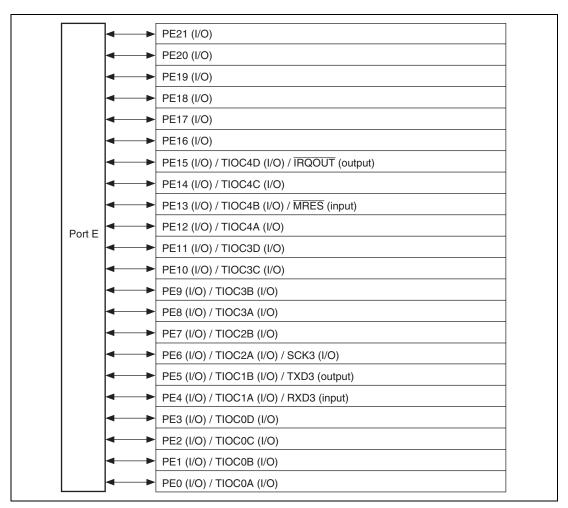

|      | 13.1.5  | Port E I/O Registers L and H (PEIORL and PEIORH)                   | 366 |

|      | 13.1.6  | Port E Control Registers L1, L2, and H (PECRL1, PECRL2, and PECRH) | 366 |

| 13.2 |         | Notes                                                              |     |

|      | 13.2.1  | Note on PFC Setting                                                | 370 |

|      |         | Note on PFC Setting Order                                          |     |

| Sect | ion 14  | I/O Ports                                                          | 371 |

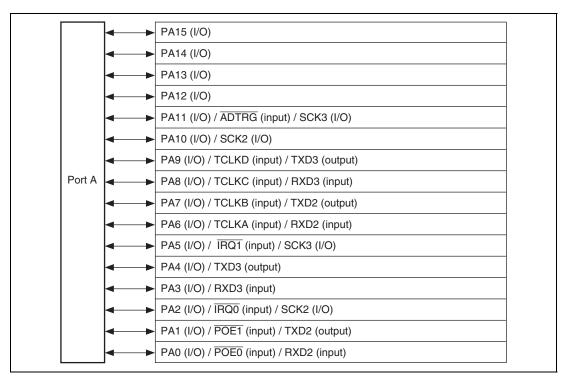

| 14.1 | Port A  |                                                                    | 371 |

|      | 14.1.1  | Register Description                                               | 372 |

|      | 14.1.2  | Port A Data Register L (PADRL)                                     |     |

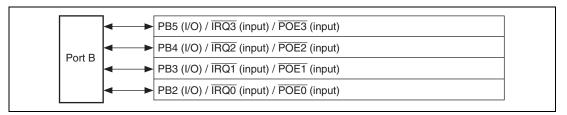

| 14.2 | Port B  |                                                                    |     |

|      | 14.2.1  | Register Description                                               | 374 |

|      | 14.2.2  | Port B Data Register (PBDR)                                        |     |

| 14.3 | Port E  |                                                                    | 376 |

|      | 14.3.1  | Register Descriptions                                              |     |

|      | 14.3.2  | Port E Data Registers H and L (PEDRH and PEDRL)                    |     |

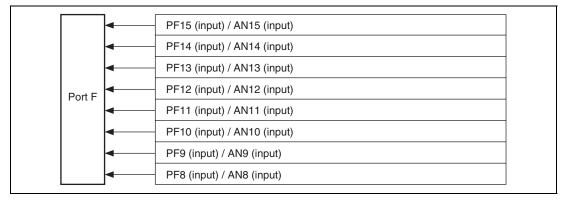

| 14.4 | Port F  |                                                                    | 379 |

|      | 14.4.1  | Register Description                                               |     |

|      | 14.4.2  | Port F Data Register (PFDR)                                        |     |

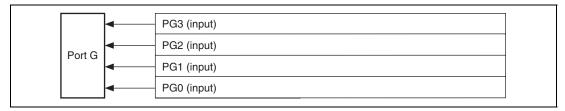

| 14.5 | Port G  |                                                                    |     |

|      | 14.5.1  | Register Description                                               |     |

|      |         | Port G Data Register (PGDR)                                        |     |

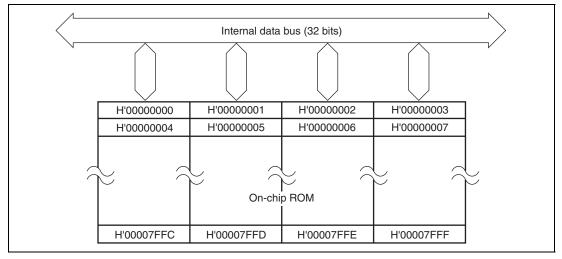

| Sect | ion 15  | Mask ROM                                                           | 383 |

| 15 1 | Hsage ' | Note                                                               | 383 |

| Secti | on 16   | RAM                                                              | 385 |

|-------|---------|------------------------------------------------------------------|-----|

| 16.1  | Usage   | Note                                                             | 385 |

|       | C       |                                                                  |     |

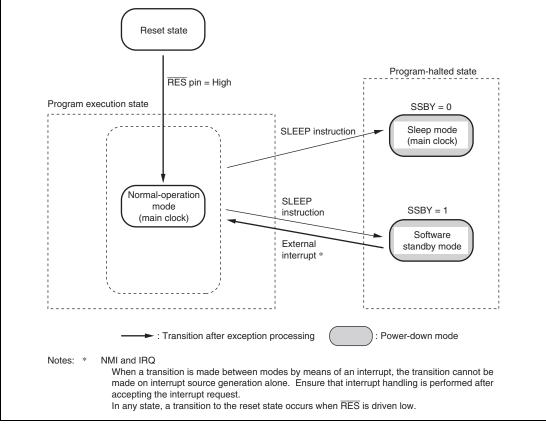

| Secti | on 17   | Power-Down Modes                                                 | 387 |

| 17.1  | Input/C | Output Pins                                                      | 389 |

| 17.2  | Registe | er Descriptions                                                  | 390 |

|       | 17.2.1  | Standby Control Register (SBYCR)                                 | 390 |

|       | 17.2.2  | System Control Register (SYSCR)                                  | 392 |

|       | 17.2.3  | Module Standby Control Register 1 and 2 (MSTCR1 and MSTCR2)      | 393 |

| 17.3  | Operat  | ion                                                              | 395 |

|       | 17.3.1  | Sleep Mode                                                       | 395 |

|       | 17.3.2  | Software Standby Mode                                            | 396 |

|       | 17.3.3  | Module Standby Mode                                              | 398 |

| 17.4  | Usage   | Notes                                                            | 399 |

|       | 17.4.1  | I/O Port Status                                                  | 399 |

|       | 17.4.2  | Current Consumption during Oscillation Stabilization Wait Period | 399 |

|       | 17.4.3  | On-Chip Peripheral Module Interrupt                              | 399 |

|       | 17.4.4  | Writing to MSTCR1 and MSTCR2                                     | 399 |

|       |         |                                                                  |     |

| Secti |         | List of Registers                                                |     |

| 18.1  | _       | er Addresses (Order of Address)                                  |     |

| 18.2  |         | er Bits                                                          |     |

| 18.3  | Registe | er States in Each Operating Mode                                 | 415 |

| Secti | on 19   | Electrical Characteristics                                       | 421 |

| 19.1  |         | te Maximum Ratings                                               |     |

| 19.2  |         | aracteristics                                                    |     |

| 19.3  | AC Ch   | aracteristics                                                    | 425 |

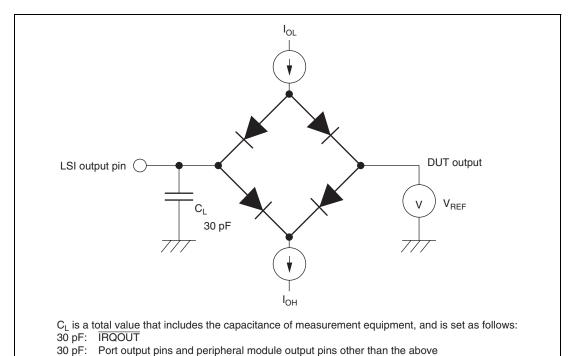

|       | 19.3.1  | Test Conditions for the AC Characteristics                       |     |

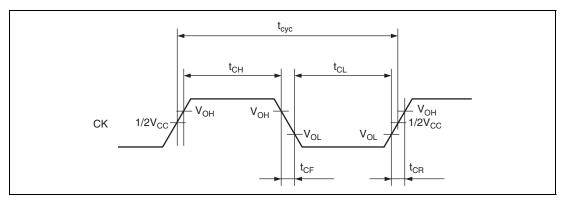

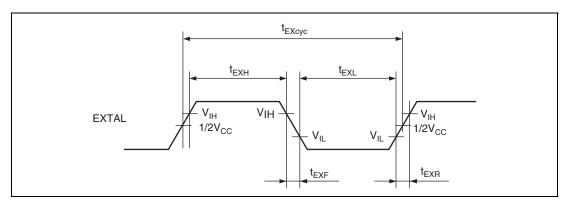

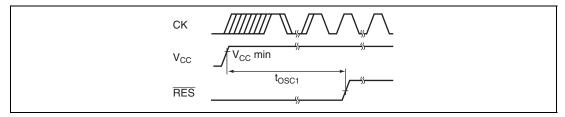

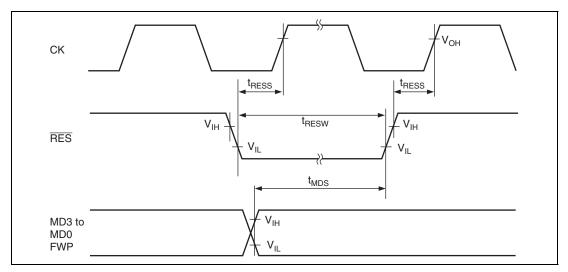

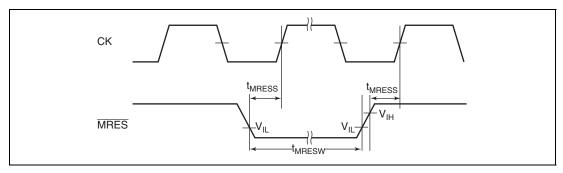

|       | 19.3.2  | Clock Timing                                                     |     |

|       |         | Control Signal Timing                                            |     |

|       |         | Multi-Function Timer Pulse Unit (MPU) Timing                     |     |

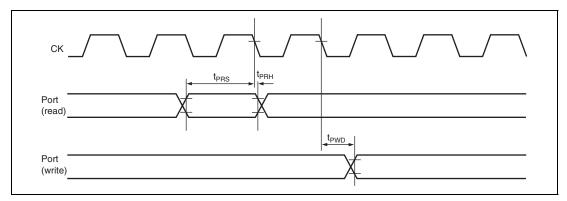

|       | 19.3.5  | I/O Port Timing                                                  | 432 |

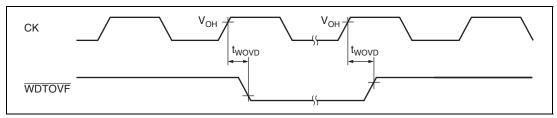

|       |         | Watchdog Timer (WDT) Timing                                      |     |

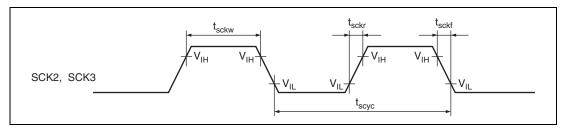

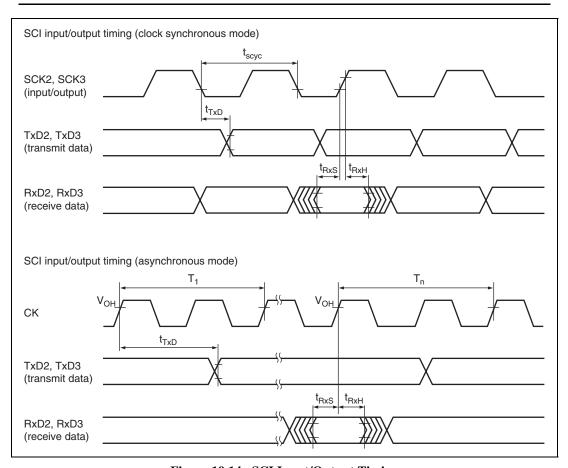

|       | 19.3.7  |                                                                  |     |

|       | 19.3.8  |                                                                  |     |

|       | 19.3.9  | A/D Converter Timing                                             | 436 |

| 19.4  | A/D C   | onverter Characteristics                                         |     |

|       |         |                                                                  |     |

| Appe  | endix A | A Pin States                                                     | 439 |

| Appendix B | Product Lineup     | 441 |

|------------|--------------------|-----|

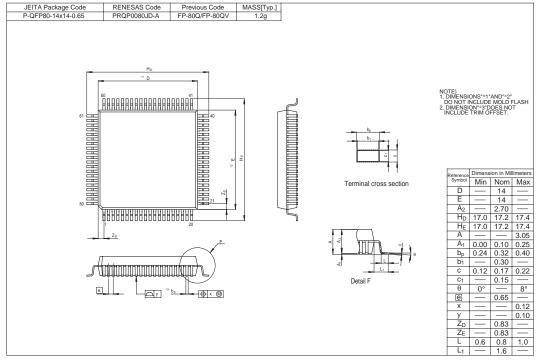

| Appendix C | Package Dimensions | 443 |

| Index      |                    | 445 |

# Figures

| Section 1   | Overview                                                            |     |

|-------------|---------------------------------------------------------------------|-----|

| Figure 1.1  | Internal Block Diagram of SH7101                                    | 3   |

| Figure 1.2  | SH7101 Pin Arrangement                                              | 4   |

| Section 2   | CPU                                                                 |     |

| Figure 2.1  | CPU Internal Registers                                              | 12  |

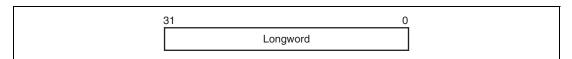

| Figure 2.2  | Data Format in Registers                                            |     |

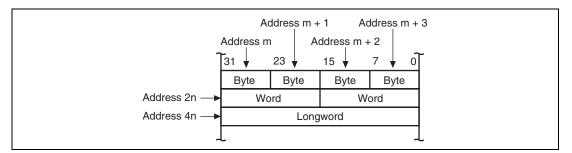

| Figure 2.3  | Data Formats in Memory                                              |     |

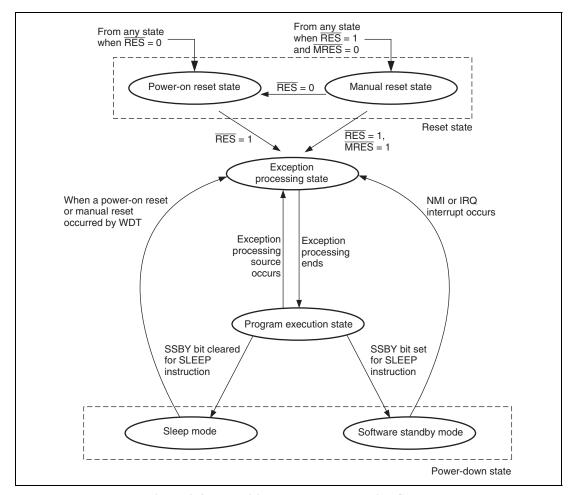

| Figure 2.4  | Transitions between Processing States                               |     |

| Section 3   | MCU Operating Modes                                                 |     |

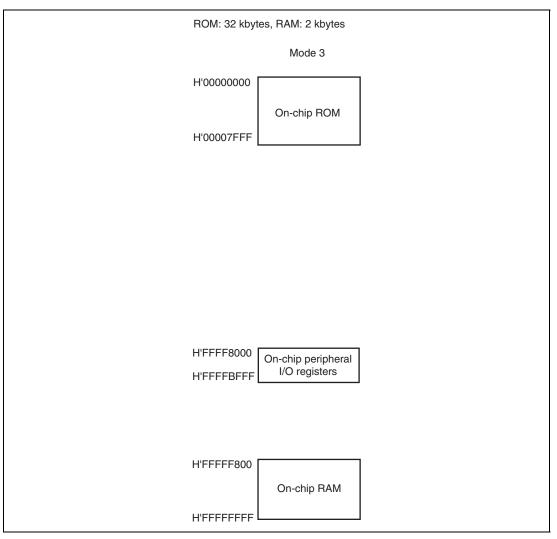

| Figure 3.1  | Address Map for SH7101 Mask ROM Version                             | 45  |

| Section 4   | Clock Pulse Generator                                               |     |

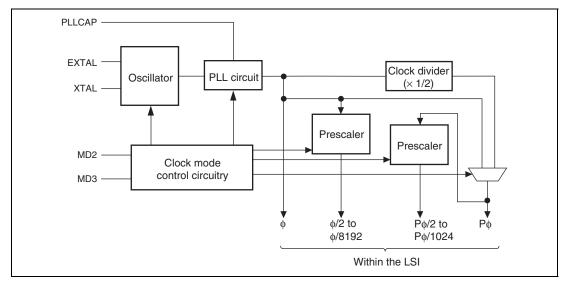

| Figure 4.1  | Block Diagram of Clock Pulse Generator                              | 47  |

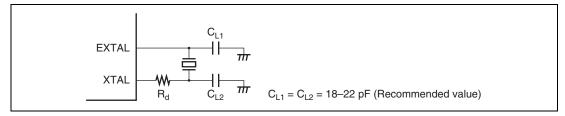

| Figure 4.2  | Connection of Crystal Resonator (Example)                           | 48  |

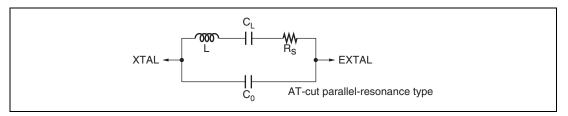

| Figure 4.3  | Crystal Resonator Equivalent Circuit                                | 48  |

| Figure 4.4  | Example of External Clock Connection                                | 49  |

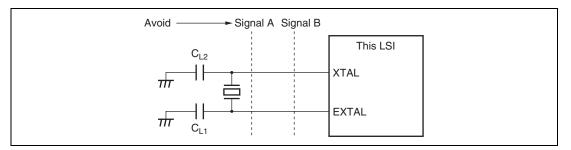

| Figure 4.5  | Cautions for Oscillator Circuit System Board Design                 | 50  |

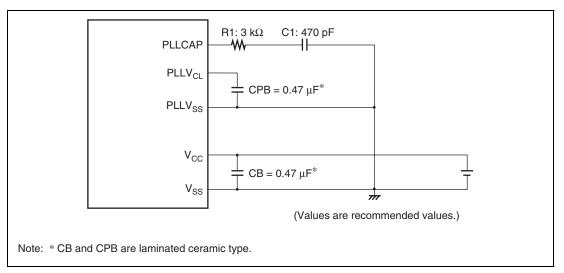

| Figure 4.6  | Recommended External Circuitry around PLL                           | 51  |

| Section 6   | Interrupt Controller (INTC)                                         |     |

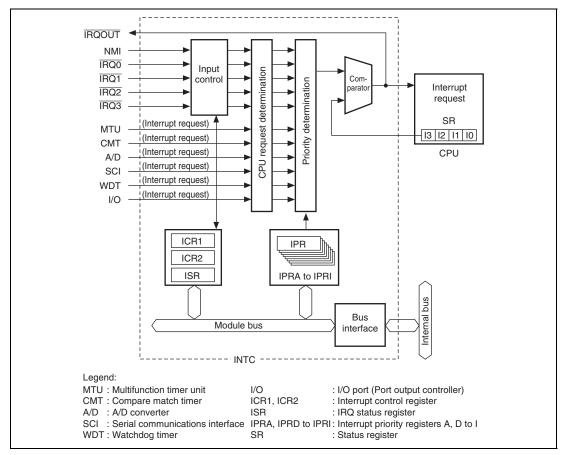

| Figure 6.1  | INTC Block Diagram                                                  | 67  |

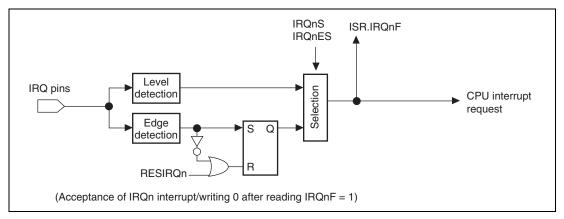

| Figure 6.2  | Block Diagram of IRQ3 to IRQ0 Interrupts Control                    | 76  |

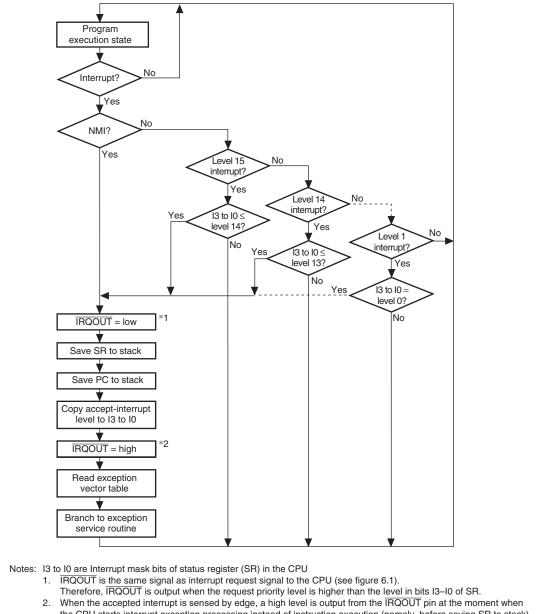

| Figure 6.3  | Interrupt Sequence Flowchart                                        | 82  |

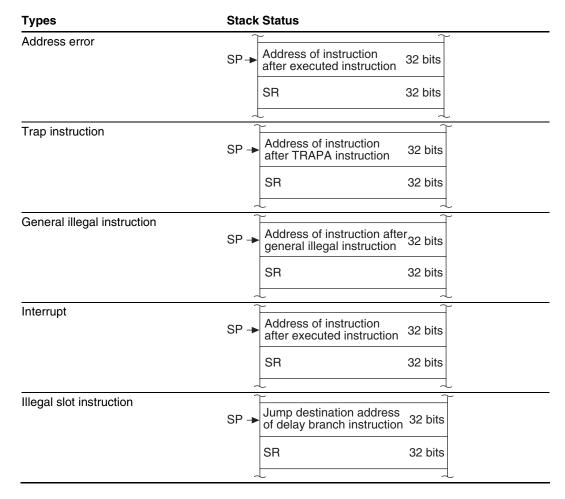

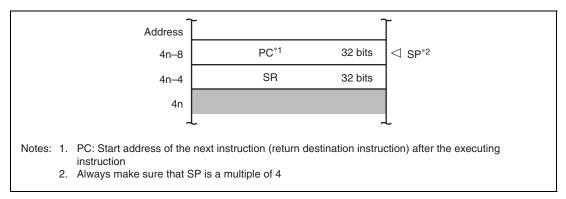

| Figure 6.4  | Stack after Interrupt Exception Processing                          | 83  |

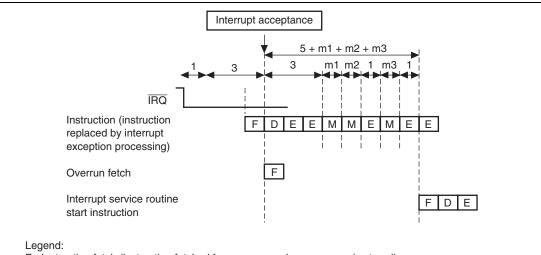

| Figure 6.5  | Example of the Pipeline Operation when an IRQ Interrupt is Accepted | 85  |

| Section 8   | Multi-Function Timer Pulse Unit (MTU)                               |     |

| Figure 8.1  | Block Diagram of MTU                                                |     |

| Figure 8.2  | Complementary PWM Mode Output Level Example                         |     |