# Features

- SRAM based FPGA designed for Space use

- 280K equivalent ASIC gates

- Unlimited reprogrammability

- SEE hardened cells (Configuration RAM, FreeRAM<sup>™</sup>, DFF, JTAG, I/O buffers)

- No need for Triple Modular Redundancy (TMR)

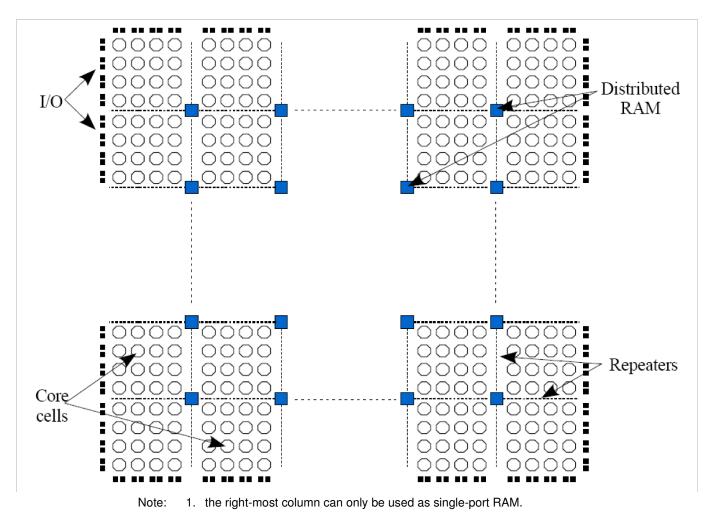

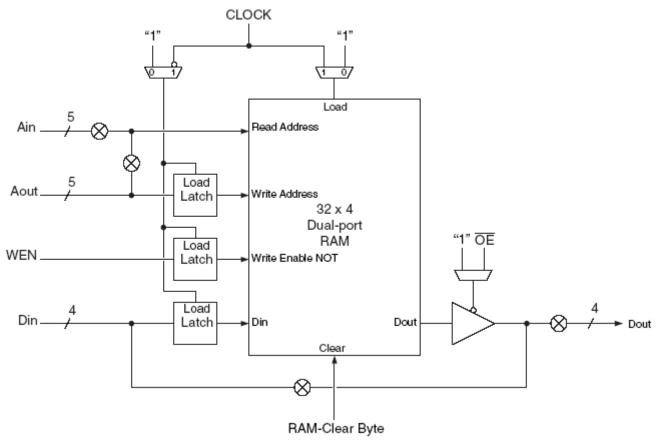

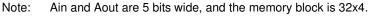

- FreeRAM™:

- 115200 Bits of Distributed RAM

- 32x4 RAM blocks organization

- Independent of Logic Cells

- Single/Dual Port capability

- Synchronous/Asynchronous capability

- Global Reset Option

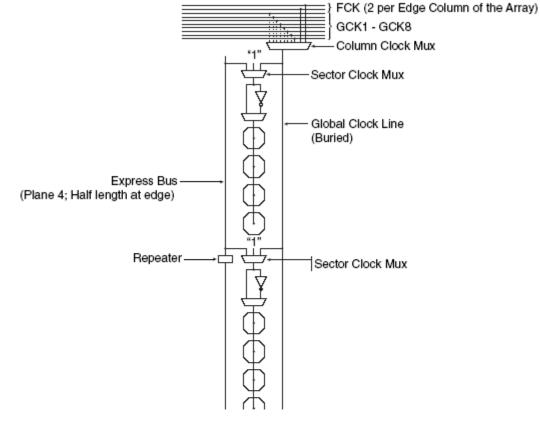

- 8 Global Clocks and 4 Fast Clocks

- 8 LVDS transceivers and 8 LVDS receivers

- Cold sparing and PCI Compliant I/Os

- 308 for 472pins MCGA package

- 150 for 256pins MQFPF package

- Flexible Configuration modes

- Master/Slave Capability

- Serial/Parallel Capability

- Check of the data during FPGA configuration

- Self Integrity Check (SIC) of the configuration during FPGA operation

- Performance

- 100 MHz Internal Performance

- 50MHz System Performance

- 10ns 32X4 FreeRAM™ access time

- Operating range

- Voltages

- 1.65V to 1.95V (Core)

- 3V to 3.6V (Clustered I/Os)

- Temperature

- - 55 ℃ to +125 ℃

- Radiation Performance

- Total Dose tested up to 300 krads (Si)

- No single event latch-up below a LET of 80 MeV/mg/cm2

- ESD better than 2000V

- Quality Grades

- QML-Q or V

- ESCC

- Ceramic packages

- 256pins MQFPF (150 I/Os, 8 LVDS Tx and 8 LVDS Rx)

- 472pins MCGA (308 I/Os, 8 LVDS Tx and 8 LVDS Rx)

- Design Kit including

- ATF280E and Configurator Samples

- Evaluation Board

- Software Design Tools

- ISP Cable/Dongle

Rad Hard Reprogrammable FPGA

**ATF280E**

Advance Information

7750A-AERO-07/07

## 1. Description

The ATF280E is a radiation hardened SRAM-based reprogrammable FPGA. It has been especially designed for space application by implementing hardened cells and permanent selfintegrity check mechanism.

The ATF280E is manufactured using the ATMEL 0.18µ rad-hard AT58KRHA CMOS technology.

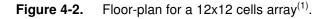

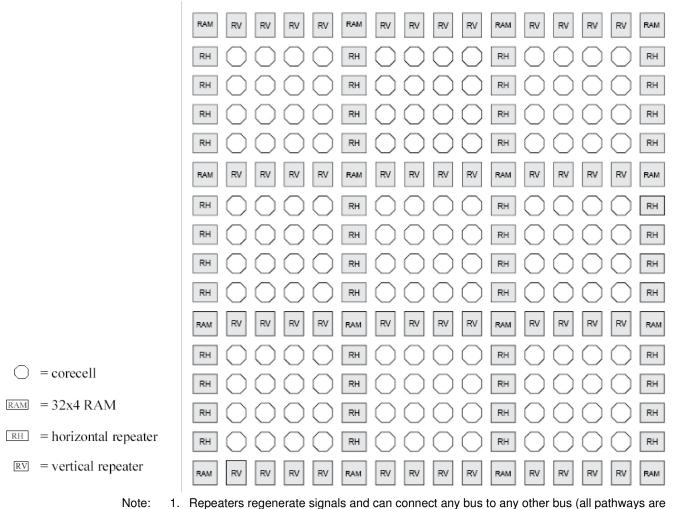

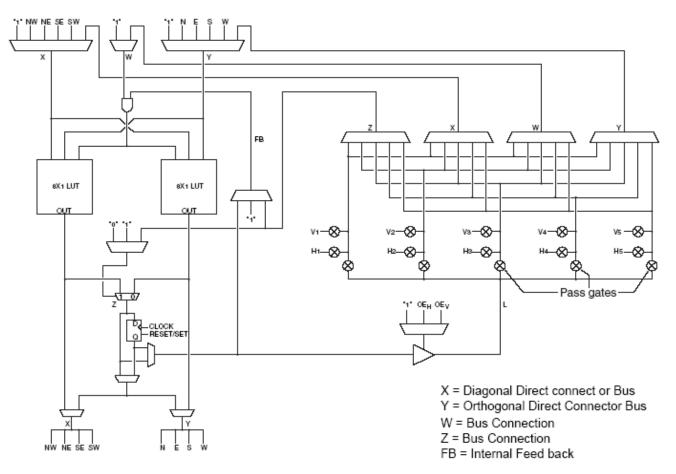

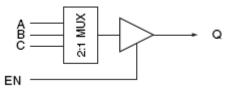

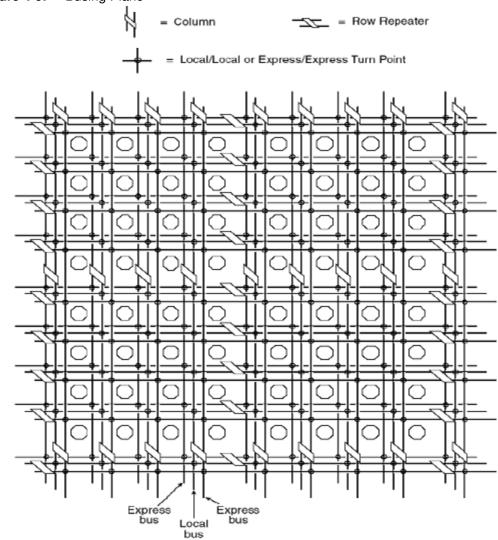

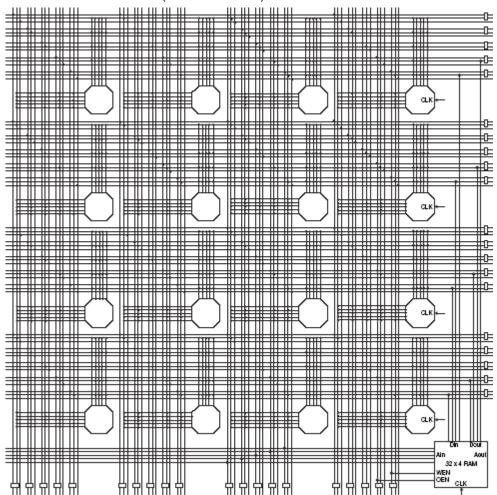

The Atmel architecture is developed to provide the highest levels of performance, functional density and design flexibility in an FPGA. The cells in the Atmel array are small, efficient and can implement any pair of Boolean functions of (the same) three inputs or any single Boolean function of four inputs. The cell's small size leads to arrays with large numbers of cells, greatly multiplying the functionality in each cell. A simple, high-speed busing network provides fast, efficient communication over medium and long distances.

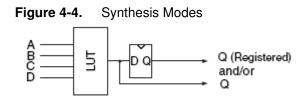

The ATF280E FPGA offers a patented distributed 10 ns SEU hardened SRAM capability where the RAM can be used without losing logic resources. Multiple independent, synchronous or asynchronous, dual port or single port RAM functions (FIFO, scratch pad, etc.) can be created using Atmel's macro generator tool. They are organized by blocks of 32x4 bits. The ATF280E also embeds 8 global clocks, 4 high speed clocks, 8 LVDS Transmit channels, 8 LVDS Receive channels and a complete set of cold sparing programmable I/Os. The ATF280E I/Os are fully PCI-compliant.

The ATF280E is available in two space qualified packages. The MCGA472 package offers up to 324 I/Os for user application. The MQFP256 package is also proposed for application requiring less than 166 I/Os.

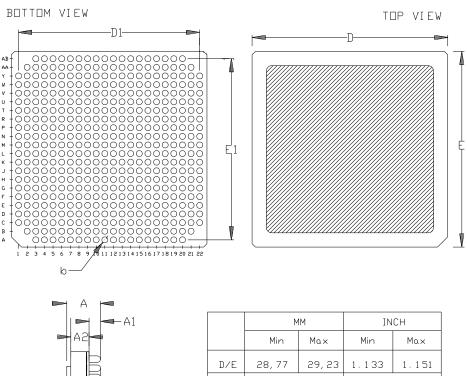

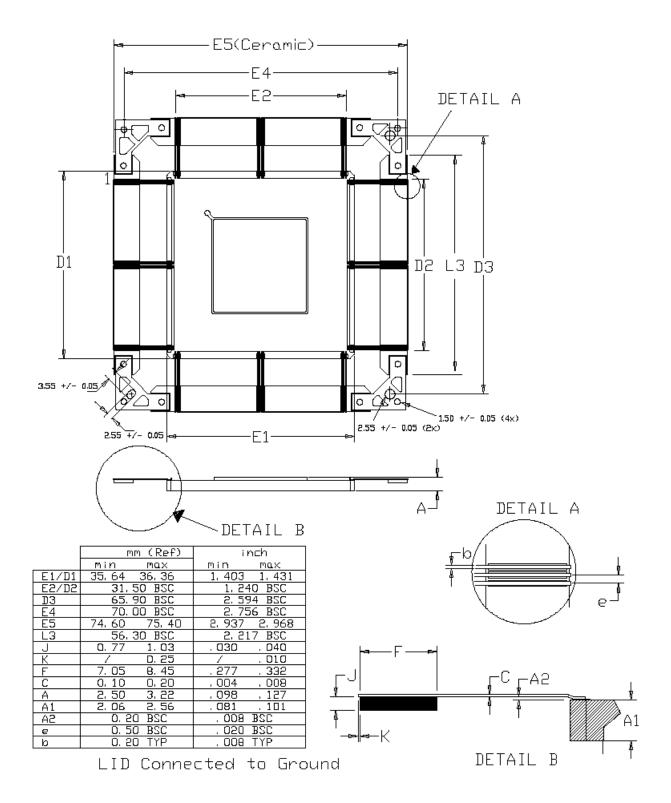

# 2. Pin Configuration

|            | Cirral  | Table 2-1. | LEAD |            |                 | LEAD            | Cinnol         | Olustar |

|------------|---------|------------|------|------------|-----------------|-----------------|----------------|---------|

| LEAD       | Signal  | Cluster    |      | Signal     | Cluster         |                 | Signal         | Cluster |

| A3         | VDD     | 1          | C7   | IO/D2      | 12              | E7              | IO/FCK4        | 12      |

| A4         | VSS     | 1          | C8   | IO/CHECKN  | 12              | E8              | IO             | 12      |

| A5         | IO      | 12         | C9   | IO         | 12              | E9              | IO             | 12      |

| <b>A</b> 6 | VCC     | 12         | C10  | OLVDS6N    | 11              | E10             | VCC            | 12      |

| A7         | IO      | 12         | C11  | OLVDS6     | 11 <b>E11</b>   |                 | IO             | 12      |

| <b>A</b> 8 | VCC     | 12         | C12  | ILVDS5N    | 11 <b>E12</b>   |                 | REFEast        | 11      |

| A9         | IO      | 12         | C13  | ILVDS5     | 11              | E13             | IO             | 10      |

| A10        | IO/D3   | 12         | C14  | IO         | 10              | E14             | Ю              | 10      |

| A11        | VCCB    | 11         | C15  | VCC        | 10              | E15             | VCC            | 10      |

| A12        | IO      | 10         | C16  | IO         | 10              | E16             | IO/FCK3        | 10      |

| A13        | IO      | 10         | C17  | VCC        | 10              | E17             | IO/D5          | 10      |

| A14        | VCC     | 10         | C18  | IO         | 10              | E18             | IO/D6          | 10      |

| A15        | IO      | 10         | C19  | IO         | 10              | E19             | IO             | 9       |

| A16        | IO      | 10         | C20  | VSS        | 4               | E20             | IO             | 9       |

| A17        | IO      | 10         | C21  | VDD        | 5 <b>E21</b> IO |                 | IO             | 9       |

| A18        | VCC     | 10         | C22  | VDD        | 6               | 6 <b>E22</b> IO |                | 9       |

| A19        | VSS     | 1          | D1   | VSS        | 6               | F1 VCC          |                | 1       |

| A20        | VDD     | 3          | D2   | IO/A2/CS1N | 1               | F2              | IO             | 1       |

| B2         | VSS     | 3          | D3   | IO         | 1               | F3              | IO             | 1       |

| B3         | VDD     | 3          | D4   | VCC        | 12              | F4              | IO/A0          | 1       |

| B4         | VCC     | 12         | D5   | IO         | 12              | F5              | IO             | 1       |

| B5         | IO      | 12         | D6   | CCLK       | 12              | F6              | IO             | 12      |

| <b>B6</b>  | IO      | 12         | D7   | IO         | 12              | F7              | IO/GCK6/CSOUTN | 12      |

| B7         | IO      | 12         | D8   | IO         | 12              | F8              | IO/D0          | 12      |

| <b>B</b> 8 | IO      | 12         | D9   | VCC        | 12              | F9              | IO             | 12      |

| B9         | IO      | 12         | D10  | IO         | 12              | F10             | IO             | 12      |

| B10        | OLVDS5N | 11         | D11  | IO         | 12              | F11             | IO             | 12      |

| B11        | OLVDS5  | 11         | D12  | IO/D4      | 10              | F12             | VCC            | 10      |

| B12        | ILVDS6N | 11         | D13  | VCC        | 10              | F13             | IO             | 10      |

| B13        | ILVDS6  | 11         | D14  | IO         | 10              | F14             | IO             | 10      |

| B14        | IO      | 10         | D15  | IO         | 10              | F15             | IO/D7          | 10      |

| B15        | IO/CS0  | 10         | D16  | IO         | 10              | F16             | DIODE          | 10      |

| B16        | VCC     | 10         | D17  | IO         | 10              | F17             | IO             | 9       |

| B17        | IO      | 10         | D18  | IO         | 10              | F18             | VCC            | 9       |

| B18        | IO      | 10         | D19  | VCC        | 9               | F19             | CON            | 9       |

| B19        | IO      | 10         | D20  | IO/D8      | 9               | F20             | VCC            | 9       |

Table 2-1. ATF280E MCGA472 pin assignment

| LEAD | Signal | Cluster | LEAD | Signal | Cluster | LEAD | Signal     | Cluster |

|------|--------|---------|------|--------|---------|------|------------|---------|

| B20  | VDD    | 4       | D21  | VCC    | 9       | F21  | IO/D9      | 9       |

| B21  | VSS    | 3       | D22  | VSS    | 6       | F22  | IO         | 9       |

| C1   | VDD    | 4       | E1   | VCC    | 1       | G1   | IO         | 1       |

| C2   | VDD    | 4       | E2   | IO     | 1       | G2   | VCC        | 1       |

| C3   | VSS    | 4       | E3   | IO     | 1       | G3   | IO         | 1       |

| C4   | IO     | 12      | E4   | IO     | 1       | G4   | IO/A3      | 1       |

| C5   | IO     | 12      | E5   | IO     | 1       | G5   | IO         | 1       |

| C6   | IO     | 12      | E6   | VCC    | 12      | G6   | IO/GCK7/A1 | 1       |

| Table 2-2. | ATF280E MCGA472 pin assignment        |

|------------|---------------------------------------|

|            | A THE LOOP MODE AND A PHIL ADDIGHTION |

| LEAD         Signal         Cluster         LEAD         Signal         Cluster         LEAD         Signal         Cluster           G7         IO         12         J8         VCC         1         L9         IO         3           G8         VCC         12         J9         IO         1         L10         IO/A         1           G9         IO/D1         12         J10         IO         12         L11         IO         1           G10         IO         12         J11         IO         12         L12         IO         10           G11         VCC         12         J12         IO         10         L14         IO         9           G13         IO         10         J15         VCC         9         L16         IO         9           G15         IO         10         J16         IO         9         L17         IO         9           G16         IO         9         J17         IO         9         L18         IO         9           G16         IO         9         J21         IO/D11         9         L21         OLVDS4         8                                                                                                               | LEAD | Signal | Cluster | LEAD | Signal  | Cluster | LEAD | Signal   | Cluster |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|---------|------|---------|---------|------|----------|---------|

| G8         VCC         12         J9         IO         1         L10         IO/A6         1           G9         IO/D1         12         J10         IO         12         L11         IO         1           G10         IO         12         J11         IO         12         L12         IO         10           G11         VCC         12         J13         IO         10         J14         IO         9           G12         IO         10         J14         IO/GCK5         10         L15         VCC         9           G14         IO         10         J16         IO         9         L17         IO         9           G15         IO         10         J16         IO         9         L17         IO         9           G16         IO         9         J17         IO         9         L18         IO         9           G16         IO         9         J20         IO/D11         9         L21         OLVDS4         8           G20         IO         9         J21         IO         9         M1         IO         1           G21                                                                                                                          | -    | -      |         |      | -       |         |      |          |         |

| G9         IO/D1         12         J10         IO         12         L11         IO         1           G10         IO         12         J11         IO         12         L12         IO         10           G11         VCC         12         J12         IO         12         L13         IO         9           G12         IO         10         J13         IO         10         L14         IO         9           G13         IO         10         J14         IO/GCK5         10         L15         VCC         9           G13         IO         10         J15         VCC         9         L16         IO         9           G15         IO         10         J16         IO         9         L17         IO         9           G17         IO/GCK4         9         J18         IO         9         L19         IO         9           G16         IO         9         J20         IO/D11         9         L21         OLVDS3         8           G19         IO         9         J22         IO         9         M1         IO         1         10         <                                                                                                              | -    |        |         |      |         |         |      |          |         |

| G10         IO         12         J11         IO         12         L12         IO         10           G11         VCC         12         J12         IO         12         L13         IO         9           G12         IO         10         J13         IO         10         L14         IO         9           G14         IO         10         J14         IO/GCK5         10         L15         VCC         9           G16         IO         9         J17         IO         9         L16         IO         9           G16         IO         9         J17         IO         9         L18         IO         9           G16         IO         9         J17         IO         9         L19         IO         9           G17         IO/GCK4         9         J18         IO         9         L20         OLVDS4         8           G19         IO         9         J20         IO/D11         9         L21         OLVDS3         8           G20         IO         9         K1         IO         1         M2         OLVDS7         2 <t< th=""><th>-</th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th></t<>                                 | -    |        |         |      |         |         |      |          |         |

| G11         VCC         12         J12         IO         12         L13         IO         9           G12         IO         10         J13         IO         10         L14         IO         9           G13         IO         10         J14         IO/GCK5         10         L15         VCC         9           G15         IO         10         J15         VCC         9         L16         IO         9           G16         IO         9         J17         IO         9         L17         IO         9           G16         IO         9         J17         IO         9         L18         IO         9           G17         IO/GCK4         9         J18         IO         9         L19         OLVDS4         8           G20         IO         9         J22         IO         9         M1         IO         1           G21         IO         9         K1         IO         1         M2         OLVDS3         8           G22         IO         9         K1         IO         1         M2         OLVDS7         2           H1 <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th>                                    |      |        |         |      |         |         |      |          |         |

| G12         IO         10         J13         IO         10         L14         IO         9           G13         IO         10         J14         IO/GCK5         10         L15         VCC         9           G14         IO         10         J15         VCC         9         L16         IO         9           G16         IO         9         J17         IO         9         L17         IO         9           G16         IO         9         J17         IO         9         L18         IO         9           G17         IO/GCK4         9         J18         IO         9         L19         IO         9           G18         IO/D10         9         J20         IO/D11         9         L21         OLVDS3         8           G20         IO         9         J21         IO         9         M1         IO         1         IO         1         IO         1         IO         1         IO         1         IO         1         ID         1         IO         1         M2         OLVDS7         2         M4         VCCB         2         H3         IO <th>-</th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th>          | -    |        |         |      |         |         |      |          |         |

| G13         IO         10         J14         IO/GCK5         10         L15         VCC         9           G14         IO         10         J15         VCC         9         L16         IO         9           G15         IO         10         J16         IO         9         L17         IO         9           G16         IO         9         J17         IO         9         L18         IO         9           G17         IO/GCK4         9         J18         IO         9         L19         IO         9           G18         IO/D10         9         J19         VCC         9         L20         OL/DS4         8           G19         IO         9         J20         IO/D11         9         L21         OL/DS3         8           G20         IO         9         J21         IO         9         M1         IO         1         10         1         10         1         IO         1         IO         1         IO         1         M2         OL/DS7         2         M4         VCCB         2         H3         IO         1         K3         IL/DS7                                                                                                       | -    |        |         |      |         |         |      |          |         |

| G14         IO         10         J15         VCC         9         L16         IO         9           G15         IO         10         J16         IO         9         L17         IO         9           G16         IO         9         J17         IO         9         L18         IO         9           G17         IO/GCK4         9         J18         IO         9         L19         IO         9           G18         IO/D10         9         J19         VCC         9         L20         OLVDS4         8           G19         IO         9         J21         IO         9         L21         OLVDS3         8           G20         IO         9         J21         IO         9         M1         IO         1           G21         IO         9         K1         IO         1         M2         OLVDS7         2           H1         IO/A4         1         K2         ILVDS8         2         M3         OLVDS8         2           H2         IO         1         K4         VCC         1         M5         IO         3           H4 <th>-</th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th>                                  | -    |        |         |      |         |         |      |          |         |

| G15         IO         10         J16         IO         9         L17         IO         9           G16         IO         9         J17         IO         9         L18         IO         9           G17         IO/GCK4         9         J18         IO         9         L19         IO         9           G18         IO/D10         9         J19         VCC         9         L20         OLVDS4         8           G19         IO         9         J20         IO/D11         9         L21         OLVDS3         8           G20         IO         9         J21         IO         9         L21         OLVDS3         8           G21         IO         9         J22         IO         9         M1         IO         1           G22         IO         9         K1         IO         1         M2         OLVDS3         2           H1         IO/A4         1         K2         ILVDS8         2         M3         OLVDS8         2           H2         IO         1         K4         VCC         1         M5         IO         3 <th< th=""><th>-</th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th></th<>                                | -    |        |         |      |         |         |      |          |         |

| G16         IO         9         J17         IO         9         L18         IO         9           G17         IO/GCK4         9         J18         IO         9         L19         IO         9           G18         IO/D10         9         J19         VCC         9         L20         OLVDS4         8           G19         IO         9         J20         IO/D11         9         L21         OLVDS3         8           G20         IO         9         J21         IO         9         L12         IO         7           G21         IO         9         K1         IO         1         M2         OLVDS7         2           H1         IO/A4         1         K2         ILVDS8         2         M3         OLVDS8         2           H2         IO         1         K4         VCC         1         M5         IO         3           H4         IO         1         K5         IO         1         M6         IO         3           H5         VCC         1         K6         VCC         1         M8         IO         3           H6                                                                                                                               | -    |        |         |      |         |         |      |          |         |

| G17         IO/GCK4         9         J18         IO         9         L19         IO         9           G18         IO/D10         9         J19         VCC         9         L20         OLVDS4         8           G19         IO         9         J20         IO/D11         9         L21         OLVDS3         8           G20         IO         9         J21         IO         9         L22         IO         7           G21         IO         9         J22         IO         9         M1         IO         1           G22         IO         9         K1         IO         1         M2         OLVDS7         2           H1         IO/A4         1         K2         ILVDS8         2         M4         VCCB         2           H3         IO         1         K3         ILVDS7         2         M4         VCCB         2           H3         IO         1         K5         IO         1         M5         IO         3           H4         IO         1         K5         IO         1         M6         IO         3           H4                                                                                                                               | -    |        |         |      |         |         |      |          |         |

| G18         IO/D10         9         J19         VCC         9         L20         OLVDS4         8           G19         IO         9         J20         IO/D11         9         L21         OLVDS3         8           G20         IO         9         J21         IO         9         L22         IO         7           G21         IO         9         J22         IO         9         M1         IO         1           G22         IO         9         K1         IO         1         M2         OLVDS7         2           H1         IO/A4         1         K2         ILVDS8         2         M3         OLVDS7         2           H2         IO         1         K3         ILVDS7         2         M4         VCCB         2           H3         IO         1         K5         IO         1         M5         IO         3           H4         IO         1         K5         IO         1         M6         IO         3           H4         IO         1         K6         VCC         1         M7         IO         3           H6                                                                                                                                    | -    |        |         |      |         |         |      |          |         |

| G19         IO         9         J20         IO/D11         9         L21         OLVDS3         8           G20         IO         9         J21         IO         9         L22         IO         7           G21         IO         9         J22         IO         9         M1         IO         1           G22         IO         9         K1         IO         1         M2         OLVDS7         2           H1         IO/A4         1         K2         ILVDS8         2         M3         OLVDS8         2           H2         IO         1         K3         ILVDS7         2         M4         VCCB         2           H3         IO         1         K4         VCC         1         M5         IO         3           H4         IO         1         K5         IO         1         M6         IO         3           H5         VCC         1         K6         VCC         1         M7         IO         3           H6         IO         1         K8         IO         1         M8         IO         3           H7         IO                                                                                                                                   | -    |        |         |      |         |         |      |          |         |

| G20         IO         9         J21         IO         9         L22         IO         7           G21         IO         9         J22         IO         9         M1         IO         1           G22         IO         9         K1         IO         1         M2         OLVDS7         2           H1         IO/A4         1         K2         ILVDS8         2         M3         OLVDS8         2           H2         IO         1         K3         ILVDS7         2         M4         VCCB         2           H3         IO         1         K4         VCC         1         M5         IO         3           H4         IO         1         K5         IO         1         M6         IO         3           H4         IO         1         K6         VCC         1         M7         IO         3           H4         IO         1         K7         IO         1         M8         IO         3           H5         VCC         1         K8         IO         1         M10         IO         3           H7         IO                                                                                                                                             | -    |        |         |      |         |         |      |          |         |

| G21         IO         9         J22         IO         9         M1         IO         1           G22         IO         9         K1         IO         1         M2         OLVDS7         2           H1         IO/A4         1         K2         ILVDS8         2         M3         OLVDS8         2           H2         IO         1         K3         ILVDS7         2         M4         VCCB         2           H3         IO         1         K4         VCC         1         M5         IO         3           H4         IO         1         K5         IO         1         M6         IO         3           H4         IO         1         K6         VCC         1         M7         IO         3           H5         VCC         1         K8         IO         1         M8         IO         3           H6         IO         1         K9         IO         1         M9         IO         3           H7         IO         1         K9         IO         1         M10         IO         3           H7         IO                                                                                                                                                | G19  | IO     | 9       | J20  | IO/D11  | 9       | L21  | OLVDS3   | 8       |

| G22         IO         9         K1         IO         1         M2         OLVDS7         2           H1         IO/A4         1         K2         ILVDS8         2         M3         OLVDS8         2           H2         IO         1         K3         ILVDS7         2         M4         VCCB         2           H3         IO         1         K4         VCC         1         M5         IO         3           H4         IO         1         K5         IO         1         M6         IO         3           H4         IO         1         K5         IO         1         M6         IO         3           H4         IO         1         K5         IO         1         M6         IO         3           H5         VCC         1         K6         VCC         1         M7         IO         3           H6         IO         1         K7         IO         1         M8         IO         3           H7         IO         1         K8         IO         1         M10         IO         3           H8         VCC                                                                                                                                                 | G20  | IO     |         | J21  | IO      | 9       | L22  | IO       | 7       |

| H1         IO/A4         1         K2         ILVDS8         2         M3         OLVDS8         2           H2         IO         1         K3         ILVDS7         2         M4         VCCB         2           H3         IO         1         K4         VCC         1         M5         IO         3           H4         IO         1         K5         IO         1         M6         IO         3           H4         IO         1         K5         IO         1         M6         IO         3           H4         IO         1         K6         VCC         1         M7         IO         3           H5         VCC         1         K7         IO         1         M8         IO         3           H6         IO         1         K7         IO         1         M9         IO         3           H7         IO         1         K8         IO         1         M10         IO         3           H7         IO         12         K10         TCK         1         M11         IO         4           H10         IO         <                                                                                                                                        | G21  | IO     | 9       | J22  | IO      | 9       | M1   | IO       | 1       |

| H2         IO         1         K3         ILVDS7         2         M4         VCCB         2           H3         IO         1         K4         VCC         1         M5         IO         3           H4         IO         1         K5         IO         1         M6         IO         3           H5         VCC         1         K6         VCC         1         M7         IO         3           H6         IO         1         K7         IO         1         M8         IO         3           H7         IO         1         K8         IO         1         M8         IO         3           H8         VCC         1         K9         IO         1         M10         IO         3           H9         VCC         12         K10         TCK         1         M11         IO         4           H10         IO         12         K11         IO         12         M12         IO/D14         7           H11         IO         12         K12         IO         10         M13         IO         7           H12         IO                                                                                                                                             | G22  | IO     | 9       | K1   | IO      | 1       | M2   | OLVDS7   | 2       |

| H3         IO         1         K4         VCC         1         M5         IO         3           H4         IO         1         K5         IO         1         M6         IO         3           H5         VCC         1         K6         VCC         1         M7         IO         3           H6         IO         1         K7         IO         1         M8         IO         3           H7         IO         1         K8         IO         1         M8         IO         3           H8         VCC         1         K9         IO         1         M9         IO         3           H9         VCC         12         K10         TCK         1         M11         IO         4           H10         IO         12         K11         IO         12         M12         IO/D14         7           H11         IO         12         K12         IO         10         M13         IO         7           H11         IO         12         K13         RESETN         10         M14         IO/D12         9           H13         IO <th>H1</th> <th>IO/A4</th> <th>1</th> <th>K2</th> <th>ILVDS8</th> <th>2</th> <th>M3</th> <th>OLVDS8</th> <th>2</th>                   | H1   | IO/A4  | 1       | K2   | ILVDS8  | 2       | M3   | OLVDS8   | 2       |

| H4         IO         1         K5         IO         1         M6         IO         3           H5         VCC         1         K6         VCC         1         M7         IO         3           H6         IO         1         K7         IO         1         M8         IO         3           H7         IO         1         K8         IO         1         M9         IO         3           H8         VCC         1         K9         IO         1         M9         IO         3           H9         VCC         12         K10         TCK         1         M11         IO         4           H10         IO         12         K11         IO         12         M12         IO/D14         7           H11         IO         12         K12         IO         10         M13         IO         7           H11         IO         12         K13         RESETN         10         M14         IO/D12         9           H13         IO         10         K15         IO         9         M16         IO/D13         7           H14 <td< th=""><th>H2</th><th>IO</th><th>1</th><th>K3</th><th>ILVDS7</th><th>2</th><th>M4</th><th>VCCB</th><th>2</th></td<>                   | H2   | IO     | 1       | K3   | ILVDS7  | 2       | M4   | VCCB     | 2       |

| H5         VCC         1         K6         VCC         1         M7         IO         3           H6         IO         1         K7         IO         1         M8         IO         3           H7         IO         1         K8         IO         1         M9         IO         3           H8         VCC         1         K9         IO         1         M10         IO         3           H9         VCC         12         K10         TCK         1         M11         IO         4           H10         IO         12         K11         IO         12         M12         IO/D14         7           H11         IO         12         K12         IO         10         M13         IO         7           H11         IO         12         K13         RESETN         10         M14         IO/D12         9           H13         IO         10         K14         IO         9         M15         VCCB         8           H14         VCC         10         K16         VCC         9         M17         IO         7           H16                                                                                                                                      | H3   | IO     | 1       | K4   | VCC     | 1       | M5   | IO       | 3       |

| H6         IO         1         K7         IO         1         M8         IO         3           H7         IO         1         K8         IO         1         M9         IO         3           H8         VCC         1         K9         IO         1         M10         IO         3           H9         VCC         12         K10         TCK         1         M11         IO         4           H10         IO         12         K10         TCK         1         M12         IO/D14         7           H11         IO         12         K11         IO         12         M12         IO/D14         7           H11         IO         12         K13         RESETN         10         M14         IO/D12         9           H13         IO         10         K14         IO         9         M15         VCCB         8           H14         VCC         10         K16         VCC         9         M17         IO         7           H15         VCC         10         K16         VCC         9         M17         IO         7           H16 <th>H4</th> <th>IO</th> <th>1</th> <th>K5</th> <th>IO</th> <th>1</th> <th>M6</th> <th>IO</th> <th>3</th>                     | H4   | IO     | 1       | K5   | IO      | 1       | M6   | IO       | 3       |

| H7         IO         1         K8         IO         1         M9         IO         3           H8         VCC         1         K9         IO         1         M10         IO         3           H9         VCC         12         K10         TCK         1         M11         IO         4           H10         IO         12         K10         TCK         1         M11         IO         4           H10         IO         12         K11         IO         12         M12         IO/D14         7           H11         IO         12         K12         IO         10         M13         IO         7           H12         IO         12         K13         RESETN         10         M14         IO/D12         9           H13         IO         10         K14         IO         9         M15         VCCB         8           H14         VCC         10         K16         VCC         9         M17         IO         7           H15         VCC         10         K16         VCC         9         M17         IO         7           H16 <th>H5</th> <th>VCC</th> <th>1</th> <th>K6</th> <th>VCC</th> <th>1</th> <th>M7</th> <th>IO</th> <th>3</th>                  | H5   | VCC    | 1       | K6   | VCC     | 1       | M7   | IO       | 3       |

| H8         VCC         1         K9         IO         1         M10         IO         3           H9         VCC         12         K10         TCK         1         M11         IO         4           H10         IO         12         K11         IO         12         M12         IO/D14         7           H11         IO         12         K11         IO         12         M12         IO/D14         7           H11         IO         12         K12         IO         10         M13         IO         7           H12         IO         12         K13         RESETN         10         M14         IO/D12         9           H13         IO         10         K14         IO         9         M15         VCCB         8           H14         VCC         10         K15         IO         9         M16         IO/D13         7           H15         VCC         10         K16         VCC         9         M17         IO         7           H16         VCC         9         K17         IO         9         M18         REFSouth         8                                                                                                                          | H6   | IO     | 1       | K7   | IO      | 1       | M8   | IO       | 3       |

| H9         VCC         12         K10         TCK         1         M11         IO         4           H10         IO         12         K11         IO         12         M12         IO/D14         7           H11         IO         12         K12         IO         10         M13         IO         7           H11         IO         12         K12         IO         10         M13         IO         7           H12         IO         12         K13         RESETN         10         M14         IO/D12         9           H13         IO         10         K14         IO         9         M15         VCCB         8           H14         VCC         10         K15         IO         9         M16         IO/D13         7           H15         VCC         10         K16         VCC         9         M17         IO         7           H16         VCC         9         K17         IO         9         M18         REFSouth         8           H17         IO         9         K18         VCC         9         M19         VCC         7                                                                                                                           | H7   | IO     | 1       | K8   | IO      | 1       | M9   | IO       | 3       |

| H10         IO         12         K11         IO         12         M12         IO/D14         7           H11         IO         12         K12         IO         10         M13         IO         7           H12         IO         12         K13         RESETN         10         M14         IO/D12         9           H13         IO         10         K14         IO         9         M15         VCCB         8           H14         VCC         10         K15         IO         9         M16         IO/D13         7           H14         VCC         10         K16         VCC         9         M17         IO         7           H14         VCC         10         K16         VCC         9         M16         IO/D13         7           H15         VCC         10         K16         VCC         9         M17         IO         7           H16         VCC         9         K17         IO         9         M18         REFSouth         8           H17         IO         9         K18         VCC         9         M19         VCC         7      <                                                                                                              | H8   | VCC    | 1       | K9   | IO      | 1       | M10  | IO       | 3       |

| H11         IO         12         K12         IO         10         M13         IO         7           H12         IO         12         K13         RESETN         10         M14         IO/D12         9           H13         IO         10         K14         IO         9         M15         VCCB         8           H14         VCC         10         K15         IO         9         M16         IO/D13         7           H14         VCC         10         K16         VCC         9         M17         IO         7           H15         VCC         10         K16         VCC         9         M17         IO         7           H16         VCC         9         K17         IO         9         M18         REFSouth         8           H17         IO         9         K18         VCC         9         M19         VCC         7           H18         IO         9         K19         IO         9         M20         ILVDS3N         8           H19         IO         9         K20         OLVDS3N         8         M22         IO         7                                                                                                                        | H9   | VCC    | 12      | K10  | ТСК     | 1       | M11  | IO       | 4       |

| H12         IO         12         K13         RESETN         10         M14         IO/D12         9           H13         IO         10         K14         IO         9         M15         VCCB         8           H14         VCC         10         K15         IO         9         M16         IO/D12         9           H14         VCC         10         K15         IO         9         M16         IO/D13         7           H15         VCC         10         K16         VCC         9         M17         IO         7           H16         VCC         9         K17         IO         9         M18         REFSouth         8           H17         IO         9         K18         VCC         9         M19         VCC         7           H18         IO         9         K19         IO         9         M20         ILVDS3N         8           H19         IO         9         K20         OLVDS4N         8         M21         ILVDS4N         8           H20         IO         9         K22         IO         9         N1         IO         3 <th>H10</th> <th>IO</th> <th>12</th> <th>K11</th> <th>IO</th> <th>12</th> <th>M12</th> <th>IO/D14</th> <th>7</th> | H10  | IO     | 12      | K11  | IO      | 12      | M12  | IO/D14   | 7       |

| H13         IO         10         K14         IO         9         M15         VCCB         8           H14         VCC         10         K15         IO         9         M16         IO/D13         7           H15         VCC         10         K16         VCC         9         M17         IO         7           H16         VCC         9         K17         IO         9         M18         REFSouth         8           H17         IO         9         K18         VCC         9         M19         VCC         7           H18         IO         9         K19         IO         9         M20         ILVDS3N         8           H19         IO         9         K20         OLVDS4N         8         M21         ILVDS4N         8           H20         IO         9         K21         OLVDS3N         8         M22         IO         7           H21         IO         9         K22         IO         9         N1         IO         3                                                                                                                                                                                                                                   | H11  | IO     | 12      | K12  | IO      | 10      | M13  | IO       | 7       |

| H14         VCC         10         K15         IO         9         M16         IO/D13         7           H15         VCC         10         K16         VCC         9         M17         IO         7           H16         VCC         9         K17         IO         9         M18         REFSouth         8           H17         IO         9         K18         VCC         9         M19         VCC         7           H18         IO         9         K18         VCC         9         M19         VCC         7           H18         IO         9         K18         VCC         9         M19         VCC         7           H18         IO         9         K19         IO         9         M20         ILVDS3N         8           H19         IO         9         K20         OLVDS4N         8         M21         ILVDS4N         8           H20         IO         9         K22         IO         9         N1         IO         3                                                                                                                                                                                                                                       | H12  | IO     | 12      | K13  | RESETN  | 10      | M14  | IO/D12   | 9       |

| H15         VCC         10         K16         VCC         9         M17         IO         7           H16         VCC         9         K17         IO         9         M18         REFSouth         8           H17         IO         9         K18         VCC         9         M19         VCC         7           H18         IO         9         K18         VCC         9         M19         VCC         7           H18         IO         9         K19         IO         9         M20         ILVDS3N         8           H19         IO         9         K20         OLVDS4N         8         M21         ILVDS4N         8           H20         IO         9         K21         OLVDS3N         8         M22         IO         7           H21         IO         9         K22         IO         9         N1         IO         3                                                                                                                                                                                                                                                                                                                                               | H13  | IO     | 10      | K14  | IO      | 9       | M15  | VCCB     | 8       |

| H16         VCC         9         K17         IO         9         M18         REFSouth         8           H17         IO         9         K18         VCC         9         M19         VCC         7           H18         IO         9         K19         IO         9         M20         ILVDS3N         8           H19         IO         9         K20         OLVDS4N         8         M21         ILVDS4N         8           H20         IO         9         K21         OLVDS3N         8         M22         IO         7           H21         IO         9         K22         IO         9         N1         IO         3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | H14  | VCC    | 10      | K15  | IO      | 9       | M16  | IO/D13   | 7       |

| H17         IO         9         K18         VCC         9         M19         VCC         7           H18         IO         9         K19         IO         9         M20         ILVDS3N         8           H19         IO         9         K20         OLVDS4N         8         M21         ILVDS4N         8           H20         IO         9         K21         OLVDS3N         8         M22         IO         7           H21         IO         9         K22         IO         9         N1         IO         3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | H15  | VCC    | 10      | K16  | VCC     | 9       | M17  | IO       | 7       |

| H18         IO         9         K19         IO         9         M20         ILVDS3N         8           H19         IO         9         K20         OLVDS4N         8         M21         ILVDS4N         8           H20         IO         9         K21         OLVDS3N         8         M22         IO         7           H21         IO         9         K22         IO         9         N1         IO         3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | H16  | VCC    | 9       | K17  | IO      | 9       | M18  | REFSouth | 8       |

| H19         IO         9         K20         OLVDS4N         8         M21         ILVDS4N         8           H20         IO         9         K21         OLVDS3N         8         M22         IO         7           H21         IO         9         K22         IO         9         N1         IO         3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | H17  | IO     | 9       | K18  | VCC     | 9       | M19  | VCC      | 7       |

| H20         IO         9         K21         OLVDS3N         8         M22         IO         7           H21         IO         9         K22         IO         9         N1         IO         3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | H18  | IO     | 9       | K19  | IO      | 9       | M20  | ILVDS3N  | 8       |

| H21         IO         9         K22         IO         9         N1         IO         3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | H19  | IO     | 9       | K20  | OLVDS4N | 8       | M21  | ILVDS4N  | 8       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | H20  | IO     | 9       | K21  | OLVDS3N | 8       | M22  | IO       | 7       |

| H22 IO 9 L1 IO/A7 1 N2 OLVDS7N 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | H21  | IO     | 9       | K22  | IO      | 9       | N1   | IO       | 3       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | H22  | IO     | 9       | L1   | IO/A7   | 1       | N2   | OLVDS7N  | 2       |

| LEAD | Signal | Cluster | LEAD | Signal   | Cluster | LEAD | Signal  | Cluster |

|------|--------|---------|------|----------|---------|------|---------|---------|

| J1   | IO     | 1       | L2   | ILVDS8N  | 2       | N3   | OLVDS8N | 2       |

| J2   | IO     | 1       | L3   | ILVDS7N  | 2       | N4   | IO      | 3       |

| J3   | IO     | 1       | L4   | VCC      | 1       | N5   | IO/A9   | 3       |

| J4   | IO/A5  | 1       | L5   | REFNorth | 2       | N6   | IO      | 3       |

| J5   | Ю      | 1       | L6   | IO       | 1       | N7   | VCC     | 3       |

| J6   | VCC    | 1       | L7   | IO       | 1       | N8   | IO/A12  | 3       |

| J7   | IO     | 1       | L8   | IO/A8    | 3       | N9   | IO      | 3       |

Cluster

4

4

6

6

6

6

6

6

7

7

7

7

7

3

3

3

3

4

4

4

4

4

4

5

6

6

6

6

6

6

7

7

7

7

7

7

3

3

Signal

VCC

10

IO

Ю

10

10

IO/GCK2

IO

10

Ю

10

IO/D15

VCC

IO

IO

IO

10

10

Ю

IO/A19

VCC

VCC

IO

REFWest

IO

10

VCC

IO

IO/A22

VCC

Ю

IO

Ю

IO

VCC

VSS

VCC

IO

LEAD

U10

U11

U12

U13

U14

U15

U16

U17

U18

U19

U20

U21

U22

V1

V2

V3

V4

V5

V6

٧7

V8

٧9

V10

V11

V12

V13

V14

V15

V16

V17

V18

V19

V20

V21

V22

W1

W2

W3

Cluster

4

5

6

6

6

7

7

7

7

7

7

7

7

3

3

3

3

3

3

3

4

4

4

4

6

6

6

6

6

7

7

7

7

7

7

3

3

3

| U1 | IO  |  |

|----|-----|--|

| U2 | IO  |  |

| U3 | VCC |  |

|    |     |  |

Table 2-3. ATF280E MCGA472 pin assignment

Signal

IO

VCCB

VCC

Ю

VCC

VCC

IO

IO

VCC

IO

10

10

IO

IO/A11

10

IO

10

10

TDO

IO/A14

IO

Ю

IO

IO/A20

Ю

VCC

IO

VCC

IO

M2

**IO/INIT**

IO

Ю

VCC

10

LEAD

**R10**

**R11**

R12

**R13**

**R14**

R15

**R16**

**R17**

**R18**

R19

**R20**

R21

**R22**

**T1**

T2

ΤЗ

Τ4

T5

Т6

**T**7

Т8

Т9

T10

T11

T12

T13

T14

T15

T16

T17

T18

T19

T20

T21

T22

7750A-AERO-07/07

LEAD

N10

N11

N12

N13

N14

N15

N16

N17

N18

N19

N20

N21

N22

**P1**

**P2**

**P3**

**P4**

**P5**

**P6**

**P7**

**P8**

**P**9

P10

P11

P12

P13

P14

P15

P16

P17

P18

P19

P20

P21

P22

**R1**

**R2**

R3

Signal

TMS

10

IO

M1

10

10

Ю

VCC

IO

VCC

ILVDS3

ILVDS4

Ю

VCC

10

Ю

VCC

VCC

Ю

IO/A13

VCC

IO/GCK1/A16

10

10

Ю

10

IO/GCK3

VCC

IO

VCC

Ю

IO

Ю

IO

IO

IO

Ю

10

Cluster

4

4

6

7

7

7

7

7

7

7

8

8

7

3

3

3

3

3

3

3

3

4

4

6

6

6

7

7

7

7

7

7

7

7

7

3

3

| LEAD | Signal | Cluster | LEAD | Signal      | Cluster | LEAD | Signal | Cluster |

|------|--------|---------|------|-------------|---------|------|--------|---------|

| R4   | IO     | 3       | U4   | TDI         | 3       | W4   | VCC    | 3       |

| R5   | IO/A10 | 3       | U5   | VCC         | 3       | W5   | IO     | 4       |

| R6   | IO     | 3       | U6   | IO/GCK8/A15 | 3       | W6   | IO     | 4       |

| R7   | VCC    | 3       | U7   | TRST        | 4       | W7   | IO     | 4       |

| R8   | VCC    | 4       | U8   | IO          | 4       | W8   | IO     | 4       |

| R9   | VCC    | 4       | U9   | VCC         | 4       | W9   | IO     | 4       |

Table 2-4.

ATF280E MCGA472 pin assignment

| LEAD | Signal  | Cluster | LEAD | Signal  | Cluster |

|------|---------|---------|------|---------|---------|

| W10  | IO      | 4       | AA4  | IO/A17  | 4       |

| W11  | VCC     | 4       | AA5  | IO      | 4       |

| W12  | IO      | 6       | AA6  | IO/A18  | 4       |

| W13  | IO      | 6       | AA7  | VCC     | 4       |

| W14  | VCC     | 6       | AA8  | IO      | 4       |

| W15  | IO      | 6       | AA9  | IO      | 4       |

| W16  | IO      | 6       | AA10 | ILVDS2  | 5       |

| W17  | MO      | 6       | AA11 | ILVDS2N | 5       |

| W18  | IO      | 6       | AA12 | OLVDS1  | 5       |

| W19  | VCC     | 6       | AA13 | OLVDS1N | 5       |

| W20  | IO      | 7       | AA14 | IO      | 6       |

| W21  | IO/LDC  | 7       | AA15 | IO      | 6       |

| W22  | VSS     | 7       | AA16 | IO      | 6       |

| Y1   | VDD     | 7       | AA17 | IO/A23  | 6       |

| Y2   | VDD     | 7       | AA18 | IO      | 6       |

| Y3   | VSS     | 9       | AA19 | VCC     | 6       |

| Y4   | IO      | 4       | AA20 | VDD     | 10      |

| Y5   | IO      | 4       | AA21 | VSS     | 10      |

| Y6   | IO      | 4       | AB3  | VDD     | 12      |

| ¥7   | IO      | 4       | AB4  | VSS     | 12      |

| Y8   | IO      | 4       | AB5  | VCC     | 4       |

| Y9   | IO      | 4       | AB6  | VCC     | 4       |

| Y10  | ILVDS1  | 5       | AB7  | IO      | 4       |

| Y11  | ILVDS1N | 5       | AB8  | IO/FCK1 | 4       |

| Y12  | OLVDS2  | 5       | AB9  | IO      | 4       |

| Y13  | OLVDS2N | 5       | AB10 | IO      | 4       |

| Y14  | IO      | 6       | AB11 | IO      | 4       |

| Y15  | IO      | 6       | AB12 | IO/A21  | 6       |

| Y16  | IO      | 6       | AB13 | IO      | 6       |

| Y17  | VCC     | 6       | AB14 | IO      | 6       |

| Y18  | IO      | 6       | AB15 | IO      | 6       |

| Y19  | IO/OTSN | 6       | AB16 | IO/FCK2 | 6       |

| Y20  | VSS     | 9       | AB17 | IO      | 6       |

| Y21  | VDD     | 7       | AB18 | IO      | 6       |

| Y22  | VDD     | 9       | AB19 | VSS     | 12      |

| AA2  | VSS     | 10      | AB20 | VDD     | 12      |

| AA3  | VDD     | 9       |      |         | İ.      |

## 3. Pin Description

## Clock

GCK1:GCK8 - Global Clock (Input)

FCK1:FCK4 - Fast Clock (Input)

I/O

### I/Oy\_x - Programmable I/O (Input/Output)

The programmable I/Os are dedicated to user's application. Each programmable I/O can independently be configured as input, output or bidirectional I/O. Each I/O is part of an I/O cluster.

This leads to the following naming:  $I/Oy_x$  where 'y' is the cluster number (1 < y < 8) and 'x' is the I/O number in the cluster.

### **OLVDSx - LVDS Driver (Output)**

OLVDSx where 'x' is the LVDS channel number (1 < x < 8).

### **OLVDSxN - Complimentary LVDS Driver (Output)**

OLVDSxN where 'x' is the LVDS channel number (1 < x < 8).

### ILVDSx - LVDS Receiver (Input)

ILVDSx where 'x' is the LVDS channel number (1 < x < 8).

### ILVDSxN - Complimentary LVDS Receiver(Input)

ILVDSxN where 'x' is the LVDS channel number (1 < x < 8).

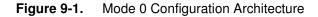

### **FPGA** Configuration

## M0, M1, M2 (Input)

The mode pins are dedicated TTL threshold inputs that determine the configuration mode to be used. Table 1 lists the states for each configuration mode. The mode pins should not be changed during power-on-reset, manual reset, or configuration download. The user may change the mode pins during configuration idle. These pins have no pull-up resistors to VCC, so they need to be driven by the user or tied off.

### CCLK (Input/Output)

CCLK is the configuration clock pin. It is an input or output depending on the mode of operation. During power-on-reset or manual reset, it is a tri-stated output. During configuration download and in Mode 0, it is an output with a typical frequency of 1 MHz. During configuration download and in all other modes, it is a Schmitt trigger input with approximately 1V of hysteresis for noise immunity. It is an input during configuration idle, but is ignored. It is pulled to VCC with a nominal 50K internal resistor.

### RESETn - Reset (Input)

RESETn is the FPGA configuration manual reset pin. It is available during all configuration states. It initiates a configuration clear cycle and, if operating in Mode 0, an auto configuration. It is a dedicated Schmitt trigger input with approximately 1V of hysteresis for noise immunity. It is pulled to VCC with a nominal 50K internal resistor.

### **INIT - (Input/Output)**

INIT is a multi-function pin. During power-on-reset and manual reset, the pin functions as an open drain bi-directional I/O which releases High when the configuration clear cycle is complete, but can be held Low to hold the configuration in a reset state. Once released, the FPGA will proceed to either configuration download or idle, as appropriate. During configuration download, the INIT pin is again an open drain bi-directional pin which signals if an error is encountered during the download of a configuration bitstream. In addition, during the Check Function, the INIT pin drives Low for any configuration SRAM mismatch (see the description of the Check Function on page 16 for more details). While in open drain mode, the pin is pulled to VDD with a nominal 20K internal resistor. When not configuring, the INIT pin becomes a fully functional user I/O.

## CON - Configuration Status (Input/Output)

CON is the FPGA configuration start and status pin. It is a dedicated open drain bi-directional pin. During power-on-reset or manual reset, CON is driven Low by the FPGA. In Modes 2, 6, or 7, when the FPGA has finished the configuration clear cycle, CON is released to indicate the device is ready for the user to initiate configuration download. The user may then drive CON Low to initiate a configuration download. After three clock cycles, CON is then driven Low by the FPGA until it finishes the download, and it is then released. In Mode 0, CON is not released by the FPGA at the end of power-on-reset or manual reset. Instead, CON is controlled by the FPGA until the end of the auto-configuration process. CON is released at the end of configuration download in Mode 0, and the user may then initiate a manual configuration download by driving CON Low. While in open drain mode, the pin is pulled to VDD with a nominal 10K internal resistor.

## HDC - High During Configuration (output)

HDC(1) is driven High by the FPGA during power-on-reset, manual reset, and configuration download. During normal operation, the pin is a fully functional user I/O.

Note: 1. All user I/O default to inputs with pull-ups "on". The HDC pin transitions from driving a strong "1" to a pull-up "1" after reset. The HDC pin will transition from driving a strong "1" to the user programmed state at the end of configuration download. If not programmed, the default state is input with pull-up.

## LDC - Low During Configuration (output)

HDC(1) is driven Low by the FPGA during power-on-reset, manual reset, and configuration download. During normal operation, the pin is a fully functional user I/O.

Note: 1. All user I/O default to inputs with pull-ups "on". The HDC pin transitions from driving a strong "1" to a pull-up "1" after reset. The HDC pin will transition from driving a strong "1" to the user programmed state at the end of configuration download. If not programmed, the default state is input with pull-up.

## D0 - Configuration Data Bus - LSB (Input/Output)

D0 is the lsb of the FPGA configuration data bus used to download configuration data to the device. During power-on-reset or manual reset, D0 is controlled by the configuration SRAM. The D0 pin will transition from the user programmed state to a CMOS input with a nominal 20K internal pull-up resistor as the SRAM at that location is cleared by the configuration clear cycle. D0 becomes an input during configuration download.

## D1:D15 - Configuration Data Bus - Upper bits (Input/Output)

D1:D15 are the upper bits of the 8/16-bit parallel data bus used to download configuration data to the device. During power-on-reset or manual reset, D1:D15 are controlled by the configura-

tion SRAM. The D1:D15 pins will transition from the user programmed state to CMOS inputs with nominal 20K internal pull-up resistors as the SRAM at those locations is cleared by the configuration clear cycle.

When in Modes 2 or 6, D1:D7 become inputs during configuration download. D1:D7 are not used in the serial Modes 0, 1 and 7.

When in Modes 2 or 6, D8:D15 become optional inputs during configuration download. They become available as soon as the appropriate bit in the configuration control register is set. D8:D15 are not used in the serial Modes 0, 1 and 7.

### A0:A19 - Configuration Address Bus (Input/Output)

A0:A19(1) are used to control external addressing of memories during downloads. During power-on-reset or manual reset, A0:A19 are controlled by the configuration SRAM. The A0:A19 pins will transition from the user programmed state to CMOS inputs with nominal 20K internal pull-up resistors as the SRAM at those locations is cleared by the configuration clear cycle. When in Mode 6, A0:A19 become outputs during configuration download. A0:A19 are used only in Mode 6.

Note: 1. Pin A2 is also pin CS1, which is available only for Mode 2. See the description for CS1 on page 5 for more details.

### CS0/CS1 - Configuration Chip Select (Input/Output)

CS0 is an FPGA configuration chip select. It is active Low. During power-on-reset or manual reset, CS0 is controlled by the configuration SRAM. The CS0 pin will transition from the user programmed state to a CMOS input with a nominal 20K internal pull-up resistor as the SRAM at that location is cleared by the configuration clear cycle. In Mode 1, it is used as a chip select to enable configuration to begin. It is most often used as the chip select of the downstream device in a cascade chain, and is usually driven by CSOUT of the upstream device. Releasing CS0 during configuration causes the Mode 1 FPGA to abort the download and release CON.

CS0 is used only in Mode 1. CS1 is used only in Mode 2

Note: 1. Pin CS1 is also pin A2, which is active only for Mode 6. See the description for A0:A19, on page 5 for more details.

### CSOUT - Configuration Cascade Output (Output)

CSOUT is the configuration pin used to enable the downstream device in a cascade chain. During power-on-reset or manual reset, CSOUT is controlled by the configuration SRAM. The CSOUT pin will transition from the user programmed state to a CMOS input with a nominal 20K internal pull-up resistor as the SRAM at that location is cleared by the configuration clear cycle. During configuration download, CSOUT becomes an optional output. It is enabled by default after reset, and may be enabled or disabled via the configuration control register. If the user has disabled the cascade function, the pin remains a user I/O. If the cascade function is enabled, the CSOUT pin is driven High at the start of configuration download. At the end of the device's portion of the cascade bitstream, the CSOUT pin is driven Low (and into the CS0 or CS1 of the downstream device) to enable the downstream device. CSOUT is released by the device at the end of the cascade bitstream and becomes a fully functional user I/O.

### CHECK - Configuration Check (Input/Output)

CHECK is a configuration control pin used to control the Check Function. The Check Function takes a bitstream and compares it to the contents of a previously loaded bitstream and notifies the user of any differences. Any differences causes the INIT pin to go Low. During power-on-

reset or manual reset, CHECK is controlled by the configuration SRAM. The CHECK pin will transition from the user programmed state to a CMOS input with a nominal 20K internal pull-up resistor as the SRAM at that location is cleared by the configuration clear cycle. During configuration download, CHECK becomes an optional input. It is enabled by default after reset, and may be enabled or disabled via the configuration control register. If the user has disabled the Check Function, the pin remains a user I/O.

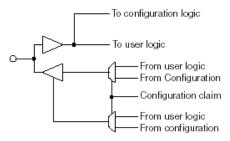

### OTS - Dual Use Tri State (Input)

OTS is an input pin used to immediately tri-state all user I/O. It is enabled by a bit in the configuration control register. Once activated, it is always an input. The OTS tri-state control of Dual-use pins is superseded by the configuration logic's claim on those pins. If the user has disabled the OTS function, the pin remains as User I/O.

### JTAG

### TCK - Test Clock (input)

Used to clock serial data into boundary scan latches and control sequence of the test

state machine. TCK can be asynchronous with CLK.

### TMS - Test Mode select (input)

Primary control signal for the state machine. Synchronous with TCK. A sequence of values on TMS adjusts the current state of the TAP.

### **TDI - Test data input (input)**

Serial input data to the boundary scan latches. Synchronous with TCK

### TDO - Test data output (output)

Serial output data from the boundary scan latches. Synchronous with TCK

### **TRST - Test Reset (input)**

Resets the test state machine. Can be asynchronous with TCK. Shall be grounded for end application.

### **Power Supply**

### **VDD - Core Power Supply**

VDD is the power supply input for the ATF280E core.  $VDD = 1.8V \pm 0.2V$

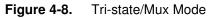

### VCCy - I/O Power Supply