### Features

- Supply Voltage up to 40V

- Operating Voltage V<sub>S</sub> = 5V to 27V

- Typically 10 µA Supply Current During Sleep Mode

- Typically 57 µA Supply Current in Silent Mode

- Linear Low-drop Voltage Regulator:

- Normal, Fail-safe, and Silent Mode

- ATA6623: V<sub>CC</sub> = 3.3V ±2%

- ATA6625:  $V_{CC} = 5.0V \pm 2\%$

- Sleep Mode:  $\mathbf{V}_{\mathbf{CC}}$  is Switched Off

- V<sub>cc</sub> Undervoltage Detection with Reset Open Drain Output NRES (4 ms Reset Time)

- Voltage Regulator is Short-circuit and Over-temperature Protected

- LIN Physical Layer According to LIN Specification Revision 2.0 and SAEJ2602-2

- Wake-up Capability via LIN Bus (90 µs Dominant)

- TXD Time-out Timer

- Bus Pin is Overtemperature and Short-circuit Protected versus GND and Battery

- Advanced EMC and ESD Performance

- ESD HBM 8 kV at Pins LIN and VS Following STM5.1

- Interference and Damage Protection According to ISO/CD7637

- Package: SO8

# 1. Description

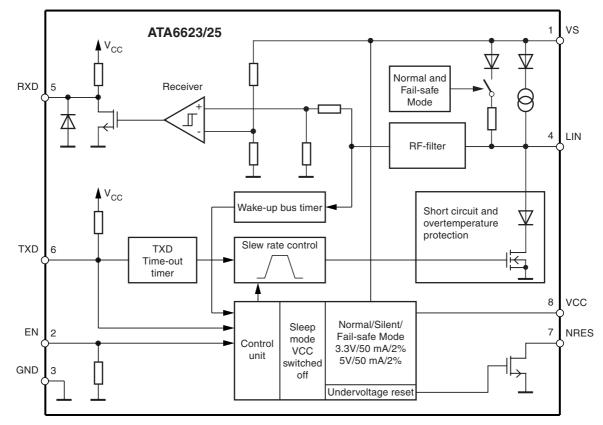

ATA6623/ATA6625 is a fully integrated LIN transceiver, designed according to the LIN specification 2.0, with a low-drop voltage regulator (3.3V/5V/50 mA). The combination of voltage regulator and bus transceiver makes it possible to develop simple, but powerful, slave nodes in LIN Bus systems. ATA6623/ATA6625 is designed to handle the low-speed data communication in vehicles (for example, in convenience electronics). Improved slope control at the LIN driver ensures secure data communication up to 20 kBaud with an RC oscillator for the protocol handling. The bus output is designed to withstand high voltage. Sleep Mode (voltage regulator switched off) and Silent Mode (communication off; V<sub>CC</sub> voltage on) guarantee minimized current consumption.

LIN Bus Transceiver with Integrated Voltage Regulator

ATA6623 ATA6625

Figure 1-1. Block Diagram

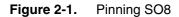

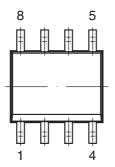

### 2. Pin Configuration

#### Table 2-1. Pin Description

| Pin | Symbol | Function                                 |

|-----|--------|------------------------------------------|

| 1   | VS     | Battery supply                           |

| 2   | EN     | Enables Normal Mode if the input is high |

| 3   | GND    | Ground, heat sink                        |

| 4   | LIN    | LIN bus line input/output                |

| 5   | RXD    | Receive data output                      |

| 6   | TXD    | Transmit data input                      |

| 7   | NRES   | Output undervoltage reset, low at reset  |

| 8   | VCC    | Output voltage regulator 3.3V/5V/50 mA   |

# <sup>2</sup> ATA6623/ATA6625

## 3. Functional Description

### 3.1 Physical Layer Compatibility

Since the LIN physical layer is independent from higher LIN layers (e.g., LIN protocol layer), all nodes with a LIN physical layer according to revision 2.0 can be mixed with LIN physical layer nodes, which are according to older versions (i.e., LIN 1.0, LIN 1.1, LIN 1.2, LIN 1.3) without any restrictions.

#### 3.2 Supply Pin (VS)

LIN operating voltage is  $V_S = 5V$  to 27V. An undervoltage detection is implemented to disable transmission if  $V_S$  falls below 5V, in order to avoid false bus messages. After switching on  $V_S$ , the IC starts with the Fail-safe Mode and the voltage regulator is switched on (i.e., 3.3V/5V/50 mA).

The supply current in Sleep Mode is typically 10  $\mu A$  and 57  $\mu A$  in Silent Mode.

#### 3.3 Ground Pin (GND)

The IC is neutral on the LIN pin in the event of GND disconnection. It is able to handle a ground shift up to 11.5% of  $V_S$ .

#### 3.4 Voltage Regulator Output Pin (VCC)

The internal 3.3V/5V voltage regulator is capable of driving loads with up to 50 mA, supplying the microcontroller and other ICs on the PCB and is protected against overload by means of current limitation and overtemperature shut-down. Furthermore, the output voltage is monitored and will cause a reset signal at the NRES output pin if it drops below a defined threshold  $V_{thun}$ .

#### 3.5 Undervoltage Reset Output (NRES)

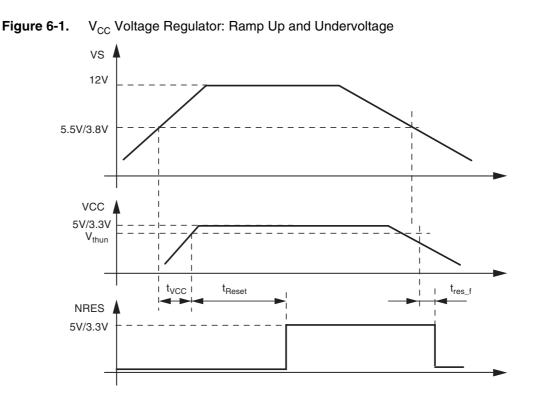

If the V<sub>CC</sub> voltage falls below the undervoltage detection threshold of V<sub>thun</sub>, NRES switches to low after tres\_f (Figure 6-1 on page 11). Even if V<sub>CC</sub> = 0V the NRES stays low, because it is internally driven from the V<sub>S</sub> voltage. If V<sub>S</sub> voltage ramps down, NRES stays low until V<sub>S</sub> < 1.5V and then becomes highly resistant.

The implemented undervoltage delay keeps NRES low for  $t_{Reset} = 4$  ms after  $V_{CC}$  reaches its nominal value.

#### 3.6 Bus Pin (LIN)

A low-side driver with internal current limitation and thermal shutdown as well as an internal pull-up resistor according to LIN specification 2.0 is implemented. The voltage range is from –27V to +40V. This pin exhibits no reverse current from the LIN bus to V<sub>S</sub>, even in the event of a GND shift or V<sub>Batt</sub> disconnection. The LIN receiver thresholds are compatible with the LIN protocol specification.

The fall time (from recessive to dominant) and the rise time (from dominant to recessive) are slope controlled.

#### 3.7 Input Pin (TXD)

In Normal Mode the TXD pin is the microcontroller interface to control the state of the LIN output. TXD must be pulled to ground in order to drive the LIN bus low. If TXD is high or unconnected (internal pull-up resistor), the LIN output transistor is turned off and the bus is in the recessive state.

#### 3.8 Dominant Time-out Function (TXD)

The TXD input has an internal pull-up resistor. An internal timer prevents the bus line from being driven permanently in the dominant state. If TXD is forced to low longer than  $t_{DOM} > 6$  ms, the LIN bus driver is switched to the recessive state. Nevertheless, when switching to Sleep Mode, the actual level at the TXD pin is relevant.

To reactivate the LIN bus driver, switch TXD to high (> 10  $\mu$ s).

#### 3.9 Output Pin (RXD)

The pin reports the state of the LIN-bus to the microcontroller. LIN high (recessive state) is reported by a high level at RXD; LIN low (dominant state) is reported by a low level at RXD. The output has an internal pull-up structure with typically 5 k $\Omega$  to V<sub>CC</sub>. The AC characteristics are measured with an external load capacitor of 20 pF.

The output is short-circuit protected. In Unpowered Mode (that is,  $V_s = 0V$ ), RXD is switched off.

#### 3.10 Enable Input Pin (EN)

This pin controls the Operation Mode of the interface. After power up of  $V_S$  (battery), the IC switches to Fail-safe Mode, even if EN is low or unconnected (internal pull-down resistor). If EN is high, the interface is in Normal Mode.

A falling edge at EN while TXD is still high forces the device to Silent Mode. A falling edge at EN while TXD is low forces the device to Sleep Mode.

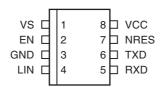

### 4. Mode of Operation

#### Table 4-1.Mode of Operation

| Mode of<br>Operation | Transceiver | V <sub>cc</sub> | RXD  | LIN           |

|----------------------|-------------|-----------------|------|---------------|

| Fail safe            | OFF         | 3.3V/5V         | High | Recessive     |

| Normal               | ON          | 3.3V/5V         | High | TXD depending |

| Silent               | OFF         | 3.3V/5V         | High | Recessive     |

| Sleep                | OFF         | 0V              | 0V   | Recessive     |

#### 4.1 Normal Mode

This is the normal transmitting and Receiving Mode of the LIN Interface, in accordance with LIN specification 2.0. The V<sub>CC</sub> voltage regulator operates with a 3.3V/5V output voltage, with a low tolerance of  $\pm 2\%$  and a maximum output current of 50 mA.

If an undervoltage condition occurs, NRES is switched to low and the IC changes its state to Fail-safe Mode. All features are available.

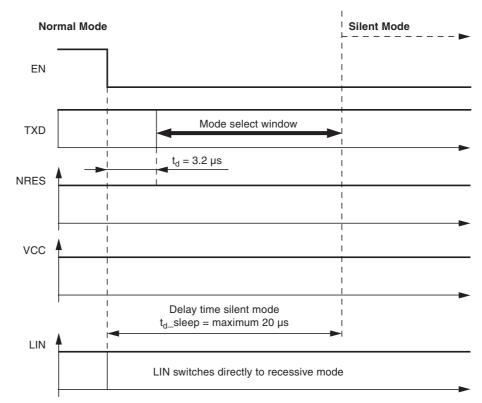

#### 4.2 Silent Mode

A falling edge at EN while TXD is high switches the IC into Silent Mode. The TXD Signal has to be logic high during the Mode Select window (Figure 4-2 on page 7). The transmission path is disabled in Silent Mode. The overall supply current from  $V_{Batt}$  is a combination of the  $I_{VSsi} = 57 \ \mu A$  plus the  $V_{CC}$  regulator output current  $I_{VCCs}$ .

The 3.3V/5V regulator with 2% tolerance can source up to 50 mA. In Silent Mode the internal slave termination between pin LIN and pin VS is disabled to minimize the power dissipation in case pin LIN is short-circuited to GND. Only a weak pull-up current (typically 10  $\mu$ A) between pin LIN and pin VS is present. The Silent Mode can be activated independently from the current level on pin LIN.

If an undervoltage condition occurs, NRES is switched to low and the ATA6623/ATA6625 changes its state to Fail-safe Mode.

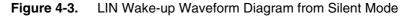

A voltage less than the LIN Pre-wake detection  $V_{\text{LINL}}$  at pin LIN activates the internal LIN receiver.

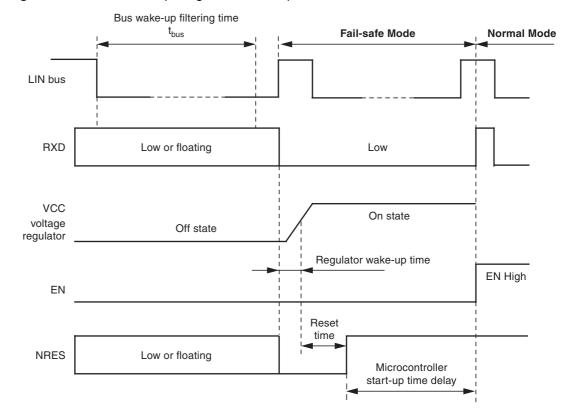

A falling edge at the LIN pin followed by a dominant bus level maintained for a certain time period ( $t_{bus}$ ) and the following rising edge at pin LIN (see Figure 4-3 on page 7) results in a remote wake-up request. The device switches from Silent Mode to Fail-safe Mode, then the internal LIN slave termination resistor is switched on. The remote wake-up request is indicated by a low level at pin RXD to interrupt the microcontroller (Figure 4-3 on page 7). EN high can be used to switch directly to Normal Mode.

#### Figure 4-2. Switch to Silent Mode

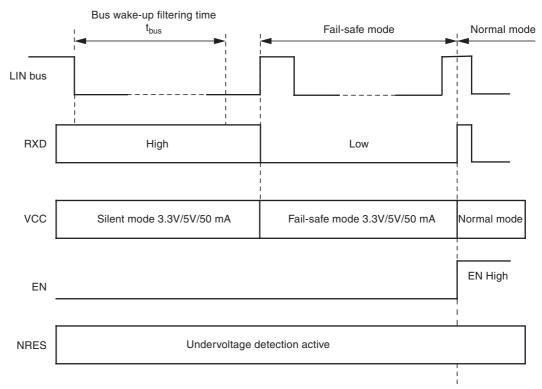

#### 4.3 Sleep Mode

A falling edge at EN while TXD is low switches the IC into Sleep Mode. The TXD Signal has to be logic low during the Mode Select window (Figure 4-4 on page 8).

In Sleep Mode the transmission path is disabled. Supply current from  $V_{Batt}$  is typically  $I_{VSsleep} = 10 \ \mu$ A. The  $V_{CC}$  regulator is switched off; NRES and RXD are low. The internal slave termination between pin LIN and pin VS is disabled to minimize the power dissipation in case pin LIN is short-circuited to GND. Only a weak pull-up current (typically 10  $\mu$ A) between pin LIN and pin VS is present. The Sleep Mode can be activated independently from the current level on pin LIN.

A voltage less than the LIN Pre-wake detection  $V_{\text{LINL}}$  at pin LIN activates the internal LIN receiver.

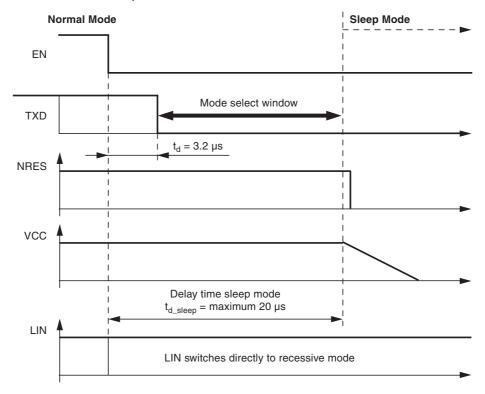

A falling edge at the LIN pin followed by a dominant bus level maintained for a certain time period ( $t_{bus}$ ) and a following rising edge at pin LIN respectively results in a remote wake-up request. The device switches from Sleep Mode to Fail-safe Mode.

The  $V_{CC}$  regulator is activated, and the internal LIN slave termination resistor is switched on. The remote wake-up request is indicated by a low level at the RXD pin to interrupt the microcontroller (Figure 4-5 on page 9).

EN high can be used to switch directly from Sleep/Silent to Fail-safe Mode. If EN is still high after VCC ramp up and undervoltage reset time, the IC switches to Normal Mode.

Figure 4-4. Switch to Sleep Mode

#### Figure 4-5. LIN Wake-up Diagram from Sleep Mode

#### 4.4 Fail-safe Mode

At system power-up the device automatically switches to Fail-safe Mode. The voltage regulator is switched on ( $V_{CC} = 3.3V/5V/50$  mA), (see Figure 6-1 on page 11). The NRES output switches to low for t<sub>res</sub> = 4 ms and gives a reset to the microcontroller. LIN communication is switched off. The IC stays in this mode until EN is switched to high, and changes then to the Normal Mode. A power down of  $V_{Batt}$  ( $V_S < 4V$ ) during Silent- or Sleep Mode switches the IC into the Fail-safe Mode after power up. A logic low at NRES switches the IC into Fail-safe Mode directly.

#### 4.5 Unpowered Mode

If you connect battery voltage to the application circuit, the voltage at the VS pin increases according to the block capacitor (see Figure 6-1 on page 11). After VS is higher than the VS undervoltage threshold VS<sub>th</sub>, the IC mode changes from Unpowered Mode to Fail-safe Mode. The VCC output voltage reaches its nominal value after  $t_{VCC}$ . This time,  $t_{VCC}$ , depends on the VCC capacitor and the load.

NRES is low for the reset time delay t<sub>Reset</sub>; no mode change is possible during this time.

### 5. Fail-safe Features

- During a short-circuit at LIN to  $V_{Battery}$ , the output limits the output current to  $I_{BUS\_LIM}$ . Due to the power dissipation, the chip temperature exceeds  $T_{LINoff}$  and the LIN output is switched off. The chip cools down and after a hysteresis of  $T_{hys}$ , switches the output on again. RXD stays on high because LIN is high. During LIN overtemperature switch-off, the  $V_{CC}$  regulator is working independently.

- During a short-circuit from LIN to GND the IC can be switched into Sleep or Silent Mode. If the short-circuit disappears, the IC starts with a remote wake-up.

- The reverse current is very low < 15  $\mu$ A at pin LIN during loss of V<sub>Batt</sub> or GND. This is optimal behavior for bus systems where some slave nodes are supplied from battery or ignition.

- During a short circuit at VCC, the output limits the output current to  $I_{VCCn}$ . Because of undervoltage, NRES switches to low and sends a reset to the microcontroller. The IC switches into Fail-safe Mode. If the chip temperature exceeds the value  $T_{VCCoff}$ , the  $V_{CC}$  output switches off. The chip cools down and after a hysteresis of  $T_{hys}$ , switches the output on again. Because of Fail-safe Mode, the  $V_{CC}$  voltage will switch on again although EN is switched off from the microcontroller. The microcontroller can then start with normal operation.

- Pin EN provides a pull-down resistor to force the transceiver into Recessive Mode if EN is disconnected.

- Pin RXD is set floating if V<sub>Batt</sub> is disconnected.

- Pin TXD provides a pull-up resistor to force the transceiver into Recessive Mode if TXD is disconnected.

- If TXD is short-circuited to GND, it is possible to switch to Sleep Mode via ENABLE after tdom > 20 ms.

### 6. Voltage Regulator

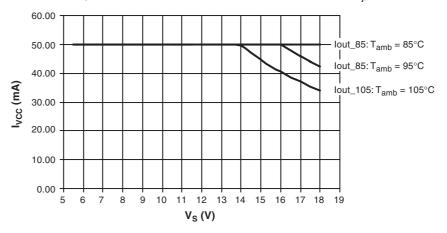

The voltage regulator needs an external capacitor for compensation and to smooth the disturbances from the microcontroller. It is recommended to use an electrolythic capacitor with  $C > 10 \ \mu\text{F}$  and a ceramic capacitor with  $C = 100 \ n\text{F}$ . The values of these capacitors can be varied by the customer, depending on the application.

With this special SO8 package (fused lead frame to pin3) an  $R_{thja}$  of 80 K/W is achieved. Therefore, it is recommended to connect pin 3 with a wide GND plate on the printed board to get a good heat sink.

The main power dissipation of the IC is created from the  $V_{CC}$  output current  $I_{VCC},$  which is needed for the application.

Figure 6-2 shows the safe operating area of the ATA6623/ATA6625.

Figure 6-2. Power Dissipation: Save Operating Area versus  $V_{CC}$  Output Current and Supply Voltage  $V_S$  at Different Ambient Temperatures Due to  $R_{thia} = 80 \text{ K/W}$

For programming purposes of the microcontroller it is potentially neccessary to supply the  $V_{CC}$  output via an external power supply while the  $V_S$  Pin of the system basis chip is disconnected. This behavior is no problem for the system basis chip.

# 7. Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameters                                                                                          | Symbol              | Min. | Тур. | Max. | Unit |

|-----------------------------------------------------------------------------------------------------|---------------------|------|------|------|------|

| Supply voltage V <sub>S</sub>                                                                       | Vs                  | -0.3 |      | +40  | V    |

| Pulse time $\leq$ 500 ms<br>T <sub>a</sub> = 25°C<br>Output current I <sub>VCC</sub> $\leq$ 50 mA   | Vs                  |      |      | +40  | V    |

| Pulse time $\leq$ 2 min<br>T <sub>a</sub> = 25°C<br>Output current I <sub>VCC</sub> $\leq$ 50 mA    | V <sub>S</sub>      |      |      | 27   | V    |

| Logic pins (RxD, TxD, EN, NRES)                                                                     |                     | -0.3 |      | +5.5 | V    |

| Output current NRES                                                                                 | I <sub>NRES</sub>   |      |      | +2   | mA   |

| LIN<br>- DC voltage                                                                                 |                     | -27  |      | +40  | V    |

| V <sub>CC</sub><br>- DC voltage                                                                     |                     | -0.3 |      | +5.5 | V    |

| According to IBEE LIN EMC<br>Test specification 1.0 following IEC 61000-4-2<br>- Pin VS, LIN to GND |                     | ±6   |      |      | ĸv   |

| ESD HBM following STM5.1<br>with 1.5 kΩ/100 pF<br>- Pin VS, LIN to GND                              |                     | ±8   |      |      | KV   |

| HBM ESD<br>ANSI/ESD-STM5.1<br>JESD22-A114<br>AEC-Q100 (002)                                         |                     | ±3   |      |      | KV   |

| CDM ESD STM 5.3.1                                                                                   |                     | ±750 |      |      | V    |

| Junction temperature                                                                                | Тj                  | -40  |      | +150 | °C   |

| Storage temperature                                                                                 | T <sub>s</sub>      | -55  |      | +150 | °C   |

| Thermal resistance junction to ambient (free air)                                                   | R <sub>thja</sub>   |      |      | 145  | K/W  |

| Special heat sink at GND (pin 3) on PCB                                                             | R <sub>thja</sub>   |      | 80   |      | K/W  |

| Thermal shutdown of V <sub>CC</sub> regulator                                                       | T <sub>VCCoff</sub> | 150  | 160  | 170  | °C   |

| Thermal shutdown of LIN output                                                                      | T <sub>LINoff</sub> | 150  | 160  | 170  | °C   |

| Thermal shutdown hysteresis                                                                         | T <sub>hys</sub>    |      | 10   |      | °C   |

### 8. Electrical Characteristics

$5V < V_S < 27V$ ,  $-40^{\circ}C < T_i < 150^{\circ}C$ ; unless otherwise specified all values refer to GND pins.

| No. | Parameters                            | Test Conditions                                                            | Pin | Symbol               | Min. | Тур. | Max.                      | Unit | Туре |

|-----|---------------------------------------|----------------------------------------------------------------------------|-----|----------------------|------|------|---------------------------|------|------|

| 1   | VS Pin                                |                                                                            |     |                      |      |      |                           |      |      |

| 1.1 | Nominal DC voltage range              |                                                                            | VS  | Vs                   | 5    | 13.5 | 27                        | V    | Α    |

| 1.2 | Supply current in Sleep               | Sleep Mode<br>$V_{LIN} > V_S - 0.5V$<br>$V_S < 14V (T_j = 25^{\circ}C)$    | VS  | I <sub>VSsleep</sub> | 3    | 10   | 14                        | μA   | A    |

| 1.2 | Mode                                  | Sleep Mode<br>$V_{LIN} > V_S - 0.5V$<br>$V_S < 14V (T_j = 125^{\circ}C)$   |     | I <sub>VSsleep</sub> | 5    | 11   | 16                        | μA   | A    |

| 1.3 | Supply current in Silent              | Bus recessive<br>$V_S < 14V (T_j = 25^{\circ}C)$<br>Without load at VCC    |     | I <sub>VSsi</sub>    | 47   | 57   | 67                        | μA   | A    |

| 1.5 | Mode                                  | Bus recessive<br>$V_S < 14V (T_j = 125^{\circ}C)$<br>Without load at VCC   |     | I <sub>VSsi</sub>    | 56   | 66   | 76                        | μA   | A    |

| 1.4 | Supply current in Normal Mode         | Bus recessive<br>V <sub>S</sub> < 14V<br>Without load at VCC               | VS  | I <sub>VSrec</sub>   | 0.3  |      | 0.8                       | mA   | A    |

| 1.5 | Supply current in Normal Mode         | Bus dominant<br>V <sub>S</sub> < 14V<br>V <sub>CC</sub> load current 50 mA | VS  | I <sub>VSdom</sub>   | 50   |      | 53                        | mA   | A    |

| 1.6 | V <sub>S</sub> undervoltage threshold |                                                                            | VS  | V <sub>Sth</sub>     | 4.0  | 4.5  | 5                         | V    | А    |

| 1.7 | VS undervoltage threshold hysteresis  |                                                                            | VS  | V <sub>Sth_hys</sub> |      | 0.2  |                           | V    | А    |

| 2   | RXD Output Pin                        |                                                                            |     |                      |      |      |                           |      |      |

| 2.1 | Low level input current               | Normal Mode<br>$V_{LIN} = 0V$<br>$V_{RXD} = 0.4V$                          | RXD | I <sub>RXD</sub>     | 1.3  | 2.5  | 8                         | mA   | A    |

| 2.2 | Low level output voltage              | I <sub>RXD</sub> = 1 mA                                                    | RXD | V <sub>RXDL</sub>    |      |      | 0.4                       | V    | Α    |

| 2.3 | Internal resistor to $V_{CC}$         |                                                                            | RXD | R <sub>RXD</sub>     | 3    | 5    | 7                         | kΩ   | Α    |

| 3   | TXD Input Pin                         |                                                                            |     |                      |      |      |                           |      |      |

| 3.1 | Low level voltage input               |                                                                            | TXD | V <sub>TXDL</sub>    | -0.3 |      | +0.8                      | V    | Α    |

| 3.2 | High level voltage input              |                                                                            | TXD | V <sub>TXDH</sub>    | 2    |      | V <sub>CC</sub> +<br>0.3V | V    | А    |

| 3.3 | Pull-up resistor                      | $V_{TXD} = 0V$                                                             | TXD | R <sub>TXD</sub>     | 125  | 250  | 400                       | kΩ   | Α    |

| 3.4 | High level leakage<br>current         | $V_{TXD} = 5V$                                                             | TXD | I <sub>TXD</sub>     | -3   |      | +3                        | μA   | Α    |

| 4   | EN Input Pin                          |                                                                            |     |                      |      |      |                           |      |      |

| 4.1 | Low level voltage input               |                                                                            | EN  | V <sub>ENL</sub>     | -0.3 |      | +0.8                      | V    | Α    |

| 4.2 | High level voltage input              |                                                                            | EN  | V <sub>ENH</sub>     | 2    |      | V <sub>CC</sub> +<br>0.3V | V    | А    |

| 4.3 | Pull-down resistor                    | $V_{EN} = 5V$                                                              | EN  | R <sub>EN</sub>      | 50   | 125  | 200                       | kΩ   | Α    |

| 4.4 | Low level input current               | $V_{EN} = 0V$                                                              | EN  | I <sub>EN</sub>      | -3   |      | +3                        | μA   | Α    |

# 8. Electrical Characteristics (Continued)

$5V < V_S < 27V$ ,  $-40^{\circ}C < T_i < 150^{\circ}C$ ; unless otherwise specified all values refer to GND pins.

| No.  | Parameters                                     | Test Conditions                                                                         | Pin  | Symbol                                   | Min.                                   | Тур. | Max.        | Unit   | Туре   |

|------|------------------------------------------------|-----------------------------------------------------------------------------------------|------|------------------------------------------|----------------------------------------|------|-------------|--------|--------|

| 5    | NRES Open Drain Outp                           | ut Pin                                                                                  |      |                                          | -l                                     |      |             | I      |        |

| 5.1  | Low level output voltage                       | $V_{S} \ge 5.5V$<br>$I_{NRES} = 1 \text{ mA}$<br>$I_{NRES} = 250 \mu\text{A}$           | NRES | V <sub>NRESL</sub><br>V <sub>NRESL</sub> |                                        |      | 0.2<br>0.14 | V<br>V | A<br>A |

| 5.2  | Low level output low                           | $10 k\Omega to VCC V_{CC} = 0V$                                                         | NRES | V <sub>NRESLL</sub>                      |                                        |      | 0.2         | V      | A      |

| 5.3  | Undervoltage reset time                        | $V_{VS} \ge 5.5V$<br>$C_{NRES} = 20 \text{ pF}$                                         | NRES | t <sub>Reset</sub>                       | 2                                      | 4    | 6           | ms     | A      |

| 5.4  | Reset debounce time for falling edge           | V <sub>VS</sub> ≥ 5.5V<br>C <sub>NRES</sub> = 20 pF                                     | NRES | t <sub>res_f</sub>                       | 1.5                                    |      | 10          | μs     | A      |

| 6    | VCC Voltage Regulator                          | ATA6623                                                                                 |      |                                          | -1 I                                   |      | l           | L      | _      |

| 6.1  | Output voltage V <sub>CC</sub>                 | 4V < VS < 18V<br>(0 mA to 50 mA)                                                        | VCC  | VCC <sub>nor</sub>                       | 3.234                                  |      | 3.366       | V      | A      |

| 6.2  | Output voltage $\rm V_{CC}$ at low $\rm V_{S}$ | 3V < VS < 4V                                                                            | VCC  | VCC <sub>low</sub>                       | V <sub>VS</sub> –<br>V <sub>Drop</sub> |      | 3.366       | V      | A      |

| 6.3  | Regulator drop voltage                         | VS > 3V, $I_{VCC} = -15 \text{ mA}$                                                     | VCC  | V <sub>Drop1</sub>                       |                                        |      | 200         | mV     | Α      |

| 6.4  | Regulator drop voltage                         | VS > 3V, $I_{VCC} = -50 \text{ mA}$                                                     | VCC  | V <sub>Drop2</sub>                       |                                        | 500  | 700         | mV     | Α      |

| 6.5  | Line regulation<br>maximum                     | 4V < VS < 18V                                                                           | VCC  | VCC <sub>line</sub>                      |                                        |      | 1           | %      | A      |

| 6.6  | Load regulation<br>maximum                     | 5 mA < I <sub>VCC</sub> < 50 mA                                                         | VCC  | VCC <sub>load</sub>                      |                                        | 0.5  | 2           | %      | A      |

| 6.7  | Power supply ripple rejection                  | 10 Hz to 100 kHz<br>$C_{VCC} = 10 \ \mu\text{F}$<br>VS = 14V, I <sub>VCC</sub> = -15 mA |      |                                          | 50                                     |      |             | dB     | с      |

| 6.8  | Output current limitation                      | VS > 4V                                                                                 | VCC  | I <sub>VCCs</sub>                        | -200                                   | -160 |             | mA     | A      |

| 6.9  | Load capacity                                  | 1Ω < ESR < 5Ω @ 100 kHz                                                                 | VCC  | C <sub>load</sub>                        | 1.8                                    | 10   |             | μF     | D      |

| 6.10 | VCC undervoltage threshold                     | Referred to VCC<br>VS > 4V                                                              | VCC  | V <sub>thunN</sub>                       | 2.8                                    |      | 3.2         | V      | A      |

| 6.11 | Hysteresis of<br>undervoltage threshold        | Referred to VCC<br>VS > 4V                                                              | VCC  | Vhys <sub>thun</sub>                     |                                        | 150  |             | mV     | A      |

| 6.12 | Ramp up time VS > 4V<br>to VCC = 3.3V          | $C_{VCC} = 2.2 \ \mu F$<br>$I_{load} = -5 \ mA \ at \ VCC$                              | VCC  | t <sub>VCC</sub>                         |                                        | 100  | 250         | μs     | A      |

| 7    | VCC Voltage Regulator                          | ATA6625                                                                                 |      |                                          |                                        |      |             |        |        |

| 7.1  | Output voltage V <sub>CC</sub>                 | 5.5V < VS < 18V<br>(0 mA to 50 mA)                                                      | VCC  | VCC <sub>nor</sub>                       | 4.9                                    |      | 5.1         | V      | A      |

| 7.2  | Output voltage $\rm V_{CC}$ at low $\rm V_{S}$ | 4V < VS < 5.5V                                                                          | VCC  | VCC <sub>low</sub>                       | $V_{VS} - V_D$                         |      | 5.1         | V      | A      |

| 7.3  | Regulator drop voltage                         | VS > 4V, $I_{VCC} = -20 \text{ mA}$                                                     | VCC  | V <sub>D1</sub>                          |                                        |      | 250         | mV     | A      |

| 7.4  | Regulator drop voltage                         | VS > 4V, $I_{VCC} = -50 \text{ mA}$                                                     | VCC  | V <sub>D2</sub>                          |                                        | 400  | 600         | mV     | Α      |

| 7.5  | Regulator drop voltage                         | VS > 3.3V, $I_{VCC} = -15 \text{ mA}$                                                   | VCC  | V <sub>D3</sub>                          |                                        |      | 200         | mV     | A      |

| 7.6  | Line regulation<br>maximum                     | 5.5V < VS < 18V                                                                         | VCC  | VCC <sub>line</sub>                      |                                        |      | 1           | %      | A      |

## 8. Electrical Characteristics (Continued)

$5V < V_S < 27V$ ,  $-40^{\circ}C < T_i < 150^{\circ}C$ ; unless otherwise specified all values refer to GND pins.

| No.  | Parameters                                                                                                                                               | Test Conditions                                                                                  | Pin | Symbol                   | Min.              | Тур.  | Max.  | Unit | Type* |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----|--------------------------|-------------------|-------|-------|------|-------|

| 7.7  | Load regulation maximum                                                                                                                                  | 5 mA < I <sub>VCC</sub> < 50 mA                                                                  | VCC | VCC <sub>load</sub>      |                   | 0.5   | 2     | %    | А     |

| 7.8  | Output current limitation                                                                                                                                | VS > 5.5V                                                                                        | VCC | I <sub>VCCs</sub>        | -200              | -160  |       | mA   | А     |

| 7.9  | Load capacity                                                                                                                                            | 1Ω < ESR < 5Ω @ 100 kHz                                                                          | VCC | Cload                    | 1.8               | 10    |       | μF   | D     |

| 7.10 | VCC undervoltage threshold                                                                                                                               | Referred to VCC<br>VS > 5.5V                                                                     | VCC | V <sub>thunN</sub>       | 4.2               |       | 4.8   | V    | А     |

| 7.11 | Hysteresis of<br>undervoltage threshold                                                                                                                  | Referred to VCC<br>VS > 5.5V                                                                     | VCC | Vhys <sub>thun</sub>     |                   | 250   |       | mV   | A     |

| 7.12 | Ramp up time VS > 5.5V<br>to VCC = 5V                                                                                                                    | $C_{VCC} = 2.2 \ \mu F$<br>$I_{load} = -5 \ mA \ at \ VCC$                                       | VCC | T <sub>VCC</sub>         |                   | 130   | 300   | μs   | А     |

| 8    |                                                                                                                                                          | ad Conditions:<br>ເΩ; Load 2 (Large): 10 nF, 5(<br>cifies the Timing Parameter                   |     |                          |                   |       | 20 pF | •    |       |

| 8.1  | Driver recessive output voltage                                                                                                                          | Load1/Load2                                                                                      | LIN | V <sub>BUSrec</sub>      | $0.9 	imes V_{S}$ |       | Vs    | V    | А     |

| 8.2  | Driver dominant voltage                                                                                                                                  | $V_{VS} = 7V$<br>$R_{load} = 500\Omega$                                                          | LIN | V_LoSUP                  |                   |       | 1.2   | V    | А     |

| 8.3  | Driver dominant voltage                                                                                                                                  | $V_{VS} = 18V$<br>$R_{load} = 500\Omega$                                                         | LIN | V_HISUP                  |                   |       | 2     | V    | А     |

| 8.4  | Driver dominant voltage                                                                                                                                  | $V_{VS} = 7V$<br>$R_{load} = 1000\Omega$                                                         | LIN | V_LoSUP_1k               | 0.6               |       |       | V    | A     |

| 8.5  | Driver dominant voltage                                                                                                                                  | $V_{VS} = 18V$<br>$R_{load} = 1000\Omega$                                                        | LIN | V_HiSUP_1k               | 0.8               |       |       | V    | Α     |

| 8.6  | Pull–up resistor to V <sub>S</sub>                                                                                                                       | The serial diode is mandatory                                                                    | LIN | R <sub>LIN</sub>         | 20                | 30    | 60    | kΩ   | Α     |

| 8.7  | LIN current limitation<br>$V_{BUS} = V_{Batt_max}$                                                                                                       |                                                                                                  | LIN | I <sub>BUS_LIM</sub>     | 40                | 120   | 200   | mA   | Α     |

| 8.8  | Input leakage current at<br>the receiver including<br>pull-up resistor as<br>specified                                                                   | Input Leakage current<br>Driver off<br>$V_{BUS} = 0V$<br>$V_{Batt} = 12V$                        | LIN | I <sub>BUS_PAS_dom</sub> | -1                | -0.35 |       | mA   | A     |

| 8.9  | Leakage current LIN recessive                                                                                                                            |                                                                                                  | LIN | I <sub>BUS_PAS_rec</sub> |                   | 15    | 20    | μA   | A     |

| 8.10 | Leakage current when<br>control unit disconnected<br>from ground.<br>Loss of local ground<br>must not affect<br>communication in the<br>residual network | GND <sub>Device</sub> = V <sub>S</sub><br>V <sub>Batt</sub> = 12V<br>0V < V <sub>BUS</sub> < 18V | LIN | I <sub>BUS_NO_gnd</sub>  | -10               | +0.5  | +10   | μA   | A     |

| 8.11 | Node has to sustain the<br>current that can flow<br>under this condition. Bus<br>must remain operational<br>under this condition.                        | $V_{Batt}$ disconnected<br>$V_{SUP_Device} = GND$<br>$0V < V_{BUS} < 18V$                        | LIN | I <sub>BUS</sub>         |                   | 5     | 15    | μA   | A     |

#### **8.** Electrical Characteristics (Continued) 5V < Vo < 27V. -40°C < T < 150°C: unless otherwise specified all values refer to GND pins. 8.

| No.  | Parameters                                                                      | Test Conditions                                                                                                                                                                                                                                                                                        | Pin | Symbol               | Min.                   | Тур.                 | Max.                                               | Unit | Type* |

|------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------|------------------------|----------------------|----------------------------------------------------|------|-------|

| 9    | LIN Bus Receiver                                                                |                                                                                                                                                                                                                                                                                                        |     |                      |                        |                      |                                                    |      | 1     |

| 9.1  | Center of receiver threshold                                                    | $V_{BUS_CNT} = (V_{th_dom} + V_{th_rec})/2$                                                                                                                                                                                                                                                            | LIN | V <sub>BUS_CNT</sub> | 0.475 × V <sub>S</sub> | $0.5 \times V_S$     | $\begin{array}{c} 0.525 \times \\ V_S \end{array}$ | V    | А     |

| 9.2  | Receiver dominant state                                                         | V <sub>EN</sub> = 5V                                                                                                                                                                                                                                                                                   | LIN | V <sub>BUSdom</sub>  | -27                    |                      | $0.4 	imes V_{S}$                                  | V    | А     |

| 9.3  | Receiver recessive state                                                        | $V_{EN} = 5V$                                                                                                                                                                                                                                                                                          | LIN | V <sub>BUSrec</sub>  | $0.6 	imes V_S$        |                      | 40                                                 | V    | Α     |

| 9.4  | Receiver input<br>hysteresis                                                    | $V_{hys} = V_{th\_rec} - V_{th\_dom}$                                                                                                                                                                                                                                                                  | LIN | V <sub>BUShys</sub>  | $0.028 \times V_S$     | 0.1 x V <sub>S</sub> | $0.175 \times V_S$                                 | V    | А     |

| 9.5  | Pre-wake detection LIN<br>High level input voltage                              |                                                                                                                                                                                                                                                                                                        | LIN | V <sub>LINH</sub>    | V <sub>S</sub> – 1V    |                      | V <sub>S</sub> +<br>0.3V                           | V    | А     |

| 9.6  | Pre-wake detection LIN<br>Low level input voltage                               | Activates the LIN receiver                                                                                                                                                                                                                                                                             | LIN | V <sub>LINL</sub>    | -27                    |                      | V <sub>S</sub> – 3.3V                              | V    | А     |

| 10   | Internal Timers                                                                 |                                                                                                                                                                                                                                                                                                        |     |                      |                        |                      |                                                    |      |       |

| 10.1 | Dominant time for wake-up via LIN bus                                           | $V_{LIN} = 0V$                                                                                                                                                                                                                                                                                         |     | t <sub>bus</sub>     | 30                     | 90                   | 150                                                | μs   | А     |

| 10.2 | Time delay for mode<br>change from Pre-normal<br>into Normal Mode via pin<br>EN | V <sub>EN</sub> = 5V                                                                                                                                                                                                                                                                                   |     | t <sub>norm</sub>    | 5                      |                      | 20                                                 | μs   | A     |

| 10.3 | Time delay for mode<br>change from Normal<br>Mode to Sleep Mode via<br>pin EN   | V <sub>EN</sub> = 0V                                                                                                                                                                                                                                                                                   |     | t <sub>sleep</sub>   | 2                      | 7                    | 15                                                 | μs   | A     |

| 10.4 | TXD dominant time out timer                                                     | V <sub>TXD</sub> = 0V                                                                                                                                                                                                                                                                                  |     | t <sub>dom</sub>     | 6                      | 13                   | 20                                                 | ms   | А     |

| 10.5 | Time delay for mode<br>change from Silent Mode<br>into Normal Mode via EN       |                                                                                                                                                                                                                                                                                                        |     | t <sub>s_n</sub>     | 5                      | 15                   | 40                                                 | μs   | A     |

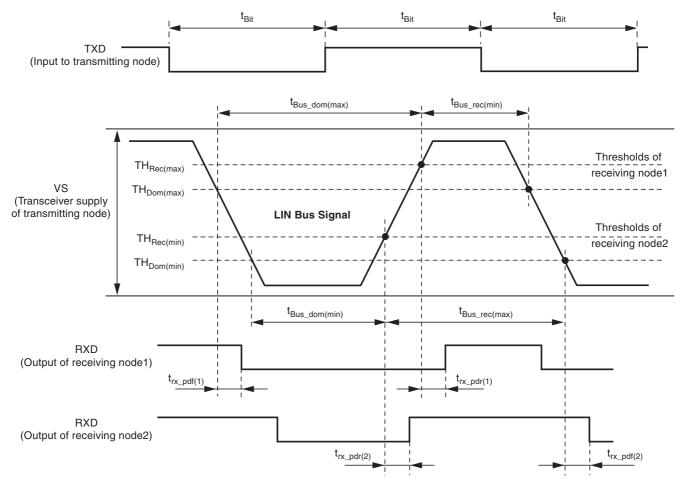

| 10.6 | Duty cycle 1                                                                    | $\begin{array}{l} TH_{Rec(max)}=0.744\times V_S\\ TH_{Dom(max)}=0.581\times V_S\\ V_S=7.0V\ to\ 18V\\ t_{Bit}=50\ \mu s\\ D1=t_{bus\_rec(min)}/(2\times t_{Bit}) \end{array}$                                                                                                                          |     | D1                   | 0.396                  |                      |                                                    |      | A     |

| 10.7 | Duty cycle 2                                                                    | $\begin{array}{l} TH_{Rec(min)}=0.422\times V_S\\ TH_{Dom(min)}=0.284\times V_S\\ V_S=7.6V\ to\ 18V\\ t_{Bit}=50\ \mu s\\ D2=t_{bus\_rec(max)}/(2\times t_{Bit}) \end{array}$                                                                                                                          |     | D2                   |                        |                      | 0.581                                              |      | A     |

| 10.8 | Duty cycle 3                                                                    | $\begin{array}{l} TH_{Rec(max)}=0.778\times V_S\\ TH_{Dom(max)}=0.616\times V_S\\ V_S=7.0V\ to\ 18V\\ t_{Bit}=96\ \mu s\\ D3=t_{bus\_rec(min)}/(2\times t_{Bit}) \end{array}$                                                                                                                          |     | D3                   | 0.417                  |                      |                                                    |      | A     |

| 10.9 | Duty cycle 4                                                                    | $\begin{array}{l} TH_{\text{Rec}(\text{min})} = 0.389 \times V_{\text{S}} \\ TH_{\text{Dom}(\text{min})} = 0.251 \times V_{\text{S}} \\ V_{\text{S}} = 7.6V \text{ to } 18V \\ t_{\text{Bit}} = 96 \ \mu\text{s} \\ D4 = t_{\text{bus}\_\text{rec}(\text{max})}/(2 \times t_{\text{Bit}}) \end{array}$ |     | D4                   |                        |                      | 0.590                                              |      | A     |

## 8. Electrical Characteristics (Continued)

$5V < V_S < 27V$ ,  $-40^{\circ}C < T_i < 150^{\circ}C$ ; unless otherwise specified all values refer to GND pins.

| 0     | 1                                                                                                                                                                            | -                                                                           |     |                                                    |      |      |      |      |       |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----|----------------------------------------------------|------|------|------|------|-------|

| No.   | Parameters                                                                                                                                                                   | Test Conditions                                                             | Pin | Symbol                                             | Min. | Тур. | Max. | Unit | Type* |

| 10.10 | Slope time falling and rising edge at LIN                                                                                                                                    | V <sub>S</sub> = 7.0V to 18V                                                |     | t <sub>SLOPE_fall</sub><br>t <sub>SLOPE_rise</sub> | 3.5  |      | 22.5 | μs   | А     |

| 11    | Receiver Electrical AC Parameters of the LIN Physical Layer<br>LIN Receiver, RXD Load Conditions: Internal Pull-up $R_{RXD} = 5 \text{ k}\Omega$ ; $C_{RXD} = 20 \text{ pF}$ |                                                                             |     |                                                    |      |      |      |      |       |

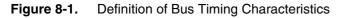

| 11.1  | Propagation delay of receiver Figure 8-1                                                                                                                                     | $V_{S} = 7.0V$ to 18V<br>$t_{rx_{pd}} = max(t_{rx_{pdr}}, t_{rx_{pdf}})$    |     | t <sub>rx_pd</sub>                                 |      |      | 6    | μs   | А     |

| 11.2  | Symmetry of receiver<br>propagation delay rising<br>edge minus falling edge                                                                                                  | $V_{s} = 7.0V \text{ to } 18V$<br>$t_{rx\_sym} = t_{rx\_pdr} - t_{rx\_pdf}$ |     | t <sub>rx_sym</sub>                                | -2   |      | +2   | μs   | A     |

#### Figure 8-2. Application Circuit

# 9. Ordering Information

| Extended Type Number | Package | Remarks                                                   |

|----------------------|---------|-----------------------------------------------------------|

| ATA6623-TAPY         | SO8     | 3.3V LIN system basis chip, Pb-free, 1k, taped and reeled |

| ATA6625-TAPY         | SO8     | 5V LIN system basis chip, Pb-free, 1k, taped and reeled   |

| ATA6623-TAQY         | SO8     | 3.3V LIN system basis chip, Pb-free, 4k, taped and reeled |

| ATA6625-TAQY         | SO8     | 5V LIN system basis chip, Pb-free, 4k, taped and reeled   |

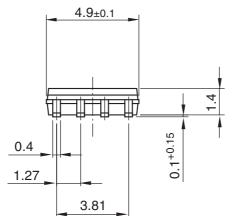

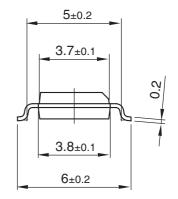

### **10. Package Information**

Package: SO 8

Dimensions in mm

Drawing-No.: 6.541-5031.01-4 Issue: 1; 15.08.06

technical drawings according to DIN specifications

## 11. Revision History

Please note that the following page numbers referred to in this section refer to the specific revision mentioned, not to this document.

| Revision No.     | History                                                                                        |

|------------------|------------------------------------------------------------------------------------------------|

|                  | "Pre-normal Mode" in "Fail-safe Mode" changed                                                  |

| 4957F-AUTO-02/08 | Section 7 "Absolute Maximum Ratings" on page 13 changed                                        |

|                  | Section 8 "Electrical Characteristics" numbers 10.5 to 10.10 on pages 17 to 18 changed         |

| 4957E-AUTO-10/07 | Section 9 "Ordering Information" on page 20 changed                                            |

|                  | Features changed                                                                               |

|                  | Block diagram changed                                                                          |

|                  | Application diagram changed                                                                    |

|                  | <ul> <li>Text changed under the headings:</li> </ul>                                           |

| 4957D-AUTO-07/07 | 3.2, 3.3, 3.4, 3.6, 3.7, 3.8, 3.9, 4, 4.1, 4.2, 4.3, 4.4, 4.5, 5.5, 5.6, 6                     |

|                  | • Figure 4-2, 4-3, 4-4, 4-5, 8-2: changed                                                      |

|                  | Figure title 6-1: text changed                                                                 |

|                  | <ul> <li>Abs. Max. Ratings: row "Output current NRES" added</li> </ul>                         |

|                  | • El. Char. table: values changed in the following rows:                                       |

|                  | 1.3, 5.1, 5.3, 5.4, 6.9, 6.12, 7.9, 11.1                                                       |

|                  | Features on page 1 changed                                                                     |

|                  | <ul> <li>Table 2-1 "Pin Description" on page 2 changed</li> </ul>                              |

|                  | <ul> <li>Section 3-1 "Physical Layer Compatibility" on page 3 added</li> </ul>                 |

|                  | <ul> <li>Section 3-2 "Supply Pin (VS) on page 3 changed</li> </ul>                             |

|                  | • Section 3-3 "Ground Pin (GND) on page 3 changed                                              |

|                  | • Section 3-8 "Dominant Time-out Function (TXD)" on page 4 changed                             |

|                  | <ul> <li>Section 4-1 "Normal Mode" on page 5 changed</li> </ul>                                |

|                  | <ul> <li>Section 4-2 "Silent Mode" on page 5 changed</li> </ul>                                |

|                  | • Figure 4-3 "LIN Wake-up Waveform Diagram from Silent Mode" on page                           |

| 4957C-AUTO-02/07 | 6 changed                                                                                      |

| -3370-7010-02/07 | <ul> <li>Section 4.3 "Sleep Mode" on page 7 changed</li> </ul>                                 |

|                  | <ul> <li>Section 4-5 "Unpowered Mode" on page 7 changed</li> </ul>                             |

|                  | <ul> <li>Figure 4-4 "Switch to Sleep Mode" on page 8 changed</li> </ul>                        |

|                  | Figure 4-6 "V <sub>CC</sub> Voltage Regulator: Ramp up and Undervoltage" on page     9 changed |

|                  | <ul> <li>Section 5 "Fail-safe Features on page 9 changed</li> </ul>                            |

|                  | Section 6 "Voltage Regulator" on page 10 changed                                               |

|                  | Section 7 "Absolute Maximum Ratings" on page 11 changed                                        |

|                  | Section 8 "Electrical Characteristics" on pages 12 to 16 changed                               |

|                  | Section 9 "Ordering Information" on page 18 changed                                            |

#### **Headquarters**

Atmel Corporation 2325 Orchard Parkway San Jose, CA 95131 USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### International

Atmel Asia Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369 Atmel Europe Le Krebs 8, Rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-Yvelines Cedex France Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11

#### Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Product Contact**

Web Site www.atmel.com *Technical Support* auto\_control@atmel.com Sales Contact www.atmel.com/contacts

Literature Requests www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNTIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, or warranted for use as components in applications intended to support or sustain life.

© 2008 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.