# RENESAS

# RNA52A10MM Dual CMOS system-RESET IC

REJ03D0858-0400 Rev.4.00 Feb 23, 2007

#### Description

The RNA52A10MM incorporates two reset circuits, one with and one without a delay function, allowing the generation of separate reset signals for a microprocessor and associated system circuits. The detection voltage of each reset circuit is determined by the value of an external resistor, and the internal reference voltage is 1.0 V. The CMOS process for the RNA52A10MM means that the device draws only 1.1  $\mu$ A (typ.). The reset cancellation delay time is set with a high degree of accuracy by the values of a capacitor and resistor connected with the CD pin. The MR (manual reset) input pin is provided for the reset circuit with the delay function, and the reset signal is output in response to a high level on the MR input pin. The MR pin is pulled down by a 2-M $\Omega$  internal resistor. Output pins Vo1 and Vo2 are open drain.

#### Features

- Two CMOS reset circuits, one with and one without the delay function

- Reference voltage: 1.0 V

- Reference voltage accuracy:  $\pm 50 \text{ mV}$

- Reference voltage hysteresis: 6% (typ.)

- Low current consumption: 1.1 µA (typ.)

- Delay time set by an external CR circuit

- Manual reset input

- Open-drain output

- MMPAK-8 (8-pin) package

- Operating temperature range: 40 to 85°C

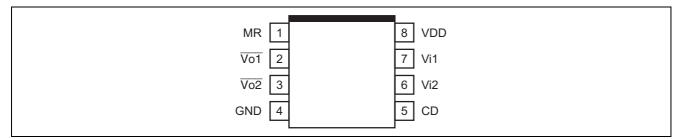

### **Pin Arrangement**

### Application

- Power-supply monitoring and resetting for microprocessors

- Power supply sequence control for microprocessors

- Desktop and laptop PCs

- PC peripheral devices such as printers

- Digital still cameras, digital video cameras, and PDAs

- Battery-driven products

- Wireless communications systems

#### $\stackrel{\}{\leq} R_{L1}$ V<sub>DD1</sub> □ Vo1 $R_{S1}$ Reset circuit Vi1 2 7 $\Box V_{DD4}$ $R_{S2}$ $\leq R_{L2}$ V<sub>DD2</sub> Vo2 Reset circuit 2 RESET 3 $R_{S3}$ Vi2 Micro-6 computer $R_{S4}$ V<sub>REF</sub> 1.0V 2M VDD MR CD GND 8 5 4 1 $C_D$ $\mathsf{R}_\mathsf{D}$ $V_{DD0}$ $C_1$

#### Functional Block Diagram and Typical application Circuit

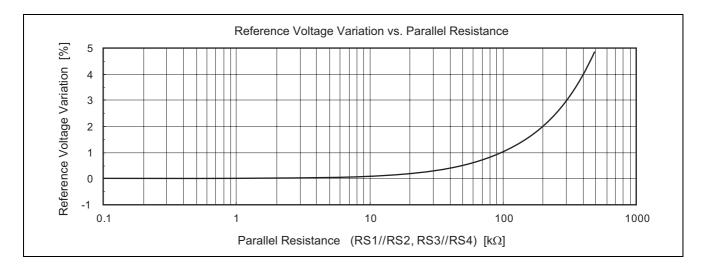

Notes: 1. Please refer to the following equations to set up reset-threshold voltages for power supplies  $V_{DD1}$  and  $V_{DD2}$ , and to set up external voltage-dividing resistor pairs  $R_{S1}$  and  $R_{S2}$ , and  $R_{S3}$  and  $R_{S4}$ .

(1)  $V_{DD1}$  reset-threshold voltage =  $V_{REF} \times (R_{S1}+R_{S2})/R_{S2}$

(2)  $V_{DD2}$  reset-threshold voltage =  $V_{REF} \times (R_{S3}+R_{S4})/R_{S4}$

Note that values must be set up within the following range: R\_{S1}, R\_{S2}, R\_{S3}, R\_{S4} \leq 50 \ k\Omega

See the following graph for the relationship between the reference voltage variation and the value selected for  $R_{S1}$ ,  $R_{S2}$ ,  $R_{S3}$  and  $R_{S4}$ .

2. For capacitor C1, select a type which has excellent frequency characteristics. For stable operation, place it between the VDD pin and the GND pin and as close as is possible to the chip.

The value of capacitor  $C_1$  must suit the system environment in terms of the quality of the power supply and so forth.

#### RNA52A10MM

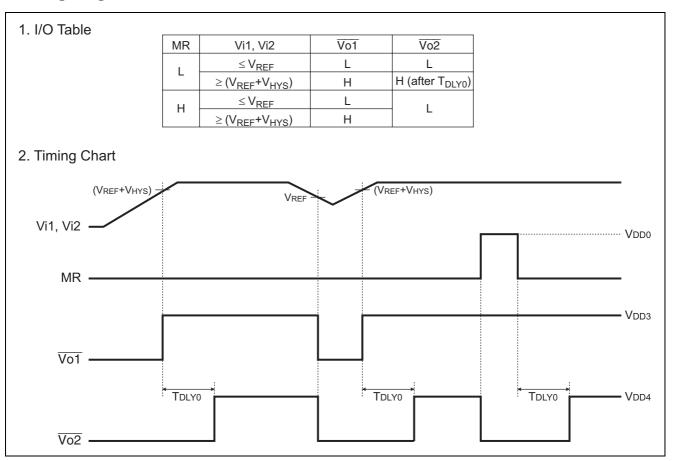

#### **Timing Diagram**

### **Absolute Maximum Ratings**

| Item                                                      | Symbol           | Ratings                 | Unit |

|-----------------------------------------------------------|------------------|-------------------------|------|

| Supply voltage (VDD)                                      | V <sub>DD</sub>  | 6.0                     | V    |

| Input voltage (Vi1, Vi2, MR, CD)                          | V <sub>IN</sub>  | -0.3 to V <sub>DD</sub> | V    |

| Output voltage (Vo1, Vo2)                                 | V <sub>OUT</sub> | -0.3 to 6.0             | V    |

| Output current (Vo1, Vo2)                                 | I <sub>OUT</sub> | 30                      | mA   |

| Continuous power dissipation<br>(Ta = 25°C, in still air) | P <sub>D</sub>   | 145                     | mW   |

| Operating temperature                                     | T <sub>OPR</sub> | -40 to 85               | °C   |

| Storage temperature                                       | T <sub>STG</sub> | -55 to 125              | °C   |

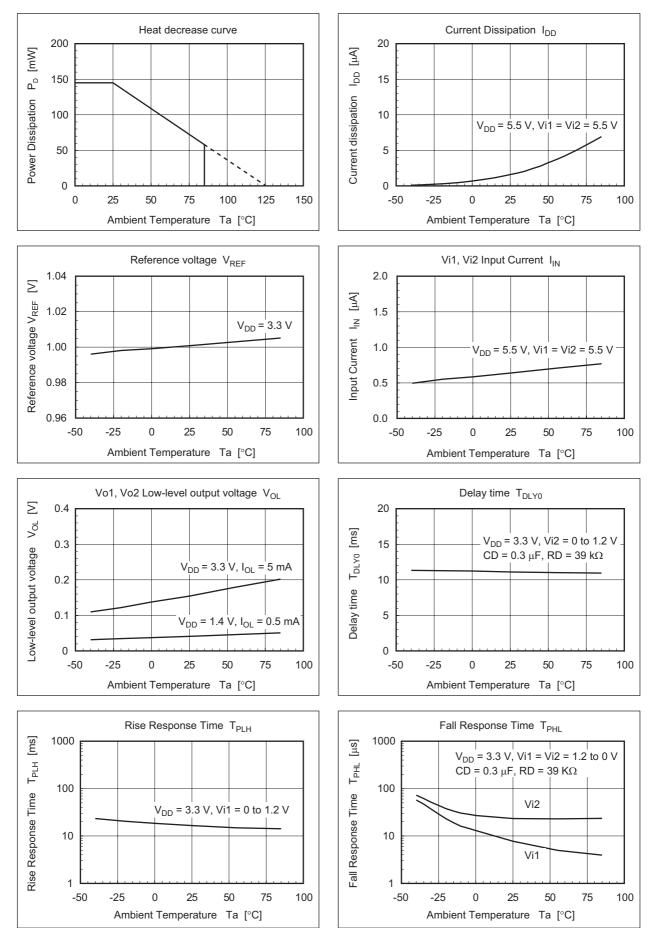

Note: Refer to the relevant characteristic curve on page 5 for continuous power dissipation.

### **Recommended Operating Conditions**

| Item                             | Symbol           | Min. | Max.            | Unit |

|----------------------------------|------------------|------|-----------------|------|

| Supply voltage (VDD)             | V <sub>DD</sub>  | 1.4  | 5.5             | V    |

| Input voltage (Vi1, Vi2, MR, CD) | V <sub>IN</sub>  | 0    | V <sub>DD</sub> | V    |

| Output voltage (Vo1, Vo2)        | V <sub>OUT</sub> | 0    | 5.5             | V    |

| Output current (Vo1, Vo2)        | I <sub>OUT</sub> | 0    | 15              | mA   |

| Operating temperature            | T <sub>OPR</sub> | -40  | 85              | °C   |

#### **Electrical Characteristics**

$(Ta = 25^{\circ}C, unless otherwise noted)$

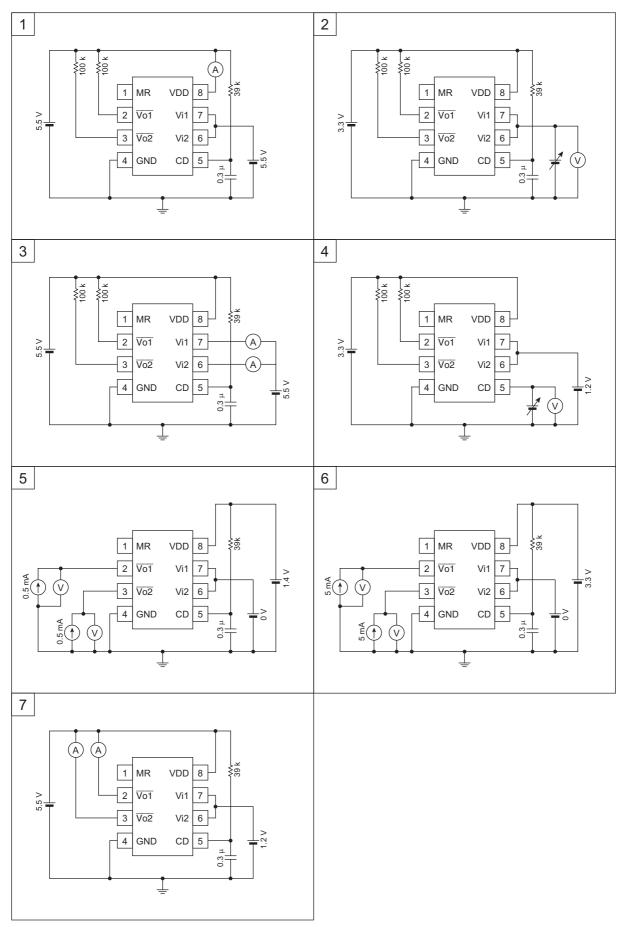

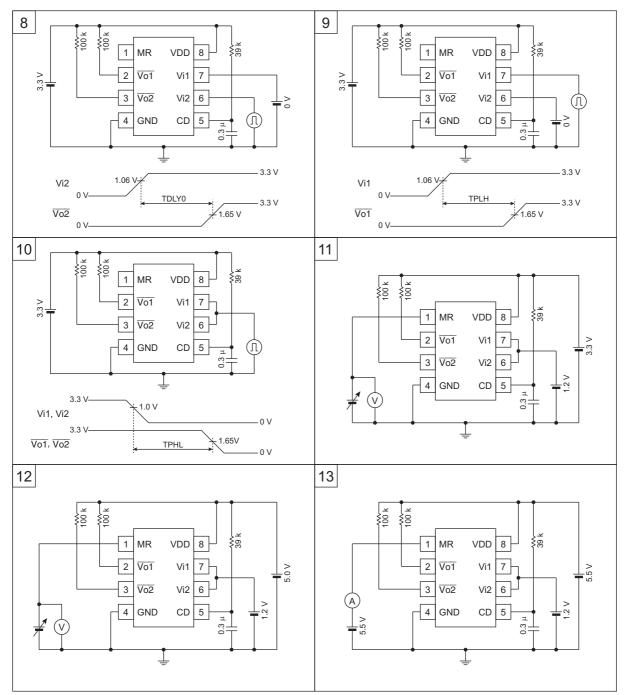

| Ite                                                                          | m                                         | Symbol                                            | Min.                           | Тур.                         | Max.                           | Unit      | Test Conditions                                                                                                                                                      | Test<br>Circuit |

|------------------------------------------------------------------------------|-------------------------------------------|---------------------------------------------------|--------------------------------|------------------------------|--------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Supply voltage                                                               |                                           | V <sub>DD</sub>                                   | 1.4                            | —                            | 5.5                            | V         |                                                                                                                                                                      | _               |

| Current consumption                                                          |                                           | I <sub>DD</sub>                                   | _                              | 1.1                          | 19                             | μΑ        | $V_{DD} = 5.5 V$<br>$V_{i1} = V_{i2} = 5.5 V$                                                                                                                        | 1               |

| Reference voltag                                                             | e                                         | V <sub>REF</sub>                                  | 0.95                           | 1.00                         | 1.05                           | V         | V <sub>DD</sub> = 3.3 V                                                                                                                                              | 2               |

| Reference voltage temperature<br>coefficient<br>(Reference value for design) |                                           | $\frac{\Delta V_{REF}}{V_{REF}\cdot\Delta T_{a}}$ | _                              | ±100                         | _                              | ppm<br>°C | $T_a = -40$ to $85^{\circ}C$                                                                                                                                         | 2               |

| Vi1, Vi2 input<br>hysteresis voltag                                          | e                                         | V <sub>HYS</sub>                                  | 28.5<br>(V <sub>REF</sub> ×3%) | 60<br>(V <sub>REF</sub> ×6%) | 94.5<br>(V <sub>REF</sub> ×9%) | mV        | V <sub>DD</sub> = 3.3 V                                                                                                                                              | 2               |

| Vi1, Vi2 input current                                                       |                                           | I <sub>IN</sub>                                   | _                              | 0.6                          | 2.2                            | μΑ        | $V_{DD} = 5.5 V$<br>$V_{i1} = V_{i2} = 5.5 V$                                                                                                                        | 3               |

| CD input thresho                                                             | ld voltage                                | V <sub>DLY</sub>                                  | V <sub>DD</sub> ×0.43          | V <sub>DD</sub> ×0.63        | V <sub>DD</sub> ×0.83          | V         | $V_{DD} = 3.3 V$<br>$V_{i1} = V_{i2} = 1.2 V$                                                                                                                        | 4               |

| Vo1, Vo2<br>low-level output voltage                                         |                                           |                                                   | _                              | 0.05                         | 0.15                           | v         | $V_{DD} = 1.4V$<br>$V_{i1} = V_{i2} = 0 V$<br>$I_{OL} = 0.5 mA$                                                                                                      | 5               |

|                                                                              |                                           | V <sub>OL</sub>                                   | _                              | 0.15                         | 0.35                           | v         | $V_{DD} = 3.3V$<br>$V_{i1} = V_{i2} = 0 V$<br>$I_{OL} = 5 mA$                                                                                                        | 6               |

| Vo1, Vo2<br>output leakage c                                                 | urrent                                    | I <sub>LK</sub>                                   | _                              | _                            | 100                            | nA        | $V_{DD} = V_{O1} = V_{O2} = 5.5 V$<br>$V_{i1} = V_{i2} = 1.2 V$                                                                                                      | 7               |

| Vo2<br>Delay time <sup>Note1</sup>                                           | Incomplete<br>discharge of<br>capacity CD | T <sub>DLY</sub>                                  | 1.1                            | 11                           | 17                             | ms        | $V_{DD}$ = 3.3 V<br>$V_{i2}$ = 0 V→1.2 V<br>$C_D$ = 0.3 μF, R <sub>D</sub> = 39 kΩ                                                                                   | 8               |

|                                                                              | complete<br>discharge of<br>capacity CD   | T <sub>DLY0</sub>                                 | 7                              | 11                           | 17                             | ms        |                                                                                                                                                                      | 8               |

| Vo1<br>Rise response time                                                    |                                           | T <sub>PLH</sub>                                  | _                              | 30                           | 300                            | μs        | $V_{DD} = 3.3 V$<br>$V_{i1} = 0 V \rightarrow 1.2 V$                                                                                                                 | 9               |

| Vo1, Vo2<br>fall response time                                               |                                           | T <sub>PHL</sub>                                  | _                              | 30                           | 800                            | μs        | $\begin{split} V_{DD} &= 3.3 \ V \\ V_{i1} &= V_{i2} = 1.2 \ V {\rightarrow} 0 \ V \\ C_{D} &= 0.3 \ \mu\text{F}, \ \text{R}_{D} = 39 \ \text{k} \Omega \end{split}$ | 10              |

| MR low-level inp                                                             | ut voltage                                | VIL                                               | _                              | _                            | V <sub>DD</sub> ×0.2           | V         | V <sub>DD</sub> = 3.3 V<br>V <sub>i1</sub> = V <sub>i2</sub> = 1.2 V                                                                                                 | 11              |

| MR high-level input voltage                                                  | $V_{DD} < 4.5V$                           | - V <sub>IH</sub>                                 | V <sub>DD</sub> ×0.75          | _                            | _                              | V         | V <sub>DD</sub> = 3.3 V<br>V <sub>i1</sub> = V <sub>i2</sub> = 1.2 V                                                                                                 | 11              |

|                                                                              | $V_{DD} \ge 4.5V$                         |                                                   | V <sub>DD</sub> ×0.5           | _                            | _                              | V         | V <sub>DD</sub> = 5.0 V<br>V <sub>i1</sub> = V <sub>i2</sub> = 1.2 V                                                                                                 | 12              |

| MR input<br>pull-down resistance                                             |                                           | R <sub>MR</sub>                                   | 0.5                            | 2                            | _                              | MΩ        | V <sub>DD</sub> = 5.5 V<br>V <sub>MR</sub> = 5.5 V                                                                                                                   | 13              |

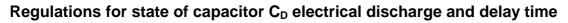

Notes: 1. When capacitor  $C_D$  is completely discharged and charging starts in the state that  $C_D$  pin voltage is 0 V, the minimum value of delay time  $T_{DLY0}$  is 7 ms. However, when the discharging time is short and charging starts in the state that the voltage does not completely fall to 0 V, the minimum value of delay time  $T_{DLY}$  is 1.1 ms. Then, the minimum value of Low time (reset time) of  $\overline{Vo2}$  is 1.1 ms as the delay time  $T_{DLY}$ . Refer to Regulations for state of capacitor  $C_D$  electrical discharge and delay time on page 9 for details.

2. Refer to the characteristic curves on page 5 for temperature dependence of the main characteristics.

3. Refer to pages 7 and 8 for the test circuits.

#### **Characteristic curves**

# **Pin Descriptions**

| Pin No. | Pin Name | Function                                                                                                                                                                                                                                                                                |

|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |          | Manual reset input pin for reset circuit 2 (the circuit with the delay function).                                                                                                                                                                                                       |

| 1 MR    |          | The MR signal is active high, so applying a high level to MR sets the Vo2 pin to the low level.                                                                                                                                                                                         |

|         | MR       | If $Vi2 > V_{REF}$ when the signal on the MR pin is changed back from the high to the low level, the Vo2 pin is                                                                                                                                                                         |

|         | IVIIX    | returned from the low to the high level after a delay time $T_{DLY0}$ . This can be set as required. The MR pin is                                                                                                                                                                      |

|         |          | pulled down to the GND level via an internal 2-M $\Omega$ resistor . However, we recommend connection of the pin to                                                                                                                                                                     |

|         |          | the GND line when it is not in use.                                                                                                                                                                                                                                                     |

|         |          | Reset signal output pin for reset circuit 1 (the circuit with no delay function). The output is open-drain.                                                                                                                                                                             |

|         |          | The recommended value of the pull-up resistor ( $R_{L1}$ ) is 3 k to 100 k $\Omega$ . When the voltage input on pin Vi1 falls                                                                                                                                                           |

| 2       | Vo1      | to or below $V_{REF}$ , the signal output from the Vo1 pin is changed from the high to the low level. Since the                                                                                                                                                                         |

|         |          | characteristic includes hysteresis, the signal output from the Vo1 pin changes from the low to the high level                                                                                                                                                                           |

|         |          | when the voltage input on pin Vi1 rises to or above $V_{REF}+V_{HYS}$ . Refer to the timing diagram on page 3 for details.                                                                                                                                                              |

|         |          | Reset signal output pin for reset circuit 2 (the circuit with the delay function). The output is open-drain.                                                                                                                                                                            |

|         |          | The recommended value for the pull-up resistor ( $R_{L2}$ ) is 3 k to 100 k $\Omega$ . When the voltage input on pin Vi2 falls                                                                                                                                                          |

|         |          | to or below $V_{REF}$ , the signal output from the $\overline{Vo2}$ pin is changed from the high to the low level. Since the input                                                                                                                                                      |

| 3       | Vo2      | characteristic includes hysteresis, the signal output from the $\overline{Vo2}$ pin changes from the low to the high level                                                                                                                                                              |

| _       | -        | when the voltage input on pin Vi2 rises to or above $V_{REF}+V_{HYS}$ and the set delay time $T_{DLY0}$ has elapsed. Refer                                                                                                                                                              |

|         |          | to the timing diagram on page 3 and regulations for state of capacitor $C_D$ electrical discharge and delay time on                                                                                                                                                                     |

|         |          | page 9 for details.                                                                                                                                                                                                                                                                     |

| 4       | GND      | GND pin                                                                                                                                                                                                                                                                                 |

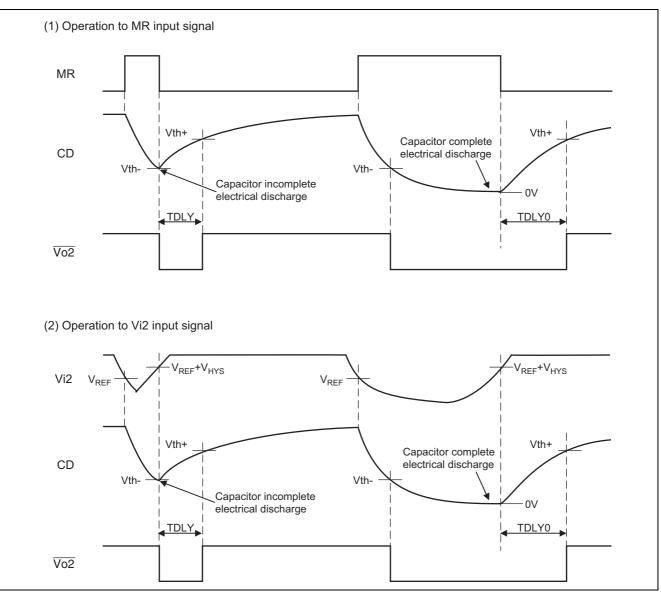

|         |          | Pin for connection to the resistor ( $R_D$ ) and capacitor ( $C_D$ ) for setting of the delay time, $T_{DLY0}$ . Refer to the Block                                                                                                                                                     |

|         |          | Diagram and Typical Application Circuit on page 2 for an example of the connection. The relation by which the                                                                                                                                                                           |

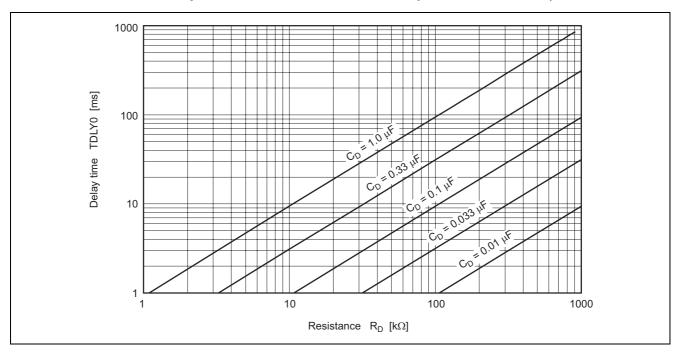

| _       |          | resistance and capacitance set up the delay time can be expressed as $T_{DLY0} = 0.94 \times C_D \times R_D$ . Refer to this                                                                                                                                                            |

| 5       | CD       | formula in determining the values of resistance and capacitance. Resistance $R_D$ must use the one within the                                                                                                                                                                           |

|         |          | range of 1 k to 1 M $\Omega$ . Ensure that capacitor C <sub>D</sub> has a value no greater than 1.3 $\mu$ F. The dependence of delay time T <sub>DLY0</sub> on the values of external capacitor C <sub>D</sub> and external resistor R <sub>D</sub> is illustrated on page 10. To avoid |

|         |          | errors due to noise input via the CD pin, this input includes a Schmitt-trigger inverter.                                                                                                                                                                                               |

|         |          | Voltage input pin for reset circuit 2 (the circuit with the delay function). When the input voltage falls to or below                                                                                                                                                                   |

|         |          | $V_{REF}$ , the signal output from the $\overline{Vo2}$ pin is changed to the low level. Since the input characteristic includes                                                                                                                                                        |

|         |          | hysteresis, the signal output from the Vo2 pin is changed from the low to the high level after the voltage input                                                                                                                                                                        |

|         |          | on pin Vi2 has risen to or above $V_{REF}+V_{HYS}$ and delay time $T_{DLY}$ has elapsed. The reset-threshold voltage is                                                                                                                                                                 |

| 6       | Vi2      | derived from the power-supply voltage $V_{\text{DD2}}$ according to the division ratio set up by resistors $R_{\text{S3}}$ and $R_{\text{S4}}$ as                                                                                                                                       |

| Ű       | VIZ      | described under the block diagram and typical application circuit on page 2. To avoid shifting of the reset                                                                                                                                                                             |

|         |          | detection voltage being shifted by input current via the Vi2 pin, select a value no greater than 25 k $\Omega$ for parallel                                                                                                                                                             |

|         |          | resistors $R_{s3}$ and $R_{s4}$ . Refer to the graph on page 2 for details. Besides, to avoid errors due to noise in                                                                                                                                                                    |

|         |          | power-supply voltage $V_{DD2}$ , select a capacitor with superior frequency characteristics and connect it between the Vi2 and GND pins.                                                                                                                                                |

| 7 Vi1   |          | Voltage input pin for reset circuit 1 (the circuit without the delay function). When the input voltage falls to or                                                                                                                                                                      |

|         | Vi1      | below $V_{REF}$ , the signal output from the Vo1 pin is changed to the low level. Since the input characteristic                                                                                                                                                                        |

|         |          | includes hysteresis, the signal output from the Vo1 pin is changed from the low to the high level after the                                                                                                                                                                             |

|         |          | voltage input on pin Vi1 has risen to or above $V_{REF}$ + $V_{HYS}$ . The reset-threshold voltage is derived from the                                                                                                                                                                  |

|         |          | power-supply voltage $V_{DD1}$ according to the division ratio set up by resistors $R_{S1}$ and $R_{S2}$ as described under the                                                                                                                                                         |

|         |          | block diagram and typical application circuit on page 2. To avoid shifting of the reset detection voltage being                                                                                                                                                                         |

|         |          | shifted by input current via the Vi1 pin, select a value no greater than 25 k $\Omega$ for parallel resistors R <sub>S1</sub> and R <sub>S2</sub> .                                                                                                                                     |

|         |          | Refer to the graph on page 2 for details. Besides, to avoid errors due to noise in power-supply voltage $V_{DD1}$ ,                                                                                                                                                                     |

|         |          | select a capacitor with superior frequency characteristics and connect it between the Vi2 and GND pins.                                                                                                                                                                                 |

| 8       | VDD      | Power-supply pin for the chip. For stable operation, select a capacitor with superior frequency characteristics                                                                                                                                                                         |

|         |          | and connect it between the VDD and GND pins and as close to the chip as possible. When selecting the value of the capacitor, consider aspects of the system environment such as the quality of the power supply. Refer to                                                               |

|         |          | of the capacitor, consider aspects of the system environment such as the quality of the power supply. Refer to the block diagram and typical application circuit on page 2 for details.                                                                                                 |

|         | 1        | and block diagram and typical application or page 2 for details.                                                                                                                                                                                                                        |

### **Test Circuits**

## Test Circuits (cont.)

# Relation between Delay Time $T_{\text{DLY}}$ and External Component Values $C_{\text{D},}\,R_{\text{D}}$

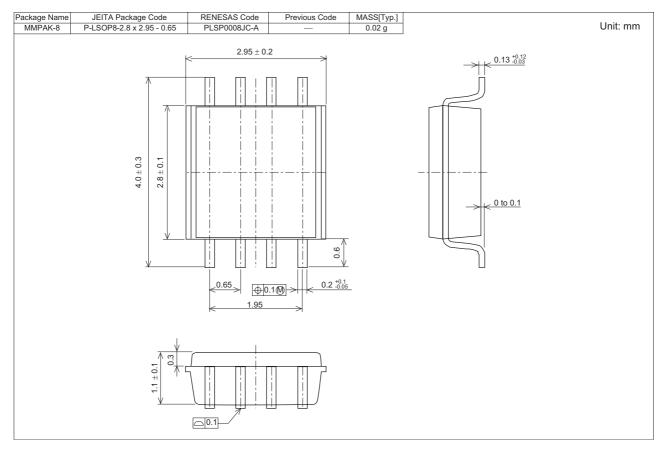

### **Package Dimensions**

#### RenesasTechnology Corp. sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

- Benesas lechnology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Pines

This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information in this document.

But not infinited to, product data. diagrams, charts, programs, algorithms, and application scule as the development of weapons of mass and regulations, and proceedures required by such laws and regulation.

All information in the purpose of any other military use. When exporting the products or the technology described herein, you should follow the applicable export control laws and regulations, and proceedures required by such laws and regulations.

All information included in this document, such as product data, diagrams, charts, programs, algorithms, and application oracit useraphes, is current as of the date this document, but has product data, diagrams, charts, programs, algorithms, and application is activated in this document, but has product data, diagrams, charts, programs, algorithms, and application is a the development of the date this document, but here applicable export control laws and regulations.

Renesas has used reasonable care in compiling the information in this document, but Renesas assumes no liability whatsoever for any damages incurred as a disclosed by Renesas study and product specified by Renesas and the study application specific by and application specific by and application in the date this document, and the date the information in this document, but Renesas as and the applicability of the total system before deciding about the applicability of the suspect of the study applications, and process as and the date this document.

When using or otherwise in systems the failute on mation included in this document, but Renesas

#### **RENESAS SALES OFFICES**

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

#### Renesas Technology America, Inc.

450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K. Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd. Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7898

Renesas Technology Hong Kong Ltd. 7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2730-6071

Renesas Technology Taiwan Co., Ltd. 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999

#### Renesas Technology Singapore Pte. Ltd.

1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jalan Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510

http://www.renesas.com