# **KH560**

# Wideband, Low Distortion Driver Amplifier

## **Features**

- 120MHz bandwidth at +24dBm output

- Low distortion (2nd/3rd: -60/-62dBc @ 20MHz and 10dBm)

- Output short circuit protection

- User-definable output impedance, gain, and compensation

- Internal current limiting

- Direct replacement for CLC560

# **Applications**

- Output amplification

- Arbitrary waveform generation

- ATE systems

- Cable/line driving

- Function generators

- SAW drivers

- Flash A/D driving and testing

## **Typical Distortion Performance**

| Output<br>Power | 20N<br>2nd | ЛНz<br>3rd | 50MHz<br>2nd 3rd |     | 100l<br>2nd | MHz<br>3rd |

|-----------------|------------|------------|------------------|-----|-------------|------------|

| 10dBm           | -60        | -62        | -50              | -54 | -54         | -44        |

| 18dBm           | -51        | -48        | -40              | -40 | -36         | -29        |

| 24dBm           | -46        | -38        | -33              | -25 |             |            |

# **General Description**

The KH560 is a wideband DC coupled, amplifier that combines high output drive and low distortion. At an output of +24dBm ( $10V_{pp}$  into  $50\Omega$ ), the -3dB bandwidth is 120MHz. As illustrated in the table below, distortion performance remains excellent even when amplifying high-frequency signals to high output power levels.

With the output current internally limited to 250mA, the KH560 is fully protected against shorts to ground and can, with the addition of a series limiting resistor at the output, withstand shorts to the ±15V supplies.

The KH560 has been designed for maximum flexibility in a wide variety of demanding applications. The two resistors comprising the feedback network set both the gain and the output impedance, without requiring the series backmatch resistor needed by most op amps. This allows driving into a matched load without dropping half the voltage swing through a series matching resistor. External compensation allows user adjustment of the frequency response. The KH560 is specified for both maximally flat frequency response and 0% pulse overshoot compensations.

The combination of wide bandwidth, high output power, and low distortion, coupled with gain, output impedance and frequency response flexibility, makes the KH560 ideal for waveform generator applications. Excellent stability driving capacitive loads yields superior performance driving ADC's, long transmission lines, and SAW devices. A companion part, the KH561, offers higher full power bandwidth for broadband sinusoidal applications.

The KH560 is constructed using thin film resistor/bipolar transistor technology, and is available in the following versions:

| KH560AI | -25°C to +85°C  | 24-pin Ceramic DIP                                                                             |

|---------|-----------------|------------------------------------------------------------------------------------------------|

| KH560AK | -55°C to +125°C | 24-pin Ceramic DIP,<br>features burn-in<br>and hermetic testing                                |

| KH560AM | -55°C to +125°C | 24-pin Ceramic DIP,<br>environmentally screened<br>and electronically tested<br>to MIL-STD-883 |

# KH560 Electrical Characteristics (A<sub>v</sub> = +10V, V<sub>CC</sub> = $\pm$ 15V, R<sub>L</sub> = $50\Omega$ , R<sub>f</sub> = $410\Omega$ , R<sub>g</sub> = $40\Omega$ , R<sub>o</sub> = $50\Omega$ ; unless specified)

# NOTES TO THE ELECTRICAL SPECIFICATIONS

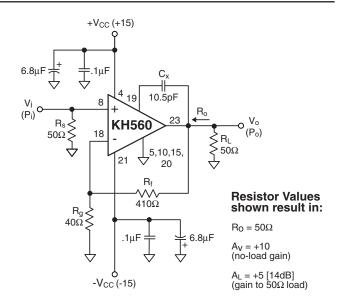

The electrical characteristics shown here apply to the specific test conditions shown above (see also Figure 1 in description of the operation). The KH560 provides an equivalent, non-zero, output impedance determined by the external resistors. The signal gain to the load is therefore load dependent. **The signal gain shown above** ( $A_v = +10$ ) is the no load gain. The actual gain to the matching  $50\Omega$  load used in these specifications is half of this (+5).

The KH560 requires an external compensation capacitor. Unless otherwise noted, this has been set to 10.5pF for the frequency domain specifications (yielding a maximally flat frequency response) and 12.5pF for the time domain specifications (yielding a 0% small signal pulse overshoot response).

| PARAMETERS CONDITIONS                                                             |                                                            | TYP        | MIN & MAX RATINGS |              |              | UNITS      | SYM            |

|-----------------------------------------------------------------------------------|------------------------------------------------------------|------------|-------------------|--------------|--------------|------------|----------------|

| Case Temperature                                                                  | KH560AI                                                    | +25°C      | -25°C             | +25°C        | +85°C        |            |                |

| Case Temperature                                                                  | KH560AK/AM                                                 | +25°C      | -55°C             | +25°C        | +125°C       |            |                |

| FREQUENCY DOMAIN RESPONSE                                                         | (Max. Flat Compensation)                                   |            |                   |              |              |            |                |

| + -3dB bandwidth                                                                  | V 0V (40 ID )                                              | 045        | 475               | 405          | 475          |            | 000            |

| <ul><li>+ maximally flat compensation</li><li>0% overshoot compensation</li></ul> | $V_0 < 2V_{pp} (+10dBm)$                                   | 215<br>210 | >175<br>>170      | >185<br>>180 | >175<br>>170 | MHz<br>MHz | SSBW           |

| large signal bandwidth                                                            | $V_0 < 2V_{pp}^{FP} (+10dBm)$<br>$V_0 < 10V_{pp} (+24dBm)$ | 120        | >170              | >100         | >170         | MHz        | FPBW           |

| (see Frequency Response vs. (                                                     | Output Power plot)                                         | 120        | /110              | 7100         | /500         | 1411.12    | ' ' ' ' '      |

| gain flatness                                                                     | $V_o < 2V_{pp} (+10dBm)$                                   |            |                   |              |              |            |                |

| t peaking                                                                         | 0.1 -50MHz                                                 | 0          | <0.50             | <0.40        | < 0.50       | dB         | GFPL           |

| t peaking                                                                         | >50MHz                                                     | 0          | <1.25             | <0.75        | <1.00        | dB         | GFPH           |

| + rolloff                                                                         | at 100MHz                                                  | 0.1        | <1.00             | <0.75        | <1.00        | dB         | GFR            |

| group delay                                                                       | to 100MHz                                                  | 3.1        | l                 |              |              | ns<br>°    | GD             |

| linear phase deviation                                                            | to 100MHz                                                  | 0.6        | <1.7              | <1.2         | <2.7         |            | LPD            |

| return loss (see discussion of Rx)                                                | to 100MHz                                                  | -15        | <-12              | <-12         | <-12         | dB         | RL             |

| <b>DISTORTION</b> (Max. Flat Compensation                                         | on)                                                        |            |                   |              |              |            |                |

| 2nd harmonic distortion                                                           |                                                            |            |                   |              |              |            |                |

| + 24dBm (10V <sub>pp</sub> ):                                                     | 20MHz                                                      | -46        | <-36              | <-36         | <-33         | dBc        | HD2HL          |

| †                                                                                 | 50MHz                                                      | -33        | <-27              | <-27         | <-27         | dBc        | HD2HM          |

| † 18dBm (5V <sub>pp</sub> ):                                                      | 20MHz                                                      | -51        | <-44              | <-44         | <-42         | dBc        | HD2ML          |

| †                                                                                 | 50MHz<br>100MHz                                            | -40<br>-36 | <-35<br><-25      | <-35<br><-28 | <-30<br><-26 | dBc<br>dBc | HD2MM<br>HD2MH |

| † 10dBm (2V <sub>pp</sub> ):                                                      | 20MHz                                                      | -60        | <- <u>2</u> 5     | <-54         | <-50         | dBc        | HD2LL          |

| † 100Biii (2 v pp).                                                               | 50MHz                                                      | -50        | <-43              | <-43         | <-40         | dBc        | HD2LM          |

| •                                                                                 | 100MHz                                                     | -54        | <-32              | <-32         | <-32         | dBc        | HD2LH          |

| 3rd harmonic distortion                                                           |                                                            |            |                   |              |              |            |                |

| t 24dBm (10V <sub>pp</sub> ):                                                     | 20MHz                                                      | -38        | <-32              | <-32         | <-25         | dBc        | HD3HL          |

| t                                                                                 | 50MHz                                                      | -25        | <-21              | <-21         | <-20         | dBc        | HD3HM          |

| + 18dBm (5V <sub>pp</sub> ):                                                      | 20MHz                                                      | -48        | <-42              | <-45         | <-42         | dBc        | HD3ML          |

| t                                                                                 | 50MHz                                                      | -40        | <-36              | <-36         | <-30         | dBc        | HD3MM          |

|                                                                                   | 100MHz                                                     | -29        | <-25              | <-25         | <-25         | dBc        | НДЗМН          |

| t 10dBm (2V <sub>pp</sub> ):                                                      | 20MHz                                                      | -62        | <-58              | <-58         | <-57         | dBc        | HD3LL          |

| † 10dBm (2V <sub>pp</sub> ):<br>†                                                 | 50MHz                                                      | -62<br>-54 | <-50<br><-50      | <-50<br><-50 | <-37<br><-48 | dBc        | HD3LL          |

| •                                                                                 | 100MHz                                                     | -44        | <-40              | <-40         | <-36         | dBc        | HD3LH          |

| 2-tone 3rd order                                                                  |                                                            |            |                   |              |              |            |                |

| intermod intercept <sup>2</sup>                                                   | 20MHz                                                      | 40         | >38               | >38          | >38          | dBm        | IM3L           |

| •                                                                                 | 50MHz                                                      | 35         | >32               | >32          | >32          | dBm        | IM3M           |

|                                                                                   | 100MHZ                                                     | 25         | >23               | >23          | >20          | dBm        | IM3H           |

Min/max ratings are based on product characterization and simulation. Individual parameters are tested as noted. Outgoing quality levels are determined from tested parameters.

# KH560 Electrical Characteristics (A<sub>V</sub> = +10V, V<sub>CC</sub> = $\pm$ 15V, R<sub>L</sub> = $50\Omega$ , R<sub>f</sub> = $410\Omega$ , R<sub>g</sub> = $40\Omega$ , R<sub>o</sub> = $50\Omega$ ; unless specified)

| PARAMETERS                                                                                                                                                                                                                                                                                                      | CONDITIONS                                                            | TYP                                                         | MIN & MAX RATINGS                                          |                                                 | UNITS                                                      | SYM                                                   |                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------|

| Case Temperature                                                                                                                                                                                                                                                                                                | KH560AI                                                               | +25°C                                                       | -25°C                                                      | +25°C                                           | +85°C                                                      |                                                       |                                                          |

| Case Temperature                                                                                                                                                                                                                                                                                                | KH560AK/AM                                                            | +25°C                                                       | -55°C                                                      | +25°C                                           | +125°C                                                     |                                                       |                                                          |

| TIME DOMAIN RESPONSE (0% Overs                                                                                                                                                                                                                                                                                  | hoot Compensation)                                                    |                                                             |                                                            |                                                 |                                                            |                                                       |                                                          |

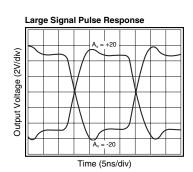

| rise and fall time 2V step 10V step settling time to 0.1% (time <1μs) long term thermal tail (time >1μs) slew rate overshoot                                                                                                                                                                                    | 5V step<br>5V step<br>10V <sub>pp</sub> , 175MHz<br>2V step           | 1.6<br>3.6<br>10<br>0.4<br>2600                             | <2.0<br><3.8<br><15<br><0.5<br>>2300                       | <1.9<br><4.5<br><15<br><0.5<br>>2000            | <2.0<br><5.3<br><25<br><0.5<br>>1800                       | ns<br>ns<br>ns<br>%<br>V/µs                           | TRS<br>TRL<br>TS<br>SE<br>SR                             |

| maximally flat compensation 0% overshoot compensation                                                                                                                                                                                                                                                           | ·                                                                     | 5<br>0                                                      | <13<br><5                                                  | <10<br><3                                       | <13<br><5                                                  | %<br>%                                                | OSMF<br>OSZO                                             |

| voltage inverting current non-inverting current noise floor <sup>3</sup> integrated noise <sup>3</sup> noise figure                                                                                                                                                                                             | >100KHz<br>>100KHz<br>>100KHz<br>>100KHz<br>1kHz to 200MHz<br>>100KHz | 2.1<br>34<br>2.8<br>-159<br>35<br>15                        | <2.5<br><40<br><4.5<br><-157<br><45<br><17                 | <2.5<br><40<br><4.5<br><-157<br><45<br><17      | <2.5<br><45<br><5.0<br><-157<br><45<br><17                 | nV/√Hz<br>pA/√Hz<br>pA/√Hz<br>dBm/(1Hz)<br>μV<br>dB   | VN<br>ICN<br>NCN<br>SNF<br>INV<br>NF                     |

| * input offset voltage     average temperature coefficient  * non-inverting bias current     average temperature coefficient  * inverting bias current     average temperature coefficient  * inverting bias current     average temperature coefficient  * power supply rejection ratio (DC)  * supply current | no load                                                               | 2.0<br>35<br>5.0<br>20<br>10.0<br>100<br>60<br>50           | <14.0<br><100<br><35<br><175<br><50<br><200<br>>58<br><60  | <5.0<br>-<br><20<br>-<br><30<br>-<br>>58<br><60 | <15.0<br><100<br><20<br><100<br><50<br><200<br>>57<br><65  | mV<br>μV/°C<br>μA<br>nA/°C<br>μA<br>nA/°C<br>dB<br>mA | VIO<br>DVIO<br>IBN<br>DIBN<br>IBI<br>DIBI<br>PSRR<br>ICC |

| open loop current gain average temperature coefficient inverting input resistance average temperature coefficient non-inverting input resistance non-inverting input capacitance output voltage range output current limit                                                                                      | (±1% tolerance) (±5% tolerance) to 100MHz 150mA load current          | 10.0<br>+0.02<br>14.0<br>+.02<br>700<br>2.3<br>±10.5<br>210 | -<br><+.03<br>-<br><+.025<br>>200<br><3.0<br>>10.0<br><250 | -<br>-<br>-<br>>400<br><3.0<br>>10.0<br><250    | -<br><+.02<br>-<br><+.025<br>>400<br><3.0<br>>10.0<br><250 | mA/mA<br>%/°C<br>Ω<br>Ω/°C<br>KΩ<br>pF<br>V<br>mA     | G<br>DG<br>RIN<br>DRIN<br>RNI<br>CNI<br>VO<br>OCL        |

Min/max ratings are based on product characterization and simulation. Individual parameters are tested as noted. Outgoing quality levels are determined from tested parameters.

# **Absolute Maximum Ratings**

# $V_{CC}$ (reversed supplies will destroy part) $\pm 20V$ differential input voltage $\pm 3V$ common mode input voltage $\pm V_{CC}$ junction temperature (see thermal model) $+175^{\circ}\text{C}$ storage temperature $+175^{\circ}\text{C}$ lead temperature (soldering 10s) $+300^{\circ}\text{C}$ output current (internally limited) +250mA

# **Recommended Operating Conditions**

| Recommended operating con         | iditions                  |

|-----------------------------------|---------------------------|

| $V_{CC}$                          | ±10V to ±15V              |

| Io                                | ≤ ±200mA                  |

| common mode input voltage         | $< \pm ( V_{CC}  - 6)V$   |

| output impedance                  | $25\Omega$ to $200\Omega$ |

| gain range (no-load voltage gain) | +5 to +80                 |

| case temperature: Al              | -25°C to +85°C            |

| AK/AM                             | -55°C to +125°C           |

# **Notes**

1) \* AI/AK/AM 100% tested at +25°C

† AK/AM 100% tested at at +25°C and sample tested at -55°C and +125°C

† Al sample tested at +25°C

2) Test Tones are set ±100kHz of indicated frequency.

3) Noise tests are perfored from 5MHz to 200MHz.

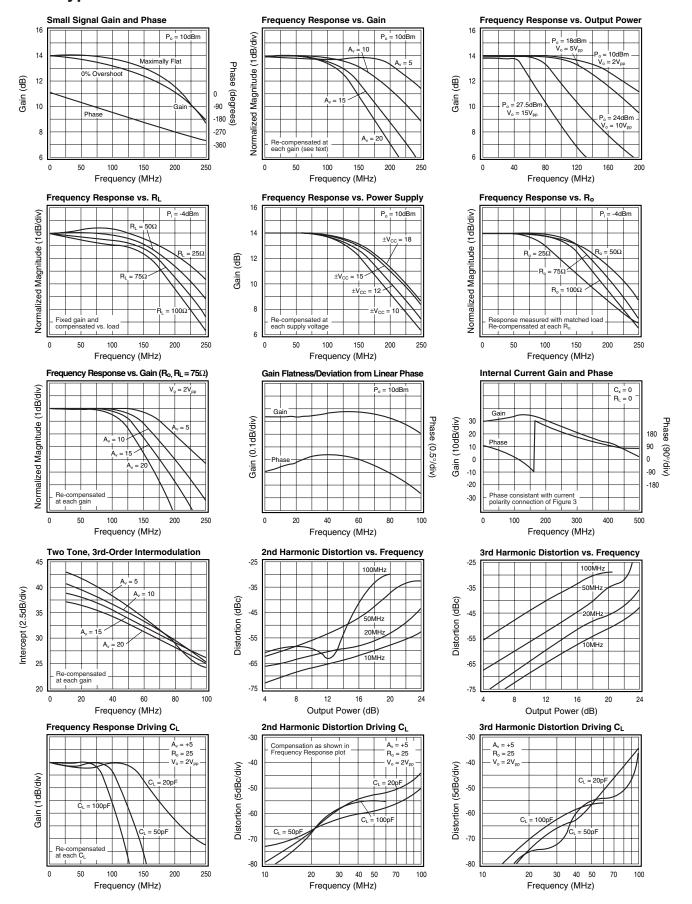

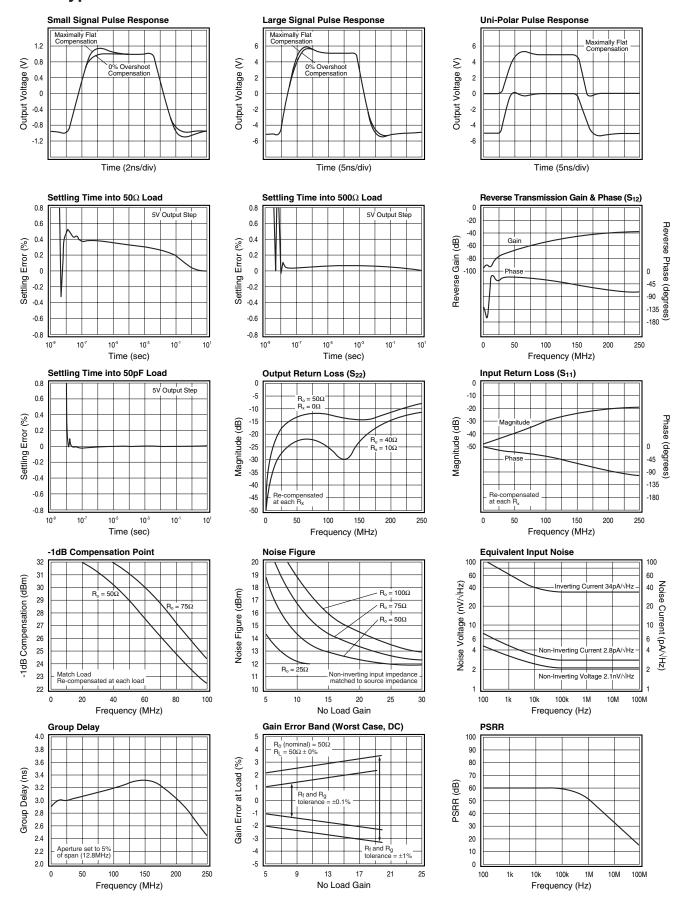

# KH560 Typical Performance Characteristics (T<sub>A</sub> = +25°C, Circuit in Figure 1; unless specified)

# KH560 Typical Performance Characteristics (T<sub>A</sub> = +25°C, Circuit in Figure 1; unless specified)

REV. 1A February 2001 5

#### SUMMARY DESIGN EQUATIONS AND DEFINITIONS

$$R_f = (G+1)R_0 - A_vR_i$$

R<sub>f</sub> – Feedback resistor from output to inverting input

$$R_g = \frac{R_f - R_o}{A_v - 1}$$

R<sub>g</sub> – Gain setting resistor from inverting input to ground

$$C_{x} = \frac{1}{\frac{R_{o}}{300\left(1 - \frac{2}{R_{g}}\right)} - 0.08}$$

C<sub>x</sub> – External compensation capacitor from output to pin 19 (in pF)

#### Where:

R<sub>o</sub> - Desired equivalent output impedance

A<sub>v</sub> – Non-inverting input to output voltage gain with no load

G – Internal current gain from inverting input to output = 10 ±1%

$R_i$  – Internal inverting input impedance = 14 $\Omega$  ±%5

R<sub>s</sub> - Non-inverting input termination resistor

R<sub>I</sub> - Load resistor

A<sub>L</sub> – Voltage gain from non-inverting input to load resistor

# KH560 Description of Operation

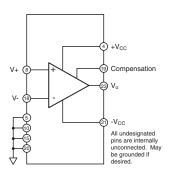

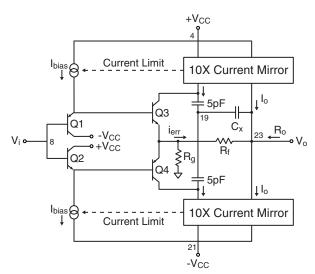

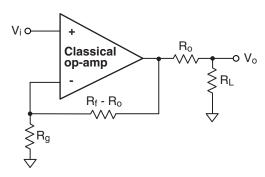

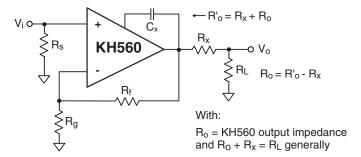

Looking at the circuit of Figure 1 (the topology and resistor values used in setting the data sheet specifications), the KH560 appears to bear a strong external resemblance to a classical op amp. As shown in the simplified block diagram of Figure 2, however, it differs in several key areas. Principally, the error signal is a current into the inverting input (current feedback) and the forward gain from this current to the output is relatively low, but very well controlled, current gain. The KH560 has been intentionally designed to have a low internal gain and a current mode output in order that an equivalent output impedance can be achieved without the series matching resistor more commonly required of low output impedance op amps. Many of the benefits of a high loop gain have, however, been retained through a very careful control of the KH560's internal characteristics.

The feedback and gain setting resistors determine both the output impedance and the gain.  $R_f$  predominately sets the output impedance  $(R_o),$  while  $R_g$  predominately determines the no load gain  $(A_v).$  solving for the required  $R_f$  and  $R_g,$  given a desired  $R_o$  and  $A_v,$  yields the design equations shown below. Conversely, given an  $R_f$  and  $R_g,$  the performance equations show that both  $R_f$  and  $R_g$  play a part in setting  $R_o$  and  $A_v.$  Independent  $R_o$  and  $A_v$  adjustment would be possible if the inverting input impedance  $(R_i)$  were 0 but, with  $R_i=14\Omega$  as shown in the specification listing, independent gain and output impedance setting is not directly possible.

Figure 1: Test Circuit

# **Design Equations**

$$R_f = (G+1)R_o - A_vR_i$$

$$R_g = \frac{R_f - R_o}{A_v - 1}$$

# **Performance Equations**

$$R_{o} = \frac{R_{f} + R_{i} \left(1 + \frac{R_{f}}{R_{g}}\right)}{G + 1 + \frac{R_{i}}{R_{g}}}$$

Where:

G ≡ forward current gain (=10)

$R_i = inverting node input resistance (=14<math>\Omega$ )

$R_0 = desired output$ impedance  $A_V = desired non-$

A<sub>v</sub> = desired noninverting voltage gain with no load

$$A_v = 1 + \frac{R_f}{R_g} \left[ \frac{G - \frac{R_i}{R_f}}{G + 1 + \frac{R_i}{R_\alpha}} \right]$$

## **Simplified Circuit Description**

Looking at the KH560's simplified schematic in Figure 2, the amplifier's operation may be described. Going from the non-inverting input at pin 8 to the inverting input at pin 18, transistors Q1 – Q4 act as an open loop unity gain buffer forcing the inverting node voltage to follow the non-inverting voltage input.

Transistors Q3 and Q4 also act as a low impedance ( $14\Omega$  looking into pin 18) path for the feedback error current. This current, ( $i_{err}$ ), flows through those transistors into a very well defined current mirror having a gain of 10 from this error current to the output. The current mirror outputs act as the amplifier output.

The input stage bias currents are supply voltage independent. Since these set the bias level for the whole

6

part, relatively constant performance over supply voltage is achieved. A current sense in the error current leg of the 10X current mirror feeds back to the bias current setup providing a current shutdown feature when the output current approaches 250mA.

Figure 2: Simplified Circuit Diagram

## **Developing the Performance Equations**

The KH560 is intended to provide both a controllable voltage gain from input to output as well as a controllable output impedance. It is best to treat these two operations separately with no load in place. Then, with the no-load gain and output impedance determined, the gain to the load will simply be the no-load gain attenuated by the voltage divider formed by the load and the equivalent output impedance.

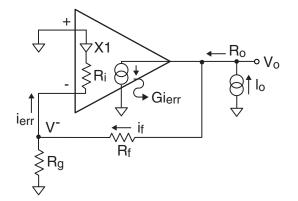

Figure 3 steps through the output impedance development using an equivalent model of Figure 2. Offering an equivalent, non-zero, output impedance into a matched load allows the KH560 to operate at lower internal voltage swings for a given desired swing at the load. This allows higher voltage swings to be delivered at the load for a given power supply voltage at lower distortion levels than an equivalent op amp needing to generate twice the voltage swing actually desired at the matched load. This improved distortion is specified and tested over a wide range as shown in the specification listing.

Get both  $V_0$  and  $I_0$  into terms of just the error current,  $i_{err}$ , using:

$$\begin{split} &V^-\!=i_{err}\;R_i\;\text{and}\\ &i_f=i_{err}+\frac{V^-}{R_g}=i_{err}\left(1\!+\!\frac{R_i}{R_g}\right)\\ &V_o=V^-\!+i_f\,R_f=i_{err}\left[R_i\!+\!R_f\left(1\!+\!\frac{R_i}{R_g}\right)\right]\\ &V_o=i_{err}\!\left[R_f\!+\!R_i\left(1\!+\!\frac{R_f}{R_g}\right)\right]\\ &\text{and}\\ &I_o=Gi_{err}+i_f=i_{err}\left[G\!+\!1\!+\!\frac{R_i}{R_g}\right]\\ &\text{then}\\ &R_o\equiv\frac{V_o}{I_o}=\frac{R_f\!+\!R_i\left(1\!+\!\frac{R_f}{R_g}\right)}{G\!+\!1\!+\!\frac{R_i}{R_g}}\\ &\text{note that}\;R_o\left|=\frac{R_f}{G\!+\!1}\end{split}$$

Figure 3: Output Impedance Derivation

Note that the  $R_o$  expression simplifies considerably if  $R_i = 0$ . Also note that if the forward current gain were to go to infinity, the output impedance would go to 0. This would be the normal op amp topology with a very high internal gain. The KH560 achieves a non-zero  $R_o$  by setting the internal forward gain to be a low, well controlled, value.

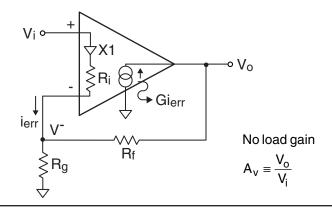

## **Developing the No-Load Gain Expression**

Taking the output impedance expression as one constraint setting the external resistor values, we now need to develop the no-load voltage gain expression from the non-inverting input to the output as the other constraint. Figure 4 shows the derivation of the no load gain.

recognize that [taking V<sub>i</sub> positive]

$$V_o = V^- + Gi_{err} R_f$$

solving for V<sup>-</sup> from two directions

$$V^{-} = V_{i} - i_{err} R_{i} = (G + 1) i_{err} R_{g}$$

solving for ierr from this

$$i_{err} = \frac{V_i}{\left(G+1\right)R_g + R_i}$$

$$V^{-} = V_{i} - \frac{V_{i} R_{i}}{(G+1) R_{q} + R_{i}}$$

and, substituting for V<sup>-</sup>and i<sub>err</sub> in the original V<sub>o</sub> expression

$$V_{o} = V_{i} \left[ 1 + \frac{GR_{f} - R_{i}}{(G+1)R_{g} + R_{i}} \right]$$

pulling an  $\frac{R_f}{R_g}$  out of the fraction

$$A_{v} \equiv \frac{V_{o}}{V_{i}} = 1 + \frac{R_{f}}{R_{g}} \left[ \frac{G - \frac{R_{i}}{R_{f}}}{G + 1 + \frac{R_{i}}{R_{g}}} \right]$$

note that

$$A_v = 1 + \frac{R_f}{R_g} \left( \frac{G}{G+1} \right)$$

$R_i = 0$

Figure 4: Voltage Gain Derivation

Note again that if  $R_i = 0$  this expression would simplify considerably. Also, if G were very large the voltage gain expression would reduce to the familiar non-inverting op amp gain equation. These two performance equations, shown below, provide a means to derive the design equations for R<sub>f</sub> and R<sub>q</sub> given a desired no load gain and output impedance.

#### **Performance Equations**

$$R_{o} = \frac{R_{f} + R_{i} \left(1 + \frac{R_{f}}{R_{g}}\right)}{G + 1 + \frac{R_{i}}{R_{o}}} \qquad \qquad R_{f} = (G + 1) R_{o} - A_{v} R_{i}$$

$$R_{g} = \frac{R_{f} - R_{o}}{A_{v} - 1}$$

$$A_{v} = 1 + \frac{R_{f}}{R_{g}} \left[ \frac{G - \frac{R_{i}}{R_{f}}}{G + 1 + \frac{R_{i}}{R_{g}}} \right]$$

#### **Design Equations**

$$R_f = (G+1)R_o - A_v R$$

$$R_g = \frac{R_f - R_o}{A_v - 1}$$

# **Equivalent Model**

Given that the physical feedback and gain setting resistors have been determined in accordance with the design equations shown above, an equivalent model may be created for the gain to the load where the amplifier block is taken as a standard op amp. Figure 5 shows this analysis model and the resulting gain equation to the load.

$$\frac{V_o}{V_i} = \left(1 + \frac{R_f - R_o}{R_g}\right) \frac{R_L}{R_L + R_o}$$

substituting in for  $R_f$  and  $R_q$  with their design equation yields

$$\frac{V_o}{V_i} = A_v \frac{R_L}{R_L + R_o} = A_L \text{ (gain to load)}$$

Figure 5: Equivalent Model

This model is used to generate the DC error and noise performance equations. As with any equivalent model, the primary intent is to match the external terminal characteristics recognizing that the model distorts the internal currents and voltages. In this case, the model would incorrectly predict the output pin voltage swing for a given swing at the load. But it does provide a simplified means of getting to the external terminal characteristics.

## External Compensation Capacitor (C<sub>x</sub>)

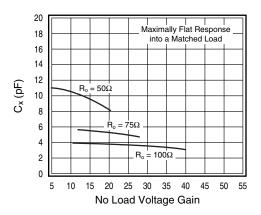

As shown in the test circuit of Figure 1, the KH560 requires an external compensation capacitor from the output to pin 19. The recommended values described here assume that a maximally flat frequency response into a matched load is desired. The required  $C_{\chi}$  varies widely with the desired value of output impedance and to a lesser degree on the desired gain. Note from Figure 2, the simplified internal schematic, that the actual total compensation (Ct) is the series combination of Cx and the internal 10pF from pin 19 to the compensation nodes. The total compensation (C<sub>t</sub>) is developed in two steps as shown below.

$$C_1 = \frac{300}{R_o} \left( 1 - \frac{2.0}{R_g} \right) \text{ pF intermediate equation}$$

$$C_t = \frac{C_1}{1 + (0.02) C_1} \text{ pF total compensation}$$

With this total value derived, the required external  $C_x$  is developed by backing out the effect of the internal 10pF. This, and an expression for the external  $C_x$  without the intermediate steps are shown below.

$$C_{x} = \frac{10 C_{t}}{10 - C_{t}}$$

or

$$C_{x} = \frac{1}{\frac{R_{o}}{300 \left(1 - \frac{2}{R_{g}}\right)} - 0.08} pF$$

The plot in Figure 6 shows the required  $C_x$  vs. gain for several desired output impedances using the equations shown above. Note that for lower  $R_o$ 's,  $C_x$  can get very large. But, since the total compensation is actually the series combination of  $C_x$  and 10pF, going to very high  $C_x$ 's is increasingly ineffective as the total compensation is only slightly changed. This, in part, sets the lower limits on allowable  $R_o$ .

Figure 6: External Compensation Capacitance (C<sub>x</sub>)

A 0% small signal overshoot response can be achieved by increasing  $C_{\rm x}$  slightly from the maximally flat value. Note that this applies only for small signals due to slew rate effects coming into play for large, fast edge rates.

Beyond the nominal compensation values developed thus far, this external  $C_x$  provides a very flexible means for tailoring the frequency response under a wide variety of gain and loading conditions. It is oftentimes useful to use a small adjustable cap in development to determine a  $C_x$  suitable to the application, then fixing that value for production. An excellent 5pF to 20pF trimmer cap for this is a Sprague-Goodman part #GKX20000.

When the KH560 is used to drive a capacitive load, such as an ADC or SAW device, the load will act to compensate the response along with  $C_{\rm x}$ . Generally, considerably lower  $C_{\rm x}$  values are required than the earlier development would indicate. This is advantageous in that a low  $R_{\rm o}$  would be desired to drive a capacitive load which,

without the compensating effect of load itself, would otherwise require very large  $C_{\rm x}$  values.

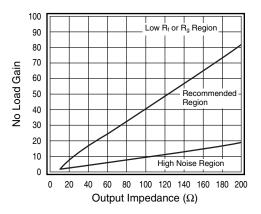

## Gain and Output Impedance Range

Figure 7 shows a plot of the recommended gain and output impedances for the KH560. Operation outside of this region is certainly possible with some degradation in performance. Several factors contribute to set this range. At very low output impedances, the required value of feedback resistor becomes so low as to excessively load the output causing a rapid degradation in distortion. The maximum  $\rm R_{\rm 0}$  was set somewhat arbitrarily at 200 $\rm \Omega$ . This allows the KH560 to drive into a 2:1 step down transformer matching to a 50 $\rm \Omega$  load. (This offers some advantages from a distortion standpoint.)

Figure 7: Recommended Gain and Output Impedance Range

For a given  $R_o$ , the minimum gain shown in Figure 7 has been set to keep the equivalent input noise voltage less than  $4nV/\!\!\sqrt{Hz}$ . Generally, the equivalent input noise voltage decreases with higher signal gains. The high gain limit has been set by targeting a minimum  $R_g$  of  $10\Omega$  or a minimum  $R_f$  of  $100\Omega$ .

# **Amplifier Configurations**

The KH560 is intended for a fixed, non-inverting, gain configuration as shown in Figure 1. The KH561 offers an enhanced slew rate at the expense of higher long-term thermal tail in the pulse response than the KH560. Due to its low internal forward gain, the inverting node does not present a low impedance, or virtual ground, node. Hence, in an inverting configuration, the signals source impedance will see a finite load whose value depends on the output loading. Inverting mode operation can be best achieved using a wideband, unity gain buffer with low output impedance to isolate the source from this varying load. A DC level can, however, be summed into the inverting node to offset the output either for offset correction or signal conditioning.

#### **Accuracy Calculations**

Several factors contribute to limit the achievable KH560 accuracy. These include the DC errors, noise effects, and

9

the impact internal amplifier characteristics have on the signal gain. Both the output DC error and noise model may be developed using the equivalent model of Figure 5. Generally, non-inverting input errors show up at the output with the same gain as the input signal, while the inverting current errors have a gain of simply ( $R_f - R_o$ ) to the output voltage (neglecting the  $R_o$  to  $R_L$  attenuation).

## Output DC Offset:

The DC error terms shown in the specification listing along with the model of Figure 5 may be used to estimate the output DC offset voltage and drift. Each term shown in the specification listing can be of either polarity. While the equations shown below are for output offset voltage, the same equation may be used for the drift with each term replaced by its temperature drift value shown in the specification listing.

$$V_{os} = \left(I_{bn} \cdot R_s \pm V_{io}\right) \cdot \left(1 + \frac{R_f - R_o}{R_g}\right) \pm I_{bi} \left(R_f - R_o\right)$$

where:  $I_{bn} \equiv \text{non-inverting bias current}$   $I_{bi} \equiv \text{inverting bias current}$  $V_{io} \equiv \text{input offset voltage}$

An example calculation for the circuit in Figure 1 using typical 25°C DC error terms and R<sub>S</sub> = 25 $\Omega$ , R<sub>L</sub> = 50 $\Omega$  yields:

$$\begin{array}{c|c} V_{o} &= \left[ \left( 5 \mu A \cdot 25 \Omega \pm 2.0 mV \right) 10 \pm 10 \mu A \left( 360 \Omega \right) \right] \cdots \\ & DC & 1/2 = \pm 12.4 mV \\ & \uparrow \\ & \text{attentuation between } R_{o} \text{ and } R_{L} \end{array}$$

Recall that the source impedance,  $R_{\rm s}$ , includes both the terminating and signal source impedance and that the actual DC level to the load includes the voltage divider between  $R_{\rm o}$  and  $R_{\rm L}$ . Also note that for the KH560, as well as for all current feedback amplifiers, the non-inverting and inverting bias currents do not track each other in either magnitude or polarity. Hence, there is no meaning in an offset current specification, and source impedance matching to cancel bias currents is ineffective.

#### Noise Analysis:

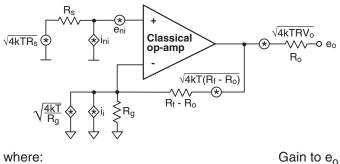

Although the DC error terms are in fact random, the calculation shown above assumes they are all additive in a worst case sense. The effect of all the various noise sources are combined as a root sum of squared terms to get an overall expression for the spot noise voltage. The circuit of Figure 8 shows the equivalent circuit with all the various noise voltages and currents included along with their gains to the output.

Figure 8: Equivalent Noise Model

1

$\sqrt{4kTR_0}$  – output resistor voltage noise

To get an expression for the equivalent output noise voltage, each of these noise voltage and current terms must be taken to the output through their appropriate gains and combined as the root sum of squares.

$$\begin{split} e_o &= \sqrt{\left({e_{ni}}^2 + \left({i_{ni}}R_s\right)^2 + 4kTR_s\right){A_v}^2 + {i_i}^2\left(R_f - R_o\right)^2 \cdots} \\ &\qquad \qquad + \frac{}{4kT\left(R_f - R_o\right)A_v + 4kTR_o} \end{split}$$

Where the  $4kT(R_f - R_o)$   $A_v$  term is the combined noise power of  $R_a$  and  $R_f - R_o$ .

It is often more useful to show the noise as an equivalent input spot noise voltage where every term shown above is reflected to the input. This allows a direct measure of the input signal to noise ratio. This is done by dividing every term inside the radical by the signal voltage gain squared. This, and an example calculation for the circuit of Figure 1, are shown below. Note that  $\rm R_L$  may be neglected in this calculation.

$$\begin{split} e_{n} &= \sqrt{ \, e_{ni}{}^{2} + \left( i_{ni}R_{s} \right)^{2} + 4kTR_{s} + \frac{i_{i}{}^{2} \left( R_{f} - R_{o} \right)^{2}}{A_{v}{}^{2}} + \cdots } \\ & \frac{ \overline{4kT \left( R_{f} - R_{o} \right)} + \frac{4kTR_{o}}{A_{v}{}^{2}} \end{split}$$

For the circuit of Figure 1, the equivalent input noise voltage may be calculated using the data sheet spot noises and R<sub>s</sub> =  $25\Omega$ , R<sub>L</sub> =  $\infty$ . Recall that 4kT = 16E-21J. All terms cast as (nV//Hz)<sup>2</sup>

$$e_n = \sqrt{(2.1)^2 + (.07)^2 + (.632)^2 + (1.22)^2 + (.759)^2 + (.089)^2}$$

= 2.62nV/ $\sqrt{Hz}$

## Gain Accuracy (DC):

A classical op amp's gain accuracy is principally set by the accuracy of the external resistors. The KH560 also depends on the internal characteristics of the forward current gain and inverting input impedance. The performance equations for  $A_{\nu}$  and  $R_{o}$  along with the Thevinin model of Figure 5 are the most direct way of assessing the absolute gain accuracy. Note that internal temperature drifts will decrease the absolute gain slightly as the part warms up. Also note that the parameter tolerances affect both the signal gain and output impedance. The gain tolerance to the load must include both of these effects as well as any variation in the load. The impact of each parameter shown in the performance equations on the gain to the load  $(A_{\rm I})$  is shown below.

Increasing current gain G Increasing inverting input  $R_i$  Increasing  $R_f$  Increasing  $R_{\alpha}$

Increases A<sub>L</sub>

Decreases A<sub>L</sub>

Increases A<sub>L</sub>

Decreases A<sub>L</sub>

#### **Applications Suggestions**

Driving a Capacitive Load:

The KH560 is particularly suitable for driving a capacitive load. Unlike a classical op amp (with an inductive output impedance), the KH560's output impedance, while starting out real at the programmed value, goes somewhat capacitive at higher frequencies. This yields a very stable performance driving a capacitive load. The overall response is limited by the (1/RC) bandwidth set by the KH560's output impedance and the load capacitance. It is therefore advantageous to set a low  $R_{\rm o}$  with the constraint that extremely low  $R_{\rm f}$  values will degrade the distortion performance.  $R_{\rm o} = 25\Omega$  was selected for the data sheet plots. Note from distortion plots into a capacitive load that the KH560 achieves better than 60dBc THD (10-bits) driving  $2V_{pp}$  into a 50pF load through 30MHz.

# Improving the Output Impedance Match vs. Frequency - Using R<sub>x</sub>:

Using the loop gain to provide a non-zero output impedance provides a very good impedance match at low frequencies. As shown on the *Output Return Loss* plot, however, this match degrades at higher frequencies. Adding a small external resistor in series with the output,  $R_x$ , as part of the output impedance (and adjusting the programmed  $R_o$  accordingly) provides a much better match over frequency. Figure 9 shows this approach.

Figure 9: Improving Output Impedance Match vs. Frequency

Increasing  $R_x$  will decrease the achievable voltage swing at the load. A minimum  $R_x$  should be used consistent with the desired output match. As discussed in the thermal analysis discussion,  $R_x$  is also very useful in limiting the internal power under an output shorted condition.

# Interpreting the Slew Rate:

The slew rate shown in the data sheet applies to the voltage swing at the load for the circuit of Figure 1. Twice this value would be required of a low output impedance amplifier using an external matching resistor to achieve the same slew rate at the load.

## Layout Suggestions:

The fastest fine scale pulse response settling requires careful attention to the power supply decoupling. Generally, the larger electrolytic capacitor ground connections should be as near the load ground (or cable shield connection) as is reasonable, while the higher frequency ceramic de-coupling caps should be as near the KH560's supply pins as possible to a low inductance ground plane.

#### Evaluation Boards:

An evaluation board (showing a good high frequency layout) for the KH560 is available. This board may be ordered as part #730019.

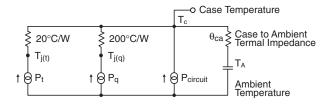

#### Thermal Analysis and Protection

A thermal analysis of a chip and wire hybrid is directed at determining the maximum junction temperature of all the internal transistors. From the total internal power dissipation, a case temperature may be developed using the ambient temperature and the case to ambient thermal impedance. Then, each of the dominant power dissipating paths are considered to determine which has the maximum rise above case temperature.

The thermal model and analysis steps are shown below. As is typical, the model is cast as an electrical model where the temperatures are voltages, the power dissipators are current sources, and the thermal impedances are resistances. Refer to the summary design equations and Figure 1 for a description of terms.

REV. 1A February 2001 11

Figure 10: Thermal Model

$I_o = V_o / R_{eq}$  total output current

with

$$R_{eq} = R_L \parallel \left\lceil \frac{R_f A_L}{A_I - 1} \right\rceil$$

total load

$$I_{t} = \frac{1}{2} \left( I_{o} + \sqrt{I_{o}^{2} + (.06)^{2}} \right)$$

total internal output stage current

$$P_t = I_t \cdot (V_{CC} - 1.4 - 17.3\Omega \cdot I_t)$$

output stage power

$$\begin{aligned} P_q &= 0.2 \cdot I_t \cdot \left( V_{CC} - V_o - 0.7 - 15.3\Omega \cdot I_t \right) \\ & \text{power in hottest internal junction} \\ & \text{prior to output stage} \end{aligned}$$

$$\begin{aligned} P_{circuit} = 1.3 \cdot V_{CC} \cdot \left(2 \cdot I_t - I_o + 19.2 \text{mA}\right) - P_t - P_q \\ \text{power in remainder of circuit [note } V_{CC} = |-V_{CC}|] \end{aligned}$$

Note that the  $P_t$  and  $P_q$  equations are written for positive  $V_o$ . Absolute values of  $-V_{CC}$ ,  $V_o$ , and  $I_o$ , should be used for a negative going  $V_o$ . since we are only interested in delta V's. For bipolar swings, the two powers for each output polarity are developed as shown above then ratioed by the duty cycle. Having the total internal power, as well as its component parts, the maximum junction temperature may be computed as follows:

$$\begin{split} T_c &= T_A + (P_q + P_T + P_{circult}) \bullet \theta_{ca} \text{ Case Temperature} \\ \theta_{ca} &= 35^{\circ}\text{C/W} \text{ for the KH560 with no heatsink in still air} \\ T_{j(t)} &= T_c + P_t \bullet 20^{\circ}\text{C/W} \\ &\quad \text{output transistor junction temperature} \\ T_{j(q)} &= T_c + P_q \bullet 200^{\circ}\text{C/W} \\ &\quad \text{hottest internal junction temperature} \end{split}$$

# The Limiting Factor for Output Power is Maximum Junction Temperature

Reducing  $\theta_{ca}$  through either heatsinking and/or airflow can greatly reduce the junction temperatures. One effective means of heatsinking the KH560 is to use a thermally conductive pad under the part from the package bottom to a top surface ground plane on the component side. Tests have shown a  $\theta_{ca}$  of 24°C in still air using a "Sil Pad" available from Bergquist (800-347-4572).

As an example of calculating the maximum internal junction temperatures, consider the circuit of Figure 1 driving  $\pm 2.5$ V, 50% duty cycle, square wave into a 50 $\Omega$  load. Note that 1/2 of the total P<sub>T</sub> and P<sub>a</sub> powers were used

$$R_{eq} = 50\Omega \left\| \left[ \frac{410\Omega \cdot 5}{5 - 1} \right] = 45.6\Omega$$

$$I_0 = 2.5 \text{V} / (45.6 \Omega) = 54.9 \text{mA}$$

$$I_T = \frac{1}{2} \left( 54.9 \text{mA} + \sqrt{(54.9 \text{mA})^2 + (.06)^2} \right) = 68.1 \text{mA}$$

$P_T = 68.1 \text{mA} \left[ 15 - 2.5 - 0.7 - 15.3\Omega \cdot 68.1 \text{mA} \right] = 733 \text{mW}$  total power in both sides of the output stage

$P_q = 0.2 \cdot 68.1 \text{mA} \left[ 15 - 1.4 - 17.3\Omega \cdot 68.1 \text{mA} \right] = 169 \text{mW}$  total power in both sides of hottest junctions prior to output stage

$$\begin{aligned} P_{circuit} = & 1.3 \cdot (15) \cdot \left[ 2 \cdot 68.1 \text{mA} - 54.9 \text{mA} + 19.2 \text{mA} \right] \\ & - 733 \text{mW} - 169 \text{mW} = 1.058 \text{W} \\ & \text{power in the remainder of circuit} \end{aligned}$$

With these powers and  $T_A = 25^{\circ}C$  and  $\theta_{ca} = 35^{\circ}C$  / W

$$T_c = 25^{\circ}C + (.733 + .169 + 1.058) \cdot 35 = 94^{\circ}C$$

case temperature

From this, the hottest internal junctions may be found as

$$T_j(t) = 94^{\circ}C + \frac{1}{2}(.733) \cdot 20 = 101^{\circ}C$$

output stage

$$T_j(q) = 94^{\circ}C + \frac{1}{2}(.169) \cdot 200 = 111^{\circ}C$$

hottest internal junction

here since the 50% duty cycle output splits the power evenly between the two halves of the circuit whereas the total powers were used to get case temperature.

Even with the output current internally limited to 250mA, the KH560's short circuiting capability is principally a thermal issue. Generally, the KH560 can survive short duration shorts to ground without any special effort. For protection against shorts to the  $\pm 15$  volt supply voltages, it is very useful to reduce some of the voltage across the output stage transistors by using some external output resistance,  $R_x$ , as shown in Figure 9.

## **Evaluation Board**

An evaluation board (part number 730019) for the KH560 is available.

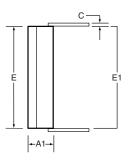

# **KH560 Package Dimensions**

| Symbol   | Inc       | hes     | Milimeters     |         |  |

|----------|-----------|---------|----------------|---------|--|

| - Cymbol | Minimun   | Maximum | Minimum        | Maximum |  |

| А        |           | 0.225   |                | 5.72    |  |

| A1       | 0.139     | 0.192   | 3.53           | 4.88    |  |

| b        | 0.014     | 0.026   | 0.36           | 0.66    |  |

| b1       | 0.050     | BSC     | 1.27 BSC       |         |  |

| С        | 0.008     | 0.018   | 0.20           | 0.46    |  |

| D        | 1.190     | 1.290   | 30.23          | 32.77   |  |

| D1       | 1.095     | 1.105   | 27.81          | 28.07   |  |

| E        | 0.500     | 0.610   | 12.70          | 15.49   |  |

| E1       | 0.600 BSC |         | 15.24 BSC      |         |  |

| е        | 0.100 BSC |         | 2.54 BSC       |         |  |

| L        | 0.165 BSC |         | 4.19 BSC       |         |  |

| Q        | 0.015     | 0.075   | 0.075 0.38 1.9 |         |  |

#### NOTES:

ES:

Seal: seam weld (AM, AK), epoxy (AI)

Lead finish: gold finish

Package composition:

Package: ceramic

Lid: kovar/nickel (AM, AK), ceramic (AI)

Leadframe: alloy 42

Die attach: epoxy

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICES TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.