# ANALOG DEVICES

# Programmable Capacitance-to-Digital Converter with Environmental Compensation

# AD7142

#### FEATURES

Programmable capacitance-to-digital converter 36 ms update rate (@ maximum sequence length) Better than 1 fF resolution 14 capacitance sensor input channels No external RC tuning components required Automatic conversion sequencer **On-chip automatic calibration logic** Automatic compensation for environmental changes Automatic adaptive threshold and sensitivity levels **On-chip RAM to store calibration data** SPI®-compatible serial interface (AD7142) I<sup>2</sup>C<sup>®</sup>-compatible serial interface (AD7142-1) Separate VDRIVE level for serial interface Interrupt output and GPIO 32-lead, 5 mm x 5 mm LFCSP\_VQ 2.6 V to 3.6 V supply voltage Low operating current Full power mode: less than 1 mA Low power mode: 50 µA

### APPLICATIONS

Personal music and multimedia players Cell phones Digital still cameras Smart hand-held devices Television, A/V, and remote controls Gaming consoles

### **GENERAL DESCRIPTION**

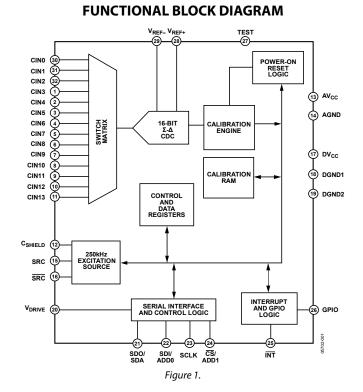

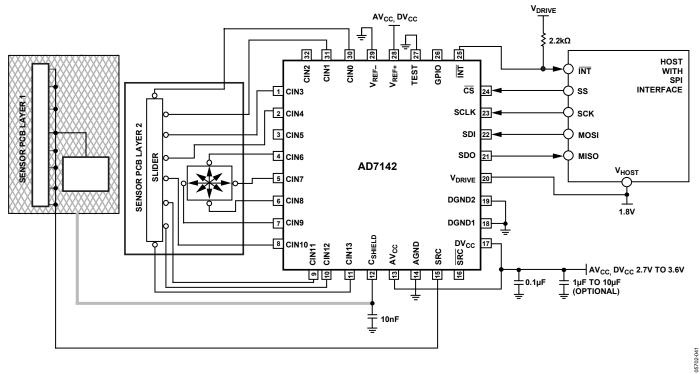

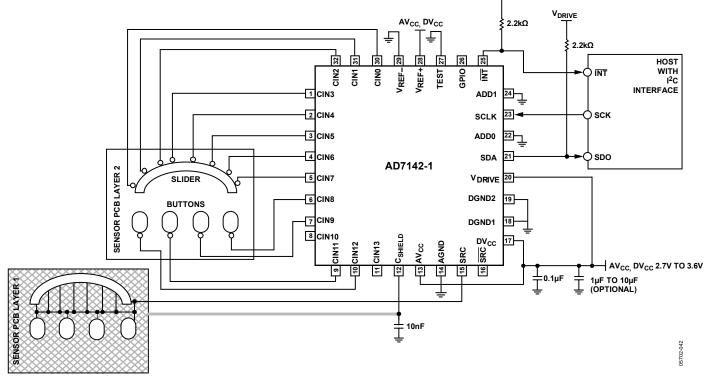

The AD7142 and AD7142-1 are integrated capacitance-todigital converters (CDCs) with on-chip environmental calibration for use in systems requiring a novel user input method. The AD7142 and AD7142-1 can interface to external capacitance sensors implementing functions such as capacitive buttons, scroll bars, or wheels.

The CDC has 14 inputs channeled through a switch matrix to a 16-bit, 250 kHz sigma-delta ( $\Sigma$ - $\Delta$ ) capacitance-to-digital converter. The CDC is capable of sensing changes in the capacitance of the external sensors and uses this information to register a sensor activation. The external sensors can be arranged as a series of buttons, as a scroll bar or wheel, or as a combination of sensor types. By programming the registers, the user has full control over the CDC setup. High resolution sensors require minor software to run on the host processor.

#### Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

The AD7142 and AD7142-1 have on-chip calibration logic to account for changes in the ambient environment. The calibration sequence is performed automatically and at continuous intervals, while the sensors are not touched. This ensures that there are no false or nonregistering touches on the external sensors due to a changing environment.

The AD7142 has an SPI-compatible serial interface, and the AD7142-1 has an I<sup>2</sup>C-compatible serial interface. Both parts have an interrupt output, as well as a general-purpose input/ output (GPIO).

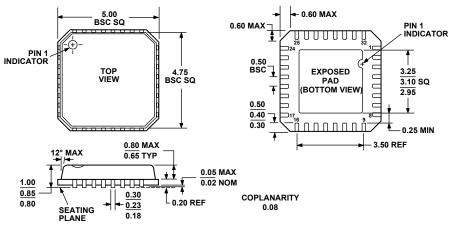

The AD7142 and AD7142-1 are available in a 32-lead, 5 mm  $\times$  5 mm LFCSP\_VQ and operate from a 2.6 V to 3.6 V supply. The operating current consumption is less than 1 mA, falling to 50  $\mu$ A in low power mode (conversion interval of 400 ms).

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2006 Analog Devices, Inc. All rights reserved.

# TABLE OF CONTENTS

| Features 1                                         |

|----------------------------------------------------|

| Applications1                                      |

| Functional Block Diagram 1                         |

| General Description                                |

| Revision History 2                                 |

| Specifications                                     |

| SPI Timing Specifications (AD7142)5                |

| I <sup>2</sup> C Timing Specifications (AD7142-1)6 |

| Absolute Maximum Ratings7                          |

| ESD Caution7                                       |

| Pin Configurations and Function Descriptions       |

| Typical Performance Characteristics                |

| Theory of Operation11                              |

| Capacitance Sensing Theory11                       |

| Operating Modes12                                  |

| Capacitance Sensor Input Configuration             |

| CIN Input Multiplexer Setup13                      |

| Capacitiance-to-Digital Converter14                |

| Oversampling the CDC Output14                      |

| Capacitance Sensor Offset Control14                |

| Conversion Sequencer14                             |

| CDC Conversion Sequence Time                       |

| CDC Conversion Results16                           |

| Noncontact Proximity Detection17                   |

| Recalibration17                                    |

| Proximity Sensitivity17                            |

| FIFO Control                                       |

| Environmental Calibration                          |

| Capacitance Sensor Behavior Without Calibration                                                                                                                                                                                                                              | 22                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Capacitance Sensor Behavior with Calibration                                                                                                                                                                                                                                 | 23                                                                                                                                 |

| Adaptive Threshold and Sensitivity                                                                                                                                                                                                                                           | 24                                                                                                                                 |

| Interrupt Output                                                                                                                                                                                                                                                             | 25                                                                                                                                 |

| CDC Conversion Complete Interrupt                                                                                                                                                                                                                                            | 25                                                                                                                                 |

| Sensor Touch Interrupt                                                                                                                                                                                                                                                       | 25                                                                                                                                 |

| GPIO INT Output Control                                                                                                                                                                                                                                                      | 27                                                                                                                                 |

| Outputs                                                                                                                                                                                                                                                                      | 29                                                                                                                                 |

| Excitation Source                                                                                                                                                                                                                                                            | 29                                                                                                                                 |

| C <sub>SHIELD</sub> Output                                                                                                                                                                                                                                                   | 29                                                                                                                                 |

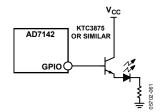

| GPIO                                                                                                                                                                                                                                                                         | 29                                                                                                                                 |

| Using the GPIO to turn on/off an LED                                                                                                                                                                                                                                         | 29                                                                                                                                 |

| Serial Interface                                                                                                                                                                                                                                                             | 30                                                                                                                                 |

| SPI Interface                                                                                                                                                                                                                                                                | 30                                                                                                                                 |

|                                                                                                                                                                                                                                                                              |                                                                                                                                    |

| I <sup>2</sup> C Compatible Interface                                                                                                                                                                                                                                        | 32                                                                                                                                 |

| I <sup>2</sup> C Compatible Interface                                                                                                                                                                                                                                        |                                                                                                                                    |

| -                                                                                                                                                                                                                                                                            | 34                                                                                                                                 |

| V <sub>DRIVE</sub> Input                                                                                                                                                                                                                                                     | 34<br>35                                                                                                                           |

| V <sub>DRIVE</sub> Input<br>PCB Design Guidelines                                                                                                                                                                                                                            | 34<br>35<br>35                                                                                                                     |

| V <sub>DRIVE</sub> Input<br>PCB Design Guidelines<br>Capacitive Sensor Board Mechanical Specifications                                                                                                                                                                       | 34<br>35<br>35<br>35                                                                                                               |

| V <sub>DRIVE</sub> Input<br>PCB Design Guidelines<br>Capacitive Sensor Board Mechanical Specifications<br>Chip Scale Packages                                                                                                                                                | <ol> <li>34</li> <li>35</li> <li>35</li> <li>35</li> <li>36</li> </ol>                                                             |

| V <sub>DRIVE</sub> Input<br>PCB Design Guidelines<br>Capacitive Sensor Board Mechanical Specifications<br>Chip Scale Packages<br>Power-Up Sequence                                                                                                                           | <ol> <li>34</li> <li>35</li> <li>35</li> <li>35</li> <li>36</li> <li>37</li> </ol>                                                 |

| V <sub>DRIVE</sub> Input<br>PCB Design Guidelines<br>Capacitive Sensor Board Mechanical Specifications<br>Chip Scale Packages<br>Power-Up Sequence<br>Typical Application Circuits                                                                                           | <ul> <li>34</li> <li>35</li> <li>35</li> <li>35</li> <li>36</li> <li>37</li> <li>38</li> </ul>                                     |

| V <sub>DRIVE</sub> Input<br>PCB Design Guidelines<br>Capacitive Sensor Board Mechanical Specifications<br>Chip Scale Packages<br>Power-Up Sequence<br>Typical Application Circuits<br>Register Map                                                                           | <ul> <li>34</li> <li>35</li> <li>35</li> <li>36</li> <li>37</li> <li>38</li> <li>39</li> </ul>                                     |

| V <sub>DRIVE</sub> Input<br>PCB Design Guidelines<br>Capacitive Sensor Board Mechanical Specifications<br>Chip Scale Packages<br>Power-Up Sequence<br>Typical Application Circuits<br>Register Map<br>Detailed Register Descriptions                                         | <ul> <li>34</li> <li>35</li> <li>35</li> <li>36</li> <li>37</li> <li>38</li> <li>39</li> <li>39</li> </ul>                         |

| V <sub>DRIVE</sub> Input<br>PCB Design Guidelines<br>Capacitive Sensor Board Mechanical Specifications<br>Chip Scale Packages<br>Power-Up Sequence<br>Typical Application Circuits<br>Register Map<br>Detailed Register Descriptions<br>Bank 1 Registers                     | <ul> <li>34</li> <li>35</li> <li>35</li> <li>36</li> <li>37</li> <li>38</li> <li>39</li> <li>39</li> <li>48</li> </ul>             |

| V <sub>DRIVE</sub> Input<br>PCB Design Guidelines<br>Capacitive Sensor Board Mechanical Specifications<br>Chip Scale Packages<br>Power-Up Sequence<br>Typical Application Circuits<br>Register Map<br>Detailed Register Descriptions<br>Bank 1 Registers<br>Bank 2 Registers | <ul> <li>34</li> <li>35</li> <li>35</li> <li>36</li> <li>37</li> <li>38</li> <li>39</li> <li>39</li> <li>48</li> <li>54</li> </ul> |

### **REVISION HISTORY**

6/06—Revision 0: Initial Version

# **SPECIFICATIONS**

AV<sub>CC</sub>, DV<sub>CC</sub> = 2.6 V to 3.6 V,  $T_A = -40^{\circ}$ C to +85°C, unless otherwise noted.

### Table 1.

| Parameter                                   | Min                      | Тур    | Max  | Unit  | Test Conditions/Comments                                                     |

|---------------------------------------------|--------------------------|--------|------|-------|------------------------------------------------------------------------------|

| CAPACITANCE-TO-DIGITAL CONVERTER            |                          |        |      |       |                                                                              |

| Update Rate                                 | 35.45                    | 36.86  | 38.4 | ms    | 12 conversion stages in sequencer,<br>decimation = 256                       |

| Resolution                                  |                          | 16     |      | Bit   |                                                                              |

| CIN Input Range <sup>1</sup>                |                          | ±2     |      | pF    |                                                                              |

| No Missing Codes                            | 16                       |        |      | Bit   | Guaranteed by design, but not production tested                              |

| CIN Input Leakage                           |                          | 25     |      | nA    |                                                                              |

| Total Unadjusted Error                      |                          |        | ±20  | %     |                                                                              |

| Output Noise (Peak-to-Peak)                 |                          | 7      |      | Codes | Decimation rate = 128                                                        |

|                                             |                          | 3      |      | Codes | Decimation rate = 256                                                        |

| Output Noise (RMS)                          |                          | 0.8    |      | Codes | Decimation rate = 128                                                        |

|                                             |                          | 0.5    |      | Codes | Decimation rate = 256                                                        |

| Parasitic Capacitance                       |                          |        | 40   | pF    | Parasitic capacitance to ground, per CIN inpu guaranteed by characterization |

| CBULK Offset Range <sup>1</sup>             |                          | ±20    |      | рF    | <i>,</i>                                                                     |

| CBULK Offset Resolution                     |                          | 156.25 |      | fF    |                                                                              |

| Low Power Mode Delay Accuracy               |                          |        | 4    | %     | % of 200 ms, 400 ms, 600 ms, or 800 ms                                       |

| EXCITATION SOURCE                           |                          |        |      |       |                                                                              |

| Frequency                                   | 240                      | 250    | 260  | kHz   |                                                                              |

| Output Voltage                              |                          |        | AVcc | V     |                                                                              |

| Short-Circuit Source Current                |                          | 20     |      | mA    |                                                                              |

| Short-Circuit Sink Current                  |                          | 50     |      | mA    |                                                                              |

| Maximum Output Load                         |                          | 250    |      | pF    | Capacitance load on source to ground                                         |

| C <sub>SHIELD</sub> Output Drive            |                          | 10     |      | μΑ    |                                                                              |

|                                             |                          | AVcc/2 |      | v     |                                                                              |

| LOGIC INPUTS (SDI, SCLK, CS, SDA, GPI TEST) |                          |        |      |       |                                                                              |

| V <sub>III</sub> Input High Voltage         | 0.7 x V <sub>DRIVE</sub> |        |      | v     |                                                                              |

| V <sub>L</sub> Input Low Voltage            | Dive                     |        | 0.4  | v     |                                                                              |

| l <sub>H</sub> Input High Voltage           | -1                       |        |      | μA    |                                                                              |

| I <sub>IL</sub> Input Low Voltage           |                          |        | 1    | μA    |                                                                              |

| Hysteresis                                  |                          | 150    |      | mV    |                                                                              |

| OPEN-DRAIN OUTPUTS (SCLK, SDA, INT)         |                          |        |      |       |                                                                              |

| V <sub>oL</sub> Output Low Voltage          |                          |        | 0.4  | v     | $I_{\text{SINK}} = -1 \text{ mA}$                                            |

| IoH Output High Leakage Current             |                          | +0.1   | ±1   | μA    | V <sub>OUT</sub> = V <sub>DRIVE</sub>                                        |

| LOGIC OUTPUTS (SDO, GPO)                    |                          |        |      |       |                                                                              |

| V <sub>oL</sub> Output Low Voltage          |                          |        | 0.4  | v     | I <sub>SINK</sub> = 1 mA, V <sub>DRIVE</sub> = 1.65 V to 3.6 V               |

| V <sub>OH</sub> Output High Voltage         | $V_{\text{DRIVE}} - 0.6$ |        | 2    | v     | $I_{SOURCE} = 1 \text{ mA}, V_{DRIVE} = 1.65 \text{ V to } 3.6 \text{ V}$    |

| SDO Floating State Leakage Current          | - Dinve 0.0              |        | ±1   | μA    | Pin three-state, leakage measured to GND an DVcc                             |

| GPO Floating State Leakage Current          | -5                       |        | +2   | μΑ    | Pin three-state, leakage measured to GND an DVcc                             |

| Parameter  | Min  | Тур  | Max | Unit | Test Conditions/Comments                            |

|------------|------|------|-----|------|-----------------------------------------------------|

| POWER      |      |      |     |      |                                                     |

| AVcc, DVcc | 2.6  | 3.3  | 3.6 | V    |                                                     |

| VDRIVE     | 1.65 |      | 3.6 | V    | Serial interface operating voltage                  |

| lcc        |      | 0.9  | 1   | mA   | In full power mode                                  |

|            |      |      | 20  | μA   | Low power mode, converter idle, $T_A = 25^{\circ}C$ |

|            |      | 16   | 33  | μA   | Low power mode, converter idle                      |

|            |      |      | 4.5 | μΑ   | Full shutdown, T <sub>A</sub> = 25°C                |

|            |      | 2.25 | 18  | μA   | Full shutdown                                       |

<sup>1</sup> C<sub>IN</sub> and C<sub>BULK</sub> are defined as follows:

Table 2. Typical Average Current in Low Power Mode,  $AV_{CC}$ ,  $DV_{CC} = 3.6$  V,  $T = 25^{\circ}$ C, Load of 50 pF on SRC Pin, No Load on  $\overline{SRC}$ Number of Conversion Stages, Current Values Expressed in UA

|                         |                      | Number of Conversion Stages, Current Values Expressed in µA |      |      |      |      |      |      |       |       |       |       |       |

|-------------------------|----------------------|-------------------------------------------------------------|------|------|------|------|------|------|-------|-------|-------|-------|-------|

| Low Power<br>Mode Delay | Decimation<br>Rate = | 1                                                           | 2    | 3    | 4    | 5    | 6    | 7    | 8     | 9     | 10    | 11    | 12    |

| 200 ms                  | 128                  | 26.4                                                        | 33.3 | 40.1 | 46.9 | 53.5 | 60   | 66.5 | 72.8  | 79.1  | 85.2  | 91.3  | 97.3  |

|                         | 256                  | 35.6                                                        | 49.1 | 62.2 | 74.9 | 87.3 | 99.3 | 111  | 122.3 | 133.4 | 144.2 | 154.7 | 164.9 |

| 400 ms                  | 128                  | 21.3                                                        | 24.8 | 28.3 | 31.7 | 35.2 | 38.6 | 42   | 45.4  | 48.7  | 52    | 55.3  | 58.6  |

|                         | 256                  | 26                                                          | 32.9 | 39.7 | 46.5 | 53.1 | 59.6 | 66.1 | 72.4  | 78.7  | 84.9  | 91    | 97    |

| 600 ms                  | 128                  | 19.6                                                        | 21.9 | 24.3 | 26.6 | 28.9 | 31.2 | 33.5 | 35.8  | 38.1  | 40.4  | 42.6  | 44.8  |

|                         | 256                  | 22.7                                                        | 27.4 | 32   | 36.6 | 41.1 | 45.6 | 50   | 54.4  | 58.8  | 63.1  | 67.4  | 71.6  |

| 800 ms                  | 128                  | 18.7                                                        | 20.5 | 22.2 | 24   | 25.7 | 27.5 | 29.2 | 31    | 32.7  | 34.4  | 36.1  | 37.8  |

|                         | 256                  | 21.1                                                        | 24.6 | 28.1 | 31.5 | 35   | 38.4 | 41.8 | 45.2  | 48.5  | 51.8  | 55.1  | 58.4  |

Table 3. Maximum Average Current in Low Power Mode, AV<sub>CC</sub>, DV<sub>CC</sub> = 3.6 V, Load of 50 pF on SRC Pin, No Load on SRC

|                         |                      | Numbe | r of Con | version | Stages, | Current | Values | Express | ed in µA |       |       |       |       |

|-------------------------|----------------------|-------|----------|---------|---------|---------|--------|---------|----------|-------|-------|-------|-------|

| Low Power<br>Mode Delay | Decimation<br>Rate = | 1     | 2        | 3       | 4       | 5       | 6      | 7       | 8        | 9     | 10    | 11    | 12    |

| 200 ms                  | 128                  | 45.4  | 53.6     | 61.5    | 69.4    | 77.1    | 84.7   | 92.2    | 99.6     | 106.8 | 113.9 | 121   | 127.9 |

|                         | 256                  | 56.2  | 72       | 87.2    | 102     | 116.3   | 130.2  | 143.7   | 156.8    | 169.5 | 181.8 | 193.8 | 205.5 |

| 400 ms                  | 128                  | 39.5  | 43.6     | 47.7    | 51.8    | 55.8    | 59.8   | 63.7    | 67.6     | 71.5  | 75.4  | 79.2  | 83    |

|                         | 256                  | 45    | 53.1     | 61.1    | 68.9    | 76.7    | 84.3   | 91.8    | 99.1     | 106.4 | 113.6 | 120.6 | 127.5 |

| 600 ms                  | 128                  | 37.5  | 40.3     | 43      | 45.8    | 48.5    | 51.2   | 53.9    | 56.5     | 59.2  | 61.8  | 64.5  | 67.1  |

|                         | 256                  | 41.2  | 46.7     | 52.1    | 57.4    | 62.7    | 67.9   | 73.1    | 78.2     | 83.3  | 88.3  | 93.3  | 98.2  |

| 800 ms                  | 128                  | 36.5  | 38.6     | 40.7    | 42.7    | 44.8    | 46.8   | 48.8    | 50.9     | 52.9  | 54.9  | 56.9  | 58.9  |

|                         | 256                  | 39.3  | 43.4     | 47.5    | 51.5    | 55.6    | 59.5   | 63.5    | 67.4     | 71.3  | 75.2  | 79    | 82.8  |

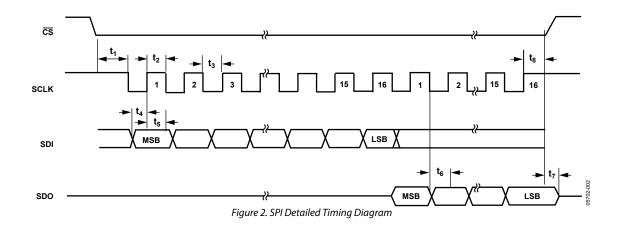

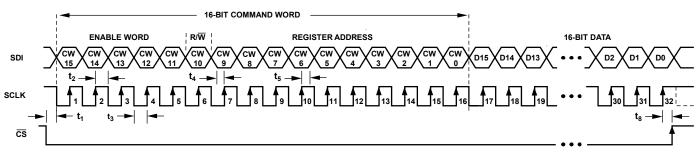

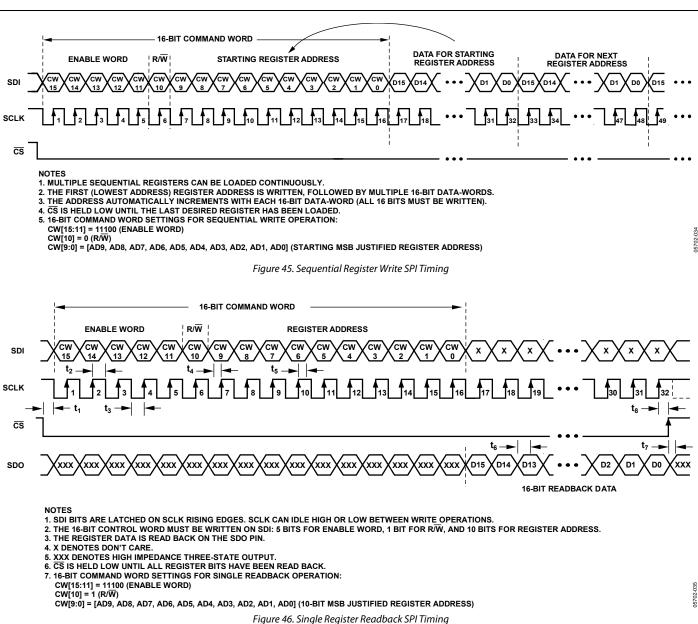

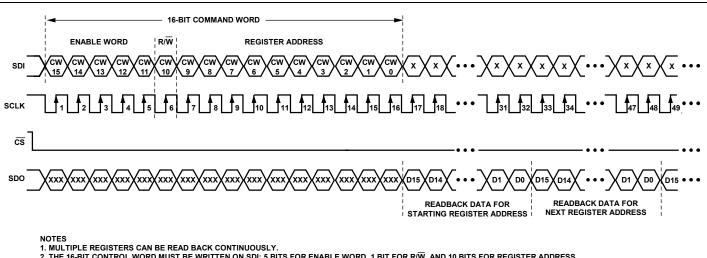

### SPI TIMING SPECIFICATIONS (AD7142)

- . .

-----

$T_A = -40^{\circ}$ C to +85°C;  $V_{DRIVE} = 1.65$  V to 3.6 V;  $AV_{CC}$ ,  $DV_{CC} = 2.6$  V to 3.6 V, unless otherwise noted. Sample tested at 25°C to ensure compliance. All input signals are specified with  $t_R = t_F = 5$  ns (10% to 90% of  $V_{CC}$ ) and timed from a voltage level of 1.6 V.

| Table 4. SPI Tir         | Table 4. SPI Timing Specifications           |         |                                            |  |  |  |  |  |

|--------------------------|----------------------------------------------|---------|--------------------------------------------|--|--|--|--|--|

| Parameter                | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit    | Description                                |  |  |  |  |  |

| <b>f</b> <sub>SCLK</sub> | 5                                            | MHz max |                                            |  |  |  |  |  |

| t1                       | 5                                            | ns min  | CS falling edge to first SCLK falling edge |  |  |  |  |  |

| t <sub>2</sub>           | 20                                           | ns min  | SCLK high pulse width                      |  |  |  |  |  |

| t <sub>3</sub>           | 20                                           | ns min  | SCLK low pulse width                       |  |  |  |  |  |

| t <sub>4</sub>           | 15                                           | ns min  | SDI setup time                             |  |  |  |  |  |

| t <sub>5</sub>           | 15                                           | ns min  | SDI hold time                              |  |  |  |  |  |

| t <sub>6</sub>           | 20                                           | ns max  | SDO access time after SCLK falling edge    |  |  |  |  |  |

| t <sub>7</sub>           | 16                                           | ns max  | CS rising edge to SDO high impedance       |  |  |  |  |  |

| t <sub>8</sub>           | 15                                           | ns min  | SCLK rising edge to $\overline{CS}$ high   |  |  |  |  |  |

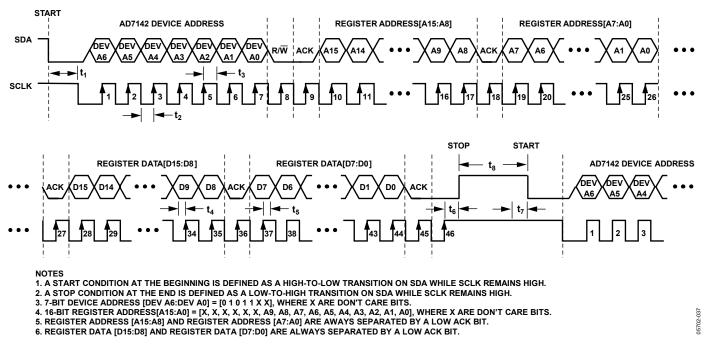

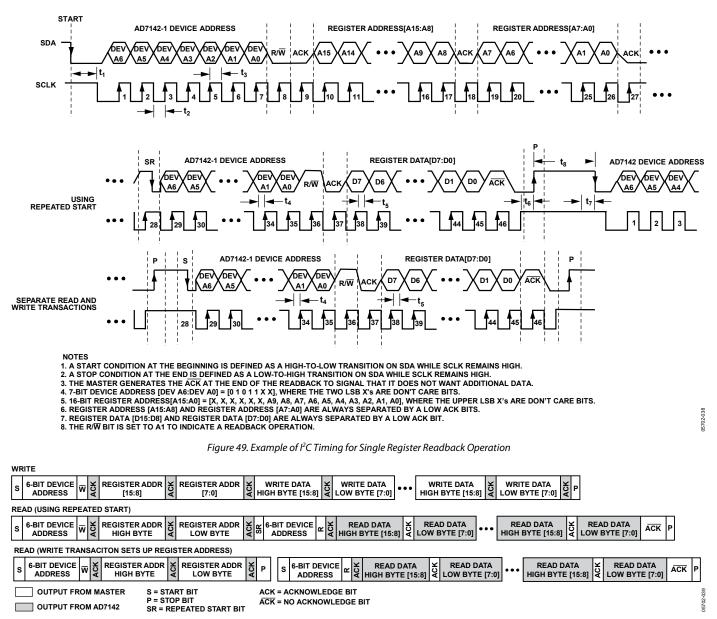

### I<sup>2</sup>C TIMING SPECIFICATIONS (AD7142-1)

$T_A = -40^{\circ}$ C to  $+85^{\circ}$ C;  $V_{DRIVE} = 1.65$  V to 3.6 V;  $AV_{CC}$ ,  $DV_{CC} = 2.6$  V to 3.6 V, unless otherwise noted. Sample tested at 25°C to ensure compliance. All input signals timed from a voltage level of 1.6 V.

| Parameter                | Limit | Unit    | Description                                           |

|--------------------------|-------|---------|-------------------------------------------------------|

| <b>f</b> <sub>SCLK</sub> | 400   | kHz max |                                                       |

| t1                       | 0.6   | μs min  | Start condition hold time, tHD; STA                   |

| t <sub>2</sub>           | 1.3   | μs min  | Clock low period, tLOW                                |

| t <sub>3</sub>           | 0.6   | μs min  | Clock high period, thigh                              |

| t4                       | 100   | ns min  | Data setup time, t <sub>su; DAT</sub>                 |

| t5                       | 300   | ns min  | Data hold time, t <sub>HD; DAT</sub>                  |

| t <sub>6</sub>           | 0.6   | μs min  | Stop condition setup time, t <sub>SU; STO</sub>       |

| t <sub>7</sub>           | 0.6   | μs min  | Start condition setup time, t <sub>SU; STA</sub>      |

| t <sub>8</sub>           | 1.3   | μs min  | Bus free time between stop and start conditions, tBUF |

| t <sub>R</sub>           | 300   | ns max  | Clock/data rise time                                  |

| t <sub>F</sub>           | 300   | ns max  | Clock/data fall time                                  |

#### Table 5. I<sup>2</sup>C Timing Specifications<sup>1</sup>

<sup>1</sup> Guaranteed by design, not production tested.

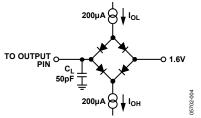

Figure 3. Load Circuit for Digital Output Timing Specifications

## **ABSOLUTE MAXIMUM RATINGS**

#### Table 6.

| Parameter                                                | Rating                               |

|----------------------------------------------------------|--------------------------------------|

| AV <sub>cc</sub> to AGND, DV <sub>cc</sub> to DGND       | –0.3 V to +3.6 V                     |

| Analog Input Voltage to AGND                             | -0.3 V to AV <sub>CC</sub> + 0.3 V   |

| Digital Input Voltage to DGND                            | $-0.3V$ to $V_{\text{DRIVE}}+0.3V$   |

| Digital Output Voltage to DGND                           | -0.3 V to V <sub>DRIVE</sub> + 0.3 V |

| Input Current to Any Pin Except<br>Supplies <sup>1</sup> | 10 mA                                |

| ESD Rating (Human Body Model)                            | 2.5 kV                               |

| Operating Temperature Range                              | -40°C to +150°C                      |

| Storage Temperature Range                                | –65°C to +150°C                      |

| Junction Temperature                                     | 150°C                                |

| LFCSP_VQ                                                 |                                      |

| Power Dissipation                                        | 450 mW                               |

| θ <sub>JA</sub> Thermal Impedance                        | 135.7°C/W                            |

| IR Reflow Peak Temperature                               | 260°C (±0.5°C)                       |

| Lead Temperature (Soldering 10 sec)                      | 300°C                                |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>1</sup> Transient currents of up to 100 mA do not cause SCR latch-up.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

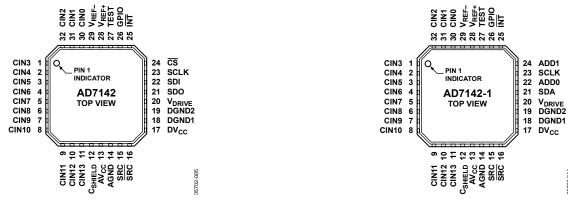

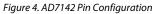

# **PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS**

05702-044

#### Table 7. Pin Function Descriptions

| Pin No. | Mnemonic          | Description                                                                                    |

|---------|-------------------|------------------------------------------------------------------------------------------------|

| 1       | CIN3              | Capacitance Sensor Input.                                                                      |

| 2       | CIN4              | Capacitance Sensor Input.                                                                      |

| 3       | CIN5              | Capacitance Sensor Input.                                                                      |

| 4       | CIN6              | Capacitance Sensor Input.                                                                      |

| 5       | CIN7              | Capacitance Sensor Input.                                                                      |

| 6       | CIN8              | Capacitance Sensor Input.                                                                      |

| 7       | CIN9              | Capacitance Sensor Input.                                                                      |

| 8       | CIN10             | Capacitance Sensor Input.                                                                      |

| 9       | CIN11             | Capacitance Sensor Input.                                                                      |

| 10      | CIN12             | Capacitance Sensor Input.                                                                      |

| 11      | CIN13             | Capacitance Sensor Input.                                                                      |

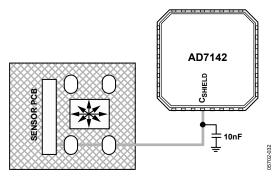

| 12      | CSHIELD           | CDC Shield Potential Output. Requires 10 nF capacitor to ground. Connect to external shield.   |

| 13      | AVcc              | CDC Supply Voltage.                                                                            |

| 14      | AGND              | Analog Ground Reference Point for All CDC Circuitry. Tie to analog ground plane.               |

| 15      | SRC               | CDC Excitation Source Output.                                                                  |

| 16      | SRC               | Inverted Excitation Source Output.                                                             |

| 17      | DVcc              | Digital Core Supply Voltage.                                                                   |

| 18      | DGND1             | Digital Ground.                                                                                |

| 19      | DGND2             | Digital Ground.                                                                                |

| 20      | VDRIVE            | Serial Interface Operating Voltage Supply.                                                     |

| 21      | SDO               | AD7142 SPI Serial Data Output.                                                                 |

|         | SDA               | AD7142-1 I <sup>2</sup> C Serial Data Input/Output. SDA requires pull-up resistor.             |

| 22      | SDI               | AD7142 SPI Serial Data Input.                                                                  |

|         | ADD0              | AD7142-1 I <sup>2</sup> C Address Bit 0.                                                       |

| 23      | SCLK              | Clock Input for Serial Interface.                                                              |

| 24      | CS                | AD7142 SPI Chip Select Signal.                                                                 |

|         | ADD1              | AD7142-1 I <sup>2</sup> C Address Bit 1.                                                       |

| 25      | INT               | General-Purpose Open-Drain Interrupt Output. Programmable polarity; requires pull-up resistor. |

| 26      | GPIO              | Programmable GPIO.                                                                             |

| 27      | TEST              | Factory Test Pin. Tie to ground.                                                               |

| 28      | V <sub>REF+</sub> | CDC Positive Reference Input. Normally tied to analog power.                                   |

| 29      | V <sub>REF-</sub> | CDC Negative Reference Input. Tie to analog ground.                                            |

| 30      | CINO              | Capacitance Sensor Input.                                                                      |

| 31      | CIN1              | Capacitance Sensor Input.                                                                      |

| 32      | CIN2              | Capacitance Sensor Input.                                                                      |

# **TYPICAL PERFORMANCE CHARACTERISTICS**

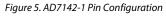

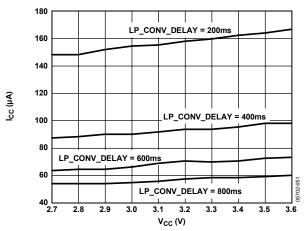

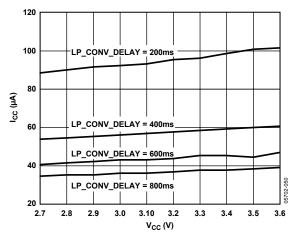

Figure 6. Supply Current vs. Supply Voltage  $(V_{cc} = AV_{cc} + DV_{cc}, I_{cc} = AI_{cc} + DI_{cc})$

Figure 7. Low Power Supply Current vs. Supply Voltage, Decimation Rate = 256 ( $V_{cc} = AV_{cc} + DV_{cc}$ ,  $I_{cc} = AI_{cc} + DI_{cc}$ )

Figure 8. Low Power Supply Current vs. Supply Voltage Decimation Rate =  $128 (V_{CC} = AV_{CC} + DV_{CC}, I_{CC} = AI_{CC} + DI_{CC})$

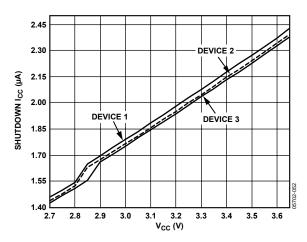

Figure 9. Shutdown Supply Current vs. Supply Voltage  $(V_{cc} = AV_{cc} + DV_{cc}, I_{cc} = AI_{cc} + DI_{cc})$

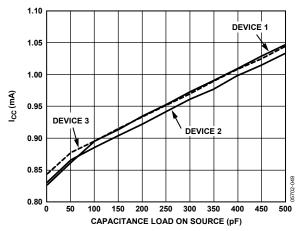

Figure 10. Supply Current vs. Capacitive Load on SRC ( $I_{CC} = AI_{CC} + DI_{CC}$ )

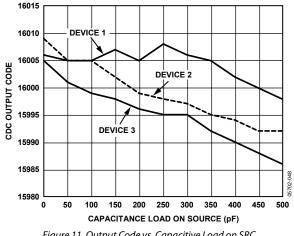

Figure 11. Output Code vs. Capacitive Load on SRC

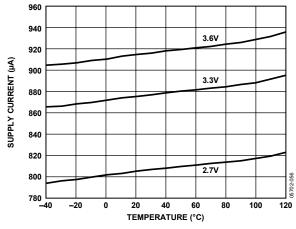

Figure 12. Supply Current vs. Temperature (Supply Current =  $AI_{CC} + DI_{CC}$ )

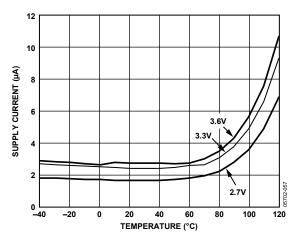

Figure 13. Shutdown Supply Current vs. Temperature (Supply Current = Alcc + Dlcc)

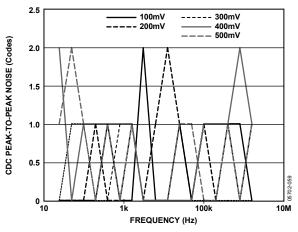

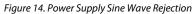

Figure 15. Power Supply Square Wave Rejection

## **THEORY OF OPERATION**

The AD7142 and AD7142-1 are capacitance-to-digital converters (CDCs) with on-chip environmental compensation, intended for use in portable systems requiring high resolution user input. The internal circuitry consists of a 16-bit,  $\Sigma$ - $\Delta$  converter that converts a capacitive input signal into a digital value. There are 14 input pins on the AD7142 and AD7142-1, CIN0 to CIN13. A switch matrix routes the input signals to the CDC. The result of each capacitance-to-digital conversion is stored in on-chip registers. The host subsequently reads the results over the serial interface. The AD7142 contains an SPI interface and the AD7142-1 has an I<sup>2</sup>C interface ensuring that the parts are compatible with a wide range of host processors. Because the AD7142 and AD7142-1 are identical parts, with the exception of the serial interface, AD7142 refers to both the AD7142 and AD7142-1 throughout this data sheet.

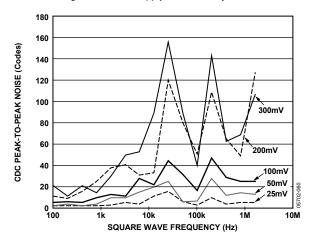

The AD7142 interfaces with up to 14 external capacitance sensors. These sensors can be arranged as buttons, scroll bars, wheels, or as a combination of sensor types. The external sensors consist of electrodes on a 2- or 4-layer PCB that interfaces directly to the AD7142.

The AD7142 can be set up to implement any set of input sensors by programming the on-chip registers. The registers can also be programmed to control features such as averaging, offsets, and gains for each of the external sensors. There is a sequencer on-chip to control how each of the capacitance inputs is polled.

The AD7142 has on-chip digital logic and 528 words of RAM that are used for environmental compensation. The effects of humidity, temperature, and other environmental factors can effect the operation of capacitance sensors. Transparent to the user, the AD7142 performs continuous calibration to compensate for these effects, allowing the AD7142 to give error-free results at all times.

The AD7142 requires some minor companion software that runs on the host or other microcontroller to implement high resolution sensor functions such as a scroll bar or wheel. However, no companion software is required to implement buttons, including 8-way button functionality. Button sensors are implemented completely in digital logic on-chip.

The AD7142 can be programmed to operate in either full power mode, or in low power automatic wake-up mode. The automatic wake-up mode is particularly suited for portable devices that require low power operation giving the user significant power savings coupled with full functionality. The AD7142 has an interrupt output,  $\overline{INT}$ , to indicate when new data has been placed into the registers.  $\overline{INT}$  is used to interrupt the host on sensor activation. The AD7142 operates from a 2.6 V to 3.6 V supply, and is available in a 32-lead, 5 mm × 5 mm LFCSP\_VQ.

### **CAPACITANCE SENSING THEORY**

The AD7142 uses a method of sensing capacitance known as the shunt method. Using this method, an excitation source is connected to a transmitter generating an electric field to a receiver. The field lines measured at the receiver are translated into the digital domain by a  $\Sigma$ - $\Delta$  converter. When a finger, or other grounded object, interferes with the electric field, some of the field lines are shunted to ground and do not reach the receiver (see Figure 16). Therefore, the total capacitance measured at the receiver decreases when an object comes close to the induced field.

Figure 16. Sensing Capacitance Method

In practice, the excitation source and  $\Sigma$ - $\Delta$  ADC are implemented on the AD7142, while the transmitter and receiver are constructed on a PCB that makes up the external sensor.

#### **Registering a Sensor Activation**

When a sensor is approached, the total capacitance associated with that sensor, measured by the AD7142, changes. When the capacitance changes to such an extent that a set threshold is exceeded, the AD7142 registers this as a sensor touch.

Preprogrammed threshold levels are used to determine if a change in capacitance is due to a button being activated. If the capacitance exceeds one of the threshold limits, the AD7142 registers this as a true button activation. The same thresholds principle is used to determine if other types of sensors, such as sliders or scroll wheels, are activated.

#### **Complete Solution for Capacitance Sensing**

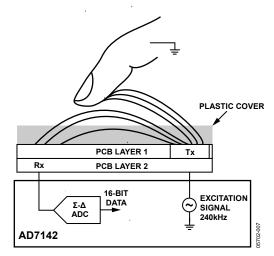

Analog Devices provides a complete solution for capacitance sensing. The two main elements to the solution are the sensor PCB and the AD7142.

If the application requires high resolution sensors such as scroll bars or wheels, software is required that runs on the host processor. (No software is required for button sensors.) The memory requirements for the host depend on the sensor, and are typically 10 kB of code and 600 bytes of data memory.

Figure 17. Three Part Capacitance Sensing Solution

Analog Devices supplies the sensor PCB design to the customer based on the customer's specifications, and supplies any necessary software on an open-source basis. Standard sensor designs are also available as PCB library components.

### **OPERATING MODES**

The AD7142 has three operating modes. Full power mode, where the device is always fully powered, is suited for applications where power is not a concern (for example, game consoles that have an ac power supply). Low power mode, where the part automatically powers down, is tailored to give significant power savings over full power mode, and is suited for mobile applications where power must be conserved. In shutdown mode, the part shuts down completely.

The POWER\_MODE bits (Bit 0 and Bit 1) of the control register set the operating mode on the AD7142. The control register is at Address 0x000. Table 8 shows the POWER\_MODE settings for each operating mode. To put the AD7142 into shutdown mode, set the POWER\_MODE bits to either 01 or 11.

#### Table 8. POWER\_MODE Settings

|                 | 0                  |

|-----------------|--------------------|

| POWER_MODE Bits | Operating Mode     |

| 00              | Full power mode    |

| 01              | Full shutdown mode |

| 10              | Low power mode     |

| 11              | Full shutdown mode |

|                 |                    |

The power-on default setting of the POWER\_MODE bits is 00, full power mode.

#### Full Power Mode

In full power mode, all sections of the AD7142 remain fully powered at all times. While a sensor is being touched, the AD7142 processes the sensor data. If no sensor is touched, the AD7142 measures the ambient capacitance level and uses this data for the on-chip compensation routines. In full power mode, the AD7142 converts at a constant rate. See the CDC Conversion Sequence Time section for more information.

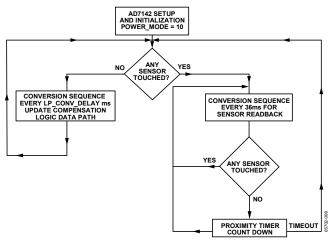

#### Low Power Mode

When in low power mode, the AD7142 POWER\_MODE bits are set to 10 upon device initialization. If the external sensors are not touched, the AD7142 reduces its conversion frequency, thereby greatly reducing its power consumption. The part remains in a low power state while the sensors are not touched. Every 400 ms, the AD7142 performs a conversion and uses this data to update the compensation logic. When an external sensor is touched, the AD7142 begins a conversion sequence every 40 ms to read back data from the sensors. In low power mode, the total current consumption of the AD7142 is an average of the current used during a conversion, and the current used while the AD7142 is waiting for the next conversion to begin. For example, when the low power mode conversion interval is 400 ms, the AD7142 typically uses 0.9 mA current for 40 ms, and 15  $\mu$ A for 400 ms of the conversion interval. (Note that these conversion timings can be altered through the register settings. See the CDC Conversion Sequence Time section for more information.)

Figure 18. Low Power Mode Operation

# **CAPACITANCE SENSOR INPUT CONFIGURATION**

Each stage of the AD7142 capacitance sensors can be uniquely configured by using the registers in Table 45 and Table 46. These registers are used to configure input pin connection setups, sensor offsets, sensor sensitivities, and sensor limits for each stage. Each sensor can be individually optimized. For example, a button sensor connected to STAGE0 can require a different sensitivity and offset values than a button with a different function that is connected to a different stage.

### **CIN INPUT MULTIPLEXER SETUP**

The CIN\_CONNECTION\_SETUP registers in Table 45 list the different options that are provided for connecting the sensor input pin to the CDC converter.

The AD7142 has an on-chip multiplexer to route the input signals from each pin to the input of the converter. Each input pin can be tied to either the negative or the positive input of the CDC, or it can be left floating. Each input can also be internally connected to the C<sub>SHIELD</sub> signal to help prevent cross coupling. If an input is not used, always connect it to C<sub>SHIELD</sub>.

For each input pin, CIN0 to CIN13, the multiplexer settings can be set on a per sequencer stage basis. For example, CIN0 is connected to the negative CDC input for conversion STAGE1, left floating for sequencer STAGE1, and so on for all twelve conversion stages.

Two bits in each register control the mux setting for the input pin.

| CIN0 0<br>CIN1 0<br>CIN2 0    | CIN_CONNECTION<br>_SETUP BITS | CIN SETTING                              |          |           |

|-------------------------------|-------------------------------|------------------------------------------|----------|-----------|

|                               | 00                            | CINX FLOATING                            |          |           |

| CIN5 0                        | 01                            | CINX CONNECTED TO<br>NEGATIVE CDC INPUT  | +<br>CDC |           |

| CIN8 0                        | 10                            | CINX CONNECTED TO<br>POSITIVE CDC INPUT  |          |           |

| CIN11 0<br>CIN12 0<br>CIN13 0 | 11                            | CINX CONNECTED TO<br>C <sub>SHIELD</sub> |          | 05702-010 |

|                               | Figure 19, Input Mu           | x Configuration Options                  | ·        |           |

Figure 19. Input Mux Configuration Options

# CAPACITIANCE-TO-DIGITAL CONVERTER

The capacitance-to-digital converter on the AD7142 has a  $\Sigma$ - $\Delta$  architecture with 16-bit resolution. There are 14 possible inputs to the CDC that are connected to the input of the converter through a switch matrix. The sampling frequency of the CDC is 250 kHz.

### **OVERSAMPLING THE CDC OUTPUT**

The decimation rate, or oversampling ratio, is determined by Bits[9:8] of the control register, as listed in Table 9.

Table 9. CDC Decimation Rate

|                      |                        | CDC Output Rate |

|----------------------|------------------------|-----------------|

| Decimation Bit Value | <b>Decimation Rate</b> | Per Stage       |

| 00                   | 256                    | 1.536 ms        |

| 01                   | 128                    | 3.072 ms        |

| 10 <sup>1</sup>      | -                      | -               |

| 11 <sup>1</sup>      | -                      | -               |

<sup>1</sup> Do not use this setting.

The decimation process on the AD7142 is an averaging process where a number of samples are taken and the averaged result is output. Due to the architecture of the digital filter employed, the amount of samples taken (per stage) is equal to  $3 \times$  the decimation rate. So  $3 \times 256$  or  $3 \times 128$  samples are averaged to obtain each stage result.

The decimation process reduces the amount of noise present in the final CDC result. However, the higher the decimation rate, the lower the output rate per stage, thus, a trade-off is possible between a noise free signal and speed of sampling.

### **CAPACITANCE SENSOR OFFSET CONTROL**

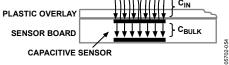

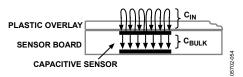

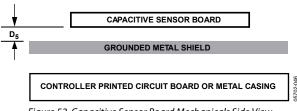

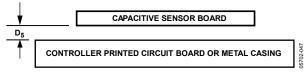

There are two programmable DACs on board the AD7142 to null any capacitance sensor offsets. These offsets are associated with printed circuit board capacitance or capacitance due to any other source, such as connectors. In Figure 20,  $C_{IN}$  is the capacitance of the input sensors, while  $C_{BULK}$  is the capacitance between layers of the sensor PCB.  $C_{BULK}$  can be offset using the on-board DACs.

Figure 20. Capacitances Around the Sensor PCB

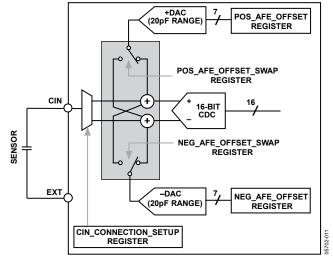

A simplified block diagram in Figure 21 shows how to apply the STAGE\_OFFSET registers to null the offsets. The 7-bit POS\_AFE\_OFFSET and NEG\_AFE\_OFFSET registers program the offset DAC to provide 0.16 pF resolution offset adjustment over a range of  $\pm 20$  pF. Apply the positive and negative offsets to either the positive or the negative CDC input using the NEG\_AFE\_OFFSET register and POS\_AFE\_OFFSET register.

This process is only required once during the initial capacitance sensor characterization.

Figure 21. Analog Front End Offset Control

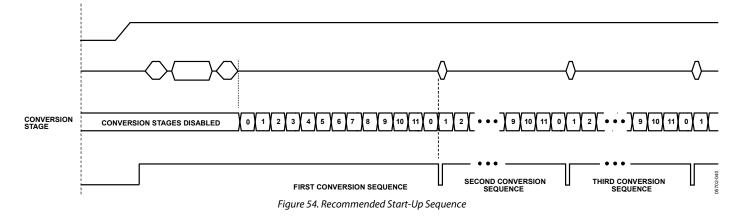

### **CONVERSION SEQUENCER**

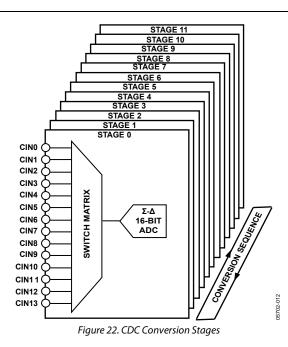

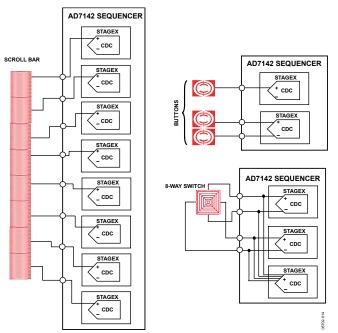

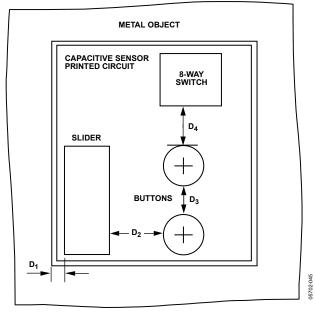

The AD7142 has an on-chip sequencer to implement conversion control for the input channels. Up to 12 conversion stages can be performed in sequence. By using the Bank 2 registers, each stage can be uniquely configured to support multiple capacitance sensor interface requirements. For example, a slider sensor can be assigned to STAGE1 with a button sensor assigned to STAGE2.

The AD7142 on-chip sequence controller provides conversion control beginning with STAGE0. Figure 22 shows a block diagram of the CDC conversion stages and CIN inputs. A conversion sequence is defined as a sequence of CDC conversions starting at STAGE0 and ending at the stage determined by the value programmed in the SEQUENCE\_STAGE\_NUM register. Depending on the number and type of capacitance sensors that are used, not all conversion stages are required. Use the SEQUENCE\_STAGE\_NUM register to set the number of conversions in one sequence, depending on the sensor interface requirements. For example, this register would be set to 5 if the CIN inputs were mapped to only six stages. In addition, set the STAGE\_CAL\_EN registers according to the number of stages that are used.

The number of required conversion stages depends completely on the number of sensors attached to the AD7142. Figure 23 shows how many conversion stages are required for each sensor, and how many inputs each sensor requires to the AD7142.

Figure 23. Sequencer Setup for Sensors

A button sensor generally requires one sequencer stage; however, it is possible to configure two button sensors to operate differentially. Only one button from the pair can be activated at a time; pressing both buttons together results in neither button being activated. This configuration requires one conversion stage. A scroll bar sensor requires eight stages. The result from each stage is used by the host software to determine the user's position on the scroll bar. The algorithm that performs this process is available from Analog Devices free of charge, on signing a software license. Scroll wheels also require eight stages.

The 8-way switch is made from two pairs of differential buttons. It, therefore, requires two conversion stages, one for each of the differential button pairs. It also requires a stage to measure whether the sensor is active. The buttons are orientated so that one pair makes up the top and bottom portions of the 8-way switch; the other pair makes up the left and right portions of the 8-way switch.

### **CDC CONVERSION SEQUENCE TIME**

The time required for one complete measurement for all 12 stages by the CDC is defined as the CDC conversion sequence time. The SEQUENCE\_STAGE\_NUM register and DECIMATION register determine the conversion time as listed in Table 10.

|                    | Conversion Time (ms) |                     |  |  |

|--------------------|----------------------|---------------------|--|--|

| SEQUENCE_STAGE_NUM | DECIMATION<br>= 128  | DECIMATION<br>= 256 |  |  |

| 0                  | 1.536                | 3.072               |  |  |

| 1                  | 3.072                | 6.144               |  |  |

| 2                  | 4.608                | 9.216               |  |  |

| 3                  | 6.144                | 12.288              |  |  |

| 4                  | 7.68                 | 15.36               |  |  |

| 5                  | 9.216                | 18.432              |  |  |

| 6                  | 10.752               | 21.504              |  |  |

| 7                  | 12.288               | 24.576              |  |  |

| 8                  | 13.824               | 27.648              |  |  |

| 9                  | 15.36                | 30.72               |  |  |

| 10                 | 16.896               | 33.792              |  |  |

| 11                 | 18.432               | 36.864              |  |  |

For example, while operating with a decimation rate of 128, if the SEQUENCE\_STAGE\_NUM register is set to 5 for the conversion of six stages in a sequence, the conversion sequence time is 9.216 ms.

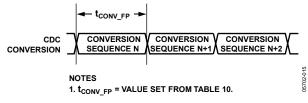

#### Full Power Mode CDC Conversion Sequence Time

The full power mode CDC conversion sequence time for all 12 stages is set by configuring the SEQUENCE\_STAGE\_NUM register, and DECIMATION register as outlined in Table 10.

Figure 24 shows a simplified timing diagram of the full power CDC conversion time. The full power mode CDC conversion time  $t_{\text{CONV}\_FP}$  is set using Table 10.

Figure 24. Full Power Mode CDC Conversion Sequence Time

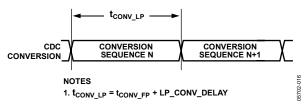

# Low Power Mode CDC Conversion Sequence Time with Delay

The frequency of each CDC conversion while operating in the low power automatic wake up mode is controlled by using the LP\_CONV\_DELAY register located at Address 0x000[3:2], in addition to the registers listed in Table 10. This feature provides some flexibility for optimizing the conversion time to meet system requirements vs. AD7142 power consumption.

For example, maximum power savings is achieved when the LP\_CONV\_DELAY register is set to 3. With a setting of 3, the AD7142 automatically wakes up, performing a conversion every 800 ms.

| Table 11. LP_CONV_DELAT Settings |                           |  |  |  |

|----------------------------------|---------------------------|--|--|--|

| LP_CONV_DELAY Bits               | Delay Between Conversions |  |  |  |

| 00                               | 200 ms                    |  |  |  |

| 01                               | 400 ms                    |  |  |  |

| 10                               | 600 ms                    |  |  |  |

| 11                               | 800 ms                    |  |  |  |

Table 11. LP\_CONV\_DELAY Settings

Figure 25 shows a simplified timing example of the low power CDC conversion time. As shown, the low power CDC conversion time is set by  $t_{CONV\_FP}$  and the LP\_CONV\_DELAY register.

Figure 25. Low Power Mode CDC Conversion Sequence Time

### CDC CONVERSION RESULTS

Certain high resolution sensors require the host to read back the CDC conversion results for processing. The registers required for host processing are located in the Bank 3 registers. The host processes the data readback from these registers using a software algorithm, to determine position information.

In addition to the results registers in the Bank 3 registers, the AD7142 provides the 16-bit CDC output data directly, starting at Address 0x00B of Bank 1. Reading back the CDC 16-bit conversion data register allows for customer-specific application data processing.

# NONCONTACT PROXIMITY DETECTION

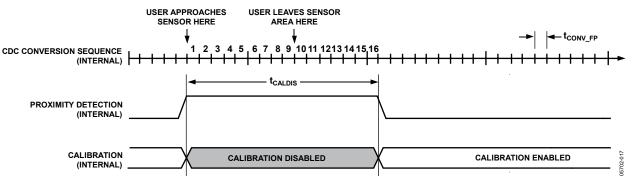

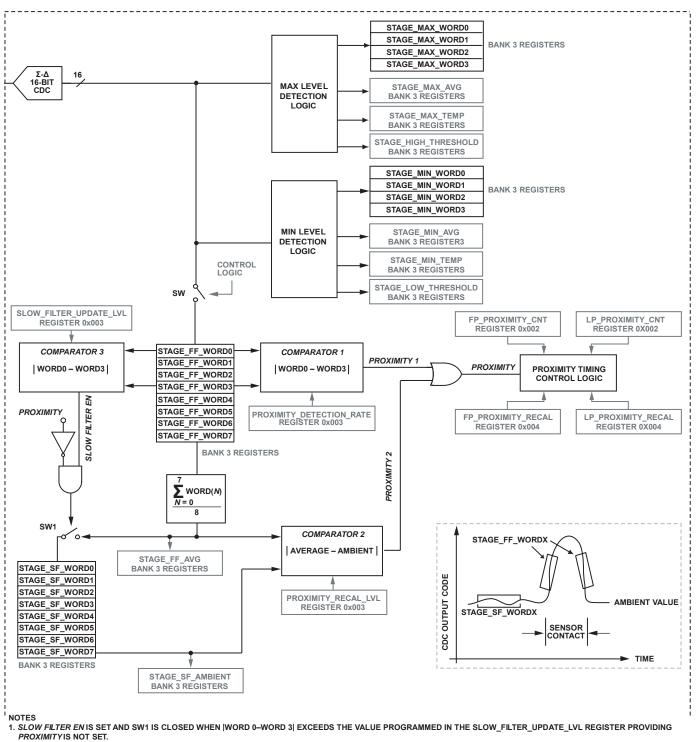

The AD7142 internal signal processing continuously monitors all capacitance sensors for noncontact proximity detection. This feature provides the ability to detect when a user is approaching a sensor, at which time all internal calibration is immediately disabled while the AD7142 is automatically configured to detect a valid contact.

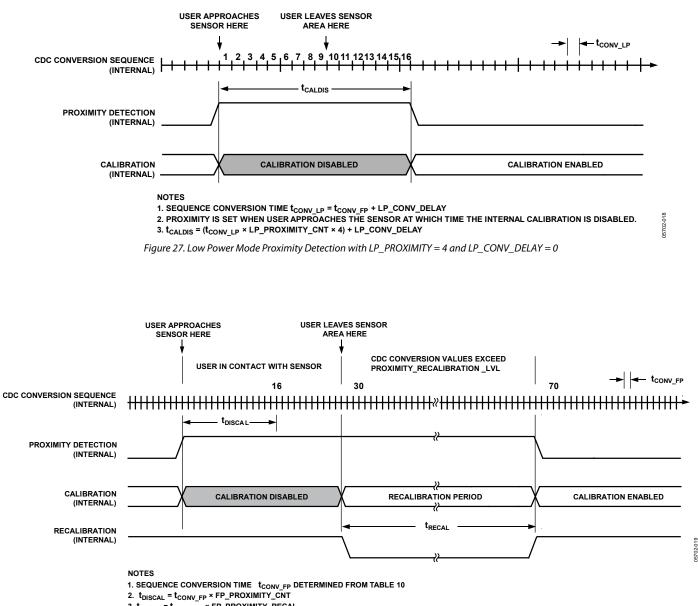

The proximity control register bits are described in Table 12. The FP\_PROXIMITY\_CNT register bits and LP\_PROXIMITY\_CNT register bits control the length of the calibration disable period after proximity is detected. The calibration is disabled during this time and enabled again at the end of this period provided that the user is no longer approaching, or in contact with, the sensor. Figure 26 and Figure 27 show examples of how these registers are used to set the full and low power mode calibration disable periods.

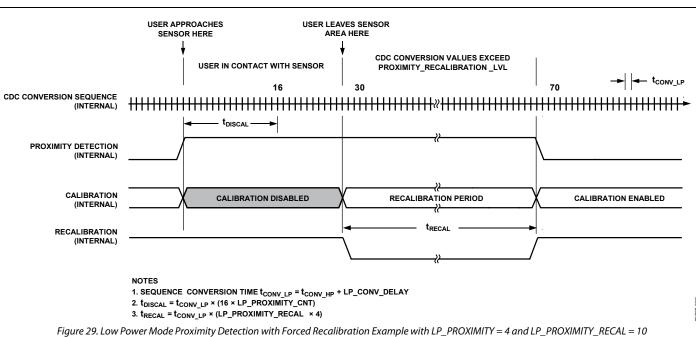

### RECALIBRATION

In the event of a very long proximity detection event, such as a user hovering over a sensor for a long period of time, the FP\_PROXIMITY\_RECAL Bits[9:0] and LP\_PROXIMITY\_RECAL Bits[15:10] in Register 0x004 can be applied to force a recalibration. This ensures that the ambient values are recalibrated regardless of how long the user hovers over a sensor. A recalibration ensures maximum AD7142 sensor performance. Figure 28 and Figure 29 show examples of using the FP\_PROXIMITY\_RECAL and

Table 12. Proximity Control Registers (See Figure 30)

LP\_PROXIMITY\_RECAL register bits to force a recalibration while operating in the full and low power modes. These figures show a user approaching a sensor followed by the user leaving the sensor while the proximity detection remains active after the user leaves the sensor. This situation could occur if the user interaction creates some moisture on the sensor causing the new sensor value to be different from the expected value. In this case, the internal recalibration is applied to automatically recalibrate the sensor. The force recalibration event takes two interrupt cycles, therefore it should not be set again during this interval.

### **PROXIMITY SENSITIVITY**

Figure 30 describes the two conditions that set the internal proximity detection signal using Comparator 1 and Comparator 2. Comparator 1 detects when a user is approaching a sensor. The PROXIMITY\_DETECTION\_RATE register controls the sensitivity of Comparator 1. For example, if PROXIMITY\_DETECTION\_RATE is set to 4, the Proximity 1 signal is set when the absolute difference between WORD1 and WORD3 exceeds four LSB codes. Comparator 2 detects when a user hovers over a sensor or approaches a sensor very slowly. The PROXIMITY\_RECAL\_LVL register (Address 0x003) controls the sensitivity of Comparator 2. For example, if PROXIMITY\_RECAL\_LVL is set to 75, the Proximity 2 signal is set when the absolute difference between the fast filter average value and the ambient value exceeds 75 LSB codes.

| Register                 | Length | Register Address                                      | Description                                    |  |  |

|--------------------------|--------|-------------------------------------------------------|------------------------------------------------|--|--|

| FP_PROXIMITY_CNT         | 4 bits | 0x002                                                 | Full power mode proximity control              |  |  |

| LP_PROXIMITY_CNT         | 4 bits | bits 0x002 Low power mode proximity control           |                                                |  |  |

| FP_PROXIMITY_RECAL       | 8 bits | 0x004 Full power mode proximity recalibration control |                                                |  |  |

| LP_PROXIMITY_RECAL       | 6 bits | 0x004                                                 | Low power mode proximity recalibration control |  |  |

| PROXIMITY_RECAL_LVL      | 8 bits | 0x003                                                 | Proximity recalibration level                  |  |  |

| PROXIMITY_DETECTION_RATE | 6 bits | 0x003                                                 | Proximity detection rate                       |  |  |

Figure 26. Full Power Mode Proximity Detection Example with FP\_PROXIMITY = 1

3.  $t_{RECAL} = t_{CONV_{FP}} \times FP_{PROXIMITY_RECAL}$

Figure 28. Full Power Mode Proximity Detection with Forced Recalibration Example with FP\_PROXIMITY = 1 and FP\_PROXIMITY\_RECAL = 40

05702-020

### **FIFO CONTROL**

As shown in Figure 30, there are a number of FIFOs implemented on the AD7142. These FIFOs are located in Bank 3 of the on-chip memory. The FIFOs are used by the on-chip logic to run the environmental calibration, adaptive threshold, and proximity algorithms.

### AVG\_FP\_SKIP and AVG\_LP\_SKIP

In Register 0x001, Bits[13:12]are the slow FIFO skip control for full power mode, AVG\_FP\_SKIP. Bits[15:14] in the same register are the slow FIFO skip control for low power mode, AVG\_LP\_SKIP. These values determine which CDC samples are not used (skipped) in the slow FIFO. Changing theses values slows down or speeds up the rate at which the ambient capacitance value tracks the measured capacitance value read by the converter.

The slow FIFO is used by the on-chip logic to track the ambient capacitance value. The slow FIFO expects to receive samples from the converter at a rate of 33 ms to 40 ms. AVG\_FP\_SKIP and AVG\_LP\_SKIP are used to normalize the frequency of the samples going into the FIFO, regardless of how many conversion stages are in a sequence.

Determining the AVG\_FP\_SKIP and AVG\_LP\_SKIP value is only required once during the initial setup of the capacitance sensor interface. Recommended values for these settings when using all 12 conversion stages on the AD7142 are:

AVG\_FP\_SKIP = 11 = skip 31 samples

AVG\_LP\_SKIP = 11 = skip 3 samples

#### FF\_SKIP\_CNT

In Register 0x02, Bits[3:0] are the fast filter skip control, FF\_SKIP\_CNT. This value determines which CDC samples are not used (skipped) in the proximity detection fast FIFO.

The proximity detection fast FIFO is used by the on-chip logic to determine if proximity is detected . The fast FIFO expects to receive samples from the converter at a set rate. FF\_SKIP\_CNT is used to normalize the frequency of the samples going into the FIFO, regardless of how many conversion stages are in a sequence.

Determining the FF\_SKIP\_CNT value is required only once during the initial setup of the capacitance sensor interface. Table 13 shows how FF\_SKIP\_CNT controls the update rate to the fast FIFO. Recommended value for this setting when using all 12 conversion stages on the AD7142 is:

FF\_SKIP\_CNT = 0000 = no samples skipped

| FF_SKIP_CNT | FAST FIFO Update Rate                |                                      |  |  |  |  |

|-------------|--------------------------------------|--------------------------------------|--|--|--|--|

|             | DECIMATION = 128                     | DECIMATION = 256                     |  |  |  |  |

| 0           | 1.536 × (SEQUENCE_STAGE_NUM + 1) ms  | 3.072 × (SEQUENCE_STAGE_NUM + 1) ms  |  |  |  |  |

| 1           | 3.072 × (SEQUENCE_STAGE_NUM + 1) ms  | 6.144 × (SEQUENCE_STAGE_NUM + 1) ms  |  |  |  |  |

| 2           | 4.608 × (SEQUENCE_STAGE_NUM + 1) ms  | 9.216 × (SEQUENCE_STAGE_NUM + 1) ms  |  |  |  |  |

| 3           | 6.144 × (SEQUENCE_STAGE_NUM + 1) ms  | 12.288 × (SEQUENCE_STAGE_NUM + 1) ms |  |  |  |  |

| 4           | 7.68 × (SEQUENCE_STAGE_NUM + 1) ms   | 15.36 × (SEQUENCE_STAGE_NUM + 1) ms  |  |  |  |  |

| 5           | 9.216 × (SEQUENCE_STAGE_NUM + 1) ms  | 18.432 × (SEQUENCE_STAGE_NUM + 1) ms |  |  |  |  |

| 6           | 10.752 × (SEQUENCE_STAGE_NUM + 1) ms | 21.504 × (SEQUENCE_STAGE_NUM + 1) ms |  |  |  |  |

| 7           | 12.288 × (SEQUENCE_STAGE_NUM + 1) ms | 24.576 × (SEQUENCE_STAGE_NUM + 1) ms |  |  |  |  |

| 8           | 13.824 × (SEQUENCE_STAGE_NUM + 1) ms | 27.648 × (SEQUENCE_STAGE_NUM + 1) ms |  |  |  |  |

| 9           | 15.36 × (SEQUENCE_STAGE_NUM + 1) ms  | 30.72 × (SEQUENCE_STAGE_NUM + 1) ms  |  |  |  |  |

| 10          | 16.896 × (SEQUENCE_STAGE_NUM + 1) ms | 33.792 × (SEQUENCE_STAGE_NUM + 1) ms |  |  |  |  |

| 11          | 18.432 × (SEQUENCE_STAGE_NUM + 1) ms | 36.864 × (SEQUENCE_STAGE_NUM + 1) ms |  |  |  |  |

| 12          | 19.968 × (SEQUENCE_STAGE_NUM + 1) ms | 39.936 × (SEQUENCE_STAGE_NUM + 1) ms |  |  |  |  |

| 13          | 21.504 × (SEQUENCE_STAGE_NUM + 1) ms | 43.008 × (SEQUENCE_STAGE_NUM + 1) ms |  |  |  |  |

| 14          | 23.04 × (SEQUENCE_STAGE_NUM + 1) ms  | 46.08 × (SEQUENCE_STAGE_NUM + 1) ms  |  |  |  |  |

| 15          | 24.576 × (SEQUENCE_STAGE_NUM + 1) ms | 49.152 × (SEQUENCE_STAGE_NUM + 1) ms |  |  |  |  |

#### Table 13. FF\_SKIP\_CNT Settings

2. PROXIMITY 1 IS SET WHEN |WORD 0-WORD 3| EXCEEDS THE VALUE PROGRAMMED IN THE PROXIMITY\_DETECTION\_RATE REGISTER.

3. PROXIMITY 2 IS SET WHEN AVERAGE-AMBIENT EXCEEDS THE VALUE PROGRAMMED IN THE PROXIMITY\_RECAL\_LVL REGISTER.

4. DESCRIPTION OF COMPARATOR FUNCTIONS:

COMPARATOR 1: USED TO DETECT WHEN A USER IS APPROACHING OR LEAVING A SENSOR.

COMPARATOR 2: USED TO DETECT WHEN A USER IS HOVERING OVER A SENSOR, OR APPROACHING A SENSOR VERY SLOWLY. ALSO USED TO DETECT IF THE SENSOR AMBIENT LEVEL HAS CHANGED AS A RESULT OF THE USER INTERACTION.

FOR EXAMPLE, HUMIDITY OR DIRT LEFT BEHIND ON SENSOR.

COMPARATOR 3: USED TO ENABLE THE SLOW FILTER UPDATE RATE. THE SLOW FILTER IS UPDATED WHEN SLOW FILTER EN IS SET AND PROXIMITY IS NOT SET.

Figure 30. AD7142 Proximity Detection and Environmental Calibration

# **ENVIRONMENTAL CALIBRATION**

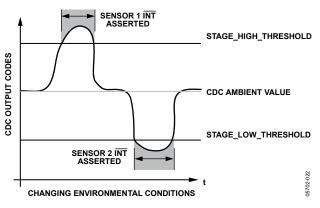

The AD7142 provides on-chip capacitance sensor calibration to automatically adjust for environmental conditions that have an effect on the capacitance sensor ambient levels. Capacitance sensor output levels are sensitive to temperature, humidity, and in some cases, dirt. The AD7142 achieves optimal and reliable sensor performance by continuously monitoring the CDC ambient levels and correcting for any changes by adjusting the STAGE\_HIGH\_THRESHOLD and STAGE\_LOW\_ THRESHOLD register values. The CDC ambient level is defined as the capacitance sensor output level during periods when the user is not approaching or in contact with the sensor.

The compensation logic runs automatically on every conversion after configuration when the AD7142 is not being touched. This allows the AD7142 to account for rapidly changing environmental conditions.

The ambient compensation control registers give the host access to general setup and controls for the compensation algorithm. The RAM stores the compensation data for each conversion stage, as well as setup information specific to each stage.

Figure 31 shows an example of an ideal capacitance sensor behavior where the CDC ambient level remains constant regardless of the environmental conditions. The CDC output shown is for a pair of differential button sensors, where one sensor caused an increase, and the other a decrease in measured capacitance when activated. The positive and negative sensor threshold levels are calculated as a percentage of the STAGE\_OFFSET\_HIGH and STAGE\_OFFSET\_LOW values based on the threshold sensitivity settings and the ambient value. These values are sufficient to detect a sensor contact, resulting with the AD7142 asserting the INT output when the threshold levels are exceeded.

Figure 31. Ideal Sensor Behavior with a Constant Ambient Level

# CAPACITANCE SENSOR BEHAVIOR WITHOUT CALIBRATION

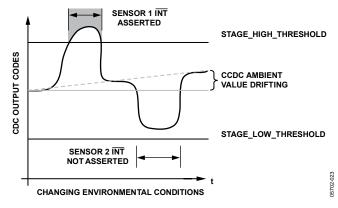

Figure 32 shows the typical behavior of a capacitance sensor with no applied calibration. This figure shows ambient levels drifting over time as environmental conditions change. The ambient level drift has resulted in the detection of a missed user contact on Sensor 2. This is a result of the initial low offset level remaining constant while the ambient levels drifted upward beyond the detection range.

The Capacitance Sensor Behavior with Calibration section describes how the AD7142 adaptive calibration algorithm prevents errors such as this from occurring.

Figure 32. Typical Sensor Behavior Without Calibration Applied

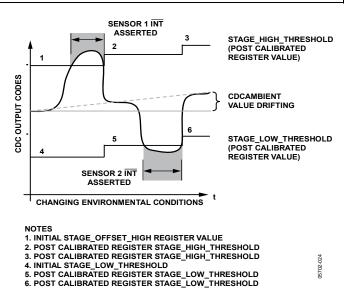

# CAPACITANCE SENSOR BEHAVIOR WITH CALIBRATION

The AD7142 on-chip adaptive calibration algorithm prevents sensor detection errors such as the one shown in Figure 32. This is achieved by monitoring the CDC ambient levels and internally adjusting the initial offset level register values according to the amount of ambient drift measured on each sensor. This closed loop routine ensures the reliability and repeatable operation of every sensor connected to the AD7142 under dynamic environmental conditions. Figure 33 shows a simplified example of how the AD7142 applies the adaptive calibration process resulting in no interrupt errors under changing CDC ambient levels due to environmental conditions.

Figure 33. Typical Sensor Behavior with Calibration Applied on the Data Path

# ADAPTIVE THRESHOLD AND SENSITIVITY

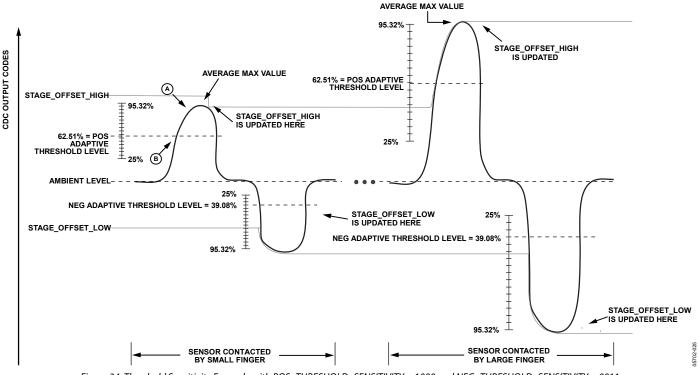

The AD7142 provides an on-chip self-learning adaptive threshold and sensitivity algorithm. This algorithm continuously monitors the output levels of each sensor and automatically rescales the threshold levels proportionally to the sensor area covered by the user. As a result, the AD7142 maintains optimal threshold and sensitivity levels for all types of users regardless of their finger sizes.

The threshold level is always referenced from the ambient level and is defined as the CDC converter output level that must be exceeded for a valid sensor contact. The sensitivity level is defined as how sensitive the sensor is before a valid contact is registered.

Figure 34 provides an example of how the adaptive threshold and sensitivity algorithm works. The positive and negative sensor threshold levels are calculated as a percentage of the STAGE\_OFFSET\_HIGH and STAGE\_OFFSET\_LOW values based on the threshold sensitivity settings and the ambient value. On configuration, initial estimates are supplied for both STAGE\_OFFSET\_HIGH and STAGE\_OFFSET\_LOW after which the calibration engine automatically adjusts the STAGE\_HIGH\_THRESHOLD and STAGE\_LOW \_THRESHOLD values for sensor response.

Reference A in Figure 34 shows an under sensitive threshold level for a small finger user, demonstrating the disadvantages of a fixed threshold level. By enabling the adaptive threshold and sensitivity algorithm, the positive and negative threshold levels are determined by the POS\_THRESHOLD\_SENSITIVITY and NEG\_THRESHOLD\_ SENSITIVITY register values and the most recent average maximum sensor output value. These registers can be used to select 16 different positive and negative sensitivity levels ranging between 25% and 95.32% of the most recent average maximum output level referenced from the ambient value. The smaller the sensitivity percentage setting, the easier it is to trigger a sensor activation. Reference B shows that the positive adaptive threshold level is set at almost midsensitivity with a 62.51% threshold level by setting POS\_THRESHOLD\_ SENSITIVITY = 1000. Figure 34 also provides a similar example for the negative threshold level with NEG\_THRESHOLD\_SENSITIVITY = 0001.

Figure 34. Threshold Sensitivity Example with POS\_THRESHOLD\_SENSITIVITY = 1000 and NEG\_THRESHOLD\_SENSITIVITY = 0011

## **INTERRUPT OUTPUT**

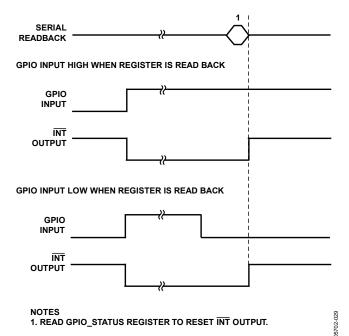

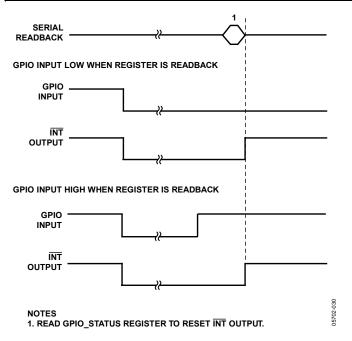

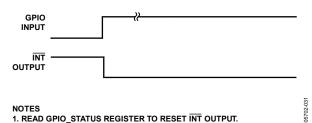

The AD7142 has an interrupt output that triggers an interrupt service routine on the host processor. The  $\overline{INT}$  signal is on Pin 25, and is an open-drain output. There are three types of interrupt events on the AD7142: a CDC conversion complete interrupt, a sensor threshold interrupt, and a GPIO interrupt. Each interrupt has enable and status registers. The conversion complete and sensor threshold interrupts can be enabled on a per conversion stage basis. The status registers indicate what type of interrupt triggered the  $\overline{INT}$  pin. Status registers are cleared, and the  $\overline{INT}$  signal is reset high, during a read operation. The signal returns high as soon as the read address has been set up.

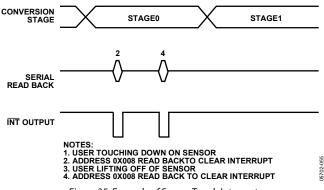

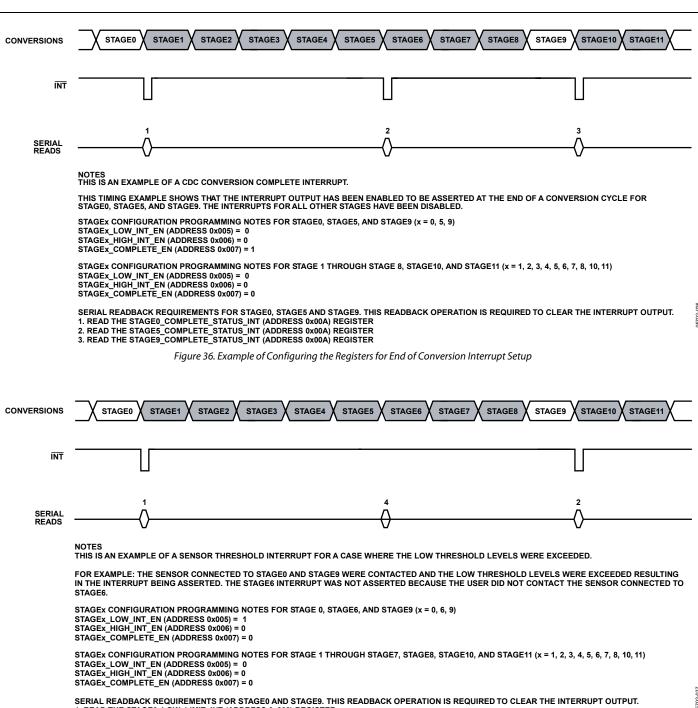

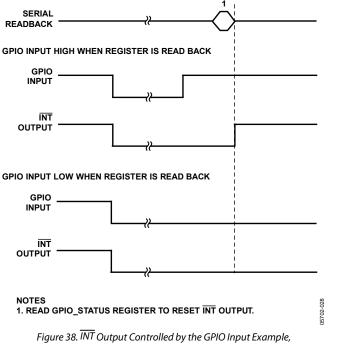

### **CDC CONVERSION COMPLETE INTERRUPT**

The AD7142 interrupt signal asserts low to indicate the completion of a conversion stage, and new conversion result data is available in the registers.