# 16Mx72 Registered DDR SDRAM FEATURES

- Registered for enhanced performance of bus speeds of 200, 225, and 250 MHz

- Package:

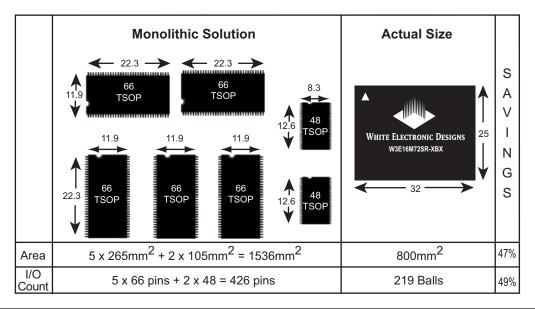

- 219 Plastic Ball Grid Array (PBGA), 32 x 25mm

- 2.5V ±0.2V core power supply

- 2.5V I/O (SSTL 2 compatible)

- Differential clock inputs (CK and CK#)

- Commands entered on each positive CK edge

- Internal pipelined double-data-rate (DDR) architecture; two data accesses per clock cycle

- Programmable Burst length: 2,4 or 8

- Bidirectional data strobe (DQS) transmitted/ received with data, i.e., source-synchronous data capture (one per byte)

- DQS edge-aligned with data for READs; centeraligned with data for WRITEs

- DLL to align DQ and DQS transitions with CK

- Four internal banks for concurrent operation

- Two data mask (DM) pins for masking write data

- Programmable loL/loн option

- Auto precharge option

- Auto Refresh and Self Refresh Modes

- Commercial, Industrial and Military Temperature Ranges

- Organized as 16M x 72

- Weight: W3E16M72SR-XBX 2.5 grams typical

#### **BENEFITS**

- 47% SPACE SAVINGS

- Glueless Connection to PCI Bridge/Memory Controller

- Reduced part count

- Reduced I/O count

- 49% I/O Reduction

- Reduced trace lengths for lower parasitic capacitance

- Suitable for hi-reliability applications

- Laminate interposer for optimum TCE match

- Upgradeable to 32M x 72 density (contact factory for information)

<sup>\*</sup> This product is subject to change without notice.

## FIGURE 1 - PIN CONFIGURATION

Top View

| ·OP | *1011 |  |

|-----|-------|--|

|     |       |  |

|     |       |  |

|   | 4    | 0          | 0    | 4    | _               | 0    | 7             | 0      | 0      | 40   | 44    | 40              | 40              | 4.4             | 45      | 40    |

|---|------|------------|------|------|-----------------|------|---------------|--------|--------|------|-------|-----------------|-----------------|-----------------|---------|-------|

| Г | 1    | 2          | 3    | 4    | 5               | 6    | 7             | 8      | 9      | 10   | 11    | 12              | 13              | 14              | 15      | 16    |

| Α |      | (DQ0)      | DQ14 | DQ15 | Vss             | Vss  | (A9)          | (A10)  | (A11)  | (A8) | Vccq  | Vccq            | DQ16            | DQ17            | DQ31    | VSS   |

| В | DQ1  | DQ2        | DQ12 | DQ13 | $\sqrt{V_{SS}}$ | Vss  | $\bigcirc$ A0 | (A7)   | (A6)   | (A1) | Vcc   | Vcc             | DQ18            | DQ19            | DQ29    | DQ30  |

| С | DQ3  | DQ4        | DQ10 | DQ11 | Vcc             | Vcc  | (A2)          | (A5)   | (A4)   | (A3) | Vss   | $\sqrt{V_{SS}}$ | DQ20            | DQ21            | DQ27    | DQ28  |

| D | DQ6  | DQ5        | DQ8  | DQ9  | Vccq            | Vccq | (A12)         | DNU    | DNU    | DNU  | Vss   | $\sqrt{V_{SS}}$ | DQ22            | DQ23            | DQ26    | DQ25  |

| Е | DQ7  | (DM0)      | Vcc  | DM1  | DQS7            | DQSO | DQS1)         | BAO    | (BA1)  | DQS2 | DQS3  | VREF            | DM2             | Vss             | NC      | DQ24  |

| F | CAS# | WE#        | Vcc  | СКО  | DQS6            |      |               |        |        |      |       | RCK0            | RCK0B           | Vss             | DM3     | CK1   |

| G | CS#  | (RAS#)     | Vcc  | CKE  | CK0#            |      |               |        |        |      |       | RCK1            | RCK1B           | Vss             | CK1#    | NC    |

| Н | Vss  | Vss        | Vcc  | Vccq | $\sqrt{V_{SS}}$ |      |               |        |        |      |       | Vcc             | Vss             | $\sqrt{V_{SS}}$ | Vccq    | Vcc   |

| J | Vss  | $(V_{SS})$ | Vcc  | Vccq | $\sqrt{V_{SS}}$ |      |               |        |        |      |       | Vcc             | $\sqrt{V_{SS}}$ | Vss             | Vccq    | Vcc   |

| K | CK3# | NC         | Vcc  | NC   | DQS8            |      |               |        |        |      |       | CK2#            | NC              | Vss             | NC      | NC    |

| L | NC   | CK3        | Vcc  | NC   | NC              |      |               |        |        |      |       | DQS4            | CK2             | Vss             | RESET#) | RVREF |

| М | DQ56 | DM7        | Vcc  | NC   | DM6             | NC   | DM9           | CK4    | NC     | NC   | NC    | NC              | DM5             | Vss             | DM4     | DQ39  |

| N | DQ57 | DQ58       | DQ55 | DQ54 | DQS9            | CK4# | DQ73          | DQ72   | DQ71   | DQ70 | (DM8) | DQS5            | DQ41            | DQ40            | DQ37    | DQ38  |

| Р | DQ60 | (DQ59)     | DQ53 | DQ52 | Vss             | Vss  | DQ75          | DQ74   | DQ69   | DQ68 | Vcc   | Vcc             | DQ43            | DQ42            | DQ36    | DQ35  |

| R | DQ62 | DQ61       | DQ51 | DQ50 | Vcc             | Vcc  | DQ77          | DQ76   | DQ67   | DQ66 | Vss   | Vss             | DQ45            | DQ44            | DQ34    | DQ33  |

| Т | Vss  | DQ63       | DQ49 | DQ48 | Vccq            | Vccq | DQ79          | (DQ78) | (DQ65) | DQ64 | Vss   | Vss             | DQ47            | DQ46            | DQ32    | Vcc   |

NOTE: DNU = Do Not Use; to be left unconnected for future upgrades. Pin D8 will be A13, D9 will be A14, and D10 will be A15 as needed. NC = Not Connected Internally.

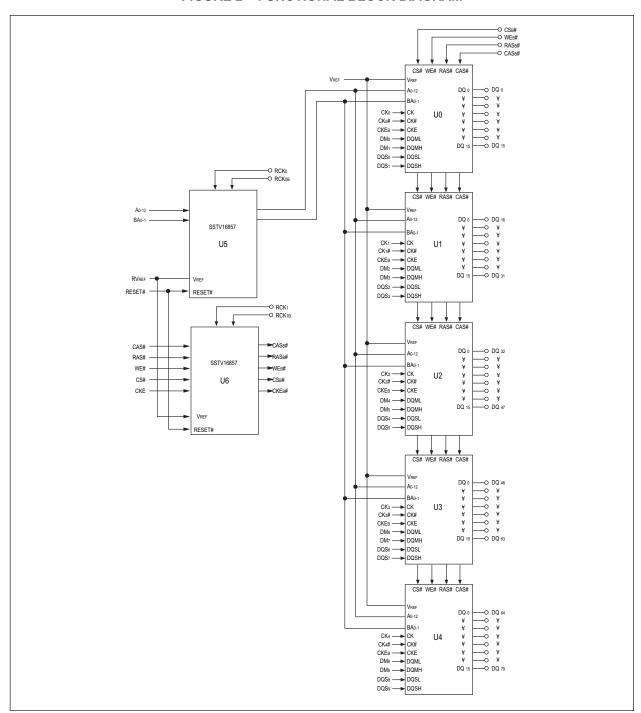

#### FIGURE 2 - FUNCTIONAL BLOCK DIAGRAM

## **GENERAL DESCRIPTION**

The 128MByte (1Gb) DDR SDRAM is a high-speed CMOS, dynamic random-access, memory using 5 chips containing 268,435,456 bits. Each chip is internally configured as a quad-bank DRAM. Each of the chip's 67,108,864-bit banks is organized as 8,192 rows by 512 columns by 16 bits.

The 128 MB DDR SDRAM uses a double data rate architecture to achieve high-speed operation. The double data rate architecture is essentially a 2n-prefetch architecture with an interface designed to transfer two data words per clock cycle at the I/O pins. A single read or write access for the 128MB DDR SDRAM effectively consists of a single 2n-bit wide, one-clock-cycle data tansfer at the internal DRAM core and two corresponding n-bit wide, one-half-clock-cycle data transfers at the I/O pins.

A bidirectional data strobe (DQS) is transmitted externally, along with data, for use in data capture at the receiver. DQS is a strobe transmitted by the DDR SDRAM during READs and by the memory contoller during WRITEs. DQS is edgealigned with data for READs and center-aligned with data for WRITEs. Each chip has two data strobes, one for the lower byte and one for the upper byte.

The 128MB DDR SDRAM operates from a differential clock (CK and CK#); the crossing of CK going HIGH and CK# going LOW will be referred to as the positive edge of CK. Commands (address and control signals) are registered at every positive edge of CK. Input data is registered on both edges of DQS, and output data is referenced to both edges of DQS, as well as to both edges of CK.

Read and write accesses to the DDR SDRAM are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of an ACTIVE command, which is then followed by a READ or WRITE command. The address bits registered coincident with the ACTIVE command are used to select the bank and row to be accessed. The address bits registered coincident with the READ or WRITE command are used to select the bank and the starting column location for the burst access.

The DDR SDRAM provides for programmable READ or WRITE burst lengths of 2, 4, or 8 locations. An auto precharge function may be enabled to provide a self-timed row precharge that is initiated at the end of the burst access.

The pipelined, multibank architecture of DDR SDRAMs allows for concurrent operation, thereby providing high effective bandwidth by hiding row precharge and activation time

An auto refresh mode is provided, along with a power-saving power-down mode.

## FUNCTIONAL DESCRIPTION

Read and write accesses to the DDR SDRAM are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of an ACTIVE command which is then followed by a READ or WRITE command. The address bits registered coincident with the ACTIVE command are used to select the bank and row to be accessed (BA0 and BA1 select the bank, A0-12 select the row). The address bits registered coincident with the READ or WRITE command are used to select the starting column location for the burst access.

Prior to normal operation, the SDRAM must be initialized. The following sections provide detailed information covering device initialization, register definition, command descriptions and device operation.

#### INITIALIZATION

DDR SDRAMs must be powered up and initialized in a predefined manner. Operational procedures other than those specified may result in undefined operation. Power must first be applied to Vcc and Vccq simultaneously, and then to VREF (and to the system VTT). VTT must be applied after V<sub>CCQ</sub> to avoid device latch-up, which may cause permanent damage to the device. VREF can be applied any time after Vccq but is expected to be nominally coincident with V<sub>TT</sub>. Except for CKE, inputs are not recognized as valid until after VREF is applied. CKE is an SSTL 2 input but will detect an LVCMOS LOW level after Vcc is applied. Maintaining an LVCMOS LOW level on CKE during powerup is required to ensure that the DQ and DQS outputs will be in the High-Z state, where they will remain until driven in normal operation (by a read access). After all power supply and reference voltages are stable, and the clock is stable, the DDR SDRAM requires a 200µs delay prior to applying an executable command.

Once the 200µs delay has been satisfied, a DESELECT or NOP command should be applied, and CKE should be brought HIGH. Following the NOP command, a PRECHARGE ALL command should be applied. Next a LOAD MODE REGISTER command should be issued for the extended mode register (BA1 LOW and BA0 HIGH) to enable the DLL, followed by another LOAD MODE REGISTER command to the mode register (BA0/BA1 both LOW) to reset the DLL and to program the operating parameters. Two-hundred clock cycles are required between the DLL reset and any READ command. A PRECHARGE ALL command should then be applied, placing the device in the all banks idle state.

Once in the idle state, two AUTO REFRESH cycles must be performed (trace must be satisfied.) Additionally, a LOAD MODE REGISTER command for the mode register with the reset DLL bit deactivated (i.e., to program operating parameters without resetting the DLL) is required. Following these requirements, the DDR SDRAM is ready for normal operation.

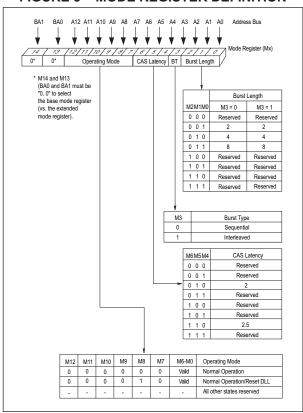

## REGISTER DEFINITION

#### MODE REGISTER

The Mode Register is used to define the specific mode of operation of the DDR SDRAM. This definition includes the selection of a burst length, a burst type, a CAS latency, and an operating mode, as shown in Figure 3. The Mode Register is programmed via the MODE REGISTER SET command (with BA0 = 0 and BA1 = 0) and will retain the stored information until it is programmed again or the device loses power. (Except for bit A8 which is self clearing).

Reprogramming the mode register will not alter the contents of the memory, provided it is performed correctly. The Mode Register must be loaded (reloaded) when all banks are idle and no bursts are in progress, and the controller must wait the specified time before initiating the subsequent operation. Violating either of these requirements will result in unspecified operation.

Mode register bits A0-A2 specify the burst length, A3 specifies the type of burst (sequential or interleaved), A4-A6 specify the CAS latency, and A7-A12 specify the operating mode.

#### **BURST LENGTH**

Read and write accesses to the DDR SDRAM are burst oriented, with the burst length being programmable, as shown in Figure 3. The burst length determines the maximum number of column locations that can be accessed for a given READ or WRITE command. Burst lengths of 2, 4 or 8 locations are available for both the sequential and the interleaved burst types.

Reserved states should not be used, as unknown operation or incompatibility with future versions may result.

When a READ or WRITE command is issued, a block of columns equal to the burst length is effectively selected. All accesses for that burst take place within this block, meaning that the burst will wrap within the block if a boundary is reached. The block is uniquely selected by A1-Ai when the burst length is set to two; by A2-Ai when the burst length is set to four (where Ai is the most significant column address for a given configuration); and by A3-Ai when the burst length is set to eight. The remaining (least significant) address bit(s) is (are) used to select the starting location within the block. The programmed burst length applies to both READ and WRITE bursts.

## **BURST TYPE**

Accesses within a given burst may be programmed to be either sequential or interleaved; this is referred to as the burst type and is selected via bit M3.

The ordering of accesses within a burst is determined by the burst length, the burst type and the starting column address, as shown in Table 1.

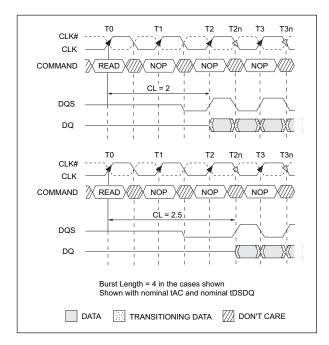

## READ LATENCY

The READ latency is the delay, in clock cycles, between the registration of a READ command and the availability of the first bit of output data. The latency can be set to 2 or 2.5 clocks.

If a READ command is registered at clock edge n, and the latency is m clocks, the data will be available by clock edge n+m. Table 2 below indicates the operating frequencies at which each CAS latency setting can be used.

Reserved states should not be used as unknown operation or incompatibility with future versions may result.

#### TABLE 2 - CAS LATENCY

|       | ALLOWABLE OPERATING<br>FREQUENCY (MHz) |                      |  |  |  |

|-------|----------------------------------------|----------------------|--|--|--|

| SPEED | CAS<br>LATENCY = 2                     | CAS<br>LATENCY = 2.5 |  |  |  |

| -200  | ≤ 75                                   | ≤ 100                |  |  |  |

| -225  | ≤ 100                                  | ≤ 112.5              |  |  |  |

| -250  | ≤ 100                                  | ≤ 125                |  |  |  |

#### **OPERATING MODE**

The normal operating mode is selected by issuing a MODE REGISTER SET command with bits A7-A12 each set to zero, and bits A0-A6 set to the desired values. A DLL reset is initiated by issuing a MODE REGISTER SET command with bits A7 and A9-A12 each set to zero, bit A8 set to one, and bits A0-A6 set to the desired values. Although not required, JEDEC specifications recommend when a LOAD MODE REGISTER command is issued to reset the DLL, it should always be followed by a LOAD MODE REGISTER command to select normal operating mode.

All other combinations of values for A7-A12 are reserved for future use and/or test modes. Test modes and reserved states should not be used because unknown operation or incompatibility with future versions may result.

#### TABLE 1 - BURST DEFINITION

| Burst Starting Column |         | Order of Access | es Within a Burst |                   |                    |

|-----------------------|---------|-----------------|-------------------|-------------------|--------------------|

| Length                | Address |                 | S                 | Type = Sequential | Type = Interleaved |

|                       |         |                 | A0                |                   |                    |

| 2                     |         |                 | 0                 | 0-1               | 0-1                |

|                       |         |                 | 1                 | 1-0               | 1-0                |

|                       |         | A1              | A0                |                   |                    |

|                       |         | 0               | 0                 | 0-1-2-3           | 0-1-2-3            |

| 4                     |         | 0               | 1                 | 1-2-3-0           | 1-0-3-2            |

|                       |         | 1               | 0                 | 2-3-0-1           | 2-3-0-1            |

|                       |         | 1               | 1                 | 3-0-1-2           | 3-2-1-0            |

|                       | A2      | A1              | A0                |                   |                    |

|                       | 0       | 0               | 0                 | 0-1-2-3-4-5-6-7   | 0-1-2-3-4-5-6-7    |

|                       | 0       | 0               | 1                 | 1-2-3-4-5-6-7-0   | 1-0-3-2-5-4-7-6    |

|                       | 0       | 1               | 0                 | 2-3-4-5-6-7-0-1   | 2-3-0-1-6-7-4-5    |

| 8                     | 0       | 1               | 1                 | 3-4-5-6-7-0-1-2   | 3-2-1-0-7-6-5-4    |

|                       | 1       | 0               | 0                 | 4-5-6-7-0-1-2-3   | 4-5-6-7-0-1-2-3    |

|                       | 1       | 0               | 1                 | 5-6-7-0-1-2-3-4   | 5-4-7-6-1-0-3-2    |

|                       | 1       | 1               | 0                 | 6-7-0-1-2-3-4-5   | 6-7-4-5-2-3-0-1    |

|                       | 1       | 1               | 1                 | 7-0-1-2-3-4-5-6   | 7-6-5-4-3-2-1-0    |

#### NOTES:

- For a burst length of two, A1-Ai select two-data-element block; A0 selects the starting column within the block.

- For a burst length of four, A2-Ai select four-data-element block; A0-1 select the starting column within the block.

- 3. For a burst length of eight, A<sub>3</sub>-Ai select eight-data-element block; A<sub>0-2</sub> select the starting column within the block.

- Whenever a boundary of the block is reached within a given sequence above, the following access wraps within the block.

#### FIGURE 3 - MODE REGISTER DEFINITION

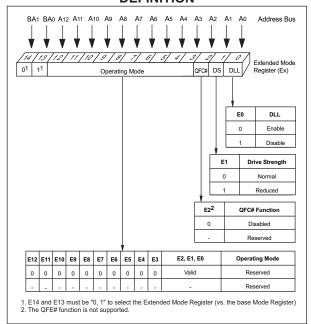

## **EXTENDED MODE REGISTER**

The extended mode register controls functions beyond those controlled by the mode register; these additional functions are DLL enable/disable, output drive strength, and QFC#. These functions are controlled via the bits shown in Figure 5. The extended mode register is programmed via the LOAD MODE REGISTER command to the mode register (with BA0 = 1 and BA1 = 0) and will retain the stored information until it is programmed again or the device loses power. The enabling of the DLL should always be followed by a LOAD MODE REGISTER command to the mode register (BA0/BA1 both LOW) to reset the DLL.

The extended mode register must be loaded when all banks are idle and no bursts are in progress, and the controller must wait the specified time before initiating any subsequent operation. Violating either of these requirements could result in unspecified operation.

#### FIGURE 4 - CAS LATENCY

#### OUTPUT DRIVE STRENGTH

The normal full drive strength for all outputs are specified to be SSTL2, Class II. The DDR SDRAM supports an option for reduced drive. This option is intended for the support of the lighter load and/or point-to-point environments. The selection of the reduced drive strength will alter the DQs and DQSs from SSTL2, Class II drive strength to a reduced drive strength, which is approximately 54 percent of the SSTL2, Class II drive strength.

#### DLL ENABLE/DISABLE

The DLL must be enabled for normal operation. DLL enable is required during power-up initialization and upon returning to normal operation after having disabled the DLL for the purpose of debug or evaluation. (When the device exits self refresh mode, the DLL is enabled automatically.) Any time the DLL is enabled, 200 clock cycles must occur before a READ command can be issued.

#### COMMANDS

The Truth Table provides a quick reference of available commands. This is followed by a written description of each command.

## FIGURE 5 – EXTENDED MODE REGISTER DEFINITION

#### DESELECT

The DESELECT function (CS# HiGH) prevents new commands from being executed by the DDR SDRAM. The SDRAM is effectively deselected. Operations already in progress are not affected.

## **NO OPERATION (NOP)**

The NO OPERATION (NOP) command is used to perform a NOP to the selected DDR SDRAM (CS# is LOW). This prevents unwanted commands from being registered during idle or wait states. Operations already in progress are not affected.

#### LOAD MODE REGISTER

The Mode Registers are loaded via inputs A0-12. The LOAD MODE REGISTER command can only be issued when all banks are idle, and a subsequent executable command cannot be issued until tMRD is met.

## TRUTH TABLE - COMMANDS (NOTE 1)

| NAME (FUNCTION)                                               | CS# | RAS# | CAS# | WE# | ADDR     |

|---------------------------------------------------------------|-----|------|------|-----|----------|

| DESELECT (NOP) (9)                                            | Н   | Х    | Х    | Х   | Х        |

| NO OPERATION (NOP) (9)                                        | L   | Н    | Н    | Н   | Х        |

| ACTIVE (Select bank and activate row) (3)                     | L   | L    | Н    | Н   | Bank/Row |

| READ (Select bank and column, and start READ burst) (4)       | L   | Н    | L    | Н   | Bank/Col |

| WRITE (Select bank and column, and start WRITE burst) (4)     | L   | Н    | L    | L   | Bank/Col |

| BURST TERMINATE (8)                                           | L   | Н    | Н    | L   | Х        |

| PRECHARGE (Deactivate row in bank or banks) (5)               | L   | L    | Н    | L   | Code     |

| AUTO REFRESH or SELF REFRESH (Enter self refresh mode) (6, 7) | L   | L    | L    | Н   | Х        |

| LOAD MODE REGISTER (2)                                        | L   | L    | L    | L   | Op-Code  |

#### TRUTH TABLE - DM OPERATION

| NAME (FUNCTION)    | DM | DQs   |

|--------------------|----|-------|

| WRITE ENABLE (10)  | L  | Valid |

| WRITE INHIBIT (10) | Н  | Х     |

#### NOTES:

- 1. CKE is HIGH for all commands shown except SELF REFRESH.

- A<sub>0-12</sub> define the op-code to be written to the selected Mode Register. BA<sub>0</sub>, BA<sub>1</sub> select either the mode register (0, 0) or the extended mode register (1, 0).

- 3. A<sub>0-12</sub> provide row address, and BA<sub>0</sub>, BA<sub>1</sub> provide bank address.

- Ao-8 provide column address; A10 HIGH enables the auto precharge feature (non persistent), while A10 LOW disables the auto precharge feature; BA0, BA1 provide bank address.

- A10 LOW: BA0, BA1 determine the bank being precharged. A10 HIGH: All banks precharged and BA0, BA1 are "Don't Care."

## **ACTIVE**

The ACTIVE command is used to open (or activate) a row in a particular bank for a subsequent access. The value on the BA0, BA1 inputs selects the bank, and the address provided on inputs A0-12 selects the row. This row remains active (or open) for accesses until a PRECHARGE command is issued to that bank. A PRECHARGE command must be issued before opening a different row in the same bank.

#### READ

The READ command is used to initiate a burst read access to an active row. The value on the BA0, BA1 inputs selects the bank, and the address provided on inputs A0-8 selects the starting column location. The value on input A10 determines whether or not AUTO PRECHARGE is used. If AUTO PRECHARGE is selected, the row being accessed

#### REGISTER FUNCTION TABLE

|        | INPUTS         |                |                |                |  |  |  |

|--------|----------------|----------------|----------------|----------------|--|--|--|

| RESET# | RCK            | RCK#           | INPUT          | Q              |  |  |  |

| Н      | 1              | <b>↓</b>       | Н              | Н              |  |  |  |

| Н      | <b>↑</b>       | <b>↓</b>       | L              | L              |  |  |  |

| Н      | L or H         | L or H         | X              | Q <sub>0</sub> |  |  |  |

| L      | X, or floating | X, or floating | X, or floating | L              |  |  |  |

- This command is AUTO REFRESH if CKE is HIGH; SELF REFRESH if CKE is LOW.

- Internal refresh counter controls row addressing; all inputs and I/Os are "Don't Care" except for CKE.

- Applies only to read bursts with auto precharge disabled; this command is undefined (and should not be used) for READ bursts with auto precharge enabled and for WRITE bursts

- 9. DESELECT and NOP are functionally interchangeable.

- 10. Used to mask write data; provided coincident with the corresponding data.

will be precharged at the end of the READ burst; if AUTO PRECHARGE is not selected, the row will remain open for subsequent accesses.

#### WRITE

The WRITE command is used to initiate a burst write access to an active row. The value on the BA0, BA1 inputs selects the bank, and the address provided on inputs A0-8 selects the starting column location. The value on input A10 determines whether or not AUTO PRECHARGE is used. If AUTO PRECHARGE is selected, the row being accessed will be precharged at the end of the WRITE burst; if AUTO PRECHARGE is not selected, the row will remain open for subsequent accesses. Input data appearing on the D/Qs is written to the memory array subject to the DQM input logic level appearing coincident with the data. If a given DQM signal is registered LOW, the corresponding data

will be written to memory; if the DQM signal is registered HIGH, the corresponding data inputs will be ignored, and a WRITE will not be executed to that byte/column location.

## **PRECHARGE**

The PRECHARGE command is used to deactivate the open row in a particular bank or the open row in all banks. The bank(s) will be available for a subsequent row access a specified time (tRP) after the PRECHARGE command is issued. Except in the case of concurrent auto precharge, where a READ or WRITE command to a different bank is allowed as long as it does not interrupt the data transfer in the current bank and does not violate any other timing parameters. Input A10 determines whether one or all banks are to be precharged, and in the case where only one bank is to be precharged, inputs BA0, BA1 select the bank. Otherwise BA0, BA1 are treated as "Don't Care." Once a bank has been precharged, it is in the idle state and must be activated prior to any READ or WRITE commands being issued to that bank. A PRECHARGE command will be treated as a NOP if there is no open row in that bank (idle state), or if the previously open row is already in the process of precharging.

## **AUTO PRECHARGE**

AUTO PRECHARGE is a feature which performs the same individual-bank PRECHARGE function described above, but without requiring an explicit command. This is accomplished by using A10 to enable AUTO PRECHARGE in conjunction with a specific READ or WRITE command. A precharge of the bank/row that is addressed with the READ or WRITE command is automatically performed upon completion of the READ or WRITE burst. AUTO PRECHARGE is nonpersistent in that it is either enabled or disabled for each individual READ or WRITE command. The device supports concurrent auto precharge if the command to the other bank does not interrupt the data transfer to the current bank.

AUTO PRECHARGE ensures that the precharge is initiated at the earliest valid stage within a burst. This "earliest valid stage" is determined as if an explicit precharge command was issued at the earliest possible time, without violating tras (MIN). The user must not issue another command to the same bank until the precharge time (trap) is completed. This is determined as if an explicit PRECHARGE command was issued at the earliest possible time, without violating tras (MIN).

## **BURST TERMINATE**

The BURST TERMINATE command is used to truncate READ bursts (with auto precharge disabled). The most recently registered READ command prior to the BURST TERMINATE command will be truncated. The open page which the READ burst was terminated from remains open.

## **AUTO REFRESH**

AUTO REFRESH is used during normal operation of the DDR SDRAM and is analogous to CAS#-BEFORE-RAS# (CBR) REFRESH in conventional DRAMs. This command is nonpersistent, so it must be issued each time a refresh is required.

The addressing is generated by the internal refresh controller. This makes the address bits "Don't Care" during an AUTO REFRESH command. Each DDR SDRAM requires AUTO REFRESH cycles at an average interval of 7.8125µs (maximum).

To allow for improved efficiency in scheduling and switching between tasks, some flexibility in the absolute refresh interval is provided. A maximum of eight AUTO REFRESH commands can be posted to any given DDR SDRAM, meaning that the maximum absolute interval between any AUTO REFRESH command and the next AUTO REFRESH command is  $9 \times 7.8125\mu s$  ( $70.3\mu s$ ). This maximum absolute interval is to allow future support for DLL updates internal to the DDR SDRAM to be restricted to AUTO REFRESH cycles, without allowing excessive drift in tAc between updates.

Although not a JEDEC requirement, to provide for future functionality features, CKE must be active (High) during the AUTO REFRESH period. The AUTO REFRESH period begins when the AUTO REFRESH command is registered and ends trec later.

## **SELF REFRESH\***

The SELF REFRESH command can be used to retain data in the DDR SDRAM, even if the rest of the system is powered down. When in the self refresh mode, the DDR SDRAM retains data without external clocking. The SELF REFRESH command is initiated like an AUTO REFRESH command except CKE is disabled (LOW). The DLL is automatically disabled upon entering SELF REFRESH and is automatically enabled upon exiting SELF REFRESH (200 clock cycles must then occur before a READ command can be issued). Input signals except CKE are "Don't Care" during SELF REFRESH.

The procedure for exiting self refresh requires a sequence of commands. First, CK must be stable prior to CKE going back HIGH. Once CKE is HIGH, the DDR SDRAM must have NOP commands issued for txsnr, because time is required for the completion of any internal refresh in progress.

A simple algorithm for meeting both refresh and DLL requirements is to apply NOPs for 200 clock cycles before applying any other command.

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                                   |             | Unit |

|---------------------------------------------|-------------|------|

| Voltage on Vcc, Vccq Supply relative to Vss | -1 to 3.6   | V    |

| Voltage on I/O pins relative to Vss         | -1 to 3.6   | V    |

| Operating Temperature T <sub>A</sub> (Mil)  | -55 to +125 | °C   |

| Operating Temperature T <sub>A</sub> (Ind)  | -40 to +85  | °C   |

| Storage Temperature, Plastic                | -55 to +125 | °C   |

## **CAPACITANCE (NOTE 13)**

| Parameter                                    | Symbol          | Max | Unit |

|----------------------------------------------|-----------------|-----|------|

| Input Capacitance: CK/CK#                    | C <sub>I1</sub> | 8   | pF   |

| Addresses, BA0-1 Input Capacitance           | CA              | 10  | pF   |

| Input Capacitance: All other input-only pins | C <sub>I2</sub> | 9   | pF   |

| Input/Output Capacitance: I/Os               | Сю              | 10  | pF   |

NOTE: Stress greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions greater than those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **BGA THERMAL RESISTANCE**

| Description                      | Symbol   | Max  | Units | Notes |

|----------------------------------|----------|------|-------|-------|

| Junction to Ambient (No Airflow) | Theta JA | 14.2 | °C/W  | 1     |

| Junction to Ball                 | Theta JB | 10.8 | °C/W  | 1     |

| Junction to Case (Top)           | Theta JC | 4.1  | °C/W  | 1     |

Note 1: Refer to AN #0001 at www.whiteedc.com in the application notes section for modeling conditions.

#### REGISTER RECOMMENDED OPERATING CONDITIONS

| Pa  | rameter/Condition           |             | Min        | Max        | Unit |

|-----|-----------------------------|-------------|------------|------------|------|

| VIH | AC high-level input voltage | Data inputs | VREF+310mV |            | V    |

| VIL | AC low-level input voltage  | Data inputs |            | VREF-310mV | V    |

| VIH | High-level input voltage    | RESET#      | 1.7        |            | V    |

| VIL | Low-level input voltage     | RESET#      |            | 0.7        | V    |

Note: The RESET# input of the device must be held at a valid logic level (not floating) to ensure proper device operation.

#### REGISTER ELECTRICAL CHARACTERISTICS

| Parameter Test Conditions |                                          | Test Conditions                                                                                                                                  |        | Vcc and Vccq | Min   | Тур | Max | Unit            |    |

|---------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------|-------|-----|-----|-----------------|----|

| li                        | All inputs                               | V <sub>I</sub> = V <sub>CC</sub> or GND                                                                                                          |        | 2.7V         | -5    |     | +5  | μΑ              |    |

| laa                       | Static standby                           | RESET# = GND                                                                                                                                     |        | 0.71/        | 0.71/ |     |     | 10              | μΑ |

| lcc                       | Static operating                         | RESET# = Vcc, Vi = Vih(AC) or ViL(AC)                                                                                                            | lo = 0 | 2.7V         |       |     | 112 | mA              |    |

|                           | Dynamic operating  – clock only          | RESET# = Vcc, Vi = ViH(AC) or ViL(AC), CK and CK# switching 50% duty cycle                                                                       |        |              |       | 56  |     | μΑ/ MHz         |    |

| ICCD                      | Dynamic operating  – per each data input | RESET# = Vcc, Vi = ViH(AC) or ViL(AC). CK and CK# switching 50% duty cycle. All data input switching at one-half clock frequency, 50% duty cycle | lo = 0 | = 0 2.5V     |       | 180 |     | μΑ/clock<br>MHz |    |

Note: All typical values are at Vcc = 2.5V, TA = 25°C.

<sup>\*</sup> Self refresh available in commercial and industrial temperatures only.

## DDR DC ELECTRICAL CHARACTERISTICS AND OPERATING CONDITIONS (NOTES 1, 6)

$V_{CC}$  = +2.5V ± 0.2V; -55°C  $\leq T_A \leq$  +125°C

| Parameter/Condition                                                                                                                    | Symbol           | Min                     | Max                     | Units |

|----------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------|-------------------------|-------|

| Supply Voltage                                                                                                                         | Vcc              | 2.3                     | 2.7                     | V     |

| I/O Supply Voltage                                                                                                                     | Vccq             | 2.3                     | 2.7                     | V     |

| Input Hight Voltage: Logic 1; All inputs (21)                                                                                          | VIH              | V <sub>REF</sub> + 0.15 | Vcc + 0.3               | V     |

| Input Low Voltage: Logic 0; All inputs (21)                                                                                            | VIL              | -0.4                    | V <sub>REF</sub> - 0.15 | V     |

| Input Leakage Current: Any input 0V ≤ V <sub>IN</sub> ≤ V <sub>CC</sub> (All other pins not under test = 0V)                           | lı .             | -2                      | 2                       | μA    |

| Output Leakage Current: I/Os are disabled; 0V ≤ V <sub>OUT</sub> ≤ V <sub>CC</sub>                                                     | loz              | -5                      | 5                       | μA    |

| Output Levels: Full drive option - x16 High Current (Vout = Voca - 0.373V, minimum VREF, minimum VTT)                                  | Іон              | -16.8                   | -                       | mA    |

| ow Current (Vout = 0.373V, maximum V <sub>REF</sub> , maximum V <sub>TT</sub> )                                                        | loL              | 16.8                    | -                       | mA    |

| Output Levels: Reduced drive option - 16 only High Current (Vout = Vcco - 0.763V, minimum V <sub>REF</sub> , minimum V <sub>TT</sub> ) | Iohr             | -9                      | -                       | mA    |

| Low Current (Vout = 0.763V, maximum VREF, maximum VTT)                                                                                 | lolr             | 9                       | _                       | mA    |

| I/O Reference Voltage                                                                                                                  | V <sub>REF</sub> | 0.49 x V <sub>CCQ</sub> | 0.51 x V <sub>CCQ</sub> | V     |

| I/O Termination Voltage                                                                                                                | VTT              | VREF - 0.04             | V <sub>REF</sub> + 0.04 | V     |

## DDR Icc SPECIFICATIONS AND CONDITIONS (NOTES 1-5, 10, 12, 14, 54)

$V_{CC} = +2.5V \pm 0.2V; -55^{\circ}C \le T_A \le +125^{\circ}C$

|                                                                                                                                                                                                                                           |                                                   |        | Max                |         |       |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------|--------------------|---------|-------|--|

| Parameter/Condition                                                                                                                                                                                                                       |                                                   | Symbol | 250Mbps<br>266Mbps | 200Mbps | Units |  |

| OPERATING CURRENT: One bank; Active-Precharge; trc = trc (MIN); tck = tck (MIN); DQ, DM, and DQS inputs changing once per clock cyle; Address and control inputs changing once every two clock cycles; (22, 48)                           |                                                   | Icco   | 625                | 600     | mA    |  |

| OPERATING CURRENT: One bank; Active-Read-Precharge; Burst = 2; tRc = tRc (MIN); tck = tck (MIN); lout = 0mA; Address and control inputs changing once per clock cycle (22, 48)                                                            |                                                   |        | 850                | 775     | mA    |  |

| PRECHARGE POWER-DOWN STANDBY CURRENT: All banks idle; Power-down mode; tck = t                                                                                                                                                            | ICC2P                                             | 20     | 20                 | mA      |       |  |

| IDLE STANDBY CURRENT: CS# = HIGH; All banks idle; tcK = tcK (MIN); CKE = HIGH; Address once per clock cycle. ViN = VREF for DQ, DQS, and DM (51)                                                                                          | I <sub>CC2F</sub>                                 | 225    | 225                | mA      |       |  |

| ACTIVE POWER-DOWN STANDBY CURRENT: One bank active; Power-down mode; tck = tck                                                                                                                                                            | Іссзр                                             | 150    | 150                | mA      |       |  |

| ACTIVE STANDBY CURRENT: CS# = HIGH; CKE = HIGH; One bank; Active-Precharge; tRc = tRAS (MAX); tck = tck (MIN); DQ, DM, and DQS inputs changing twice per clock cycle; Address and other control inputs changing once per clock cycle (22) |                                                   |        | 250                | 250     | mA    |  |

| OPERATING CURRENT: Burst = 2; Reads; Continuous burst; One bank active; Address and control inputs changing once per clock cycle; tck = tck (MIN); lout = 0mA (22, 48)                                                                    |                                                   |        | 925                | 925     | mA    |  |

| OPERATING CURRENT: Burst = 2; Writes; Continuous burst; One bank active; Address and cord clock cycle; tck = tck (MIN); DQ, DM, and DQS inputs changing twice per clock cycle (22)                                                        | Icc4w                                             | 800    | 800                | mA      |       |  |

| AUTO REFRESH CURRENT                                                                                                                                                                                                                      | t <sub>REF</sub> = t <sub>RC</sub> (MIN) (27, 50) | Icc5   | 1225               | 1225    | mA    |  |

|                                                                                                                                                                                                                                           | tref = 7.8125µs (27, 50)                          | ICC5A  | 30                 | 30      | mA    |  |

| SELF REFRESH CURRENT: CKE ≤ 0.2V                                                                                                                                                                                                          | Standard (11)                                     | Icc6   | 20                 | 20      | mA    |  |

| OPERATING CURRENT: Four bank interleaving READs (BL=4) with auto precharge, trc =trc (MIN); tck = tck (MIN); Address and control inputs change only during Active READ or WRITE commands. (22, 49)                                        |                                                   | Icc7   | 2000               | 2000    | mA    |  |

## **ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CHARACTERISTICS** (NOTES 1-5, 14-17, 33)

| (NOTES 1-                                                         |                   |                  | 266Mbps CL2.5<br>200Mbps CL2 |                       | 250Mbps CL2.5<br>200Mbps CL2 |            | 200Mbps CL2.5<br>150Mbps CL2 |         |       |

|-------------------------------------------------------------------|-------------------|------------------|------------------------------|-----------------------|------------------------------|------------|------------------------------|---------|-------|

|                                                                   |                   | Symbol           | Min                          | Max                   | Min                          | Max        | Min                          | Max     | Units |

| Access window of DQs from CLK/CLK#                                |                   | tac              | -0.75                        | +0.75                 | -0.75                        | +0.75      | -0.75                        | +0.75   | ns    |

| CLK high-level width (30)                                         |                   | tсн              | 0.45                         | 0.55                  | 0.45                         | 0.55       | 0.45                         | 0.55    | tcĸ   |

| CLK low-level width (30)                                          | T                 | tcL              | 0.45                         | 0.55                  | 0.45                         | 0.55       | 0.45                         | 0.55    | tcĸ   |

| Clock cycle time                                                  | CL = 2.5 (45, 52) | tcк (2.5)        | 8                            | 13                    | 9                            | 13         | 10                           | 13      | ns    |

|                                                                   | CL = 2 (45, 52)   | tck (2)          | 10                           | 13                    | 10                           | 13         | 13                           | 15      | ns    |

| DQ and DM input hold time relative to DQS (26, 31)                |                   | tон              | 0.5                          |                       | 0.5                          |            | 0.5                          |         | ns    |

| DQ and DM input setup time relative to DQS (26, 31)               |                   | tos              | 0.5                          |                       | 0.5                          |            | 0.5                          |         | ns    |

| DQ and DM input pulse width (for each input) (31)                 |                   | tolpw            | 1.75                         |                       | 1.75                         |            | 1.75                         |         | ns    |

| Access window of DQS from CLK/CLK#                                |                   | togsck           | -0.75                        | +0.75                 | -0.8                         | +0.8       | -0.8                         | +0.8    | ns    |

| DQS input high pulse width                                        |                   | toqsh            | 0.35                         |                       | 0.35                         |            | 0.35                         |         | tcĸ   |

| DQS input low pulse width                                         |                   | toqsl            | 0.35                         |                       | 0.35                         |            | 0.35                         |         | tcĸ   |

| DQS-DQ skew, DQS to last DQ valid, per group, per access (25,     | 26)               | toasa            |                              | 0.5                   |                              | 0.5        |                              | 0.5     | ns    |

| Write command to first DQS latching transition                    |                   | togss            | 0.75                         | 1.25                  | 0.75                         | 1.25       | 0.75                         | 1.25    | tcĸ   |

| DQS falling edge to CLK rising - setup time                       |                   | toss             | 0.2                          |                       | 0.2                          |            | 0.2                          |         | tcĸ   |

| DQS falling edge from CLK rising - hold time                      |                   | tоsн             | 0.2                          |                       | 0.2                          |            | 0.2                          |         | tcĸ   |

| Half clock period (34)                                            |                   | thp              | tcH, tcL                     |                       | tcH, tcL                     |            | tcH, tcL                     |         | ns    |

| Data-out high-impedance window from CLK/CLK# (18, 42)             |                   | tHZ              |                              | +0.75                 |                              | +0.75      |                              | +0.75   | ns    |

| Data-out low-impedance window from CLK/CLK# (18, 43)              |                   | tız              | -0.75                        |                       | -0.75                        |            | -0.75                        |         | ns    |

| Address and control input hold time (fast slew rate) (14)         |                   | tıн <sub>F</sub> | 0.90                         |                       | 0.90                         |            | 0.90                         |         | ns    |

| Address and control input setup time (fast slew rate) (14)        |                   | tis <sub>F</sub> | 0.90                         |                       | 0.90                         |            | 0.90                         |         | ns    |

| Address and control input hold time (slow slew rate) (14)         |                   | tıнs             | 1                            |                       | 1                            |            | 1                            |         | ns    |

| Address and control input setup time (slow slew rate) (14)        |                   | tiss             | 1                            |                       | 1                            |            | 1                            |         | ns    |

| LOAD MODE REGISTER command cycle time                             |                   | tmrd             | 15                           |                       | 15                           |            | 15                           |         | ns    |

| DQ-DQS hold, DQS to first DQ to go non-valid, per access (25, 26) |                   | tqн              | thp -                        | thp - tans thp - tans |                              | thp - tqhs |                              | ns      |       |

| Data hold skew factor                                             |                   | tons             |                              | 0.75                  |                              | 0.75       |                              | 0.75    | ns    |

| ACTIVE to PRECHARGE command (35)                                  |                   | tras             | 40                           | 120,000               | 40                           | 120,000    | 40                           | 120,000 | ns    |

| ACTIVE to READ with Auto precharge command                        |                   | trap             | 20                           |                       | 20                           |            | 20                           |         | ns    |

| ACTIVE to ACTIVE/AUTO REFRESH command period                      |                   | trc              | 65                           |                       | 65                           |            | 65                           |         | ns    |

| AUTO REFRESH command period (50)                                  |                   | trec             | 75                           |                       | 75                           |            | 75                           |         | ns    |

| ACTIVE to READ or WRITE delay                                     |                   | trco             | 20                           |                       | 20                           |            | 20                           |         | ns    |

| PRECHARGE command period                                          |                   | trp              | 20                           |                       | 20                           |            | 20                           |         | ns    |

| DQS read preamble (42)                                            |                   | trpre            | 0.9                          | 1.1                   | 0.9                          | 1.1        | 0.9                          | 1.1     | tcĸ   |

| DQS read postamble                                                |                   | trpst            | 0.4                          | 0.6                   | 0.4                          | 0.6        | 0.4                          | 0.6     | tcĸ   |

| ACTIVE bank a to ACTIVE bank b command                            |                   | trrd             | 15                           |                       | 15                           |            | 15                           |         | ns    |

| DQS write preamble                                                |                   | twpre            | 0.25                         |                       | 0.25                         |            | 0.25                         |         | tcĸ   |

| DQS write preamble setup time (20, 21)                            |                   | twpres           | 0                            |                       | 0                            |            | 0                            |         | ns    |

| DQS write postamble (19)                                          |                   | twpst            | 0.4                          | 0.6                   | 0.4                          | 0.6        | 0.4                          | 0.6     | tcĸ   |

| Write recovery time                                               |                   | twr              | 15                           |                       | 15                           |            | 15                           |         | ns    |

| Internal WRITE to READ command delay                              |                   | twr              | 1                            |                       | 1                            |            | 1                            |         | tcĸ   |

| ata valid output window (25)                                      |                   | na               | tan - toasa tan - toasa      |                       | tan - tagsa                  |            | ns                           |         |       |

| REFRESH to REFRESH command interval (23)                          |                   | trefc            |                              | 70.3                  |                              | 70.3       |                              | 70.3    | μs    |

| Average periodic refresh interval (23)                            |                   | trefi            |                              | 7.8                   |                              | 7.8        |                              | 7.8     | μs    |

| Terminating voltage delay to Vcc (53)                             |                   | tvtd             | 0                            | -                     | 0                            | -          | 0                            |         | ns    |

| Exit SELF REFRESH to non-READ command                             |                   | txsnr            | 75                           |                       | 80                           |            | 80                           |         | ns    |

| Exit SELF REFRESH to READ command                                 |                   | 1                |                              | 1                     | 1                            | 1          | 1                            | 1       |       |

#### NOTES:

- 1. All voltages referenced to Vss.

- Tests for AC timing, Icc, and electrical AC and DC characteristics may be conducted at nominal reference/supply voltage levels, but the related specifications and device operation are guaranteed for the full voltage range specified.

- 3. Outputs measured with equivalent load:

- 4. AC timing and Icc tests may use a VIL-to-VIH swing of up to 1.5V in the test environment, but input timing is still referenced to VREF (or to the crossing point for CK/CK#), and parameter specifications are guaranteed for the specified AC input levels under normal use conditions. The minimum slew rate for the input signals used to test the device is 1V/ns in the range between VIL(AC) and VIH(AC).

- The AC and DC input level specifications are as defined in the SSTL\_2 Standard (i.e., the receiver will effectively switch as a result of the signal crossing the AC input level, and will remain in that state as long as the signal does not ring back above [below] the DC input LOW [HIGH] level).

- 6. VREF is expected to equal Vcco/2 of the transmitting device and to track variations in the DC level of the same. Peak-to-peak noise (noncommon mode) on VREF may not exceed ±2 percent of the DC value. Thus, from Vcco/2, VREF is allowed ±25mV for DC error and an additional ±25mV for AC noise. This measurement is to be taken at the nearest VREF by-pass capacitor.

- VTT is not applied directly to the device. VTT is a system supply for signal termination resistors, is expected to be set equal to VREF and must track variations in the DC level of VREF.

- Vip is the magnitude of the difference between the input level on CK and the input level on CK#

- The value of V<sub>IX</sub> and V<sub>MP</sub> are expected to equal Vcco/2 of the transmitting device and must track variations in the DC level of the same.

- Icc is dependent on output loading and cycle rates. Specified values are obtained with minimum cycle time with the outputs open.

- 11. Enables on-chip refresh and address counters.

- lcc specifications are tested after the device is properly initialized, and is averaged at the defined cycle rate.

- 13. This parameter is not tested but guaranteed by design. tA = 25°C, F = 1 MHz

- 14. Command/Address input slew rate = 0.5V/ns. For 266 MHz with slew rates 1V/ns and faster, tis and ti⊩ are reduced to 900ps. If the slew rate is less than 0.5V/ns, timing must be derated: tis has an additional 50ps per each 100mV/ns reduction in slew rate from the 500mV/ns. tiн has 0ps added, that is, it remains constant. If the slew rate exceeds 4.5V/ns. functionality is uncertain.

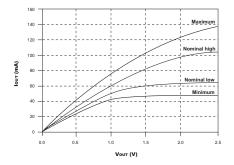

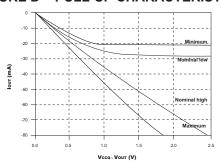

#### FIGURE A - PULL-DOWN CHARACTERISTICS

- The CK/CK# input reference level (for timing referenced to CK/CK#) is the point at which CK and CK# cross: the input reference level for signals other than CK/CK# is VREF.

- Inputs are not recognized as valid until VREF stabilizes. Exception: during the period before VREF stabilizes, CKE ≤ 0.3 x Vcca is recognized as LOW.

- The output timing reference level, as measured at the timing reference point indicated in Note 3. is Vττ.

- 18. tHz and tLz transitions occur in the same access time windows as valid data transitions. These parameters are not referenced to a specific voltage level, but specify when the device output is no longer driving (HZ) or begins driving (LZ).

- The maximum limit for this parameter is not a device limit. The device will operate

with a greater value for this parameter, but system performance (bus turnaround)

will degrade accordingly.

- This is not a device limit. The device will operate with a negative value, but system performance could be degraded due to bus turnaround.

- 21. It is recommended that DQS be valid (HIGH or LOW) on or before the WRITE command. The case shown (DQS going from High-Z to logic LOW) applies when no WRITEs were previously in progress on the bus. If a previous WRITE was in progress, DQS could be HIGH during this time, depending on tboss.

- 22. MIN (trc or trrc) for Icc measurements is the smallest multiple of tck that meets the minimum absolute value for the respective parameter. tras (MAX) for Icc measurements is the largest multiple of tck that meets the maximum absolute value for tras.

- 23. The refresh period 64ms. This equates to an average refresh rate of 7.8125µs. However, an AUTO REFRESH command must be asserted at least once every 70.3µs; burst refreshing or posting by the DRAM controller greater than eight refresh cycles is not allowed.

- The I/O capacitance per DQS and DQ byte/group will not differ by more than this

maximum amount for any given device.

- 25. The valid data window is derived by achieving other specifications thr (tcκ/2), tboso, and toh (toh = thr tohs). The data valid window derates directly porportional with the clock duty cycle and a practical data valid window can be derived. The clock is allowed a maximum duty cycle variation of 45/55. Functionality is uncertain when operating beyond a 45/55 ratio. The data valid window derating curves are provided below for duty cycles ranging between 50/50 and 45/55.

- Referenced to each output group: DQS0 with DQ0-DQ7; and DQS1 with DQ8-DQ15 of each chip.

- This limit is actually a nominal value and does not result in a fail value. CKE is HIGH during REFRESH command period (IRFC [MIN]) else CKE is LOW (i.e., during standby).

- 28. To maintain a valid level, the transitioning edge of the input must:

- a) Sustain a constant slew rate from the current AC level through to the target AC level, VIL(AC) or VIH(AC).

- b) Reach at least the target AC level.

- c) After the AC target level is reached, continue to maintain at least the target DC level, ViL(DC) or ViH(DC).

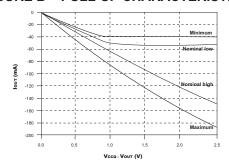

#### FIGURE B - PULL-UP CHARACTERISTICS

- The Input capacitance per pin group will not differ by more than this maximum amount for any given device.

- 30. CK and CK# input slew rate must be  $\geq$  1V/ns ( $\geq$ 2V/ns differentially).

- 31. DQ and DM input slew rates must not deviate from DQS by more than 10%. If the DQ/DM/DQS slew rate is less than 0.5V/ns, timing must be derated: 50ps must be added to tos and ton for each 100mV/ns reduction in slew rate. If slew rate exceeds 4V/ns, functionality is uncertain.

- 32. Vcc must not vary more than 4% if CKE is not active while any bank is active.

- The clock is allowed up to ±150ps of jitter. Each timing parameter is allowed to vary by the same amount

- 34. thp min is the lesser of tcl minimum and tch minimum actually applied to the device CK and CK# inputs, collectively during bank active.

- READs and WRITEs with auto precharge are not allowed to be issued until tras(MIN) can be satisfied prior to the internal precharge command being issued.

- 36. Any positive glitch must be less than 1/3 of the clock and not more than +400mV or 2.9 volts, whichever is less. Any negative glitch must be less than 1/3 of the clock cycle and not exceed either -300mV or 2.2 volts, whichever is more positive.

- 37. Normal Output Drive Curves:

- a) The full variation in driver pull-down current from minimum to maximum process, temperature and voltage will lie within the outer bounding lines of the V-I curve of Figure A.

- b) The variation in driver pull-down current within nominal limits of voltage and temperature is expected, but not guaranteed, to lie within the inner bounding lines of the V-I curve of Figure A.

- c) The full variation in driver pull-up current from minimum to maximum process, temperature and voltage will lie within the outer bounding lines of the V-I curve of Figure B.

- d) The variation in driver pull-up current within nominal limits of voltage and temperature is expected, but not guaranteed, to lie within the inner bounding lines of the V-I curve of Figure B.

- e) The full variation in the ratio of the maximum to minimum pull-up and pull-down current should be between .71 and 1.4, for device drain-to-source voltages from 0.1V to 1.0 Volt, and at the same voltage and temperature.

- f) The full variation in the ratio of the nominal pull-up to pull-down current should be unity ±10%, for device drain-to-source voltages from 0.1V to 1.0 Volt.

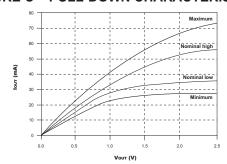

- 38. Reduced Output Drive Curves:

- a) The full variation in driver pull-down current from minimum to maximum process, temperature and voltage will lie within the outer bounding lines of the V-I curve of Figure C.

- b) The variation in driver pull-down current within nominal limits of voltage and temperature is expected, but not guaranteed, to lie within the inner bounding lines of the V-I curve of Figure C.

- c) The full variation in driver pull-up current from minimum to maximum process, temperature and voltage will lie within the outer bounding lines of the V-I curve

- of Figure D.

- d) The variation in driver pull-up current within nominal limits of voltage and temperature is expected, but not guaranteed, to lie within the inner bounding lines of the V-I curve of Figure D.

- e) The full variation in the ratio of the maximum to minimum pull-up and pull-down current should be between .71 and 1.4, for device drain-to-source voltages from 0.1V to 1.0 V. and at the same voltage and temperature.

- f) The full variation in the ratio of the nominal pull-up to pull-down current should be unity ±10%, for device drain-to-source voltages from 0.1V to 1.0 V.

- 39. The voltage levels used are derived from a minimum Vcc level and the referenced test load. In practice, the voltage levels obtained from a properly terminated bus will provide significantly different voltage values.

- ViH overshoot: ViH(MAX) = Vcco+1.5V for a pulse width ≤ 3ns and the pulse width can not be greater than 1/3 of the cycle rate.

- 41. Vcc and Vccq must track each other.

- 42. This maximum value is derived from the referenced test load. In practice, the values obtained in a typical terminated design may reflect up to 310ps less for thz(MAX) and the last DVW. thz(MAX) will prevail over tbosck(MAX) + trpst(MAX) condition. thz(MIN) will prevail over tbosck(MIN) + trpre(MAX) condition.

- 43. For slew rates greater than 1V/ns the (LZ) transition will start about 310ps earlier.

- 44. During initialization, Vcco, Vττ, and VREF must be equal to or less than Vcc + 0.3V. Alternatively, Vττ may be 1.35V maximum during power up, even if Vcc/Vcco are 0 volts, provided a minimum of 42 ohms of series resistance is used between the Vττ supply and the input pin.

- The current part operates below the slowest JEDEC operating frequency of 83 MHz. As such, future die may not reflect this option.

- 46. Reserved for future use.

- 47. Reserved for future use.

- 48. Random addressing changing 50% of data changing at every transfer.

- 49. Random addressing changing 100% of data changing at every transfer.

- 50. CKE must be active (high) during the entire time a refresh command is executed. That is, from the time the AUTO REFRESH command is registered, CKE must be active at each rising clock edge, until terc has been satisfied.

- Icc2N specifies the DQ, DQS, and DM to be driven to a valid high or low logic level.

Icc2Q is similar to Icc2F except Icc2Q specifies the address and control inputs to remain stable. Although Icc2F, Icc2N, and Icc2Q are similar, Icc2F is "worst case."

- Whenever the operating frequency is altered, not including jitter, the DLL is required to be reset. This is followed by 200 clock cycles before any READ command.

- All AC timings do not count extra clock needed on address and control signals to be registered.

- 54. DDR currents only. Register currents not included.

#### FIGURE C - PULL-DOWN CHARACTERISTICS

#### FIGURE D - PULL-UP CHARACTERISTICS

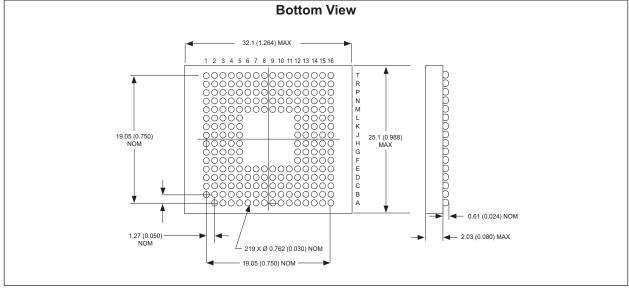

## PACKAGE DIMENSION: 219 PLASTIC BALL GRID ARRAY (PBGA)

ALL LINEAR DIMENSIONS ARE MILLIMETERS AND PARENTHETICALLY IN INCHES

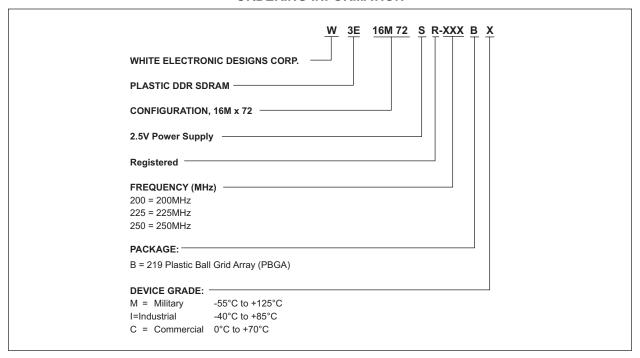

#### ORDERING INFORMATION

## **Document Title**

16M x 72 Registered DDR SDRAM Multi-Chip Package

## **Revision History**

| Rev#  | History                                                                                                                                                                                                                                                     | Release Date  | Status   |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------|

| Rev 0 | Initial Release                                                                                                                                                                                                                                             | August 2003   | Advanced |

| Rev 1 | Changes (Pg. 1, 15, 16) 1.1 Change mechanical drawing to new style                                                                                                                                                                                          | November 2003 | Advanced |

| Rev 2 | Changes (Pg. 1, 10, 11, 16)  2.1 Change status to Final  2.2 Update Icc specifications table values  2.3 Change max storage temperature to 125°C  2.4 Delete V <sub>IH</sub> /V <sub>IL</sub> DC low-level input voltage operating condition specification. | February 2005 | Final    |

|       | 2.5 Update capacitance table values                                                                                                                                                                                                                         |               |          |