# Four Character 5.0 mm (0.20 inch) 5 x 7 Alphanumeric Displays

# Technical Data

HDSP-2301 HDSP-2302 HDSP-2303

#### Features

- Integrated Shift Registers with Constant Current Drivers

- Compact Ceramic Package

- Wide Viewing Angle

- End Stackable Four Character Package

- TTL Compatible

- 5 x 7 LED Matrix Displays Full ASCII Set

- Categorized for Luminous Intensity

- HDSP-2301/2303 Categorized for Color

### Applications

- Avionics

- Business Machines

- Medical Instruments

- Portable Data Entry Devices

#### Description

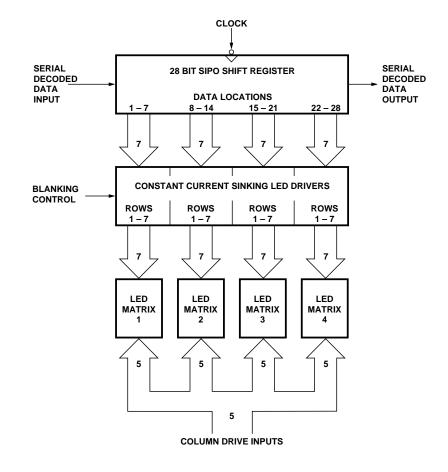

The HDSP-2301/-2302/-2303 series of displays are 5.0 mm (0.20 inch) 5 x 7 LED arrays for display of alphanumeric information. These devices are available in yellow, high efficiency red, and high performance green. Each four character cluster is contained in a 12 pin dual-in-line package. An

on-board SIPO (Serial-In-Parallel-Out) 7-bit shift register associated with each digit controls constant current LED row drivers. Full character display is achieved by external column strobing.

#### **Devices**

| Yellow    | Yellow High Efficiency Red |           |  |  |

|-----------|----------------------------|-----------|--|--|

| HDSP-2301 | HDSP-2302                  | HDSP-2303 |  |  |

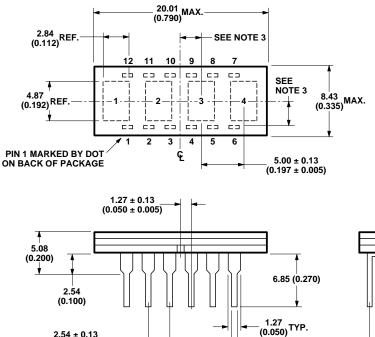

## **Package Dimensions**

| PIN | FUNCTION      | PIN | FUNCTION |

|-----|---------------|-----|----------|

| 1   | COLUMN 1      | 7   | DATA OUT |

| 2   | COLUMN 2      | 8   | VB       |

| 3   | COLUMN 3      | 9   | Vcc      |

| 4   | COLUMN 4      | 10  | CLOCK    |

| 5   | COLUMN 5      | 11  | GROUND   |

| 6   | INT. CONNECT* | 12  | DATA IN  |

NOTES:

\*DO NOT CONNECT OR USE

- 1. DIMENSIONS IN MILLIMETERS (INCHES). 2. UNLESS OTHERWISE SPECIFIED, THE TOLERANCE

- ON ALL DIMENSIONS IS ± 0.38 mm (± 0.015"). 3. CHARACTERS ARE CENTERED WITH RESPECT TO

- LEADS WITHIN ± 0.13 mm (± 0.005").

# 2.54 ± 0.13 (0.100 ± 0.005) TYP. NON ACCUM.

# Absolute Maximum Ratings (HDSP-2301/-2302/-2303)

| Supply Voltage, $V_{CC}$ to Ground0.5 V to 6.0 V                        |

|-------------------------------------------------------------------------|

| Inputs, Data Out and $V_{\rm B}$ –0.5 V to $V_{\rm CC}$                 |

| Column Input Voltage, $V_{COL}$                                         |

| Free Air Operating Temperature Range, $T_A^{[1,2]}$ 20°C to +85°C       |

| Storage Temperature Range, $T_S$                                        |

| Maximum Allowable Package Dissipation at $T_A = 25 \degree C^{[1,2,3]}$ |

| HDSP-2301/-2302/-2303 1.46 Watts                                        |

| Maximum Solder Temperature 1.59 mm (0.63")                              |

| Below Seating Plane t < 5 sec                                           |

# **Recommended Operating Conditions (HDSP-2301/-2302/-2303)**

| Parameter                                             | Symbol                | Min. | Nom. | Max. | Units | Fig. |

|-------------------------------------------------------|-----------------------|------|------|------|-------|------|

| Supply Voltage                                        | V <sub>CC</sub>       | 4.75 | 5.0  | 5.25 | V     |      |

| Data Out Current, Low State                           | I <sub>OL</sub>       |      |      | 1.6  | mA    |      |

| Data Out Current, High State                          | I <sub>OH</sub>       |      |      | -0.5 | mA    |      |

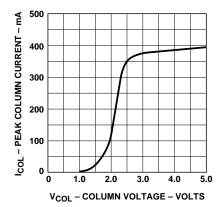

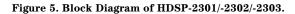

| Column Input Voltage, Column On HDSP-2301/-2302/-2303 | V <sub>COL</sub>      | 2.75 |      | 3.5  | V     | 4    |

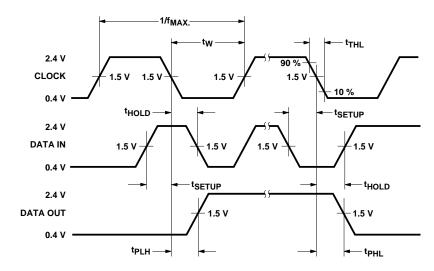

| Setup Time                                            | t <sub>setup</sub>    | 70   | 45   |      | ns    | 1    |

| Hold Time                                             | t <sub>hold</sub>     | 30   | 0    |      | ns    | 1    |

| Width of Clock                                        | t <sub>w(Clock)</sub> | 75   |      |      | ns    | 1    |

| Clock Frequency                                       | f <sub>clock</sub>    | 0    |      | 3    | MHz   | 1    |

| Clock Transition Time                                 | $t_{THL}$             |      |      | 200  | ns    | 1    |

| Free Air Operating Temperature Range <sup>[1,2]</sup> | TA                    | -20  |      | 85   | °C    | 2    |

\_\_ 0.54 ± 0.08 (0.020 ± 0.003)

# Electrical Characteristics over Operating Temperature Range

(Unless otherwise specified)

Yellow HDSP-2301/High Efficiency Red HDSP-2302/ High Performance Green HDSP-2303

| Descript                                       | ion                    | Symbol            | Test Conditions                                                                                                                                                 |                                                                                                                                           |     | Typ.* | Max. | Units           | Fig. |

|------------------------------------------------|------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------|-----------------|------|

| Supply Current                                 |                        | Icc               | $ \begin{vmatrix} V_{CC} = 5.25 \text{ V} \\ V_{CLOCK} = V_{DATA} = 2.4 \text{ V} \end{vmatrix} V_B = 0.4 \text{ V} $                                           |                                                                                                                                           |     | 45    | 60   | mA              |      |

| Supply Current                                 |                        | I <sub>CC</sub>   | All SR Stages =<br>Logical 1                                                                                                                                    | $V_{\rm B} = 2.4 \ {\rm V}$                                                                                                               |     | 73    | 95   | mA              |      |

| Column Current<br>Column Input                 | •                      | I <sub>COL</sub>  | $V_{CC} = 5.25 V$ $V_{COL} = 3.5 V$                                                                                                                             | $V_{\rm B} = 0.4 \ \rm V$                                                                                                                 |     |       | 500  | μΑ              |      |

| Column Current<br>Column Input                 | •                      | I <sub>COL</sub>  | All SR Stages =<br>Logical 1                                                                                                                                    | $V_{\rm B} = 2.4 \text{ V}$                                                                                                               |     | 380   | 520  | mA              | 4    |

| V <sub>B</sub> , Clock or Dat<br>Threshold Hig | -                      | V <sub>IH</sub>   | $V_{CC} = V_{COL} = 4.75 V$                                                                                                                                     |                                                                                                                                           | 2.0 |       |      | V               |      |

| V <sub>B</sub> , Clock or Dat<br>Threshold Lov |                        | V <sub>IL</sub>   |                                                                                                                                                                 |                                                                                                                                           |     |       | 0.8  | V               |      |

| Input Current                                  | V <sub>B</sub> , Clock | I <sub>IH</sub>   | $V_{\rm CC} = 5.25 \text{ V}, V_{\rm IH} = 2.4 \text{ V}$                                                                                                       | 7                                                                                                                                         |     | 20    | 80   | μΑ              |      |

| Logical 1                                      | Data In                | I <sub>IH</sub>   | $v_{\rm CC} = 5.25 v, v_{\rm IH} = 2.4 v$                                                                                                                       | /                                                                                                                                         |     | 10    | 40   | μΑ              | ]    |

| Input Current                                  | V <sub>B</sub> , Clock | I <sub>IL</sub>   | $V_{CC} = 5.25 \text{ V}, V_{IL} = 0.4 \text{V}$                                                                                                                |                                                                                                                                           |     | -500  | -800 | μΑ              |      |

| Logical 0                                      | Data In                | I <sub>IL</sub>   | $v_{\rm CC} = 5.25  v,  v_{\rm IL} = 0.4  v$                                                                                                                    |                                                                                                                                           |     | -250  | -400 | μΑ              |      |

| Data Out Voltage                               | 9                      | V <sub>OH</sub>   | $\label{eq:VCC} \begin{split} V_{CC} &= 4.75 \text{ V}, \ I_{OH} = -0.5 \text{ mA}, \\ I_{COL} &= 0 \text{ mA} \end{split}$                                     |                                                                                                                                           | 2.4 | 3.4   |      | V               |      |

|                                                | -                      | V <sub>OL</sub>   | $\label{eq:VCC} \begin{array}{l} V_{CC} = 4.75 \ \text{V}, \ I_{OL} = 1.6 \ \text{r} \\ I_{COL} = 0 \ \text{mA} \end{array}$                                    | $\label{eq:VCC} \begin{array}{l} V_{CC} = 4.75 \mbox{ V}, \mbox{ I}_{OL} = 1.6 \mbox{ mA}, \\ \mbox{ I}_{COL} = 0 \mbox{ mA} \end{array}$ |     | 0.2   | 0.4  | V               |      |

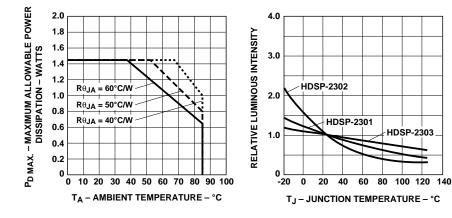

| Power Dissipatio<br>Package**                  | on Per                 | P <sub>D</sub>    | $\begin{split} V_{CC} &= 5.0 \text{ V}, V_{COL} = 3.5 \text{ V}, \\ 17.5\% \text{ DF} \\ 15 \text{ LEDs on per character}, \\ V_B &= 2.4 \text{ V} \end{split}$ |                                                                                                                                           |     | 0.78  |      | W               | 2    |

| Thermal Resistan<br>Junction-to-Ca             |                        | R <sub>θJ-C</sub> |                                                                                                                                                                 |                                                                                                                                           |     | 25    |      | °C/W/<br>Device | 2    |

\*All typical values specified at  $V_{CC} = 5.0$  V and  $T_A = 25$  °C unless otherwise noted.

\*\*Power dissipation per package with four characters illuminated.

#### Notes:

3. Maximum allowable dissipation is derived from  $V_{CC}$  = 5.25 V,  $V_B$  = 2.4 V,  $V_{COL}$  = 3.5 V 20 LEDs on per character, 20% DF.

<sup>1.</sup> Operation above  $85^{\circ}$ C ambient is possible provided the following conditions are met. The junction temperature should not exceed  $125^{\circ}$ C T<sub>J</sub> and the case temperature (as measured at pin 1 or the back of the display) should not exceed  $100^{\circ}$ C T<sub>C</sub>.

<sup>2.</sup> The HDSP-2301/-2302/-2303 should be derated linearly above 37°C at 16.7 mW/°C. This derating is based on a device mounted in a socket having a thermal resistance from case to ambient at 35°\*\* C/W per device. See Figure 2 for power deratings based on a lower thermal resistance.

#### **Optical Characteristics** Yellow HDSP-2301

| Description                                                                | Symbol                  | Test Conditions                                                                                                                                          | Min. | Typ.* | Max. | Units | Fig. |

|----------------------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|------|

| Peak Luminous Intensity<br>per LED <sup>[4,8]</sup><br>(Character Average) | I <sub>vPeak</sub>      | $\label{eq:VCC} \begin{split} v_{CC} &= 5.0 \; \text{V}, v_{COL} = 3.5 \; \text{V} \\ T_i &= 25 ^\circ\text{C}^{[6]}, v_B = 2.4 \; \text{V} \end{split}$ | 650  | 1140  |      | μcd   | 3    |

| Peak Wavelength                                                            | $\lambda_{\text{PEAK}}$ |                                                                                                                                                          |      | 583   |      | nm    |      |

| Dominant Wavelength <sup>[5,7]</sup>                                       | $\lambda_d$             |                                                                                                                                                          |      | 585   |      | nm    |      |

#### **High Efficiency Red HDSP-2302**

| Description                                                                | Symbol                 | Test Conditions                                                                                                               | Min. | Typ.* | Max. | Units | Fig. |

|----------------------------------------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|------|

| Peak Luminous Intensity<br>per LED <sup>[4,8]</sup><br>(Character Average) | I <sub>vPeak</sub>     | $\label{eq:VCC} \begin{array}{l} V_{CC} = 5.0 \ V, V_{COL} = 3.5 \ V \\ T_i = 25 \ ^\circ C^{[6]}, V_B = 2.4 \ V \end{array}$ | 650  | 1430  |      | μcd   | 3    |

| Peak Wavelength                                                            | $\lambda_{	ext{PEAK}}$ |                                                                                                                               |      | 635   |      | nm    |      |

| Dominant Wavelength <sup>[7]</sup>                                         | $\lambda_{d}$          |                                                                                                                               |      | 626   |      | nm    |      |

#### **High Performance Green HDSP-2303**

| Description                                                                | Symbol                    | Test Conditions                                                                                                                                            | Min. | Typ.* | Max. | Units | Fig. |

|----------------------------------------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|------|

| Peak Luminous Intensity<br>per LED <sup>[4,8]</sup><br>(Character Average) | I <sub>vPeak</sub>        | $\label{eq:VCC} \begin{split} V_{CC} &= 5.0 \ \text{V}, V_{COL} = 3.5 \ \text{V} \\ T_i &= 25 \ ^\circ \text{C}^{[6]}, V_{B} = 2.4 \ \text{V} \end{split}$ | 1280 | 2410  |      | μcd   | 3    |

| Peak Wavelength                                                            | $\lambda_{\mathrm{PEAK}}$ |                                                                                                                                                            |      | 568   |      | nm    |      |

| Dominant Wavelength <sup>[5,7]</sup>                                       | $\lambda_{d}$             |                                                                                                                                                            |      | 574   |      | nm    |      |

\*All typical values specified at  $V_{CC}$  = 5.0 V and  $T_A$  = 25 °C unless otherwise noted.

\*\*Power dissipation per package with four characters illuminated.

#### Notes:

- 4. The characters are categorized for luminous intensity with the intensity category designated by a letter code on the bottom of the package.

- 5. The HDSP-2301/-2303 are categorized for color with the color category designated by a number code on the bottom of the package.

- 6. T<sub>i</sub> refers to the initial case temperature of the device immediately prior to the light measurement.

- 7. Dominant wavelength  $\lambda_d$ , is derived from the CIE chromaticity diagram, and represents the single wavelength which defines the color of the device.

- 8. The luminous sterance of the LED may be calculated using the following relationships:

$L_v (cd/m^2) = l_v (Candela)/A (Metre)^2$

$L_v$  (Footlamberts) =  $\pi i_v$  (Candela)/A (Foot)<sup>2</sup>

A = 5.3 x 10<sup>-8</sup> M<sup>2</sup> = 5.8 x 10<sup>-7</sup> (Foot)<sup>2</sup>

| PARAMETER                                                                        | CONDITION                                         | MIN. | TYP. | MAX. | UNITS |

|----------------------------------------------------------------------------------|---------------------------------------------------|------|------|------|-------|

| <sup>f</sup> CLOCK<br>CLOCK RATE                                                 |                                                   |      |      | 3    | MHz   |

| t <sub>PLH</sub> , t <sub>PHL</sub><br>PROPAGATION<br>DELAY CLOCK<br>TO DATA OUT | C <sub>L</sub> = 15 pF<br>R <sub>L</sub> = 2.4 KΩ |      |      | 125  | ns    |

Figure 1. Switching Characteristics HDSP-2301/-2302/-2303 (T  $_{\rm A}$  = -20°C to +85°C).

#### HDSP-2301/-2302/-2303

Figure 2. Maximum Allowable Power Dissipation vs. Temperature.

Figure 3. Relative Luminous Intensity vs. Temperature.

Figure 4. Peak Column Current vs. Column Voltage.

#### **Electrical Description**

The HDSP-230X series of four character alphanumeric displays have been designed to allow the user maximum flexibility in interface electronics design. Each four character display module features Data In and Data Out terminals arrayed for easy PC board interconnection. Data Out represents the output of the 7th bit of digit number 4 shift register. Shift register clocking occurs on the high to low transition of the Clock input. The like columns of each character in a display cluster are tied to a single pin. Figure 5 is the block diagram for the displays. High true data in the shift register enables the output current mirror driver stage associated with each row of LEDs in the 5 x 7 diode array.

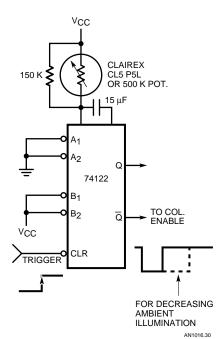

The TTL compatible  $V_B$  input may either be tied to  $V_{CC}$  for maximum display intensity or pulse width modulated to achieve intensity control and reduction in power consumption.

The normal mode of operation input data for digit 4, column 1,

|                      | Ambient Lighting                             |                                                                  |                 |  |  |  |

|----------------------|----------------------------------------------|------------------------------------------------------------------|-----------------|--|--|--|

| Display Color        | Dim                                          | Moderate                                                         | Bright          |  |  |  |

| HDSP-2301 (Yellow)   | Panelgraphic Yellow 27<br>Chequers Amber 107 | Polaroid HNCP37<br>3M Light Control Film<br>Panelgraphic Gray 10 |                 |  |  |  |

| HDSP-2302 (HER)      | Panelgraphic Ruby Red 60<br>Chequers Red 112 | Chequers Grey 105                                                | Polaroid HNCP10 |  |  |  |

| HDSP-2303 (HP Green) | Panelgraphic Green 48<br>Chequers Green 107  |                                                                  |                 |  |  |  |

Figure 6. Contrast Enhancement Filters.

is loaded into the 7 on-board shift register locations 1 through 7. Column 1 data for digits 3, 2, and 1 is similarly shifted into the display shift register locations. The column 1 input is now enabled for an appropriate period of time, T. A similar process is repeated for columns 2, 3, 4, and 5. If the time necessary to decode and load data into the shift register is t, then with five columns, each column of the display is operating at a duty factor of:

D.F. =

$$\frac{T}{5 (t + T)}$$

The time frame, t + T, allotted to each column of the display is generally chosen to provide the maximum duty factor consistent with the minimum refresh rate necessary to achieve a flicker free display. For most strobed display systems, each column of the display should be refreshed (turned on) at a minimum rate of 100 times per second.

With columns to be addressed, this refresh rate then gives a value for the time t + T of:

$1/[5 \ge (100)] = 2$  msec

If the device is operated at 3.0 MHz clock rate maximum, it is possible to maintain t << T. For short display strings, the duty factor will then approach 20%.

For further applications information, refer to Agilent Application Note 1016.

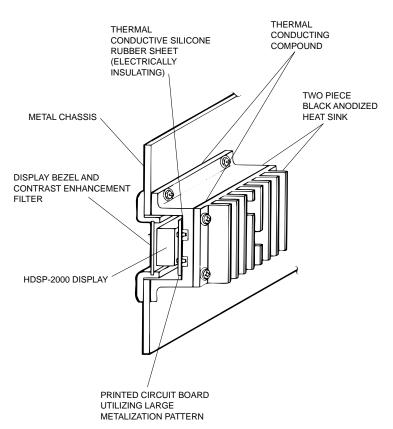

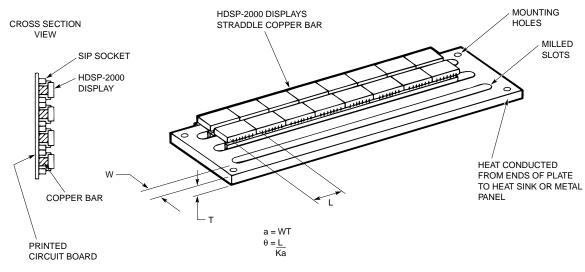

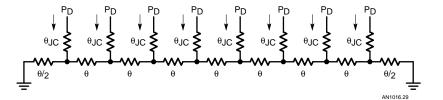

#### Mechanical and Thermal Considerations

The HDSP-2301/-2302/-2303 are available in standard ceramic dual-in-line packages. They are designed for plugging into sockets or soldering into PC boards. The packages may be horizontally or vertically stacked for character arrays of any desired size. The HDSP-2301/-2302/-2303 utilize a high output current IC to provide excellent readability in bright ambient lighting. Full power operation  $(V_{CC} = 5.25 \text{ V}, V_B = 2.4 \text{ V}, V_{COL})$ = 3.5 V) with worst case thermal resistance from IC junction to ambient of 60°C/watt/device is possible up to ambient temperature of 37°C. For operation above 37°C, the maximum device dissipation should be derated linearly at 16.7 mW/°C (see Figure 2). With an improved thermal design, operation at higher ambient temperatures without derating is possible.

Power derating for this family of displays can be achieved in several ways. The power supply voltage can be lowered to a minimum of 4.75 V. Column Input Voltage,  $V_{COL}$ , can be decreased to the recommended minimum value of 2.75 V for the HDSP-2301/-2302/-2303. Also, the average drive current can be decreased through pulse width modulation of  $V_B$ .

The HDSP-2301/-2302/-2303 displays have glass windows. A front panel contrast enhancement filter is desirable in most actual display applications. Some suggested filter materials are provided in Figure 6. Additional information on filtering and contrast enhancement can be found in Agilent Application Note 1015.

For more information on soldering and post-solder cleaning, please see Application Note 1027, Soldering LED Components.

# Agilent Technologies

www.semiconductor.agilent.com Data subject to change. Copyright © 1999 Agilent Technologies, Inc. Obsoletes 5953-7749E 5966-2487E (11/99)

# Using the HDSP-2000 Alphanumeric Display Family

# **Application Note 1016**

#### Introduction

First introduced in 1975, the HDSP-2000 alphanumeric display has been designed into a variety of applications. The HDSP-2000 display was originally designed for commercial, industrial, instrumentation, and business equipment applications. However, the introduction of high efficiency red, yellow, and high performance green devices as well as several display sizes has opened up a multitude of new applications for the HDSP-2000 alphanumeric display family. The high efficiency red, yellow, and high performance green devices use gallium phosphide (GaP) LEDs. The GaP displays are readable in direct sunlight with proper contrast enhancement techniques. For this reason, the HDSP-2000 family displays have been designed into a variety of avionic and process control applications. The HDSP-2000 family displays are available in three character sizes of 3.8 mm (0.15"), 4.9 mm (0.19"), and  $6.9 \text{ mm} (0.27^{"})$  to allow the designer to optimize display compactness versus long distance readability. Versions of the HDSP-2000 family alphanumeric displays are available with a true hermetic package and an operating temperature range of  $-55^{\circ}$ C to  $+85^{\circ}$ C to allow designers to utilize the proven reliability of LED display technology in military and aerospace applications.

This note is intended to serve as a design and application guide for users of the HDSP-2000 family of alphanumeric display devices. The information presented will cover: the theory of the device design and operation; considerations for specific circuit designs; thermal management, power derating and heat sinking; intensity modulation techniques.

The HDSP-2000 family has been designed to provide a high resolution information display subsystem. Each character of the 4 character package consists of a 5 x 7 array of LEDs which can display a full range of alphabetic and numeric characters plus punctuation, mathematical and other special symbols. The HDSP-2000 family is available in four colors: red, high efficiency red, yellow, and high performance green.

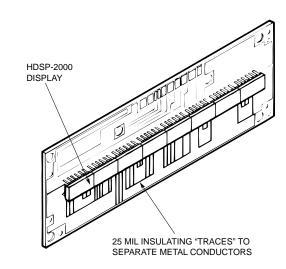

The character height, character spacing, color and part number of each member of the HDSP-2000 family of displays is shown in Table 1. The overall package size is designed to allow end stacking of multiple clusters to form character strings of any desired length.

#### **Electrical Description**

The on-board electronics of the HDSP-2000 display family eliminates some of the classical difficulties associated with the use of alphanumeric displays. Traditionally, single digit LED dot matrix displays have been organized in an x-y addressable array requiring 12 interconnect pins per digit plus extensive row and column drive support electronics. All members of the HDSP-2000 display family provide on-board storage of decoded row data plus constant current sinking row drivers for each of the 28 rows in the 4 character display. This approach allows the user to address each display package through just 11 active interconnections vs. the 176 interconnections and 36 components required to effect a similar function using conventional LED matrices.

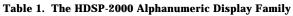

Figure 1 is a block diagram of the internal circuitry of the HDSP-2000 display. The device consists of four LED matrices and

| Device                                           | Color                                                          | Character<br>Height                                                                                   | Character<br>Spacing                                                                 | Operating<br>Temperature                                                               |

|--------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| HDSP-2000<br>HDSP-2001<br>HDSP-2002<br>HDSP-2003 | Red<br>Yellow<br>High Efficiency Red<br>High Performance Green | 3.8 mm (0.15 in.)<br>3.8 mm (0.15 in.)<br>3.8 mm (0.15 in.)<br>3.8 mm (0.15 in.)<br>3.8 mm (0.15 in.) | 4.5 mm (0.175 in.)<br>4.5 mm (0.175 in.)<br>4.5 mm (0.175 in.)<br>4.5 mm (0.175 in.) | -20°C to +85°C<br>-20°C to +85°C<br>-20°C to +85°C<br>-20°C to +85°C<br>-20°C to +85°C |

| HDSP-2300<br>HDSP-2301<br>HDSP-2302<br>HDSP-2303 | Red<br>Yellow<br>High Efficiency Red<br>High Performance Green | 4.9 mm (0.192 in.)<br>4.9 mm (0.192 in.)<br>4.9 mm (0.192 in.)<br>4.9 mm (0.192 in.)                  | 5.0 mm (0.197 in.)<br>5.0 mm (0.197 in.)<br>5.0 mm (0.197 in.)<br>5.0 mm (0.197 in.) | -20°C to +85°C<br>-20°C to +85°C<br>-20°C to +85°C<br>-20°C to +85°C<br>-20°C to +85°C |

| HDSP-2490<br>HDSP-2491<br>HDSP-2492<br>HDSP-2493 | Red<br>Yellow<br>High Efficiency Red<br>High Performance Green | 6.9 mm (0.27 in.)<br>6.9 mm (0.27 in.)<br>6.9 mm (0.27 in.)<br>6.9 mm (0.27 in.)                      | 8.9 mm (0.35 in.)<br>8.9 mm (0.35 in.)<br>8.9 mm (0.35 in.)<br>8.9 mm (0.35 in.)     | -20°C to +85°C<br>-20°C to +85°C<br>-20°C to +85°C<br>-20°C to +85°C<br>-20°C to +85°C |

| HDSP-2010                                        | Red                                                            | 3.8 mm (0.15 in.)                                                                                     | 4.5 mm (0.175 in.)                                                                   | -40°C to +85°C                                                                         |

| HDSP-2310<br>HDSP-2311<br>HDSP-2312              | Red<br>Yellow<br>High Efficiency Red                           | 4.9 mm (0.192 in.)<br>4.9 mm (0.192 in.)<br>4.9 mm (0.192 in.)                                        | 5.0 mm (0.197 in.)<br>5.0 mm (0.197 in.)<br>5.0 mm (0.197 in.)                       | -55°C to +85°C<br>-55°C to +85°C<br>-55°C to +85°C                                     |

| HDSP-2450<br>HDSP-2451<br>HDSP-2452              | Red<br>Yellow<br>High Efficiency Red                           | 6.9 mm (0.27 in.)<br>6.9 mm (0.27 in.)<br>6.9 mm (0.27 in.)                                           | 8.9 mm (0.35 in.)<br>8.9 mm (0.35 in.)<br>8.9 mm (0.35 in.)                          | -55°C to +85°C<br>-55°C to +85°C<br>-55°C to +85°C                                     |

two 14-bit serial-in-parallel-out shift registers. The LED matrix for each character is a 5 x 7 diode array organized with the anodes of each column tied in common and the cathodes of each row tied in common. The 7 row cathode commons of each character are tied to the constant current sinking outputs of 7 successive stages of the shift register. The like columns of the 4 characters are tied together and brought to a single address pin (i.e., column 1 of all 4 characters is tied to pin 1, etc.). In this way, any diode in the four  $5 \times 7$ matrices may be addressed by shifting data to the appropriate shift register location and applying a voltage to the appropriate column.

The serial-in-parallel-out (SIPO) shift register has a constant current sinking output associated with each shift register stage. This constant current output drives each LED at a nominal peak current of 12 to 14 mA peak. The output stage is a current mirror design with a nominal current gain of 10. A logical 1 loaded into each shift register bit will turn "ON" the corresponding current source provided that a logical 1 is applied to the Blanking Input, V<sub>B</sub>. If V<sub>COL</sub> is applied to the appropriate Column Input, the corresponding LED diode will be turned "ON". Since the row drivers have a constant current output, the LED current will remain constant as long as the **Column Input voltage exceeds 2.4** V for red and 2.75 V for high efficiency red, yellow, and high performance green devices.

Data is loaded serially into the shift register on the high to low transition of the Clock Input. During the time that data is being loaded into the display, the column current must be disabled to minimize the generation of "current spikes" between  $V_{CC}$ , the columns, and ground. The resulting power supply noise could induce noise on the Clock and Data Inputs. The column current can be disabled either by switching off the column drivers or by applying a logical 0 to the Blanking Input.

The Data Output terminal is a TTL buffer interface to the 28th bit of the shift register (i.e., the 7th row of character 4 in each package) The Data Output is arranged to directly interconnect to the Data Input on a succeeding 4 digit HDSP-2000 display package. The Data, Clock and V<sub>B</sub> inputs are all buffered to allow direct interface to any TTL logic family.

#### **Theory of Operation**

Dot matrix alphanumeric display systems generally have a logical organization which prescribes that any character be generated as a combination of several subsets of data. In a 5 x 7 matrix, this could be either 5 subsets of 7 bits each or 7 subsets of 5 bits each. This technique is utilized to reduce from 35 to 5 or 7 the number of outputs required from the character generator. In order to display a complete character, these subsets of data are then presented sequentially to the appropriate locations of the display matrix. If this process is repeated at a rate which insures that each of the appropriate matrix locations is reenergized a minimum of 100 times per second, the eye will perceive a continuous image of the entire character. The apparent intensity of each of the display elements will be equal to

the intensity of that element during the "ON" period multiplied by the ratio of "ON" time to refresh period. This ratio is referred to as the display duty factor, and the technique is referred to as "strobing". In the case of HDSP-2000, each character is made up of 5 subsets of 7 bits. For a four character display, 28 bits representing the first subset of each of the four characters are loaded serially into the on-board SIPO shift register and the first column is then energized for a period of time, T. This process is then repeated for columns 2 through 5. If the time required to load the 28 bits into the SIPO shift register is t, then the duty factor is:

$$D.F. = \frac{T}{5(t+T)};$$

(1)

the term 5(t + T) is then the refresh period. For satisfactory display, the refresh period should be:

$$1/[5(t+T)] \ge 100 \text{ Hz}$$

(2)

or conversely

$$5(t+T) \le 10 \text{ m sec},$$

(3)

which gives

$$(t+T) \leq 2 m \sec.$$

(4)

The time averaged luminous intensity of the display can be varied continuously over a range greater than 1000 to 1 by turning off or blanking the display before loading new data into the SIPO shift register. If the time that the display is blanked is  $T_B$ , then the duty factor of the display becomes:

$$D.F. = \frac{T}{5(t+T+T_B)}$$

(5)

where

$$(t+T+T_B) \leq 2 m \operatorname{sec.}$$

(5a)

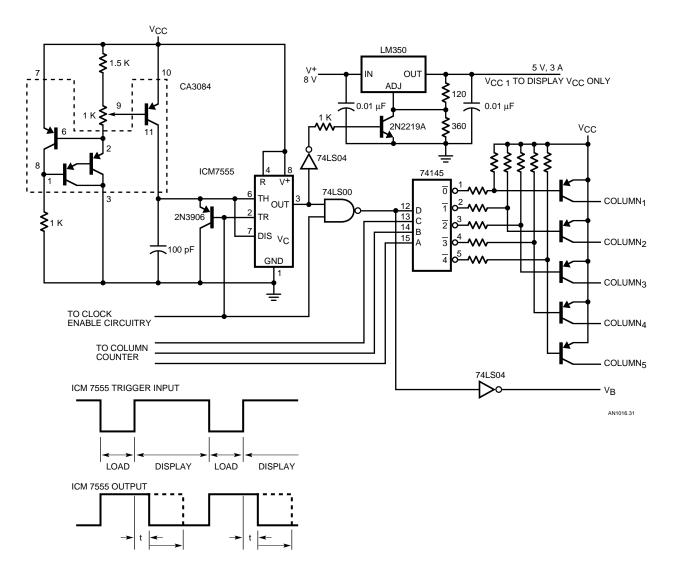

#### **Drive Circuit Concepts**

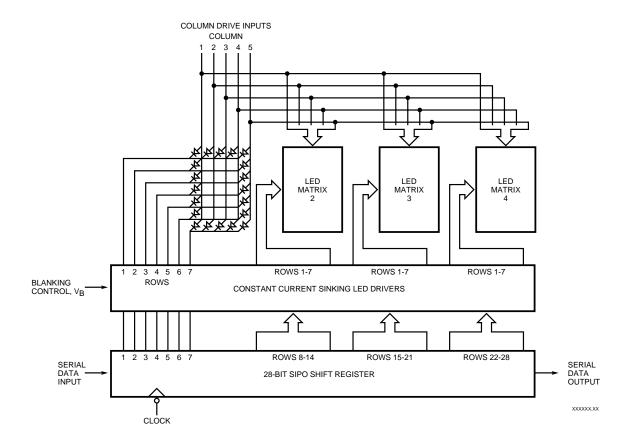

A practical display system utilizing the HDSP-2000 family of displays requires interfacing with a character generator, refresh memory and some timing circuitry. A block diagram of such a display system is depicted in Figure 2. This circuit provides for ASCII data storage and decoding and properly refreshes the display at a 100 Hz refresh rate. In this figure, the display length is shown as N characters with the leftmost display character labeled as character 1 and the right most character of the display labeled as character N. The refreshing of the display is accomplished by a series of counters.

Each coded information symbol is read from the N x 7 RAM and decoded by a 5 x 7 decoder. The decoder can be selected to decode ASCII, EBDIC, or any customized character font In this example, the ASCII decoder is organized as 128 x 7 words of 5 bits each. The ASCII symbol and row select information is applied to the decoder and the decoder outputs information for all 5 columns for the selected row and symbol. The ÷7 counter sequentially accesses all seven rows of each ASCII symbol. Note that row 7 must be decoded first, then row 6, and row 1 is decoded last. The ÷M counter is used to periodically load new serial data into the HDSP-2000 display. During one count, the display clock is enabled and 7N bits of serial data are loaded into the display. During the remaining (M1) counts, this data is displayed. Thus the duty factor for the circuit in Figure 2 is

D.F. =

$$\frac{(M-1)}{5 M}$$

= .20  $\left(1 - M^{-1}\right)$  (6)

The  $\div$ 5 counter sequentially refreshes all 5 columns of the display. The outputs of the  $\div$ 5 counter are connected to a data multiplexer which selects one of the 5 outputs from the ASCII decoder and loads it into the Data Input of the HDSP-2000 display string. The  $\div$ 5 counter also enables one of the 5 column driver

transistors. Note that the display is blanked via the  $V_B$  input and also that the column driver transistors are turned off during the time that new data is being loaded into the HDSP-2000 display string. This will eliminate any high current transients between the column inputs and ground during the data shifting operation.

Since data is loaded for all of the like columns in the display string and these columns are then enabled simultaneously, only five column switch transistors are required regardless of the number of characters in the string. The column switch transistors should be selected to handle 105 to 130 mA per character in the display string. The collector emitter saturation voltage characteristics and column voltage supply should be chosen to provide 2.4 V  $\leq$  V<sub>COL</sub>  $\leq$ V<sub>CC</sub> for the standard red displays and 2.75 V  $\leq$  V<sub>COL</sub>  $\leq$  V<sub>CC</sub> for the high efficiency red, yellow, and high performance green displays. To save on power supply costs and improve efficiency, this supply may be a fullwave rectified unregulated DC voltage as long as the PEAK value does not exceed the value of V<sub>CC</sub> and the minimum value does not drop below 2.4 V or 2.75 V depending on display color.

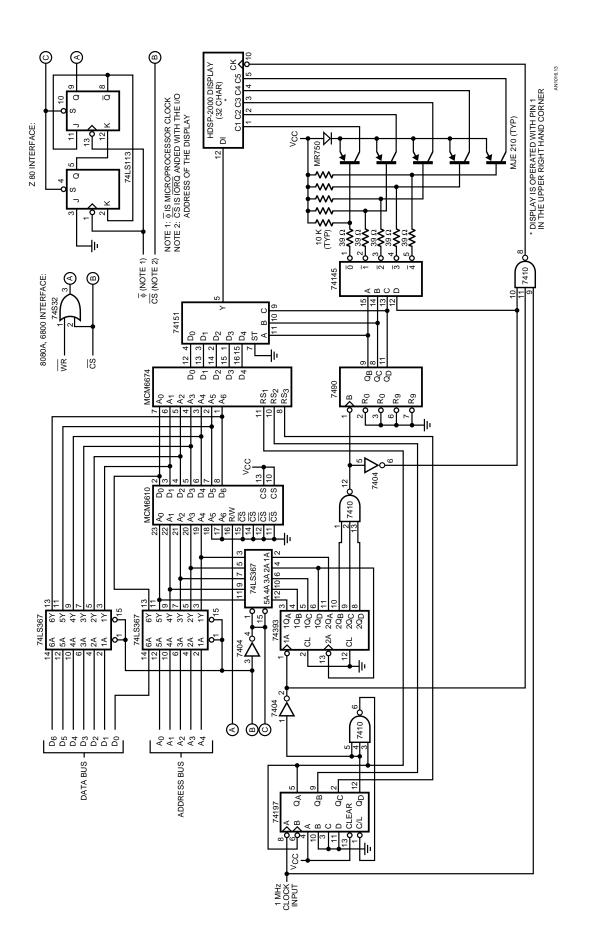

Figures 13 and 16 show practical implementations of the block diagram shown in Figure 2. In those circuits, the display is mounted upside down, so that pin 1 is in the upper right hand corner. With this technique, data is loaded into display character N and data shifts from right to left as new data is loaded. The first bit loaded into the display would be row 1, character 1, then row 2, etc., and the last bit loaded would be row 7

of character N. This allows the  $\div$ 7, +N and +M counters to be implemented as up counters instead of down counters. Since the display is upside down, column 5 of the display appears to be column 1 and column 4 of the display appears to be column 2. Thus, column 1 data for the display must be loaded into the display and column 5 must subsequently be enabled. This is accomplished by reversing the outputs of the 5 x 7 decoder. The D<sub>0</sub>, D<sub>1</sub>, D<sub>2</sub>, D<sub>3</sub>, and D<sub>4</sub> outputs of the MCM6674 decoder output column 5, column 4, column 3, column 2, and column 1 information.

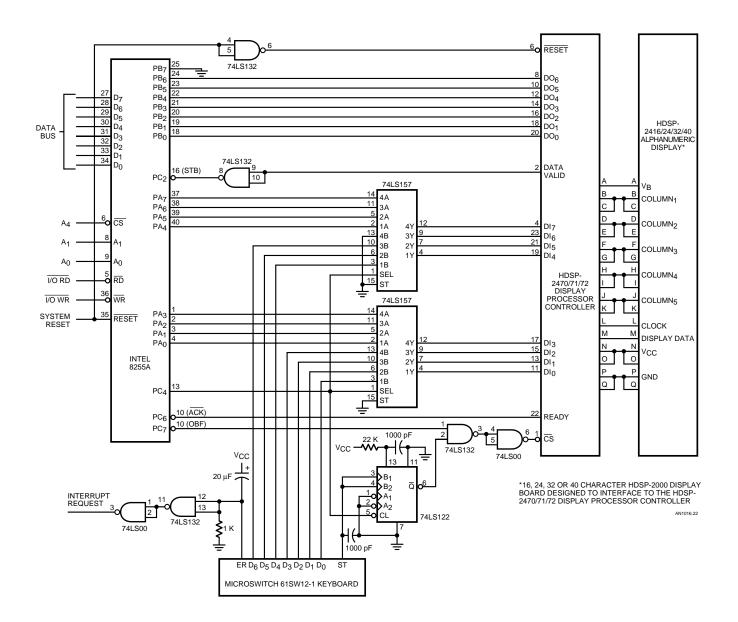

### Interfacing the HDSP-2000 Display to Microprocessors

Because of the complexity of dealing with alphanumeric information, a microprocessor based system is typically used in conjunction with the HDSP-2000 family displays. Depending upon overall systems configuration, microprocessor time available to dedicate to display support, and the type of information to be displayed, one may choose several different partitioning schemes to drive such a display.

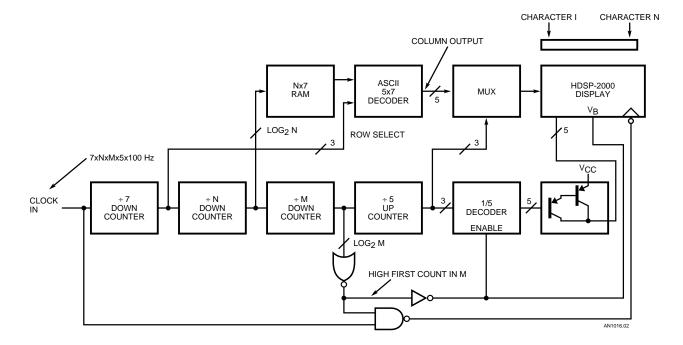

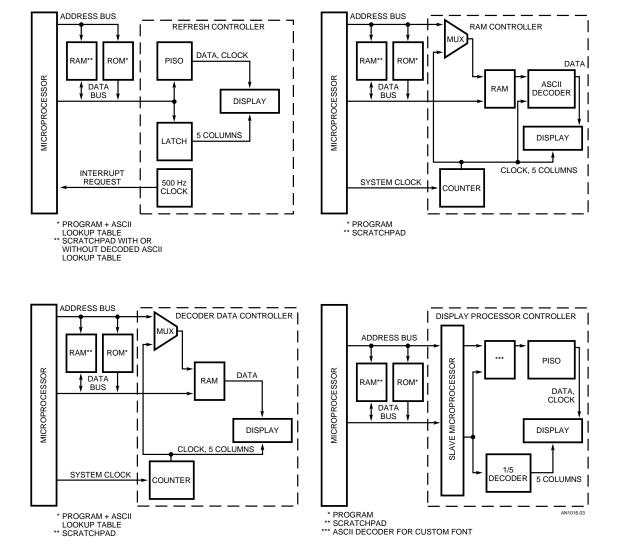

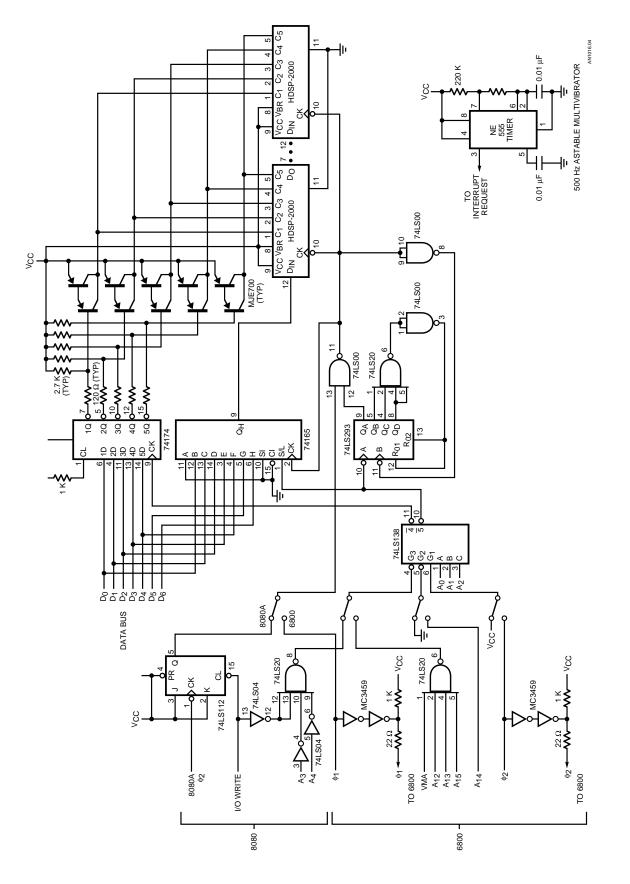

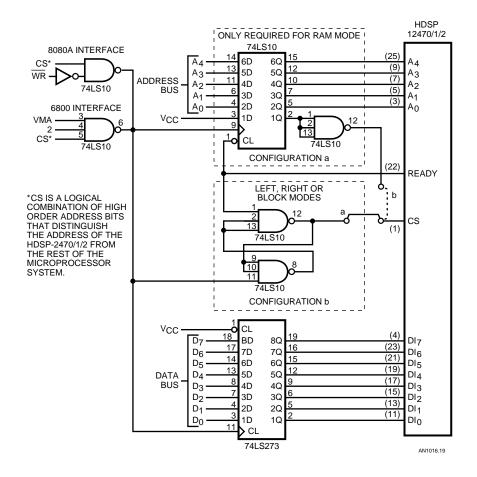

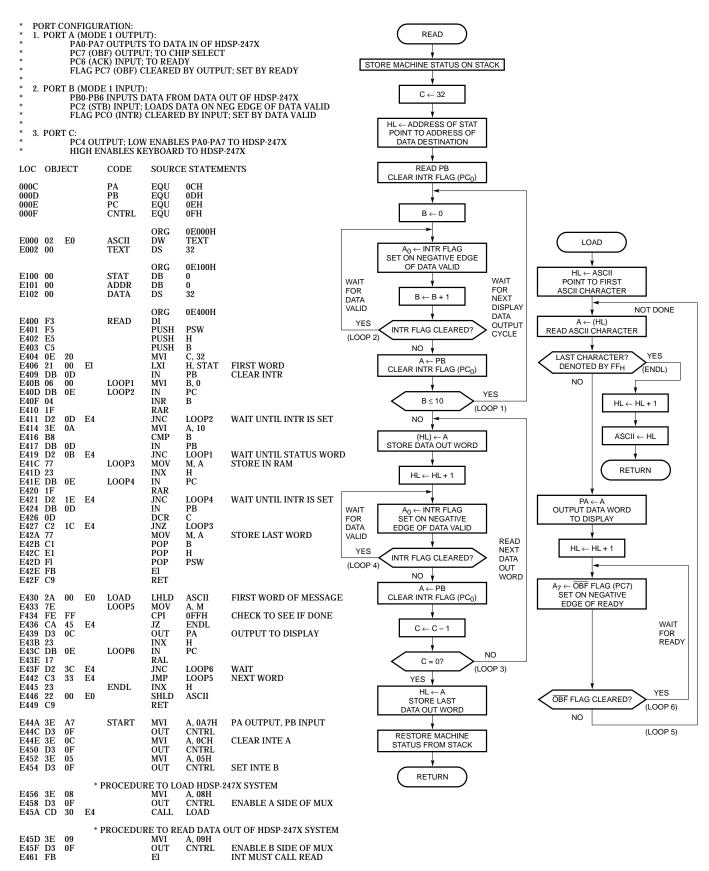

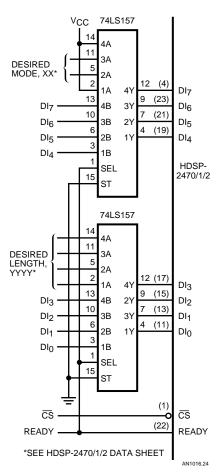

Figure 3 shows four different techniques to interface the HDSP-200 family displays to microprocessor systems:

- 1. The REFRESH CONTROLLER interrupts the microprocessor at a 500 Hz rate to request refresh data for the display.

- 2. The DECODED DATA CON-TROLLER accepts 5 x 7 matrix data from the microprocessor and then automatically refreshes the display with the

same information until new data is supplied by the microprocessor.

- 3. The CODED DATA CONTROL-LER accepts ASCII data and interfaces like a RAM to the microprocessor.

- 4. The DISPLAY PROCESSOR CONTROLLER (HDSP-247X series) employs a dedicated single chip microprocessor as a data display/control/keyboard interface which has many of the features of a complete terminal.

The interface techniques depicted are specifically for the 8080A or 6800 microprocessor families. Extension of these techniques to other processors should be a relatively simple software chore with little or no hardware changes required.

The choice of a particular interface is an important consideration because it affects the design of the entire microprocessor system. The REFRESH CONTROLLER provides the lowest cost interface because it uses the microprocessor to provide ASCII decoding and display strobing. Because the ASCII decoder is located within the microprocessor system, the designer has total control over the display font within the program. This feature is particularly important when the system will be used to display different languages and special graphic symbols. However, the REFRESH CON-TROLLER requires a significant amount of microprocessor time. Furthermore, while the interrupt allows the refresh program to operate asynchronously from the main program, this technique

limits some of the software techniques that can be used in the main program.

The DECODED DATA CONTROL-LER requires microprocessor interaction only when the display message is changed. Like the RE-FRESH CONTROLLER, the ASCII decoder is located within the microprocessor program. However, the time required to decode the ASCII string and store the resulting 5 x 7 display data into the interface requires several milliseconds of microprocessor time.

#### The CODED DATA CONTROL-

LER also requires interaction from the microprocessor system only when the display message is changed. Because the ASCII decoder is located within the display interface, the microprocessor requires much less time to load a new message into the display.

The DISPLAY PROCESSOR CON-TROLLER, the HDSP-247X series, is the most powerful interface. The software within the DISPLAY PROCESSOR CONTROLLER further reduces the host microprocessor interaction by providing more powerful left and right data entry modes compared to the RAM entry mode of the DE-CODED DATA and CODED DATA CONTROLLERS. The DISPLAY PROCESSOR CONTROLLER can also provide features such as a Blinking Cursor, Editing Commands, and a Data Out function. One version of the DISPLAY PRO-CESSOR CONTROLLER allows the user to provide a custom ASCII decoder for applications needing a special character font.

Figure 3. Four Different Techniques to Interface the HDSP-2000 Alphanumeric Display to a Microprocessor System

Figure 4. 6800 or 8080A Microprocessor Interface to the HDSP-2000 REFRESH CONTROLLER

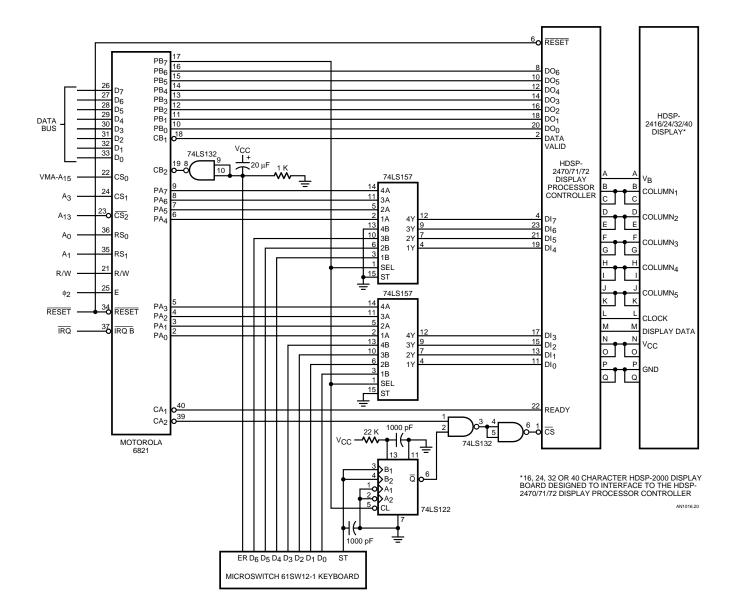

#### **Refresh Controller**

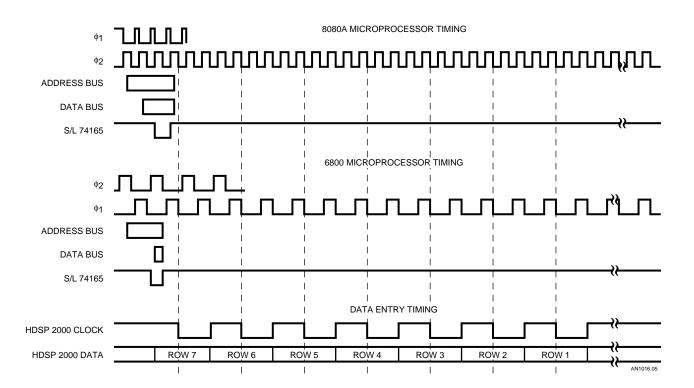

The REFRESH CONTROLLER circuit depicted in Figure 4 operates by interrupting the microprocessor every two milliseconds to request a new block of display data and column select data. Display data is loaded from the data bus into the serial input of the HDSP-2000 via a 74165 parallel in, serial out shift register. The 74LS293 counter and associated gates insure that only seven clock pulses are delivered to the shift register and the HDSP-2000 for each word loaded. Column Select data is loaded into a 74174 latch which, in turn, drives the column switch transistors. The circuit timing relative to the microprocessor clock and I/O is depicted in Figure 5.

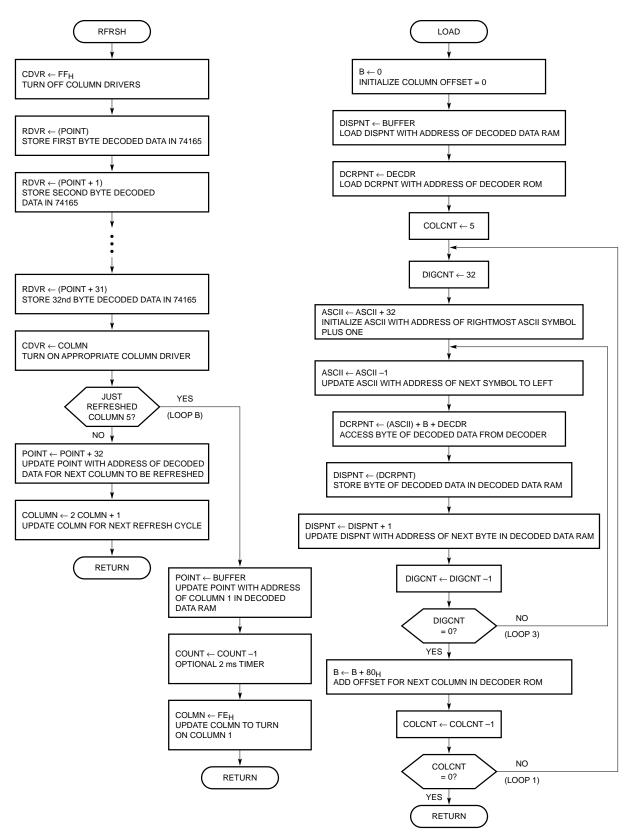

The 6800 software necessary to support this interface is divided

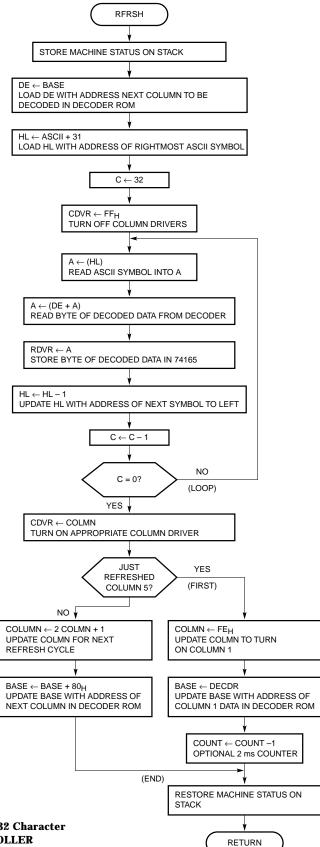

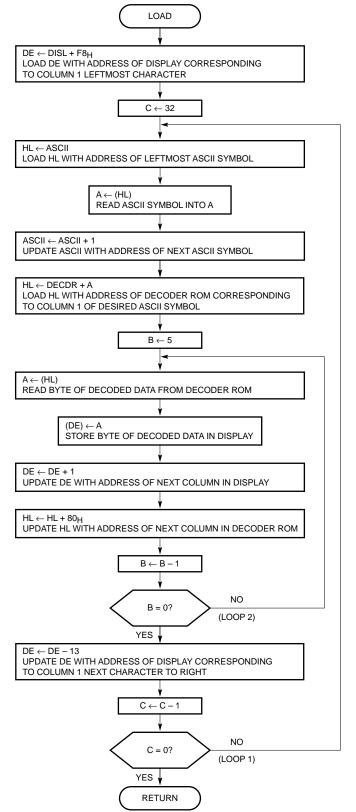

into two separate subroutines, "RFRSH" and "LOAD" (Figure 6). This approach is desirable to minimize microprocessor involvement during display refresh. The subroutine "RFRSH" loads a new set of decoded display data from the microprocessor scratchpad memory into the interface at each interrupt request. The subroutine "LOAD" is utilized to decode a string of 32 ASCII characters into 5 x 7 formatted display data and store this data in the scratchpad memory used by "RFRSH".

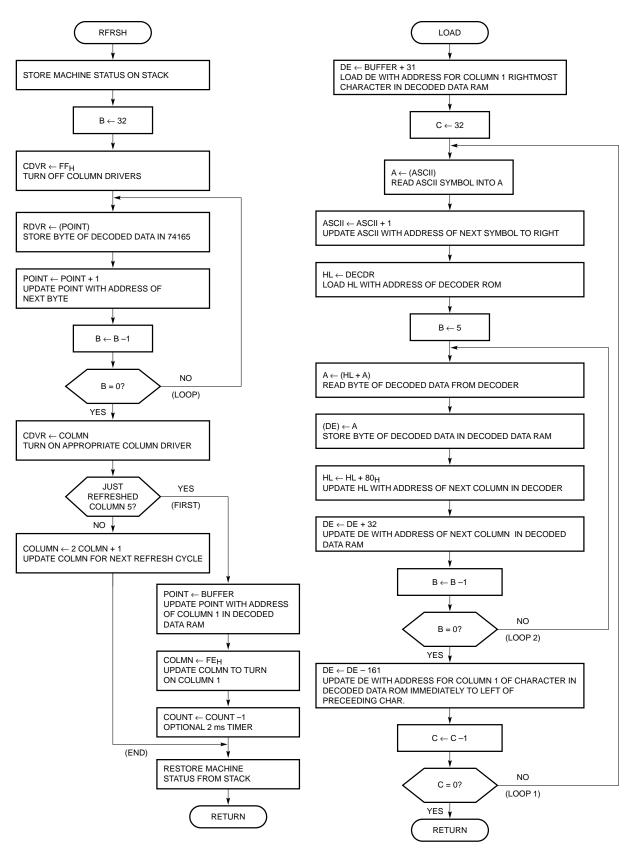

Figures 7 and 8 depict two different software routines for interfacing the REFRESH CON-TROLLER to an 8080A microprocessor. The two subroutines shown in Figure 7 are functional replacements for the 6800 program shown in Figure 6. The programs shown in Figures 6 and 7 require a 5N byte scratchpad memory where N is the display length. The routine in Figure 8 eliminates this scratchpad memory by decoding and loading data each time a new interrupt request is received.

Because the microprocessor system is interrupted every 2 ms, proper software design is especially important for the REFRESH CONTROLLER. The use of the scratchpad memory significantly reduces the time required to refresh the display. The fastest program, shown in Figure 6, uses in-line code to access data from the buffer and output it to the display. This program requires 3.7% + .50N% of the available microprocessor time for a 1 MHz clock. The program shown in Figure 7 is similar to the one shown in Figure 6, except that it uses a program

Figure 5. REFRESH CONTROLLER Timing

loop instead of the in-line code. This program uses 5.4% + .93N% of the microprocessor time for a 2 MHz clock. These programs utilize a subroutine "LOAD" which is called whenever the display message is changed. This subroutine executes in 10.2 ms and 7.5 ms respectively for Figure 6 and Figure 7. The program in Figure 8 uses 7.6% + 1.35N% of the microprocessor time for a 2 MHz clock. A 50% reduction in the previously described microprocessor times can be achieved by using faster versions of the 6800 and 8080A microprocessors.

The ASCII to 5 x 7 dot matrix decoder used by the programs in Figures 6, 7, and 8 is located within the microprocessor program. This decoder requires 640 bytes of storage to decode the 128 character ASCII set. The decoder used by these controllers is formatted so that the first 128 bytes contain column 1 information; the next 128 bytes contain column 2 information, etc. Each byte of this decoder is formatted such that D<sub>6</sub> through D<sub>0</sub> contain Row 7 through Row 1 display data respectively. The data is coded so that a HIGH bit will turn the corresponding 5 x7 display dot ON. This decoder table is shown in Figure 9. The resulting 5 x 7 dot matrix display font is shown in the HDSP-2471 data sheet.

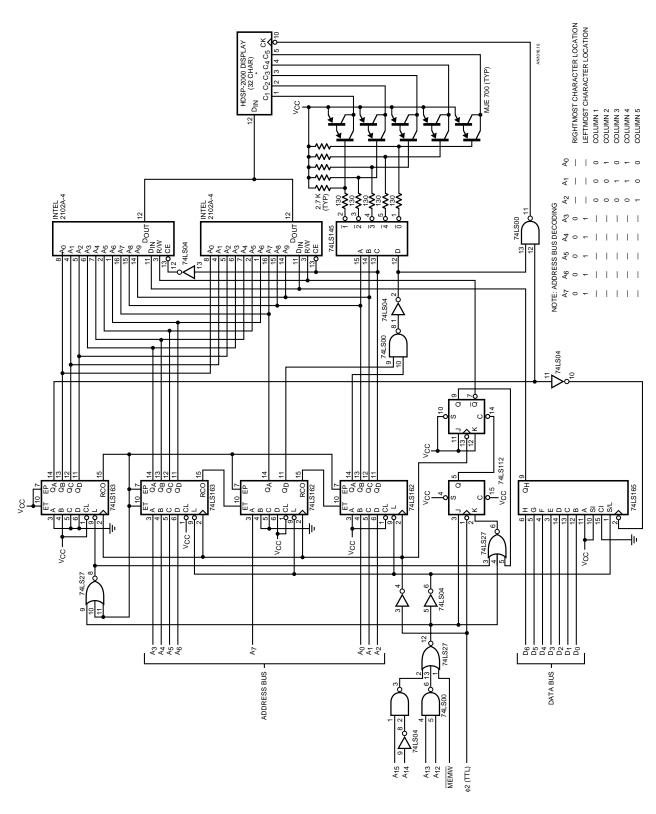

#### **Decoded Data Controller**

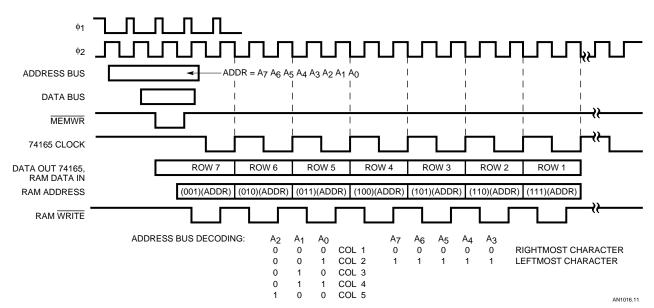

The DECODED DATA CONTROL-LER circuit schematic for a 32 character display is depicted in Figure 10. The circuit is specifically designed for interface to an 8080A microprocessor. This circuit is designed to accept and store in local memory all of the display data for a 32 character HDSP-2000 display (1120 bits). The microprocessor loads 160 bytes of display data into the two 1 K x 1 RAM's via the 74165 parallel in, serial out shift register. Each byte of data represents one column of display data. The counter string automatically generates the proper address location for each serial bit of data after initialization by MEM W, the character address, and the desired column. Once the loading is complete, the counter sequentially loads and displays each column (224 bits) of data at a 90 Hz rate (2 MHz input clock rate). The timing for this circuit is shown in Figure 11. The software required to decode a 32 character ASCII string is shown in Figure 12. This program decodes the 32 ASCII characters into 160 bytes of display data which are then stored in the controller. The program requires about 6.6 ms, for a 2 MHz clock, to decode and load the message into the DECODED DATA CONTROLLER. This program also uses the same decoder table as shown in Figure 9.

#### **Coded Data Controller**

The CODED DATA CONTROL-LER (Figure 13) is designed to accept ASCII coded data for storage in a local 128 x 8 RAM. After the microprocessor has loaded the RAM, local scanning circuitry controls the decoding of the ASCII, the display data loading, and the column select function. With minor modification, the circuit can be utilized for up to 128 display characters. The RAM used in this circuit is an MCM6810P with the Address and Data inputs isolated via 74LS367 tri-state buffers. This allows the RAM to be accessed either by the microprocessor or by the local electronics. The protocol is arranged such that the microprocessor always takes

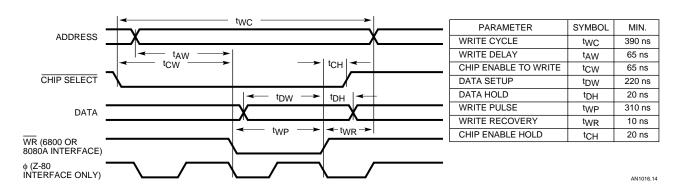

precedence over the local scanning electronics. The "Write" cycle timing for the CODED DATA CONTROLLER is depicted in Figure 14. This circuit, as with the DECODED DATA CONTROL-LER, requires no microprocessor time once the local RAM has been loaded with the desired data.

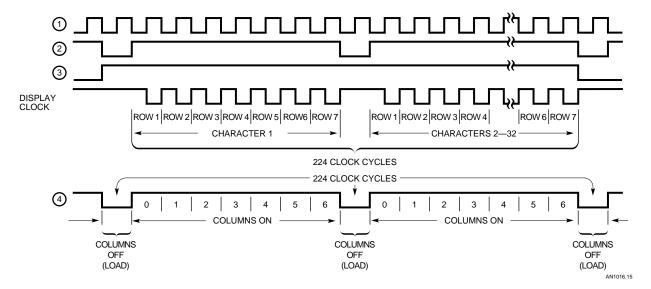

The circuit shown in Figure 13 shows a CODED DATA CON-**TROLLER** designed for a 32 character HDSP-2000 alphanumeric display. The key waveforms shown in Figure 15, labeled ①, ②, and ③, are shown to simplify the analysis of this circuit. Label ① is the 1 MHz clock. Label (2) is the output of 7404 pin 2 which is the inverted Q<sub>D</sub> output of the 74197. Label ③ is the output of the 7404 pin 6 which is the ANDed output of 2Q<sub>B</sub>, 2Q<sub>C</sub>, and 2Q<sub>D</sub> of the 74393. The Motorola 6810 RAM stores 32 bytes of ASCII data which is continuously read, decoded, and displayed. The ASCII data from the RAM is decoded by the Motorola 6674 128 character ASCII decoder. The 6674 decoder has five column outputs which are gated to the Data Input of the display via a 74151 multiplexer. Strobing of the display is accomplished via the 74197, 74393, and 7490 counter string. The 74197 is connected as a divide by 8 counter that sequentially selects the seven rows within the 6674. As shown by waveform (2), the 74197 also enables seven clock cycles to be gated to the clock input of the display. The 74393 is a divide by 256 counter connected so that the five lowest order outputs select each of the 32 ASCII characters within the RAM. The three highest order outputs determine the relationship between load time and column on time. When  $2Q_B = 2Q_C = 2Q_D = 1$  of the

74393, waveform ③ goes to a logical 1. The circuit then scans 32 characters from the RAM and serializes the column data by counting through each of the seven rows of the 6674 and gating the appropriate column of the display. During the seven counts when  $2Q_B$ ,  $2Q_C$ , and  $2Q_D$  of the 74393 are not equal to a logical 1, the column data is displayed, as shown in waveform ④). The duty factor of the display shown in Figure 13 is 17.5%.

Changing the display length to 64 characters is a simple modification. This configuration can be easily realized by disconnecting  $2Q_B$  of the 74393 from the 7410 and connecting it through the remaining tri-state buffer on the 74LS367 and using the 6810 RAM to store 64 ASCII characters. By leaving only 2Q<sub>C</sub> and 2Q<sub>D</sub> attached to the 7410, the column on time of the display is reduced from 17.5% to 15%. This reduction is caused because the relationship between actual column on time and theoretical column on time is 3/4 as opposed to 7/8 for the 32characters. Since the display length has been doubled, the drive transistors must be upgraded to handle the higher column currents.

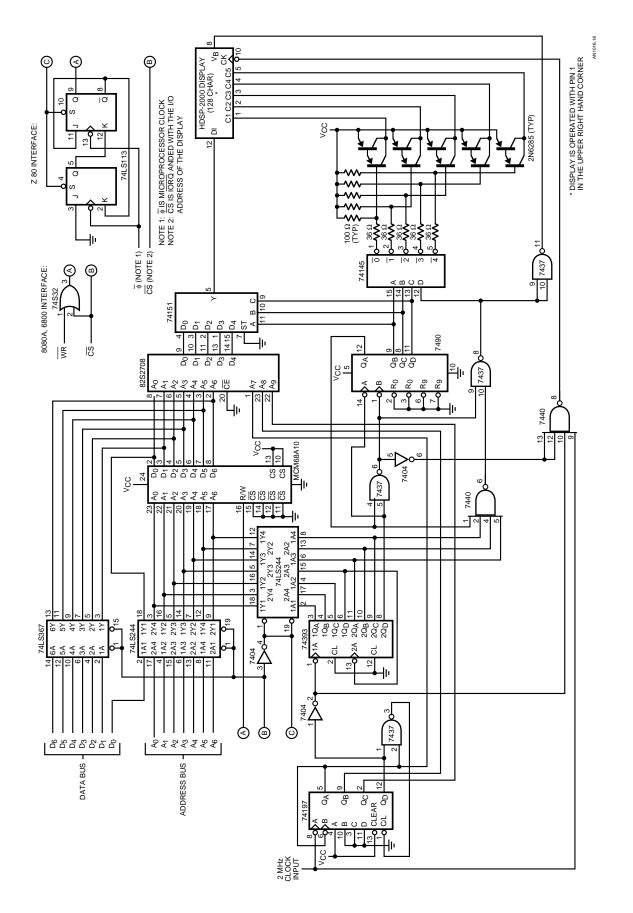

To implement a 128 character display, several modifications are needed. These changes are incorporated into the circuit in Figure 16. First, the input clock frequency has been increased to 2 MHz. This has been done to maintain a refresh rate of approximately 100 Hz for each digit, thus providing a flicker-free display. This higher speed of operation causes propagation delay problems within the MCM6674 (NMOS) whose maximum access time is 350 ns. For this reason, the

| LOC                                                                                                                                                                                  |                                                                                                                            | )BJEC<br>CODE                                                                                                              |                            | SOURCE S                                              | STATEMEN                                                                                                                                                                                                          | ITS                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000<br>0002<br>0003                                                                                                                                                                 | BF<br>Bl<br>06                                                                                                             | 05<br>04<br>00                                                                                                             |                            | *<br>CDVR<br>RDVR<br>DECDR<br>POINT<br>COLMN<br>COUNT | EQU<br>EQU<br>EQU<br>RMB<br>RMB<br>RMB                                                                                                                                                                            | SBF05<br>SBF04<br>S0600<br>2<br>1<br>2                                                                                                                                                                            |

| 0005<br>0007<br>0009<br>000B<br>000C                                                                                                                                                 | 00                                                                                                                         | AD                                                                                                                         |                            | ASCII<br>DISPNT<br>DCRPNT<br>COLCNT<br>DIGCNT         | FDB<br>RMB<br>RMB<br>RMB<br>RMB                                                                                                                                                                                   | DATA<br>2<br>2<br>1<br>1                                                                                                                                                                                          |

| 000D<br>00AD                                                                                                                                                                         |                                                                                                                            |                                                                                                                            |                            | BUFFR<br>DATA                                         | RMB<br>RMB                                                                                                                                                                                                        | 160<br>32                                                                                                                                                                                                         |

| 0400<br>0400<br>0402<br>0405<br>0407<br>0409<br>040C<br>040E                                                                                                                         | 86<br>B7<br>DE<br>A6<br>B7<br>A6<br>B7                                                                                     | FF<br>BF<br>00<br>00<br>BF<br>01<br>BF                                                                                     | 05<br>04<br>04             | RFRSH<br>LOOPHH                                       | ORG<br>LDA A<br>STA A<br>LDX<br>LDA A<br>STA A<br>LDA A<br>STA A<br>•                                                                                                                                             | \$0400<br>I, \$FF<br>E, CDVR<br>D, POINT<br>X, 0<br>E, RDVR<br>X, I<br>E, RDVR                                                                                                                                    |

| 04A2<br>04A4<br>04A7<br>04A9<br>04AC<br>04B2<br>04B4<br>04B6<br>04B8<br>04B8<br>04B8<br>04BB<br>04BC<br>04B7<br>04C0<br>04C3<br>04C5<br>04C7<br>04C8<br>04CA<br>04CC<br>04C2         | A6<br>B7<br>96<br>B7<br>81<br>27<br>D6<br>CB<br>D7<br>24<br>7C<br>OD<br>79<br>3B<br>CE<br>DF<br>09<br>DF<br>86<br>97<br>3B | 1F<br>BF<br>02<br>BF<br>EF<br>10<br>00<br>20<br>00<br>00<br>00<br>00<br>00<br>00<br>00<br>00<br>00<br>00<br>03<br>FE<br>02 | 04<br>05<br>00<br>02<br>0D | LOOPA<br>LOOPB                                        | LDA A<br>STA A<br>LDA A<br>STA A<br>CMP A<br>BEQ<br>LDA B<br>ADD B<br>STA B<br>BCC<br>INC<br>STA<br>BCC<br>INC<br>RTI<br>LDX<br>STX<br>LDX<br>STX<br>LDX<br>STX<br>LDA A<br>STA<br>A<br>RTI                       | X, 31<br>E, RDVR<br>D, COLMN<br>E, CDVR<br>I, SEF<br>LOOPB<br>D, POINT +1<br>I, 32<br>D, POINT +1<br>LOOPA<br>E, POINT<br>E, COLMN<br>I, BUFFER<br>D, POINT<br>D, COUNT<br>I, SFE<br>D, COLMN                     |

| 04CF<br>04D0<br>04D3<br>04D5<br>04D7<br>04D9<br>04DB<br>04DB<br>04DF<br>04E1<br>04E2                                                                                                 | 5F<br>CE<br>DF<br>86<br>97<br>86<br>97<br>86<br>97<br>9B                                                                   | 00<br>07<br>06<br>09<br>05<br>0B<br>20<br>0C<br>06                                                                         | OD                         | LOAD<br>LOOP I                                        | CLR B<br>LDX<br>STX<br>LDA A<br>STA A<br>LDA A<br>STA A<br>LDA A<br>STA A<br>ADD A                                                                                                                                | I, BUFFR<br>D, DISPNT<br>I, < DECDR<br>D, DCRPNT<br>I, 5<br>D, COLCNT<br>I, 32<br>D, DIGCNT<br>D, ASCII+1                                                                                                         |

| 04E3<br>04E5<br>04E8<br>04EA<br>04EC<br>04ED<br>04FF<br>04F1<br>04F2<br>04F4<br>04F6<br>04F8<br>04FA<br>04FC<br>04FD<br>04FF<br>0502<br>0504<br>0506<br>0508<br>0508<br>050E<br>0510 | 24<br>7C<br>97<br>DE<br>09<br>A6<br>DF<br>1B<br>97<br>DE<br>A6<br>DF<br>A6<br>DF<br>7A<br>26<br>24<br>7C<br>26<br>39       | 03<br>00<br>06<br>05<br>00<br>05<br>0A<br>09<br>00<br>07<br>00<br>07<br>00<br>07<br>00<br>E6<br>80<br>03<br>00<br>00<br>CD | 05<br>0C<br>09<br>0B       | LOOP2<br>LOOP3                                        | BCC<br>INC<br>STA A<br>LDX<br>DEX<br>LDA A<br>STX<br>ABA<br>STA A<br>LDX<br>LDA A<br>LDX<br>LDA A<br>LDX<br>STA A<br>INX<br>STA A<br>INX<br>STA A<br>INX<br>STA B<br>NE<br>BNE<br>BCC<br>BNC<br>DEC<br>BNE<br>RTS | LOOP2<br>E, ASCII<br>D, ASCII+1<br>D, ASCII<br>X, 0<br>D, ASCII<br>D, DCRPNT+1<br>D, DCRPNT<br>X, 0<br>D, DISPNT<br>X, 0<br>D, DISPNT<br>E, DIGCNT<br>LOOP3<br>I, S80<br>LOOP4<br>E, DCRPNT<br>E, COLCNT<br>LOOP1 |

Figure 6. 6800 Microprocessor Program Utilizing a 160 Byte RAM Buffer that Interfaces to the REFRESH CONTROLLER

Figure 6. 6800 Microprocessor Program Utilizing a 160 Byte RAM Buffer that Interfaces to the REFRESH CONTROLLER (cont.)

MCM6674 must be replaced by a faster Bipolar PROM. If this PROM is programmed with the code listed in Figure 17, it will decode a character font identical to the MCM6674. This same propagation delay problem is present with the MCM6810 RAM. Following worst case design procedures, the MCM68A10 1.5 MHz RAM should be used. To accommodate the additional address line made necessary by the display length expansion, the two 74LS367 tri-state buffers have been replaced with the 74LS244 octal version. Strobing of the display is accomplished using the 74197, 74393, and 7490 counter string. The 74197 is connected as a divide by 8 counter that sequentially selects the seven rows within the 82S2708. The 74393 is a divide by 256 counter connected so that the seven lowest outputs select each of the 128 ASCII characters within the RAM. The previously unused input A/output QA of the 7490 has been used as an additional divide by 2 counter. Thus, when the highest output of the 74393, 2Q<sub>D</sub>, and the QA output of the 7490 are NANDed through 7437, the basic relationship between load time and column on time is established. However, the external gating that has been added does affect the duty factor slightly. Although these additional gates increase the total package count by one, they perform the necessary function of ensuring that the column drivers are turned off before the clock is gated to the display. This prevents noise from being generated on the clock of the display and eliminates erroneous display data. The resultant duty factor is (23/32) (1/5) or 14.4%. Since the HDSP-2000 is rated at  $I_{col(max)} = 410$  mA and

| LOC                                          | (                                | )BJEC<br>CODE              |                      | SOURCE                           | STATEME                                   | NTS                                              |

|----------------------------------------------|----------------------------------|----------------------------|----------------------|----------------------------------|-------------------------------------------|--------------------------------------------------|

| 0004<br>0005<br>E500                         |                                  |                            |                      | RDVR<br>CDVR<br>DECDR            | EQU<br>EQU<br>EQU                         | 0004H<br>0005H<br>0E500H                         |

| E000<br>E002<br>E003<br>E005                 | 05<br>FE<br>FF<br>00             | E0<br>FF                   |                      | POINT<br>COLMN<br>COUNT<br>BUFFR | ORG<br>DW<br>DB<br>DW<br>DS               | 0E000H<br>BUFFR<br>0FEH<br>0FFFFH<br>160         |

| E0A5<br>E0A7                                 | A7<br>00                         | E0                         |                      | ASCII<br>DATA                    | ORG<br>DW<br>DS                           | 0E0A5H<br>DATA<br>32                             |

| E400<br>E401<br>E402<br>E403                 | F5<br>C5<br>E5<br>2A             | 00                         | E0                   | RFRSH                            | ORG<br>PUSH<br>PUSH<br>PUSH<br>LHLD       | 0E400H<br>PSW<br>B<br>H<br>POINT                 |

| E406<br>E408<br>E40A<br>F40C<br>E40D<br>E40F | 06<br>3E<br>D3<br>7E<br>D3<br>23 | 20<br>FF<br>05<br>04       |                      | LOOP                             | MVI<br>MVI<br>OUT<br>MOV<br>OUT<br>INX    | B, 32<br>A, 0FFH<br>CDVR<br>A, M<br>RDVR<br>H    |

| E410<br>E411<br>E414<br>E417<br>E419<br>E41B | 05<br>C2<br>3A<br>D3<br>FE<br>CA | 0C<br>02<br>05<br>EF<br>28 | E4<br>E0<br>E4       |                                  | DCR<br>JNZ<br>LDA<br>OUT<br>CPI<br>JZ     | B<br>LOOP<br>COLMN<br>CDVR<br>0EFH<br>FIRST      |

| E41E<br>E421<br>E422<br>E425<br>E428         | 22<br>07<br>32<br>C3<br>21       | 00<br>02<br>3A<br>05       | E0<br>E0<br>E4<br>E0 | FIRST                            | SHLD<br>RLC<br>STA<br>JMP<br>LXI          | POINT<br>COLMN<br>END<br>H, BUFFR                |

| E42B<br>E42E<br>E430<br>E433<br>E436<br>E437 | 22<br>3E<br>32<br>2A<br>2B<br>22 | 00<br>FE<br>02<br>03<br>03 | E0<br>E0<br>E0<br>E0 |                                  | SHLD<br>MVI<br>STA<br>LHLD<br>DCX<br>SHLD | POINT<br>A, 0FEH<br>COLMN<br>COUNT<br>H<br>COUNT |

| E43A<br>E43B<br>E43C<br>E43D                 | El<br>Cl<br>F1<br>C9             |                            |                      | END                              | POP<br>POP<br>POP<br>RET                  | H<br>B<br>PSW                                    |

| E43E<br>E441<br>E443<br>E446                 | 11<br>0E<br>2A<br>7E             | 24<br>20<br>A5             | E0<br>E0             | LOAD<br>LOOP1                    | LXI<br>MVI<br>LHLD<br>MOV                 | D, BUFFR+31<br>C, 32<br>ASCII<br>A, M            |

| E447<br>E448<br>E44B<br>E44D<br>E44E         | 23<br>22<br>26<br>6F<br>06       | A5<br>E5<br>05             | E0                   |                                  | INX<br>SHLD<br>MVI<br>MOV<br>MVI          | H<br>ASCII<br>H, DECDR/256<br>L, A<br>B, 5       |

| E450<br>E451<br>E452<br>E453                 | 7E<br>12<br>7D<br>C6             | 80                         |                      | LOOP2                            | MOV<br>STAX<br>MOV<br>ADI                 | A, M<br>D<br>A, L<br>80H                         |

| E455<br>E456<br>E459<br>E45A<br>E45B         | 6F<br>D2<br>24<br>7B<br>C6       | 5A<br>20                   | E4                   | LOOP3                            | MOV<br>JNC<br>INR<br>MOV<br>ADI           | L, A<br>LOOP3<br>H<br>A, E<br>32                 |

| E43B<br>E45D<br>E45E<br>E45F<br>E462         | 5F<br>05<br>C2<br>7B             | 20<br>50                   | E4                   |                                  | MOV<br>DCR<br>JNZ<br>MOV                  | SZ<br>E, A<br>B<br>LOOP2<br>A, E                 |

| E463<br>E465<br>E466<br>E467<br>E46A         | C6<br>5F<br>0D<br>C2<br>C9       | 5F<br>43                   | E4                   |                                  | ADI<br>MOV<br>DCR<br>JNZ<br>RET           | 5FH<br>E, A<br>C<br>LOOP1                        |

|                                              |                                  |                            |                      |                                  |                                           |                                                  |

Figure 7. 8080A Microprocessor Program Utilizing a 160 Byte RAM Buffer that Interfaces to the REFRESH CONTROLLER

Figure 7. 8080A Microprocessor Program Utilizing a 160 Byte RAM Buffer that Interfaces to the REFRESH CONTROLLER (cont.)

| LOC                                                                                                                                                                                                          | C                                                                                                                                                  | )BJEC<br>CODE                                                  |                                  | SOURCE                                  | STATEME                                                                                                                                                                      | NTS                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0004<br>0005<br>E500                                                                                                                                                                                         |                                                                                                                                                    |                                                                |                                  | RDVR<br>CDVR<br>DECDR                   | EQU<br>EQU<br>EQU                                                                                                                                                            | 0004H<br>0005H<br>0E500H                                                                                                                                                                            |

| E000<br>E002<br>E003<br>E005<br>E007                                                                                                                                                                         | 07<br>FE<br>FF<br>00<br>00                                                                                                                         | E0<br>FF<br>E5                                                 |                                  | ASCII<br>COLMN<br>COUNT<br>BASE<br>DATA | ORG<br>DW<br>DB<br>DW<br>DW<br>DS                                                                                                                                            | 0E000H<br>DATA<br>0FEH<br>0FFFFH<br>DECDR<br>32                                                                                                                                                     |

| E400<br>E401<br>E403<br>E404<br>E407<br>E408<br>E408<br>E408<br>E408<br>E402<br>E410<br>E412<br>E414<br>E414<br>E417<br>E418<br>E417<br>E418<br>E414<br>E411<br>E412<br>E412<br>E412<br>E421<br>E422<br>E422 | F5<br>C5<br>E5<br>2A<br>EB<br>2A<br>09<br>43<br>0E<br>5F<br>D3<br>78<br>86<br>5F<br>1A<br>D3<br>2B<br>0D<br>22<br>EB<br>3A<br>D3<br>3A<br>D3<br>FE | 05<br>00<br>1F<br>20<br>FF<br>05<br>04<br>16<br>02<br>05<br>EF | E0<br>E0<br>00<br>E4<br>E0       | ORG<br>RFRSH                            | PUSH<br>PUSH<br>PUSH<br>LHLD<br>XCHG<br>LHLD<br>LXI<br>DAD<br>MOV<br>MVI<br>MVI<br>OUT<br>MOV<br>ADD<br>MOV<br>LDAX<br>OUT<br>DCX<br>DCR<br>JNZ<br>XCHG<br>LDA<br>OUT<br>CPI | 0E400H<br>PSW<br>B<br>D<br>H<br>BASE<br>ASCII<br>B, 31<br>B<br>B, E<br>C, 32<br>A, 0FFH<br>CDVR<br>A, B<br>M<br>E, A<br>D<br>M<br>E, A<br>D<br>RDVR<br>H<br>C<br>C<br>LOOP<br>COLMN<br>CDVR<br>0EFH |

| E429<br>E42C<br>E42D<br>E430<br>E431                                                                                                                                                                         | CA<br>07<br>32<br>68<br>01                                                                                                                         | 3B<br>02<br>80                                                 | E4<br>E0<br>00                   |                                         | JZ<br>RLC<br>STA<br>MOV<br>LXI                                                                                                                                               | FIRST<br>COLMN<br>L, B<br>B, 0080H                                                                                                                                                                  |

| E434<br>E435<br>E438<br>E43B<br>E43D<br>E440<br>E443<br>E440<br>E443<br>E446<br>E449<br>E44A<br>E44D                                                                                                         | 09<br>22<br>C3<br>3E<br>32<br>21<br>22<br>2A<br>2B<br>22<br>E1                                                                                     | 05<br>4D<br>FE<br>02<br>00<br>05<br>03<br>03                   | E0<br>E4<br>E5<br>E0<br>E0<br>E0 | FIRST                                   | DAD<br>SHLD<br>JMP<br>MVI<br>STA<br>LXI<br>SHLD<br>LHLD<br>DCX<br>SHLD<br>POP                                                                                                | B<br>BASE<br>END<br>A, 0FEH<br>COLMN<br>H, DECDR<br>BASE<br>COUNT<br>H<br>COUNT<br>H                                                                                                                |

| E44E<br>E44F<br>E450<br>E451                                                                                                                                                                                 | D1<br>C1<br>F1<br>C9                                                                                                                               |                                                                |                                  |                                         | POP<br>POP<br>POP<br>RET                                                                                                                                                     | D<br>B<br>PSW                                                                                                                                                                                       |

Figure 8. 8080A Microprocessor Program that Decodes a 32 Character ASCII String Prior to Loading into the REFRESH CONTROLLER

there are 32 modules of four digits each, the transistors must source up to 32 times 410 mA or approximately 13 A. Darlington PNP power transistors (2N6285) with the proper resistors have been used to accomplish this task.

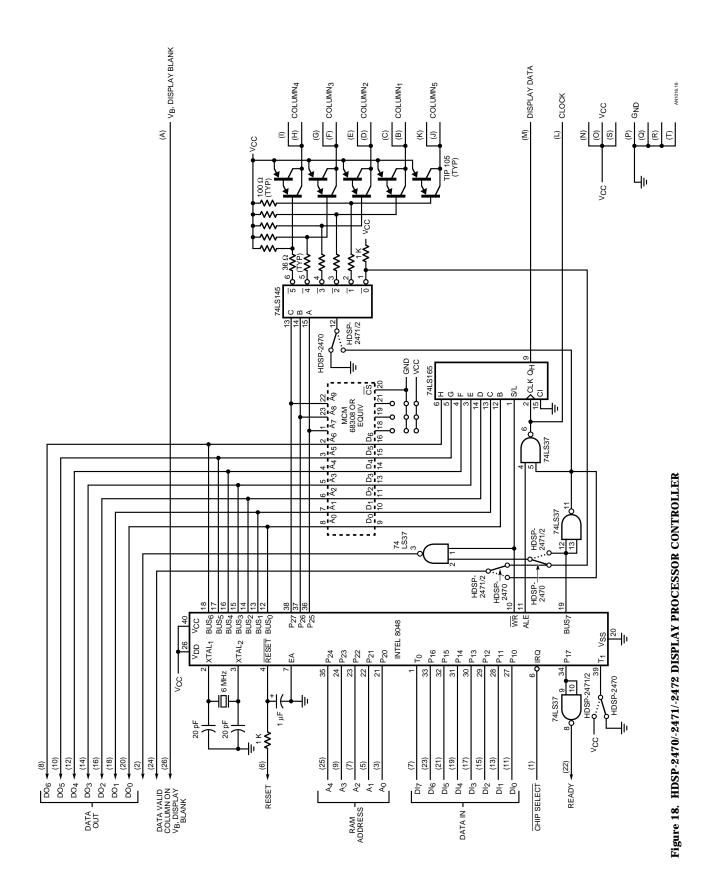

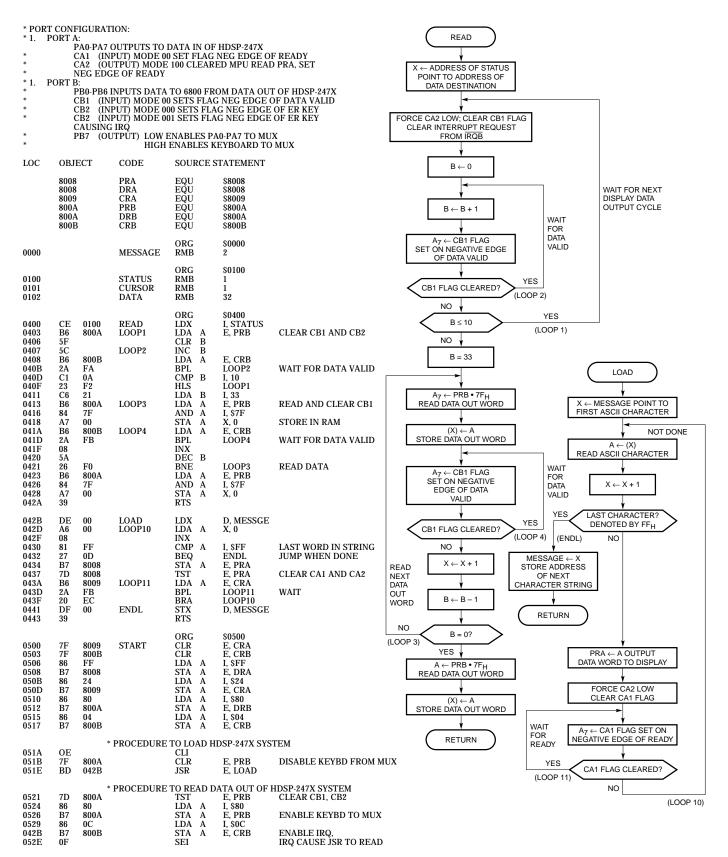

## Display Processor Controller

The previously mentioned interface techniques provide only for the display of ASCII coded data. Such important features as a blinking cursor, editing routines, and character addressing must be provided by other subroutines in the microprocessor software. The DISPLAY PROCESSOR CON-TROLLER is a system which utilizes a dedicated 8048 single chip microprocessor to provide these important features. This controller, as depicted in Figure 18, is a series of printed circuit board subsystems available from

| DECODER<br>ADDRESS<br>FOR FIG.<br>7,8,12 | DECODER<br>ADDRESS<br>FOR<br>FIG.6 | HDSP-2471<br>ROM<br>ADDRESS |    |    |    |    |    | ]  | HEXI | DEC | IMAI | . DAT | 'A |    |    |    |    |    |                     |

|------------------------------------------|------------------------------------|-----------------------------|----|----|----|----|----|----|------|-----|------|-------|----|----|----|----|----|----|---------------------|

| E500                                     | 0600                               | 080                         | 08 | 30 | 45 | 7D | 7D | 38 | 7E   | 30  | 60   | 1E    | 3E | 62 | 40 | 08 | 38 | 41 | COLUMN <sub>1</sub> |

|                                          |                                    | 090                         | 10 | 18 | 5E | 78 | 38 | 78 | 38   | 3C  | 38   | 3C    | 38 | 08 | 20 | 12 | 48 | 01 |                     |

|                                          |                                    | 0A0                         | 00 | 00 | 00 | 14 | 24 | 23 | 36   | 00  | 00   | 00    | 08 | 08 | 00 | 08 | 00 | 20 |                     |

|                                          |                                    | 0B0                         | 3E | 00 | 62 | 22 | 18 | 27 | 3C   | 01  | 36   | 06    | 00 | 00 | 00 | 14 | 41 | 06 |                     |

|                                          |                                    | 0C0                         | 3E | 7E | 7F | 3E | 7F | 7F | 7F   | 3E  | 7F   | 00    | 20 | 7F | 7F | 7F | 7F | 3E |                     |

|                                          |                                    | 0D0                         | 7F | 3E | 7F | 26 | 01 | 3F | 07   | 7F  | 63   | 03    | 61 | 00 | 02 | 41 | 04 | 40 |                     |

|                                          |                                    | 0E0                         | 00 | 38 | 7F | 38 | 38 | 38 | 08   | 08  | 7F   | 00    | 20 | 00 | 00 | 78 | 7C | 38 |                     |

|                                          |                                    | 0F0                         | 7C | 18 | 00 | 48 | 04 | 3C | 1C   | 3C  | 44   | 04    | 44 | 00 | 00 | 00 | 08 | 2A |                     |

| E580                                     | 0680                               | 100                         | 1C | 48 | 29 | 09 | 09 | 44 | 01   | 4A  | 50   | 04    | 49 | 14 | 3C | 7C | 44 | 63 | COLUMN <sub>2</sub> |

|                                          |                                    | 110                         | 08 | 24 | 61 | 14 | 44 | 15 | 45   | 43  | 45   | 41    | 42 | 08 | 7E | 19 | 7E | 12 |                     |

|                                          |                                    | 120                         | 00 | 5F | 03 | 7F | 2A | 13 | 49   | 0B  | 00   | 41    | 2A | 08 | 58 | 08 | 30 | 10 |                     |

|                                          |                                    | 130                         | 51 | 42 | 51 | 41 | 14 | 45 | 4A   | 71  | 49   | 49    | 36 | 5B | 08 | 14 | 22 | 01 |                     |

|                                          |                                    | 140                         | 41 | 09 | 49 | 41 | 41 | 49 | 09   | 41  | 08   | 41    | 40 | 08 | 40 | 02 | 04 | 41 |                     |