## = Preliminary =

AK2571

# Single-Chip Automatic Power/Temperature Control for WDM Laser Diodes

#### **Features**

- Single Chip LSI that integrates APC (Auto Power Control) and ATC (Auto Temperature Control) functions for WDM Laser Module

- A controlling TEC (Thermal Electrical Cooler) stabilizes the temperature of LD module in the range of +/-0.1°C by PID algorithm.

- Parameters controlling Laser Diode are user programmable and stored in EEPROM

- Internal Temperature Sensor detects on-chip temperature, enabling compensation internal and external components that may be affected by changing ambient temperature.

- Autonomous operation (internal oscillator and logic).

- Pin-selectable wavelength data for tunable laser diodes (four options).

- Single 3.3V operation

- 64-pin LQFP or Bare chip

#### Description

The AK2571 is a single-chip solution for WDM Laser Diode Module applications. It integrates both ATC (Auto Temperature Control) and APC (Auto Power Control) functions in a small 64-pin LQFP or bare die package..

The ATC function of the AK2571 detects the LD module temperature via an external thermister and uses the PID algorithm to control the Thermo-Electric Cooler (TEC). This provides +/- 0.1°C stabilization.. A customer can program the appropriate PID parameters into the internal EEPROM, thereby providing compensation characteristics for each Laser Diode. TEC control is handled through either PWM or Analog current control through I-DAC4. These are easily selected by an EEPROM (Register) setting.

The APC has two functions. The first function is to compensate for Laser Diode power decreases caused by aging. The other function is to compensate for temperature variations of AK2571 and external components (current amplifier or driver circuits) which may be affected by ambient temperature within the LDM. The AK2571 does this by controlling BIAS and modulation current according to the look up table in EEPROM.

The AK2571 has every alarm needed for WDM modules (Loss of power, Over current, Temperature etc.). There is a dithering function for modulation current that improves the extinction ratio for long distance transmissions.

Also, parameter and compensation data can be stored for four wavelengths. If a customer uses a tunable laser diode, it is very easy to change the wavelength by pin control.

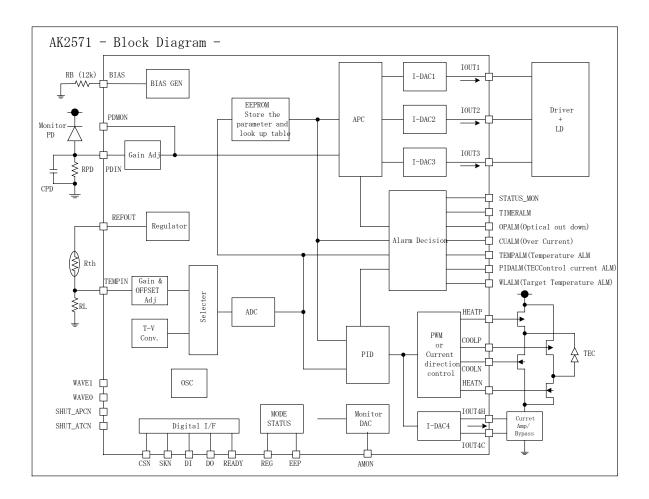

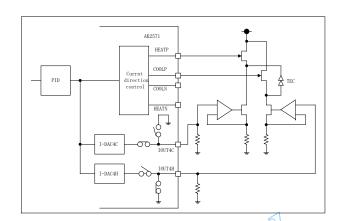

#### Block Diagram

#### Circuit Description

#### 1. Over view

The AK2571 has two primary functions. The first function is APC (Automatic Temperature Control) which supplies adequate modulation /BIAS current to a Laser diode and the other is ATC (Automatic Temperature control) which controls the TEC (Thermo Electric Cooler) to stabilize the temperature of the Laser diode.

#### 1.1 APC

There are three Digital to Analog Converters (I-DAC1, 2, 3) that output the current for modulation, BIAS and EA (Electrical Absorption) Modulation.

Maximum output currents:

I-DAC1: 120mA (typ.),

I-DAC2 and I-DAC3: 20mA (typ.)

Each DAC has a current limit function whose value is stored in the internal EEPROM. This is especially important for I-DAC1, which has the modulation function for dithering.

In WDM systems, there is no need for discrete laser diode temperature compensation. However the outer current amplifier or LD drivers may be affected by ambient temperature changes. In order to compensate for these the AK2571 has a feed-forward APC that can supply adequate current corresponding to the ambient temperature change detected by the internal  $T_V$  converter.

Please refer the part "3. APC" for details.

#### 1.2 ATC

The AK2571 controls TEC to stabilize the input voltage from the temperature sensor of the LD module (Thermistor). The control algorithm is PID (Proportion Integration Differential) which has user-programmable parameters that are stored in EEPROM. There are two ways for driving TEC, one is PWM (more energy effective than DC drive), the other is DC current drive through I-DAC, which has lower noise.

Please refer the part "4. ATC" for details.

#### 1.3 Control Sequence

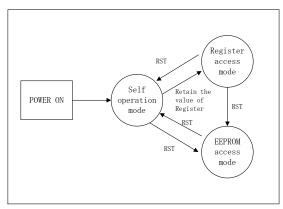

There are three functional modes in AK2571 below.

- 1) Self-operation mode: The AK2571 operates ATC and APC independently. When self-operating mode starts, , ATC Lock (detects when the target temperature is reached), APC Count up (prevents jumps in BIAS and Modulation currents) and Timer (counts the time from device start to beginning of operation) are available.

- 2) Register Access Mode: AK2571 permits writing registers through the digital interface. Customers can adjust any parameters or tables in this mode.

- 3) EEPROM mode: AK2571 permits EEPROM writes. Customers can store the parameters or table data in EEPROM.

Please refer the part "5, Sequencer" for details.

#### 2. Reference

### 2.1 Definition

All values are expressed in the order shown below

Tab\_(Function Block\_)Main name(Function\_).Sub name[Bit]

| Setting way | Tab | Main name                         | Subname           | Bits  | Example                                  |

|-------------|-----|-----------------------------------|-------------------|-------|------------------------------------------|

| Register    | R   | REGISTER NAME<br>(Capital letter) | Sub register name | [x,x] | R_PDGAIN  R_DAC_SET.Dac1  R_DAC_SET[2:0] |

| EEPROM      | Е   | EEPROM NAME<br>(Capital letter)   | Sub eeprom name   | [x,x] | E_PDGAIN E_DAC_SET.Dac1                  |

| PIN         | P   | PIN NAME (Capital letter)         |                   |       | P_WAVE0                                  |

Register and EEPROM names may include additional tags as described below

| Classify       | Additional Tag | Contents                                   | Example        |

|----------------|----------------|--------------------------------------------|----------------|

| Function Block | APC            | APC relate                                 | E_APC_FF_SET   |

|                | DAC            | I-DAC relate                               | E_DAC1_FIX     |

|                | ATC            | ATC relate                                 | E_ATC_OFFSET   |

|                | ALM            | Alarm relate                               | E_ALM_POL      |

|                | PID            | PID relate                                 | E_PID_P        |

|                | LK             | ATC Lock counter relate                    | E_LK_CNT_SET   |

|                | TMPRT          | Temperature decode value                   | R_TMPRT_TRNT < |

| Function       | SET            | Settled value (ALM or Counter etc.)        | E_DAC1_SET     |

|                | WIN            | Hysteresis (ALM or counter etc.)           | E_TMPRTALM_WIN |

|                | CTRL           | Hysteresis (ALM or counter etc.)           | E_INI_CURL_USR |

|                | FIX            | Fixed data for APC                         | E_DAC1_FIX     |

|                | TV             | APC compensation data                      | E_DAC1_TV      |

|                | CMPNST <       | LD aging compensation data                 | R_APC_CMPNST   |

|                | TRGT           | Target value (Temperature or Voltage etc.) | E_APC_TRGT     |

|                | CRNT           | Current value                              | R_TMPRT_CRNT   |

|                | BFR            | Before value                               | R_TMPRT_BFR    |

All circuit blocks and internal nodes are noted as below

|               | Main name                   | Example |

|---------------|-----------------------------|---------|

| Circuit Block | BLOCK NAME (Capital letter) | I-DAC1  |

|               |                             | PID     |

| Internal Node | Signal name (Small letter)  | vout    |

#### 2.2 Functional explanation

Some values are stored in both register and EEPROM to simplify user programming. Explanations of these values are in the register description tables.

For EEPROM details, refer to Section 7. EEPROM

For Register details, refer to Section 8. Registers

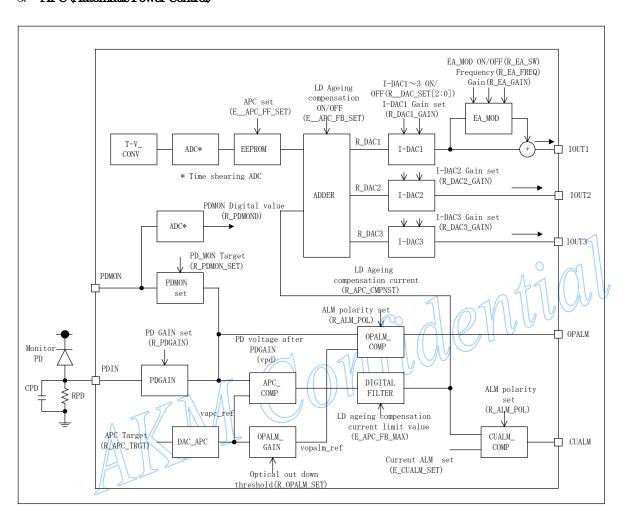

#### 3. APC (Automatic Power Control)

## 3.1 Functional description

| Block             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Note |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| T_V CONV          | Internal Temperature Sensor. Outputs a voltage that corresponds to the surface temperature of the AK2571. This function controls temperature compensation of an external current amplifier, driver IC, etc. By activating the E_APC_FF_SET (=1), the ADC outputs the digital data of T_V CONV as the address of EEPROM stores the lookup table of temperature compensation data for external components every 5.6degree. This data is output through I-DAC and supplies the Laser Diode modulation and BIAS currents. If this function is not required set E_APC_FF_SET to a fixed value and set the current value in E_DACx_FIX. |      |

| ADC               | 8-bits A-to-D converter for temperature detection. (5-bit MSB is used for temperature compensation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| EEPROM            | E_APC_FF_SET=0 (Default): APC is not activated. Fixed data (E_DACx_FIX, x=1-3) is sent to I-DACs.  E_APC_FF_SET=1: APC activation. 5-bits MSB of ADC sent to E_DACxTV[AD], x=1-3 and work the APC sequence.                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| ADDER             | E_APC_FB_SET.Dacx(x=1-3)=0 (default): Do not add aging compensation current to I-DACs.  E_APC_FB_SET.Dacx(x=1-3)=1: Add aging compensation (R_APC_CMPNST) current to I-DACs.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

| I-DAC1            | 8-bit current output DAC (120mA max.). Output current corresponds to R_DAC1 data. When R_DAC_SET=1, this outputs is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

| I-DAC2            | 8-bit current output DAC (20mA max.). Output current corresponding to R_DAC1 data. When R_DAC_SET=1, this outputs is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| I-DAC3            | 8 bit current output DAC (20mA max.). Output current corresponding to R_DAC1 data. When R_DAC_SET=1, this outputs is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| EA_MOD            | Dithering function. R_EA_SW=0: Non-Active/ 1: Active. R_EA_FREQ: Modulation frequency selection: 16kHz(000), 32kHz(001), 64kHz(010), 128kHz(011) and 256kHz(100). R_EA_GAIN: Additional level to I=DAC1 out selection:16%(00), 8%(01), 10.4%(10) and 2%(11).                                                                                                                                                                                                                                                                                                                                                                      |      |

| PDGAIN            | Amplifies the input signal from the monitoring Photo Diode. (vpd).  Customers can set the gain from 0dB to 21dB(Typ.) by 0.7dB steps, using values stored in the EEPROM.  Input range: 0.2V - 1.5V  Full-scale output through PDMON can be set from 0.4V to 1.1V in 0.1V steps. Internal attenuator adjusts the full scale per E_PDMON_SET                                                                                                                                                                                                                                                                                        |      |

| DACAPC            | Generates the target APC (R_APC_TRGT) voltage (vact_ref) in proportion to PDGAIN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | J    |

| APC_COMP          | Compares the PD monitoring voltage (vpd) with APC target voltage (vapc_ref), if vpd < vapc_ref, outputs UP signals to digital filter. And if vpd > vapc_ref, outputs DOWN signals to digital filter. The sampling rate is 512kHz.                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| DIGITAL<br>FILTER | Receives signals from APC_COMP, calculates the value to make vpd and vapc_ref equal. Its value is the LD aging error (R_APC_CMPNST), and is limited by the value of E_APC_FB_MAX. There is no need to supply negative current for aging error.                                                                                                                                                                                                                                                                                                                                                                                    |      |

| CUALM_COMP        | LD aging error current (R_APC_CMPNST) over Alarm value (E_CUALM_SET), output CUALM. Its polarity is selected by register R_ALM_POL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| OPALM_GAIN        | OPALM (light sparkle fail) output level (vopalm_ref) setting by register R_OPALM_SET. 000: 1/2, 001: 1/3, 010: 1/4, 011: 1/5, 100: 1/6, 101:1/8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| OPALM_COMP        | Compares the PD monitoring voltage (vpd) with OPALM voltage (vpalm), if vpd < vpalm, outputs OPALM (light power down alarm). Its polarity is selected by register R_ALM_POL                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

#### 3.2 Feed forward APC Function

The AK2571 compensates for ambient temperature variations caused by the current amplifier or driver chip located outside of the LD module. If this function is not required, a fixed-current source for the LD can be used instead..

The Feed-forward process is described below:

- The internal T\_V converter (please refer to "3.6 Internal T-V converter") senses the ambient temperature. The integrated ADC converts the signal to a digital value.

- 5-bit MSB data address for the EEPROM stores the temperature compensation data, which is sent to I-DACx.

- Compensation current is output from I-DACx.

To execute feed forward APC, temperature compensation data must be stored in the internal EEPROM as a look-up table that is programmed during the customer assembly process.

In Self-operation mode, all compensation operations (sensing T\_V converter, access to EEPROM and compensation current output through I-DACs) are automatically executed.

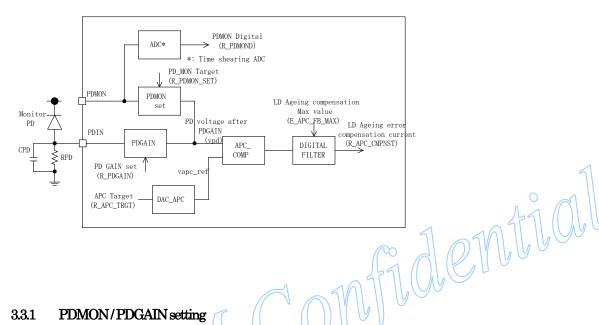

#### 3.3 LD aging error compensation

Compensation current outputs are available for LD light power deterioration, APC COMP compares the feedback voltage from PDIN (vpd) with the output voltage of DACAPC (vapc ref. R APC TRGT). Based on this result a compensation current (R APC CMPNST) is added to the output current of I-DAC set by E APC FB SET after averaging through a digital filter.

#### 3.3.1 PDMON/PDGAIN setting

Selects the output range from PDMON pin by R PDMON SET in the range from 0.4 to 1.1V. Adjust the input signal level using R PD GAIN (E PD GAIN) to make the initial input level equal the value of R PDMON SET. Table 3-2 indicates the function of R\_PDMON\_SET and output voltages, Table 3.3 indicates the function of R\_PDGAIN and Gain. After this adjustment, the internal PD input voltage (vpd) is set at 1.8V(typ) in Self-operation mode.

Table 3-2 R\_PDMON\_SET setting

| R_PDMON_SET(E_PDMON_SET)[2:0] | PDMON Full Scale |

|-------------------------------|------------------|

| 111                           | 1.1V             |

| -                             | 0.1V/step        |

| 000                           | 0.4V             |

#### Table 3-3 R\_PDGAIN setting

| R_PDGAIN_SET(E_PDGAIN_SET)[4:0] | Gain       |

|---------------------------------|------------|

| 11111                           | 21.7dB     |

| -                               | 0.7dB/step |

| 00000                           | 0dB        |

Make sure the PDMON voltage equals the value of R(E)\_PDMON\_SET.

Conversion expression: Gain = 20\*log (1.8/PDIN voltage)

#### 3.3.2 DACAPC

Generates the reference voltage for aging compensation. Table 3-4 indicates the function of R(E)\_APC\_TRGT and vapc\_ref

| R_APC_TRGT (E_APC_TRGT)[6:0] | Reference voltage for Aging compensation (vapc_ref) |  |

|------------------------------|-----------------------------------------------------|--|

| 1111111                      | 2.1V                                                |  |

|                              | 4.8mV/step                                          |  |

| 0000000                      | 1.5V                                                |  |

Refer to "5.3.1 Process - ATC and APC Adjustment Example" for further instructions regarding the adjustment process, .

#### 3.4 Gain setting of I-DAC1,2,3

See the table below for a description on how to set the three I-DACs full-scale voltages. The resolution is set in proportion with the gain.

I-DAC1 gain setting

| R_DAC1_GAIN<br>(E_DAC1_GAIN) | Gain set value | Max output current (typ) | Setting range of output current (typ) | Non missing code<br>warranty range (typ) | Current resolution (typ) |

|------------------------------|----------------|--------------------------|---------------------------------------|------------------------------------------|--------------------------|

| 00                           | 1              | 121.8mA                  | 30mA-121.8mA                          | 30mA over                                | 0.36mA                   |

| 01                           | 1/2            | 60.9mA                   | 15mA-60.9mA                           | 15mA over                                | 0.18mA                   |

| 10                           | 1/4            | 30.45mA                  | 7.5mA-30.45mA                         | 7.5mA over                               | 0.09mA                   |

| 11                           | 1/12           | 10.15mA                  | 2.5mA-10.15mA                         | 2.5mA over                               | 0.03mA                   |

I-DAC2 Gain setting

| R_DAC1_GAIN<br>(E_DAC1_GAIN) | Gain set value | Max output current (typ) | Setting range of output current (typ) | Non missing code<br>warranty range (typ) | Current resolution (typ) |

|------------------------------|----------------|--------------------------|---------------------------------------|------------------------------------------|--------------------------|

| 00(11)                       | 1              | 20.42mA                  | 0mA-21.42mA                           | 2.5mA over                               | 0.084mA                  |

| 10                           | 1/2            | 10.71mA                  | 0mA-10.71mA                           | 1.25mA over                              | 0.042mA                  |

| 11                           | 1/4            | 5.36mA                   | 0mA-5.36mA                            | 0.625mA over                             | 0.021mA                  |

I-DAC3 Gain setting

| R_DAC1_GAIN<br>(E_DAC1_GAIN) | Gain set value | Max output current (typ) | Setting range of output current (typ) | Non missing code<br>warranty range (typ) | Current<br>resolution (typ) |

|------------------------------|----------------|--------------------------|---------------------------------------|------------------------------------------|-----------------------------|

| 00(11)                       | 1              | 21.42mA                  | 0mA-20.42mA                           | 2.5mA over                               | 0.084mA                     |

| 10                           | 1/2            | 10.71mA                  | 0mA-10.71mA                           | 1,25mA over                              | 0.042mA                     |

| 11                           | 1/4            | 5.36mA                   | 0mA-5.36mA                            | 0.625mA over                             | 0.021mA                     |

|                              |                |                          | onsi                                  | Jenti                                    |                             |

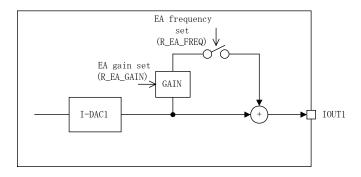

#### 3.5 Modulation for dithering through I-DAC1

I-DAC1 has a modulation function for dithering. It's added to the current of I-DAC1 and output through IOUT1. Its function is available to set R\_EA\_SW.

Figure 3-3 shows the block diagram and Table 3-8/3-9 explains the setting

Figure 3-3 EA Block diagram

Table 3-8 EA Dithering frequency

| R_EA_FREQ<br>(E_EA_FREQ) | Setting frequency (Typ) | Deviation (typ) | Remarks   |

|--------------------------|-------------------------|-----------------|-----------|

| 000                      | 16kHz                   | TBD             | (Default) |

| 001                      | 32kHz                   | TBD             |           |

| 010                      | 64kHz                   | TBD             |           |

| 011                      | 128kHz                  | TBD             |           |

| 100-111                  | 256kHz                  | TBD             |           |

Table 3-9 Additional gain

| R_EA_GAIN<br>(E_EA_GAIN) | Additional gain | Deviation (typ) | Remarks   |

|--------------------------|-----------------|-----------------|-----------|

| 00                       | 16%             | TBD             | (Default) |

| 01                       | 8%              | TBD $\sim$      |           |

| 10                       | 4%              | TBD 477 ( )     |           |

| 11                       | 2%              | TBD             |           |

|                          |                 |                 |           |

#### 3.6 Internal T\_V converter

The internal temperature sensor's output voltage function is shown in Figure 3-4. This offset is different for each device, and is adjusted during factory test by AKM. If re-adjustment of the offset is necessary (for higher accuracy, etc.), it is possible to rewrite the R(E)\_TV\_OFFSET. Table 3-10 diagrams the offset voltage and R\_TV\_OFFSET. The internal T\_V converter has a gain of -12.3mV / degree (typ) and the 8-bit ADC (full scale is 2.2V) is changed 0.7degree for each LSB. Actually, only 5bits MSB of ADC is valid for feed forward APC, so the compensation data is renewed every 5.6 degrees.

The internal T\_V converter monitors the surface temperature of the AK2571 and detects any difference between this temperature, the ambient temperature and the temperature of external components. It is possible to increase the accuracy of this function by "training" the device beforehand and writing the compensation data trained as described below.

#### 1) Single-point temperature adjustment

Read R\_TV at one ambient temperature, and using the T\_V Conv. Gain (-0.7degree/LSB), calculates the 8-bit ADC value and enter it into the look-up table address for Feed forward APC.

By performing this training, the offset error can be cancelled. Of course this training must be executed in conjunction with an APC adjustment. Please refer to **5.3.1 APC/ATC adjustment**.

#### 2) Two-point temperature adjustment

Read R\_TV at two ambient temperatures, calculate the T\_V Conversion gain. From this gain, calculate the 8-bit ADC value and enter it into the look-up table address for Feed forward APC.

By performing this training, the offset error and gain variation can be cancelled. Of course this training must be executed in conjunction with an APC adjustment. Please refer to **5.3.1 APC/ATC** adjustment.

Table 3-10 R\_TV\_OFFSET setting

| R_TV_OFFSET[4:0]<br>E_TV_OFFSET[4:0] | Offset voltage [mV]<br>(Reference value) |

|--------------------------------------|------------------------------------------|

| 11111                                | +375                                     |

| 11110                                | +350                                     |

| 11101                                | +325                                     |

|                                      | I                                        |

| 10001                                | +25                                      |

| 10000                                | 0                                        |

| 01111                                | -25                                      |

|                                      | I                                        |

| 00010                                | -350                                     |

| 00001                                | -375                                     |

| 00000                                | -400                                     |

Default value of E\_TV\_OFFSET is set by AKM.

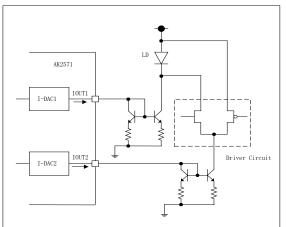

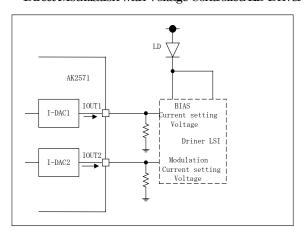

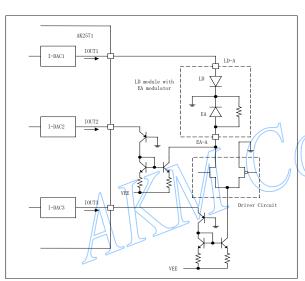

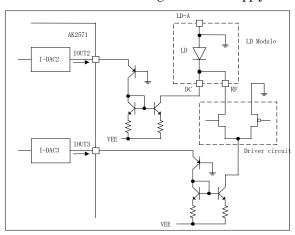

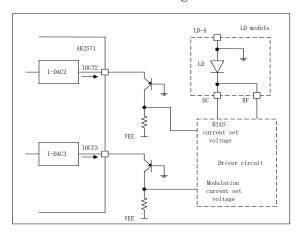

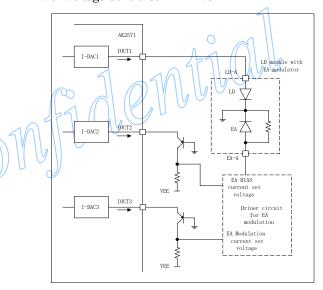

#### 3.7 Example schematics of connect ion to external components

Figures 3-5 to 3-10 illustrate typical system connections. When connecting to a negative voltage source, use a level shifter to ensure that the signal voltages stays within the specified range. In addition to that, I-DAC1 can't be forced negative voltage supply.

Figure 3-5

Direct Modulation with Positive Power Supply

Figure 3-7

Direct Modulation with Voltage Controlled LD Driver

Figure 3-9 EA Modulation

Figure-3-6

Direct Modulation with Negative Power Supply

Figure 3-8

Direct Modulation with Voltage Controlled LD Driver

Figure 3-10

EA with Voltage Controlled LD Drive

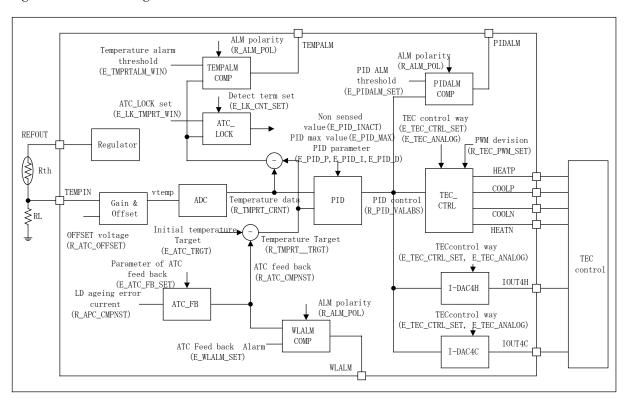

#### 4. ATC (Automatic Temperature Compensation)

Figure 4-1 ATC Block diagram

## 4.1 ATC Block Explanation

Table 4-1 indicates the functions of the ATC block

| Block              | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Remarks |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Regulator          | Supplies voltage to thermister included in the LD module. REFOUT=2.3V (typ). Thermister output voltage (TEMPIN) error tracks the varying voltage supply temperature characteristics of REFOUT and automatically calculates and cancels this in the AK2571.                                                                                                                                                                                                                                                                                                     |         |

| Gain & Offset      | AK2571 amplifies (x13 typically) the input signal to enable higher resolution from the 8-bit ADC. The input signal should be set to the midpoint of its full scale to meet the target temperature of the offset setting function. For example, when thermister R0=10kohm@25 degree, B=3900, load resistance 6.8kohm., its sensitivity is about 0.03degree/LSB.                                                                                                                                                                                                 |         |

| ADC                | 8brit A-to-D converter. Reference voltage is 2.2V (typ). Temperature signal from Gain & OFFSET is converted to digital and transferred to PID calculator.                                                                                                                                                                                                                                                                                                                                                                                                      |         |

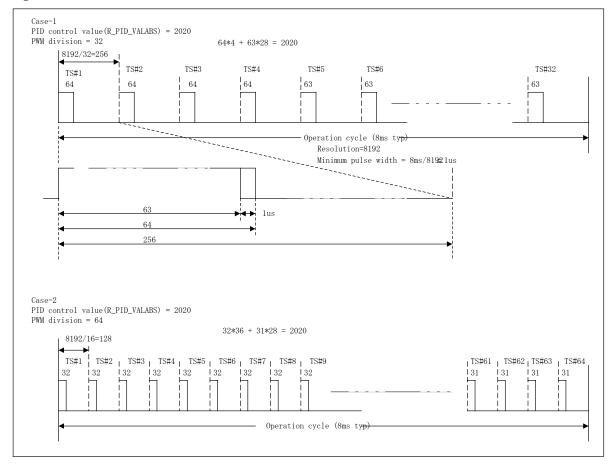

| PID                | Executes a PID (Proportion, Integration and differential) calculation to meet the temperature signal (R_TMPRT_CRNT) at the target temperature (R_TMPRT_TRGT). Output data (R_PID_VALABS) is composed of 13-bits absolute value and a positive/negative bit. Each PID parameter can be set in the EEPROM. The cycle time for this calculation is 8mS (typ) and is set by the internal oscillator.                                                                                                                                                               |         |

| TEC_CTRL           | Using the PID data (R_PID_VALABS), the TEC (Thermo Electric Cooler) is controlled by PWM or Analog control. When PWM control is selected, the FET switch is controlled through the PWM division set register (R_TEC_PWM_SET).                                                                                                                                                                                                                                                                                                                                  |         |

| I-DAC4H<br>I-DAC4C | 10brit current Dto-A converter. When analog control for TEC is selected, the IDAC outputs current following 10bits MSB data from PID. Its full-scale output current is 50mA (typ). When Analog-1 is selected (Control the current direction by FET: refer to figure 4-4), it is possible for I-DAC4H to output both cooling and heating current, depending on current direction. On the other hand, when Analog-2 is selected, heating current is output through I-DAC4H (I-DAC4C output is GND) and cooling current is output through I-DAC4H output is GND). |         |

| ATC_FB             | Change the target temperature according to LD aging error from PD monitor voltage. Its value (R_ATC_CMPNST) is calculated from the parameter (E_ATC_FB_SET). This function assumes that there is first order function between the LD aging error and moving the wavelength to the longer, can compensate wavelength shift cause from aging. When use this function, please note this assumption carefully.                                                                                                                                                     | 1       |

| ATC_LOCK           | Detect the stabilization of LD temperature from start or reset of AK2571. The stabilization judge range (E_IK_TMPRT_WIN) and its decision term (E_IK_CNT_SEI) are set in EEPROM. If the LD temperature data (R_TMPRT_CRNI) stays within the stabilization judge range for a period that is longer than the decision term, the AK2571 moves to the next operation.                                                                                                                                                                                              |         |

| TEMPALMCOMP        | If the difference between LD temperature data (R_TMPRT_CRNT) and target temperature (R_TMPRT_TRGT) exceeds the temperature alarm threshold (E_TEMPALM_WIN), TEMPALM is triggered. RegisterI R_ALM_POL sets the polarity of this signal.                                                                                                                                                                                                                                                                                                                        |         |

| PIDALMCOMP         | When the PID control value (R_PID_VALUE) exceeds the PID alarm threshold (E_PIDALM_SET), PID alarm is triggered. RegisterIR_ALM_POL sets the polarity of this signal                                                                                                                                                                                                                                                                                                                                                                                           |         |

| WLALMCOMP          | When the aging target temperature aging (R_ATC_CMPNST) is exceeds the threshold of the wavelength aging error alarm (E_WLALM_SET), WLALM is output. Its polarity is selectable by the R_ALM_POL register.                                                                                                                                                                                                                                                                                                                                                      |         |

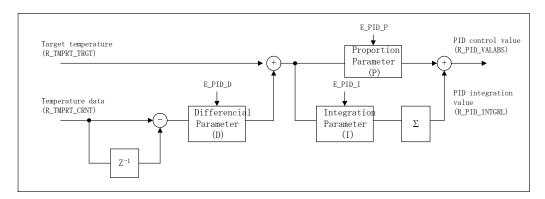

#### 4.2 PID control

Figure 4.2 explains the block diagram for PID control and table 4.3 indicates the parameter setting range

#### Figure 4-2 PID control

Table 4-3: PID parameter setting range

| Parameter    | EEPROM  | Min. | Default | Max.    |

|--------------|---------|------|---------|---------|

| Proportion   | E_PID_P | 0    | 8       | 255     |

| Integration  | E_PID_I | 0    | 7/256   | 255/256 |

| Differential | E_PID_D | 0    | 6/256   | 255/256 |

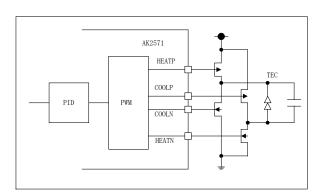

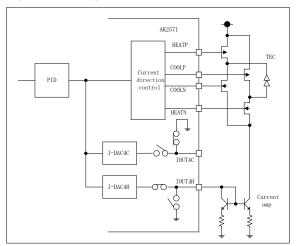

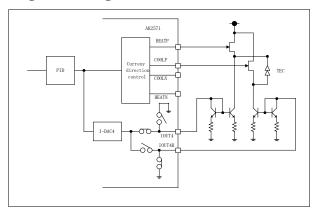

#### 4.3 TEC control

The TEC control process is illustrated in table 4-4. Figures 4-3 to 4-6 explain the circuit that drives TEC and table 4-5 indicate the pin strapping for different control modes.

Figure 4-3 PWM control

Figure 4-4 Analog control-1

Figure 4-5 Analog control 2-1

Figure 4-6 Analog control 2-2

Table 4-5 pin status

| PID data | TEC     | Control way | IOUT4H      | IOUT4C     | HEAT_P | HEAT_N   | COOL_P | COOL_N |

|----------|---------|-------------|-------------|------------|--------|----------|--------|--------|

| PID=0    | OFF     | PWM         | GND         | GND        |        | 0// 1/ U | Y      | 0      |

|          |         | Analog-1    | GND         | GND        |        |          | 1      | 0      |

|          |         | Analog-2    | GND         | GND        |        | 0        | 1      | 0      |

| PID>0    | Heating | PWM         | GND         | GND        | 0      | PWM      | 1      | 0      |

|          |         | Analog 1    | Currentout  | GND        | 0      | 1        | 1      | 0      |

|          | 5       | Analog 2    | Current out | GND        | 0      | 0        | 1      | 0      |

| PID<0    | Cooling | PWM \\      | GND         | GND        | 1      | 0        | 0      | PWM    |

|          | //\ \   | Analog 1    | Current out | GND        | 1      | 0        | 0      | 1      |

|          |         | Analog-2    | GND         | Currentout | 1      | 0        | 0      | 0      |

Figure 4-7 PWM division

#### 4.4 Gain & Offset

The AK2571 amplifies (typically x13) the input signal from the thermister to provide higher resolution for the 8-bit ADC. It also adds an offset voltage to meet the middle of full scale at target temperature. Table 4-6 indicates temperature levels that correspond to ADC values when using a thermister R0=10kohm@25degree, B=3900 and Table 4-7 indicates a thermister R0=10kohm@25degree, B=3450. Both load resistances RL) are 6.8kohm, REFOUT is 2.3V. When adjusting Offset voltage (R\_ATC\_OFFSET), target temperature must be a value between 96 (60h) and 160 (A0h).

Table 4-6 Temperature corresponding to code of ADC (Thermister: R0=10kohm@25degree,B=3900)

| $R_ATC_OFFSET$   | Offset voltage | Temperature [d | legree] (typ) |              |                                        |              |

|------------------|----------------|----------------|---------------|--------------|----------------------------------------|--------------|

|                  | [V]            | ADC=0          | ADC=96        | ADC=128      | ADC=160                                | ADC=256      |

| 0                | 0.30           | -7.6           | -3.2          | -1.9         | -0.6                                   | 3.0          |

| 1                | 0.33           | -5.6           | -1.5          | -0.2         | 1.0                                    | 4.5          |

| 2                | 0.36           | -3.8           | 0.2           | 1.4          | 2.6                                    | 5.9          |

| 3                | 0.39           | -2.0           | 1.8           | 2.9          | 4.1                                    | 7.3          |

| 4                | 0.42           | -0.3           | 3.3           | 4.4          | 5.5                                    | 8.7          |

| 5                | 0.45           | 1.3            | 4.7           | 5.8          | 6.9                                    | 10.0         |

| 6                | 0.48           | 2.8            | 6.2           | 7.2          | 8.3                                    | 11.3         |

| 7                | 0.51           | 4.3            | 7.5           | 8.6          | 9.6                                    | 12.5         |

| 8                | 0.54           | 5.7            | 8.9           | 9.9          | 10.9                                   | 13.8         |

| 9                | 0.57           | 7.1            | 10.2          | 11.2         | 12.2                                   | 15.0         |

| 10               | 0.60           | 8.5            | 11.5          | 12.5         | 13.4                                   | 16.2         |

| 11               | 0.63           | 9.8            | 12.7          | 13.7         | 14.6                                   | 17.4         |

| 12               | 0.66           | 11.1           | 14.0          | 14.9         | 15.8                                   | 18.5         |

| 13               | 0.69           | 12.4           | 15.2          | 16.1         | 17.0                                   | 19.7         |

| 14               | 0.72           | 13.6           | 16.4          | 17.3         | 18.2                                   | 20.9         |

| 15               | 0.75           | 14.8           | 17.6          | 18.5         | 19.4                                   | 22.0         |

| 16               | 0.78           | 16.0           | 18.8          | 19.6         | 20.5                                   | 23.2         |

| 17               | 0.81           | 17.2           | 19.9          | 20.8         | 21.7                                   | 24.3         |

| 18               | 0.84           | 18.4           | 21.1          | 21.9         | 22.8                                   | 25.4         |

| 19               | 0.87           | 19.6           | 22,2          | 23.1         | 24.0                                   | 26.6         |

| 20               | 0.90           | 20.7           | 23.4          | 24,2         | 25.1                                   | 27.7         |

| 21<br>22         | 0.93           | 21.9           | 24.5          | 25.4         | 26.2                                   | 28.8         |

|                  | 0.96           | 23.0           | 25.6          | 26.5         | 27.4                                   | 30.0         |

| 23<br>24         | 0.99           | 24.1           | 26.8          | 27.6         | 28.5                                   | 31.1         |

| 24<br>25         | 1.02<br>1.05   | 25.3<br>26.4   | 27.9          | 28.8<br>29.9 | 29.6<br>30.8                           | 32,2<br>33.4 |

| 26               | 1.08           |                | 29.0<br>30.2  |              |                                        |              |

| <u> 26</u><br>27 | 1.11           | 27.5<br>28.7   | 31.3          | 31.0<br>32.2 | 31.9<br>33.1                           | 34.5<br>35.7 |

| 28               | 1.11           | 29.8           | 32.4          | 33.3         | 34.2                                   | 36.9         |

| 29               | 1.14           | 30.9           | 33.6          | 34.5         | 35.4                                   | 38.1         |

| 30               | 1.19           | 32.1           | 34.7          | 35.6         | 36.6                                   | 39.5         |

| 31               | 1.13           | 33.2           | 35.9          | 36.8         | 37.7                                   | 40.5         |

| 32               | 1.25           | 34.4           | 37.1          | 38.0         | 38.9                                   | 41.7         |

| 33               | 1.28           | 35.6           | 38.3          | 39.2         | 40.2                                   | 43.0         |

| 34               | 1.31           | 36.7           | 39.5          | 40.4         | 41.4                                   | 44.3         |

| 35               | 1.34           | 37.9           | 40.7          | 41.7         | 42.6                                   | 45.6         |

| 36               | 1.37           | 39.1           | 42.0          | 42.9         | 43.9                                   | 46.9         |

| 37               | 1.40           | 40.3           | 43.2          | 44.2         | Λ 45.2                                 | 48.3         |

| 38               | 1.43           | 41.6           | 44.5          | 45.5         | 46.5                                   | 49.7         |

| 39               | 1.46           | 42.8           | 45.8          | 46.8         | 47.9                                   | 51.1         |

| 40               | 1.49           | 44.1           | 47.2 /        | 48.2         | // // // // // // // // // // // // // | 52.5         |

| 41               | 1.52           | 45.4           | 48.5          | 49.6         | 50.7                                   | 54.0         |

| 42               | 1.55           | 46.7           | 49.9          | 51.0         | 52.1                                   | 55.6         |

| 43               | 1.58           | 48.1           | 51.3          | 52.5         | 53.6                                   | 57.2         |

| 44               | 1.61           | (49.5          | 52.8          | 54.0         | 55.1                                   | 58.8         |

| 45               | 1.64           | 50.9           | 54.3          | 55.5         | 56.7                                   | 60.6         |

| 46               | 7 1.67         | 52.3           | 55.9          | 57.1         | 58.4                                   | 62.3         |

| 47\              | 1.70           | 53.8           | 57.5          | 58.7         | 60.1                                   | 64.2         |

|                  |                | 7 25           |               |              |                                        |              |

Table 4-6 Temperature levels corresponding to ADC values (Thermister: R0=10kohm@25degree,B=3450)

| R_ATC_OFFSET | Offset voltage | Temperature [c |              |              |              |          |

|--------------|----------------|----------------|--------------|--------------|--------------|----------|

|              | [V]            | ADC=0          | ADC=96       | ADC=128      | ADC=160      | ADC=256  |

| 0            | 0.30           | -11.3          | <b>-6.</b> 3 | -4.7         | -3.3         | 0.       |

| 1            | 0.33           | -9.2           | -4.4         | -2.9         | -1.5         | 2.       |

| 2            | 0.36           | -7.1           | -2.6         | -1.2         | 0.2          | 4.       |

| 3            | 0.39           | -5.2           | -0.8         | 0.5          | 1.8          | 5.       |

| 4            | 0.42           | -3.3           | 0.9          | 2.2          | 3.4          | 7.       |

| 5            | 0.45           | -1.5           | 2.5          | 3.7          | 5.0          | 8        |

| 6            | 0.48           | 0.2            | 4.0          | 5.3          | 6.5          | 10       |

| 7            | 0.51           | 1.8            | 5.6          | 6.8          | 8.0          | 11       |

| 9            | 0.54<br>0.57   | 3.4<br>4.9     | 7.1<br>8.5   | 8.2<br>9.7   | 9.4          | 12<br>14 |

| 10           | 0.60           | 6.5            | 10.0         | 11.1         | 12.2         | 15       |

| 11           | 0.63           | 7.9            | 11.4         | 12.5         | 13.6         | 16       |

| 12           | 0.66           | 9.4            | 12.7         | 13.8         | 14.9         | 18       |

| 13           | 0.69           | 10.8           | 14.1         | 15.2         | 16.3         | 19       |

| 14           | 0.72           | 12.2           | 15.4         | 16.5         | 17.6         | 20       |

| 15           | 0.75           | 13.5           | 16.8         | 17.8         | 18.9         | 22       |

| 16           | 0.78           | 14.9           | 18.1         | 19.1         | 20.2         | 23       |

| 17           | 0.81           | 16.2           | 19.4         | 20.4         | 21.5         | 24       |

| 18           | 0.84           | 17.5           | 20.7         | 21.7         | 22.8         | 25       |

| 19           | 0.87           | 18.9           | 22.0         | 23.0         | 24.1         | 27       |

| 20           | 0.90           | 20.2           | 23.3         | 24.3         | 25.3         | 28       |

| 21           | 0.93           | 21.5           | 24.6         | 25.6         | 26.6         | 29       |

| 22           | 0.96           | 22.7           | 25.8         | 26.9         | 27.9         | 31       |

| 23           | 0.99           | 24.0           | 27.1         | 28.1         | 29.2         | 32       |

| 24           | 1.02           | 25.3           | 28.4         | 29.4         | 30.5         | 33       |

| 25           | 1.05           | 26.6           | 29.7         | 30.7         | 31.8         | 34       |

| 26           | 1.08           | 27.9           | 31.0         | 32.0         | 33.1         | 36       |

| 27           | 1.11           | 29.1           | 32.3         | 33.3         | 34.4         | 37       |

| 28           | 1.14           | 30.4           | 33.6         | 34.6         | 35.7         | 38       |

| 29           | 1.16           | 31.7           | 34.9         | 35.9         | 37.0         | 40       |

| 30           | 1.19           | 33.0           | 36.2         | 37.3         | 38.4         | 41       |

| 31           | 1.22           | 34.3           | 37.5         | 38.6         | 39.7         | 45       |

| 32           | 1.25           | 35.7           | 38.9         | 40.0         | 41.1         | 44       |

| 33<br>34     | 1.28           | 37.0           | 40.3         | 41.4         | 42.5         | 45       |

| 35           | 1.31<br>1.34   | 38.3<br>39.7   | 41.6<br>43.0 | 42.8<br>44.2 | 43.9         | 47       |

| 36           | 1.37           | 41.1           | 44.5         | 45.6         | 45.4<br>46.8 | 50       |

| 37           | 1.37           | 42.5           | 45.9         | 47.1         | 1 48.3 A     | 52       |

| 38           | 1.43           | 43.9           | 47.4         | 48.6         | 49.8         | 53       |

| 39           | 1.46           | 45.3           | 48.9         | 50.1         | 51.4         | 55       |

| 40           | 1.49           | 46.8           | 50.4 /       | 51.7         | 53.0         | 57       |

| 41           | 1.52           | 48.3           | 52.0         | 53.3         | 54.6         | 58       |

| 42           | 1.55           | 49.8           | 53.6         | 55.0         | 56.3         | 60       |

| 43           | 1.58           | 51.4           | 55.3         | 56.7         | 58.1         | 62       |

| 44           | 1.61           | 53.0           | 57.0         | 58.4         | 59.9         | 6/       |

| 45           | 1.64           | 54.6           | 58.8         | 60.2         | 61.7         | 66       |

| 46           | 7 1.67         | 56.3           | 60.6         | 62.1         | 63.6         | 68       |

| 47\          | 1.70           | 58.0           | 62.4         | 64.0         | 65.6         | 70       |

|              |                | 7 25           |              |              |              |          |

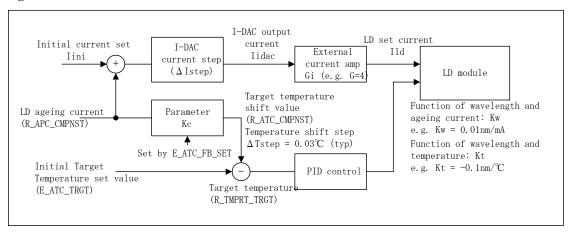

#### 4.5 ATC Feedback function

The ATC Feedback function compensates for wavelength shifts caused by aging. R\_CTRL\_USER.Atc\_fb="1" enables the function, "0" disables it. Turning on this function changes the target temperature according to LD aging error from the PD monitor voltage. Its value (R\_ATC\_CMPNST) is calculated from (E\_ATC\_FB\_SET). This function assumes that there is a first order function between the LD aging error and wavelength increases and uses this function to compensate for this shift caused by aging. When using this function, please note this assumption carefully. Figure 4-8 indicates the block diagram for this function.

Figure 4-8 ATC Feedback Block

#### Its operation is described below

- 1) With LD aging error engaged, initiate the APC compensation circuit. LD compensation current (Digital) is added to the I-DACs selected by R\_APC\_CMPNST.

- 2) Calculate the shift value of the target temperature (R\_ATC\_CMPNST) from the compensation current and the parameter stored in E\_ATC\_FB\_SET (=Kc).

- 3) Shift the target temperature (R\_TMPRT\_TARGET) which is the initial target temperature (E\_ATC\_TRGT) minus the shift value of target temperature (R\_ATC\_CMPNST).

Kc as above is calculated by the expression below.

| If the shift value of wavelength is $\Delta\lambda$ 1, Compensation current (Analog) is $\Delta$ Ild,                 |                                  |

|-----------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Δλ1=Kw*Δlld                                                                                                           | (1)                              |

| If the rate of analog output current per one step of I-DACs is $\Delta$ Istep, the gain of external cur               | rent amplifier is Gi,            |

| The value of compensation current (Digital)                                                                           | 151 (1)                          |

| R_APC_CMPNST=Alld/Gi/Alstep                                                                                           |                                  |

| The shift value of target temperature                                                                                 | W 11, W W ~                      |

| R_ATC_CMPNST=Kc*R_APC_CMPNST                                                                                          | (3)                              |

| If the rate of temperature shift per one step of R_ATC_CMPNST is $\Delta$ Tstep, the value of                         | wavelength shift by the shift of |

| target temperature is $\Delta\lambda 2$ ,                                                                             |                                  |

| Δλ2=Kt*R_ATC_CMPNST*ΔTstep                                                                                            | (4)                              |

| In that sense the value of $Kc$ to make $\Delta\lambda 1=\Delta\lambda 2$ , for compensation of the wavelength shift. |                                  |

| Kc=Kw*Gi/Kt* ΔIstep/ΔTstep                                                                                            | (5)                              |

|                                                                                                                       |                                  |

For example: If Kw=0.01nm/mA, Gi=4, Kt=0.1nm/°C, \( \text{Alstep=0.08mA/step}, \text{ATstep=0.03°C/step}, Kc=1.07. \)

Since this function does not actually watch the wavelength, care must be exercised when setting these values. Parameter values of Kc can be selected from 0.125, 0.25, 0.375, 0.5, 0.625, 0.75, 1.0, 1.125, 1.25 and 1.5.

#### 5. Sequencer

#### 5.1 Operation mode

The AK2571 has three operation modes shown below. Use the serial interface to change from one mode to another. Figure 5-1 shows the operating flowchart and table 5-1 indicates the circuit block capabilities.

- 1) Self-operation mode: Operates ATC and APC automatically according to the data stored in EEPROM.

- 2) Register access mode: Adjust the data to set the characteristics of LD. Read and write registers are accessed by writing commands to the Digital interface.

- 3) EEPROM access mode: Fix the adjusted data and parameters in EEPROM. Data in register are written in EEPROM and reset. All ATC and APC functions are disabled in this mode.

Figure 5-1

Table 5-1

|          |       | Self operation mode | Register access       | EEPROM access |

|----------|-------|---------------------|-----------------------|---------------|

| Register | Read  | O.K.                | O.K.                  | Non           |

|          | Write | Non                 | O.K.                  | Non           |

| EEPROM   | Read  | Non                 | Non                   | O.K.          |

|          | Write | Non                 | Non                   | O.K.          |

| Status   | P_EEP | 0                   | 0                     | 1             |

| APC      |       | Auto operation by   | Operation by register | Shut Down     |

|          |       | EEPROM data         | data                  |               |

| ATC      |       | Auto operation by   | Auto operation by     | Shut Down     |

|          |       | EEPROM data         | register data         | 0 01          |

#### 5.2 Self operation mode

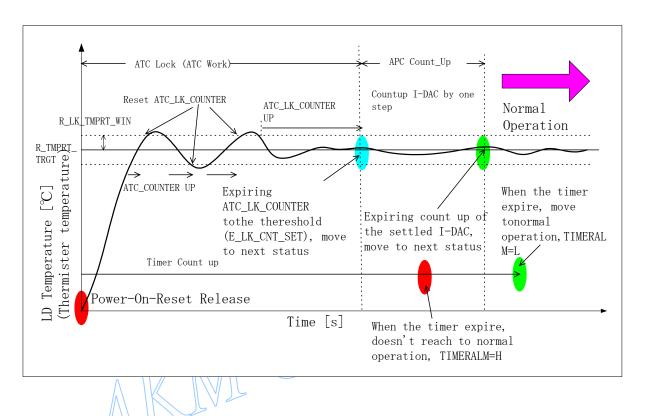

### 5.2.1 Start up sequence

The AK2571 has various start-up sequence patterns that set the control register (R\_CTRL\_AKM/R\_CTRL\_USER). The AK2571 automatically executes the start up sequence stored in EEPROM when it is started or re-start. Table 5-2 and Figure 5-2 explains each sequence.

Table 5-2

|                                    | Condition of finish | ATC status          | APC status                               | APC_FB       | ATC_FB       | APCALM       | ATCALM       |

|------------------------------------|---------------------|---------------------|------------------------------------------|--------------|--------------|--------------|--------------|

|                                    |                     |                     | Powe                                     | er ON        |              |              |              |

|                                    |                     |                     | Į                                        |              |              |              |              |

| Status-1<br>(Only ATC<br>work)     | ATC Lock            | ATC Lock            | Disable                                  | Disable      | Disable      | User setting | User setting |

|                                    |                     |                     | Į                                        |              |              |              |              |

| Status-2<br>(APC Count<br>up work) | APC<br>Count up     | Normal operation    | Count up or<br>Disable<br>(User setting) | Disable      | Disable      | User setting | User setting |

|                                    |                     |                     | Į                                        |              |              |              |              |

| Status-3<br>(Normal<br>operation)  |                     | Normal<br>operation | Normal<br>operation                      | User setting | User setting | User setting | User setting |

Figure 5-2 Start up sequence

#### 5.2.2 Control registers

Figure 5-3 illustrates the register format. There are two areas in these registers, one is for AKM factory use and the other is for user customization. Even though both areas are re-writable, the AKM values SHOULD NOT BE OVERWRITTEN. If the AKM values are modified product functionality cannot be guaranteed.

Self operation mode: Load the data from EEPROM to register Register access mode: All data can be rewritable D6 D5 D7 Register alm[4] alm[3] count[2] fb[1] fb[0] main[5] lock[4]main[3] [7] [6] Atc\_main / Atc\_lock / Apc\_main / Timer / Atc\_fb / Apc\_fb / Apc\_cnt: 0: Disable 1: Enable Atc\_alm / Apc\_alm: O ALM Enable, 1: ALM Disable Fix\_ctrl[2:000: Start up or APC Count-up, Except000: Normal operation User available area Factory usage area by AKM REPROM E\_INI\_CTRL\_USER E INI CNTL AKM Initial Stat E\_APC\_CNT\_CTRL\_USER E\_APC\_CNT\_CTRL\_AKM APC Count-up E\_FIX\_CTRL\_AKM Normal Operation X: Forbidden (Ignore the setting)

Figure 5-3 Control Register

#### 5.2.3 ATC Lock

- 1) When temperature data (R\_TMPRT\_CRNT) enters the target temperature range (R\_TMPRT\_TRGT) +/- hysteresis (E\_LK\_TMPRT\_WIN) ATC\_LOCK\_COUNTER starts to count up\_every 8mS.

- 2) Once temperature data is out of the range, ATC LOCK COUNTER is reset.

- 3) LD temperature is stabilized when ATC\_LOCK\_COUNTER reaches the settled value (E\_LK\_CNT\_SET),. When this happens, the AK2571 completes the ATC Lock sequence and moves to Status-2.

#### 5.2.4 APC Count up

- 1) Increment the selected I-DAC value by one step (each 8mS) to prevent abrupt heat increases from affecting ATC.

- 2) Count up ends when the I-DACx selected by E\_APC\_CNT\_SET (Count up DAC) reaches the target value (E\_APC\_CNT\_CTRL\_USER[7:0]).

- 3) The unselected I-DAC retains the feed forward APC value if the Count up DAC doesn't reach settled value.

- 4) Although the unselected DAC doesn't reach its feed forward APC (or fixed) value, if count up DAC reaches to the settled value, the AK2571 moves to Status-3

#### 5.2.5 Timer

- 1) Counts the time from power on reset or release of shut down.

- 2) If the AK2571 does not reach normal operation within the period set by the settling time register (E\_TIMER\_SET), , TIMERALM is output.

#### 5.2.6 Normal operation

After the AK2571 has been properly configured and is in "normal" operating mode, continuous temperature compensation is performed every 8 milliseconds using the data in EEPROM.

#### 5.3 Register access mode

Register access mode is used to for adjust the characteristics of the Laser Diode Module. Any characteristics can be adjusted while monitoring by writing to the appropriate register. Please refer to "8. Registers" for details.

#### 5.3.1 ATC and APC Adjustment Example

The following adjustment process example is based on the assumption that polarity of ALM, threshold level of ALM, PID, Max current of APC feedback, etc. are already fixed and every parameter is written in the EEPROM continuously.

- Change the operation mode from self-operation to register access by sending the appropriate command through the Digital interface.

- 2) Common settings

- 2-1) Write zero ("O") to all registers R\_CTRL\_AKM .to stop the AK2571 working.

- 2-2) Select I-DACx for APC by using the R DAC SET register.

- 2-3) If the temperature corresponding to wave length is known (either exactly or approximately), set the input temperature offset by using the R\_ATC\_OFFSET register. (Please refer to "4.4 Gain & Offset"). In this process, the target temperature must be set at the midpoint of the ADC (80h).

- 2-4) Write 80h to the target temperature register (R\_TMPRT\_TRGT)

- 2-5) Use register R\_TEC\_CTRL\_SET to select a way to control the TEC.. When using Analog control use register R\_TEC\_ANALOG to select Analog-1 or Analog-2.. If using Digital control, use register IR\_TEC\_PWM\_SET to set the PWM division.

- 3) ATC adjustment

- 3-1) Temperature Adjustment

When a "1" is written to the R\_CTRL\_AKM Atc\_main(R\_CTRL=08h), the ATC begins control of the TEC to meet target the temperature. 10 to 30 seconds are required before the LD temperature is fully stabilized. This time depends on the difference between ambient temperature and target temperature. Stabilization is detected from the ATC Lock completion signal through the STATUS\_MON pin moving from Low to High. To detect this signal, E\_LK\_CNT\_SET and E\_LK\_TMPRT\_WIN must be set to the appropriate values, STATUS\_MON pin must be set to ATC\_LK (R\_STATUS\_SET=000), and a "1" must be written R\_CTRL\_AKM.Atc\_lk (R\_CTRL\_AKM=18h) prior to ATC adjustment.

To complete the ATC adjustment by monitoring the temperature, a preliminary rough adjustment is made using the offset (R\_ATC\_OFFSET) and secondary fine adjustment using the target temperature register(R\_TMPRT\_TRGT) should be executed to match the temperature required.

#### 3-2) Wavelength Adjustment

It is also possible to adjust the ATC monitoring wavelength. When doing this, the APC be adjusted to work to maintain consistent light power. Writing "1" in R\_CTRL\_AKM.Apc\_main (R\_CTRL\_AKM=28h) starts APC. Follow the APC adjustment instructions in the next section and roughly set R\_DACx\_GAIN and R\_DACx corresponding to I-DAC for use

A preliminary rough adjustment is made using the offset (R\_ATC\_OFFSET) and secondary fine adjustment using the target temperature register(R\_TMPRT\_TRGT) should be executed to match the temperature required.

#### 4) APC adjustment

#### 4-1) I-DAC adjustment

a) Adjust R\_DACx to set the light power of the LD. Firstly set register R\_DACx\_GAIN for the full code of I-DAC being over 80h to get sufficient accuracy. But it is need to take the margin for LD aging compensation for the APC Feed back DAC. R\_DACx\_GAIN of APC Feed back must be limited to remain Feed back compensation current. For example R\_DACx must not beyond 80h if aging compensation current is needed by the same amount of initial current. And not beyond C0h if aging compensation current is needed by the half amount of initial current.

- b) When using the I-DAC1 dithering function, enable R\_EA\_SW, set the gain using register R\_EA\_GAIN and set the frequency using R\_EA\_FREQ. Monitor the total I-DAC1 current since this dithering current is added to R\_DAC1 R\_DAC1 must be adjusted with this in mind.

- c) If the wavelength moves after the APC adjustment, adjust R\_TMPRT\_TRGT to match the wavelength or go back and readjust the ATC.

#### 4-2) PDMON Gain setting

Set the PD voltage gain monitoring. The range is from 0.4V to 1.1V / 0.1V step. This setting must be executed after R PDGAIN is set.

- 4-3) Initial aging error setting (R\_APC\_TRGT adjustment)

- a) STATUSMON setting: Set R\_STATUS\_SET = "APC FB". When the aging compensation current is added to the I-DAC output, STATUS\_MON becomes High.

- b) R\_CTRL\_USER.Apc\_fb = 1 executes the APC Feedback function. In this register access mode, actually the APC Feedback function doesn't add current to the R\_DACx to make sure this adjustment.

- c) Moving R\_APC\_TRGT, identify the point at which STATUS\_MON becomes High. This is the initial aging set point.

- 5) APC setting

If there are external components affected by ambient temperature changes (current amplifiers, driver IC etc.), training for cancellation of temperature characteristics is needed. To do this:

- 5-1) Stabilize the ambient temperature

- 5-2) Read the R TV[7:0] (internal T V converter digital output) through the serial interface.

- 5-3) Adjust R\_DACx to output adequate current at the temperature.

- 5-4) Store the data 5-2) as address and 5-3) as data in the look-up table.

- 5-5) Change temperature and repeat this sequence.

- 6) Set another wavelength

The AK2571 can store the data for four wavelengths in EEPROM. To get the data for another three wavelengths, repeat the sequence from 2) to 5).

Wavelength selection is via pin control.

- 7) Writing the EEPROM

- 7-1) Compose the data to write in the EEPROM based on the adjustment above.

- 7-2) Change the mode to EEPROM mode.

- 7-3) Write the data in EEPROM through the serial interface.

- 8) Test

Change to Self-operation mode, and confirm all functions work. If there are problems, repeat steps1 to7 and readjust.

Caution: All the data in registers is reset when the power is removed or when the operating mode is changed.

#### 5.3.2 Confirmation of other functions

#### 1) OPALM confirmation

When the APC adjustments are complete, set R\_OPALM\_SET.

Gradually decrement the value of R\_DACx OPALM is output as a current. Confirm LD light power is settled value or not by monitoring the output of PDMON.

#### 2) Aging Error Compensation confirmation

After APC adjustments are complete, write "1" in R\_CTRLApc\_fb. decrement the value of R\_DACx, but don't reduce it too much as OPALM is output. APC Feedback begins to function and will increase the value of R\_APC\_CMPNST. In this register access mode, APC does not add to R\_DACx and the light power of the LD does not increase, actually. Eventually R\_APC\_CMPNST will equal E\_APC\_FB\_MAX. If E\_CUALM\_SET is set to an equal value of E\_APC\_FB\_MAX beforehand, CUALM out expresses the increment of aging compensation current.

#### 3) Aging shift of wavelength compensation confirmation

This confirmation can be done with 2) Aging Error Compensation confirmation. R\_CTRLAtc\_fb="1" enables the ATC feedback confirmation. Decrement the value of R\_DACx, but do not reduce it too much as OPALM is output. APC Feedback begins to function and increases the value of R\_APC\_CMPNST. According to this value, R\_ATC\_CMPNST is increased by the E\_ATC\_FB\_SET parameter. R\_ATC\_CMPNST will eventually equal E\_ATC\_FB\_MAX. If E\_WLALM\_SET is set equal to E\_ATC\_FB\_MAX and below the value of E\_APC\_FB\_SET or E\_ATC\_FB\_SET beforehand, WLALM output indicates the shift of target temperature.

#### 6. Monitor function

#### 6.1 AMON pin analog monitor

Set R\_MON\_SET (E\_MON\_SET) register, and monitor the values in the registers below through MON-DAC. Table 6-1 indicates the registers that can be monitored. Output voltage (Vmon) (typ) is expressed below.

Vmon = (2.1-0.5)/255\*K+0.5 [V]

K=the decimal value of the register

Table 6-1 Monitoring Register

| R_MO | N_SET |   |   | Monitoring Function        | Remarks           |  |  |  |

|------|-------|---|---|----------------------------|-------------------|--|--|--|

| 0    | 0     | 0 | 0 | Fixed voltage              | R_MON_DAC_FIX     |  |  |  |

| 0    | 0     | 0 | 1 | PID control absolute value | R_RID_ABS[12:5]   |  |  |  |

| 0    | 0     | 1 | 0 | APC feedback value         | R_APC_CMPNST[7:0] |  |  |  |

| 0    | 0     | 1 | 1 | ATC target value           | R_TMPRT_CRNT[7:0] |  |  |  |

| 0    | 1     | 0 | 0 | ATC feedback value         | R_ATC_CMPNST[7:0] |  |  |  |

| 0    | 1     | 0 | 1 | IDAC1 set value            | R_DAC1[7:0]       |  |  |  |

| 0    | 1     | 1 | 0 | IDAC2 set value            | R_DAC2[7:0]       |  |  |  |

| 0    | 1     | 1 | 1 | IDAC3 set value            | R_DAC3[7:0]       |  |  |  |

| 1    | 0     | 0 | 0 | T_V converter output       | R_TV[7:0]         |  |  |  |

|      |       |   |   |                            |                   |  |  |  |

#### 6.2 STATUS\_MON pin output

Set R\_STATUS\_MON (E\_STATUS\_SET), and monitor the status in AK2571 through STATUS\_MON pin. Table 6-2 indicates the setting

Table 6-2 STATUS\_MON output

| E_STATUS_SET[20] | STATUS_MON output                   | Remarks                                                                          |

|------------------|-------------------------------------|----------------------------------------------------------------------------------|

| 000              | ATC_LOCKATCLook count up            | 0:counting<br>1:countup                                                          |

| 001              | APC_END<br>APC Count-up expiring    | 0:APC CountuporCountupdisable<br>1:APC Countupexpiring                           |

| 010              | E_FIX_CTRL Move to normal operation | 0: before normal operation (startup)<br>1: Normal Operation                      |

| 011              | APC_FB<br>APC Feedbackworking       | 0: APC Feedback Compensation current=0<br>1: APC Feedback Compensation current>0 |

| 100              | ATC_FB<br>ATCFeedbackworking        | 0:ATC Feedback target temp. shift=0<br>1:ATC Feedback target temp. shift>0       |

| 101              | REG<br>Registeraccess mode          | 0:Selfoperation or EEPROM mode<br>1:Register access mode                         |

| 110              | PID_SIGN<br>PID control direction   | 0:Heating<br>1:Cooling                                                           |

| 111              | APC_COMP  APC_COMPoutput            | 0: PDIN is higher than target<br>1: PDIN is lower than target                    |

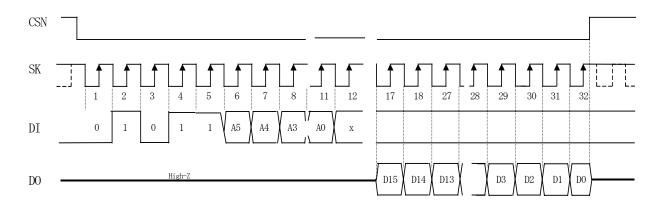

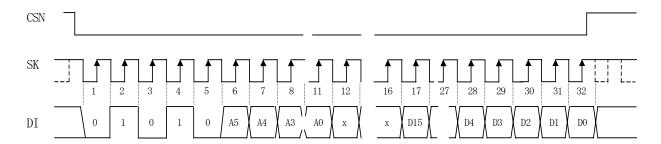

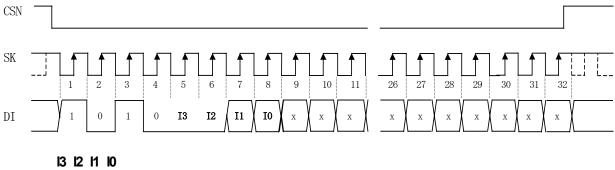

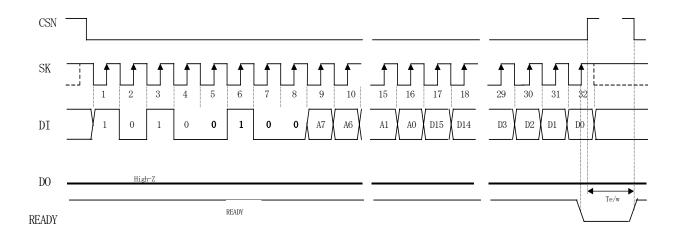

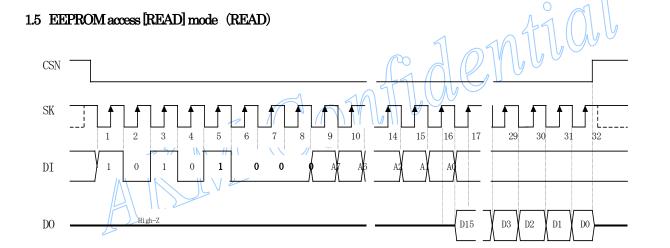

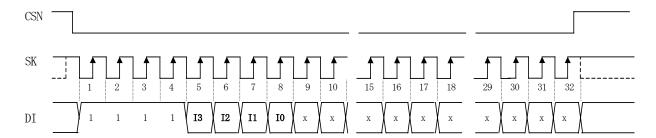

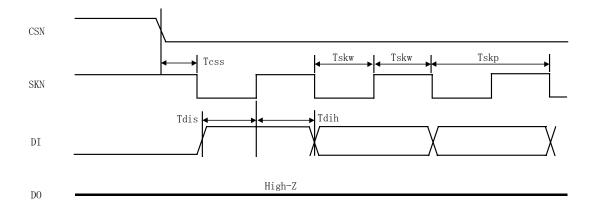

#### 7. EEPROM

The internal 4k-bits EEPROM is composed of 16-bits\*256 addresses. The memory map is shown in Table 7-1. Two MSB bits are set by WAVEO and 1,. It is possible to change the target temperature via pin strapping if the adjustment data for each wavelength is stored in an EEPROM address. Table 7-2 indicate the relationship between WAVEO, 1 and the EEPROM addresses. Addresses from [xx111010] to [xx111111], which contain system data, user program area and AKM factory data, are valid regardless of the settings of WAVEO,1.

Table 7-1 EEPROM Memory Map Overview

| Address | 3  |      | D15-D8                               | D7-D0             |

|---------|----|------|--------------------------------------|-------------------|

| 00      | 00 | 0000 | E_DAC1_TV[00001]                     | E_DAC1_TV[00000]  |

|         |    |      |                                      |                   |

|         |    |      | Wavelength-1: I-DAC1temperature      |                   |

|         |    |      | compensation value                   |                   |

|         |    | 1111 |                                      | E_DAC1_TV[11110]  |

|         |    |      | E_DAC1_TV[11111]                     |                   |

|         | 01 | 0000 | E_DAC2_TV                            | _                 |

|         |    | 1111 | Wavelengh-1 I-DAC2 temperature of    | ompensation value |

|         | 10 | 0000 | E_DAC3_TV                            |                   |

|         |    | 1111 | Wavelength-1 I-DAC3 temperature o    |                   |

|         | 11 | 0000 | Wavelength-1setting data for each wa | velength          |

|         |    | 1001 |                                      |                   |

|         |    | 1010 | Common setting data-1                |                   |

|         |    | 1111 |                                      |                   |

| 01      | 00 | 0000 | Wavelength-2 data                    |                   |

|         | 11 | 1001 |                                      |                   |

|         |    | 1010 | Common setting data-2                |                   |

|         |    | 1111 |                                      |                   |

| 10      | 00 | 0000 | Wavelength-3 data                    |                   |

|         | 11 | 1001 |                                      |                   |

|         |    | 1010 | User program area                    |                   |

|         |    | 1111 |                                      |                   |

| 11      | 00 | 0000 | Wavelength-4 data                    |                   |

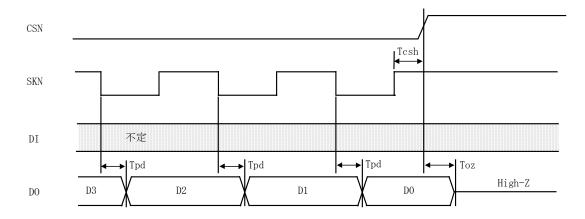

|         | 11 | 1001 |                                      |                   |