# TRANSWITCH

#### DATA SHEET

#### **FEATURES**

- Maps an asynchronous 139.264 Mbit/s tributary into an AU-4/VC-4 STS-3c/SPE.

- Nibble or byte 139.264 Mbit/s line interface

G.751 receive and transmit performance monitoring (frame alignment, distant alarm indication)

- SDH/SONET bus access

- Drop/add byte buses

- Optional drop bus AU-4 pointer tracking with framing delay compensation

- SDH/SONET timing mode

- Drop bus timing

- Add bus timing

- External timing with framing delay compensation

- Microprocessor access

- Intel I/O with separate address/data buses

- Motorola I/O with separate address/data buses

- Motorola I/O with multiplexed bus

- Interrupt capability with individual mask bits

- POH byte processing

- Enhanced desynchronizer access

- Testing features

- Line loopback

- SDH/SONET loopback

- 2<sup>23</sup>-1 test generator and analyzer

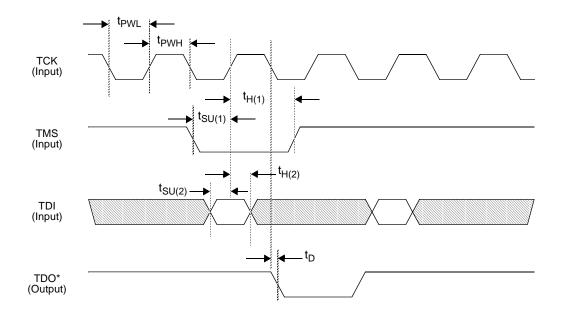

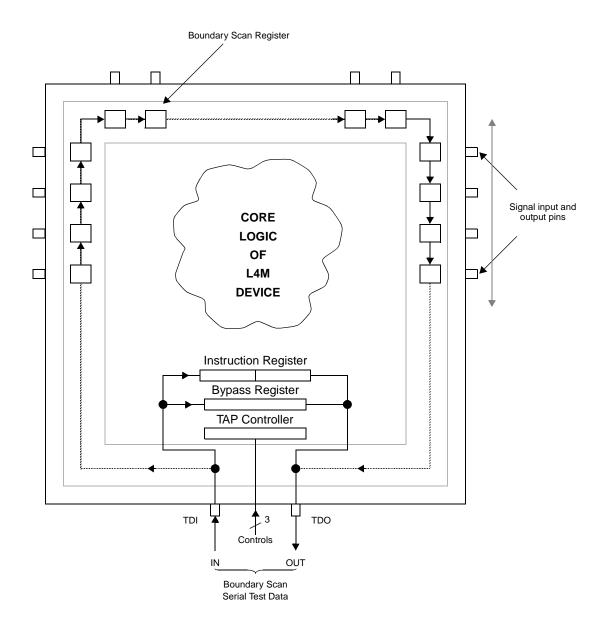

- Boundary scan capability (IEEE 1149.1)

- 144-pin plastic quad flat package

#### **DESCRIPTION**

The L4M device maps a 139.264 Mbit/s asynchronous line signal into an AU-4 VC-4/STS-3c SPE signal. The SDH/SONET signal is transmitted via the add bus with timing derived from the drop bus, add bus, or external clock source. The L4M can compensate for up to a frame offset when using external timing and an external C1 pulse. An option is provided to generate TOH bytes, such as the A1 and A2 framing bytes, a C1 byte, and the H1 and H2 pointer bytes only in drop bus and external timing modes. The VC-4/SPE can be fixed to a known J1 reference when add bus timing is selected, or it can be positioned with a pointer value of 0 or 522 when drop bus or external timing is selected.

In the drop direction, an optional pointer tracking machine is provided. In this mode, the L4M can compensate for up to a frame in offset. External access is provided for the POH bytes, in addition to internal processing capability. Serial access is provided for the overhead communications bits in the format. An alarm indication port is provided for ring configuration applications.

### APPLICATIONS

- Add/drop multiplexers

- Digital cross-connect systems

- Broadband switching systems

- Transmission equipment

#### TABLE OF CONTENTS

| Section                                 | <u>Page</u> |

|-----------------------------------------|-------------|

| Block Diagram                           | 3           |

| Block Diagram Description               | 4           |

| Pin Diagram                             | 7           |

| Pin Descriptions                        | 8           |

| Absolute Maximum Ratings                | 19          |

| Thermal Characteristics                 |             |

| Power Requirements                      | 19          |

| Input, Output and I/O Parameters        | 20          |

| Timing Characteristics                  | 22          |

| Operation                               | 40-61       |

| Internal Device Operation               | 40          |

| External Device Operation               | 57          |

| Memory Map                              | 62          |

| Memory Map Descriptions                 | 66          |

| Package Information                     | 89          |

| Ordering Information                    |             |

| Related Products                        |             |

| Standards Documentation Sources         | 91          |

| List of Data Sheet Changes              | 93          |

| Documentation Update Registration Form* |             |

\* Please note that TranSwitch provides documentation for all of its products. Customers who are using a TranSwitch Product, or planning to do so, should register with the TranSwitch Marketing Department to receive relevant updated and supplemental documentation as it is issued. They should also contact the Applications Engineering Department to ensure that they are provided with the latest available information about the product, especially before undertaking development of new designs incorporating the product.

#### LIST OF FIGURES

| <u>Figure</u> | <u>Pa</u>                                                  | age  |

|---------------|------------------------------------------------------------|------|

| 1             | L4M TXC-03456 Block Diagram                                | 3    |

| 2             | L4M TXC-03456 Pin Diagram                                  | 7    |

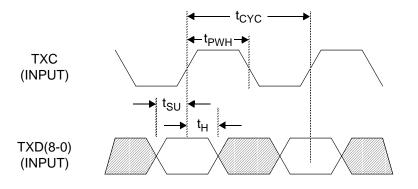

| 3             | Transmit Line Interface Timing                             | . 22 |

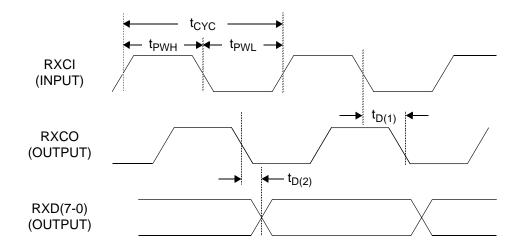

| 4             | Receive Line Interface Timing                              | . 23 |

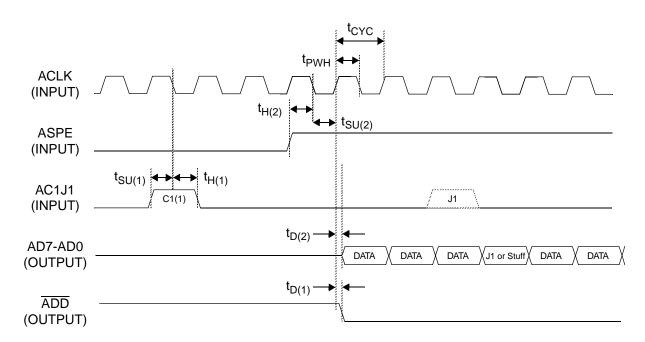

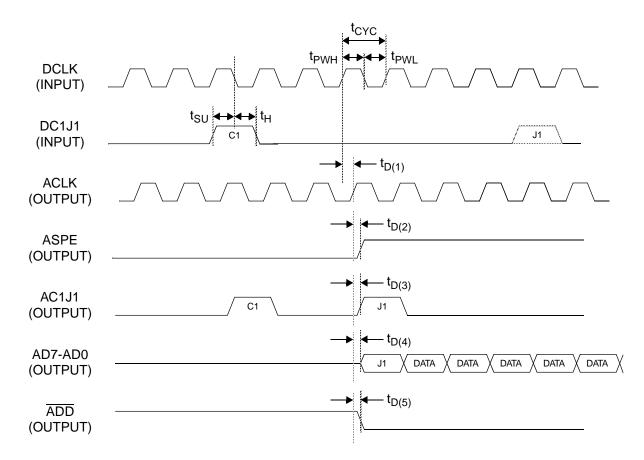

| 5             | Add Bus Interface Timing (Add Bus)                         | . 24 |

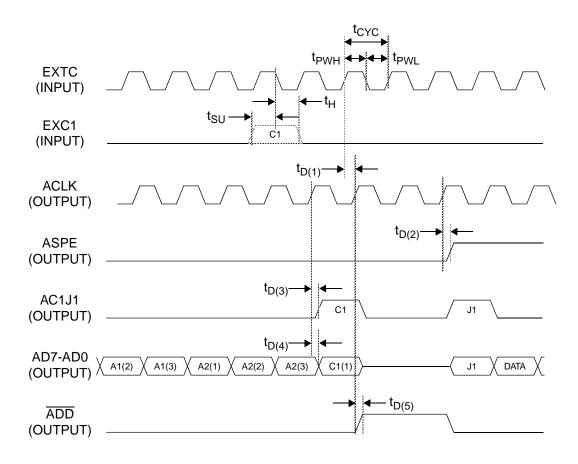

| 6             | Add Bus Interface Timing (External Clock)                  | . 25 |

| 7             | Add Bus Interface Timing (Drop Bus Clock and C1)           | . 26 |

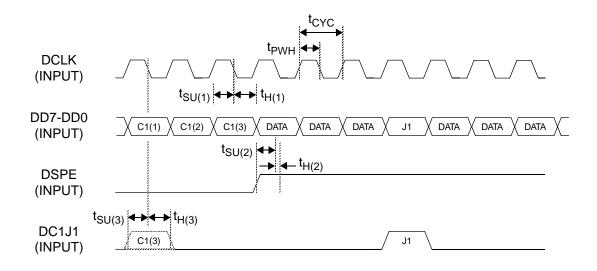

| 8             | Drop Bus Interface Timing                                  | . 27 |

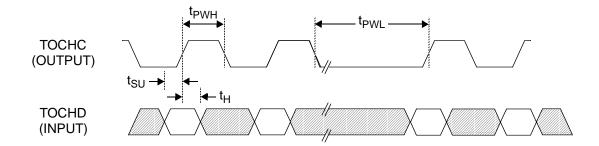

| 9             | Transmit Overhead Comm Channel Timing                      | . 28 |

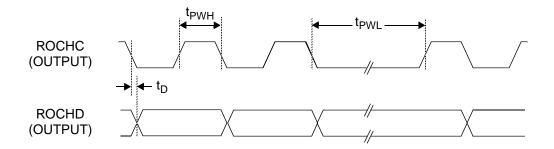

| 10            | Receive Overhead Comm Channel Timing                       | . 28 |

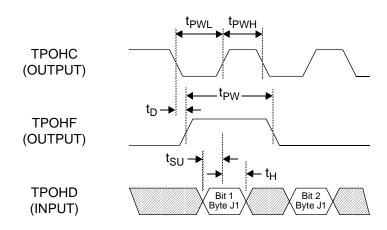

| 11            | Transmit Path Overhead Interface Timing                    | . 29 |

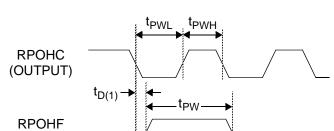

| 12            | Receive Path Overhead Interface Timing                     | . 30 |

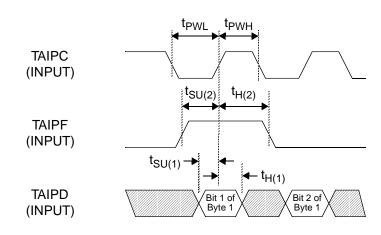

| 13            | Transmit Alarm Indication Port Timing                      | . 31 |

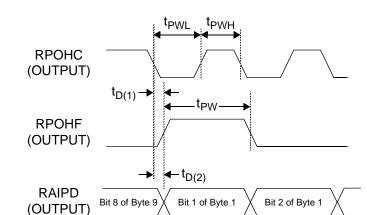

| 14            | Receive Alarm Indication Port Timing                       | . 32 |

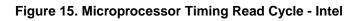

| 15            | Microprocessor Timing Read Cycle - Intel                   | . 33 |

| 16            | Microprocessor Timing Write Cycle - Intel                  | . 34 |

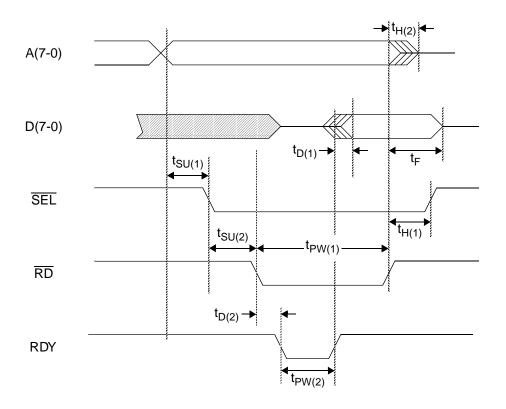

| 17            | Microprocessor Timing Read Cycle - Motorola                | . 35 |

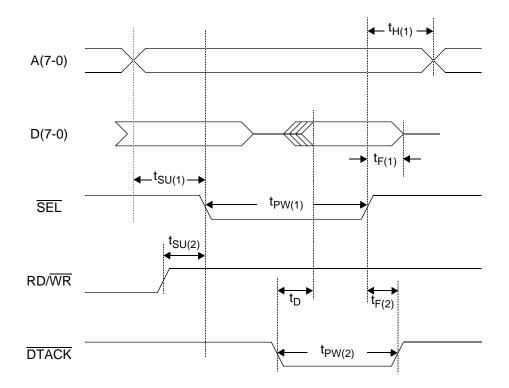

| 18            | Microprocessor Timing Write Cycle - Motorola               | . 36 |

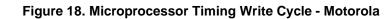

| 19            | Microprocessor Timing Read Cycle Multiplex Bus - Motorola  | . 37 |

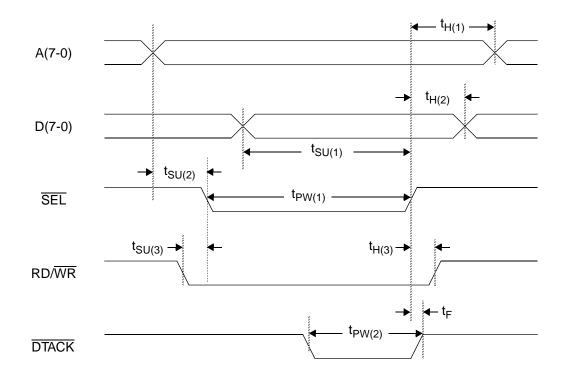

| 20            | Microprocessor Timing Write Cycle Multiplex Bus - Motorola | . 38 |

| 21            | Boundary Scan Timing                                       | . 39 |

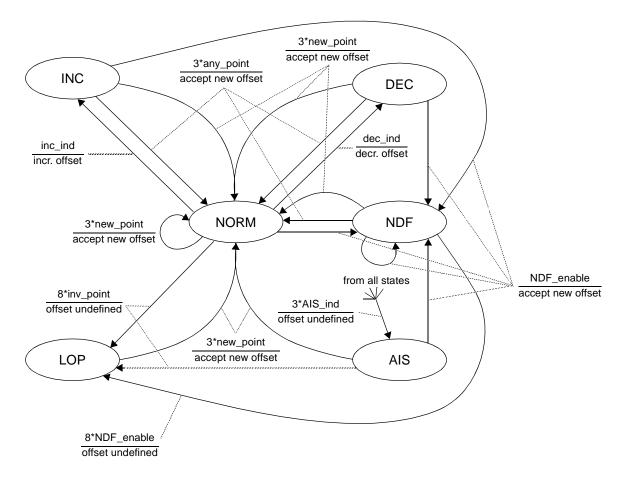

| 22            | Pointer Interpretation State Diagram                       | . 41 |

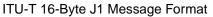

| 23            | Test Generator, Analyzer and Loopback                      | . 49 |

| 24            | Boundary Scan Schematic                                    |      |

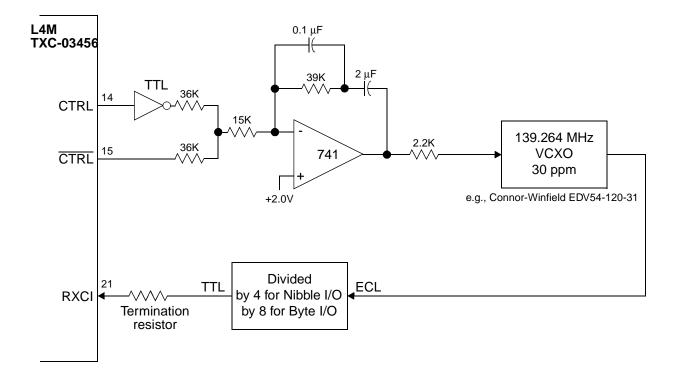

| 25            | Phase-Locked Loop                                          | . 57 |

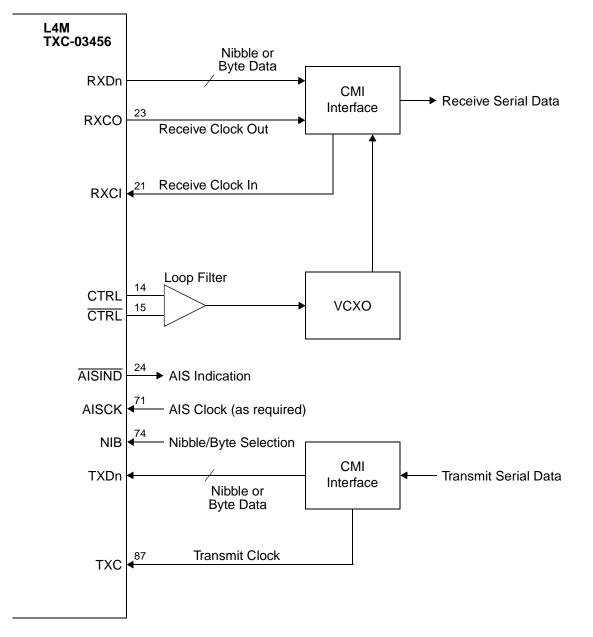

| 26            | L4M 140 Mbit/s Line Interface                              | . 58 |

| 27            | Use of Two L4M Devices in Ring Configuration               | . 60 |

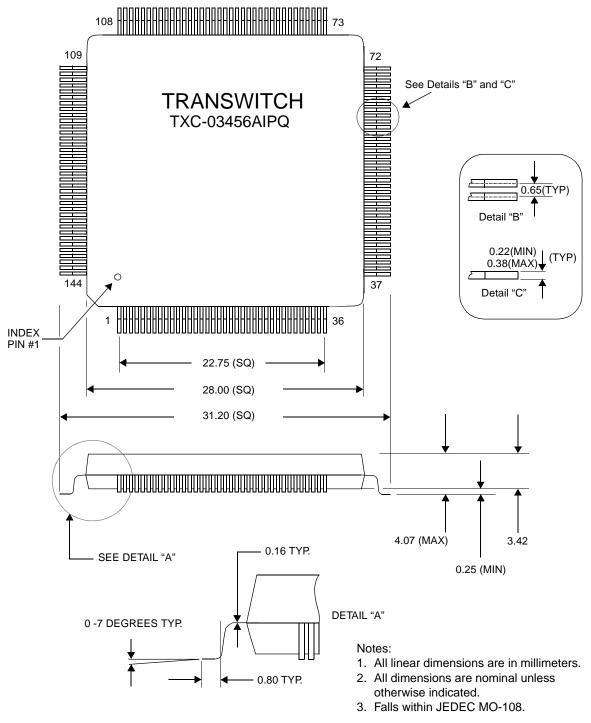

| 28            | L4M TXC-03456 144-Pin Plastic Quad Flat Package            | . 89 |

# TRANSWITCH<sup>®</sup>\_\_\_\_

DATA SHEET

LINE SIDE

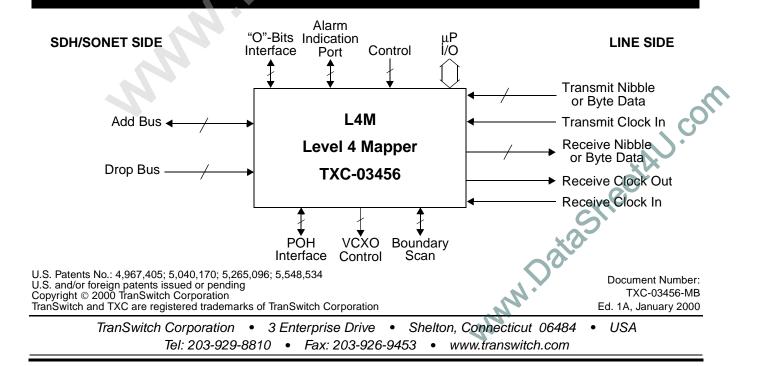

**BLOCK DIAGRAM**

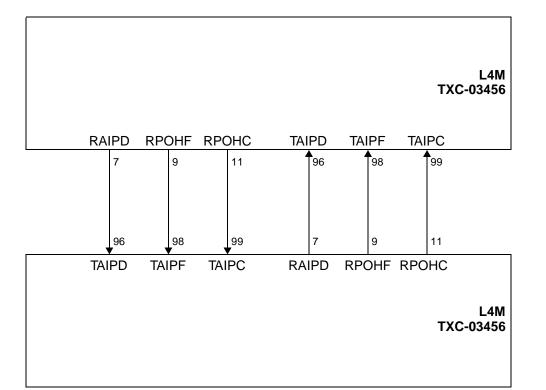

Figure 1. L4M TXC-03456 Block Diagram

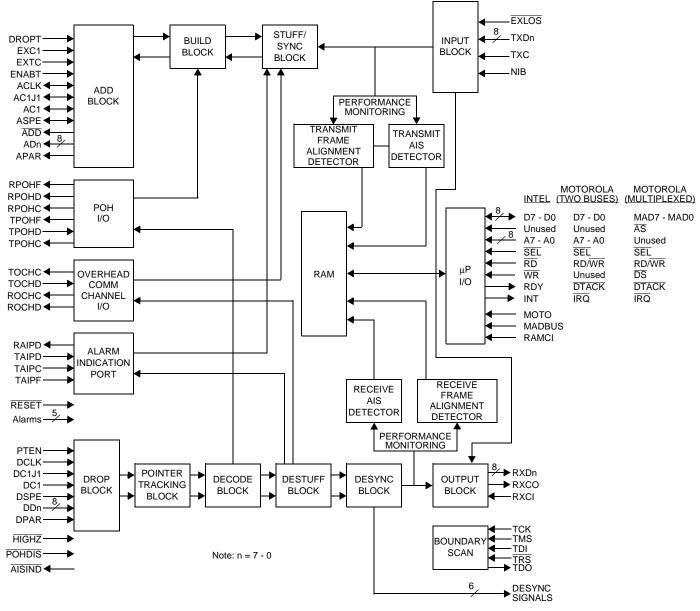

# **BLOCK DIAGRAM DESCRIPTION**

<u>SWITCH</u>

A simplified block diagram of the L4M device is shown in Figure 1. A byte-wide or nibble-wide 139.264 Mbit/s signal (TXDn) is connected to the Input Block. The nibble interface is selected by placing a high on the lead designated as NIB. Data is clocked into the L4M on positive transitions of the clock signal TXC. A control bit is provided which enables data to be clocked into the L4M on negative transitions of the clock. The L4M Input Block also terminates an external loss of signal (EXLOS) indication. A low placed on this lead indicates that an external line interface device, such as a CMI interface device, has detected a loss of signal. This signal is reported as an alarm within the L4M for the microprocessor, and can generate an interrupt and a 140 Mbit/s AIS when enabled.

The 140 Mbit/s transmit line signal is monitored by the two Transmit Performance Monitoring Blocks for ITU-T G.751 frame alignment and a Distant Alarm Status. A Distant Alarm is defined as a 1 in bit 13 of the G.751 frame format. This alarm can generate an interrupt indication when enabled. When frame alignment is established, framing errors are counted in a 16-bit performance counter. The 140 Mbit/s line signal is also monitored for an Alarm Indication Signal (AIS). The AIS detection circuit can be enabled to work in conjunction with the frame alignment circuit. An AIS condition is reported as an alarm, and can generate an interrupt when enabled.

The Stuff/Sync Block contains a FIFO and is controlled by write timing from the Input Block, and by read timing from the Build Block. The FIFO accommodates input and timing jitter as specified in ITU-T Recommendation G.823. The FIFO is protected against overflow and underflow conditions by reporting a FIFO error alarm, and will automatically recenter when a FIFO underflow or overflow alarm has been detected. The reset is held for approximately one frame before the FIFO is released for operation. Upon power-up, or on applying a reset, the transmit FIFO is also recentered. The stuffing algorithm uses one set of five control bits (C-bits) with one stuff opportunity bit (S-bit) per subframe (nine subframes) for frequency justification.

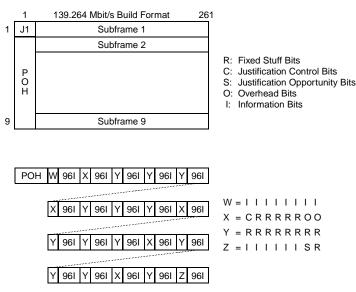

The Build Block, with timing signals exchanged with the Stuff/Sync Block, constructs the VC-4 format as illustrated below.

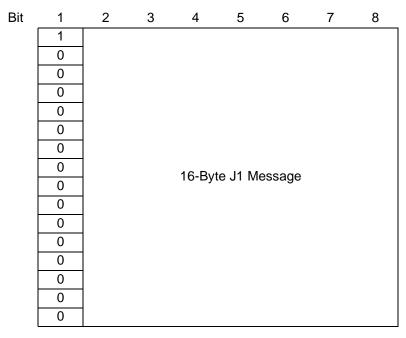

The L4M can build the 261 column by 9 row VC-4 format without or with path overhead bytes, and "O"-bits, depending on the features selected. The addition of POH bytes to the VC-4 format is disabled by applying a low to the pin designated POHDIS (also applying a low to POHDIS disables receive VC-4 POH processing). The starting position of the VC-4 J1 bytes can be synchronized to the add bus J1 pulse, when add bus timing is selected, or have a starting location of 0 or 522, when drop bus or the external timing modes are selected.

The L4M can also generate an unequipped or supervisory unequipped VC-4. An unequipped VC-4 is defined as all zeros for the POH and payload bytes, while a supervisory unequipped VC-4 is defined as having valid POH bytes, but the payload bytes equal to zero. The Build Block is also responsible for multiplexing individual

POH bytes from the Path Overhead interface, or from RAM locations written to by the microprocessor, into the add bus data stream. The RDI state and FEBE count may be provided from a mate L4M for path-protected ring configurations.

The Add Block uses drop bus timing signals, add bus timing signals, or external timing signals for outputting the SDH/STS-3c data signal and parity to the add bus. A feature is also provided that generates the A1, A2, C1 and H1/H2 Transport (SDH Section) Overhead bytes, depending upon the timing mode selected. The C1 byte value may be a fixed or a microprocessor-written value. The SS-bits in the transmitted pointer may be fixed or written by the microprocessor. Unused Transport Overhead bytes can be selected to be three-stated or forced to zero. In the add bus timing mode, the clock and C1J1 signals are monitored for operation. In the external timing mode, an option is provided which can compensate up to a frame for the position of the C1 byte framing pulse (EXC1).

The Add Block interface for the add bus timing mode consists of an input clock (ACLK), input C1 and J1 indicator (AC1J1), a separate C1 input (AC1) when enabled, an input SPE indicator (ASPE), output byte data (AD7-AD0), output parity indication (APAR), and an output add data to bus indicator (ADD). When the L4M is configured to operate in the external timing mode, the add bus signals consist of: external reference input clock (EXTC) and framing signal (EXC1) (optional), an output clock (ACLK), output C1 and J1 indicator (AC1J1), an output SPE indicator (ASPE), output byte data (AD7-AD0), output parity indication (APAR), and an output add data to bus indicator (ADD). When the L4M is configured to operate in the drop bus timing mode, the add bus signals consist of: an output clock (ACLK), output C1 and J1 indicator (AC1J1), an output SPE indicator (ASPE), output byte data (AD7-AD0), output parity indicator (AC1J1), an output SPE indicator (ASPE), output byte data (AD7-AD0), output parity indicator (AC1J1), an output SPE indicator (ASPE), output byte data (AD7-AD0), output parity indication (APAR), and an output add data to bus indicator (ADD). Odd parity may be calculated over all add bus signals (except the add indicator), or data only.

The Drop Block terminates the drop bus signals. The drop bus signals consists of an input clock (DCLK), input C1 and J1 indicator (DC1J1), an input SPE indicator (DSPE), input byte data (DD7-DD0), input parity indication (DPAR), and an optional framing pulse (DC1). When the pointer tracking machine feature is enabled, the J1 signal in the C1J1 signal must not be present. Odd parity may be checked over all of the drop bus signals, or for the data byte only. When the pointer tracking machine is enabled, the relative position of C1 can be compensated up to one frame.

The Pointer Tracking Block is enabled by placing a high on the lead designated as PTEN. The pointer tracking machine meets the pointer tracking requirements specified in ETSI 1015. The Pointer Tracking Block determines the starting location of the J1 byte in the VC-4 format. The S-bit transition check in the H1 pointer byte may be disabled in the Pointer Tracking Block. When enabled, the S-bit check can be a fixed value or a value written by the microprocessor. In addition, the AIS to LOP transition can be disabled to have the Pointer Tracking state machine conform to Bellcore standards. The Pointer Tracking Block monitors the pointer bytes for a path AIS and LOP alarm. Positive, negative and NDF occurrences are counted in 8-bit performance counters.

Having established the starting location of the VC-4, the Decode Block performs Path Overhead byte processing. The POH bytes are written into RAM locations for a microprocessor read cycle in addition to being provided at a POH interface for external access. Capability is also provided in the L4M for performing the path trace message comparison for the J1 byte. B3 BIP-8 parity errors and the input FEBE count in the G1 byte are counted as bit or block errors. The status of the RDI bit is also checked, and an alarm indication provided. The FEBE count is also provided, along with an RDI indication (as a result of local alarms) to an Alarm Indication Port for path-protected ring operation. A bit stuffing AIS feature is also provided in addition to using an external AIS clock to generate line AIS as a result of receive alarms.

The Desynchronizer Block is based on a proprietary TranSwitch design. The Desynchronizer Block removes the effect on the output signal of systemic jitter due to signal mapping and pointer movements, and consists of two FIFOs. The FIFOs are monitored for overflow and underflow alarms, and reset automatically when an alarm is detected. A 15-bit pointer leak register is provided for a microprocessor-written value. The following six desynchronizer signals are provided: Positive and negative phase detector outputs (CTRL and CTRL), a stuff indicator (STUFF) that provides the status of the stuff (justification) on a per-subframe basis, positive and negative justification indicator bits (PJ and NJ), and a pointer leak counter equal to zero indication (PLEQ0). In

addition, the desynchronizer pointer offset counter (9 bits plus sign value) is provided in the memory map for a microprocessor read, if required.

The output of the Desynchronizer Block is connected to the L4M Output Block, Receive Frame Alignment Detector Block and Receive AIS Detector Block. The 140 Mbit/s receive line signal is monitored by the Receive Frame Alignment Detector Block for ITU-T G.751 frame alignment and the Distant Alarm Status. A Distant alarm is defined as a 1 in bit 13 of the G.751 frame format. This alarm can generate an interrupt indication when enabled. When frame alignment is established, framing errors are counted in a 16-bit performance counter.

The 140 Mbit/s line signal is also monitored for an Alarm Indication Signal (AIS). The AIS detection circuit can be enabled to work in conjunction with the frame alignment circuit. An AIS condition is reported as an alarm, and can generate an interrupt when enabled. The Receive Frame Alignment Detector and Receive AIS Detector Blocks are disabled when the bit stuffing approach for generating 140 Mbit/s AIS is enabled and when the L4M generates a receive line AIS. AIS using a bit stuffing approach is implemented in the Decode Block prior to the Desynchronizer Block.

A byte-wide or nibble-wide 139.264 Mbit/s signal (RXDn) is provided as an output from the Output Block. A nibble interface is selected by placing a high on the lead designated as NIB. Data is normally clocked out of the L4M on negative transitions of the clock signal RXCO. A control bit is provided which enables data to be clocked out of the L4M on positive transitions of the clock.

External access to the Path Overhead bytes is provided by the POH I/O Block. The nine receive POH bytes present in the serial data channel (RPOHD) are clocked out on negative transitions of the gapped clock (RPOHC). A framing pulse (RPOHF), one clock cycle wide, identifies the starting location of the POH bytes, with bit 1 in the J1 byte. In the transmit direction, a gapped clock (TPOHC), and framing pulse (TPOHF) are provided. Serial data containing the POH bytes is clocked into the L4M on positive transitions of the clock. The B3 byte is present in the serial bit stream, but it is ignored by the L4M, and is recalculated. The framing pulse is one clock cycle wide and identifies the starting location of the POH bytes, with bit 1 in the J1 byte.

An external AIS input is provided for generating a received 140 Mbit/s AIS and an RDI indication, if the POH bytes are processed externally.

The Overhead Communications Channel I/O block provides an asynchronous interface for the 90 "O"-bits found in the SDH/SONET format. Serial data (ROCHD) which contains the "O"-bits, is clocked out of the L4M on negative transitions of the gapped clock (ROCHC). The received "O"-bits are not synchronized with the starting location of the frame. In the transmit direction, the "O"-bits (TOCHD) are clocked into the L4M by the gapped output clock (TOCHC).

The Alarm Indication Port data output signal (RAIPD), consisting of the FEBE count and RDI indication, is clocked out of the L4M on negative transitions of the receive POH clock (RPOHC). The serial data consists of nine bytes each frame. The first four bits correspond to the FEBE count, which has been derived from the B3 BIP-8 parity check. The next bit, bit 5, corresponds to the RDI indication. Bits 6 and 7 are set to 0, while bit 8 is set to a 1. The received POH framing pulse (RPOHF) identifies the starting location of bit 1 in the first byte. In the transmit direction, the received serial data, framing pulse, and clock from the mate L4M become the data input (TAIPD), framing pulse input (TAIPF), and clock input (TAIPC). When the ring mode is selected, the mate L4M FEBE count and RDI indication are transmitted in the G1 byte.

An upstream AIS indication may be inputted into the L4M using the E1 byte in the Transport (Section) Overhead bytes, or the external ISTAT, PAIS, and STAI pins. The upstream AIS indication can generate a 140 Mbit/s AIS, and a transmit RDI indication.

The L4M supports three types of microprocessor interfaces: Intel microprocessor with separate address and data buses, Motorola microprocessor with separate address and data buses, and a Motorola microprocessor with a multiplexed address/data bus interface.

The Boundary Scan block provides a mechanism for external access to the input and output pins of the device, so that they may be observed and tested. The structure and operation of this block are described in the Operation section.

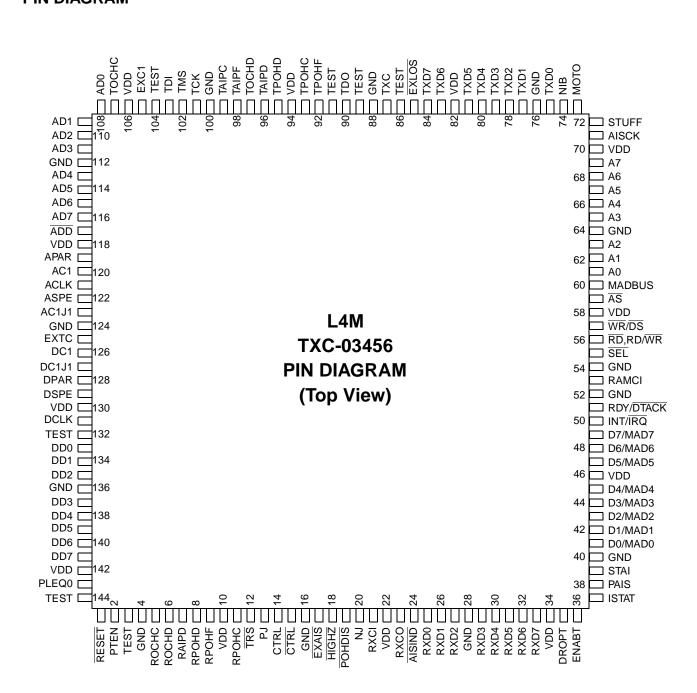

Figure 2. L4M TXC-03456 Pin Diagram

- 7 -

PIN DIAGRAM

SWITCH

I RAI

# **PIN DESCRIPTIONS**

#### POWER SUPPLY AND GROUND

| Symbol | Pin No.                                                  | I/O/P* | Туре | Name/Function                            |

|--------|----------------------------------------------------------|--------|------|------------------------------------------|

| VDD    | 10, 22, 34, 46, 58, 70, 82,<br>94, 106, 118, 130, 142    | Р      |      | <b>VDD:</b> +5 volt supply voltage, ± 5% |

| GND    | 4, 16, 28, 40, 52, 54, 64,<br>76, 88, 100, 112, 124, 136 | Ρ      |      | Ground: 0 volt reference.                |

\*Note: I = Input; O = Output; P = Power

#### 140 MBIT/S LINE INTERFACE

| Symbol          | Pin No.                 | I/O/P | Type*  | Name/Function                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------|-------------------------|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXC             | 87                      | I     | TTL    | <b>Transmit 140 Mbit/s Line Clock:</b> The clock rate is 34.816 MHz (nibble rate), or 17.408 MHz (byte rate). Byte or nibble-wide line data is clocked into the L4M on positive transitions of this clock when control bit TINVC is a 0. Data is clocked in on negative transitions of this clock when control bit TINVC is a 1.                                                                          |

| TXDn<br>(n=7-0) | 84, 83,<br>81-77,<br>75 | I     | TTL    | <b>Transmit 140 Mbit/s Line Data:</b> TXD7 (pin 84) is defined as the MSB for the byte interface, and is the first bit transmitted. For the nibble interface, TXD3 (pin 79) is defined as the MSB. TXD0 (pin 75) is the LSB for both the byte and nibble interfaces.                                                                                                                                      |

| EXLOS           | 85                      | Ι     | TTLp   | <b>External 140 Mbit/s Loss of Signal:</b> An optional low input signal to report an external transmit 140 Mbit/s line loss of signal. If this lead is not used it must be connected to VDD.                                                                                                                                                                                                              |

| RXDn<br>(n=7-0) | 33-29<br>27-25          | 0     | TTL4mA | <b>Receive 140 Mbit/s Line Data:</b> RXD7 (pin 33) is defined as the MSB for the byte interface, and is the first bit received. For the nibble interface, RXD3 (pin 29) is defined as the MSB. RXD0 (pin 25) is the LSB for both the byte and nibble interfaces.                                                                                                                                          |

| RXCO            | 23                      | 0     | TTL4mA | <b>Receive 140 Mbit/s Line Output Clock:</b> The clock rate is 34.816 MHz (nibble rate), or 17.408 MHz (byte rate). Byte or nibble-wide line data is clocked out of the L4M on negative transitions of this clock when control bit RINVC is a 0. Data is clocked out on positive transitions of this clock when control bit RINVC is a 1. This clock is derived from the receive line input clock (RXCI). |

| RXCI            | 21                      | I     | TTL    | <b>Receive 140 Mbit/s Line Input Clock:</b> Byte (17.408 MHz) or nibble (34.816 MHz) clock used by the internal desynchronizer for sourcing data. This clock is used to derive the receive line output clock (RXCO).                                                                                                                                                                                      |

| NIB             | 74                      | I     | TTL    | <b>Nibble/Byte Data Selection:</b> Common control lead for both the transmit and receive 140 Mbit/s interfaces. A high selects the interfaces as nibble, while a low selects the interfaces as byte.                                                                                                                                                                                                      |

\*Note: See Input, Output and I/O Parameters section for Type definitions.

# TRANSWITCH

### SDH/SONET DROP BUS INTERFACE

| Symbol         | Pin No.            | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------|--------------------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DCLK           | 131                | I     | TTL  | <b>Drop Bus Clock:</b> Byte-wide data (DD7-DD0), parity (DPAR), payload indicator (DSPE), and the C1 and J1 pulses (DC1J1) are clocked into the L4M on negative transitions of this clock, which has a rate of 19.44 MHz. The clock signal is used for receive timing, and is monitored for loss of clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DPAR           | 128                | I     | ΤΤL  | <b>Drop Bus Parity Bit:</b> This input represents an odd parity cal-<br>culation for each data byte, the DSPE signal, and the DC1J1<br>signal. When the internal pointer tracking feature is enabled,<br>parity is calculated for data and the C1 pulse only. When a 1 is<br>written to control bit PARDO, parity is calculated for the data<br>byte only.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DC1J1          | 127                | Ι     | TTL  | <b>Drop Bus C1J1 Indicator:</b> The C1 pulse is an active high, one clock cycle wide timing pulse, that indicates the starting location of the first C1 byte time slot in the STM-1 or STS-3c frame when DSPE is low. When the pointer tracking feature is disabled, a J1 pulse, also one clock cycle wide, must be present to identify the starting location of the J1 byte in the AU-4 VC-4, or in the STS-3c SPE signal when DSPE is high. If the J1 pulse is not present, the pointer tracking feature must be enabled. The C1 pulse must be provided on this signal lead, or on the DC1 signal lead. Up to a frame in offset delay for the C1 byte can be compensated for when the pointer tracking mode is enabled. The receive offset delay is controlled by bit RC1DC in the memory map. |

| DSPE           | 129                | I     | TTL  | <b>Drop Bus SPE Indicator:</b> A signal that is active high during the AU-4/STS-3c SPE time when the pointer tracking feature is disabled. This signal is not required when the pointer tracking feature is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DDn<br>(n=7-0) | 141-137<br>135-133 | I     | TTL  | <b>Drop Bus Byte:</b> Byte-wide data that corresponds to the AU-4/STS-3c signal from the drop bus. The first bit dropped corresponds to DD7 (pin 141).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DC1            | 126                | Ι     | TTL  | <b>Drop Bus C1 Pulse:</b> An external positive C1 pulse that may be provided on this pin instead of in the DC1J1 signal. This signal is or-gated internally with the DC1J1 signal to form a composite C1J1. When this signal lead is not used, it must be grounded.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

## SDH/SONET ADD BUS INTERFACE

| Symbol         | Pin No.            | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------|--------------------|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACLK           | 121                | I/O   | TTL4mA | Add Bus Clock: The add clock is used for build timing, trans-<br>mit FIFO, and for sourcing the add bus byte-wide data (AD7-<br>AD0) and parity (APAR), when add bus timing is selected.<br>When external timing or drop timing mode is selected, this sig-<br>nal becomes an output. The add bus clock rate is 19.44 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| AC1J1          | 123                | I/O   | TTL4mA | Add Bus C1J1 Indicator: The C1 pulse is an active high, one clock cycle wide, timing pulse that identifies the starting location of the first C1 byte time slot in the STM-1 or STS-3c frame. The C1 pulse may be provided on a separate lead (AC1) when the add bus timing mode is selected. A J1 pulse, also one clock cycle wide, identifies the starting location of the J1 byte in the AU-4 VC-4 or STS-3c SPE signal when the POH bytes are used. When the POH feature is disabled, the J1 pulse is not required. When external timing or drop timing is enabled this signal becomes an output. The C1J1 pulses correspond to the C1 and J1 bytes present on AD(7-0). When a 1 is written to control bit AC1EN, the C1 pulse may be provided on a separate lead (AC1) instead of in the AC1J1 signal. |

| APAR           | 119                | 0     | TTL4mA | Add Bus Parity Bit: This output bit represents the odd parity calculation for each data byte (and SPE and C1J1, including AC1, when they are outputs). When a 1 is written to control bit PARDO, parity is calculated for the data byte only. APAR is not calculated over the unused TOH Byte times.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ASPE           | 122                | I/O   | TTL4mA | Add Bus SPE Indicator: An input signal in add timing mode that is high during the AU-4/STS-3c SPE time. When the external timing or drop timing modes are enabled, this signal becomes an output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ADn<br>(n=7-0) | 116-113<br>111-108 | 0     | TTL4mA | Add Data Byte: Byte-wide data that corresponds to the AU-4/STS-3c signal to be placed on the add bus. The first bit transmitted corresponds to AD7 (pin 116). Data is three-stated during periods of no activity (e.g., during unused TOH times).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ADD            | 117                | 0     | TTL4mA | Add Indicator: An active low signal that identifies the time slots corresponding to the output data (AD7-AD0).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AC1            | 120                | I/O   | TTL4mA | Add Bus C1 Pulse: This lead provides the C1 pulse as an output when the drop bus timing or external timing modes are enabled, and when the AC1EN control signal is a 1. The AC1J1 signal will contain the C1 pulse. When the add bus timing mode is enabled, this lead may be used as the C1 input, independent of the AC1EN control bit. This signal is or-gated internally with the AC1J1 signal in the add bus timing mode to form a composite C1J1signal. If this signal lead is not used in the add bus timing mode, it must be grounded.                                                                                                                                                                                                                                                              |

### RECEIVE AND TRANSMIT PATH OVERHEAD BYTE INTERFACE

| Symbol | Pin No. | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|---------|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RPOHF  | 9       | 0     | TTL4mA | <b>Receive Path Overhead Framing:</b> A positive, one clock cycle wide, framing pulse that is synchronous with bit 1 in the J1 byte in the POH interface data.                                                                                                                                                                                                                                                                                                                                                                                                 |

| RPOHD  | 8       | 0     | TTL4mA | <b>Receive Path Overhead Data:</b> The serial output for the nine<br>Path Overhead bytes: J1, B3, C2, G1, F2, H4, Z3, Z4, and Z5<br>bytes. The bytes are clocked out, starting with bit 1 in J1, on<br>negative transitions of the clock signal (RPOHC) when the<br>POH feature is enabled.                                                                                                                                                                                                                                                                    |

| RPOHC  | 11      | 0     | TTL4mA | <b>Receive Path Overhead Clock:</b> The nine POH bytes and RAIPD data are clocked out on negative transitions of this clock signal (RPOHC).                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TPOHF  | 92      | 0     | TTL4mA | <b>Transmit Path Overhead Framing:</b> A positive, one clock cycle wide, framing pulse that is synchronous with bit 1 in the J1 byte in the POH interface data.                                                                                                                                                                                                                                                                                                                                                                                                |

| TPOHD  | 95      | Ι     | TTL    | <b>Transmit Path Overhead Data:</b> A serial input for the Path<br>Overhead bytes: J1, C2, G1, F2, H4, Z3, Z4, and Z5 bytes.<br>The B3 byte time slot must be provided, but the contents are<br>ignored by the L4M. The bytes are clocked in, starting with bit<br>1 in J1, on positive transitions of the clock signal (TPOHC). 8<br>bits are clocked in during the B3 Byte time, but they are<br>ignored by the L4M device. The L4M recalculates the B3 byte<br>parity value. The POH bytes are ignored when a low is placed<br>on the POHDIS lead (pin 19). |

| ТРОНС  | 93      | 0     | TTL    | <b>Transmit Path Overhead Clock:</b> The transmit clock used for clocking in the Path Overhead bytes. Data is clocked in on positive transitions of the clock.                                                                                                                                                                                                                                                                                                                                                                                                 |

#### RECEIVE AND TRANSMIT OVERHEAD COMM CHANNEL INTERFACE

| Symbol | Pin No. | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                  |

|--------|---------|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ТОСНС  | 107     | 0     | TTL4mA | <b>Transmit Overhead Comm Channel Clock:</b> An output clock provided for sourcing the transmit overhead communications channel data ("O"-bits). This clock has an effective data transfer rate of 720 kHz (8 kHz per bit, times 90 bits).                     |

| TOCHD  | 97      | I     | TTL    | <b>Transmit Overhead Comm Channel Data:</b> Data is clocked in<br>on positive transitions of the clock signal (TOCHC). The data is<br>unaligned in relationship to the overhead communications<br>channel data bit placement in the SDH/SONET format.          |

| ROCHC  | 5       | 0     | TTL4mA | <b>Receive Overhead Comm Channel Clock:</b> A clock provided for outputting the transmit overhead communications channel data. This clock has an effective data transfer rate of 720 kHz (8 kHz per bit, times 90 bits).                                       |

| ROCHD  | 6       | 0     | TTL4mA | <b>Receive Overhead Comm Channel Data:</b> Data is clocked<br>out on negative transitions of the clock signal (ROCHC). The<br>data output for the overhead communications channel from the<br>format is unaligned in relationship with the SDH/SONET<br>frame. |

### EXTERNAL TIMING FOR ADD BUS

| Symbol | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                             |

|--------|---------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTC   | 125     | I     | TTL  | <b>External Clock Input:</b> Enabled by placing a high on the ENABT lead (pin 36). Used for deriving output timing for the add bus. A clock rate of 19.44 MHz is required for AU-4/STS-3c operation. This clock input is monitored for loss of clock.                                                                     |

| EXC1   | 105     | Ι     | TTL  | <b>External C1 Input:</b> Enabled by placing a high on the ENABT lead (pin 36). An optional C1 input signal that can be used for frame alignment. In addition, an option is provided for the pointer tracking feature which can compensate up to a frame in offset delay. If this pin is not used, it should be grounded. |

### RECEIVE DESYNCHRONIZER

| Symbol | Pin No. | I/O/P | Туре    | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------|---------|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CTRL   | 14      | 0     | CMOS4mA | Phase Detector Output Positive: Normally connected to low pass filter as part of the desynchronizer phase-locked loop. See Figure 25.                                                                                                                                                                                                                                                                                                                     |

| CTRL   | 15      | 0     | CMOS4mA | <b>Phase Detector Output Negative:</b> Normally connected to low pass filter as part of the desynchronizer phase-locked loop. See Figure 25.                                                                                                                                                                                                                                                                                                              |

| STUFF  | 72      | 0     | TTL4mA  | <b>Stuff (Justification) Opportunity Indication:</b> This lead provides a status of the stuff (justification) S-bit in the Z byte for each row in the nine subframes in the 140 Mbit/s SDH/SONET format. The pin is high for one SONET/SDH row when there is a stuff indication, and low when this bit is information. The output on this pin is updated each row based on majority voting of the five c-bits.                                            |

| PJ     | 13      | 0     | TTL4mA  | <b>Positive Justification Indication:</b> This lead provides a positive pulse when a positive pointer movement is detected. The pulse width is one DCLK cycle wide.                                                                                                                                                                                                                                                                                       |

| NJ     | 20      | 0     | TTL4mA  | <b>Negative Justification Indication:</b> This lead provides a posi-<br>tive pulse when a negative pointer movement is detected. The<br>pulse width is one DCLK cycle wide.                                                                                                                                                                                                                                                                               |

| PLEQ0  | 143     | 0     | TTL4mA  | <b>Pointer Leak Counter Equal to Zero Indication:</b> This lead<br>provides a positive indication when the internal pointer leak<br>counter is equal to zero. This signal is reset to zero when the<br>internal counter is preset. A positive pulse, one DCLK cycle<br>wide, is then output for each time a bit is leaked out of the<br>L4M's Desynchronizer. The last bit leaked out is represented<br>by the last rising edge of the PLEQ0 signal lead. |

# RECEIVE AND TRANSMIT ALARM INDICATION PORT

| Symbol | Pin No. | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------|---------|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAIPD  | 7       | 0     | TTL4mA | <b>Receive Alarm Indication Port Data:</b> A serial output that provides the four-bit FEBE count (received B3 BIP-8 parity errors, bits 1-4), and Path RDI alarm indication (bit 5) for ring operation. Bits 6, 7, and 8 are set to 0, 0, 1, respectively. This lead is normally connected to the TAIPD lead at the mate 140 Mbit/s Mapper for ring operation. The RPOHC signal is used to clock out this signal. The RPOHF signal is used to provide the frame reference signal. The data output is disabled (forced to 0) when an active low is placed on the POHDIS lead. |

| TAIPD  | 96      | I     | TTL    | <b>Transmit Alarm Indication Port Data:</b> This serial input lead is<br>normally connected to the RAIPD lead at the mate L4M for ring<br>operation. Provides an input for the four-bit FEBE count<br>(received B3 BIP-8 parity errors), and Path RDI alarm indication<br>from the mate L4M. The data input is disabled when an active<br>low is placed on the POHDIS lead.                                                                                                                                                                                                  |

| TAIPC  | 99      | I     | TTL    | <b>Transmit Alarm Indication Port Clock:</b> This clock input is nor-<br>mally connected to the RPOHC clock lead at the mate L4M for<br>ring operation. Transmit alarm data (TAIPD) is clocked into the<br>L4M on positive transitions of the clock. This clock input is mon-<br>itored for loss of clock.                                                                                                                                                                                                                                                                   |

| TAIPF  | 98      | I     | TTL    | <b>Transmit Alarm Indication Port Framing Pulse:</b> Normally connected to RPOHF lead at the mate L4M for ring operation. Used to indicate the start of the external alarm indications for ring operation.                                                                                                                                                                                                                                                                                                                                                                   |

#### BOUNDARY SCAN

| Symbol | Pin No. | I/O/P        | Туре   | Name/Function                                                                                                                                                                            |

|--------|---------|--------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ТСК    | 101     | Ι            | TTL    | <b>Test Boundary Scan Clock:</b> The input clock for boundary scan testing. The TDI and TMS states are clocked in on positive transitions.                                               |

| TDI    | 103     | I            | TTLp   | <b>Test Boundary Data Input:</b> Serial data input for boundary scan test messages.                                                                                                      |

| TDO    | 90      | O<br>3-state | TTL4mA | <b>Test Boundary Data Output:</b> Serial data output whose information is clocked out on negative transitions of TCK. This pin requires a 4.7 k $\Omega$ pull-up resistor if it is used. |

| TMS    | 102     | I            | TTLp   | <b>Test Boundary Mode Select:</b> The signal present on this lead is used to control test operations.                                                                                    |

| TRS    | 12      | Ι            | TTLp   | <b>Test Boundary Scan Reset:</b> An active low asynchronous reset signal. This lead should be held low if the boundary scan is not being used.                                           |

# TRANSWITCH

### OTHER PINS

| Symbol | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|--------|---------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ENABT  | 36      | I     | TTL  | <b>Enable Add Bus Timing:</b> Works in conjunction with the DROPT lead. The following table is the definition of the timing modes:                                                                                                                                                                                                                                                                |  |  |  |  |

|        |         |       |      | ENABTDROPTAction1XExternal timing. Add bus timing derived<br>from the external clock (EXTC) and the<br>external framing pulse (EXC1). The<br>ASPE, AC1J1, ACLK and AC1 signal<br>leads become output leads.                                                                                                                                                                                       |  |  |  |  |

|        |         |       |      | 0 0 Add bus timing. Data derived from the<br>add bus clock, ASPE, and AC1J1 input<br>signals. Note: ASPE, AC1J1, AC1 and<br>ACLK are inputs.                                                                                                                                                                                                                                                      |  |  |  |  |

|        |         |       |      | 0 1 Drop bus timing. Data, ASPE, AC1J1,<br>and ACLK output signals are derived<br>from the drop bus clock (DCLK) and C1<br>pulse in the drop bus DC1J1 signal.                                                                                                                                                                                                                                    |  |  |  |  |

| DROPT  | 35      | I     | TTL  | <b>Drop Timing Mode Enabled:</b> Works in conjunction with the ENABT lead. See table above.                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| ISTAT  | 37      | I     | TTL  | <b>External STS Alarm Indication:</b> The purpose of this lead is to provide an upstream AIS indication for the L4M. This pin is enabled by writing a 1 to the EAPE control bit. A high on this lead generates AIS, and path RDI, when enabled.                                                                                                                                                   |  |  |  |  |

| PAIS   | 38      | I     | TTL  | <b>External Path AIS Indication:</b> The purpose of this lead is to provide an upstream AIS indication for the L4M. This pin is enabled by writing a 1 to the EAPE control bit. A high generates line AIS, and path RDI, when enabled.                                                                                                                                                            |  |  |  |  |

| STAI   | 39      | I     | TTL  | <b>STS Network Alarm Indication:</b> This pin is enabled by writing a 1 to the XRDIEN control bit. A high generates a path RDI, when enabled.                                                                                                                                                                                                                                                     |  |  |  |  |

| AISCK  | 71      | I     | CMOS | <b>AIS Clock Input:</b> Enabled when control bit BSAISE is a 0. This clock is used to generate transmit and receive 140 Mbit/s AIS on defined alarms. The clock frequency must be 34.816 MHz +/- 15 ppm for a nibble interface, and 17.408 MHz +/- 15 ppm for a byte interface. If AIS bit stuffing is used to generate AIS (control bit BSAISE is written with a 0), this clock is not required. |  |  |  |  |

| EXAIS  | 17      | I     | TTLp | <b>External AIS Alarm Input:</b> A low causes a receive 140 Mbit/s AIS when enabled, and a path RDI to be generated. May be used when processing received POH bytes via external circuitry (e.g., C2 byte).                                                                                                                                                                                       |  |  |  |  |

| Symbol | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|--------|---------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| POHDIS | 19      | Ι     | TTLp | <b>Path Overhead Byte Processing Disabled:</b> A low disables the insertion of the POH bytes (they are tri-stated) into the SPE from either the memory map RAM or the POH interface. It also disables the processing of the POH bytes in the receive direction and their subsequent actions.                                                                                                                                                                  |  |  |  |

| AISIND | 24      | 0     | TTL  | Receive AIS Indication Output: A low indicates that 140<br>Mbit/s AIS is being generated in the receive path. This pin is<br>disabled when the BSAISE control bit=1 and the RLAISD<br>alarm=1. However, when the L4M generates a receive line AIS<br>this pin will go low even if BSAISE=1 and RLAISD=1.                                                                                                                                                      |  |  |  |

| HIGHZ  | 18      | I     | TTLp | <b>High Impedance Enable:</b> A low causes all output and bi-directional pins to three-state for test purposes.                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| PTEN   | 2       | Ι     | TTL  | Pointer Tracking Enable: A high enables the internal pointer tracking feature. The pointer tracking feature determines the starting location of J1 in the dropped signal. The C1 pulse must be provided as the DC1, or DC1J1 signal. The J1 pulse must not be provided. The DSPE lead is ignored when the pointer tracking machine feature is enabled. A low requires the DC1J and DSPE signals to be provided as inputs.                                     |  |  |  |

| RESET  | 1       | Ι     | TTLp | Hardware Reset: A low clears all performance counters, and<br>presets the internal FIFOs and counters. All control bits (10H-<br>1FH) are preset to 0 except for bit 3 of register 13H and bit 0 of<br>registers 1AH and 1BH. These 3 bits are preset to 1. This pulse<br>must be present for a minimum of 200 nanoseconds. Note: The<br>L4M requires approximately 1 microsecond upon power-up for<br>stabilization before a low can be applied to this pin. |  |  |  |

### MICROPROCESSOR INTERFACE

| Symbol             | Pin No.        | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                                             |

|--------------------|----------------|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A(7-0)             | 69-65<br>63-61 | I     | TTL    | Address Bus (Motorola/Intel Buses): These are address line inputs that are used for accessing a RAM location for a read/write cycle. A0 is the least significant bit. High is logic 1.                                                                                                                                                                    |

| AS                 | 59             | I     | TTL    | Address Select (Multiplex Bus): A low is used for address select when the multiplex bus mode is selected.                                                                                                                                                                                                                                                 |

| D(7-0)<br>MAD(7-0) | 49-47<br>45-41 | I/O   | TTL8mA | <b>Data Bus:</b> Bi-directional data lines used for transferring data.<br>D0 is the least significant bit. Can also be used as multiplexed<br>address and data bus with Motorola interface. High is logic 1.                                                                                                                                              |

| SEL                | 55             | I     | TTLp   | <b>Select:</b> A low will enable data transfers between the processor and the L4M RAM during a read/write cycle.                                                                                                                                                                                                                                          |

| RD<br>RD/WR        | 56             | I     | TTL    | Read (Intel mode) or Read/Write (Motorola mode):<br>Intel Mode - An active low signal generated by the microproces-<br>sor for reading the L4M RAM locations.<br>Motorola and multiplex Mode - An active high signal generated<br>by the microprocessor for reading the L4M RAM locations. An<br>active low signal is used to write to L4M RAM locations. |

| Symbol        | Pin No. | I/O/P | Туре              | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|---------------|---------|-------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| WR<br>DS      | 57      | Ι     | TTL               | Write (Intel mode):<br>Intel Mode - An active low signal generated by the microproces<br>sor for writing to the Mapper RAM locations.<br>Motorola Mode - Not used. For the multiplex mode, this lead is<br>used for the Data Select control.                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| RDY/<br>DTACK | 51      | 0     | TTL8mA<br>3-state | Ready (Intel mode) or Data Transfer Acknowledge<br>(Motorola modes): This lead is three-stated.<br>Intel Mode - A high is an acknowledgment from the addressed<br>RAM location that the transfer can be completed. A low indi-<br>cates that the L4M cannot complete the transfer cycle, and<br>microprocessor wait states must be generated.<br>Motorola and multiplex Mode - During a read bus cycle, a low<br>signal indicates that the information on the data bus is valid.<br>During a write bus cycle, a low signal acknowledges the accep-<br>tance of data. |  |  |  |  |

| INT/<br>IRQ   | 50      | 0     | TTL4mA            | Interrupt:<br>Intel Mode - A high on this output pin signals an interrupt<br>request to the microprocessor.<br>Motorola Mode - A low on this output pin signals an interrupt<br>request to the microprocessor.                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| мото          | 73      | I     | TTL               | Motorola/Intel Microprocessor Select:       This lead works in conjunction with the MADBUS lead. A high selects a Motorola microprocessor compatible bus interface. A low selects the Intel microprocessor compatible bus interface. The following table summarizes the microprocessor selection.         MOTO       MADBUS       Action         0       X       Intel Microprocessor Interface,                                                                                                                                                                     |  |  |  |  |

|               |         |       |                   | <ul> <li>separate address/data buses.</li> <li>Motorola Microprocessor Interface, separate address/data buses.</li> <li>1</li> <li>Motorola Microprocessor Interface, multiplexed address/data buses.</li> </ul>                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| MADBUS        | 60      | I     | TTL               | Multiplexed Address/Data Bus: When the MOTO lead is high,<br>a high on this lead selects a Multiplexed Address/Data Bus<br>interface, while a low selects separate Address/Data buses.<br>This lead is disabled when MOTO is low.                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| RAMCI         | 53      | Ι     | CMOS              | <b>RAM Clock Input:</b> Asynchronous clock input used for the internal L4M RAM operation. This clock must be connected to the microprocessor clock that has an operating rate of between 12 and 25 MHz with a duty cycle of $50 \pm 10\%$ . This clock is also used as an internal time base for the loss of signal detectors.                                                                                                                                                                                                                                       |  |  |  |  |

### MANUFACTURE TEST PINS

| Symbol | Pin No. | I/O/P | Туре   | Name/Function                                                                                    |

|--------|---------|-------|--------|--------------------------------------------------------------------------------------------------|

| TEST   | 144     | I     | TTLp   | <b>Test Pin for Manufacture Testing:</b> For normal operation this pin must be grounded.         |

| TEST   | 89      | I     | TTLp   | <b>Test Pin for Manufacture Testing.</b> For normal operation this pin must be grounded.         |

| TEST   | 91      | 0     | TTL4mA | <b>Test Pin for Manufacture Testing:</b> For normal operation this pin must be left unconnected. |

| TEST   | 104     | I     | TTLp   | <b>Test Pin for Manufacture Testing:</b> For normal operation this pin must be grounded.         |

| TEST   | 86      | I     | TTLp   | Test Pin for Manufacture Testing: For normal operation this pin must be grounded.                |

| TEST   | 132     | I     | TTLp   | <b>Test Pin for Manufacture Testing:</b> For normal operation this pin must be grounded.         |

| TEST   | 3       | I     | TTLp   | <b>Test Pin for Manufacture Testing:</b> For normal operation this pin must be grounded.         |

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter                     | Symbol          | Min* | Max*                  | Unit |

|-------------------------------|-----------------|------|-----------------------|------|

| Supply voltage                | V <sub>DD</sub> | -0.3 | +7.0                  | V    |

| DC input voltage              | V <sub>IN</sub> | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| Ambient operating temperature | T <sub>A</sub>  | -40  | 85                    | ٥C   |

| Storage temperature range     | Τ <sub>S</sub>  | -55  | 150                   | °C   |

\*Note: Operating conditions exceeding those listed in Absolute Maximum Ratings may cause permanent failure. Exposure to absolute maximum ratings for extended periods may impair device reliability.

# THERMAL CHARACTERISTICS

| Parameter                                   | Min | Тур | Max  | Unit | Test Conditions |

|---------------------------------------------|-----|-----|------|------|-----------------|

| Thermal resistance -<br>junction to ambient |     |     | 23.0 | °C/W |                 |

# POWER REQUIREMENTS

| Parameter       | Min  | Тур  | Max  | Unit | Test Conditions  |

|-----------------|------|------|------|------|------------------|

| V <sub>DD</sub> | 4.75 | 5.00 | 5.25 | V    |                  |

| I <sub>DD</sub> |      | 251  | 320  | mA   |                  |

| P <sub>DD</sub> |      | 1.27 | 1.68 | W    | Inputs switching |

# INPUT, OUTPUT AND I/O PARAMETERS

#### Input Parameters For CMOS

| Parameter             | Min  | Тур | Мах  | Unit | Test Conditions               |

|-----------------------|------|-----|------|------|-------------------------------|

| V <sub>IH</sub>       | 3.15 |     |      | V    | 4.75 ≤ V <sub>DD</sub> ≤ 5.25 |

| V <sub>IL</sub>       |      |     | 1.65 | V    | 4.75 ≤ V <sub>DD</sub> ≤ 5.25 |

| Input leakage current |      |     | 10   | μA   | V <sub>DD</sub> = 5.25        |

| Input capacitance     |      | 3.5 |      | pF   |                               |

#### Input Parameters For TTL

| Parameter             | Min | Тур | Max | Unit | Test Conditions                             |

|-----------------------|-----|-----|-----|------|---------------------------------------------|

| V <sub>IH</sub>       | 2.0 |     |     | V    | 4.75 <u>≤</u> V <sub>DD</sub> <u>≤</u> 5.25 |

| V <sub>IL</sub>       |     |     | 0.8 | V    | 4.75 <u>≤</u> V <sub>DD</sub> <u>≤</u> 5.25 |

| Input leakage current |     |     | 10  | μA   | V <sub>DD</sub> = 5.25                      |

| Input capacitance     |     | 3.5 |     | pF   |                                             |

#### Input Parameters For TTLp

| Parameter             | Min | Тур | Max | Unit | Test Conditions                         |

|-----------------------|-----|-----|-----|------|-----------------------------------------|

| V <sub>IH</sub>       | 2.0 |     |     | V    | 4.75 ≤ V <sub>DD</sub> ≤ 5.25           |

| V <sub>IL</sub>       |     |     | 0.8 | V    | 4.75 ≤ V <sub>DD</sub> ≤ 5.25           |

| Input leakage current |     | 0.5 | 1.4 | mA   | V <sub>DD</sub> = 5.25; Input = 0 volts |

| Input capacitance     |     | 3.5 |     | pF   |                                         |

Note: Input has a 9k (nominal) internal pull-up resistor.

#### **Output Parameters For CMOS4mA**

| Parameter         | Min                   | Тур | Мах  | Unit | Test Conditions                                |

|-------------------|-----------------------|-----|------|------|------------------------------------------------|

| V <sub>OH</sub>   | V <sub>DD</sub> - 0.5 |     |      | V    | V <sub>DD</sub> = 4.75; I <sub>OH</sub> = -4.0 |

| V <sub>OL</sub>   |                       |     | 0.4  | V    | V <sub>DD</sub> = 4.75; I <sub>OL</sub> = 4.0  |

| I <sub>OL</sub>   |                       |     | 4.0  | mA   |                                                |