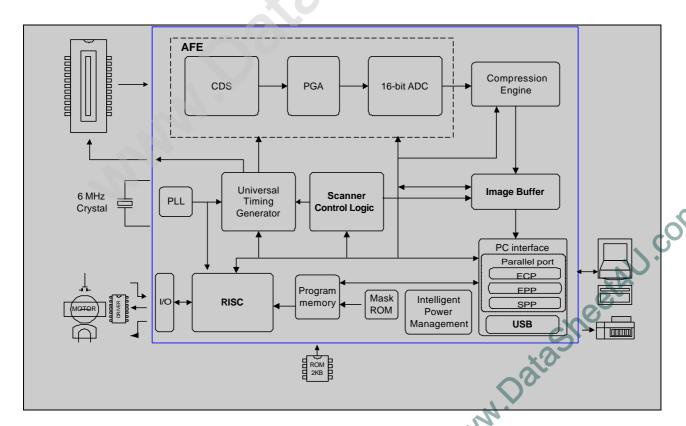

## I. General Descriptions-

The GT-6816 is an enhanced version of GT-6801, which provides highly integrated **System-On-Chip** (**SOC**) solution for high-performance color scanner. The GT-6816 is enhanced not only in the AFE (Analog Front End) from 12-bit to 16-bit but also built-in an intelligent power management circuit to meet both operating and suspend mode for USB bus-powered Scanner. The GT-6816 is also pin to pin backward compatible with the GT-6801, providing system designer easy way to upgrade the current applications without changing the hardware design.

#### II. Features-

- ♦ Single-chip integration for high-performance color scanner application

- ♦ On-chip Analog Front End: CDS/AGC and 16-bit ADC Maximum 6MHz

- On-chip universal TG supports various types of CCD/CIS sensors

- ♦ Embedded high-performance RISC controller

- ♦ On-chip USB transceiver

- ♦ Built-in 16KB image line buffers

- ♦ PC interface supports : USB/EPP/ECP/BPP

- ♦ No external memory component required for typical application

- ♦ Firmware programmable frame size

- Intelligent power management meets both operating and suspend mode for USB bus power

- ♦ On-chip PLL circuits

- ♦ Operating clock :48 MHz with external crystal: 6 MHz

- ♦ Operating voltage: Core: 3.3V, I/O: 5V

- ♦ Operating current: Core 80mA, AFE 50mA

- ♦ Suspend current: 50 A

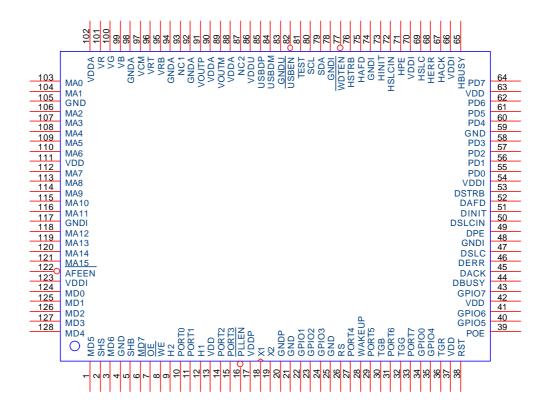

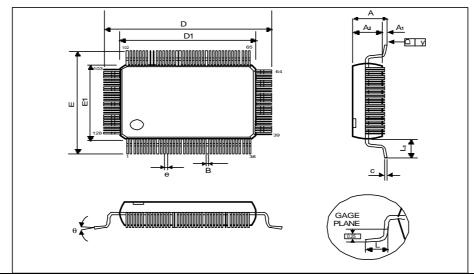

- Package: 128-QFP & 44-QFP

#### III. Benefits-

- Provides a total solution, fast time-to-market

- Provides a total solution, fast time-to-market

USB bus power without additional power line

Supports a wide range of applications

Customer differentiation via firmware

Provides firmware update path via USB channel

Easy to meet EMI standard

Minimum external components

Supports a full set of development kit

Single chip solution, stock management becomes easier

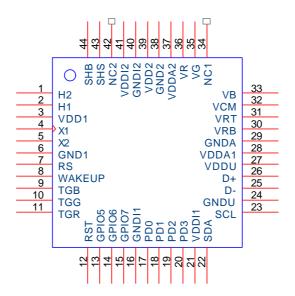

#### IV. Pin Configuration-

Type(A)-44-pin QFP

# V. Pin Descriptions-

| 128 No. | 44 No. | Name     | Reset State | Туре | Driven | Description                                    |

|---------|--------|----------|-------------|------|--------|------------------------------------------------|

| 1       |        | MD4      | Tri-state   | I/O  | 4mA    | External memory data bus bit 4                 |

| 2       |        | MD5      | Tri-state   | I/O  | 4mA    | External memory data bus bit 5                 |

| 3       | 43     | SHS      | Tri-state   | О    | 8mA    | CCD sample hold signal control signal          |

| 4       |        | MD6      | Tri-state   | I/O  | 4mA    | External memory data bus bit 6                 |

| 5       |        | GNDC1    |             | P    |        | Core ground                                    |

| 6       | 44     | SHB      | Tri-state   | О    | 8mA    | CCD sample hold reset control signal           |

| 7       |        | MD7      | Tri-state   | I/O  | 4mA    | External memory data bus bit 7                 |

| 8       |        | MOE#     | High        | О    | 4mA    | External memory output enable                  |

| 9       |        | MWE#     | High        | О    | 4mA    | External memory write enable                   |

| 10      | 1      | H2/CLK   | Tri-state   | О    | 8mA    | CCD shift clock/CIS clock control signal       |

| 11      |        | PORT1 0  | Tri-state   | I/O  | 4mA    | uP port 1 bit 0                                |

| 12      |        | PORT1 1  | Tri-state   | I/O  | 4mA    | uP port 1 bit 1                                |

| 13      | 2      | H1/SP    | Tri-state   | О    | 8mA    | CCD shift clock/CIS SP control signal          |

| 14      |        | VDDC1    |             | P    |        | Core power                                     |

| 15      |        | PORT1 2  | Tri-state   | I/O  | 4mA    | uP port 1 bit 2                                |

| 16      |        | PORT1 3  | Tri-state   | I/O  | 4mA    | uP port 1 bit 3                                |

| 17      |        | PLL EN#  |             | I    |        | PLL enable control signal, with pull-down, not |

| 18      | 3      | VDDP     |             | P    |        | PLL power                                      |

| 19      | 4      | X1       |             | I    |        | Crystal input                                  |

| 20      | 5      | X2       |             | О    |        | Crystal output                                 |

| 21      | 6      | GNDP     |             | P    |        | PLL ground                                     |

| 22      |        | GNDC2    |             | P    |        | Core ground                                    |

| 23      |        | GPIO1    | Tri-state   | I/O  | 4mA    | GPIO bit 1                                     |

| 24      |        | GPIO2    | Tri-state   | I/O  | 4mA    | GPIO bit 2                                     |

| 25      |        | GPIO3    | Tri-state   | I/O  | 4mA    | GPIO bit 3                                     |

| 26      |        | GNDC3    |             | P    |        | Core ground                                    |

| 27      | 7      | RS       | Tri-state   | О    | 8mA    | CCD reset signal                               |

| 28      |        | PORT1 4  | Tri-state   | I/O  | 4mA    | uP port 1 bit 4                                |

| 29      | 8      | WAKEUP   |             | I    |        | USB device remoter wakeup                      |

| 30      |        | PORT1 5  | Tri-state   | I/O  | 4mA    | uP port 1 bit 5                                |

| 31      | 9      | TGB/LEDB | Tri-state   | О    | 8mA    | CCD TG/CIS LED B channel control signal        |

| 32      |        | PORT1 6  | Tri-state   | I/O  | 4mA    | uP port 1 bit 6                                |

| 33      | 10     | TGG/LEDG | Tri-state   | О    | 8mA    | CCD TG/CIS LED G channel control signal        |

| 34      |        | PORT71   | Tri-state   | I/O  | 4mA    | uP port 1 bit 7                                |

| 35      |        | GPIO0    | Tri-state   | I/O  | 4mA    | GPIO bit 0                                     |

| 36      |        | GPIO4    | Tri-state   | I/O  | 4mA    | GPIO bit 4                                     |

| 37      | 11     | TGR/LEDR | Tri-state   | О    | 8mA    | CCD TG/CIS LED R channel control signal        |

| 38      |        | VDDC2    |             | P    |        | Core power                                     |

| 39      | 12     | RESET    |             | I    |        | Power on reset, high active                    |

| 40      |        | GPIO5    | Tri-state   | I/O  | 4mA    | GPIO bit 5                                     |

| 41      | 13     | GPIO6    | Tri-state   | I/O  | 4mA    | GPIO bit 6                                     |

| 42      | 14     | VDDC3    |             | P    |        | Core power                                     |

| 43      |        | GPIO7    | Tri-state   | I/O  | 4mA    | GPIO bit 7                                     |

| 44      | 15     | DBUSY    |             | I    |        | Device parallel port (Busy) signal, with       |

| 45 DACK I Device parallel port 46 DERR I Device parallel port (F 47 DSLC I Device parallel port (F 48 GNDI1 P IO ground 49 16 GNDI2 P IO ground 50 DPE I Device parallel port (S 51 DSLCIN Low O 24mA Device parallel port (S 52 DINIT Low O 24mA Device parallel port (III) | Fault) (select (Pape | signa   | ıl    |        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------|-------|--------|

| 47 DSLC I Device parallel port ( 48 GNDI1 P IO ground 49 16 GNDI2 P IO ground 50 DPE I Device parallel port ( 51 DSLCIN Low O 24mA Device parallel port (S                                                                                                                   | (Select              |         |       | with   |

| 48 GNDI1 P IO ground 49 16 GNDI2 P IO ground 50 DPE I Device parallel port 51 DSLCIN Low O 24mA Device parallel port (S                                                                                                                                                      | (Pape                | et) si  | gnal. | with   |

| 49 16 GNDI2 P IO ground 50 DPE I Device parallel port 51 DSLCIN Low O 24mA Device parallel port (S                                                                                                                                                                           | Select               |         |       |        |

| 50DPEIDevice parallel port51DSLCINLowO24mADevice parallel port (S                                                                                                                                                                                                            | Select               |         |       |        |

| 51 DSLCIN Low O 24mA Device parallel port (S                                                                                                                                                                                                                                 | Select               |         |       |        |

|                                                                                                                                                                                                                                                                              |                      | er en   | d) s  | ignal, |

| 52 DINIT Low O 24mA Device parallel port (b                                                                                                                                                                                                                                  | nit) ci              | in) s   | igna  | 1      |

| 27   Division   Device Daraner Bott (II                                                                                                                                                                                                                                      | m v si               | gnal    |       |        |

| 53 DAFD Low O 24mA Device parallel port (A                                                                                                                                                                                                                                   | \uto f               | eed)    | sign  | al     |

| 54 DSTRB Low O 24mA Device parallel port (S                                                                                                                                                                                                                                  | Strobe               | e) sign | nal   |        |

| 55 VDDI1 P IO power                                                                                                                                                                                                                                                          |                      |         |       |        |

| 56 17 PD0 Tri-state I/O 24mA Parallel port data                                                                                                                                                                                                                              | bus                  | bit     | 0.    | with   |

| 57 18 PD1 Tri-state I/O 24mA Parallel port data                                                                                                                                                                                                                              | bus                  | bit     | 1.    | with   |

| 58 19 PD2 Tri-state I/O 24mA Parallel port data                                                                                                                                                                                                                              | bus                  | bit     | 2.    | with   |

| 59 20 PD3 Tri-state I/O 24mA Parallel port data                                                                                                                                                                                                                              | bus                  | bit     | 3,    | with   |

| 60 GNDC4 P Core ground                                                                                                                                                                                                                                                       |                      |         |       |        |

| 61 PD4 Tri-state I/O 24mA Parallel port data                                                                                                                                                                                                                                 | bus                  | bit     | 4.    | with   |

| 62 PD5 Tri-state I/O 24mA Parallel port data                                                                                                                                                                                                                                 | bus                  | bit     | 5.    | with   |

| 63 PD6 Tri-state I/O 24mA Parallel port data                                                                                                                                                                                                                                 | bus                  | bit     | 6.    | with   |

| 64 VDDC4 P Core power.                                                                                                                                                                                                                                                       |                      |         |       |        |

| 65 PD7 Tri-state I/O 24mA Parallel port data                                                                                                                                                                                                                                 | bus                  | bit     | 7.    | with   |

| 66 HBUSY Low O 24mA Host parallel port (Bus                                                                                                                                                                                                                                  | sv) si               | gnal    |       |        |

| 67 21 VDDI2 P I/O Power                                                                                                                                                                                                                                                      |                      |         |       |        |

| 68 VDDI3 P I/O Power                                                                                                                                                                                                                                                         |                      |         |       |        |

| 69 HACK Low O 24mA Host parallel port (Act                                                                                                                                                                                                                                   | k) sig               | nal     |       |        |

| 70 HERR Low O 24mA Host parallel port (                                                                                                                                                                                                                                      |                      |         | nal.  | with   |

| 71 HSLC Low O 24mA Host parallel port (Sel-                                                                                                                                                                                                                                  |                      |         |       |        |

| 72 VDDI4 P I/O power                                                                                                                                                                                                                                                         |                      |         |       |        |

| 73 HPE Low O 24mA Host parallel port (Par                                                                                                                                                                                                                                    | oer en               | d) si   | gnal  |        |

| 74 HSLCIN I Host parallel port (Se                                                                                                                                                                                                                                           |                      |         |       | , with |

| 75 HINIT I Host parallel port                                                                                                                                                                                                                                                |                      |         |       |        |

| 76 GNDI3 P I/O ground                                                                                                                                                                                                                                                        |                      |         |       |        |

| 77 HAFD I Host parallel port (                                                                                                                                                                                                                                               | Auto                 | fee     | d) s  | ignal. |

| 78 HSTRB I Host parallel port (S                                                                                                                                                                                                                                             |                      |         |       |        |

| 79 GNDI4 P I/O ground                                                                                                                                                                                                                                                        |                      |         |       |        |

| 80 22 SDA Tri-state I/O 4mA Serial EEPROM dat                                                                                                                                                                                                                                | ta lir               | ne. F   | PCB   | need   |

| 81 23 SCL Tri-state I/O 4mA Serial EEPROM clo                                                                                                                                                                                                                                |                      |         |       |        |

| 82 TEST I For test only, with                                                                                                                                                                                                                                                |                      |         |       |        |

| 83 GNDU P USB transceiver groun                                                                                                                                                                                                                                              |                      |         |       |        |

| 84 24 D- I/O USB transceiver D-                                                                                                                                                                                                                                              |                      |         |       |        |

| 85 25 D+ I/O USB transceiver D+                                                                                                                                                                                                                                              |                      |         |       |        |

| 86 26 VDDU P USB transceiver power                                                                                                                                                                                                                                           | er                   |         |       |        |

# VI.Registers map-

| tegisters map     |            |                  |                                                    |

|-------------------|------------|------------------|----------------------------------------------------|

| PPCR              | R/W        | 'hff             | Parallel nort control register                     |

| PPHAR             | R/W        | 'hfe             | Parallel port high address register                |

| PPLAR             | R/W        | 'hfd             | Parallel port low address register                 |

| <u>PPDR</u>       | R/W        | 'hfc             | Parallel port data register                        |

| IVDHPR            | R/W        | 'hfb             | Image valid data high pointer register             |

| <u>IVDLPR</u>     | R/W        | 'hfa             | Image valid data low pointer register              |

| IVIR              | R/W        | 'hf9             | Image valid indication register                    |

| HADFR<br>TOOR     | R/W        | 'he4             | Host access device flag register                   |

| TGCR<br>MOD6DR    | R/W<br>R/W | 'hff00<br>'hff01 | TG Control Register  Modulo 6 bit for dot clock    |

| MODODK<br>MOD6PR  | R/W        | 'hff02           | Modulo 6 bit for pixel clock                       |

| MODOLK<br>MOD16HR | R/W        | 'hff03           | Modulo 16 bit high byte                            |

| MOD16LR           | R/W        | hff04            | Modulo 16 bit low byte                             |

| ADCLKRR           | R/W        | 'hff05           | ADCLK rise register                                |

| ADCLKFR           | R/W        | 'hff06           | ADCLK fall register                                |

| SHR6R             | R/W        | 'hff07           | SH(TG) setup register(reference to 6bit counter)   |

| SHF6R             | R/W        | 'hff08           | SH(TG) setup register(reference to 6bit counter)   |

| SHR8R             | R/W        | 'hff09           | SH(TG) setup register(reference to 16bit counter)  |

| SHF8R             | R/W        | 'hff0a           | SH(TG) setup register(reference to 16bit counter)  |

| SHCR              | R/W        | 'hff0b           | SH(TG) configuration register                      |

| LEDRHR            | R/W        | 'hff0c           | LED rise high register(reference to 16bit counter) |

| LEDRLR            | R/W        | 'hff0d           | LED rise low register(reference to 16bit counter)  |

| LEDFHR            | R/W        | 'hff0e           | LED fall high register(reference to 16bit counter) |

| LEDFLR            | R/W        | 'hff0f           | LED fall low register(reference to 16bit counter)  |

| LEDCR             | R/W        | 'hff10           | LED configuration register                         |

| TGMR              | R/W        | 'hff11           | TG Mask register                                   |

| RS1RR             | R/W        | hff12            | RS1 rise register                                  |

| RS1FR             | R/W        | 'hff13           | RS1 fall register                                  |

| RS2RR             | R/W        | 'hff14           | RS2 rise register                                  |

| RS2FR             | R/W        | hff15            | RS2 fall register                                  |

| SHRRR             | R/W        | 'hff16           | SHR rise register                                  |

| SHRFR             | R/W        | 'hff17           | SHR fall register                                  |

| SHSRR             | R/W        | 'hff18           | SHS rise register                                  |

| SHSFR             | R/W        | 'hff19           | SHS fall register                                  |

| H1RR              | R/W        | 'hff1a           | H1 rise register                                   |

| H1FR              | R/W        | 'hff1b           | H1 fall register                                   |

| H2RR              | R/W        | 'hff1c           | H2 rise register                                   |

| H2FR              | R/W        | 'hff1d           | H2 fall register                                   |

| CLAMP0RR          | R/W        | 'hff1e           | CLAMP 0 rise register                              |

| CLAMP0FR          | R/W        | 'hff1f           | CLAMP 0 fall register                              |

| Name     | R/W | Address | Description                  |

|----------|-----|---------|------------------------------|

| CCLP0RR  | R/W | 'hff20  | CCLP 0 rise register         |

| CCLP0FR  | R/W | hff21   | CCLP 0 fall register         |

| CLAMP1RR | R/W | hff22   | CLAMP 1 rise register        |

| CLAMP1FR | R/W | hff23   | CLAMP 1 fall register        |

| CCLP1RR  | R/W | 'hff24  | CCLP 1 rise register         |

| CCLP1FR  | R/W | hff25   | CCLP 1 fall register         |

| CLAMP2RR | R/W | 'hff26  | CLAMP 2 rise register        |

| CLAMP2FR | R/W | 'hff27  | CLAMP 2 fall register        |

| CCLP2RR  | R/W | 'hff28  | CCLP 2 rise register         |

| CCLP2FR  | R/W | hff29   | CCLP 2 fall register         |

| CDSR0RR  | R/W | 'hff2a  | CDSR channel 0 rise register |

| CDSR0FR  | R/W | 'hff2b  | CDSR channel 0 fall register |

| CDSR1RR  | R/W | 'hff2c  | CDSR channel 1 rise register |

| CDSR1FR  | R/W | 'hff2d  | CDSR channel 1 fall register |

| CDSR2RR  | R/W | 'hff2e  | CDSR channel 2 rise register |

| CDSR2FR  | R/W | 'hff2f  | CDSR channel 2 fall register |

| CDSS0RR  | R/W | hff30   | CDSS channel 0 rise register |

| CDSS0FR  | R/W | 'hff31  | CDSS channel 0 fall register |

| CDSS1RR  | R/W | 'hff32  | CDSS channel 1 rise register |

| CDSS1FR  | R/W | hff33   | CDSS channel 1 fall register |

| CDSS2RR  | R/W | 'hff34  | CDSS channel 2 rise register |

| CDSS2FR  | R/W | hff35   | CDSS channel 2 fall register |

| CDSD0RR  | R/W | 'hff36  | CDSD channel 0 rise register |

| CDSD0FR  | R/W | 'hff37  | CDSD channel 0 fall register |

| CDSD1RR  | R/W | 'hff38  | CDSD channel 1 rise register |

| CDSD1FR  | R/W | 'hff39  | CDSD channel 1 fall register |

| CDSD2RR  | R/W | 'hff3a  | CDSD channel 2 rise register |

| CDSD2FR  | R/W | 'hff3b  | CDSD channel 2 fall register |

| MUXA0RR  | R/W | 'hff3c  | MUXA sel 0 rise register     |

| MUXA0FR  | R/W | 'hff3d  | MUXA sel 0 fall register     |

| MUXA1RR  | R/W | 'hff3e  | MUXA sel 1 rise register     |

| MUXA1FR  | R/W | 'hff3f  | MUXA sel 1 fall register     |

| MUXB0RR  | R/W | 'hff40  | MUXB sel 0 rise register     |

| MUXB0FR  | R/W | 'hff41  | MUXB sel 0 fall register     |

| MUXB1RR  | R/W | 'hff42  | MUXB sel 1 rise register     |

| MUXB1FR  | R/W | 'hff43  | MUXB sel 1 fall register     |

| OFFM0RR  | R/W | 'hff44  | OFFM sel 0 rise register     |

| OFFM0FR  | R/W | 'hff45  | OFFM sel 0 fall register     |

| OFFM1RR  | R/W | 'hff46  | OFFM sel 1 rise register     |

| OFFM1FR  | R/W | 'hff47  | OFFM sel 1 fall register     |

| PGAM0RR  | R/W | 'hff48  | PGAM sel 0 rise register     |

| PGAM0FR  | R/W | 'hff49  | PGAM sel 0 fall register     |

| PGAM1RR  | R/W | 'hff4a  | PGAM sel 1 rise register     |

| PGAM1FR  | R/W | 'hff4b  | PGAM sel 1 fall register     |

| Name          | R/W | Address | Description                                 |

|---------------|-----|---------|---------------------------------------------|

| GAINM0RR      | R/W | 'hff4c  | GAINM sel 0 rise register                   |

| GAINM0FR      | R/W | 'hff4d  | GAINM sel 0 fall register                   |

| GAINM1RR      | R/W | 'hff4e  | GAINM sel 1 rise register                   |

| GAINM1FR      | R/W | 'hff4f  | GAINM sel 1 fall register                   |

| DCR           | R/W | 'hff80  | DMA Control Register                        |

| D1TBHR        | W   | 'hff81  | DMA1 Transfer Byte Count High Byte Register |

| D1TBLR        | W   | 'hff82  | DMA1 Transfer Byte Count Low Byte Register  |

| MISAHR        | W   | 'hff83  | M1 Starting Address High Byte Register      |

| MISALR        | W   | 'hff84  | M1 Starting Address Low Byte Register       |

| M2SAHR        | R/W | 'hff85  | M2 Starting Address High Byte Register      |

| M2SALR        | R/W | 'hff86  | M2 Starting Address Low Byte Register       |

| D2BCHR        | R/W | 'hff88  | DMA2 byte count high register               |

| D2BCLR        | R/W | 'hff89  | DMA2 byte count low register                |

| <b>DMACR</b>  | R/W | ʻhff8a  | DMA configuration register                  |

| D2THR         | R/W | 'hff8b  | DMA2 Transfer Count High Byte Register      |

| D2TLR         | R/W | 'hff8c  | DMA2 Transfer Count Low Byte Register       |

| D2SHR         | R/W | 'hff8d  | DMA2 Sync Count High Byte Register          |

| D2SLR         | R/W | 'hff8e  | DMA2 Svnc Count Low Byte Register           |

| RHR           | R/W | 'hff8f  | Resolution High Byte Register               |

| RLR           | R/W | 'hff90  | Resolution Low Byte Register                |

| CCR           | W   | 'hff91  | Compression Configuration Register          |

| MBLHR         | R/W | hff92   | Minimum Buffer length High Register         |

| MBLLR         | R/W | hff93   | Minimum Buffer length Low Register          |

| <i>GPIOCR</i> | R/W | 'hff94  | GPIO control register                       |

| <i>GPIODR</i> | R/W | 'hff95  | GPIO data register                          |

| WDTRR         | W   | 'hff96  | Watch Dog Timer Reset register              |

| ASR           | R/W | 'hff87  | AFE suspend register                        |

| ACR           | R/W | 'hff97  | AFE configuration register                  |

| AC2R          | R/W | 'hff98  | AFE configuration 2 register                |

| COFF0R        | R/W | 'hff99  | CDS OFFSET for channel 0                    |

| CPGA0R        | R/W | ʻhff9a  | CDS PGA for channel 0                       |

| COFF1R        | R/W | 'hff9b  | CDS OFFSET for channel 1                    |

| CPGA1R        | R/W | 'hff9c  | CDS PGA for channel 1                       |

| COFF2R        | R/W | 'hff9d  | CDS OFFSET for channel 2                    |

| CPGA2R        | R/W | 'hff9e  | CDS PGA for channel 2                       |

| SCR           | R/W | 'hff9f  | Suspend Control                             |

| <i>PPMCR</i>  | R/W | 'hffA0  | Parallel port mode control register         |

| <i>PPHSR</i>  | R/W | 'hffA1  | Parallel port Host Status register          |

| <i>PPHDR</i>  | R/W | 'hffA2  | Parallel port Host Data register            |

| PPDSR         | R/W | 'hffA3  | Parallel port Device Status register        |

| <i>EDHSAR</i> | R/W | 'hffA5  | EPP/USB DMA3 high start address register    |

| EDLSAR        | R/W | 'hffA6  | EPP/USB DMA3 low start address register     |

| <i>EDHBCR</i> | R/W | 'hffA7  | EPP DMA3 high byte count register           |

| EDLBCR        | R/W | 'hffA8  | EPP DMA3 low byte count register            |

| NAME          | R/W | Address | Description                                 |

|---------------|-----|---------|---------------------------------------------|

| GAINMORR      | R/W | 'hff4c  | GAINM sel 0 rise register                   |

| GAINM0FR      | R/W | 'hff4d  | GAINM sel 0 fall register                   |

| GAINM1RR      | R/W | 'hff4e  | GAINM sel 1 rise register                   |

| GAINM1FR      | R/W | 'hff4f  | GAINM sel 1 fall register                   |

| <u>DCR</u>    | R/W | 'hff80  | DMA Control Register                        |

| D1TBHR        | W   | 'hff81  | DMA1 Transfer Byte Count High Byte Register |

| D1TBLR        | W   | 'hff82  | DMA1 Transfer Byte Count Low Byte Register  |

| M1SAHR        | W   | 'hff83  | M1 Starting Address High Byte Register      |

| M1SALR        | W   | 'hff84  | M1 Starting Address Low Byte Register       |

| M2SAHR        | R/W | 'hff85  | M2 Starting Address High Byte Register      |

| M2SALR        | R/W | 'hff86  | M2 Starting Address Low Byte Register       |

| D2BCHR        | R/W | 'hff88  | DMA2 byte count high register               |

| D2BCLR        | R/W | 'hff89  | DMA2 byte count low register                |

| <b>DMACR</b>  | R/W | ʻhff8a  | DMA configuration register                  |

| D2THR         | R/W | 'hff8b  | DMA2 Transfer Count High Byte Register      |

| D2TLR         | R/W | 'hff8c  | DMA2 Transfer Count Low Byte Register       |

| D2SHR         | R/W | 'hff8d  | DMA2 Sync Count High Byte Register          |

| D2SLR         | R/W | 'hff8e  | DMA2 Svnc Count Low Byte Register           |

| RHR           | R/W | 'hff8f  | Resolution High Byte Register               |

| RLR           | R/W | 'hff90  | Resolution Low Byte Register                |

| CCR           | W   | 'hff91  | Compression Configuration Register          |

| MBLHR         | R/W | 'hff92  | Minimum Buffer length High Register         |

| MBLLR         | R/W | 'hff93  | Minimum Buffer length Low Register          |

| <i>GPIOCR</i> | R/W | 'hff94  | GPIO control register                       |

| <i>GPIODR</i> | R/W | 'hff95  | GPIO data register                          |

| WDTRR         | W   | 'hff96  | Watch Dog Timer Reset register              |

| ASR           | R/W | 'hff87  | AFE suspend register                        |

| ACR           | R/W | 'hff97  | AFE configuration register                  |

| AC2R          | R/W | 'hff98  | AFE configuration 2 register                |

| COFF0R        | R/W | 'hff99  | CDS OFFSET for channel 0                    |

| CPGA0R        | R/W | 'hff9a  | CDS PGA for channel 0                       |

| COFF1R        | R/W | 'hff9b  | CDS OFFSET for channel 1                    |

| CPGA1R        | R/W | 'hff9c  | CDS PGA for channel 1                       |

| COFF2R        | R/W | 'hff9d  | CDS OFFSET for channel 2                    |

| CPGA2R        | R/W | 'hff9e  | CDS PGA for channel 2                       |

| SCR           | R/W | 'hff9f  | Suspend Control                             |

| <i>PPMCR</i>  | R/W | 'hffA0  | Parallel port mode control register         |

| PPHSR         | R/W | 'hffA1  | Parallel port Host Status register          |

| <i>PPHDR</i>  | R/W | 'hffA2  | Parallel port Host Data register            |

| <i>PPDSR</i>  | R/W | 'hffA3  | Parallel port Device Status register        |

| <i>EDHSAR</i> | R/W | 'hffA5  | EPP/USB DMA3 high start address register    |

| EDLSAR        | R/W | 'hffA6  | EPP/USB DMA3 low start address register     |

| <b>EDHBCR</b> | R/W | 'hffA7  | EPP DMA3 high byte count register           |

| EDLBCR        | R/W | 'hffA8  | EPP DMA3 low byte count register            |

| N/43/E         | D /II/ | 4 1 1   | D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME           | R/W    | Address | Description  EDD/JCD DMA2 and all all all and all all all and all all all all all all all all all al |

| EDCR           | R/W    | 'hffA9  | EPP/USB DMA3 control register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TISR           | R/W    | 'hffAA  | Ton Interrupt status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| UIS2R          | R/W    | 'hffAB  | USB Interrupt status 2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| UIS1R          | R/W    | 'hffAC  | USB Interrupt status 1 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TIER           | R/W    | 'hffAD  | Ton Interrupt Enable Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| UIE2R          | R/W    | 'hffAE  | USB Interrunt Enable 2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <u>UIE1R</u>   | R/W    | 'hffAF  | USB Interrupt Enable 1 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ISR            | R/W    | 'hffB0  | Interrunt Select Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DFR            | R/W    | 'hffB1  | Device Flag register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <b>DBCARCR</b> | R/W    | 'hffB2  | DMA3 byte count auto-reload control register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| URLBCR         | R/W    | 'hffB3  | USB Receive low byte count Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| URHBCR         | R/W    | 'hffB4  | USB Receive high byte count Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| URLBCGIR       | R/W    | 'hffB5  | USB Receive low byte count to generate IRO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| URLBCGIR       | R/W    | 'hffB6  | USB Receive high byte count to generate IRO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| URT            | R      | 'hffB8  | USB Request Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| URC            | R      | 'hffB9  | USB Request Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| URVLB          | R      | 'hffBA  | USB Request Value Low Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| URVHB          | R      | 'hffBB  | USB Request Value High Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| URILB          | R      | 'hffBC  | USB Request Index Low Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <u>URIHB</u>   | R      | 'hffBD  | USB Reauest Index High Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| URLLB          | R      | 'hffBE  | USB Request Length Low Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| URLHB          | R      | 'hffBF  | USB Request Length High Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| UEIR           | R/W    | 'hffC0  | USB Endpoint index Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DUSR           | R      | 'hffC1  | DMA3 USB Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DUTBCI8R       | R/W    | 'hffC2  | DMA3 USB TX Byte Count for internal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DUTPS2R        | R/W    | 'hffC3  | DMA3 USB TX Packet Size 2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DUTPS1R        | R/W    | 'hffC4  | DMA3 USB TX Packet Size 1 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DUTPC2R        | R/W    | 'hffC5  | DMA3 USB TX Packet Count 2 (# of packet)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DUTPC1R        | R/W    | 'hffC6  | DMA3 USB TX Packet Count 1 (# of nacket)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <b>DURPSR</b>  | R      | 'hffC7  | DMA3 USB Receive packet size Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <u>UECR</u>    | R/W    | 'hffC8  | USB Endpoint Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <u>UETSR</u>   | R/W    | 'hffC9  | USB Endpoint Transmit Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| UERSR          | R/W    | 'hffCA  | USB Endpoint Receive Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <u>UDAR</u>    | R/W    | 'hffCB  | USB Device Address Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| UDCR           | R/W    | 'hffCC  | USB Device Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| UDSTR0         | R/W    | 'hffD0  | USB Device Status Transmit Register 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| UDSTR1         | R/W    | 'hffD1  | USB Device Status Transmit Register 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| UDSTR2         | R/W    | 'hffD2  | USB Device Status Transmit Register 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| UDSTR3         | R/W    | 'hffD3  | USB Device Status Transmit Register 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| UDSTR4         | R/W    | 'hffD4  | USB Device Status Transmit Register 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| UDSTR5         | R/W    | 'hffD5  | USB Device Status Transmit Register 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| UDSTR6         | R/W    | 'hffD6  | USB Device Status Transmit Register 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| UDSTR7         | R/W    | 'hffD7  | USB Device Status Transmit Register 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| UDCRR0         | R      | 'hffD8  | USB Device Command Receive Register 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Name   | R/W | Address | Description                           |

|--------|-----|---------|---------------------------------------|

| UDCRR1 | R   | 'hffD9  | USB Device Command Receive Register 1 |

| UDCRR2 | R   | 'hffDA  | USB Device Command Receive Register 2 |

| UDCRR3 | R   | 'hffDB  | USB Device Command Receive Register 3 |

| UDCRR4 | R   | 'hffDC  | USB Device Command Receive Register 4 |

| UDCRR5 | R   | 'hffDD  | USB Device Command Receive Register 5 |

| UDCRR6 | R   | 'hffDE  | USB Device Command Receive Register 6 |

| UDCRR7 | R   | 'hffDF  | USB Device Command Receive Register 7 |

- Registers Definitions

- Timing Generator Setup Register

# **CPU Read/Write**

Address: FF00H

| Bit | Reset | Description                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7:4 | 4' b0 | Reserved                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 3   | 1'b0  | Select LED control signal output to PEPP_AD0~PEPP_AD2 for the sake of driving issue.  When this bit is set, the mapping of pins are changed to:  PTGR = TG_R,  PTGG = TG_G,  PTGB = TG_B,  PEPP_AD0 = LED_R,  PEPP_AD1 = LED_G,  PEPP_AD2 = LED_B;  Note: TG_R, TG_G, TG_B are TG signal for R, G, B channel. |  |  |  |  |