FUJITSU SEMICONDUCTOR CONTROLLER MANUAL

# F<sup>2</sup>MC-16LX 16-BIT MICROCONTROLLER MB90580 SERIES HARDWARE MANUAL

## PREFACE

Thank you for selecting FUJITSU Semiconductor Devices.

The FUJITSU MB90580 series has been developed as one general-application version of the  $F^2MC^{\circledast}$ \*16LX series of original 16-bit one-chip microcontrollers for ASIC (application specific IC) applications. This manual describes the functions and operations of the MB90580 series, and is intended for use by engineers actually designing products using these semiconductors. Please be sure to read it carefully.

\*: F<sup>2</sup>MC is an abbreviation for FUJITSU Flexible Microcontroller, and is a registered trademark of Fujitsu.

This document is organized as follows.

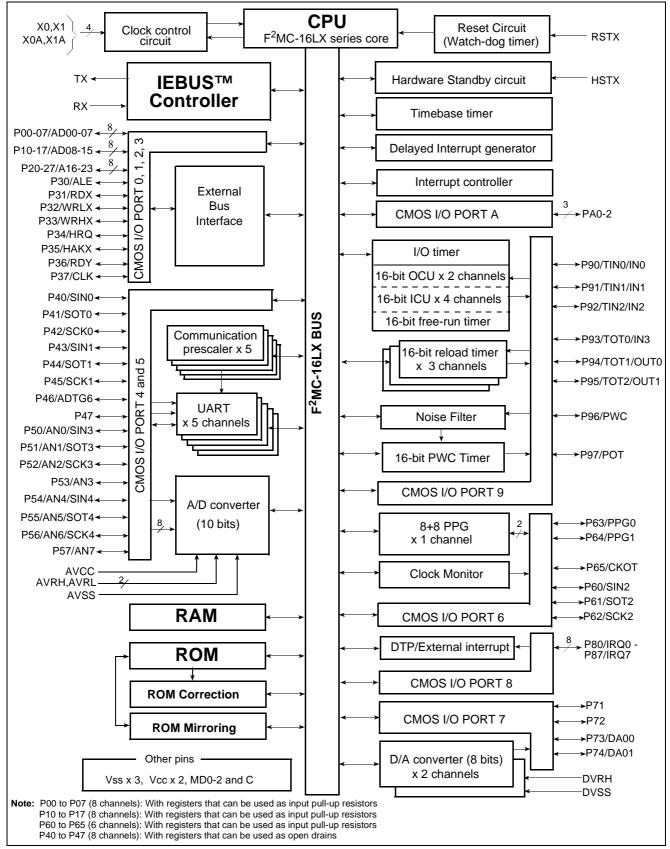

Chapter 1 OVERVIEW

This section presents an overview of MB90580 series features and functions.

Chapter 2 CPU

This section describes the functions of the  $F^2MC-16LX$  series CPU.

Chapter 3 MEMORY

This section describes the functions of the F<sup>2</sup>MC-16LX series memory.

Chapter 4 CLOCK AND RESET

This section describes the functions of the MB90580 series clocks and resets.

Chapter 5 WATCHDOG TIMER, TIME BASE TIMER, AND WATCH TIMER FUNCTION

This section describes the functions and operation of the MB90580 series watchdog timer, timebase timer and watch timer function.

Chapter 6 LOW POWER CONTROL CIRCUIT

This section describes the MB90580 series low power control circuits (CPU intermittent operation function, oscillator stabilization wait time, PLL clock multiplier function).

Chapter 7 INTERRUPT

This section describes the functions of each MB90580 each interrupt and interrupt source.

Chapter 8 PARALLEL PORTS

This section describes the functions of the MB90580 series parallel port.

Chapter 9 DTP/EXTERNAL INTERRUPT

This section describes the function and operation of the MB90580 series DTP and external interrupts.

Chapter 10 DELAY INTERRUPT MODULE

This section describes the functions and operation of the MB90580 series delay interrupt module.

Chapter 11

Chapter 12 COMMUNICATION PRESCALER

This section describes the MB90580 series communication prescaler.

Chapter 13 UART

This section describes the function and operation of the MB90580 UART.

Chapter 14 IE BUS

This section describes the functions and operation of the MB90580 series IE Bus.

Chapter 15 8/16-BIT PPG

This section describes the functions and operation of the MB90580 series 8/16-bit PPG.

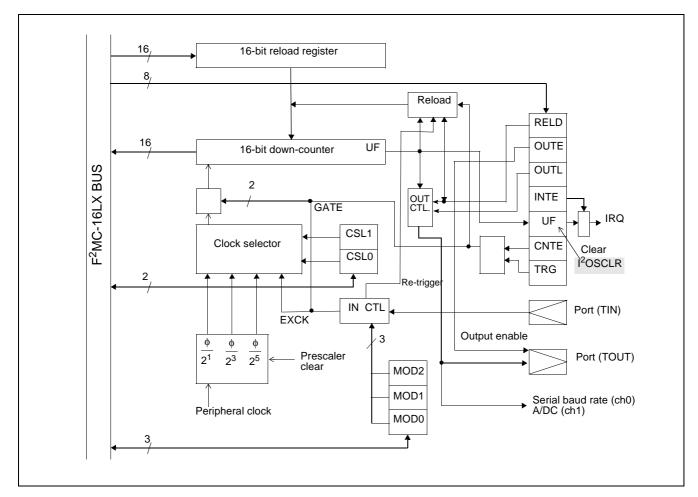

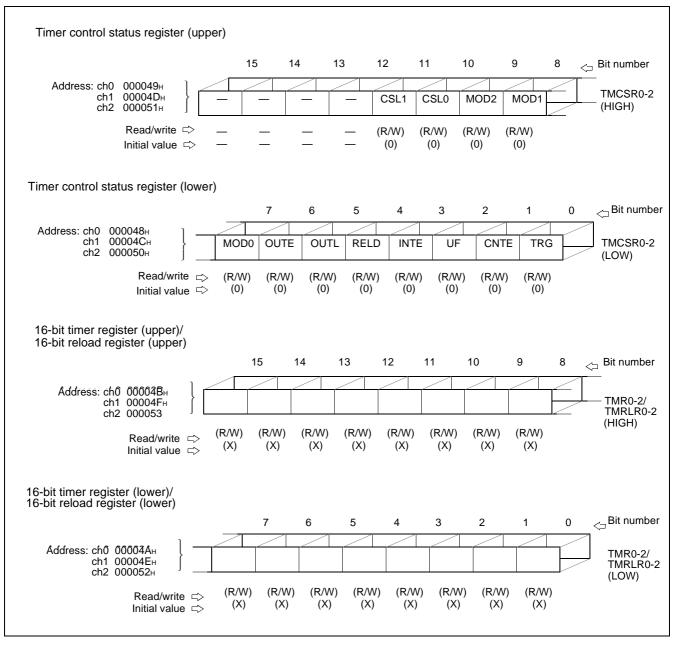

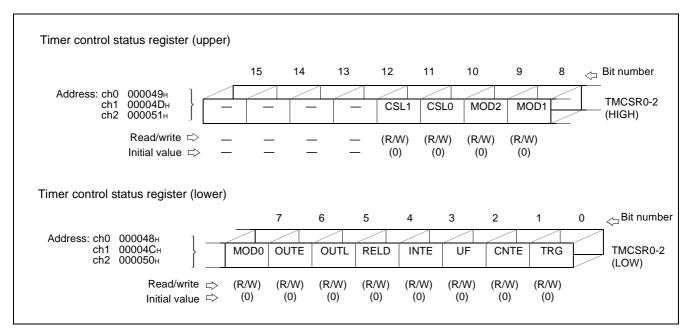

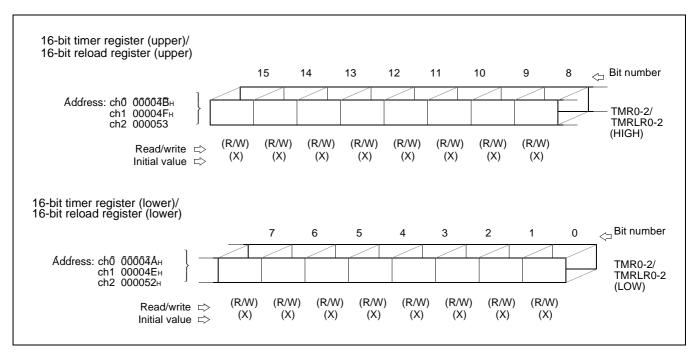

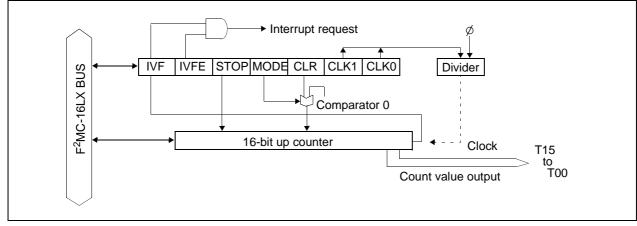

Chapter 16 16-BIT RELOAD TIMER (WITH EVENT COUNT FUNCTION)

This section describes the functions and operation of the MB90580 series 16-bit reload timer.

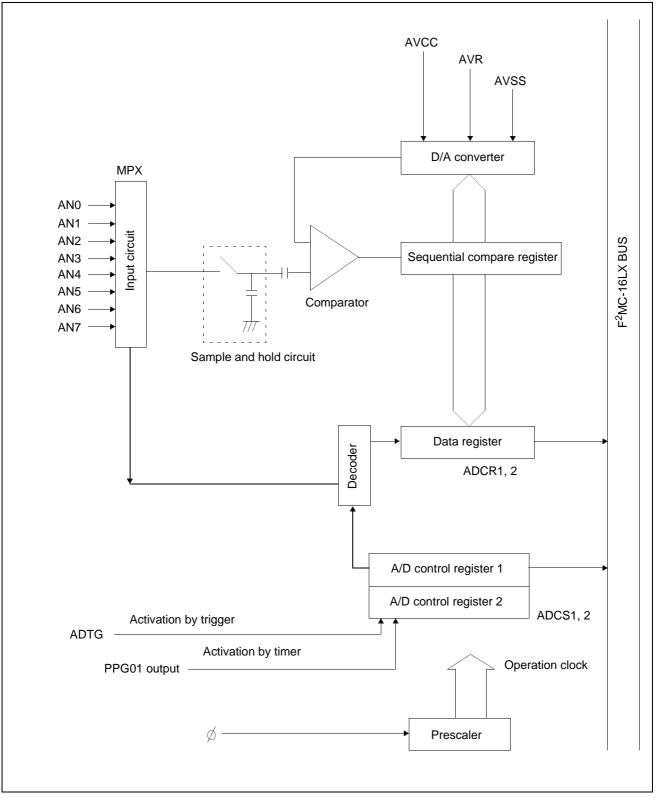

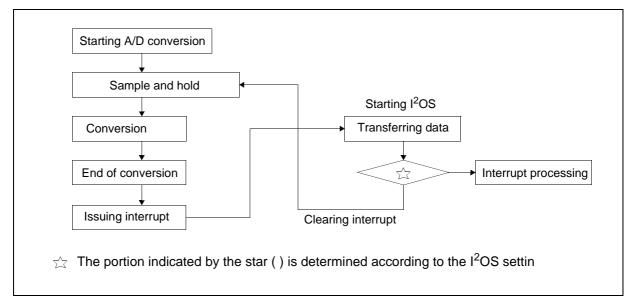

Chapter 17 A/D CONVERTERr

This section describes the functions and oeration of the MB90580 series A/D converter.

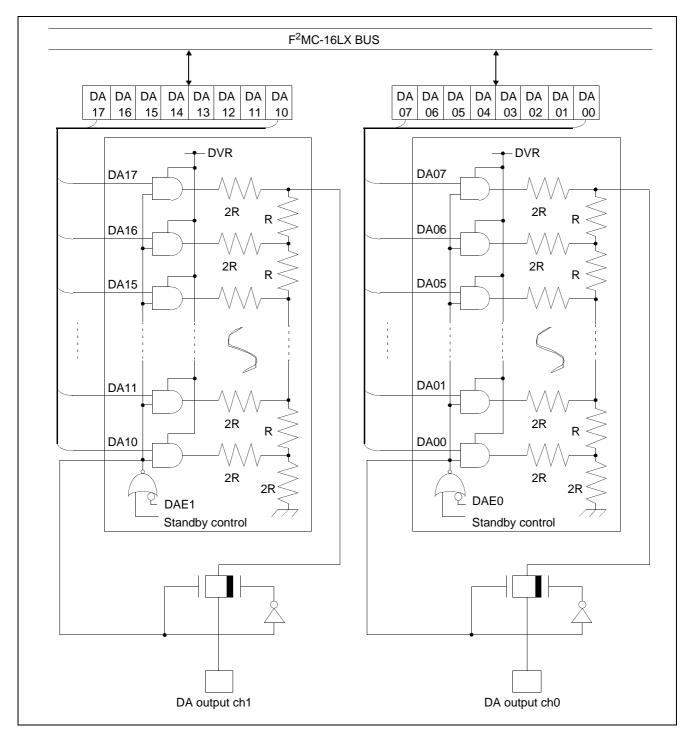

Chapter 18 D/A CONVERTER

This section describes the functions and oeration of the MB90580 series D/A converter

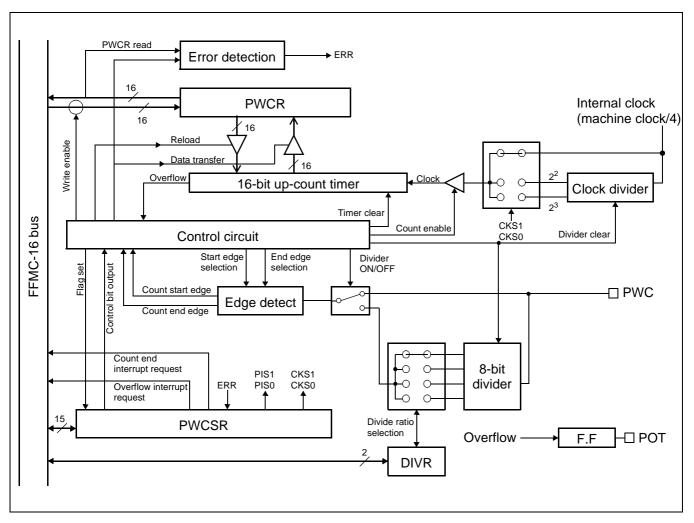

Chapter 19 PULSE WIDTH COUNTER (PWC) TIMER

This section describes the functions and oeration of the MB90580 series pulse width counter (PWC) timer.

Chapter 20 CLOCK MONITOR FUNCTION

This section describes the functions of the MB90580 series clock monitor function.

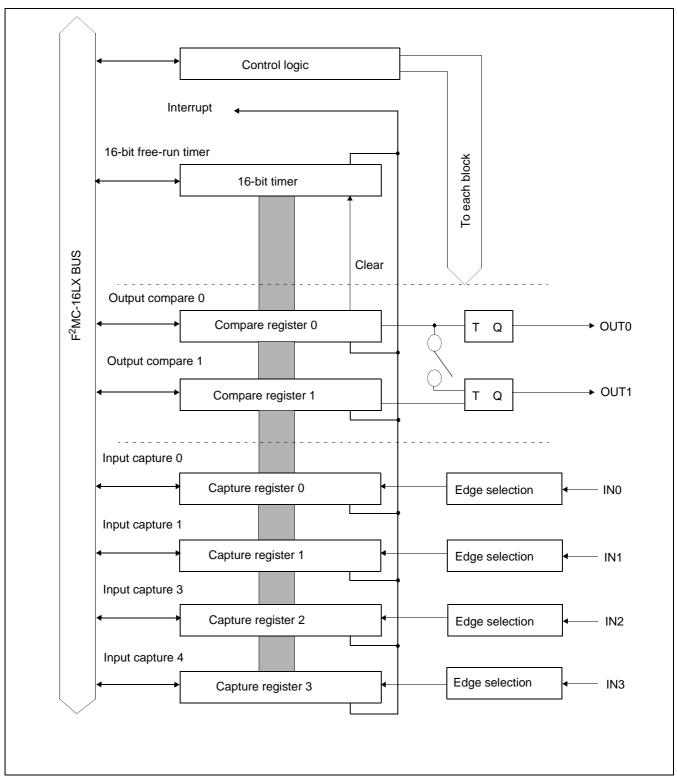

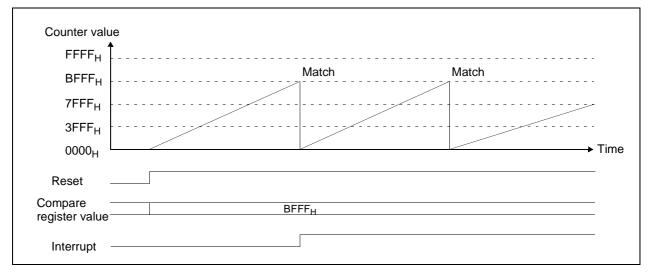

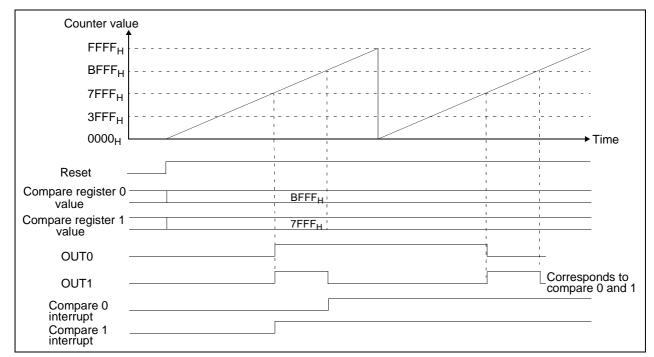

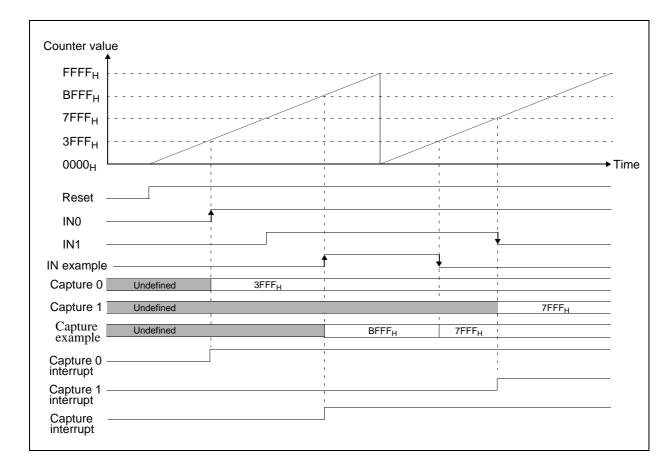

Chapter 21 16-bit I/O Timers

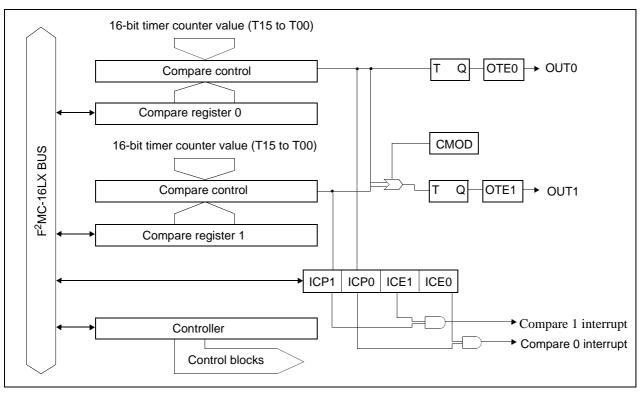

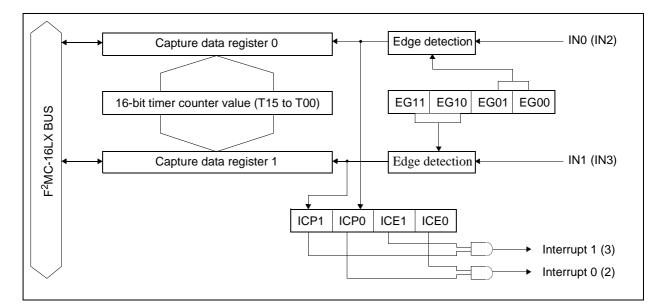

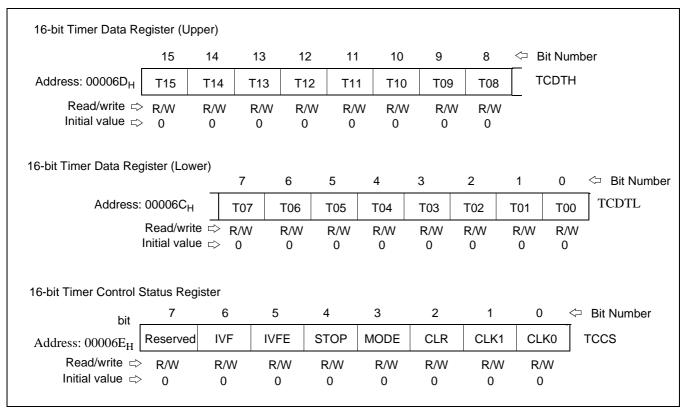

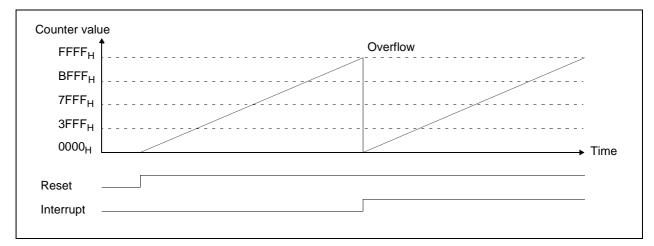

This section describes the functions and operation of the MB90580 series 16-bit I/O timers which consists of 16-bit free-run timer, 2 output compare registers and 4 input capture registers.

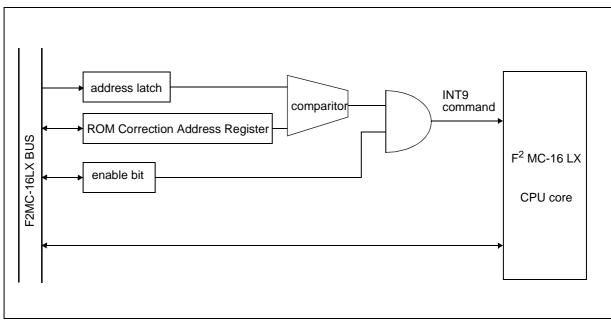

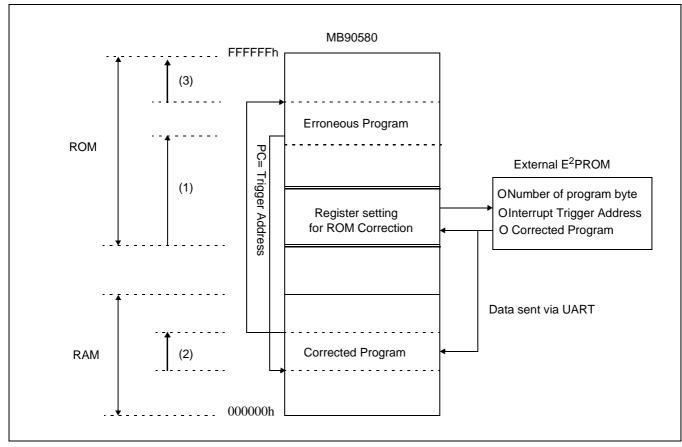

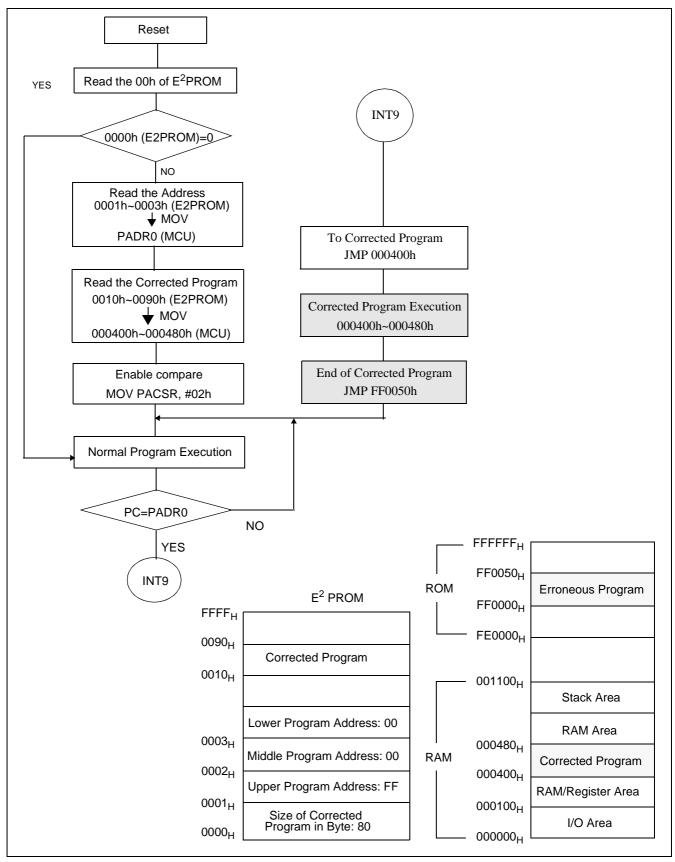

Chapter 22 ROM CORRECTION module

This section describes the function and operation of the MB90580 series rom correction module.

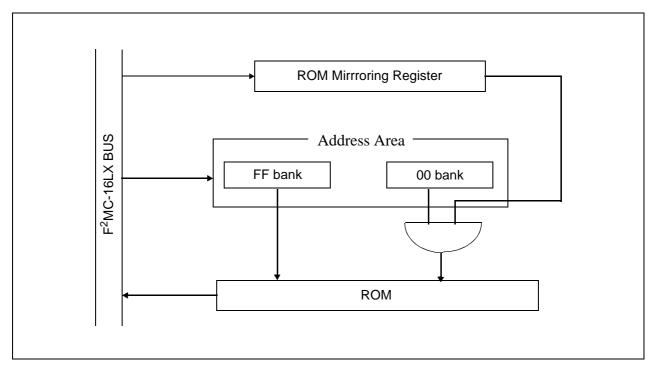

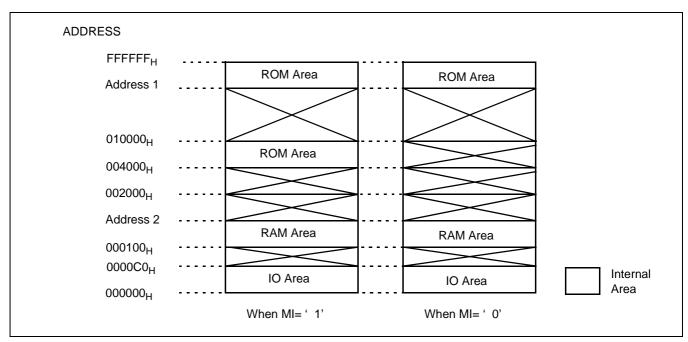

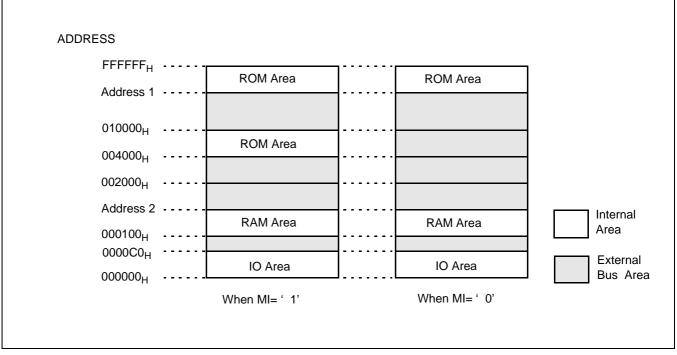

Chapter 23 ROM MIRRORING MODULE

This section describes the function of the MB90580 series ROM mirrorling module.

Appendix A I/O MAP

The appendix A provides I/O maps, and low power mode status transition charts.

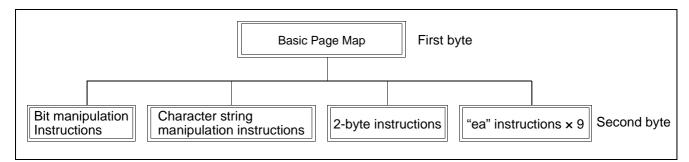

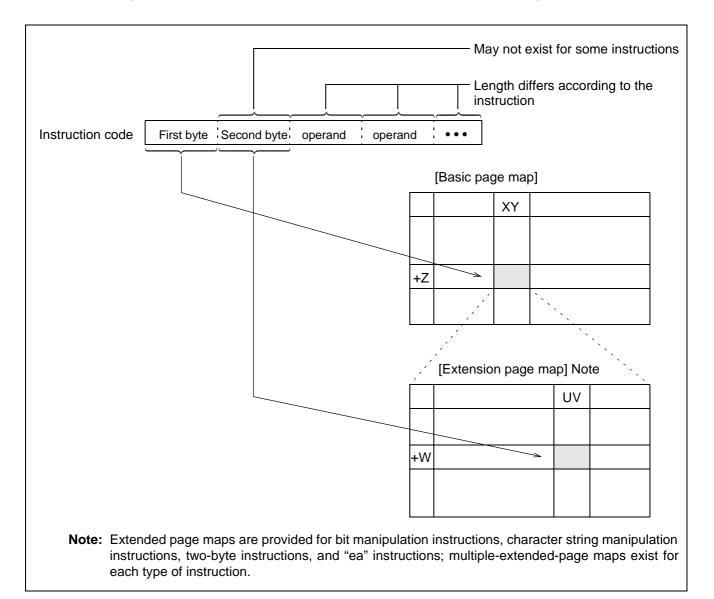

Appendix B INSTRUCTION

The appendix B describes addressing in the  $F^2MC^{\mathbb{R}*}$ -16LX series, and provides instruction lists and instruction maps.

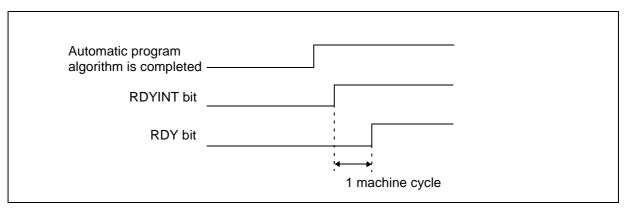

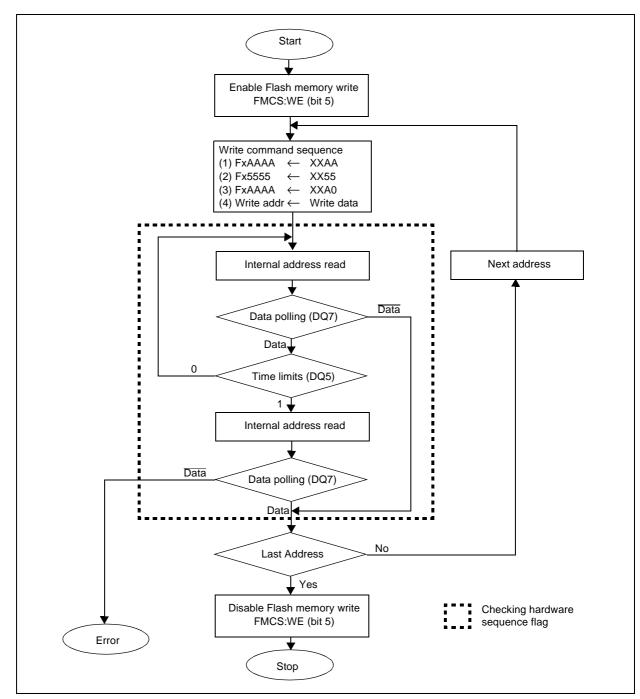

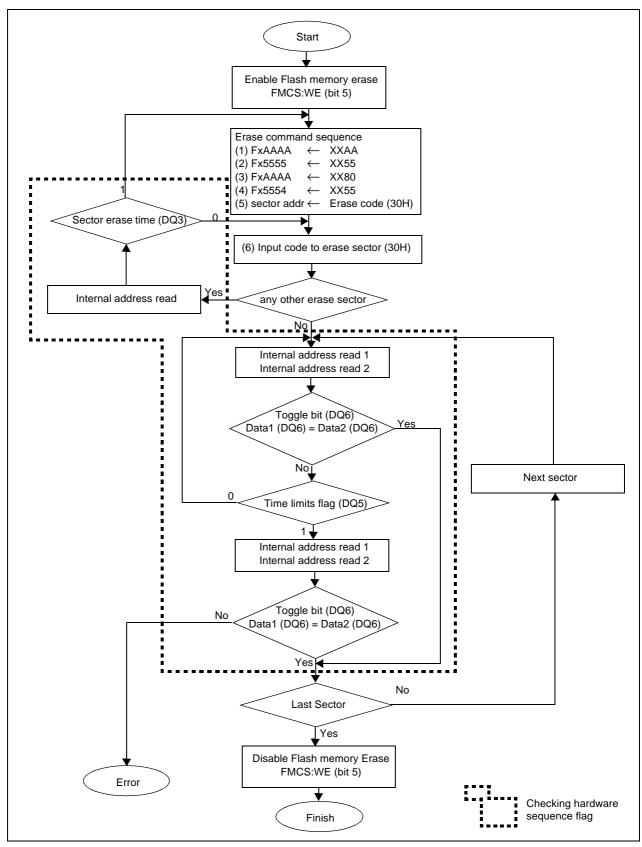

Appendix C PROGRAMMING THE FLASH MEMORY ON THE MB90F584

The appendix C provides programming method of the flash memory on the MB90F584.

# CONTENTS

| Chapter | 1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                           |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

|         | 1.1 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                           |

|         | 1.2 Product Lineup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3                           |

|         | 1.3 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4                           |

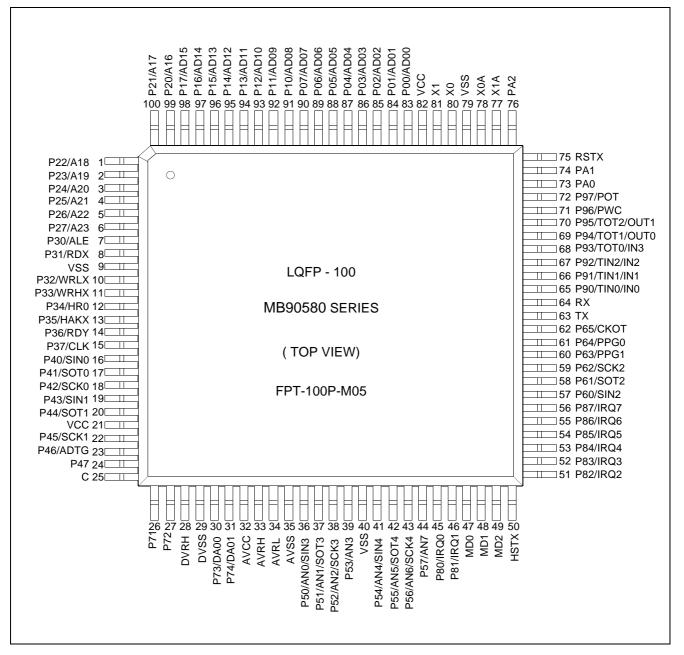

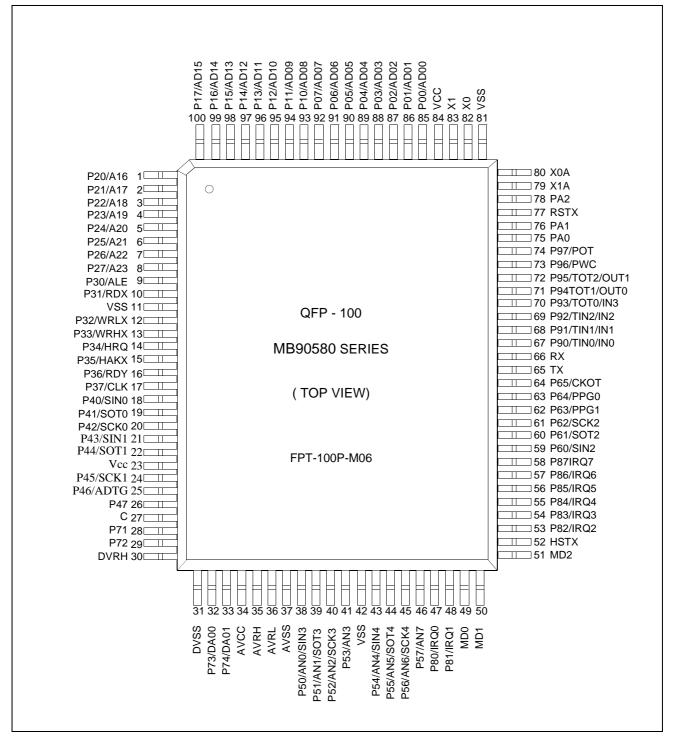

|         | 1.4 Pin Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5                           |

|         | 1.4.1 SQFP-100 Pin Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5                           |

|         | 1.4.1 QFP-100 Pin Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6                           |

|         | 1.5 Pin Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7                           |

|         | 1.6 Handling the Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 14                          |

| Chapter | 2 CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 15                          |

|         | 2.1 CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                             |

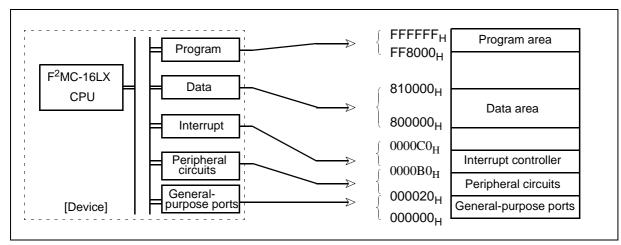

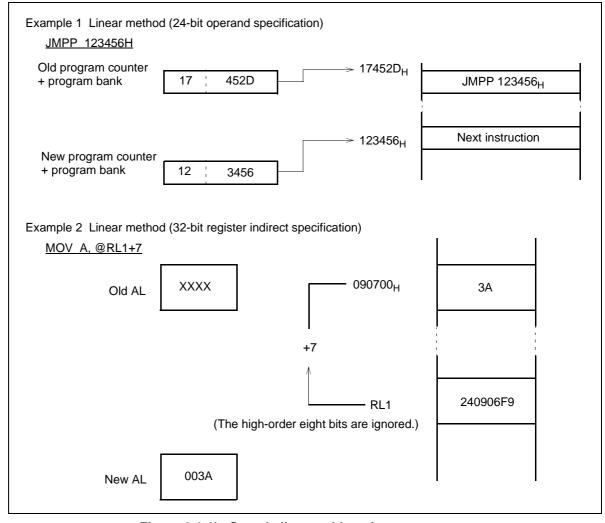

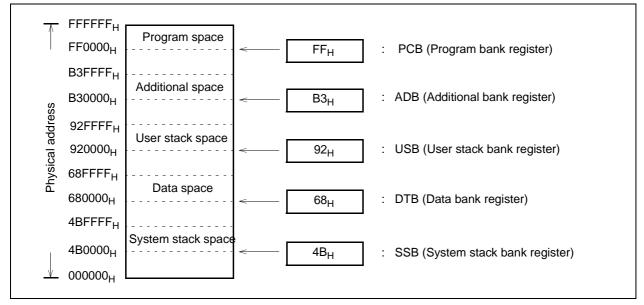

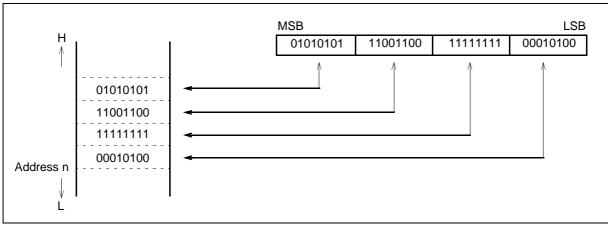

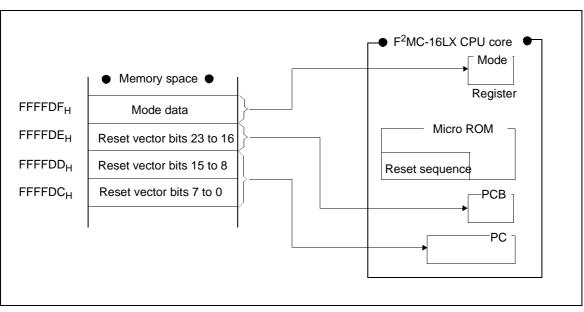

|         | 2.1.1 Memory space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                             |

|         | 2.1.2 Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                             |

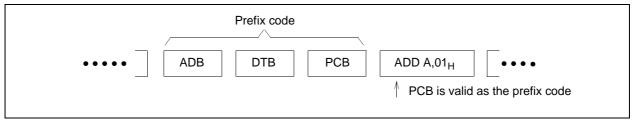

|         | 2.1.3 Prefix codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                             |

| Chantor | 3 Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                             |

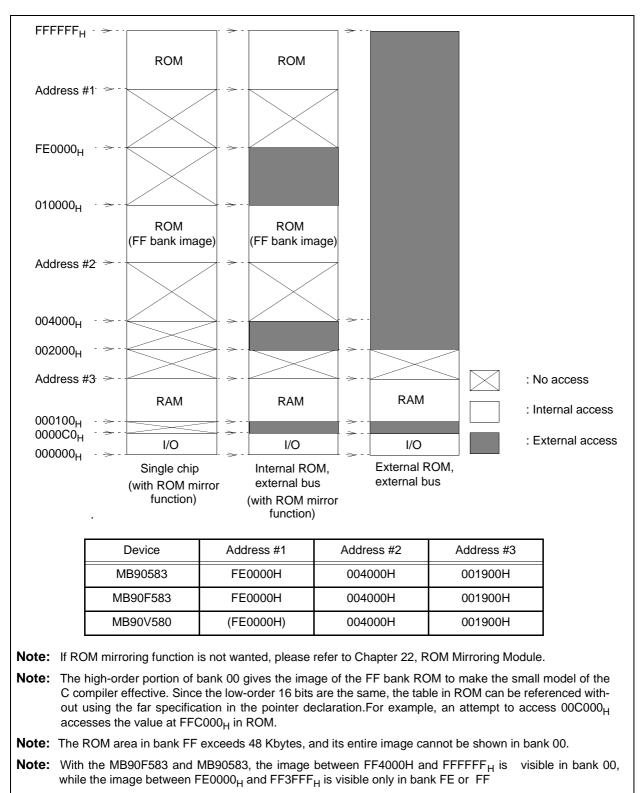

| Shaptel | 3.1 Memory Access Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                             |

|         | 3.1.1 Mode pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                             |

|         | 3.1.2 Mode data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                             |

|         | 3.1.3 Bus Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                             |

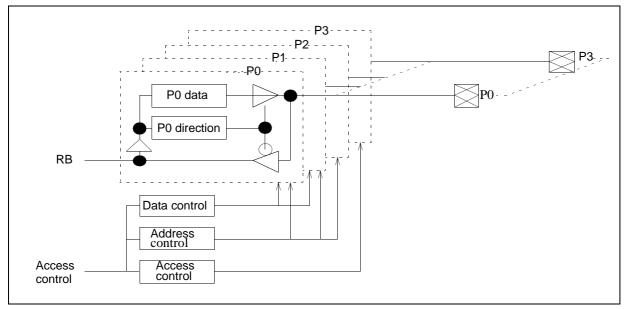

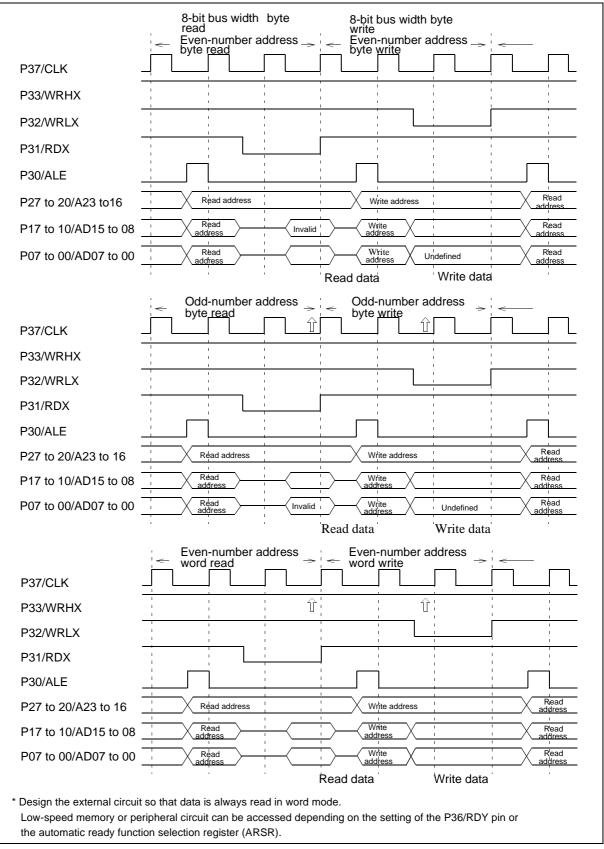

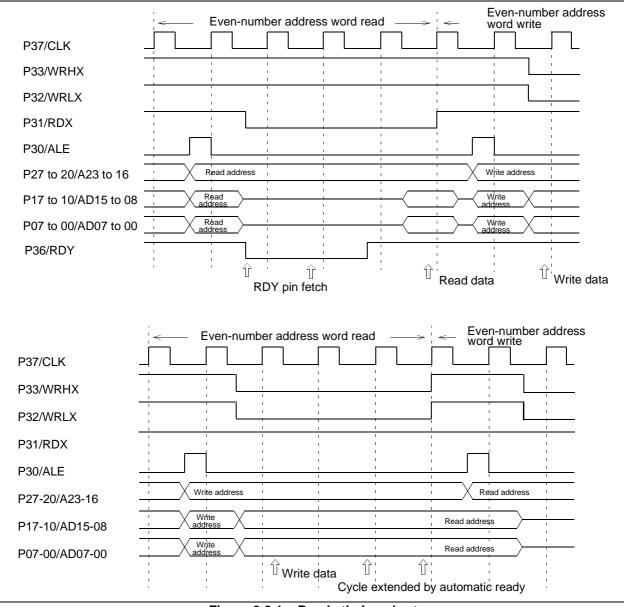

|         | 3.2 External Memory Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                             |

|         | 3.2.1 Block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                             |

|         | 3.2.2 Registers and Register details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                             |

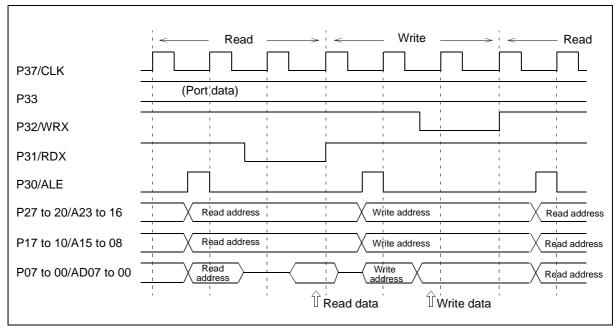

|         | 3.2.1 Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                             |

|         | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                             |

| Chanter | A Cleak and Deept                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 47                          |

| Chapter | 4 Clock and Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                             |

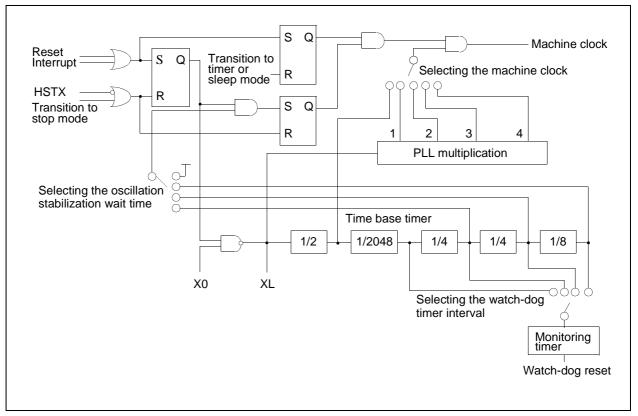

| Chapter | 4.1 Clock Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 47                          |

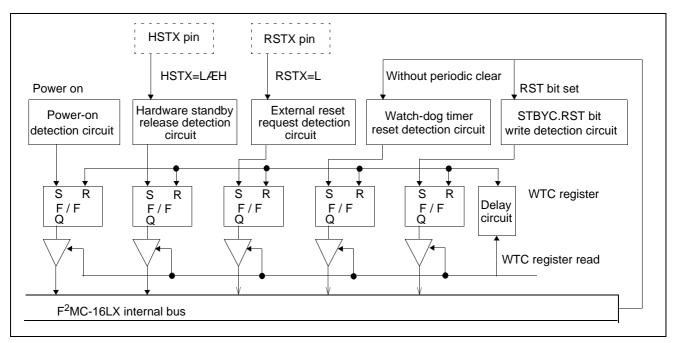

| Chapter | <ul><li>4.1 Clock Generator</li><li>4.2 Reset Causes</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 47<br>48                    |

|         | <ul> <li>4.1 Clock Generator</li> <li>4.2 Reset Causes</li> <li>4.3 Operation after reset release</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 47<br>48<br>50              |

|         | <ul> <li>4.1 Clock Generator</li> <li>4.2 Reset Causes</li> <li>4.3 Operation after reset release</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 47<br>48<br>50<br><b>51</b> |

|         | <ul> <li>4.1 Clock Generator</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 47<br>48<br>                |

|         | <ul> <li>4.1 Clock Generator</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                             |

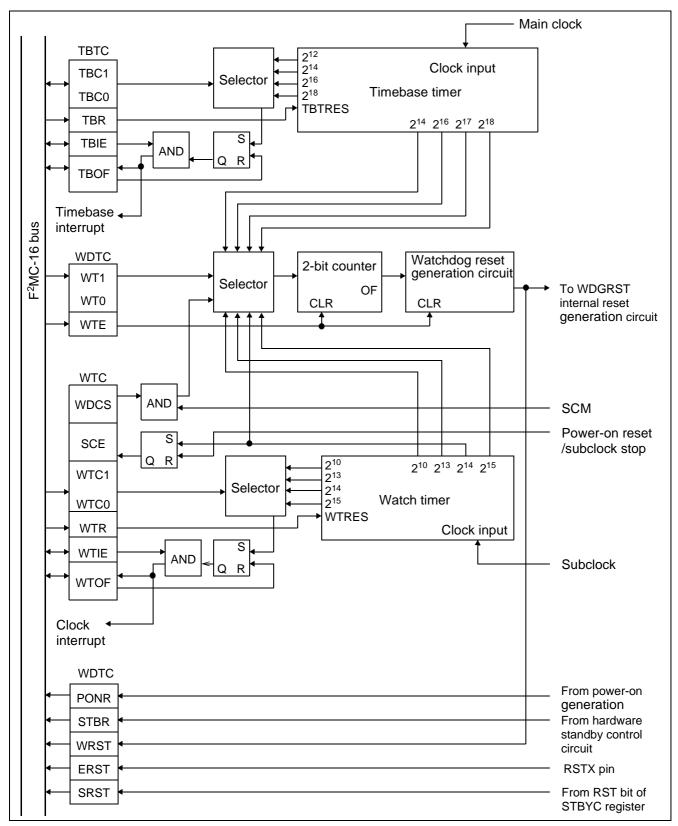

| Chapter | <ul> <li>4.1 Clock Generator</li> <li>4.2 Reset Causes</li> <li>4.3 Operation after reset release</li> <li>5 Watchdog Timer, Timebase Timer, and Watch Timer Functions</li> <li>5.1 Outline</li> <li>5.2 Block diagram</li> <li>5.3 Registers and register details</li> <li>5.3.1 WDTC (Watch-Dog Timer Control Register)</li> <li>5.3.2 TBTC (Time Base Timer Control Register)</li> <li>5.3.3 Watch Timer Control Register)</li> <li>5.4 Operation</li> <li>5.4.1 Watch-Dog Timer</li> <li>5.4.2 Time Base Timer</li> <li>5.4.3 Watch Timer</li> </ul>                                                                                                                                                                                                                                                                      |                             |

| Chapter | <ul> <li>4.1 Clock Generator</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                             |

| Chapter | <ul> <li>4.1 Clock Generator</li> <li>4.2 Reset Causes</li> <li>4.3 Operation after reset release</li> <li>5 Watchdog Timer, Timebase Timer, and Watch Timer Functions</li> <li>5.1 Outline</li> <li>5.2 Block diagram</li> <li>5.3 Registers and register details</li> <li>5.3.1 WDTC (Watch-Dog Timer Control Register)</li> <li>5.3.2 TBTC (Time Base Timer Control Register)</li> <li>5.3.3 Watch Timer Control Register)</li> <li>5.4 Operation</li> <li>5.4.1 Watch-Dog Timer</li> <li>5.4.2 Time Base Timer</li> <li>5.4.3 Watch Timer</li> </ul>                                                                                                                                                                                                                                                                      |                             |

| Chapter | <ul> <li>4.1 Clock Generator</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                             |

| Chapter | <ul> <li>4.1 Clock Generator</li> <li>4.2 Reset Causes</li> <li>4.3 Operation after reset release</li> <li>5 Watchdog Timer, Timebase Timer, and Watch Timer Functions</li> <li>5.1 Outline</li> <li>5.2 Block diagram</li> <li>5.3 Registers and register details</li> <li>5.3.1 WDTC (Watch-Dog Timer Control Register)</li> <li>5.3.2 TBTC (Time Base Timer Control Register)</li> <li>5.3.3 Watch Timer Control Register (WTC)</li> <li>5.4 Operation</li> <li>5.4.1 Watch-Dog Timer</li> <li>5.4.2 Time Base Timer</li> <li>5.4.3 Watch Timer</li> </ul>                                                                                                                                                                                                                                                                 |                             |

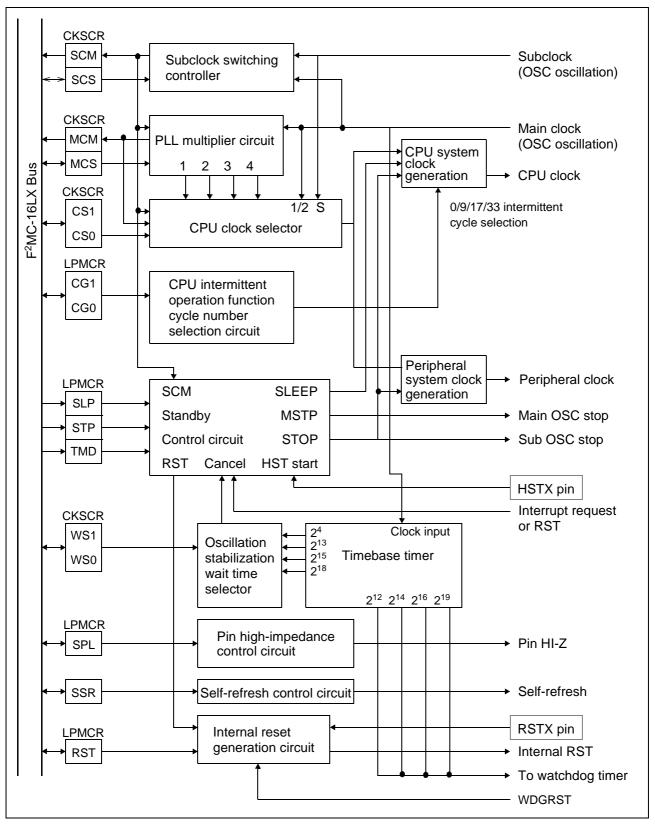

| Chapter | <ul> <li>4.1 Clock Generator</li> <li>4.2 Reset Causes</li> <li>4.3 Operation after reset release</li> <li>5 Watchdog Timer, Timebase Timer, and Watch Timer Functions</li> <li>5.1 Outline</li> <li>5.2 Block diagram</li> <li>5.3 Registers and register details</li> <li>5.3.1 WDTC (Watch-Dog Timer Control Register)</li> <li>5.3.2 TBTC (Time Base Timer Control Register)</li> <li>5.3.3 Watch Timer Control Register (WTC)</li> <li>5.4 Operation</li> <li>5.4.1 Watch-Dog Timer</li> <li>5.4.2 Time Base Timer</li> <li>5.4.3 Watch Timer</li> <li>6.4 Outline</li> <li>6.1 Outline</li> <li>6.2 Block Diagram</li> <li>6.3 Registers and register details</li> </ul>                                                                                                                                                |                             |

| Chapter | <ul> <li>4.1 Clock Generator</li> <li>4.2 Reset Causes</li> <li>4.3 Operation after reset release</li> <li>5 Watchdog Timer, Timebase Timer, and Watch Timer Functions</li> <li>5.1 Outline</li> <li>5.2 Block diagram</li> <li>5.3 Registers and register details</li> <li>5.3.1 WDTC (Watch-Dog Timer Control Register)</li> <li>5.3.2 TBTC (Time Base Timer Control Register)</li> <li>5.3.3 Watch Timer Control Register (WTC)</li> <li>5.4 Operation</li> <li>5.4.1 Watch-Dog Timer</li> <li>5.4.2 Time Base Timer</li> <li>5.4.3 Watch Timer</li> <li>6 Low Power Control Circuit</li> <li>6.1 Outline</li> <li>6.2 Block Diagram</li> <li>6.3 Registers and register details</li> <li>6.3.1 LPMCR (Low power mode control register)</li> <li>6.3.2 CKSCR (Clock selection register)</li> <li>6.4 Operations</li> </ul> |                             |

| Chapter | <ul> <li>4.1 Clock Generator</li> <li>4.2 Reset Causes</li> <li>4.3 Operation after reset release</li> <li>5 Watchdog Timer, Timebase Timer, and Watch Timer Functions</li> <li>5.1 Outline</li> <li>5.2 Block diagram</li> <li>5.3 Registers and register details</li> <li>5.3.1 WDTC (Watch-Dog Timer Control Register)</li> <li>5.3.2 TBTC (Time Base Timer Control Register)</li> <li>5.3.3 Watch Timer Control Register (WTC)</li> <li>5.4 Operation</li> <li>5.4.1 Watch-Dog Timer</li> <li>5.4.2 Time Base Timer</li> <li>5.4.3 Watch Timer</li> <li>6 Low Power Control Circuit</li> <li>6.1 Outline</li> <li>6.2 Block Diagram</li> <li>6.3 Registers and register details</li> <li>6.3.1 LPMCR (Low power mode control register)</li> <li>6.3.2 CKSCR (Clock selection register)</li> </ul>                         |                             |

|         |            | 6.4.3 Watch mode                                                               | 69  |

|---------|------------|--------------------------------------------------------------------------------|-----|

|         |            | 6.4.4 Stop mode                                                                | 69  |

|         |            | 6.4.5 Hardware standby mode                                                    | 70  |

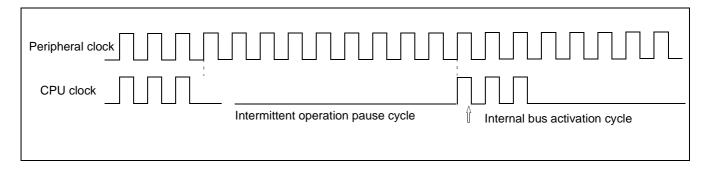

|         |            | 6.4.6 CPU intermittent operation function                                      | 70  |

|         |            | 6.4.7 Setting the main clock oscillation stabilization waiting period          | 71  |

|         |            | 6.4.8 Switching the machine clock                                              | 71  |

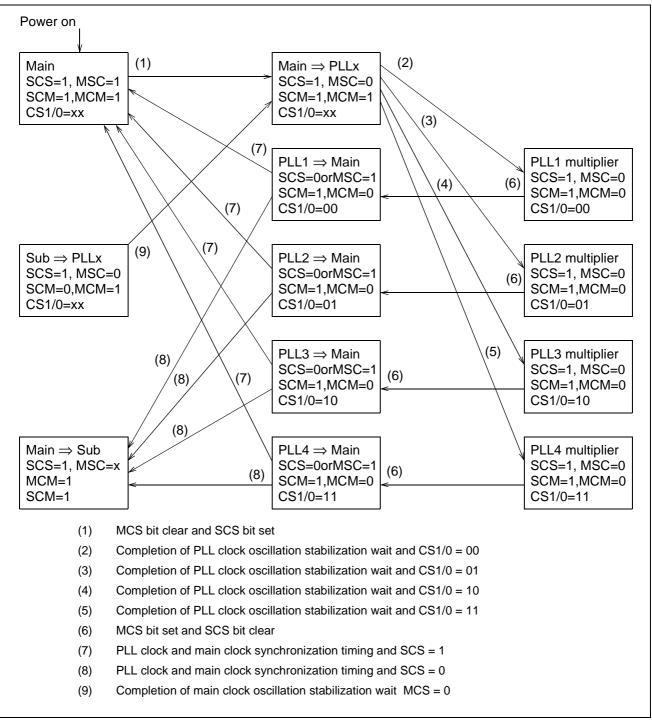

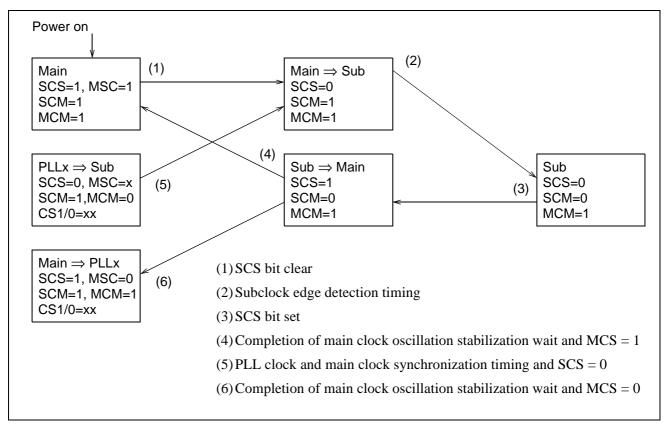

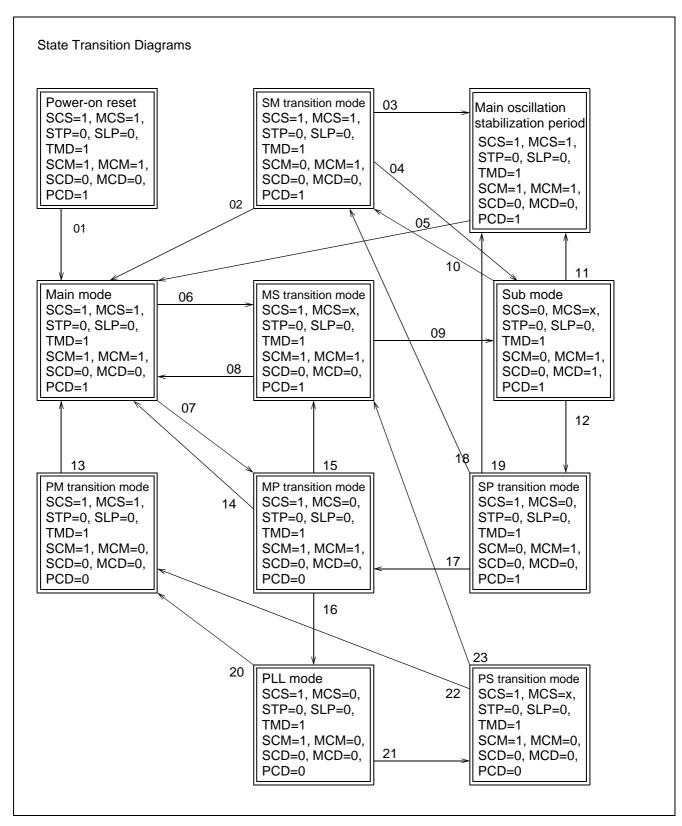

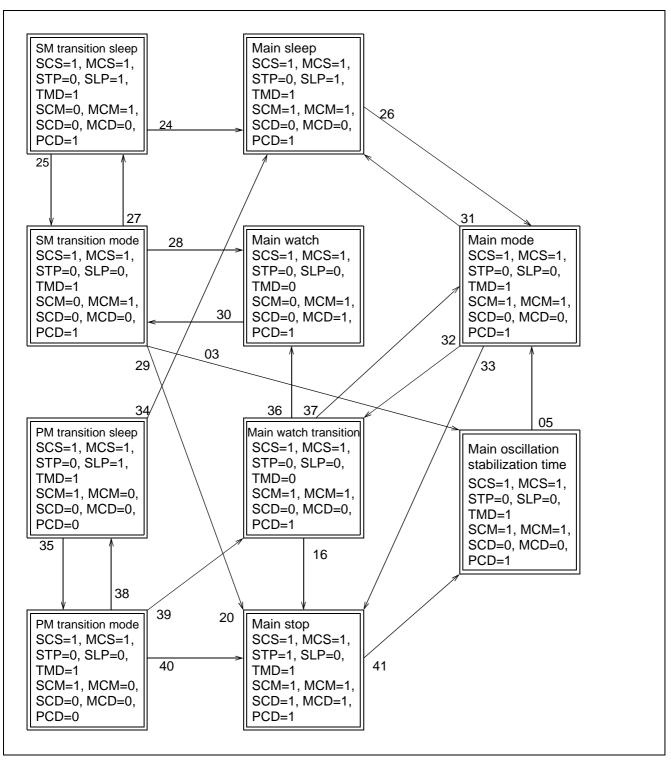

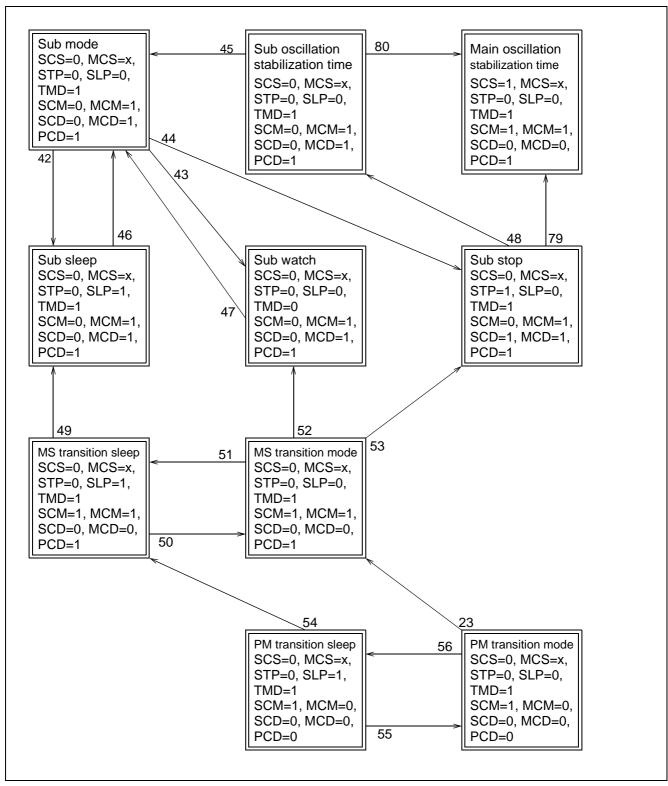

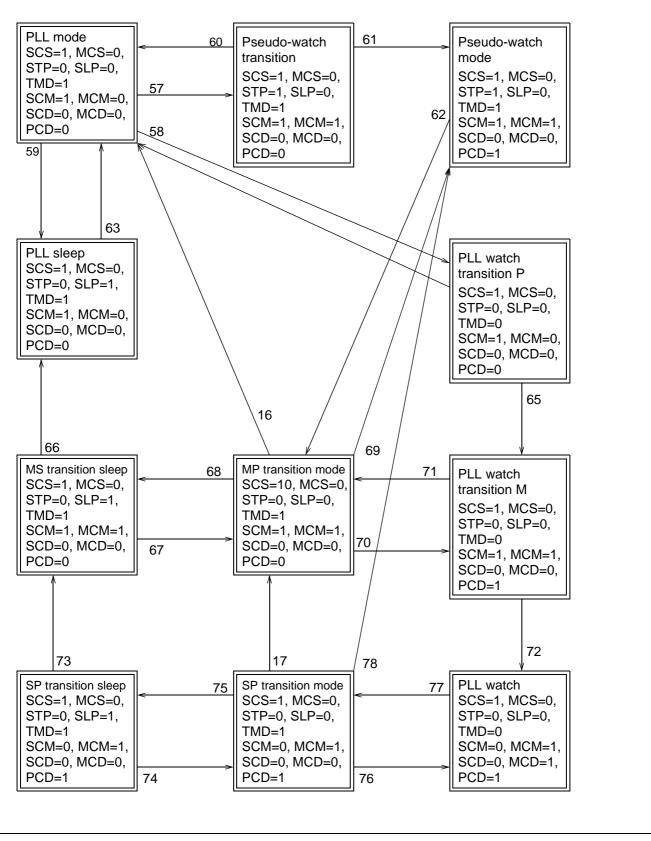

|         |            | 6.4.9 State transition                                                         | 73  |

| Chapter | 7 Ir       | nterrupt                                                                       | 81  |

|         |            | Outline                                                                        |     |

|         |            | 2 Causes of Interrupt                                                          |     |

|         | 7.3        | 3 Interrupt Vector                                                             | 83  |

|         |            | Hardware Interrupt                                                             |     |

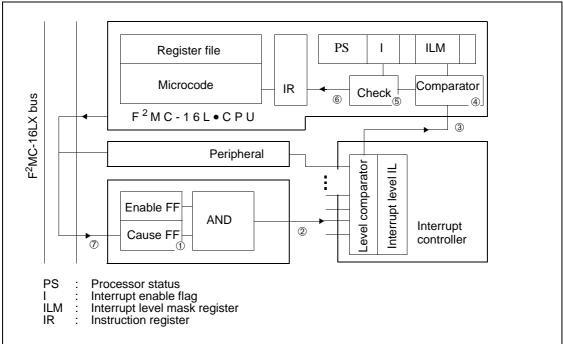

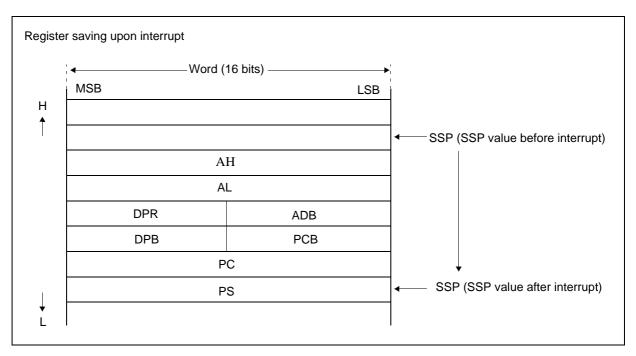

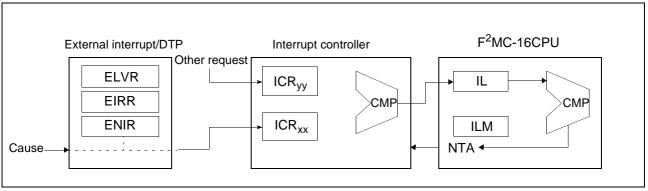

|         |            | 7.4.1 Overview                                                                 |     |

|         |            | 7.4.2 Structure                                                                |     |

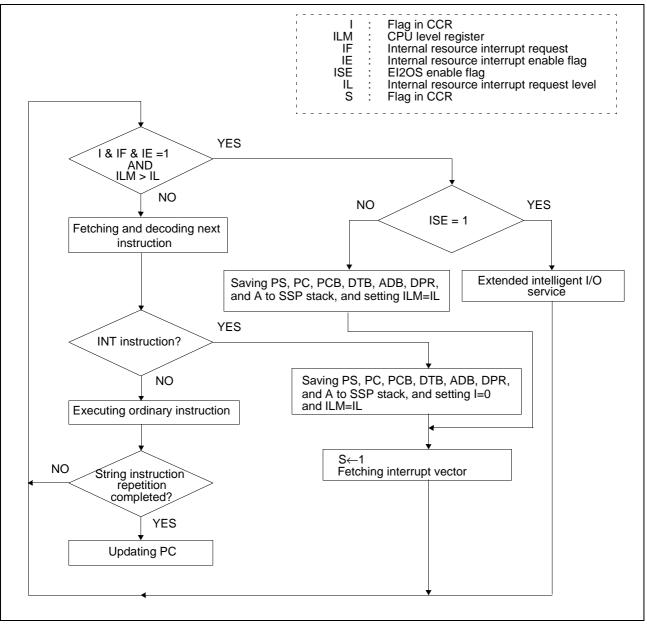

|         |            | 7.4.3 Operation                                                                |     |

|         |            | 7.4.4 Hardware Interrupt Ocurrence When Internal Resource Is Being Accessed    |     |

|         |            | 7.4.5 Interrupt Inhibit Instruction                                            |     |

|         |            | 7.4.6 Multiple Interrupts                                                      |     |

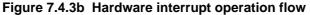

|         |            | 7.4.7 Register Saving In Stack Upon Interrupt                                  |     |

|         |            | 7.4.8 Precaution in Using Hardware Interrupt                                   |     |

|         | 7.5        | 5 Software Interrupt                                                           |     |

|         |            | 7.5.1 Overview                                                                 |     |

|         |            | 7.5.2 Structure                                                                |     |

|         |            | 7.5.3 Operation                                                                | 89  |

|         |            | 7.5.4 Others                                                                   |     |

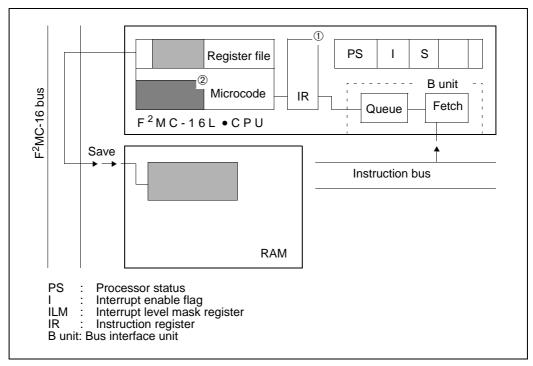

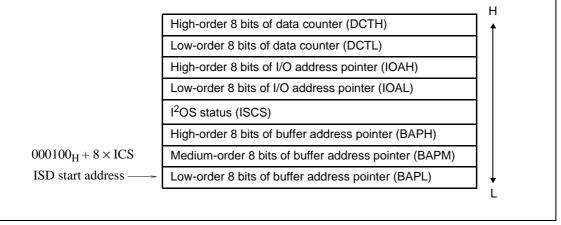

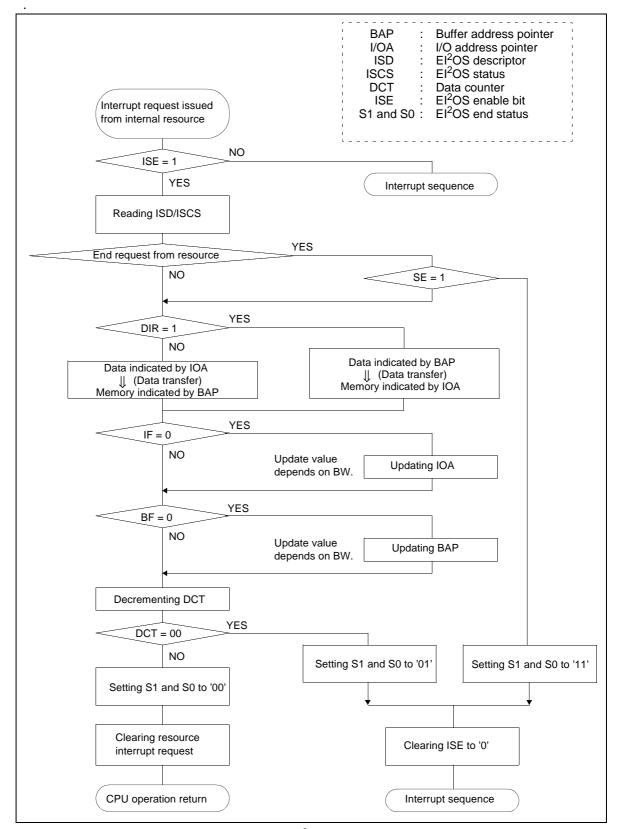

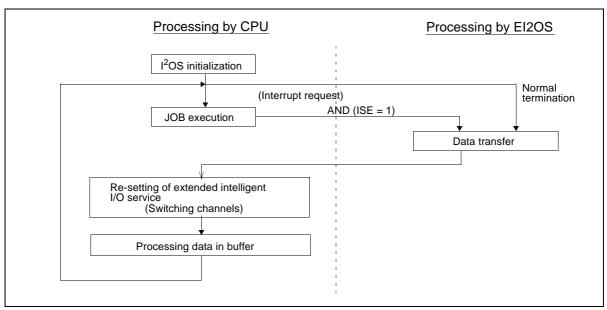

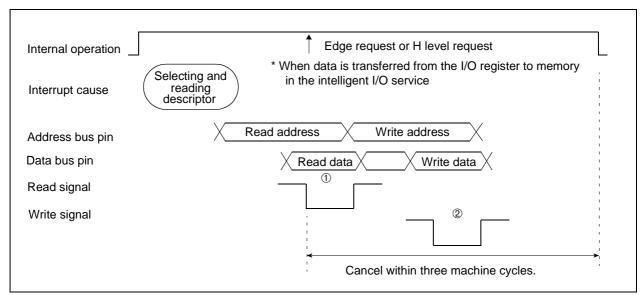

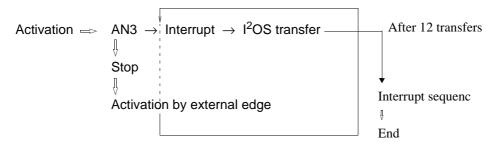

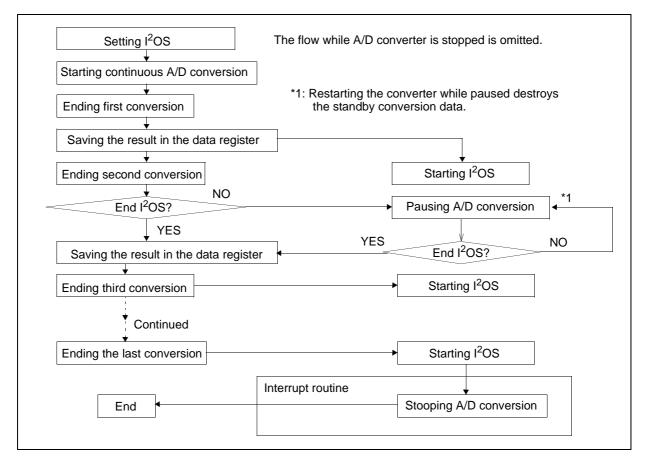

|         | 7.6        | Extended intelligent I/O service (EI2OS)                                       | 90  |

|         |            | 7.6.1 Overview                                                                 |     |

|         |            | 7.6.2 Structure                                                                |     |

|         |            | 7.6.3 Operation                                                                | 97  |

|         |            | 7.6.4 EI2OS Execution Time                                                     | 99  |

|         | 7.7        | ' Exceptions                                                                   | 100 |

|         |            | 7.7.1 Exception due to execution of an undefined instruction                   |     |

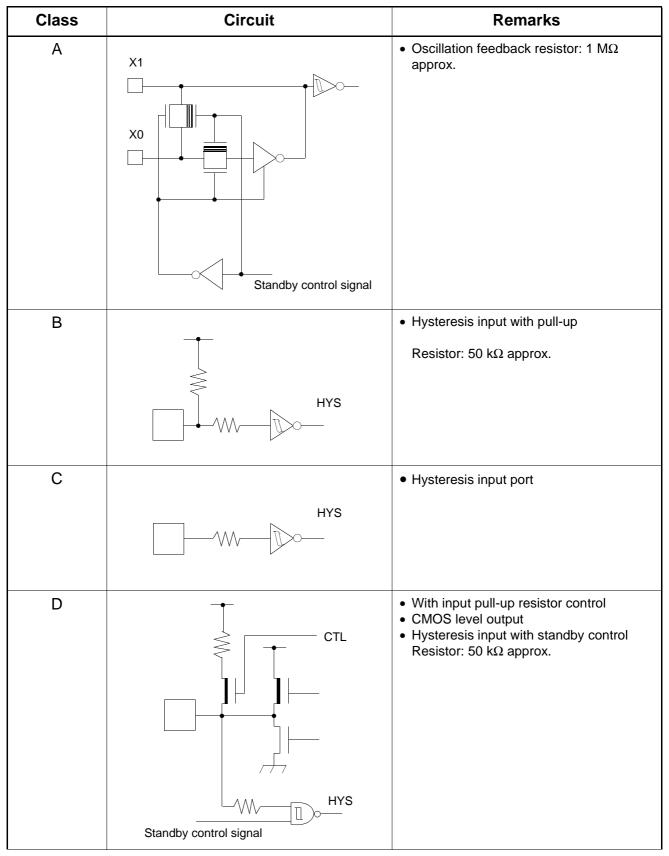

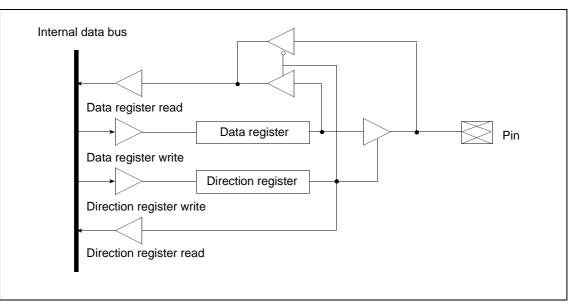

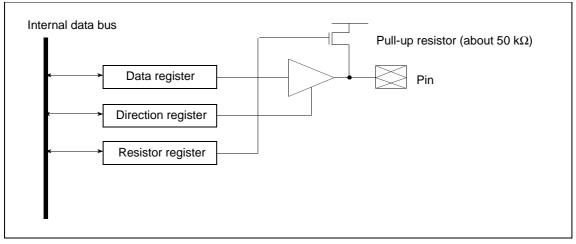

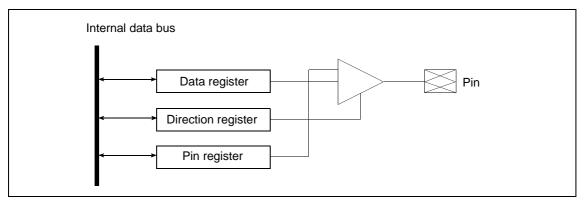

| Chapter | 8 P        | Parallel Ports                                                                 |     |

| enapter |            | Outline                                                                        |     |

|         |            | 2 Block Diagram                                                                |     |

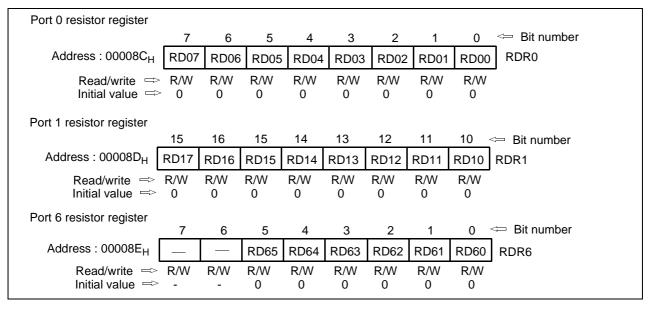

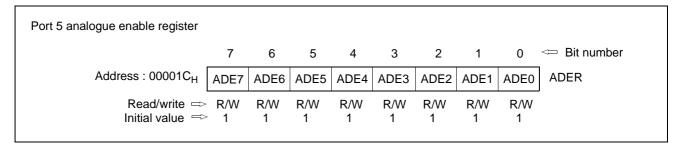

|         |            | <ul> <li>B Registers and register details</li> </ul>                           |     |

|         | 0.0        | 8.3.1 Port data register                                                       |     |

|         |            | 8.3.2 Port direction registers                                                 |     |

|         |            | 8.3.3 Output pin register                                                      |     |

|         |            | 8.3.4 Input resistor register                                                  |     |

|         |            | 8.3.5 Analogue Input Enable Register                                           |     |

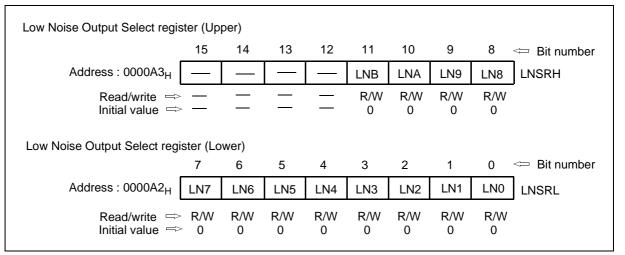

|         |            | 8.3.6 Low Noise Output Select Register                                         |     |

| Chanter | <b>9</b> ח | DTP/External Interrupt                                                         |     |

| Shapter |            | Outline                                                                        |     |

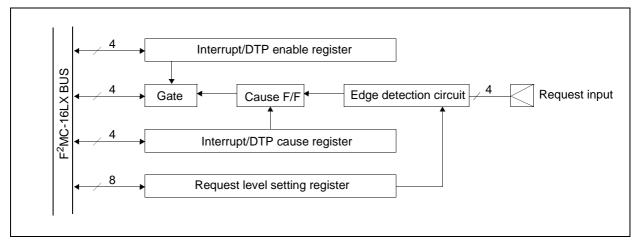

|         |            | 2 Block Diagram                                                                |     |

|         |            | Block Diagram                                                                  |     |

|         | 0.0        | 9.3.1 Interrupt/DTP enable register (ENIR: Enable interrupt request register)  |     |

|         |            | 9.3.2 Interrupt/DTP cause register (EIRR: External interrupt request register) |     |

|         |            | 9.3.3 Request level setting register (ELVR: External level register)           |     |

|         |            |                                                                                |     |

| 9.4 Operations                                                                           | 112 |

|------------------------------------------------------------------------------------------|-----|

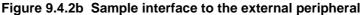

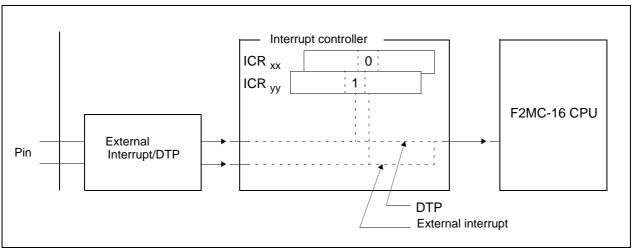

| 9.4.1 External interrupts                                                                | 112 |

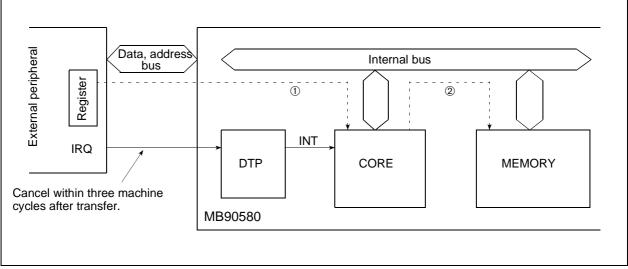

| 9.4.2 DTP operation                                                                      | 113 |

| 9.4.3 Switching between external interrupt and DTP requests                              | 114 |

| 9.5 Notes on use                                                                         | 115 |

| 9.5.1 Conditions on the externally connected peripheral when DTP is used                 | 115 |

| 9.5.2 Recovery from standby                                                              | 115 |

| 9.5.3 External interrupt/DTP operation procedure                                         | 115 |

| 9.5.4 External interrupt request level                                                   | 115 |

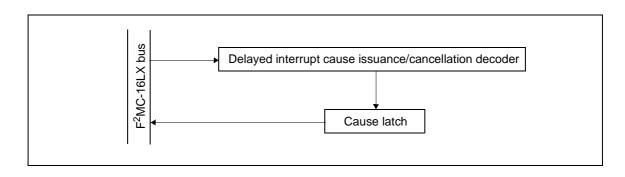

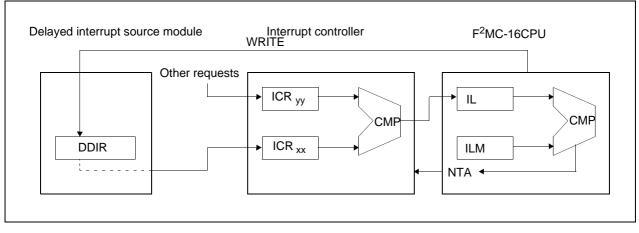

| Chapter 10 Delayed Interrupt Generation Module                                           | 117 |

| 10.1 Outline                                                                             |     |

| 10.2 Block Diagram                                                                       | 117 |

| 10.3 Registers and Register Details                                                      | 117 |

| 10.4 Operations                                                                          | 118 |

| 10.4.1 Delayed interrupt occurrence                                                      | 118 |

| 10.5 Notes on operation                                                                  | 118 |

| 10.5.1 Delayed interrupt request lock                                                    | 118 |

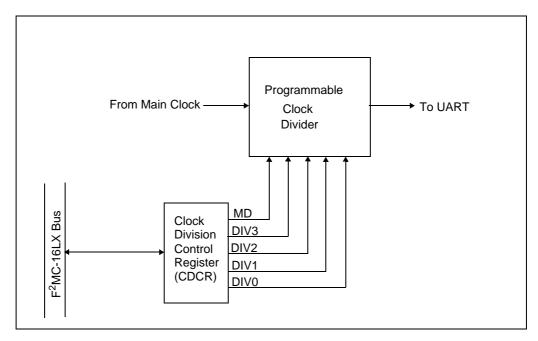

| Chapter 11 Communication Prescaler                                                       | 119 |

| 11.1 Outline                                                                             |     |

| 11.2 Block Diagram                                                                       |     |

| 11.3 Register and Register Details                                                       |     |

| 11.3.1 Clock Division Control Registers                                                  | 120 |

| 11.4 Operations                                                                          | 121 |

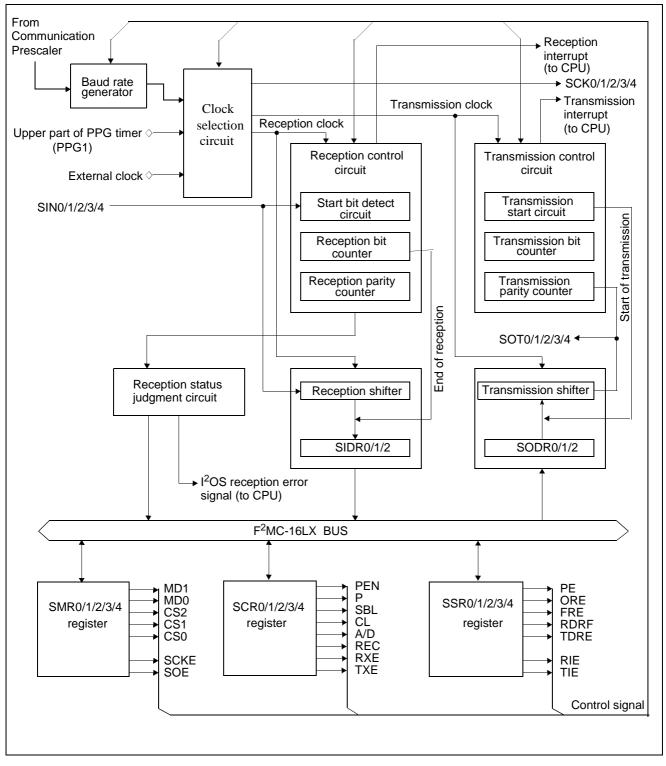

| Chapter 12 UART                                                                          | 123 |

| 12.1 Outline                                                                             |     |

| 12.2 Block Diagram                                                                       |     |

| 12.3 Register and Register Details                                                       |     |

| 12.3.1 Serial Mode Register (SMR0/1/2/3/4)                                               |     |

| 12.3.2 Serial Control Register (SCR0/1/2/3/4)                                            |     |

| 12.3.3 Serial Input Data Register (SIDR0/1/2/3/4)/ Serial Ouput Data Register (SODR0/1/2 |     |

| 12.3.4 Serial Status Register (SSR0/1/2/3/4)                                             | 130 |

| 12.4 Operations                                                                          | 132 |

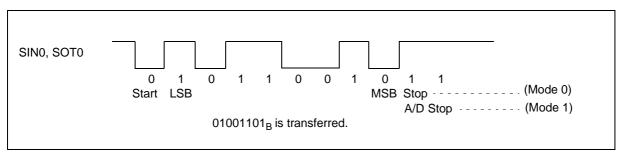

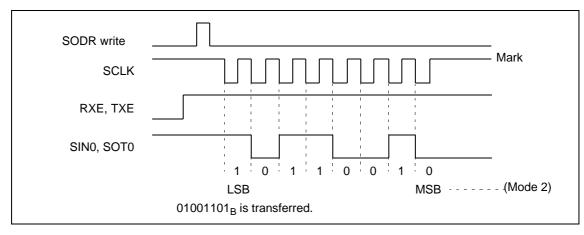

| 12.4.1 Operation modes                                                                   |     |

| 12.4.2 UART clock selection                                                              | 132 |

| 12.4.3 Asynchronous mode                                                                 |     |

| 12.4.4 CLK synchronous mode                                                              |     |

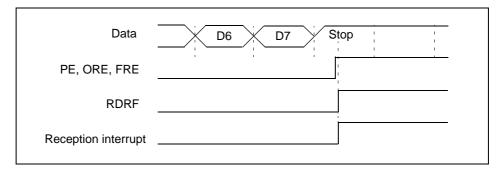

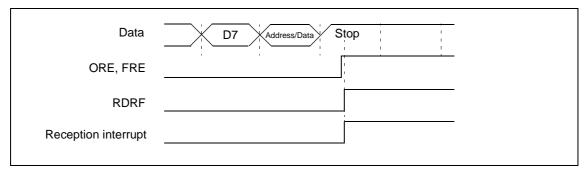

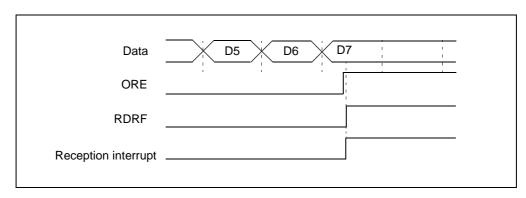

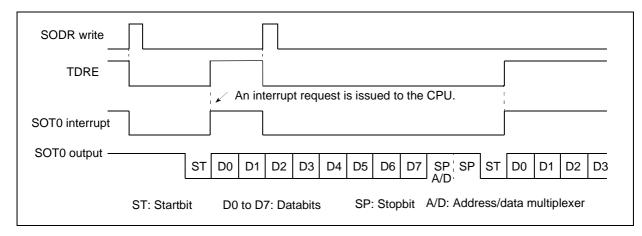

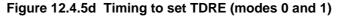

| 12.4.5 Interrupt occurrence and flag set timing                                          |     |

| 12.4.6 I2OS (Intelligent I/O service)                                                    |     |

| 12.4.7 Notes on use                                                                      |     |

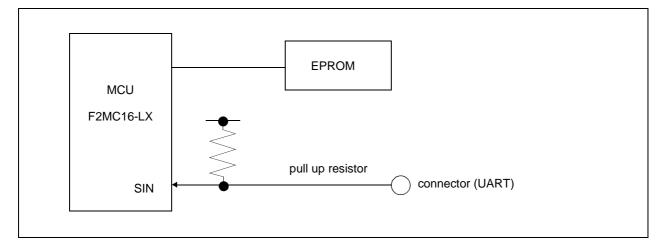

| 12.4.8 Application                                                                       | 139 |

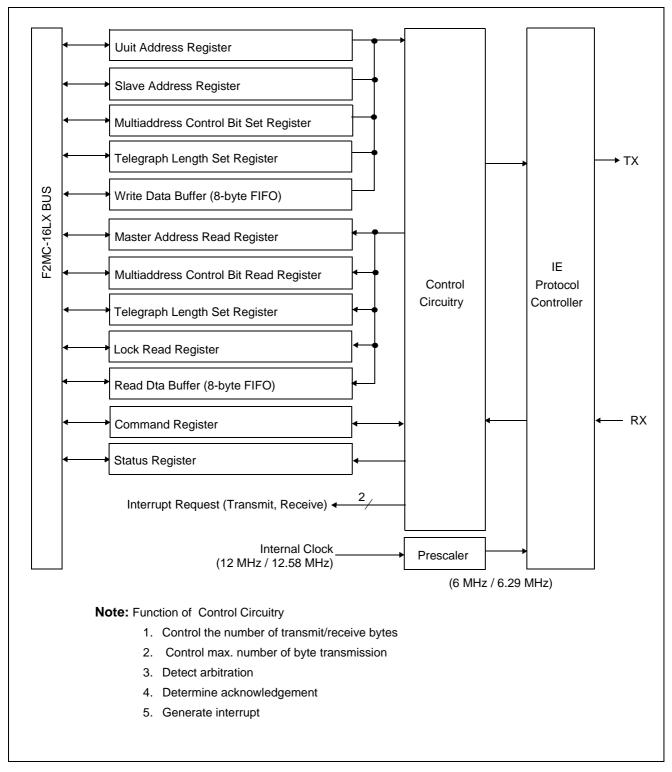

| Chapter 13 IE Bus                                                                        | 141 |

| 13.1 Outline                                                                             |     |

| 13.2 Block Diagram                                                                       |     |

| 13.3 Registers and Register Details                                                      |     |

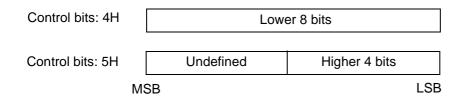

| 13.3.1 Command register upper byte (CMRH)                                                |     |

| 13.3.2 Command register lower byte (CMRL)                                                |     |

| 13.3.3 Unit address register (MAWH, MAWL)                                                |     |

| 13.3.4 Slave address register (SAWH, SAWL)                                               |     |

| 13.3.5 Mutliaddress, control bit set register (DCWR)                                     | 151 |

| <ul> <li>13.3.7 Status register upper byte (STRH)</li> <li>13.3.8 Status register lower byte (STRL)</li> <li>13.3.9 Lock read register (LRRH, LRRL)</li> <li>13.3.10 Master address read register (MARH, MARL)</li> <li>13.3.11 Multiaddress, control bit read register (DCRR)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13.3.9 Lock read register (LRRH, LRRL)<br>13.3.10 Master address read register (MARH, MARL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .153                                                                                                                                                 |

| 13.3.10 Master address read register (MARH, MARL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .155                                                                                                                                                 |

| 13.3.10 Master address read register (MARH, MARL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .157                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                      |

| 19.9.11 WUMAUUE33, CONTO DIL TEAU TEUSIEL (DONN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                      |

| 13.3.12 Telegraph length read register (DERR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                      |

| 13.3.13 Read data buffer (RDB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                      |

| 13.3.14 Write data buffer (WDB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                      |

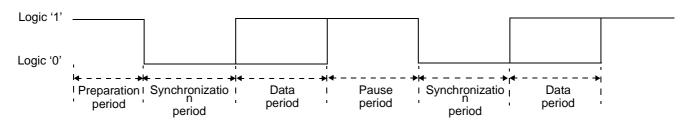

| 13.4 IEBus Communication Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                      |

| 13.4.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                      |

| 13.4.2 Determining bus mastership (arbitration)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                      |

| 13.4.3 Communication mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                      |

| 13.4.4 Communication address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                      |

| 13.4.5 Multiaddress communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                      |

| 13.4.6 Transfer protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                      |

| 13.4.7 Transmit data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                      |

| 13.4.8 Bit format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                      |

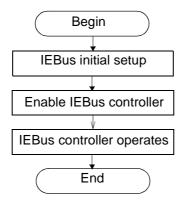

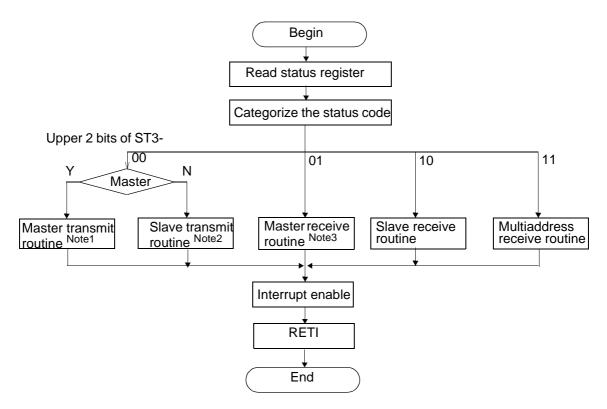

| 13.5 Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                      |

| 13.5.1 IEBus control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                      |

| 13.5.2 Communication status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                      |

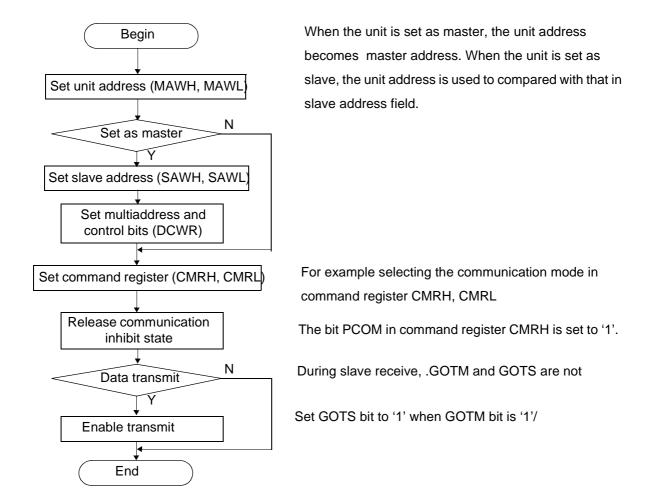

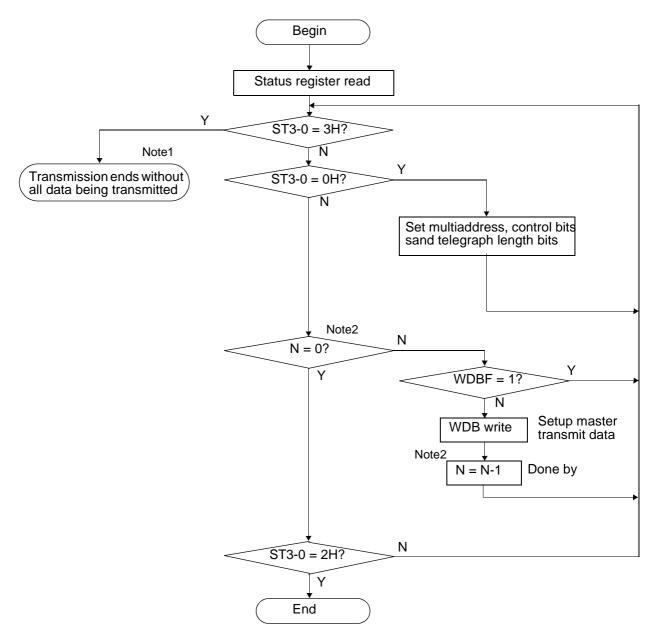

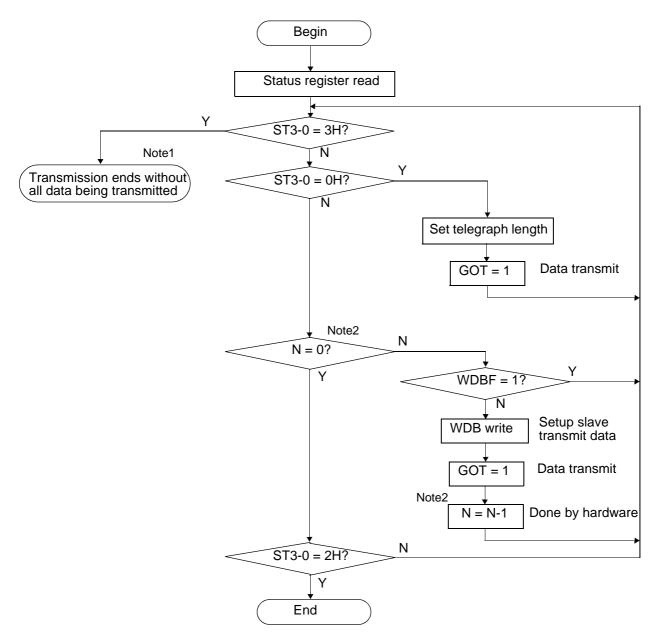

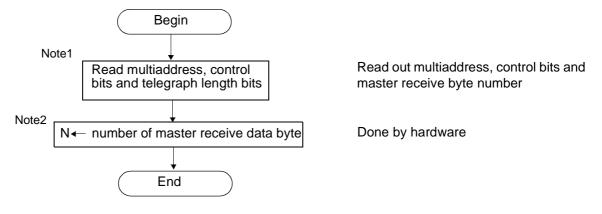

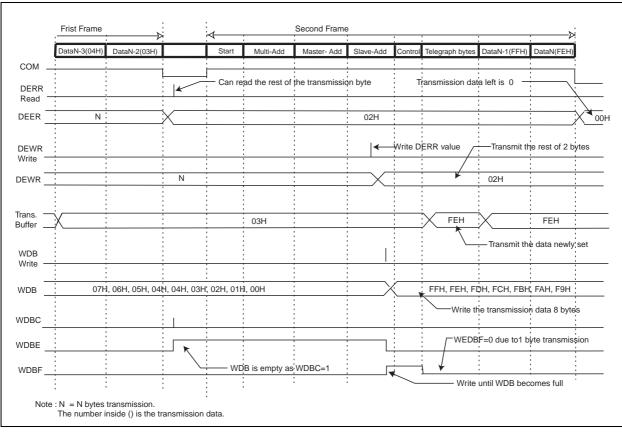

| 13.5.3 Program flow example for IEBus controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                      |

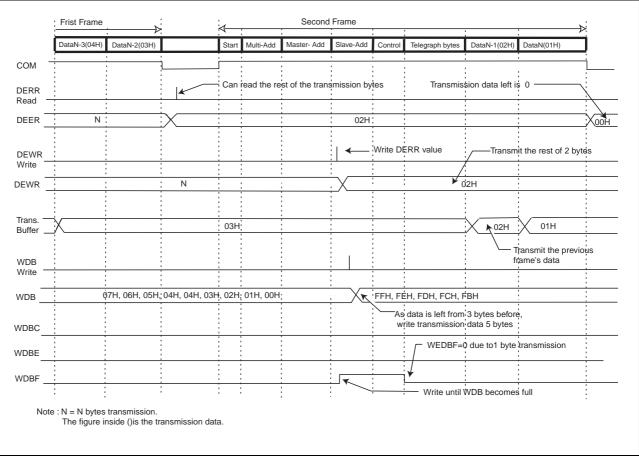

| 13.5.4 Timing Diagram of Multiple Frame Transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                      |

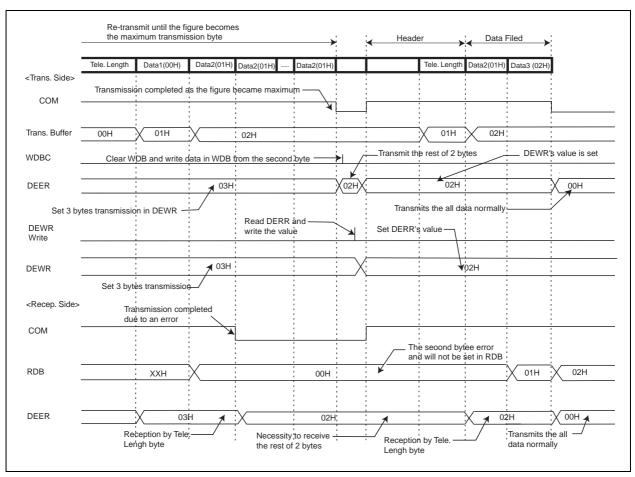

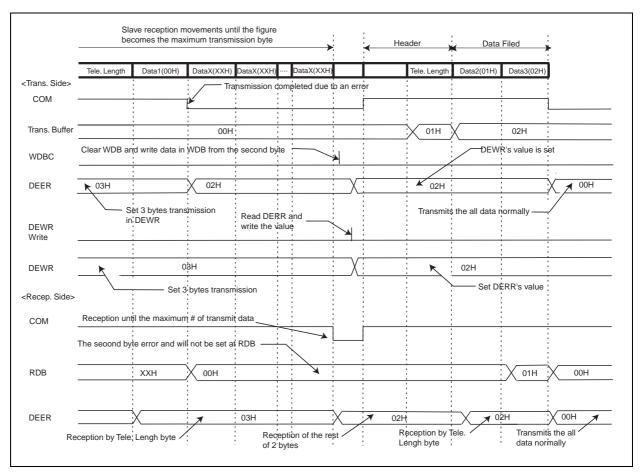

| 13.5.5 Timing diaram of transmission data when an error is generated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                      |

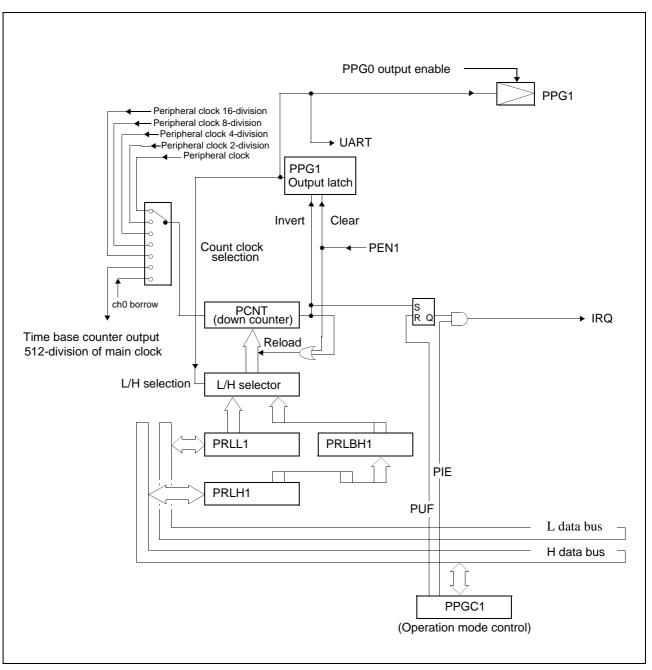

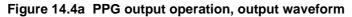

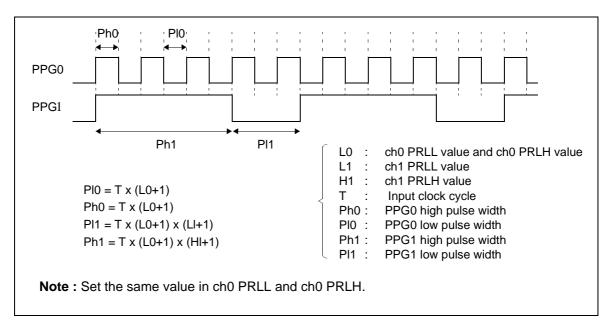

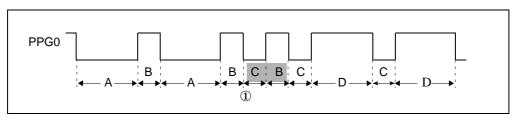

| Chapter 14 8/16-Bit PPG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                      |

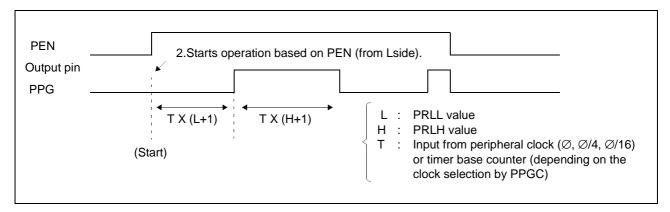

| 14.1 Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                      |

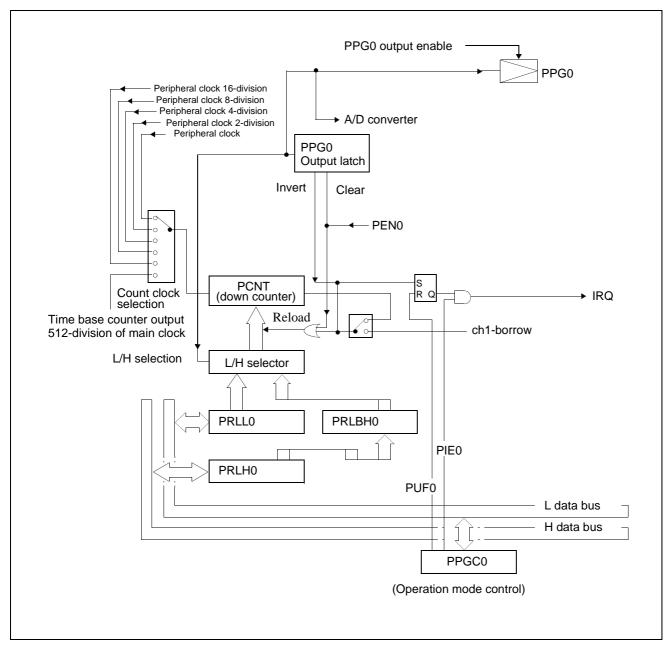

| 14.2 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                      |

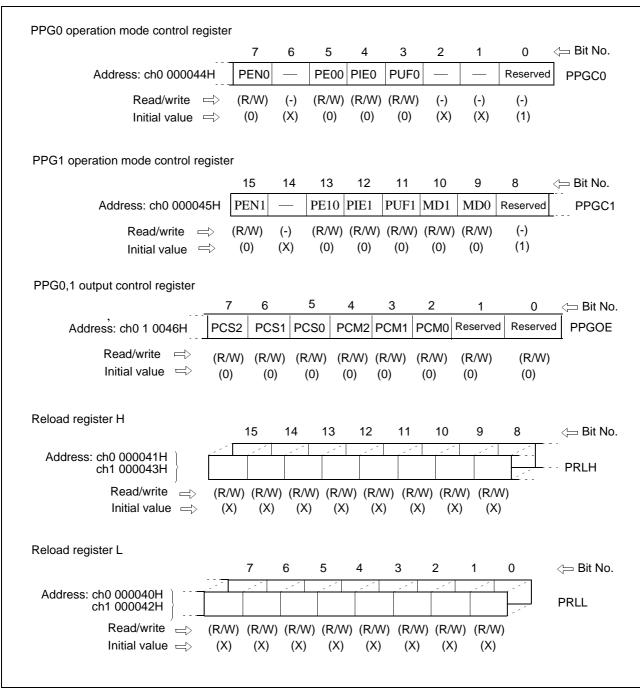

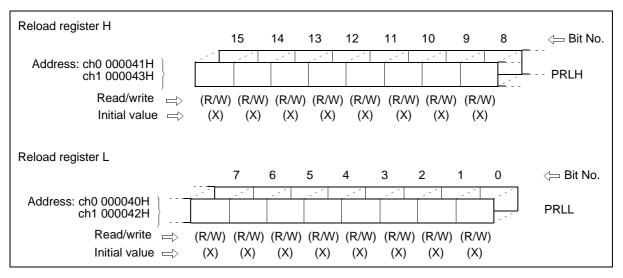

| 14.3 Registers and Register Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                      |

| 14.3.1 PPG0 operation mode control register (PPGC0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                      |

| 14.3.2 PPG1 operation mode control register (PPGC1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .197                                                                                                                                                 |