# LCP1521

A.S.D.™

# PROGRAMMABLE TRANSIENT VOLTAGE SUPPRESSOR FOR SLIC PROTECTION

#### **FEATURES**

- Dual programmable transient suppressor

- Wide negative firing voltage range: V<sub>MGL</sub> = -150 V max.

- Low dynamic switching voltages: V<sub>FP</sub> and V<sub>DGL</sub>

- Low gate triggering current: I<sub>GT</sub> = 5 mA max

- Peak pulse current: I<sub>PP</sub> = 30 A (10/1000 μs)

- Holding current: I<sub>H</sub> = 150 mA min

This device has been especially designed to protect new high voltage, as well as classical SLICs, against transient overvoltages.

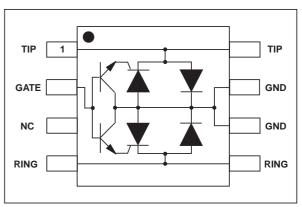

Positive overvoltages are clamped by 2 diodes. Negative surges are suppressed by 2 thyristors, their breakdown voltage being referenced to  $\text{-V}_{\text{BAT}}$  through the gate.

This component presents a very low gate triggering current ( $I_{GT}$ ) in order to reduce the current consumption on printed circuit board during the firing phase.

A particular attention has been given to the internal wire bonding. The Kelvin method configuration ensures reliable protection, reducing the overvoltage introduced by the parasitic inductances of the wiring, especially for very fast transients.

#### **BENEFITS**

Trisils are not subject to ageing and provide a fail safe mode in short circuit for a better protection. Trisils are used to help equipment to meet various standards such as UL1950, IEC950 / CSA C22.2, UL1459 and FCC part68. Trisils have UL94 V0 resin approved (Trisils are UL497B approved (file: E136224)).

#### **FUNCTIONAL DIAGRAM**

January 2002 - Ed: 3B 1/9

# IN COMPLIANCES WITH THE FOLLOWING STANDARDS

| STANDARD                            | Peak Surge<br>Voltage<br>(V) | Voltage<br>Waveform  | Required peak current (A) | Current<br>Waveform  | $\begin{array}{c} \textbf{Minimum serial} \\ \textbf{resistor to meet} \\ \textbf{standard } (\Omega) \end{array}$ |

|-------------------------------------|------------------------------|----------------------|---------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------|

| GR-1089 Core<br>First level         | 2500<br>1000                 | 2/10µs<br>10/1000µs  | 500<br>100                | 2/10µs<br>10/1000µs  | 10<br>24                                                                                                           |

| GR-1089 Core<br>Second level        | 5000                         | 2/10µs               | 500                       | 2/10µs               | 20                                                                                                                 |

| GR-1089 Core<br>Intra-building      | 1500                         | 2/10µs               | 100                       | 2/10µs               | 0                                                                                                                  |

| ITU-T-K20/K21                       | 6000<br>1500                 | 10/700µs             | 150<br>37.5               | 5/310µs              | 110<br>0                                                                                                           |

| ITU-T-K20<br>(IEC61000-4-2)         | 8000<br>15000                | 1/60 ns              | ESD contact<br>ESD air di |                      | 0                                                                                                                  |

| VDE0433                             | 4000<br>2000                 | 10/700µs             | 100<br>50                 | 5/310µs              | 60<br>10                                                                                                           |

| VDE0878                             | 4000<br>2000                 | 1.2/50µs             | 100<br>50                 | 1/20µs               | 0                                                                                                                  |

| IEC61000-4-5                        | 4000<br>4000                 | 10/700µs<br>1.2/50µs | 100<br>100                | 5/310µs<br>8/20µs    | 60<br>0                                                                                                            |

| FCC Part 68, lightning surge type A | 1500<br>800                  | 10/160µs<br>10/560µs | 200<br>100                | 10/160µs<br>10/560µs | 22.5<br>15                                                                                                         |

| FCC Part 68, lightning surge type B | 1000                         | 9/720µs              | 25                        | 5/320µs              | 0                                                                                                                  |

# THERMAL RESISTANCE

| Symbol    | Parameter           | Value | Unit |

|-----------|---------------------|-------|------|

| Rth (j-a) | Junction to ambient | 170   | °C/W |

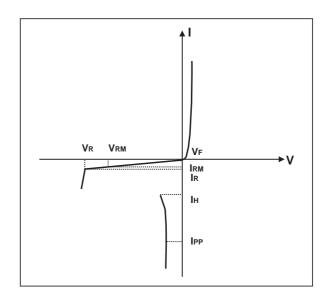

# **ELECTRICAL CHARACTERISTICS** (T<sub>amb</sub> = 25°C)

| Symbol            | Parameter                             |

|-------------------|---------------------------------------|

| I <sub>GT</sub>   | Gate triggering current               |

| lΗ                | Holding current                       |

| I <sub>RM</sub>   | Reverse leakage current LINE / GND    |

| I <sub>RG</sub>   | Reverse leakage current GATE / LINE   |

| $V_{RM}$          | Reverse voltage LINE / GND            |

| V <sub>GT</sub>   | Gate triggering voltage               |

| V <sub>F</sub>    | Forward drop voltage LINE / GND       |

| V <sub>FP</sub>   | Peak forward voltage LINE / GND       |

| $V_{DGL}$         | Dynamic switching voltage GATE / LINE |

| V <sub>GATE</sub> | GATE / GND voltage                    |

| V <sub>RG</sub>   | Reverse voltage GATE / LINE           |

| С                 | Capacitance LINE / GND                |

2/9

# **ABSOLUTE RATINGS** (T<sub>amb</sub> = 25°C, unless otherwise specified).

| Symbol                               | Parameter                                                    |                                                                            | Value                              | Unit |

|--------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------|------|

| Ірр                                  | Peak pulse current (see note1)                               | 10/1000μs<br>8/20μs<br>10/560μs<br>5/310μs<br>10/160μs<br>1/20μs<br>2/10μs | 30<br>100<br>35<br>40<br>50<br>100 | А    |

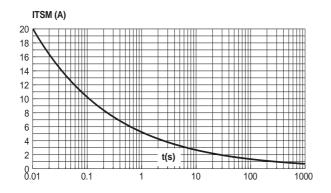

| I <sub>TSM</sub>                     | Non repetitive surge peak on-state current (50Hz sinusoidal) | t = 10ms<br>t = 1s                                                         | 20<br>5                            | А    |

| I <sub>GSM</sub>                     | Maximum gate current (50Hz sinusoidal)                       | 2                                                                          | Α                                  |      |

| V <sub>MLG</sub><br>V <sub>MGL</sub> | Maximum voltage LINE/GND<br>Maximum voltage GATE/LINE        | -150<br>-150                                                               | V                                  |      |

| T <sub>stg</sub><br>Tj               | Storage temperature range<br>Maximum junction temperature    | - 55 to + 150<br>150                                                       | °C                                 |      |

| TL                                   | Maximum lead temperature for solde                           | ering during 10s                                                           | 260                                | °C   |

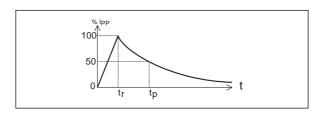

# Repetitive peak pulse current

tr: rise time (µs)

tp: pulse duration (µs) ex: Pulse waveform 10/1000µs

$tr = 10 \mu s$   $tp = 1000 \mu s$

# 1- PARAMETERS RELATED TO THE DIODE LINE / GND $(T_{amb} = 25$ °C)

| Symbol                   |                                | Test conditi            | Max                                                | Unit         |   |

|--------------------------|--------------------------------|-------------------------|----------------------------------------------------|--------------|---|

| V <sub>F</sub>           | I <sub>F</sub> = 5A            |                         | t = 500µs                                          | 2            | V |

| V <sub>FP</sub> (note 1) | 10/700μs<br>1.2/50μs<br>2/10μs | 1.5kV<br>1.5kV<br>2.5kV | $R_s = 10\Omega$ $R_s = 10\Omega$ $R_s = 62\Omega$ | 5<br>7<br>12 | V |

Note 1: see test circuit for VFP; Rs is the protection resistor located on the line card.

# 2 - PARAMETERS RELATED TO THE PROTECTION THYRISTOR (Tamb = 25°C unless otherwise specified)

| Symbol           | Test conditions                                                                                                                                               | Min                                                | Max | Unit          |    |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----|---------------|----|

| I <sub>GT</sub>  | $V_{GND/LINE} = -48V$                                                                                                                                         |                                                    | 0.1 | 5             | mA |

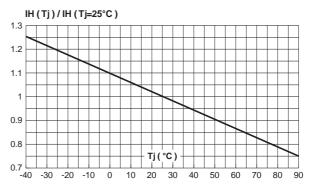

| lΗ               | V <sub>GATE</sub> = -48V (note 2)                                                                                                                             |                                                    | 150 |               | mA |

| V <sub>GT</sub>  | at I <sub>GT</sub>                                                                                                                                            |                                                    |     | 2.5           | V  |

| I <sub>RG</sub>  | $V_{RG} = -150V$<br>$V_{RG} = -150V$                                                                                                                          | Tc=25°C<br>Tc=85°C                                 |     | 5<br>50       | μA |

| V <sub>DGL</sub> | V <sub>GATE</sub> = -48V (note 3)                                                                                                                             |                                                    |     |               |    |

|                  | $\begin{array}{cccc} 10/700 \mu s & 1.5 kV & R_s = 10 \Omega \\ 1.2/50 \mu s & 1.5 kV & R_s = 10 \Omega \\ 2/10 \mu s & 2.5 kV & R_s = 62 \Omega \end{array}$ | $I_{PP} = 30A$<br>$I_{PP} = 30A$<br>$I_{PP} = 38A$ |     | 7<br>10<br>25 | V  |

Note 2: see functional holding current (I<sub>H</sub>) test circuit

Note 3: see test circuit for VDGL

The oscillations with a time duration lower than 50ns are not taken into account

# **3 - PARAMETERS RELATED TO DIODE AND PROTECTION THYRISTOR** ( $T_{amb} = 25$ °C, unless otherwise specified)

| Symbol          | Test conditions                                                                                           | Тур.               | Max.     | Unit    |    |

|-----------------|-----------------------------------------------------------------------------------------------------------|--------------------|----------|---------|----|

| I <sub>RM</sub> | $V_{\text{GATE/LINE}} = -1V$ $V_{\text{RM}} = -150V$ $V_{\text{GATE/LINE}} = -1V$ $V_{\text{RM}} = -150V$ | Tc=25°C<br>Tc=85°C |          | 5<br>50 | μΑ |

| С               | $V_R = 50V$ bias, $V_{RMS} = 1V$ , $F = 1MHz$<br>$V_R = 2V$ bias, $V_{RMS} = 1V$ , $F = 1MHz$             |                    | 30<br>70 |         | pF |

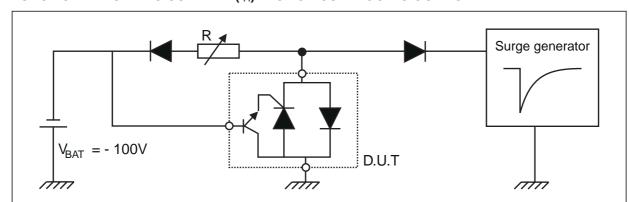

# FUNCTIONAL HOLDING CURRENT ( $I_H$ ) TEST CIRCUIT : GO-NO GO TEST

This is a GO-NO GO test which allows to confirm the holding current (I<sub>H</sub>) level in a functional test circuit.

#### **TEST PROCEDURE:**

- Adjust the current level at the  $I_H$  value by short circuiting the D.U.T. Fire the D.U.T. with a surge current :  $I_{PP}$  = 10A, 10/1000 $\mu s$ .

- The D.U.T. will come back to the off-state within a duration of 50ms max.

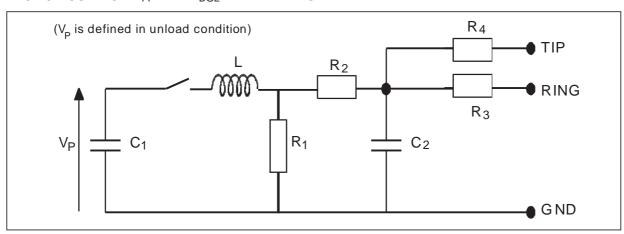

#### TEST CIRCUIT FOR V<sub>FP</sub> AND V<sub>DGL</sub> PARAMETERS

| Pulse          | e (µs) | Vp   | C <sub>1</sub> | C <sub>2</sub> | L    | R <sub>1</sub> | R <sub>2</sub> | R <sub>3</sub> | R <sub>4</sub> | IPP | Rs         |

|----------------|--------|------|----------------|----------------|------|----------------|----------------|----------------|----------------|-----|------------|

| t <sub>r</sub> | tp     | (V)  | (μF)           | (nF)           | (μH) | $(\Omega)$     | $(\Omega)$     | $(\Omega)$     | $(\Omega)$     | (A) | $(\Omega)$ |

| 10             | 700    | 1500 | 20             | 200            | 0    | 50             | 15             | 25             | 25             | 30  | 10         |

| 1.2            | 50     | 1500 | 1              | 33             | 0    | 76             | 13             | 25             | 25             | 30  | 10         |

| 2              | 10     | 2500 | 10             | 0              | 1.1  | 1.3            | 0              | 3              | 3              | 38  | 62         |

#### **TECHNICAL INFORMATION**

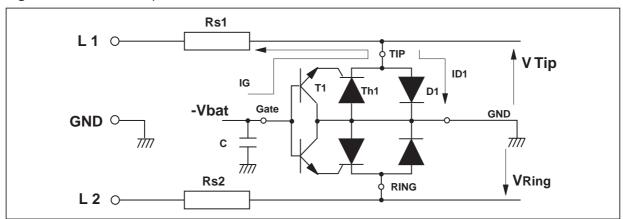

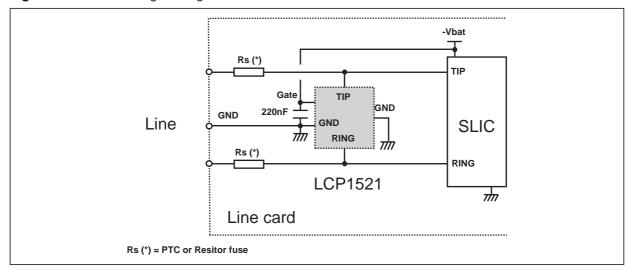

Fig. A1: LCP1521 concept behavior.

Figure A1 shows the classical protection circuit using the LCP1521 crowbar concept. This topology has been developed to protect the new high voltage SLIC's. It allows to program the negative firing threshold while the positive clamping value is fixed at GND.

When a negative surge occurs on one wire (L1 for example) a current IG flows through the base of the transistor T1 and then injects a current in the gate of the thyristor Th1. Th1 fires and all the surge current flows through the ground. After the surge when the current flowing through Th1 becomes less negative than the holding current I<sub>H</sub>, then Th1 switches off.

When a positive surge occurs on one wire (L1 for example) the diode D1 conducts and the surge current flows through the ground.

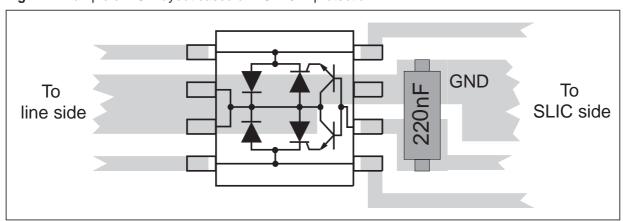

Fig. A2: Example of PCB layout based on LCP1521 protection.

In order to minimize the remaining voltage across the SLIC inputs during the surge, the TIP and RING pins of the LCP1521 are doubled (Pins 1 and 8 for TIP / Pins 4 and 5 for RING).

This fact allows the board designer to connect the tracks like in figure A2. With such a PCB design, the extra voltages caused by track stray inductance remain located on the line side of the LCP and do not affects the SLIC side.

The capacitor C is used to speed up the crowbar structure firing during the fast surge edges.

This allows to minimize the dynamical breakover voltage at the SLIC Tip and Ring inputs during fast strikes. Note that this capacitor is generally present around the SLIC - Vbat pin.

So to be efficient it has to be as close as possible from the LCP1521 Gate pin and from the reference ground track (or plan) (see Fig. A2). The optimized value for C is 220nF.

5//

The series resitors Rs1 and Rs2 designed in figure A1 represent the fuse resistors or the PTC which are mandatory to withstand the power contact or the power induction tests imposed by the various country standards. Taking into account this fact the actual lightning surge current flowing through the LCP is equal to:

I surge =

$$V surge / (Rg + Rs)$$

With V surge = peak surge voltage imposed by the standard.

Rg = series resistor of the surge generator

Rs = series resistor of the line card (e.g. PTC)

e.g. For a line card with  $30\Omega$  of series resistors which has to be qualified under GR1089 Core 1000V  $10/1000\mu s$  surge, the actual current through the LCP1521 is equal to:

I surge =

$$1000 / (10 + 30) = 25A$$

The LCP1521 is particularly optimized for the new telecom applications such as the fiber in the loop, the WLL, the remote central office. In this case, the operating voltages are smaller than in the classical system. This makes the high voltage SLICs particularly suitable. The schematics of figure A3 gives the most frequent topology used for these applications.

Fig. A3: Protection of high voltage SLIC.

Fig. 1: Surge peak current versus overload duration.

**Fig. 2:** Relative variation of holding current versus junction temperature

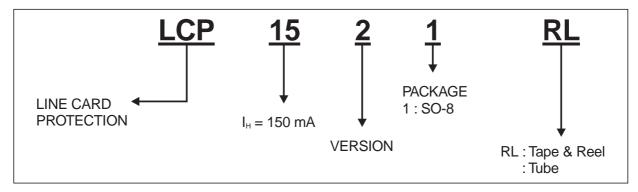

#### **ORDER CODE**

57

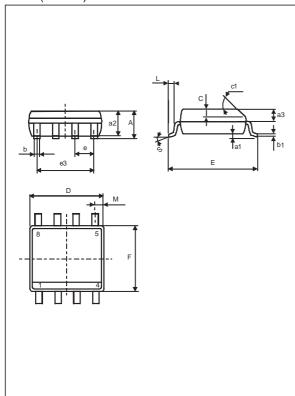

#### **PACKAGE MECHANICAL DATA**

SO-8 (Plastic)

|      |      |         | DIMEN | SIONS  |       |       |  |

|------|------|---------|-------|--------|-------|-------|--|

| REF. | Mi   | llimetr | es    | Inches |       |       |  |

|      | Min. | Тур.    | Max.  | Min.   | Тур.  | Max.  |  |

| Α    |      |         | 1.75  |        |       | 0.069 |  |

| a1   | 0.1  |         | 0.25  | 0.004  |       | 0.010 |  |

| a2   |      |         | 1.65  |        |       | 0.065 |  |

| а3   | 0.65 |         | 0.85  | 0.025  |       | 0.033 |  |

| b    | 0.35 |         | 0.48  | 0.014  |       | 0.019 |  |

| b1   | 0.19 |         | 0.25  | 0.007  |       | 0.010 |  |

| С    | 0.25 | 0.50    | 0.50  | 0.010  |       | 0.020 |  |

| c1   |      |         | 45°   | (typ)  |       |       |  |

| D    | 4.8  |         | 5.0   | 0.189  |       | 0.197 |  |

| E    | 5.8  |         | 6.2   | 0.228  |       | 0.244 |  |

| е    |      | 1.27    |       |        | 0.050 |       |  |

| e3   |      | 3.81    |       |        | 0.150 |       |  |

| F    | 3.8  |         | 4.0   | 0.15   |       | 0.157 |  |

| L    | 0.4  |         | 1.27  | 0.016  |       | 0.050 |  |

| М    |      |         | 0.6   |        |       | 0.024 |  |

| S    |      |         | 8° (r | max)   |       |       |  |

| Order code | Marking | Package | Weight | Base qty | Delivery mode |

|------------|---------|---------|--------|----------|---------------|

| LCP1521    | 151DHV  | SO-8    | 0.08 g | 100      | Tube          |

| LCP1521RL  | 151DHV  | SO-8    | 0.08 g | 2000     | Tape & Reel   |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied.

STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

© 2002 STMicroelectronics - Printed in Italy - All rights reserved.

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - Finland - France - Germany Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore

Spain - Sweden - Switzerland - United Kingdom - United States.

http://www.st.com