# International Rectifier

# **IR1110**

# SOFT START CONTROLLER IC

#### **Features**

- Self-contained soft charging of DC bus capacitor

- DC bus voltage regulation

- 3-phase or 1-phase AC input

- Applicable to 115/230/380/460/575V AC input

- Drives SCR phase controlled half bridge

- Programmable ramp rate

- Protection against DC bus short circuit

- Fast power dip ride through with automatic ramp back

- Selectable shutdown on single phase loss

- 1-phase and 3-phase loss fault output

- Insensitive to phase rotation

- High line or low line fault output

- Low power consumption

- Integrated watchdog function for each phase

- 64-pin MQFP package

# **Description**

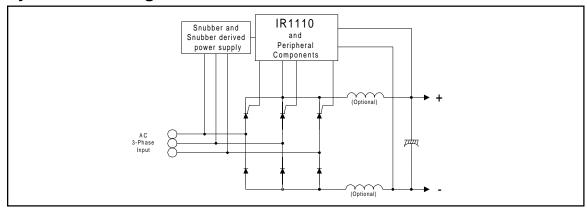

The IR1110 is a high performance analog IC designed to control ramp rate and voltage of the DC bus from either single or three phase AC line voltage input. It controls a SCR half bridge and provides robust ride through capability in event of transient loss of line, and DC bus regulation with eternal reference input. Comprehensive line status fault output including 1/3 phase loss and high or low line fault provides versatile line diagnostic capability to the system. The IR1110 is based on advanced low power design so it can utilize the SCR snubber derived power supply.

## **Product Summary**

V<sub>DDS</sub>/V<sub>SS</sub> +/- 5V

I<sub>SS</sub>/I<sub>DD</sub> +/- 5mA

DC bus registration 100msec (typ.) response time

Min. DC bus regulation 35% of V<sub>DCMAX</sub> voltage with capacitive load

Programmable 100msec to DC bus ramp time 330msec (typ.)

# **Typical Application**

- Motor drives

- Welders

- Battery chargers

- Power supplies

# **Package**

# System Block Diagram

# **IR1110**

International

TOR Rectifier

# **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to AGND and DGND, all currents are defined positive into any lead. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

| Symbol             | Definition                                                 | Min.             | Max.                    | Units |

|--------------------|------------------------------------------------------------|------------------|-------------------------|-------|

| V <sub>DD</sub>    | Positive supply voltage                                    | _                | 6.0                     |       |

| V <sub>SS</sub>    | Negative supply voltage                                    | _                | -6.0                    |       |

| V <sub>IN</sub>    | Operating input voltage range on UIN,VIN & WIN pins        | $(V_{SS} + 0.4)$ | (V <sub>DD</sub> - 0.4) |       |

| V <sub>BIN</sub>   | Operating input voltage on VBOS and VBNEG                  | - 4.5            | 3.0                     | V     |

| V <sub>LED</sub>   | Operating input voltage on 1PHLED, LNLED, and LNLSLED pins | _                | $V_{DD}$                |       |

| V <sub>LNSET</sub> | Operating input voltage on LNSET                           | _                | (V <sub>DD</sub> - 0.4) |       |

| I <sub>LED</sub>   | Sinking current on 1PHLED, LNLED, and LNLSLED pins         | _                | 3                       | mA    |

| RthJA              | Thermal resistance, junction to ambient                    | _                | 60                      | °C/W  |

| T <sub>A</sub>     | Operating ambient temperature                              | -40              | 85                      |       |

| TJ                 | Junction temperature                                       | _                | 150                     | °C    |

| T <sub>S</sub>     | Storage temperature                                        | -55              | 150                     | 3     |

| TL                 | Lead temperature (soldering, 10 seconds)                   | _                | 300                     |       |

# **Recommended Component Values**

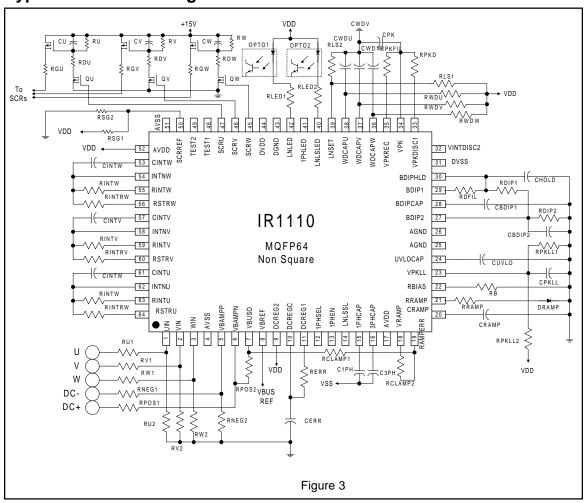

All capacitors are rated 6.3V unless otherwise specified. All resistors are rated 1/16W unless otherwise specified. The typical connection diagram is shown in figure 3. For proper operation the device should be used with the recommended components specified below.

| Symbol              | Definition                         | Тур.    | Tolerance | Units | Comments      |

|---------------------|------------------------------------|---------|-----------|-------|---------------|

| QU                  | Phase U/V/W complementary MOSFET   | IRF7509 |           |       | Complementary |

| Q <sub>V</sub>      |                                    |         |           |       | NMOS/PMOS     |

| QW                  |                                    |         |           |       | Driver        |

| R <sub>U1</sub>     | Resistor divider for input voltage | 3.4 X   | 1%        | kΩ    | Note 1        |

| R <sub>V1</sub>     |                                    | VACrms  | .25W      |       |               |

| R <sub>W1</sub>     |                                    | max     |           |       |               |

| R <sub>B</sub>      | Bias resistor                      | 249k    | 1%        |       |               |

| R <sub>U2</sub>     | Resistor divider for input voltage | 9.09k   | 1%        |       |               |

| R <sub>V2</sub>     |                                    |         |           |       |               |

| R <sub>W2</sub>     |                                    |         |           | Ω     |               |

| R <sub>ERR</sub>    | DC bus regulation error resistor   | 2M      | 5%        | •     |               |

| R <sub>CLAMP1</sub> | Ramp clamp resistor 1              | 430k    | 5%        |       |               |

| R <sub>CLAMP2</sub> | Ramp clamp resistor 2              | 100k    | 5%        |       |               |

| R <sub>RAMP</sub>   | Ramp resistor                      | 82k     | 5%        | •     |               |

# **Recommended Operating Conditions cont.**

All capacitors are rated 6.3V unless otherwise specified. All resistors are rated 1/16W unless otherwise specified. The typical connection diagram is shown in figure 3. For proper operation the device should be used with the recommended components specified below.

| Symbol                                         | Definition                                     | Тур.      | Tolerance | Units | Comments |

|------------------------------------------------|------------------------------------------------|-----------|-----------|-------|----------|

| R <sub>PKLL1</sub>                             | Line voltage peak holding resistor 1           | 2.2M      | 5%        |       |          |

| R <sub>PKLL2</sub>                             | Line voltage peak holding resistor 2           | 6.8M      | 5%        | 0     |          |

| R <sub>DIP1</sub>                              | Voltage dip resistor 1                         | 332k      | 1%        | Ω     |          |

| R <sub>DIP2</sub>                              | Voltage dip resistor 2                         | 1.0M      | 1%        |       |          |

| R <sub>DFIL</sub>                              | Voltage dip filter resistor                    | 15k       | 5%        |       |          |

| R <sub>PKD</sub>                               | Timing wave peak voltage discharge resisto     | r 1M      | 5%        |       |          |

| R <sub>PKFIL</sub>                             | Timing wave peak voltage filter resistor       | 56k       | 5%        | •     |          |

| R <sub>POS1</sub>                              | Resistor divider for DC bus voltage input      | 3.2 X     | 1%        | kΩ    | Note 1,2 |

| R <sub>NEG1</sub>                              |                                                | VACrmsmax | .5W       |       |          |

| R <sub>POS2</sub>                              | Feedback resistor for DC bus voltage Amp       | 9.09k     | 1%        |       |          |

| R <sub>NEG2</sub>                              | Resistor divider for DC bus voltage            | 9.09k     | 1%        |       |          |

| R <sub>WDU</sub>                               | Phase U/V/W watchdog resistor                  | 845k      | 1%        |       | Note 3   |

| $R_{WDV}$                                      |                                                |           |           |       |          |

| RWDW                                           |                                                |           |           |       |          |

| R <sub>LS1</sub>                               | Line fault output reference divider resistor 1 | 357k      | 1%        |       |          |

| R <sub>LS2</sub>                               | Line fault output reference divider resistor 2 | 78.7k     | 1%        |       |          |

| R <sub>SG1</sub>                               | SCR firing anode voltage reference resistor 1  | 0.82k X   | 1%        |       | Note 4   |

|                                                |                                                | VACrmsmax |           |       |          |

| R <sub>SG2</sub>                               | SCR firing anode voltage reference resistor 2  | 10k       | 1%        |       |          |

| R <sub>INTU</sub>                              | Phase U/V/W integrator resistor                | 1M        | 1%        |       |          |

| $R_{INTV}$                                     |                                                |           |           | Ω     |          |

| RINTW                                          |                                                |           |           |       |          |

| R <sub>INTRU</sub>                             | Phase U/V/W integrator reset resistor          | 33.2k     | 1%        |       |          |

| R <sub>INTRV</sub>                             |                                                |           |           |       |          |

| R <sub>INTRW</sub>                             |                                                |           |           |       |          |

| R <sub>LED1</sub>                              | LNLSLED pin resistor for opto interface        | 6.2k      | 5%        |       |          |

| R <sub>LED2</sub>                              | LNLED pin resistor for opto interface          | 6.2k      | 5%        |       |          |

| R <sub>U,</sub> R <sub>V,</sub> R <sub>W</sub> | Phase U/V/W SCR driver pull-up resistor        | 5.6k      | 5%        |       |          |

| $R_{GU}$                                       | Phase U/V/W SCR driver output resistor         | 33        | 5%        |       |          |

| $R_{GV}$                                       |                                                |           | .25W      |       |          |

| R <sub>GW</sub>                                |                                                |           |           |       |          |

| R <sub>DU</sub>                                | Phase U/V/W SCR driver filter resistor         | 470       | 5%        |       |          |

| $R_{DV}$                                       |                                                |           |           |       |          |

| R <sub>DW</sub>                                |                                                |           |           |       |          |

# IR1110 ADVANCE INFORMATION

International

TOR Rectifier

## **Recommended Operating Conditions cont.**

All capacitors are rated 6.3V unless otherwise specified. All resistors are rated 1/16W unless otherwise specified. The typical connection diagram is shown in figure 3. For proper operation the device should be used with the recommended componens specified below.

| Symbol                                         | Definition                       | Тур.      | Tolerance | Units | Comments |

|------------------------------------------------|----------------------------------|-----------|-----------|-------|----------|

| C <sub>UVLO</sub>                              | Capacitor on UVLOCAP pin         | .1        | 5%        | Ī     |          |

| C <sub>1PH</sub>                               | Capacitor on 1PHCAP pin          | .001      | 5%        | Ī     |          |

| C <sub>3PH</sub>                               | Capacitor on 3PHCAP pin          | .022      | 5%        | _ [   |          |

| C <sub>ERR</sub>                               | Capacitor on DCREGC pin          | .22       | 10%       | μF    |          |

| CRAMP                                          | Capacitor on CRAMP pin           | 1.0       | 10%       |       |          |

| C <sub>PKLL</sub>                              | Capacitor on VPKLL pin           | .1        | 10%       |       |          |

| C <sub>BDIP1</sub>                             | Capacitor on BDIP1               | 3300      | 5%        | חר    |          |

| C <sub>BDIP2</sub>                             | Capacitor on BDIP2               | 1000      | 5%        | PF ·  |          |

| CHOLD                                          | Capacitor on BDIPHLD             | .33       | 10%       |       |          |

| C <sub>PK</sub>                                | Capacitor on VPK                 | .33       | 10%       |       |          |

| C <sub>WDU</sub>                               | Capacitor on WDCAPU, WDCAPV, and | .027      | 2%        |       |          |

| C <sub>WDV</sub>                               | WDCAPW                           |           |           | _     |          |

| C <sub>WDW</sub>                               |                                  |           |           | μF    |          |

| C <sub>INTU</sub>                              | Capacitor between CINTU/V/W and  | .0082     | 2%        |       |          |

| C <sub>INTV</sub>                              | INTNU/V/W                        |           |           |       |          |

| C <sub>INTW</sub>                              |                                  |           |           |       |          |

| C <sub>U,</sub> C <sub>V,</sub> C <sub>W</sub> | Capacitor in SCR driver circuit  | .0047/25V | 10%       |       |          |

| DRAMP                                          | Diode in series with RRAMP       | IN4148    |           |       |          |

| Opto1,Opto2                                    | Fault output opto couplers       | HCPL0701  |           |       |          |

**Note 1)** Power rating is based on 550VAC rms maximum. For lower AC line voltage, power can be reduced proportionally. Vac rms max = Maximum operating RMS value of AC line voltage. Use the nearest standard 1% value to calculated value. Resistor must be rated for peak line voltage.

Note 2) RPOS2 is not required if no series inductor(s) in place on positive DC bus. Resistor must be rated for peak line voltage.

**Note 3)** VDD =  $5.0V\pm2.5\%$ . If  $5.1V\pm2\%$  zener diode sets VDD, use 866k 1%.

**Note 4)** With these values LNLED is used for low line detection and is low at line voltage greater than approximately 57% of Vacrms maximum voltage.

Note 5) Use the nearest standard 1% value to calculated value.

Note 6) CRAMP and RRAMP sets the bus voltage ranp-up time. Minimum value of CRAMP is  $0.68\mu F$ , maximum value is  $3.3\mu F$ . See Operation Description - Ramp Circuit.

## **Special Mode of Operation**

#### 1. Dedicated single phase operation

For operation with a one-phase bridge, connect 1PHSEL (pin12) to VSS. Use the U and V inputs. Connect WIN (pin3) to ground. Use the SCRU (pin47) and SCRV (pin46) outputs. Use RPKD =  $3.0M\Omega$ , RWDU, RWDV =  $1.0M\Omega$ , CINTU,CINTV =  $0.0068\nu$ F 2%.

The following components can be omitted: RW1, RW2, RWDW, CWDW, RINTW, RINTRW, CINTW.

#### 2. Operation without DC bus voltage regulation

For operation without bus voltage, ie. maximum DC bus voltage only, connect VBREF (pin8) to VSS. RERR and CERR can be omitted. Connect DCREGC (pin10) to ground.

## **DC Electrical Characteristics**

$R_{BIAS}$  = 249K/1%,  $V_{DD}$  = 5.1V,  $V_{SS}$  = 5.1V and  $T_A$  = 25°C unless otherwise specified.

| Symbol                | Definition                                                          | Min.            | Тур. | Max.     | Units | <b>Test Conditions</b>        |

|-----------------------|---------------------------------------------------------------------|-----------------|------|----------|-------|-------------------------------|

| V <sub>DD</sub>       | Positive Supply Voltage                                             | 4.8             | 5.1  | 5.6      | V     | Note 3                        |

| V <sub>SS</sub>       | Negative Supply Voltage                                             | -4.8            | -5.1 | -5.6     | ]     | Note 3                        |

| I <sub>DD</sub>       | V <sub>DD</sub> Supply Current                                      |                 | 3.0  | 6.0      |       | Note 4                        |

| ISS                   | VSS Supply Current                                                  |                 | -3.0 | -5.0     | mA    | Note 4                        |

| VIN                   | Input Voltage Range for UIN, VIN, and WIN                           | 1.5             |      | 4.0      |       |                               |

| V <sub>BREF</sub>     | Input Voltage Range for VBREF                                       | 0               |      | 5.0      |       | Note 1                        |

| V <sub>IL1</sub>      | Input logic low voltage on 1PHEN, LNLSSL                            | <b> </b>        |      | -2.0     |       |                               |

| V <sub>IH1</sub>      | Input logic high voltage on 1PHEN, LNLSSL                           | 2.2             |      |          | V     |                               |

| V <sub>PCINT</sub>    | Positive Output Voltage Swing at CINTU, CINTV, and CINTW Pins       |                 | 4.0  | 4.5      |       | Peak voltage of Vin<br>= 4.0V |

| V <sub>PCR+</sub>     | Positive Output Voltage Swing at CRAMP Pin                          |                 | 4.0  | 4.5      |       |                               |

| V <sub>PCR</sub> -    | Negative Output Voltage Swing at CRAMP Pin                          | 0               |      |          |       |                               |

| I <sub>1PHCAP+</sub>  | Sourcing Current at 1PHCAP pin                                      |                 | 2.0  |          |       | 1PHCAP=VSS                    |

| I <sub>1PHCAP</sub> - | Sinking Current at 1PHCAP pin                                       |                 | 5.0  |          |       | 1PHCAP=GND                    |

| I3PHCAP+              | Sourcing Current at 3PHCAP pin                                      |                 | 3.0  |          | μΑ    | 3PHCAP=VSS                    |

| I <sub>3PHCAP</sub> - | Sinking Current at 3PHCAP pin                                       |                 | 15.0 |          | Ī     | 3PHCAP=GND                    |

| VOL <sub>LED</sub>    | Output Low Voltage at 1PHLED, LNLSLED, and                          | 0               | 0.12 | .4       |       | Output sinking                |

|                       | LNLED pins                                                          |                 |      |          |       | current = 3.0mA               |

| VOHLED                | Output High Voltage at 1PHLED, LNLSLED,                             | V <sub>DD</sub> |      | $V_{DD}$ | V     | Output sourcing               |

|                       | and LNLSLED pin                                                     | 0.4             |      |          |       | current = 3mA                 |

| UVLO                  | Undervoltage lockout between VDD-GND                                | 4.1             | 4.4  | 4.6      | 1     |                               |

| IUVLO+                | Sinking Current at UVLOCAP pin                                      | 60              | 86   | 110      | uA    | VUVLOCAP=VDD                  |

| VHSCR                 | Output Voltage at High level at SCRU, SCRV, and SCRW pins           |                 | 4.5  |          |       | IO = 1mA                      |

| VLSCR                 | Output Voltage at Low level at SCRU, SCRV, and SCRW pins            |                 | 0.1  | 0.31     | V     | IO = -1mA                     |

| VRAMPBUF              | Output Voltage at VRAMP pin                                         |                 | 4.0  |          |       |                               |

| RVBREF                | Input Resistance On VBREF pin                                       |                 | 400  |          | kΩ    |                               |

| IBDIPCAP              | Sourcing Current of BDIPCAP pin                                     |                 | 5    |          | uA    | BDIPCAP=VSS                   |

| V <sub>tLNLED+</sub>  | Peak threshold voltage on UIN/VIN/WIN pins for LNLED to switch low  | 2.2             | 2.3  | 2.4      |       | VLNSET = 1.0V                 |

| V <sub>tLNLED</sub> - | Peak threshold voltage on UIN/VIN/WIN pins for LNLED to switch high | 2.0             | 2.1  | 2.2      |       | Note 2                        |

| VtLNLS                | Peak threshold voltage on UIN/VIN/WIN pins for LNLSLED to stay low  |                 | .5   |          | V     | All input voltages present    |

| V <sub>t1PH</sub>     | Peak threshold voltage on UIN/VIN/WIN pins for 1PHLED to stay low   |                 | .5   |          |       | All input voltages present    |

# IR1110 ADVANCE INFORMATION

International

TOR Rectifier

#### **Notes for DC Electrical Characteristics**

**Note 1**) VBREF=5.0V will assure full SCR firing on to produce the maximum amount of DC bus voltage and faster convergence to the maximum DC bus voltage. Although VBREF=4.0V corresponds to the maximum voltage, it will take longer time to converge to the maximum DC bus voltage.

**Note 2)** These voltage values are linearly proportional to VLNSET. For example, if VLNSET = 2.0V, then all values are twice of those values listed in the table.

Note 3) VDD must be regulated within  $\pm 2.5\%$ . VSS must be regulated within  $\pm 5\%$ .

## **AC Electrical Characteristics**

$V_{DD}$  = 5.1V,  $V_{SS,}$  = 5.1V, CL = 1000pF and  $T_A$  = 25°C unless otherwise specified.

| Symbol             | Definition                                 | Min. | Тур.                            | Max. | Units | Test Conditions     |

|--------------------|--------------------------------------------|------|---------------------------------|------|-------|---------------------|

| tr                 | Turn-on rise time on SCRU, SCRV, and SCRW  |      | 500                             |      |       |                     |

| tf                 | Turn-off fall time on SCRU, SCRV, and SCRW |      | 500                             |      | ns    |                     |

| twscr              | Output pulse width of SCRU,SCRV, and SCRW  |      | 15                              |      | μs    |                     |

| t <sub>DLL</sub>   | LNLSLED propagation delay                  |      | 30                              |      |       | LNLSSL=VDD,         |

|                    |                                            |      |                                 |      |       | C3PH =.022uF,       |

|                    |                                            |      |                                 |      |       | (note 1)            |

| t <sub>D1PH</sub>  | 1PHLED propagation delay                   |      | 8.3                             |      | ms    | C1PH = .001uF       |

| t <sub>LN</sub>    | LNLED propagation delay                    |      | 150                             |      |       | (note 2)            |

| t <sub>S1PH</sub>  | Shutdown time after loss of single phase   |      | 15                              | 20   | ms    | 1PHEN = VDD,        |

|                    |                                            |      |                                 |      |       | CUVLO = .1mF,       |

|                    |                                            |      |                                 |      |       | C1PH = .001mF,      |

|                    |                                            |      |                                 |      |       | (note 3)            |

| tfFO               | Fall time from high to low on LNLSLED,     |      | 50                              |      | ns    | Pull-up resistor    |

|                    | 1PHLED, LNLED                              |      |                                 |      |       | = 6.2kW             |

| tW1PH              | 1PHLED pulse width                         |      | 2                               |      |       | C1PH =.001mF,       |

|                    |                                            |      |                                 |      |       | (note 4)            |

| tuvlck             | Power up UVLOCK delay                      |      | 60                              |      | msec  | CUVLCK=.1uF,        |

|                    |                                            |      |                                 |      |       | (note 5)            |

| tRAMP              | DC bus ramp time                           |      | 150                             |      |       | CRAMP=1uF,          |

|                    |                                            |      |                                 |      |       | RRAMP=82k,(note 6)  |

| VENSCR             | Minimum input voltage on UIN, VIN, and WIN | _    | R <sub>U2</sub> /R <sub>U</sub> |      | V     | (note 7)            |

|                    | for enabling SCR firing                    |      | X 12                            |      |       |                     |

| P <sub>PUBAL</sub> | Phase-to-phase unbalance between           |      | ±1.5                            |      |       | Firing angle = 90°  |

|                    | pulses on SCRU, SCRV, and SCRW             |      |                                 |      |       | Notes 8 and 9       |

|                    |                                            |      | ±3                              |      |       | Firing angle = 140° |

|                    |                                            |      |                                 |      |       | Note 9              |

See Notes on page 7

**IR1110**

#### **Notes for AC Electrical Characteristics**

- Note 1) Delay is proportional to the capacitor values with minimum allowed value of  $C_{3PH} = .01 \mu F$

- Note 2) Depends on CPKLL charge condition

- Note 3) C<sub>UVLO</sub> = .1μF, C<sub>1PH</sub> = .001μF. Increasing C<sub>UVLO</sub> increases the delay/response time of the 1phase lockout.

- Note 4) Pulse width is proportional to C1PH. Maximum allowed values of C<sub>1PH</sub> is .001μF.

- Note 5) Power up delay is set by C<sub>UVLO</sub> or by V<sub>DD</sub> rise time whichever takes longer. In this condition, V<sub>DD</sub> rise time must not be less than 100msec, and 1-phase shutdown must be enabled. If this is less than 100msec or 1-phase shut down is disabled, C<sub>UVLO</sub> must be increased to 0.22µF in order to increase the undervoltage lockout time to greater than 100msec. See Note 3) above on additional effect of increasing C<sub>UVLO</sub>.

- Note 6) Ramp time is proportional to the capacitor value.

- Note 7) This value corresponds approximately to 15V minimum SCR firing voltage. For 15V minimum SCR firing voltage,  $(R_{SG2}/R_{SG1}) \times V_{DD} = (R_{U2}/R_{U1}) \times 15$ .

- Note 8) PPUBAL applies to steady operation, is deviation of any firing point to closest balanced set of firing points.

- Note 9) Firing angle is defined with respect to zero delay (ie. max output voltage.

#### **System Operating Characteristics and Specifications**

All peripheral component values are those listed in the recommended operating condition unless otherwise specified.

| Symbol              | Definition                                        | Min.     | Тур.  | Max. | Units            | <b>Test Conditions</b>                                  |

|---------------------|---------------------------------------------------|----------|-------|------|------------------|---------------------------------------------------------|

| VAC                 | Line-to-line AC voltage range (1%)                | 80       | 120   | 140  |                  | R <sub>u1</sub> ,R <sub>v1</sub> ,R <sub>w1</sub> =475K |

|                     |                                                   |          |       |      |                  | R <sub>POS1</sub> ,R <sub>NEG1</sub> =453K              |

|                     |                                                   | 161      | 230   | 276  | V <sub>RMS</sub> | R <sub>u1</sub> ,R <sub>v1</sub> ,R <sub>w1</sub> 9537K |

|                     |                                                   |          |       |      |                  | R <sub>POS1</sub> ,R <sub>NEG1</sub> =887K              |

|                     |                                                   | 322      | 460   | 552  |                  | $R_{u1}, R_{v1}, R_{w1} = 2X953K$                       |

|                     |                                                   |          |       |      |                  | R <sub>POS1</sub> ,R <sub>NEG1</sub> =887K              |

| fLINE               | Input line frequency                              | 47       | 50/60 | 63   | Hz               |                                                         |

| V <sub>BRANGE</sub> | DC bus voltage controllable range                 | 35       |       | 99.8 | %                | V <sub>BREF</sub> =1.4V to 4V                           |

| V <sub>BREG</sub>   | DC bus voltage regulation                         |          | 2     |      | %                |                                                         |

| V <sub>BRES</sub>   | DC bus voltage step response time                 |          | 100   |      | msec             | V <sub>BUS</sub> =35% to 100%                           |

|                     |                                                   |          |       |      |                  | Note 6                                                  |

| tramp1              | DC bus voltage ramp up time at power up           | <b>-</b> | 150   |      | msec             | $C_{RAMP} = 1\mu F$                                     |

|                     |                                                   |          |       |      |                  | R <sub>RAMP</sub> = 82k                                 |

|                     |                                                   |          |       |      |                  | (Note 7)                                                |

| t <sub>RAMP2</sub>  | DC bus voltage ramp up time at power dip          |          | 75    |      | msec             | $C_{RAMP} = 1\mu F$                                     |

|                     | ride through                                      |          |       |      |                  | $R_{RAMP} = 82k$                                        |

|                     |                                                   |          |       |      |                  | (Note 7)                                                |

| tdpwr               | Power up delay time before ramp up                |          | 190   |      | msec             | C <sub>RAMP</sub> = 1µF                                 |

|                     |                                                   |          |       |      |                  | $C_{UVLO} = 0.1 \mu F$                                  |

|                     |                                                   |          |       |      |                  | Note 9)                                                 |

| tdDIP1              | Delay time to start ramp-up after recovery from   |          | 15    |      | msec             | Voltage drop below                                      |

|                     | a transient loss of line voltage                  |          |       |      |                  | the reference voltage                                   |

|                     |                                                   |          |       |      |                  | at B <sub>DIP2</sub> pin                                |

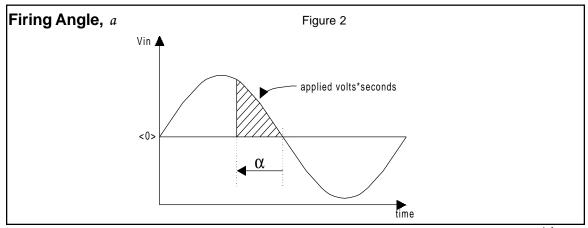

| a <sub>FIRE</sub>   | Firing angle range                                | 1.5      |       | 160  | ٥                | Figure 2, Note 14                                       |

| t <sub>d1PHS</sub>  | Delay time to shutdown SCR firing pulses after    | 15       |       | 30   | msec             | 1PHEN = V <sub>DD</sub>                                 |

|                     | loss of one phase input                           |          |       |      |                  |                                                         |

| t <sub>d1PHE</sub>  | Delay time to start ramp-up after recovery from a |          | 30    |      | msec             | 1PHEN = V <sub>DD</sub>                                 |

|                     | loss of one phase input                           |          |       |      |                  |                                                         |

# **IR1110**

International

TOR Rectifier

## **System Operating Characteristics and Specifications**

All peripheral component values are those listed in the recommended operating condition unless otherwise specified.

| td1FIRE  | First SCR firing angle at ramp-up                    | _  | 20 | 32  | 0 | CRAMP=1μF,              |

|----------|------------------------------------------------------|----|----|-----|---|-------------------------|

|          |                                                      |    |    |     |   | R <sub>RAMP</sub> = 82k |

|          |                                                      |    |    |     |   | (Note 10)               |

|          |                                                      |    | 16 | 25  | 0 | CRAMP=2.2µF,            |

|          |                                                      |    |    |     |   | $R_{RAMP} = 47k$        |

|          |                                                      |    |    |     |   | (Note 10)               |

|          |                                                      |    | 14 | 22  | 0 | CRAMP=3.3μF,            |

|          |                                                      |    |    |     |   | $R_{RAMP} = 30k$        |

|          |                                                      |    |    |     |   | (Notes10,12, 13)        |

| RLIMFIRE | Rate of advance of firing angle from last max firing | —- | 10 | 20° |   | CRAMP = 1µF,            |

|          | angle during ramp-up                                 |    |    |     |   | $R_{RAMP} = 82k$        |

|          |                                                      |    | 7  | 14  |   | CRAMP=3.3μF,            |

|          |                                                      |    |    |     |   | R <sub>RAMP</sub> = 30k |

|          |                                                      |    |    |     |   | (Notes 11 and 13)       |

#### **Notes for System Operating Characteristics**

- **Note 6)** Step change of VBREF may result in excessive bus capacitor charging current. Rate of change of VBREF should be decreased in order to limit bus capacitor charging current for practical application.

- Note 7) Time to ramp up to 99.8% DC bus level at a power up. It does not include the power up delay time. The practical limitation of the minimum time (50msec) depends on the inrush current to the DC bus capacitor. Ramp time is proportional to CRAMP.

- Note 8) Time to ramp back to 99.8% DC bus level from 50% DC bus level at a momentary power dip. This does not include the delay time to start ramp-up (tDDIP)

- Note 9) The value depends on CUVLCK

- Note 10) The value depends on CRAMP, RPK, RRAMP

- Note 11) The value depends on CRAMP

- Note 12) See operation description Ramp Circuit

- Note 13) Firing angle defined with respect to fully off (zero output voltage) firing angle.

- Note 14) Firing angle defined with respect to zero delay.

uld

tical e is

# **Operating Mode/Fault Output Matrix Chart**

|           | Fault     | Fault output  |                                                                                        |                                    |

|-----------|-----------|---------------|----------------------------------------------------------------------------------------|------------------------------------|

| Mode      | condition | indicator     | Description                                                                            | External setting                   |

|           |           | Non-          | SCR output firing active. LNLSLED = low,                                               | LNLSSL = VDD                       |

|           |           | multiplexed   | 1PHLED = high                                                                          | 1PHEN = VDD or VSS                 |

|           | Normal    |               | -                                                                                      | 1PHSEL = VDD                       |

|           |           | Multiplexed   | SCR output firing active. LNLSLED = low,                                               | LNLSSL = VSS                       |

|           |           |               | 1PHLED = high                                                                          | 1PHEN =VDD or VSS                  |

|           |           |               |                                                                                        | 1PHSEL = VDD                       |

|           | _         | Non-          | SCR output firing disabled for period of loss.                                         | LNLSSL = VDD                       |

|           | 3-phase   | multiplexed   | LNLSLED = high, 1PHLED = high                                                          | 1PHEN =VDD or VSS                  |

|           | lass      | Multipland    |                                                                                        | 1PHSEL = VDD                       |

|           | loss      | Multiplexed   | SCR output firing disabled for period of loss.  LNLSLED = high, 1PHLED = high (Note 1) | LNLSSL = VSS<br>1PHEN =VDD or VSS  |

|           |           |               | LINESLED = High, TPHLED = High (Note 1)                                                | 1PHSEL = VDD                       |

|           |           | Non-          | SCR output firing active.                                                              | LNLSSL = VDD                       |

|           | 1-phase   | multiplexed   | LNLSLED = low, 1PHLED = toggles low for                                                | 1PHEN = VSS                        |

| 3-phase   | loss      | тапроход      | 2msec once or twice per line cycle                                                     | 1PHSEL = VDD                       |

| Input     | without   | Multiplexed   | SCR output firing active.LNLSLED toggles                                               | LNLSSL = VSS                       |

| operation | shutdown  |               | high while 1PHLED toggles low for 2msec                                                | 1PHEN = VSS                        |

| '         |           |               | once or twice per line cycle. (Note 2)                                                 | 1PHSEL = VDD                       |

|           |           | Non-          | SCR output firing disabled for period of loss.                                         | LNLSSL = VDD                       |

|           | 1-phase   | multiplexed   | LNLSLED = low, 1PHLED = toggles low                                                    | 1PHEN = VDD                        |

|           | loss      |               | for 2msec once or twice per line cycle                                                 | 1PHSEL = VDD                       |

|           | with      | Multiplexed   | SCR output firing disabled for period of loss.                                         | LNLSSL = VSS                       |

|           | shutdown  |               | LNLSLED toggles high while 1PHLED toggles                                              | 1PHEN = VDD                        |

|           |           |               | low for 2msec once or twice per line cycle. (Note 2)                                   | 1PHSEL = VDD                       |

|           | High/Low  | LNLED         | If line voltage exceeds the specified level on                                         | LNSET=desired voltage,             |

|           | AC line   |               | LNSET voltage, then LNLED = low. Otherwise                                             | 1PHEN =VDD or VSS                  |

|           |           |               | LNLED = high                                                                           | 1PHSEL = VDD                       |

|           |           | Non-          | SCR output firing disabled for period of loss.                                         | LNLSSL = VDD                       |

|           |           | multiplexed   | LNLSLED = high, 1PHLED = high                                                          | 1PHEN =VDD or VSS                  |

|           | 1-phase   |               |                                                                                        | 1PHSEL = VSS                       |

|           | loss      | Multiplexed   | SCR output firing disabled for period of loss.                                         | LNLSSL = VSS                       |

|           |           |               | LNLSLED = high, 1PHLED = high                                                          | 1PHEN =VDD or VSS                  |

|           |           |               |                                                                                        | 1PHSEL = VSS                       |

| 1-phase   |           | Non-          | SCR output firing active. LNLSLED = low.                                               | LNLSSL = VDD                       |

| input     | Name      | multiplexed   | 1PHLED toggles low for 2msec once or twice                                             | 1PHEN =VDD or VSS                  |

| operation | Normal    | Multiplexed   | per line cycle SCR output firing active. LNLSLED toggles                               | 1PHSEL = VSS<br>LNLSSL = VSS       |

|           |           | iviuitipiexed | high while 1PHLED toggles low for 2msec                                                | 1PHEN =VDD or VSS                  |

|           |           |               | once or twice per line cycle. (N ote 2)                                                | 1PHEN = VDD 01 VSS<br>1PHSEL = VSS |

|           | High/Low  | LNLED         | If line voltage exceeds the specified level on                                         | LNSET=desired voltage,             |

|           | AC line   |               | LNSET voltage, then LNLED = low. Otherwise                                             | 1PHSEL= VSS                        |

|           |           |               | LNLED = high                                                                           | 1PHEN =VDD or VSS                  |

|           |           |               | <u> </u>                                                                               |                                    |

Note 1) LNLSLED may toggle high once for 2msec after event of phase loss.

Note 2) 1PHLED and LNLSLED are completely synchronized and complementary.  $\mbox{www.irf.com}$

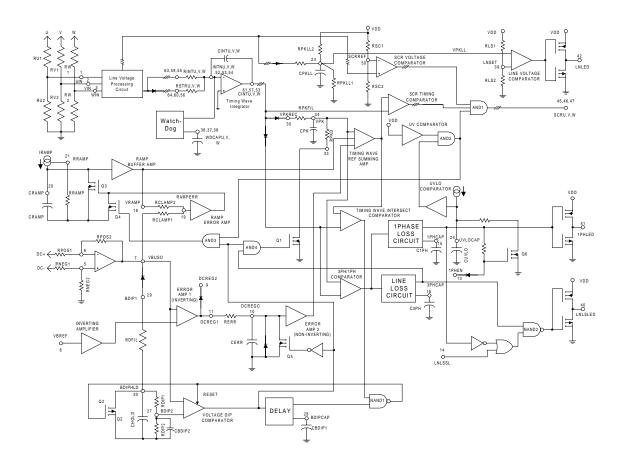

# **Functional Block Diagram**

# **Typical Connection Diagram**

# IR1110

## **ADVANCE INFORMATION**

International

Rectifier

# **Lead Definitions**

| Symbol      | Pin#     | Description                                                        |

|-------------|----------|--------------------------------------------------------------------|

| DVDD        | 44       | Logic positive supply voltage.                                     |

| DGND        | 43       | Logic ground                                                       |

| DVSS        | 31       | Logic negative supply voltage                                      |

| AVDD        | 17       | Analog positive supply voltage                                     |

| AGND        | 25,26,43 | Analog ground                                                      |

| AVSS        | 4,31,51  | Analog negative supply voltage                                     |

| UIN/VIN/WIN | 1,2,3    | Phase U/V/W voltage inputs                                         |

| VBAMPP      | 5        | DC bus OP Amp. positive input, connect to DC bus(-) via resistor   |

| VBAMPN      | 6        | DC bus OP Amp. negative input, connect to DC bus (+) via resistor  |

| VBUSO       | 7        | DC bus OP Amp. output                                              |

| VBREF       | 8        | DC bus regulation voltage reference input                          |

| DCREG2      | 9        | DC bus error amplifier output via series diode                     |

| DCREG1      | 11       | DC bus error amplifier output                                      |

| DCREGC      | 10       | DC bus error compensation (External capacitor connection pin)      |

| 1PHSEL      | 12       | Single phase input mode select.  Note 1) on page 12                |

| 1PHEN       | 13       | Single phase shutdown mode enable. Note 2) on page 12              |

| LNLSSL      | 14       | Phase loss Fault Output Select. Note 3) on page 12                 |

| 1PHCAP      | 15       | Single phase loss detect timing capacitor                          |

| 3PHCAP      | 16       | Three phase loss detect timing capacitor                           |

| VRAMP       | 18       | Buffered voltage ramp circuit output                               |

| RAMPERR     | 19       | Ramp error amplifier input                                         |

| CRAMP       | 20       | Ramp timing capacitor                                              |

| RRAMP       | 21       | Ramp timing resistor                                               |

| RBIAS       | 22       | Bias current resistor                                              |

| VPKLL       | 23       | Line-to-line peak voltage holding capacitor                        |

| UVLOCAP     | 24       | Under voltage lockout delay capacitor                              |

| BDIP1       | 29       | DC bus voltage dip detection 1                                     |

| BDIP2       | 27       | DC bus voltage dip detection 2                                     |

| BDIPHLD     | 30       | DC bus voltage dip hold capacitor                                  |

| BDIPCAP     | 28       | DC bus voltage dip timing capacitor                                |

| VPKDISC1    | 33       | Line synchronization timing wave peak voltage discharging resistor |

| VPKDISC2    | 32       | No connection                                                      |

| VPK         | 34       | Line synchronization timing wave peak voltage                      |

| VPKREC      | 35       | Line synchronization timing waveform                               |

| WDCAPU/V/W  | 38,37,36 | Watchdog timing capacitor for phase U, V, and W                    |

| LNSET       | 39       | Line voltage comparator reference input                            |

| LNLSLED     | 40       | Line Loss Fault Output                                             |

| 1PHLED      | 41       | Single Phase Loss Fault Output                                     |

| LNLED       | 42       | High/Low line status Output                                        |

| CINTU/V/W   | 61,57,53 | Phase U/V/W integral amplifier output                              |

| INTNU/V/W   | 62,58,54 | Phase U/V/W integral amplifier negative input                      |

| RINTU/V/W   | 63,59,55 | Phase U/V/W integral amplifier resistor connection                 |

| RSTRU/V/W   | 64,60,56 | Phase U/V/W integral discharge resistor                            |

| SCRU/V/W    | 47,46,45 | Phase U/V/W SCR gate signal                                        |

| TEST1       | 48       | Test purpose pin (Should be tied to VDD)                           |

|             | 49       | Test purpose pin (No connection should be made)                    |

| TEST2       | 43       | i lest pulpose pill tho colliection silouid be made.               |

#### **Lead Definitions**

**Note 1)** 1PHSEL = VDD for 3 phase operation, 1PHSEL = VSS for 1 phase operation. See Operating Mode/Fault Output Matrix Chart for the detail.

**Note 2)** 1PHEN = VDD for enable, 1PHEN = VSS for disable. See Operating Mode/Fault Output Matrix Chart for the detail.

**Note 3)** LNLSSL = VDD for total line loss only, LNLSSL = VSS for multiplexing total line loss/1 phase loss. See Operating Mode/Fault Output Matrix Chart for the detail.

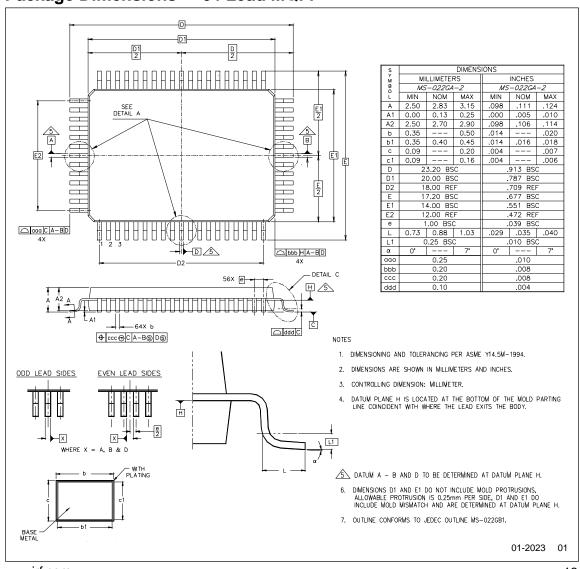

## Package Dimensions - 64 Lead MQFP

# **Operation Description**

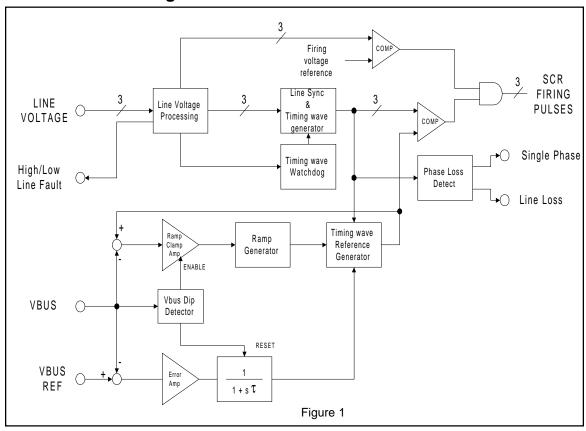

#### **Overall Functional Diagram**

A detailed functional diagram of the IR1110 and peripheral components is shown in Figure 4. The IR1110 receives signals from the AC input lines U, V, W, and DC bus voltage, DC+, DC-, via resistor dividers, and delivers line-synchronized pulses SCRU, SCRV, SCRW to external SCR gate driver circuits. The timing of these pulses controls the DC bus voltage.

The IR1110 also delivers Status Feedback signals, that denote loss of all input phases, loss of one input phase and low/high AC line voltage.

The "ground" of the IR1110 is common with the SCR cathodes.

#### Line Voltage Processing circuit

The inputs to the line voltage processing circuit represent the voltage across the SCRs. Each of the three outputs of this circuit, RINTU, RINTV, RINTW is a voltage waveform that is negative over the range of control of firing angle of the associated SCR, and positive outside this range.

The possible portion only of these waveforms appears at RSTRU, RSTRV, RSTRW.

#### **Timing Wave Integrators**

Each Timing Wave Integrator integrates the negative portions of the output waveforms of the Line Voltage Processing circuit, via RINT, and the positive portions, via RINT and RINTR in parallel.

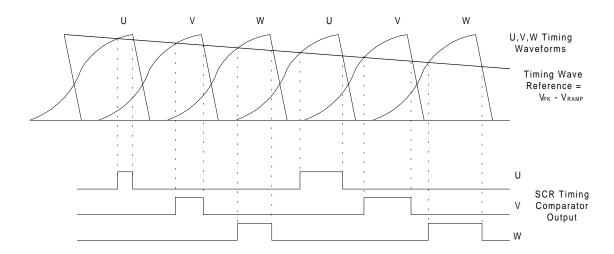

The outputs, CINTU, CINTV, CINTW are a set of line synchronized "sawtooth" timing waves. These have the desired phase relationship to the line voltages, so that intersection of these waves with the Timing Wave Reference defines the SCR firing instants. See Figure 5.

#### **VPKL-L Store**

Voltages Uin-Vin, Vin-Win, Win-Uin are rectified and the peak value, proportional to the peak line voltage, is stored on Cpkll. The time constant of Rpkll1 and Rpkll2 with Cpkll allows Vpll to track changes of line voltage that take place over a number of cycles, while maintaining an essentially smooth waveform.

#### Watchdog

The watchdog resets the Timing Wave Integrator within a few milliseconds of the normal reset point, should an abnormality in the line voltage waveshapes, such as one or all input phases missing, prevent resetting at the normal time.

In the normal operation, the watchdog circuit plays only a passive role.

#### VPK Store

CPK stores a voltage, VPK, that is essentially equal to the peak of the timing waves. RPKD is normally connected to ground via Q1. The time constant of RPKD with CPK allows VPK to track changes of amplitude of the timing waves that take place over a number of cycles, while maintaining an essentially smooth waveform.

#### **Ramp Circuit**

The current source, IRAMP, creates an increasing voltage, VRAMP, across CRAMP, whenever Q3 has been conducting, then switches OFF. The maximum value of VRAMP is clamped at VPK.

VRAMP controls the ramp-up rate of the bus voltage. RRAMP shapes VRAMP to a parabolic form, which gives an approximately linear rise of DC bus voltage with a capacitive load.

The rate of change of VRAMP at the start of the ramp is set by CRAMP. RRAMP also has some influence on the initial rate of change, but more influence later during the ramp-up period.

The greater the initial rate of rise of VRAMP, the greater the maximum first firing angle. Typical relationships between CRAMP, RRAMP, tDPWR, tRAMP1, and tD1FIRE are as follows:

| Скамр | RRAMP      | <b>t</b> DPWR | <b>t</b> RAMP | t <sub>D1FIRE</sub> |

|-------|------------|---------------|---------------|---------------------|

| uF    | k $\Omega$ | (typical)     | (typical)     | (max)               |

|       |            | msec          | msec          | degrees             |

| 0.68  | 130        | 165           | 100           | 35                  |

| 1     | 82         | 190           | 150           | 32                  |

| 2.2   | 47         | 230           | 220           | 25                  |

| 3.3   | 30         | 270           | 330           | 22                  |

The minimum and maximum permissible values of CRAMP are 0.68uF and 3.3uF respectively. Total ramp-up time can be increased above the values shown by increasing RRAMP. For example, with CRAMP=3.3uF and RRAMP open, ramp-up time increases to about 1.2 seconds.

The maximum first firing angle is specified at maximum AC input voltage, and assumes that worst case cumulative tolerances of the governing external components cause sufficient phase-to-phase unbalance that firing on one phase only occurs during the early part of ramp-up.

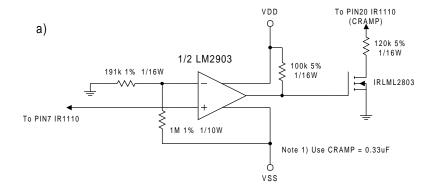

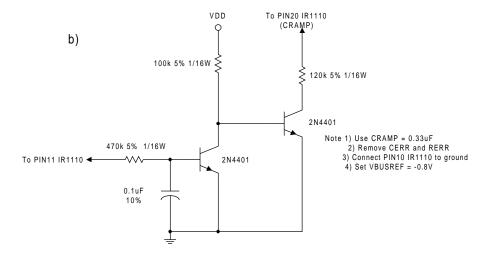

The circuit in Figure 15(a) will reduce the maximum first firing angle to  $17^{\circ}$ , if desired. If the voltage regulation function is not used, and the circuit of Figure 13 is not used, the Figure 15(b) circuit can be used in place of the Figure 15(a) circuit for the same purpose. With either circuit, both tdpwr and tramp will increase to about 400msec.

#### **Ramp Clamp Circuit**

When Q4 is OFF, the ramp clamp is enabled, and Q3 is controlled by the output of the Ramp Error Amplifier. This amplifier compares |Vbuso|, via Rclamp1, with Vramp, via Rclamp2. The amplified output drives Q3 in a linear mode, diverting Iramp from Cramp and forcing Vramp to be essentially equal to Vbuso x Rclamp2/Rclamp1.

**IR1110**

International

TOR Rectifier

During transient line voltage outage, the Ramp Clamp is enabled. VRAMP is then forced into the above relationship with VBUSO. The amplitude of VRAMP is thereby preset when the line voltage returns, so that the bus voltage ramps back without significant delay, but also without unacceptable jump of bus voltage.

The choice of RCLAMP2/RCLAMP1 is a compromise between the delay in starting ramp-back of the output voltage, and the initial jump of voltage when the line voltage returns after outage.

With an inductive filter at the output of the rectifier, Rclamp2/Rclamp1 can be set to a higher value than with just a bus capacitor, to minimize the response time in restoring the DC bus voltage after line outage.

#### **Timing Wave Reference Summing Amplifier**

The output of the Timing Wave Reference Summing Amplifier is the Timing Wave Reference; this is essentially the difference between VPK and VRAMP, so long as the output of Error Amplifier 2 is zero. Thus, when VRAMP is zero, the Timing Wave Reference voltage is essentially equal to VPK, and SCR firing angle is close to the zero crossing of the line-to-line voltage; as the ramp increases, the firing angle advances. Refer to Figure 5.

#### **Closed Loop Bus Voltage Regulation**

The bus voltage reference, -VBUSREF, sets the amplitude of the steady bus voltage. This external reference is negative with respect to "ground", i.e., with respect to the positive output terminal of the rectifier bridge. This facilitates derivation of VBUSREF, if required, via a level shift circuit that is referenced to the negative DC bus.

If bus voltage control is not used, and steady operation at the maximum DC bus voltage only is required, VBUSREF should be connected to Vss.

The Inverting Amplifier inverts the reference to +VBUSREF. If the maximum possible value of |VBUSO| is less than |VBUSREF|, the voltage regulation loop is inactive. The average output of Error Amplifier 1 is always negative, the voltage across CERR is clamped to zero by the parallel diode, the output of Error Amplifier 2 is always zero, and the bus voltage ramps to the maximum possible value.

If |VBUSO| becomes greater than |VBUSREF|, the average output of Error Amplifier 1 becomes positive. This output is filtered by Rerr and Cerr, and a smooth voltage representing the dc error between |VBUSO| and |VBUSREF| appears across Cerr. This voltage is amplified by Error Amplifier 2, and fed as an input to the Timing Wave Reference Summing Amplifier. The added input to the Timing Wave Reference Summing Wave Reference, delaying the SCR firing angle, and forcing the bus voltage to a value proportional to |VBUSREF|.

Since the voltage regulation circuit becomes active only when |VBUSO| exceeds |VBUSREF|, the ramp rate during power-up of the bus voltage is determined solely by the rate of increase of VRAMP. If |VBUSO| starts to exceed |VBUSREF| during ramp up, the output of Error Amplifier 2 starts to oppose the increasing ramp voltage, restraining further increase of bus voltage. Some overshoot occurs while the ramp continues to increase to VPK.

In normal operation, after ramp up, the bus voltage is no longer controlled by the ramp, unless an event occurs that causes the ramp to be clamped.

Rise and fall rates of the bus voltage that are driven by changes in |VBUSREF| in normal operation are determined by the applied rise and fall rates of |VBUSREF|, and by the characteristics www.irf.com

**IR1110**

of the load connected to the DC bus. The rate of increase of applied |VBUSREF| should be limited if necessary, to limit the bus capacitor charging current.

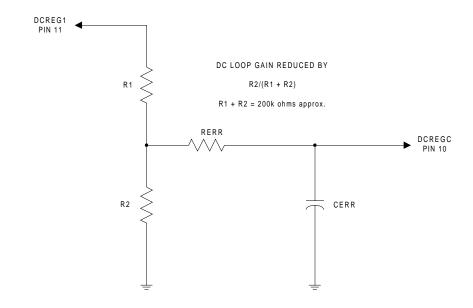

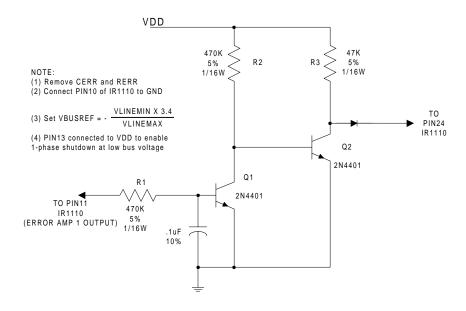

#### Adjustment of DC loop gain

The voltage regulation loop may exhibit uneven firing angle from one SCR to the next, with loads which have unusually high ripple voltage. Such ripple instability, if it occurs, can be corrected by reducing the DC loop gain. Figure 6 shows how this is done with a voltage divider, R1 and R2, in the voltage regulation loop.

#### **SCR Timing Comparators**

Each SCR Timing Comparator delivers a high output whenever the Timing Wave is instantaneously greater than the Timing Wave Reference. The leading edge is the demanded initiation point for the SCR firing pulse.

The duration of the output pulse of the SCR timing comparator is generally much longer than needed to fire the SCR, because the Timing Wave remains higher than the Timing Wave Reference for a significant portion, if not all, of the total cycle time. See Figure 5.

#### **SCR Voltage Comparators**

Each SCR Voltage Comparator compares the instantaneous anode-cathode voltage of the SCR with a fixed reference, SCRREF, which is set by Rsg1 and Rsg2. This reference is set to represent an actual anode-cathode voltage of about 15V, before attenuation through the input divider resistors.

When the instantaneous SCR anode voltage is greater than 15V, the output of the SCR Voltage comparator is high. The outputs of the SCR Voltage and Timing Comparators are ANDed to obtain the output SCR timing pulses, SCRU, SCRV, SCRW.

The SCRU, SCRV, SCRW output pulses are thus controlled so that;

- a) they do not occur when the Timing Wave is less than the Timing Wave Reference

- b) they do not occur unless the instantaneous SCR voltage is at least 15V positive

- c) they are terminated when the instantaneous anode-cathode voltage falls below 15V; -i.e. as soon as the SCR turns on

With discontinuous output current, more than one firing pulse per cycle for each SCR may be generated.

The pulse width of SCRU, SCRV, SCRW is about 6usec at maximum output voltage, and about 13usec at reduced output voltage.

#### **SCR Gate Drivers**

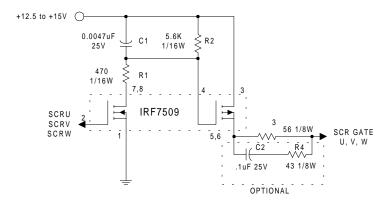

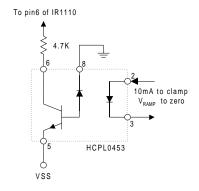

The SCR gate driver circuit, shown in Figure 7, amplifies and stretches the SCRU, SCRV, SCRW timing pulses. C1 and R2 stretch the duration of the output pulse to 60-80usec. This is generally necessary to ensure reliable SCR turn-on.

C2 and R4 provide an initial peak turn-on firing current of about .45A, decaying to about .2A within 5usec. The maximum average current consumed by the three SCR driver circuits is about 10mA.

If C2 and R4 are omitted, the peak firing current will be reduced to about .2A. R3 can be decreased to say 33W, to restore the peak firing current to .45A; the maximum average supply current will now increase to about 20mA.

# **IR1110**

International

TOR Rectifier

#### **Voltage Dip Circuit**

The DC bus voltage will fall if the input line voltage dips or is lost.

For short period outage, the bus capacitor voltage may hold up sufficiently that ramp back when the line voltage returns is unnecessary.

If the bus voltage falls below a preset level, then the ramp is automatically clamped, in order to avoid an unacceptable jump of bus voltage when the line returns.

The Voltage Dip Comparator monitors dips on the DC bus voltage. The bus voltage, - Vbuso, is captured on Chold. The Voltage Dip Comparator compares a fraction of this captured voltage, with -Vbuso.

In normal operation, |kVBUSO| is less than |VBUSO|, and the output of the Voltage Dip Comparator is high. When a short line outage occurs, the voltage captured on CHOLD remains substantially equal to the pre-dip value, while |VBUSO| starts to decrease as the bus capacitor discharges. If |VBUSO| dips to less than k x VBUS1, where VBUS1 is the initial bus voltage, the output of the Voltage Dip Comparator latches low, Q4 is switched off and the ramp is clamped. Q5 is turned ON, discharging the voltage on CERR.

$$kV_{BUS1} = \frac{R_{DIP2}}{R_{DIP1} + R_{DIP2}} x V_{BUS1} - (0.1 V_{LLMAX})$$

where VLLMAX is the maximum design value of rms line voltage

The Voltage Dip Comparator remains low for a minimum period, TDELAY2, of approxmately 5 milliseconds, set by CBDIP1. Thereafter, so long as the line voltage is absent or remains abnormally low, the output of the Timing Wave Intersect Comparator remains low, keeping the Voltage Dip Comparator latched low.

TDELAY2 in milliseconds is approximately equal to (.0015 X CBDIP1 pF). Thus for CBDIP1 = 3300pF, TDELAY2 is about 5 milliseconds.

The total delay, TDELAY\_TOT, between the point of initiation of the line voltage outage, and the point at which the voltage dip comparator is allowed to reset, must be at least 10 milliseconds.

TDELAY\_TOT is the sum of TDELAY1 and TDELAY2. TDELAY1 is the time between the point of initiation of the line outage, and the point at which the bus voltage falls to kVBUS1. Thus, with TDELAY2 set at 5 milliseconds, the minimum allowed value for TDELAY1 is 5 milliseconds.

If the bus capacitor is sized so that, at maximum DC load current, the bus voltage will fall to kVBUS1 in less than 5 milliseconds, then CBDIP1 should be increased to ensure that TDELAY\_TOT cannot fall below 10 milliseconds.

If CBDIP1 is increased so that TDELAY2 is at least 10 milliseconds, TDELAY\_TOT will always be greater than 10 milliseconds. This is an inherently safe design approach, though it does add a few milliseconds of potentially unnecessary delay, before ramp-back can commence during a short line outage.

After the above delay, the Voltage Dip Comparator is reset when the output of the Timing Wave Intersect Comparator goes high, which occurs when the line voltage returns to normal. Q2 is momentarily turned ON, allowing the voltage on Chold to reset. Q4 is turned ON, unclamping the Ramp, and Q5 is turned OFF, unclamping CERR. Ramp-back of the bus voltage now occurs.

When the output of the Voltage Dip Comparator is low, Q1 is turned OFF. RPKD is then disconnected from ground, allowing CPK to hold its charge during the voltage dip.

#### Voltage Dip during Dynamic Regulation

If |VBREF| is rapidly decreased by a sufficient amount, this may cause a decrease of bus voltage that will set the Voltage Dip Comparator and cause the bus voltage to undershoot.

Since the timing waves are still present, the output of the Timing Wave Intersect Comparator remains high, and the Voltage Dip Comparator will be quickly reset, ramping the bus voltage back to the set value.

This undershoot of the bus voltage will be avoided if changes in |VBUSREF| are controlled at a rate that does not significantly "overtake" the discharge rate of CHOLD, which is set by CHOLD, RDIP1 and RDIP2.

#### **Undervoltage and Undervoltage Lockout Comparators**

The UV Comparator delivers a high output when VDD exceeds the internally fixed reference value.

The UV Lockout Comparator delivers a high output when the voltage Cuvlo exceeds a nominal value of about 1.5V. Cuvlo is driven from a current source of approximately 2uA.

The outputs of the UV and UV Lockout Comparators are ANDed. When the output of either comparator is low, the SCR firing pulses are inhibited, and Q4 is turned OFF, clamping the ramp.

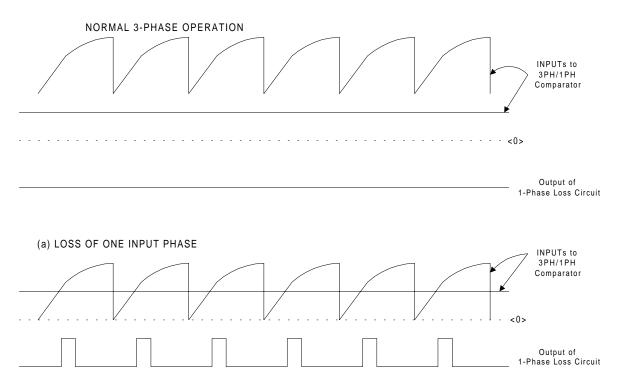

#### One Phase Loss Circuit

A train of fixed duration (nominal 2msec) pulses are delivered to the gate of Q6, if one input phase is missing. With 1-phase shutdown enabled, each 1-phase loss pulse discharges Cuvlo by about 1.5V. During the third successive pulse, Cuvlo is discharged sufficiently that the output of the UV Lockout Comparator goes low.

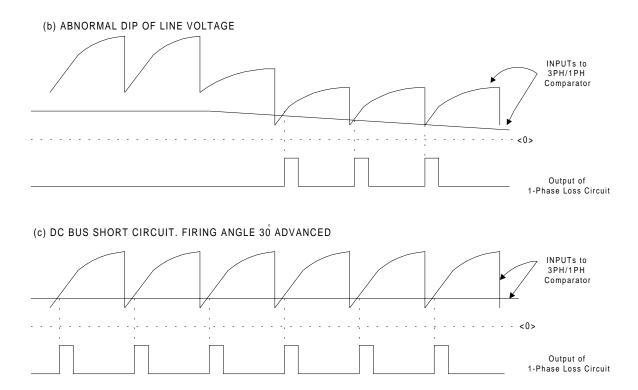

The principle of generation of the 1-phase loss pulses is illustrated in Figure 8. These pulses are generated;

- (a) during one phase loss

- (b) briefly during abnormal dips of line voltage

- (c) if the DC bus is short circuited and the SCR firing angle is advanced by more than about 30° from the zero crossing of the line voltage

With 1-phase shutdown enabled, generation of "1-phase loss" pulses under condition (b) reinforces the ramp clamp function. Under condition (c) it results in automatic limiting of short circuit current, as explained later.

The 1-phase loss pulses at 1PHLED output follow the output of the 1-Phase Loss Circuit.

# **IR1110**

International

TOR Rectifier

#### **Line Loss Circuit**

The output of the line loss detection circuit is high in normal operation. If all input phases are lost, it goes low, after a delay, determined by C<sub>3PH</sub>, which would typically be set to about 2 cycles.

When the output of the Line Loss circuit goes low, Q1 is turned OFF. This disconnects RPKD from ground, allowing CPK to hold its charge during the line outage.

The output of the line loss circuit feeds via NAND 2 to the LNLSLED output driver. If LNLSSL is connected to Vss, the 1-phase loss pulses are multiplexed with the output of the line loss circuit at the LNLSLED output. If LNLSSL is connected to Vdd, the LNLSLED signal signifies loss of all input phase only.

#### **Line Voltage Comparator**

The output of the Line Voltage Comparator is low when VPKLL exceeds a reference value that is set by RLs1 and RLs2. The LNLED output follows the output of the Line Voltage comparator.

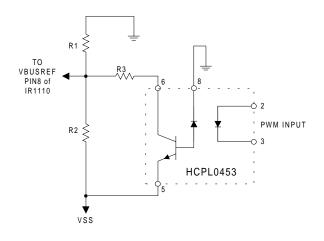

#### **PWM Control of VBUSREF**

VBUSREF can be controlled by Pulse Width Modulation (PWM). The IR1110 responds only to the average value of this waveform; suitable PWM frequency is in the range of one to several kHz.

Figure 9 shows an opto-coupler circuit for transmitting an isolated PWM input. Control of the ON/OFF duty cycle of the opto-transistor, from 0 to 100%, controls the average value of VBUSREF from VMIN to VMAX, where;

$$V_{MIN} = \frac{R_1}{R_1 + R_2} V_{SS}$$

$$V_{MAX} = \frac{R_1}{R_1 + R'} V_{SS}$$

$$R' = \frac{R_2R_3}{R_2 + R_3}$$

The average value of VBUSREF(D) at duty cycle D is:

$$V_{BUSREF}(D) = V_{MIN} + D(V_{MAX} - V_{MIN})$$

As an example, if Vss = -5.0V,  $R_1 = 7.32k$ ,  $R_2 = 16.9k$ ,  $R_3 = 1.91k$ , then the average value of VBUSREF will be controlled from approximately -1.5V to -4.0V, corresponding to a range of control of the bus voltage from 37.5% to 100% of the maximum value at maximum operating line voltage.

#### **Dedicated One Phase Operation**

The IR1110 can be set for dedicated operation of a 1-phase half-controlled SCR bridge. The UIN and VIN input terminals are used. No connection is made to WIN.

When Pin 12 is connected to Vss, the W timing wave and watchdog circuits are disabled, the watchdog reset time is optimized for 1-phase operation, and 1-phase shutdown is disabled, regardless of the connection of Pin 13.

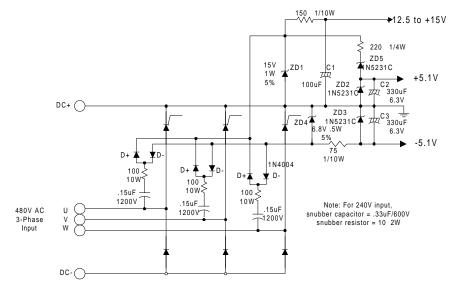

#### **Snubber Derived Power Supply**

Snubbers will generally be required, either across the AC lines or directly across the SCRs, to limit dv/dt when the line voltage is switched on.

If SCR snubbers are used, the snubber current can be used to derive the power supply voltages for the IR1110 and SCR drivers.

With reference to Figure 10, positive snubber current flows via the three RC snubbers and the D+ diodes, to create a nominal 15V supply across ZD1 and C1, for the SCR driver.

A nominal positive 5.1V VDD supply is developed across ZD2 and C2. Negative snubber current flows via D- diodes, to create a nominal -5.1V Vss supply across ZD3 and C3.

The ZD1 and ZD4 protect the supply voltages against transients on the line voltages.

This power supply circuit requires that the average current consumed by the SCR driver circuits does not exceed about 10mA.

Note that an auxiliary winding on a DC bus derived switching power supply would not by itself serve the IR1110. This is because bus-derived power cannot deliver voltage until *after* charging of the DC bus capacitor has already commenced, while the IR1110 must be powered *before* charging of the bus capacitor commences.

It would be possible to use an auxiliary winding on a DC bus derived power supply to supplement the snubber derived power. This could be preferred where the AC input line inductance is high, therefore only minimal snubbers - insufficient to furnish the total power required by the IR1110 and SCR drivers - are needed for dv/dt protection of the SCRs.

Figure 4 Detailed Functional Block Diagram

Figure 5 Timing Waveforms, Timing Wave Reference SCR Timing Comparators

Figure 6 Circuit for Reducing the DC loop gain

Figure 7 SCR Gate Driver Circuit

Figure 8, 8(a) Principle of Generation of 1-Phase Loss Pulses

Figure 8(b), 8(c) Principle of Generation of 1-Phase Loss Pulses

Figure 9 Circuit for PWM Control of DC Bus Voltage

Figure 10 Snubber Derived Power Supply

1.0msec < T0 - T1 < 80msec

100msec < T1 - T2

T3 - T4 < 40msec

VSS should track VDD within +/-10% during rise/fall time

Note: T4 is the event of Undervoltage Lockout

**Figure 11 Power Supply Requirement**

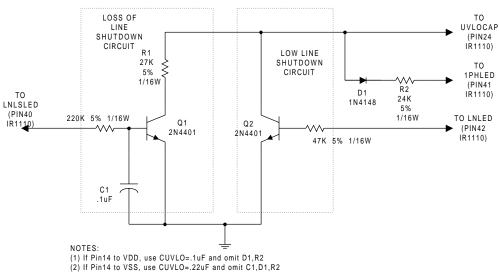

- (3) If power supply rise time < 80msec (Figure 11), connect pin 14 to VSS, use CUVLO=.22uF, and omit C1,D1,R2.

(4) If Figure 13 circuit is used. Connect pin 14 to VDD. Use CUVLO=0.22uF and R1=0.

(5) Set RLS1, RLS2 for LNLED low above 85% of min operating voltage

Figure 12 Loss of Line and Low Line Shutdown Circuits

Figure 13 Circuit for Enabling 1-Phase Shutdown During Ramp-Up, Disabling During Normal Operation (Bus Voltage Control Function Not Used)

Figure 14 Circuit for Externally Clamping VRAMP to zero

Figure 15 Circuits for reducing tDIFIRE

## **Operating Scenarios and Design Options**

#### **Power Supply Response Characteristics**

The UV comparator responds to the amplitude of the VDD supply, to control the ramp clamp. In order to correctly accomplish this function, the power supply should have the response characteristics illustrated in Figure 11, and 1-phase shutdown must be enabled. A minimum rise time of 100msec during initial power-up is required to provide sufficient delay time, before the output of the UV comparator goes high, for VPK to become established before ramp-up commences.

During loss of line voltage, VDD should not hold up above 4.0V for more than 40msec, to ensure timely clamping of the ramp via the UV comparator.

The snubber derived power supply in Figure 10 has the required rise time, however holdup time exceeds 40msec. Timely clamping of the ramp can instead be accomplished by the external Loss of Line Shutdown circuit, described below.

If 1-phase shutdown is disabled, the rise time of VDD must be increased to about 200msec to control the ramp clamping function. In this case it may generally be better to control the ramp clamp via the UVLO comparator, by increasing CUVLO to 0.22uF. The rise time of VDD is no longer critical, and can have a minimum value of 1msec.

#### **Loss of Line Shutdown circuits**

The Loss of Line Shutdown circuit in Figure 12 clamps the ramp during line outage, via the Undervoltage Lockout Comparator.

The Note (3) option of Figure 12 also eliminates dependence on a minimum power supply rise time of 80msec. Cuvlo is increased to 0.22uF, to provide sufficient delay during power-up, via the UVLO Comparator. The rise time of the power supply is not now critical, and can have a minimum value of 2.0msec.

A side effect of increasing CuvLo is to increase the shutdown time when one phase is lost. With Pin 14 connected to Vss, this is corrected by Q1 being turned on during each 1-phase loss pulse, which adds to the discharge current for CuvLo, via R1.

#### Low Line Shutdown circuit

The Low Line Shutdown circuit in Figure 12 clamps the ramp and removes the SCR firing pulses if the line voltage falls to less than 85% of the minimum normal operating level. This circuit may not be necessary for all applications, but its inclusion will provide added insurance of correct operation during abnormal low line conditions.

#### Loss of one phase during three phase operation

The 1-Phase Shutdown circuit clamps the ramp and removes the SCR firing pulses if one input phase is lost for more than about one cycle. When the missing phase returns, the ramp is unclamped and the bus voltage ramps back to the set value.

If 1-Phase Shutdown is disabled, the IR1110 will continue to deliver DC bus voltage when one input phase is lost. A potential problem arises, however, if the bus voltage is being regulated significantly below the maximum value. If one phase is lost and the ramp remains unclamped for more than one or two cycles, when the missing phase returns the bus voltage may transiently jump to almost the maximum possible value, before it is regulated back to the set value. This can www.irf.com

result in excessive bus capacitor charging current.

For this reason it is recommended that the 1-Phase Shutdown circuit is enabled, (Pin 13 connected to VDD) in designs where the voltage control function of the IR1110 is used.

For designs where the voltage control function is not used, operation at full bus voltage, with 1 Phase Shutdown disabled, allows natural transitioning from 3-Phase to 1-Phase operation, and vice versa, without excessive voltage jumps.

With 1-Phase Shutdown disabled, however, transient loss of one phase, during the early part of ramp-up, could cause a jump of bus voltage and a high instantaneous bus capacitor charging current, if the missing phase returns before ramp-up has finished, while the instantaneous bus voltage is still low.

The likelihood is remote of one phase being lost and then returning during the infrequently occurring first 50 to 100ms window of the initial ramp-up period. Given the improbability of such an event, provided the instantaneous charging current cannot exceed the surge capability of the SCRs, no additional remedy may generally be necessary.

The circuit shown in Figure 13 can be used to protect against this unlikely event, if judged necessary. The polarity of the Error Amplifier 1 average output signifies whether the instantaneous bus voltage is above or below a fixed level, set by VBREF.

If one phase loss occurs during ramp-up, when the bus voltage is instantaneously below the set level, the output of Error Amplifier 1 is negative, and Q2 is ON, 1-Phase Shutdown is enabled. If one phase loss occurs at instantaneous bus voltage above the set level, Q2 is OFF and the voltage on Cuvlo is pulled high by R3, disabling 1-Phase Shutdown.

#### **DC bus Short Circuit**

With a short circuit across the DC bus, the line-to-line voltages collapse to zero at the SCR firing instants, causing the timing waves to terminate prematurely.

If a short circuit is present at start up, 1-phase loss pulses start to be generated as the ramp increases, and the firing angle advances by more than about 30°. See Figure 8. With 1-Phase Shutdown enabled, these pulses set the UV lock comparator and clamp the ramp.